BiCMOS PFC/PWM Combination Controller

UCC18500/1/2/3

UCC28500/1/2/3

UCC38500/1/2/3

PRELIMINARY

FEATURES

nd

Combines PFC and 2

•

Converter Function

Controls Boost PWM to Near-unity Power

•

Factor

Accurate Power Limiting

•

Average Current Mode Control in PFC

•

Stage

Peak Current Mode Control in Second

•

Stage

Programmable Oscillator

•

Leading Edge/Trailing Edge Modulation

•

for Reduced Output Ripple Using

SmartSync™

• Low Startup Supply Current

• Synchronized Second Stage Start-up,

with Programmable Soft-start

• Programmable Second Stage Shut-down

Stage Down

DESCRIPTION

The UCC18500 family provides all of the functions necessary for an ac

tive power factor corrected preregulator and a second stage DC-to-DC

converter. The controller achieves near-unity power factor by shaping

the AC input line current waveform to correspond to the AC input line

voltage using average current mode control. The DC-to-DC converter

uses peak current mode control to perform the step down power con

version.

The PFC stage is leading edge modulated while the second stage is

trailing edge synchronized to allow for minimum overlap between the

boost and PWM switches.This reduces ripple current in the bulk output

capacitor.

In order to operate with a three to one range of input line voltages, a

line feedforward (V

ing input voltage. Generation of V

with an external single pole filter. This not only reduces external parts

count, but avoids the use of high voltage components offering a lower

cost solution. The multiplier then divides the line current by the square

.

of V

FF

) in used to keep input power constant with vary

FF

is done using IACin conjunction

FF

(continued)

-

-

-

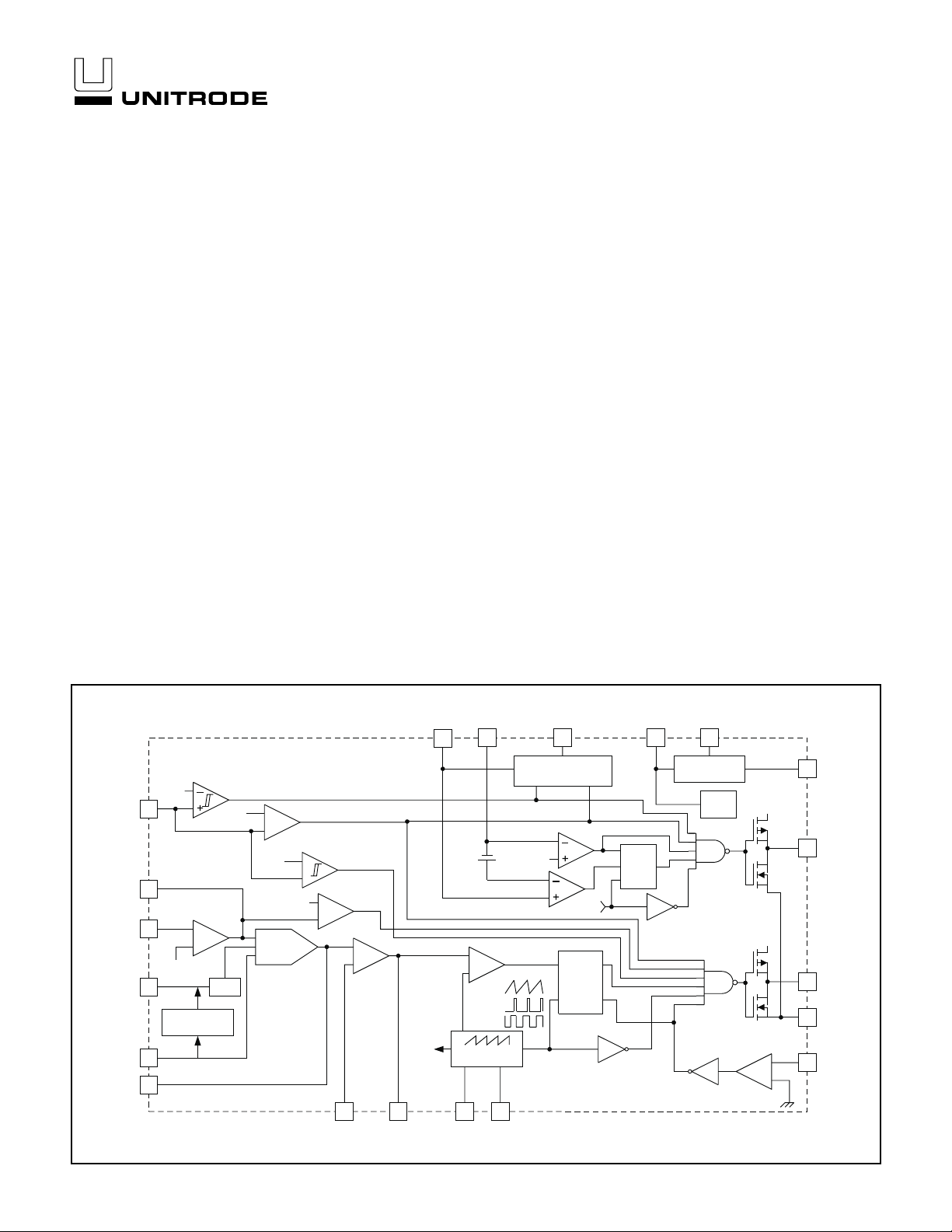

BLOCK DIAGRAM

6.75V

OVP/ENBL

VAOUT

VFF

IAC

MOUT

4

1

3VSENSE

19

18

17

VOLTAGE

ERROR AMP

–

+

7.5V

MIRROR

2:1

(VFF)

1.5V

UVLO2

2

–

+

8.0V

X

÷

X

0.25V

MULT

ENABLE

+

–

–

+

ISENSE1

PFCOVP

ZERO

POWER

–

+

16

VERR

CURRENT AMP

CLK2

15

CAOUT

ISENSE2

7

–

PWM

+

OSCILLATOR

2RT5

8

OSC

CLK1

CLK2

CT

SECOND STAGE

SOFT START

1.5V

1.3V

SS2

13

PWM

I

LIMIT

CLK2

S

PWM

LATCH

R

CLK1

VCC

R

R

Q

S

Q

R

9

GND

6

7.5V

REFERENCE

UVLO

16V/10

I

LIMIT

VCC

VCC

–

+

10

12

11

14

UDG-98189

VREF20

GT2

GT1

PWRGND

PKLMT

SLUS419 - AUGUST 1999

DESCRIPTION (cont.)

The UCC18500 PFC section incorporates a low offset

voltage amplifier with 7.5V reference, a highly linear mul

tiplier capable of a wide current range, a high bandwidth,

low offset current amplifier, with a novel noise attenuation

configuration, PWM comparator and latch and a high cur

rent output driver. Additional PFC features include

over-voltage protection, zero power detection to turn-off

the output when VAOUT is below 0.25V and peak current

and power limiting.

The DC-to-DC section relies on an error signal generated

on secondary-side and processes it by performing peak

current mode control. The DC-to-DC section also fea

tures current limiting, a controlled soft-start, preset oper

UCC18500/1/2/3

UCC28500/1/2/3

UCC38500/1/2/3

ating range with selectable options, and 50% maximum

duty cycle.

The UCC38500 and UCC38502 have a wide PFC-UVLO

threshold (16.5V/10V) for bootstrap bias supply opera

-

tion. The UCC38501 and UCC38503 are designed with a

narrow UVLO range (10.5V/10V) more suitable for fixed

bias operation. The UCC38500 and UCC38501 have a

narrow UVLO threshold for PWM stage (to allow opera

tion down to 75% of nominal bulk voltage), while the

UCC38502 and UCC38503 are configured for a much

wider operation range for the PWM stage (down to 50%

-

of bulk nominal voltage).

-

-

-

ABSOLUTE MAXIMUM RATINGS

Supply Voltage VCC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18V

Gate Drive Current

Continuous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.2A

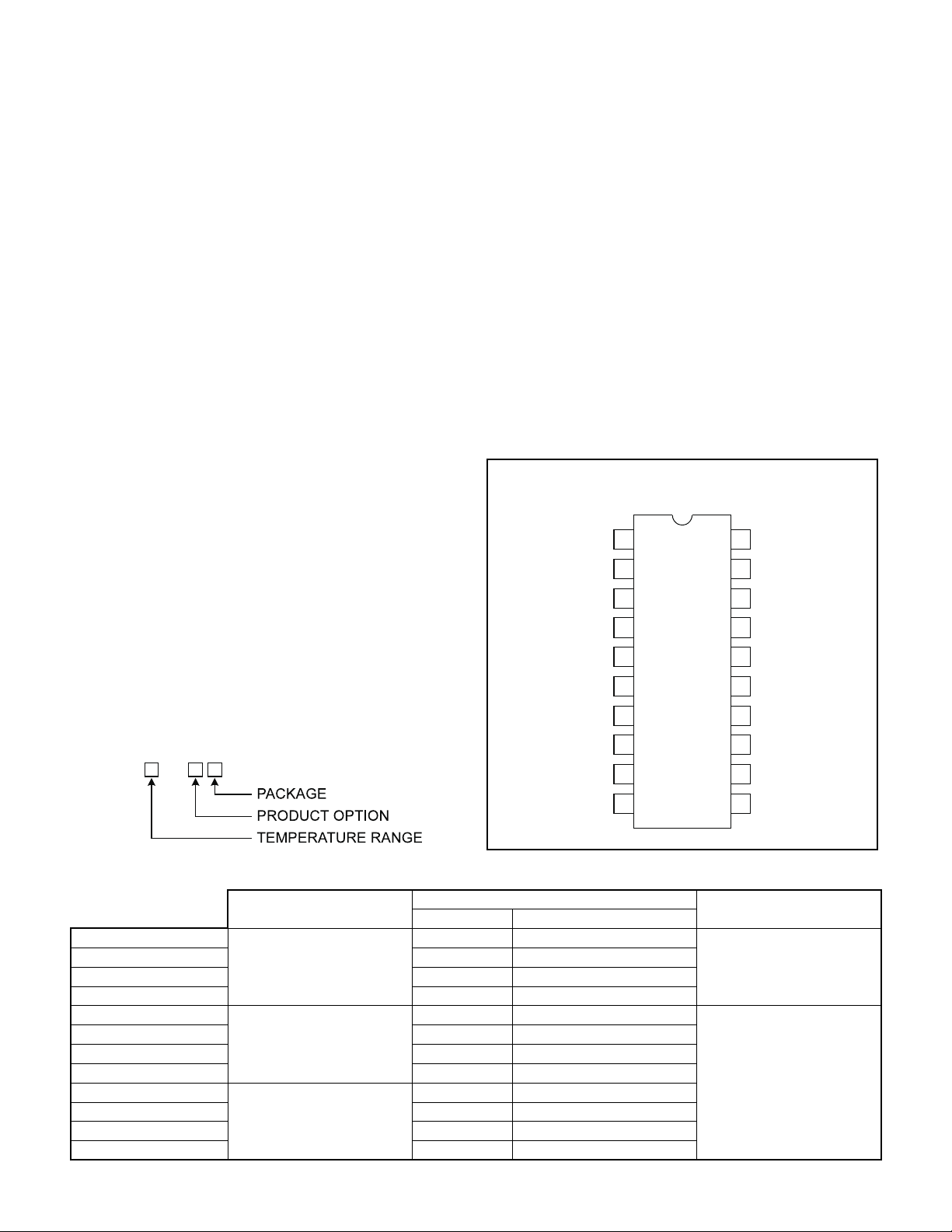

CONNECTION DIAGRAMS

DIL-20, SOIC-20 (TOP VIEW)

N, DW and J Packages

50% Duty Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1A

Input Voltage

I

SENSE1

, I

SENSE2

MOUT,V

OVP, ENBL, . . . . . . . . 11V

SENSE,

PKLMT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5V

Input Current, R

SET,IAC

, PKLMT, ENA . . . . . . . . . . . . . . 10mA

Maximum Negative Voltage, GT1, GT2,

PKLMT, MOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5V

Power Dissipation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1W

Currents are positive into, negative out of the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of packages. All voltages are

referenced to GND.

ORDERING INFORMATION

UCC 850

VAOUT

VSENSE

OVP/ENA

VERR

ISENSE2

1

RT

2

3

4

5

CT

6

GND

7

8

VCC GT1

9

GT2

10 PWRGND

PACKAGE INFORMATION

PRODUCT OPTION

TEMPERATURE RANGE

UCC18500 16 1.2

UCC18501 –55°C to +125°C 10.5 1.2 J-CDIP

UCC18502 16 3.0 N-PDIP

UCC18503 10.5 3.0 DW-SOIC

UCC28500 16 1.2

UCC28501 –40°C to +85°C 10.5 1.2

UCC28502 16 3.0

UCC28503 10.5 3.0

UCC38500 16 1.2

UCC38501 0°C to +70°C 10.5 1.2

UCC38502 16 3.0

UCC38503 10.5 3.0

UVLO UVLO2 HYSTERESIS

VREF

20

VFF

19

IAC

18

17

MOUT

16

ISENSE1

15

CAOUT

14

PKLMT

13

SS2

12

11

PACKAGE

N-PDIP

DW-SOIC

2

UCC18500/1/2/3

UCC28500/1/2/3

UCC38500/1/2/3

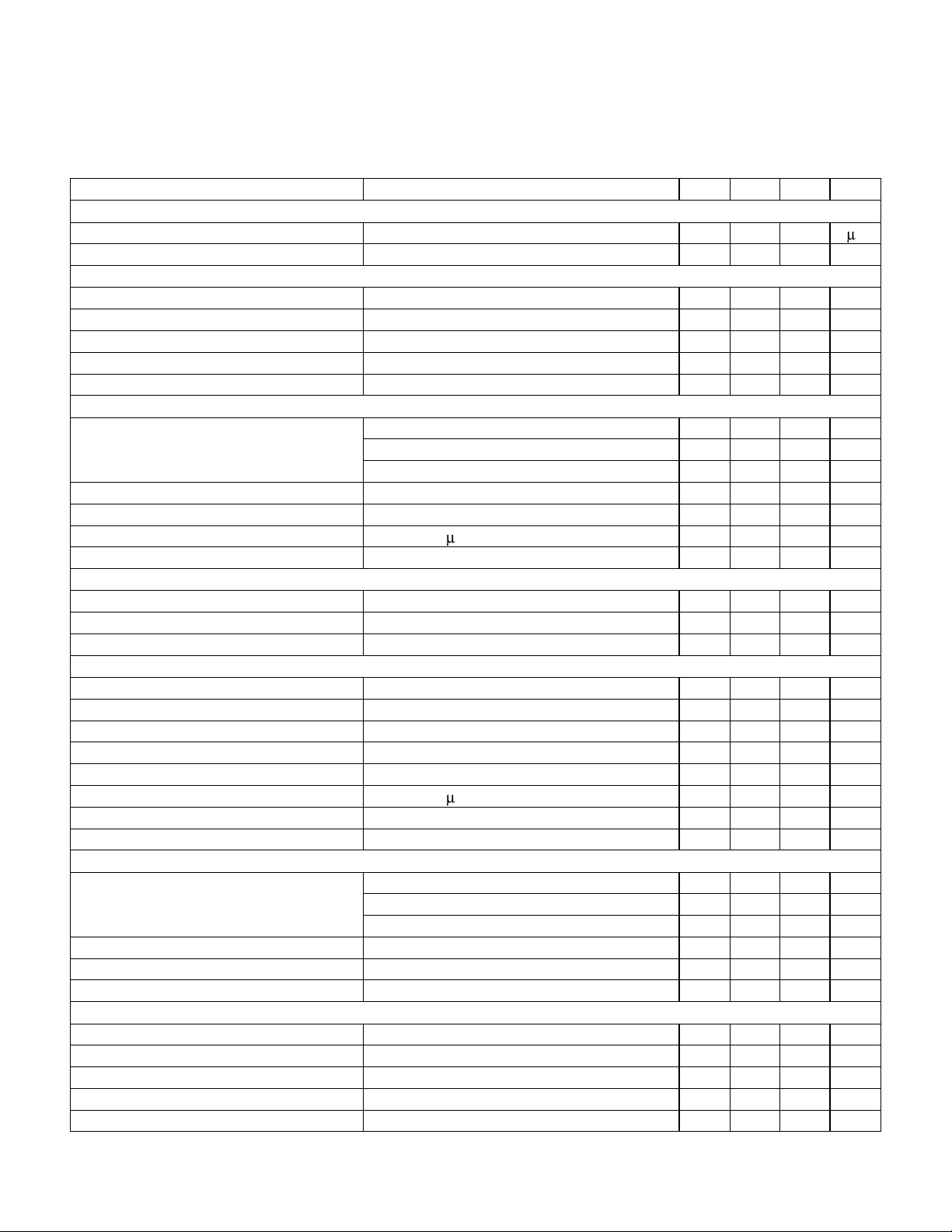

ELECTRICAL CHARACTERISTICS:

UCC3850X, –40°C to +85°C for the UCC2850X, and –55°C to +125°C for the UCC1850X, T

Unless otherwise specified, these specifications hold for TA=0°C to 70°C for the

. VCC = 12V, RT = 22k, CT =

A=TJ

330pF.

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Supply Current Section

Supply Current, Off VCC = 12V (VCC Turn-on Threshold –300mV) 150 300

Supply Current, On VCC = 12V 4 6 mA

UVLO Section

VCC Turn-On Threshold (UCCX8500/502) 15.4 16 16.6 V

UVLO Hysteresis (UCCX8500/502) 5.4 6 6.2 V

Shunt Voltage (UCCX8500/502) I

= 10mA 17 17.5 V

VCC

VCC Turn-On Threshold (UCCX8501/503) 10.2 10.5 10.8 V

UVLO Hysteresis (UCCX8501/503) 0.4 0.5 0.6 V

Voltage Amplifier Section

Input Voltage T

V

Bias Current 50 nA

SENSE

= 0°C to 70°C 7.388 7.500 7.613 V

A

= –40°C to 85°C 7.369 7.500 7.631 V

T

A

= –55°C to125°C 7.313 7.500 7.687 V

T

A

Open Loop Gain VAOUT = 2V to 5V 80 dB

High I

V

OUT

Low I

V

OUT

= –150 A 5.4 5.5 5.6 V

LOAD

= 150µA 0.05 0.10 V

LOAD

Over Voltage Protection and Enable Section

Over Voltage Reference 7.8 8.0 8.2 V

Hysteresis 400 500 600 mV

Enable Threshold 1 1.5 2 V

Current Amplifier Section

Input Offset Voltage V

Input Bias Current V

Input Offset Current V

Open Loop Gain V

CMRR V

High I

V

OUT

Low I

V

OUT

= 0V, V

CM

= 0V, V

CM

= 0V, V

CM

= 0V, V

CM

= 0V to 1.5V, V

CM

= –120 A 6.3 V

LOAD

= 1mA 0.2 V

LOAD

= 3V –5 0 5 mV

CAOUT

= 3V –50 nA

CAOUT

= 3V 25 nA

CAOUT

= 2V to 5V 90 dB

CAOUT

= 3V 80 dB

CAOUT

Gain Bandwidth Product (Note 1) 2.5 MHz

Voltage Reference Section

Input Voltage TA = 0°C to 70°C 7.388 7.500 7.613 V

TA = –40°C to 85°C 7.369 7.500 7.631 V

TA = –55°C to 125°C 7.313 7.500 7.687 V

Load Regulation I

= 1mA to 2mA 5 10 mV

REF

Line Regulation VCC = 12V to 16V 10 20 mV

Short Circuit Current VREF = 0V –25 mA

Oscillator Section

Initial Accuracy T

= 25°C 85 100 115 kHz

A

Voltage Stability VCC = 10.8V to 15V 1 %

Total Variation Line, Temp 80 120 kHz

Ramp Peak Voltage 4.5 5 5.5 V

Ramp Amplitude Voltage (peak to peak) 4 V

A

3

Loading...

Loading...