Page 1

RD-8504/R-774

AUDIO/VIDEO RECEIVER

SAFETY PRECAUTIONS......................................... 2

SPECIFICATIONS.................................................... 3

TUNER SECTION.................................................... 9

ALIGNMENT PROCEDURES.................................. 11

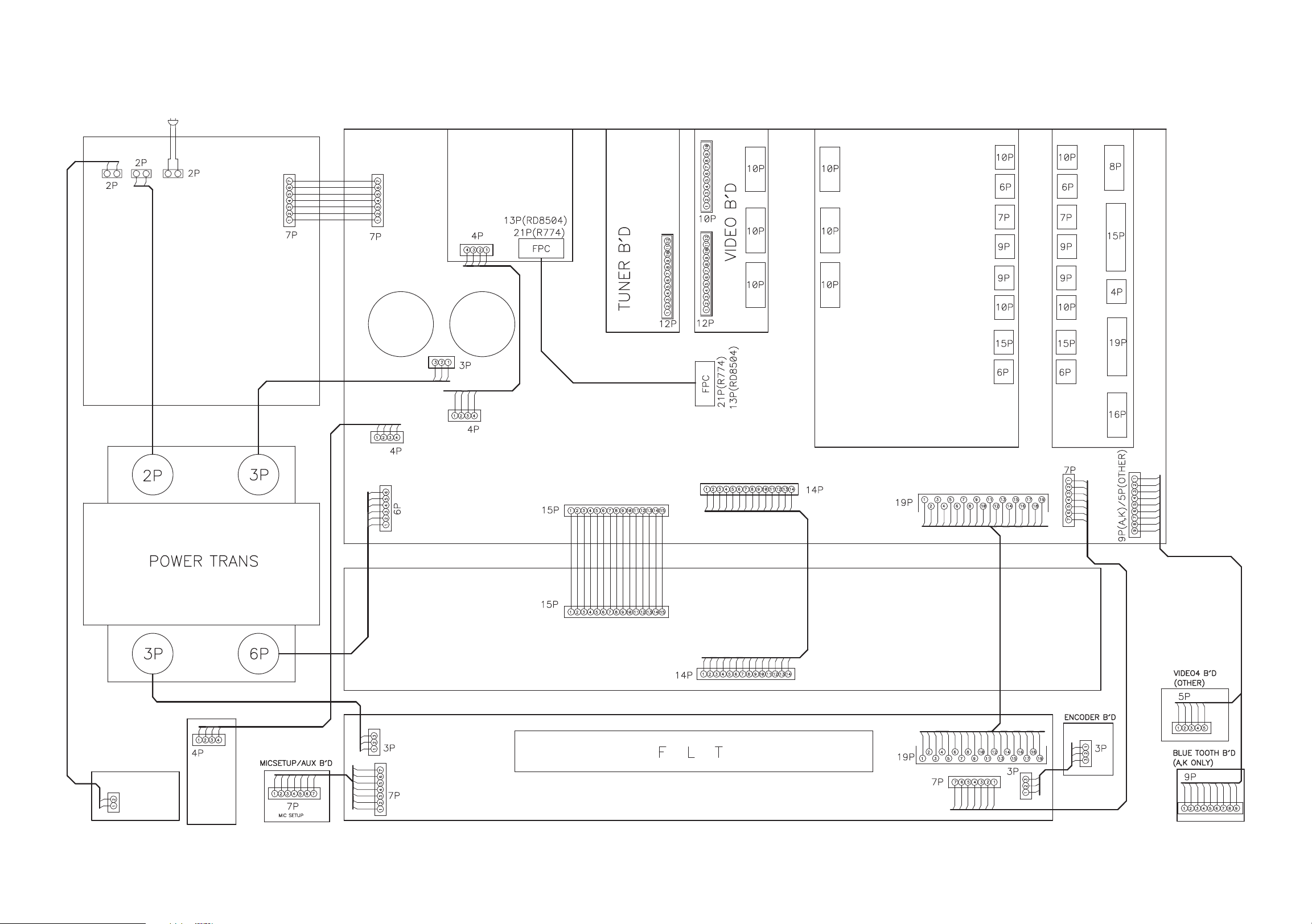

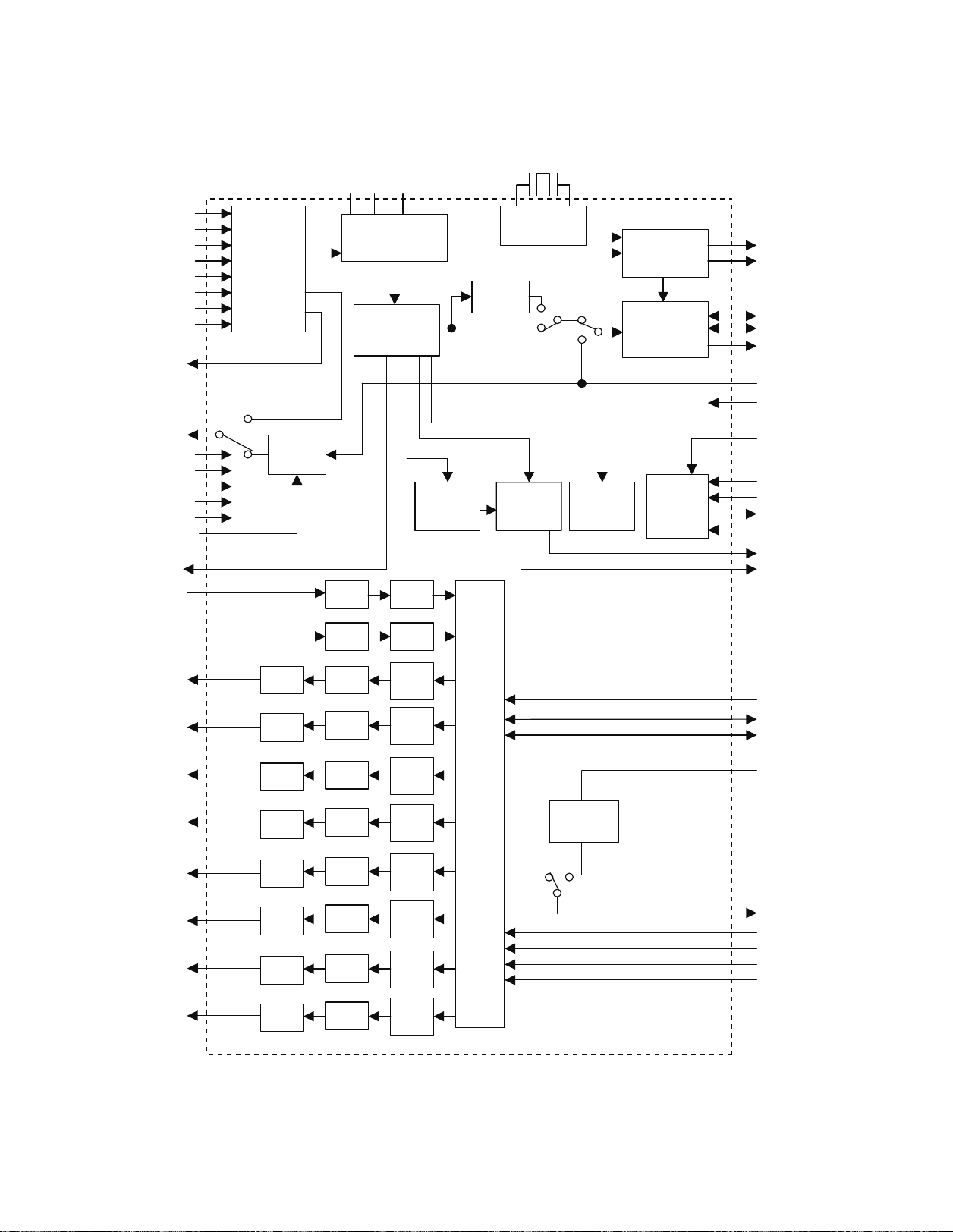

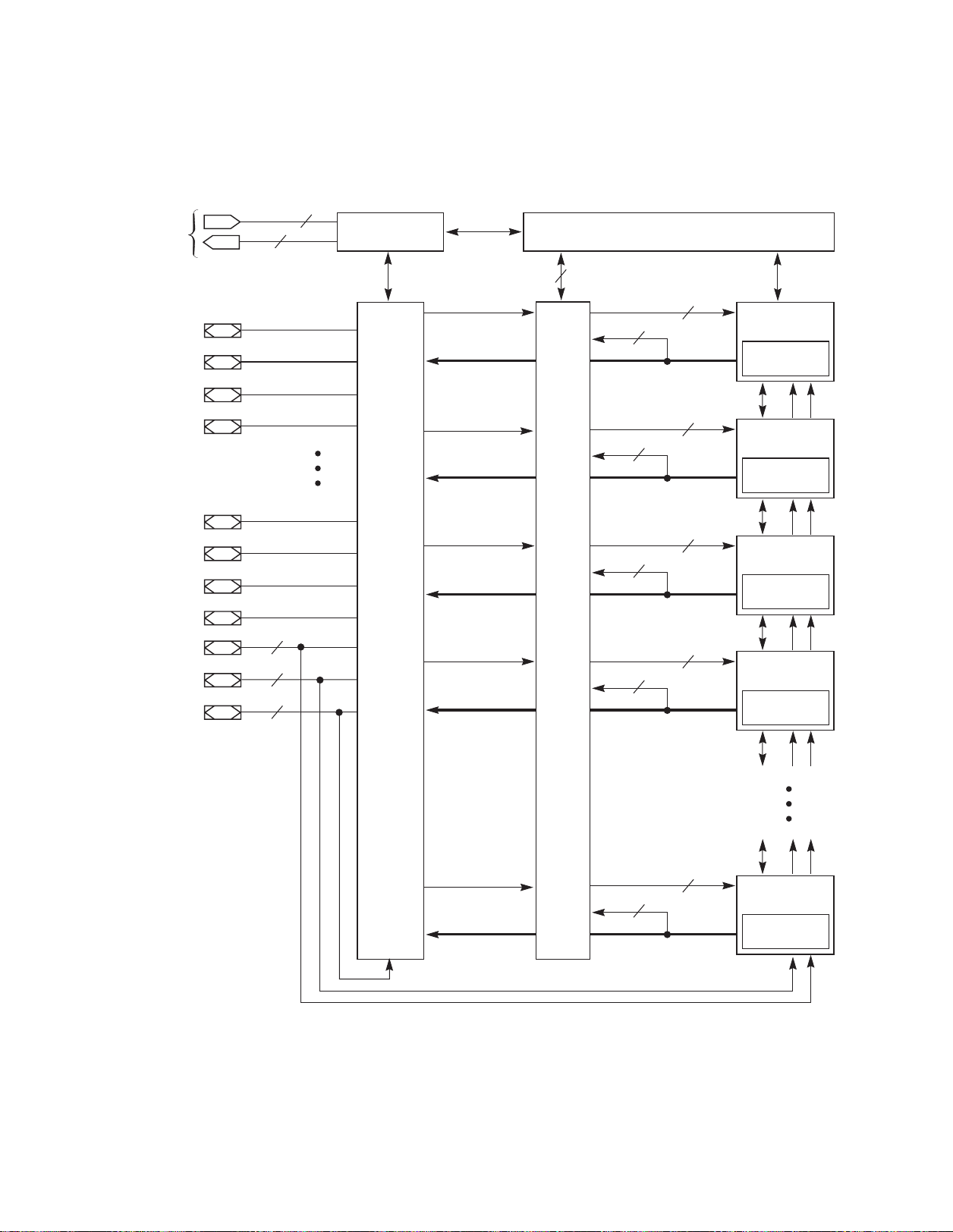

BLOCK DIAGRAM................................................... 12

WIRING DIAGRAM................................................. 13

CIRCUIT DESCRIPTION........................................ 14

TROUBLESHOOTING............................................ 33

MECHANICAL PARTS LIST.................................... 36

EXPLODED VIEW................................................... 38

ELECTRICAL PARTS LIST...................................... 39

PRINTED CIRCUIT BOARDS................................. 59

SCHEMATIC DIAGRAMS........................................ 68

5737-04602-001-0

Page 2

SAFETY PRECAUTIONS

WARNING

Before servicing this unit, familiarize yourself with the following precautions:

1. Many electrical and mechanical parts in this chassis

have special safety characteristics that often pass

unnoticed and the protection afforded by them cannot

necess a r ily be o btain e d by usi n g repl a c ement

components rated for higher voltage, wattage, etc.

Replacement parts that have these special safety

characteristics are identified in this manual and its

supplements: electrical components having such

feature s are iden t i fied by in the s c h ematic

diagram and the parts list.

Before replacing any of these components, read the

part s l i st i n t his man u al c are f ull y . T he u se of

substitute replacement parts that do not have the

same safety characteristics as specified in the parts

list may create shock, fire, or other hazards.

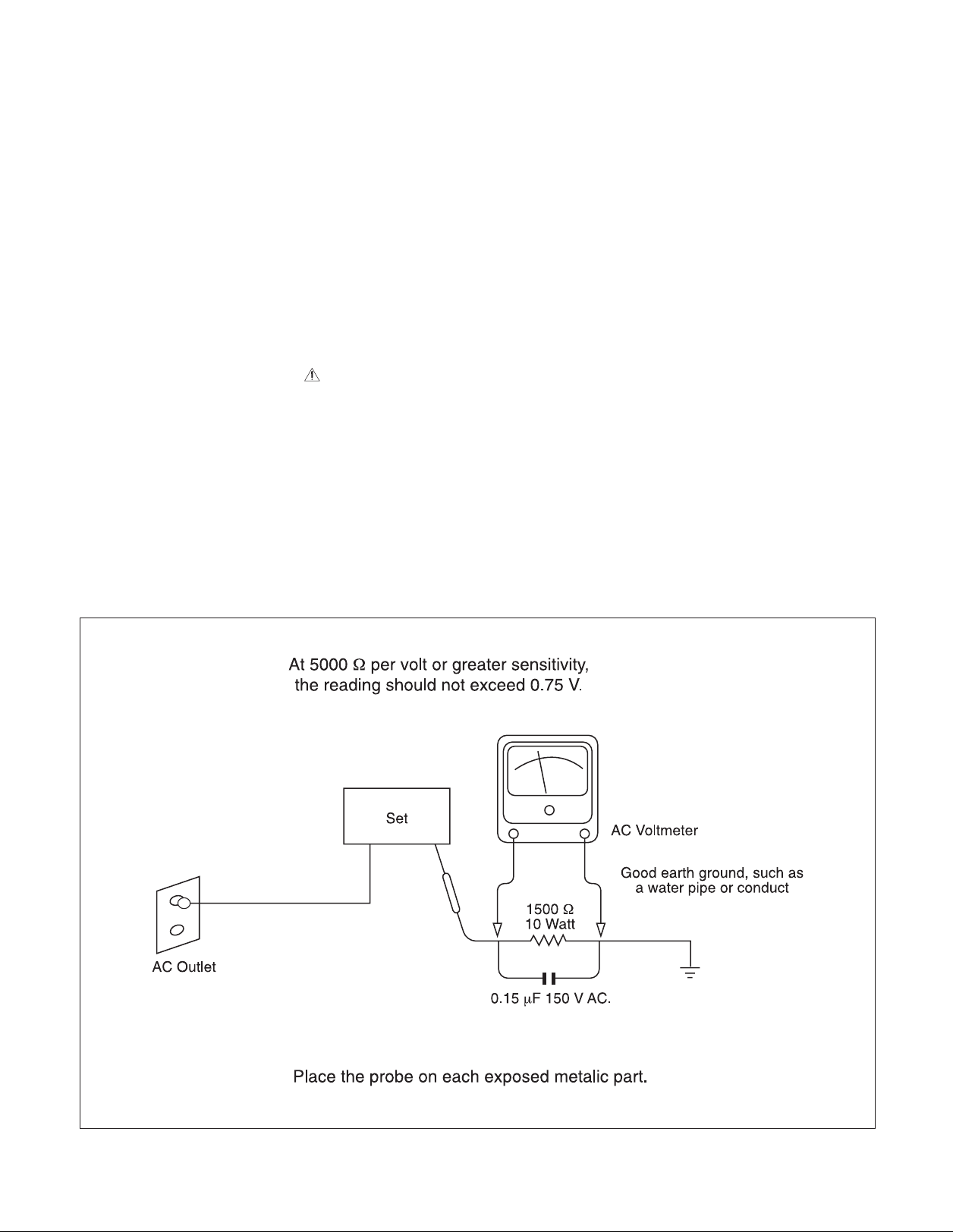

2. Before returning the set to the customer, always do

an AC leakage current check on the exposed metal

parts of the cabinet, such as terminals, screw heads,

and metal overlays, to be sure the set is safe to

operate danger of electrical shock. Plug the AC line

cord directly into a 120 V AC outlet(USA Version) or

230 V AC outlet(EU Version). (Do not use a line

isolation transformer during this check.) Be sure your

AC voltmeter has a sensitivity of 5000 Ω per volt or

greater. Then connect a 1500 Ω 10 watt resistor,

paralleled by a 0.15 µF 150 V AC capacitor, between

a known good earth ground(such as a water pipe, or

conduct) and the exposed metallic parts, one at a

time. Measure the AC voltage across the combination

of a 1500 Ω resistor and a 0.15 µF capacitor. Reverse

the AC plug at the AC outlet and repeat AC voltage

measu r ement s for e a ch ex p o sed m e talic p art.

Voltage measured must not exceed 0.75 V RMS. This

corresponds to 0.2 mA AC. Any value exceeding this

limit constitutes a potential shock hazard and must be

corrected immediately.

2

Page 3

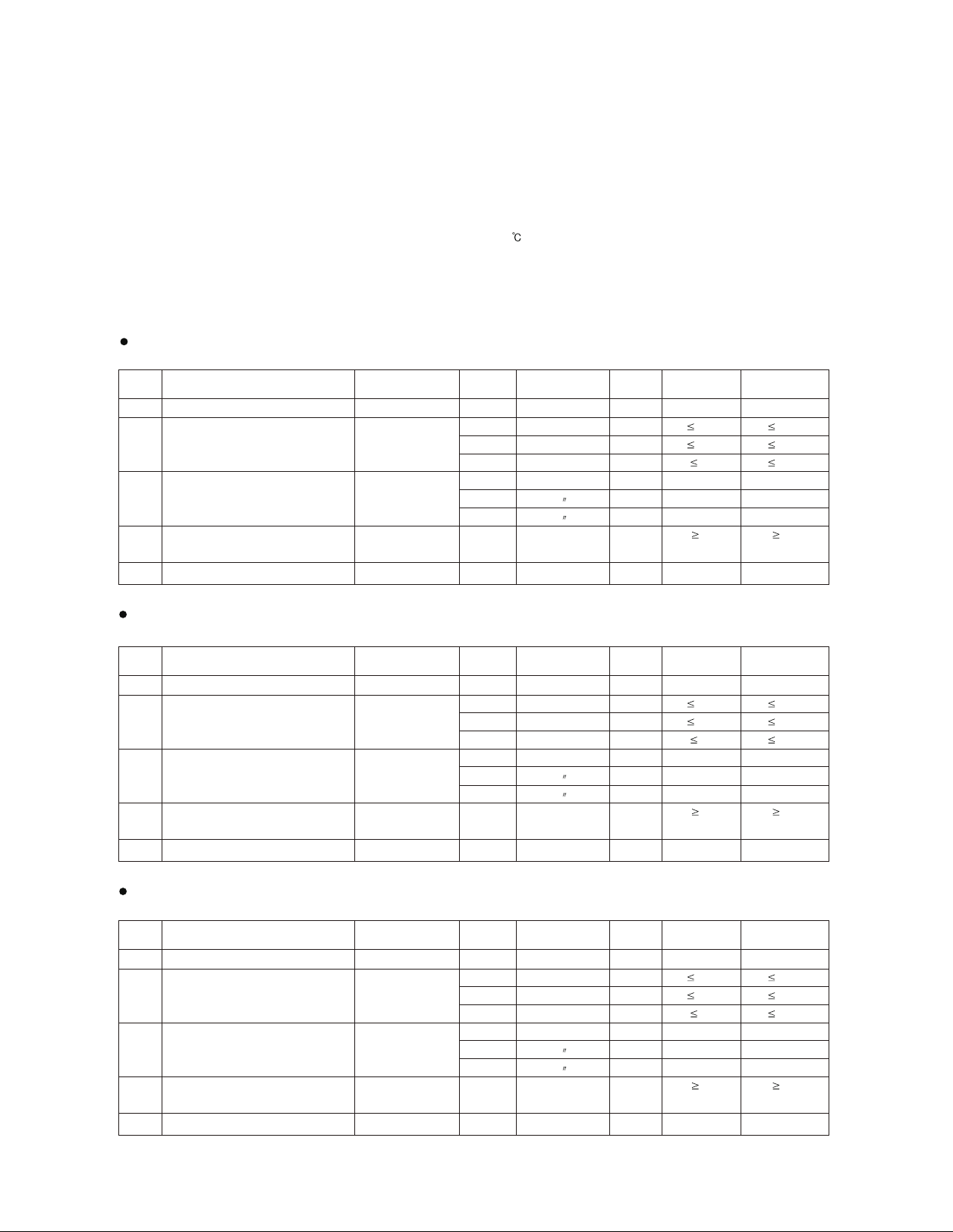

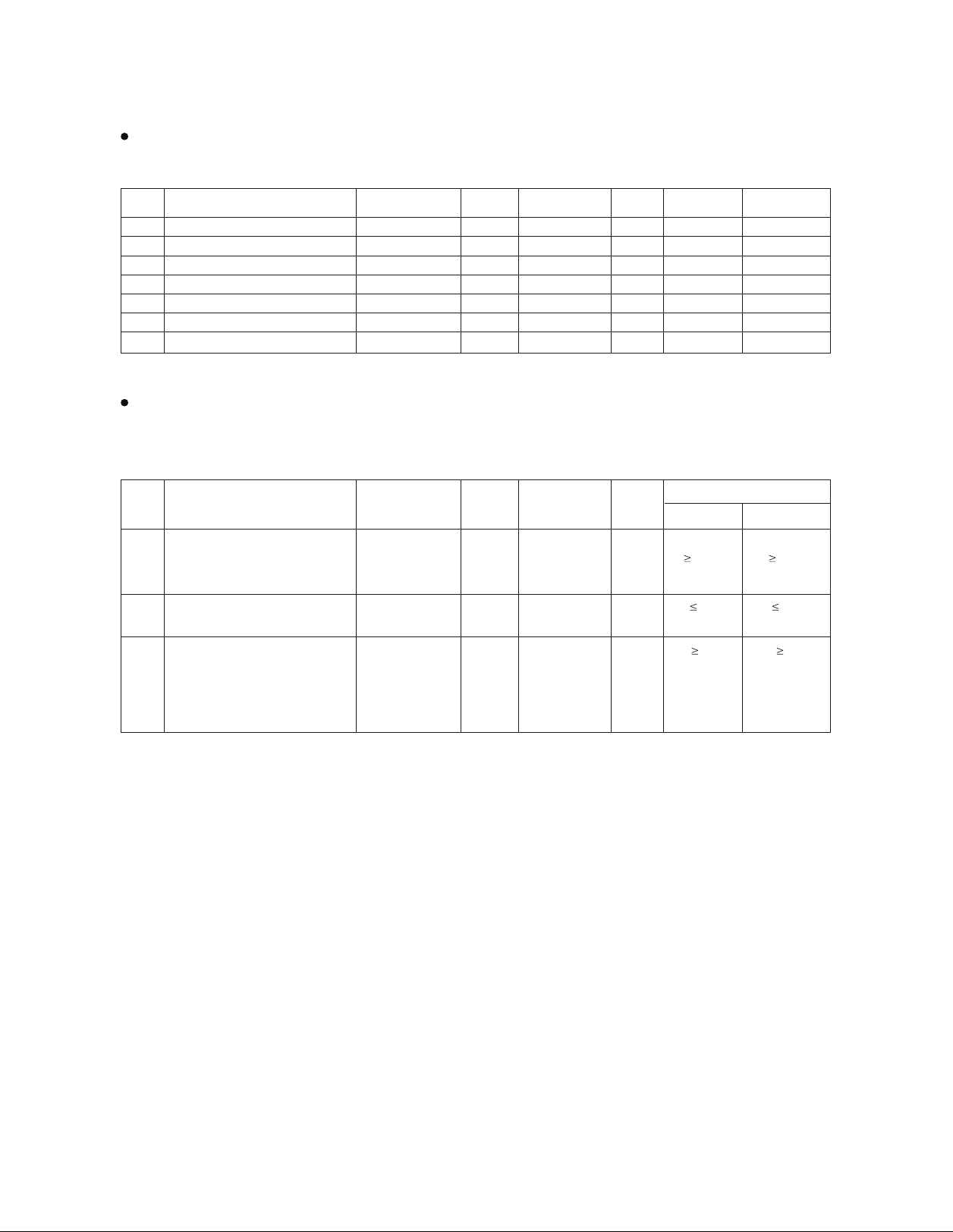

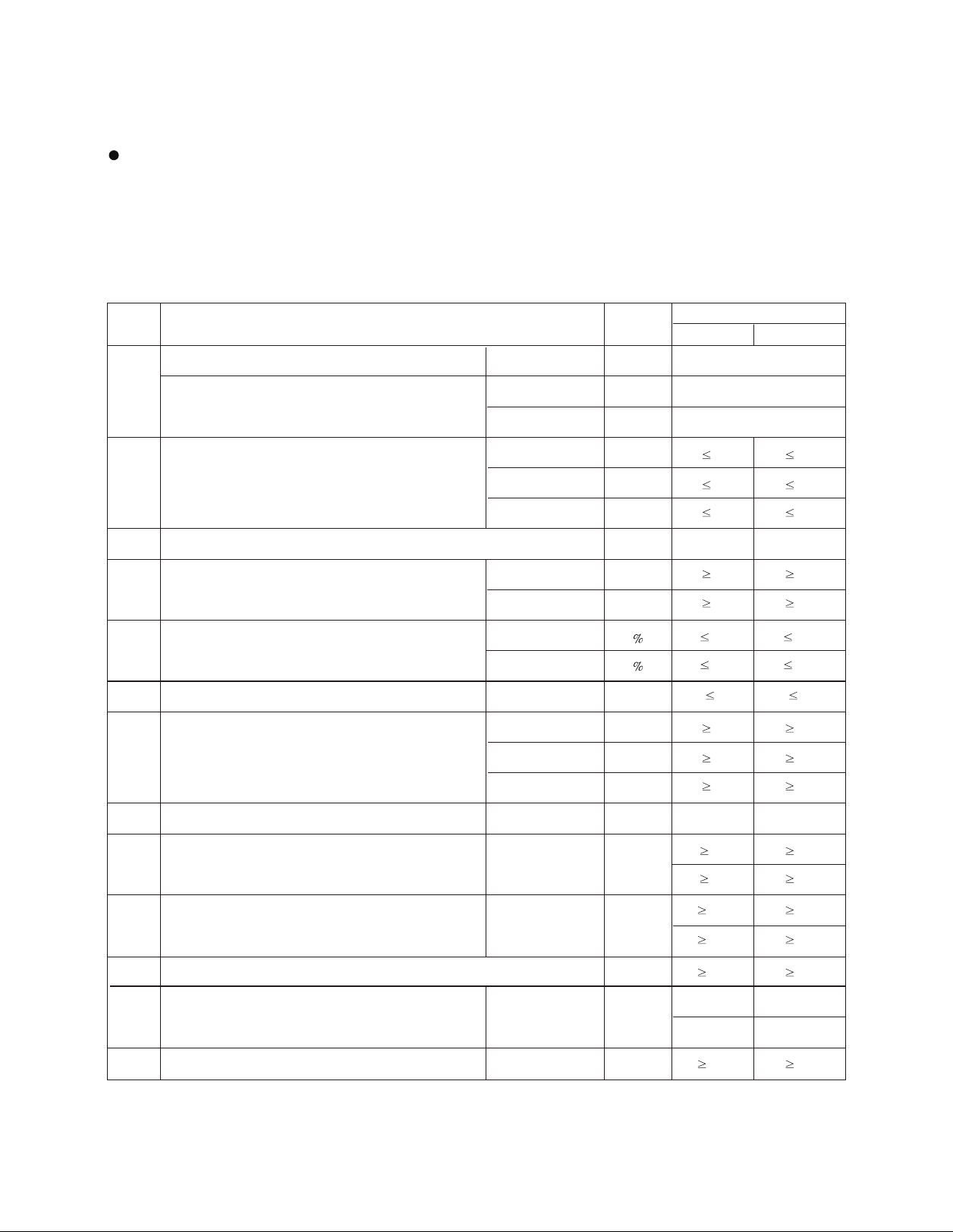

SPECIFICATIONS

Measuring methods are based on IHF and IEC standard 268-3

Measurements conditions,unless otherwise noted :

Output resistive load = (6) ohms / Both channel driven

Tone Direct ON , Other SW's : OFF

Nominal input level : 5mV for MM, 0.5mV for MC, 500mV for general purpose inputs

Power figures should be kept minimum 10min. between 15 and 35

Terminator : 100ohm for MC, 1kohm for MM and general purpose inputs

Filter : IHF-A filter,

R/O = Rated Output

Power supply : 120V/60HZ (A), 230V/50HZ (G)

FRONT AMP SECTION

*SPKR LEVEL: ALL 0dB *SPK SIZE: YES

*EXT IN INPUT *TONE OFF *X-OVER: FULL RANGE

NO

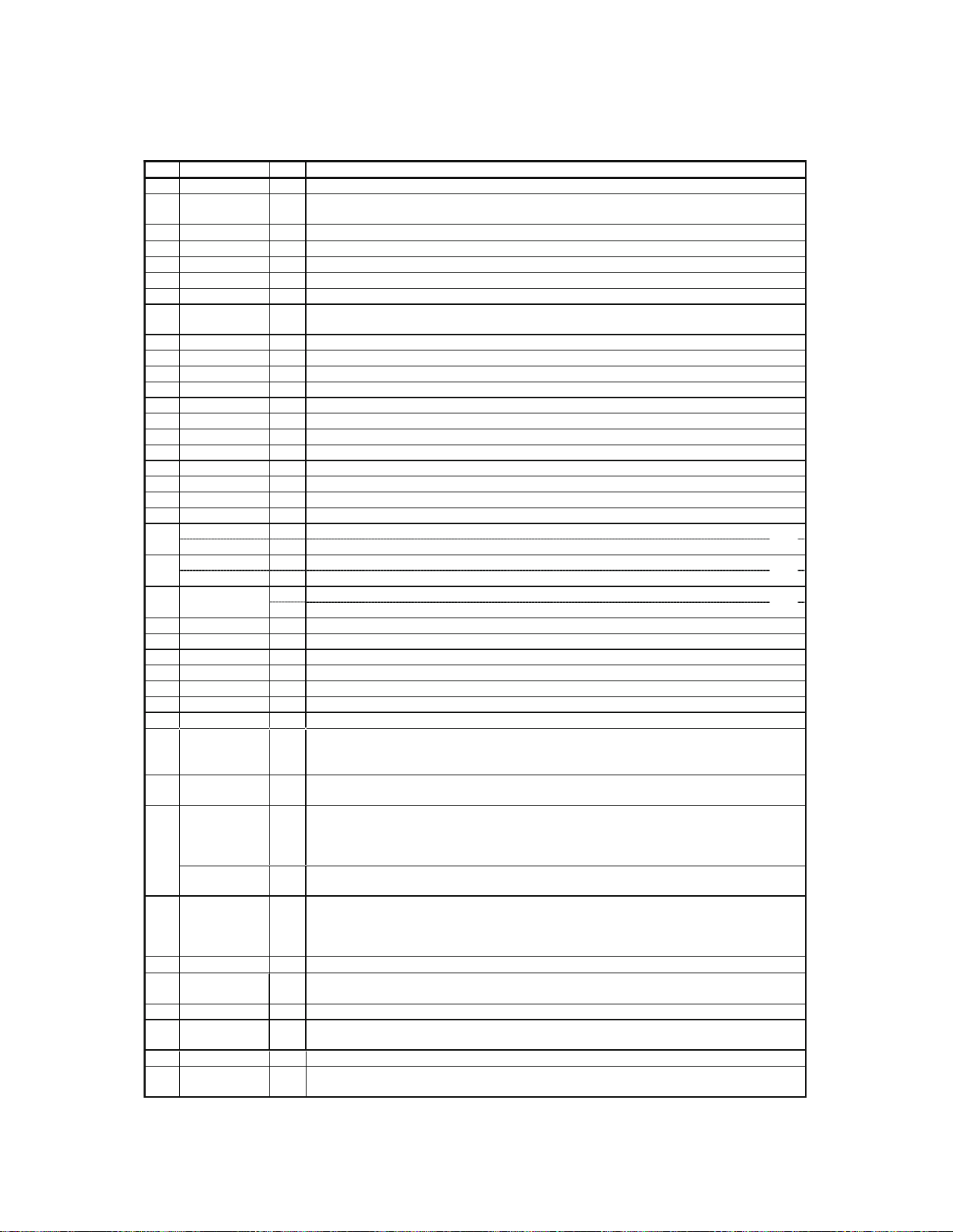

DESCRIPTION INPUT FREQ. REMARK UNIT LIMIT L/R

NOMINAL

L/R

1 INPUT SENSITIVITY EXT IN INPUT 1kHz R/O mV 300±50 300±30

2 TOTAL HARMONIC DISTORTION EXT IN INPUT 40Hz R/O-3dB %

0.12 0.08

%Bd3-O/RzHk1)NI OERETS(

0.12 0.08

20kHz R/O-3dB %

0.2 0.12

3 CONTINUOUS AVERAGE POWER EXT IN INPUT 40Hz 6ohms W 85 90

zHk1DHT %1 ta

W 95 100

kHz02

)NI OERETS(

W 85 90

4 S/N RATIO, INPUT SHORT EXT IN INPUT 1kHz R/O dB

85 90

IHF-A FILTER

5 FREQUENCY RESPONSE (-3dB) EXT IN INPUT 1W/1kHz Ref. Hz~kHz

20~50 20~55

NO

DESCRIPTION INPUT FREQ. REMARK UNIT LIMIT L/R

NOMINAL

L/R

1 INPUT SENSITIVITY EXT IN INPUT 1kHz R/O mV 300±50 300±30

2 TOTAL HARMONIC DISTORTION EXT IN INPUT 40Hz R/O-3dB %

0.12 0.08

%Bd3-O/RzHk1)NI OERETS(

0.12 0.08

20kHz R/O-3dB %

0.2 0.12

3 CONTINUOUS AVERAGE POWER EXT IN INPUT 40Hz 6ohms W 85 90

zHk1DHT %1 ta

W 95 100

kHz02

)NI OERETS(

W 85 90

4 S/N RATIO, INPUT SHORT EXT IN INPUT 1kHz R/O dB

85 90

IHF-A FILTER

5 FREQUENCY RESPONSE (-3dB) EXT IN INPUT 1W/1kHz Ref. Hz~kHz

20~50 20~55

NO

DESCRIPTION INPUT FREQ. REMARK UNIT LIMIT L/R

NOMINAL

L/R

1 INPUT SENSITIVITY EXT IN INPUT 1kHz R/O mV 300±50 300±30

2 TOTAL HARMONIC DISTORTION EXT IN INPUT 40Hz R/O-3dB %

0.12 0.08

%Bd3-O/RzHk1)NI OERETS(

0.12 0.08

20kHz R/O-3dB %

0.3 0.2

3 CONTINUOUS AVERAGE POWER EXT IN INPUT 40Hz 6ohms W 85 90

zHk1DHT %1 ta

W 95 100

kHz02

)NI OERETS(

W 85 90

4 S/N RATIO, INPUT SHORT EXT IN INPUT 1kHz R/O dB

85 90

IHF-A FILTER

5 FREQUENCY RESPONSE (-3dB) EXT IN INPUT 1W/1kHz Ref. Hz~kHz 20~50 20~55

CENTER AMP SECTION (FRONT CENTER)

*SPKR LEVEL: ALL 0dB *SPK SIZE: YES

*EXT IN INPUT *TONE OFF *X-OVER: FULL RANGE

*SPKR LEVEL: ALL 0dB *SPK SIZE: YES

*EXT IN INPUT *TONE OFF *X-OVER: FULL RANGE

SURROUND AMP SECTION

3

Page 4

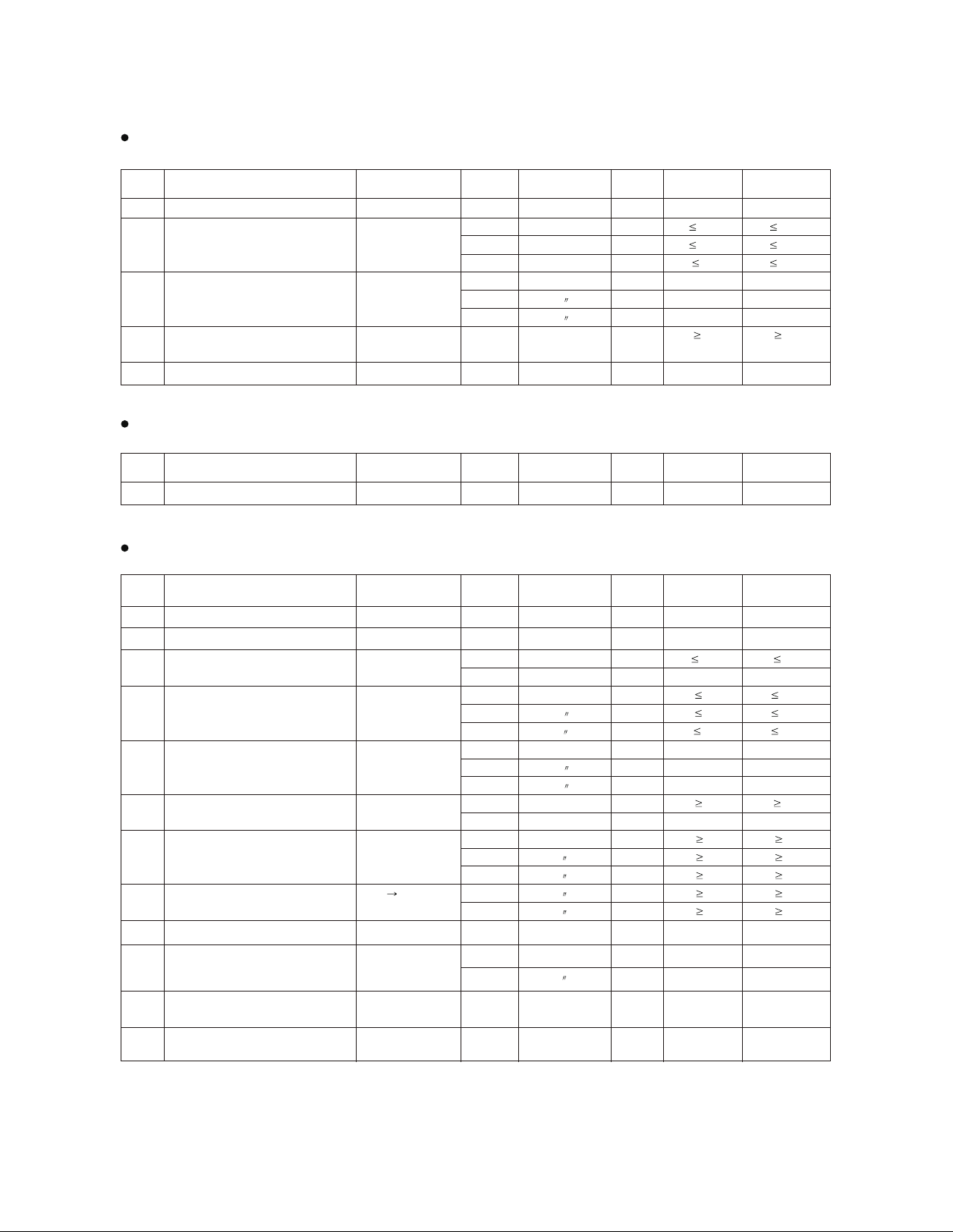

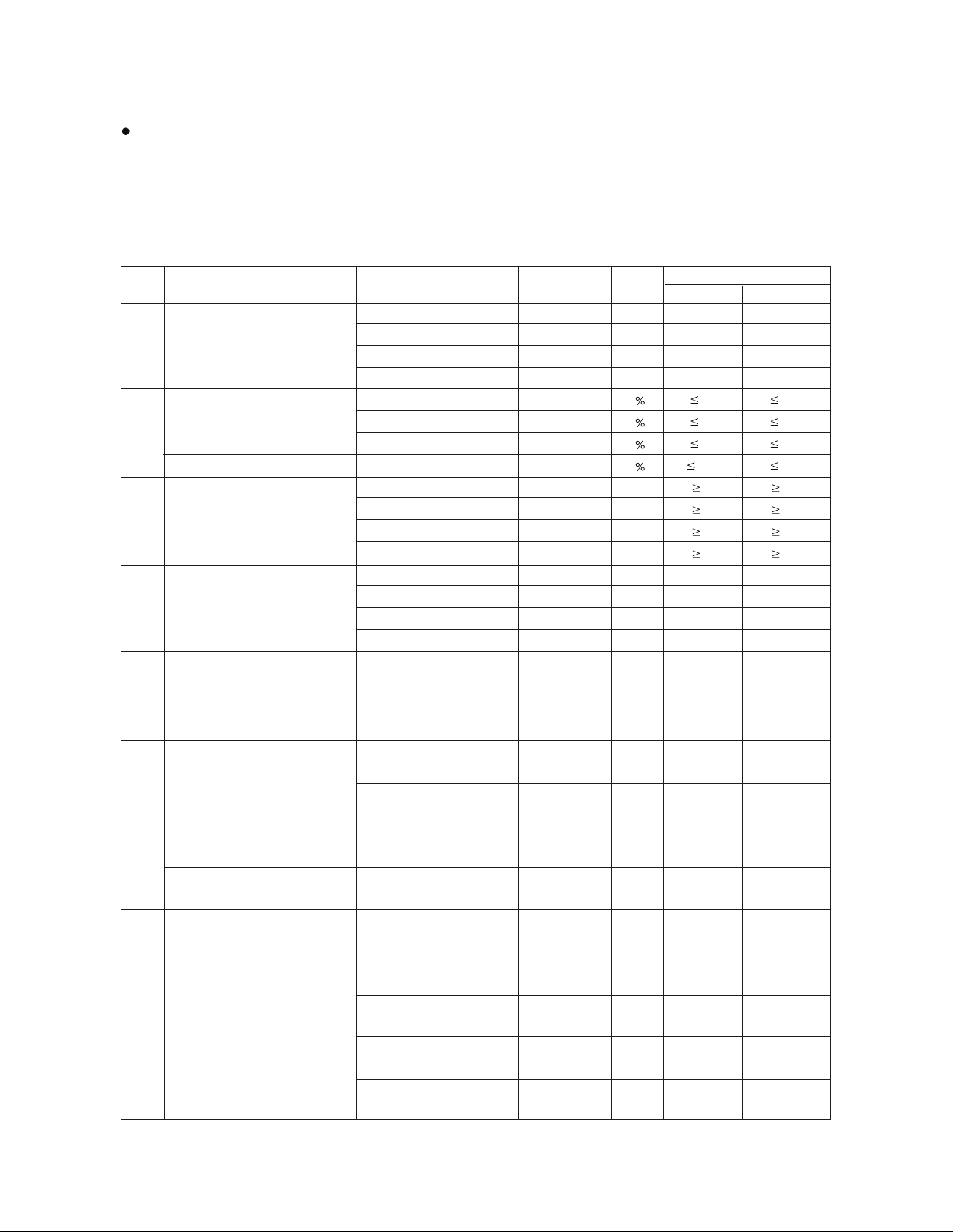

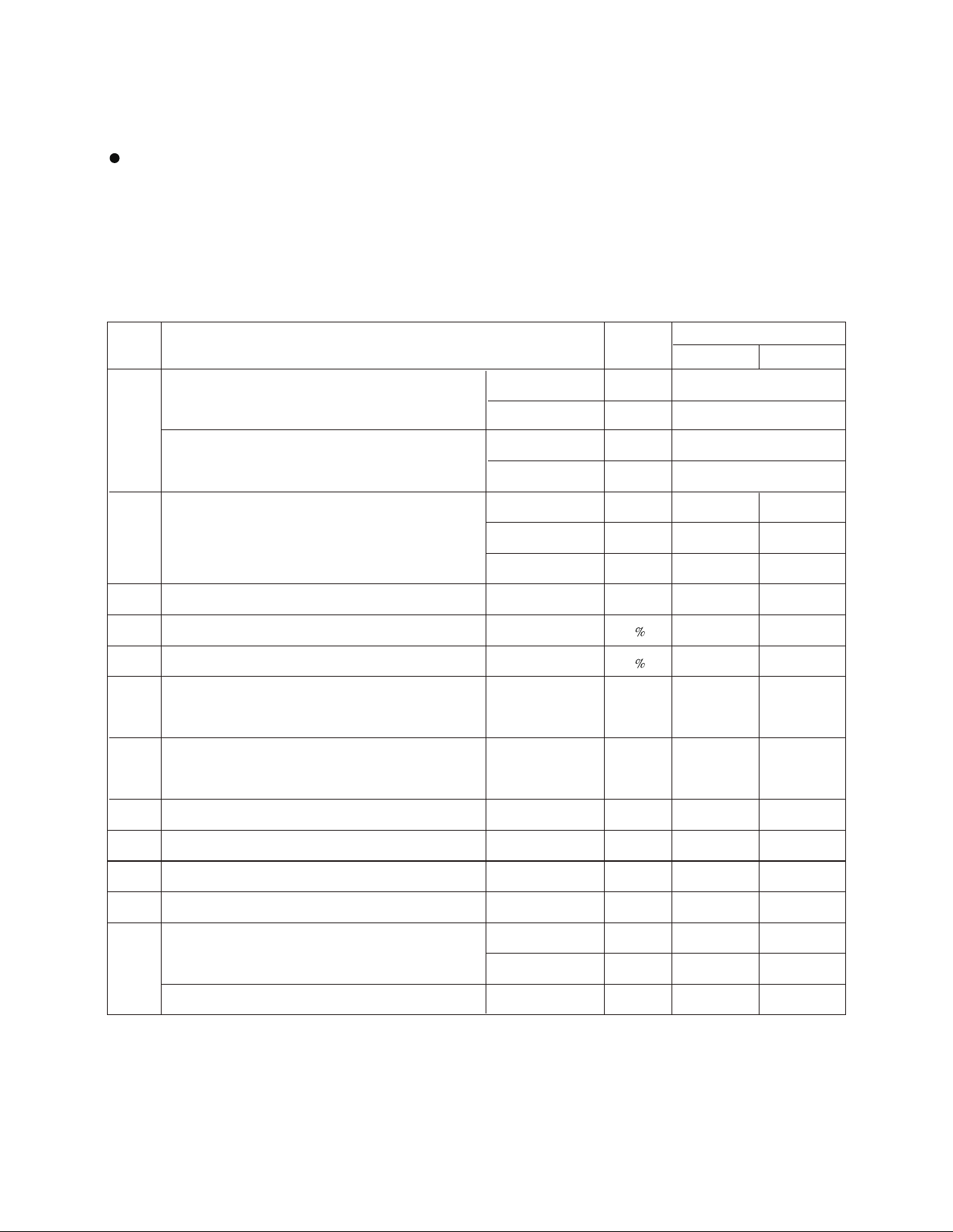

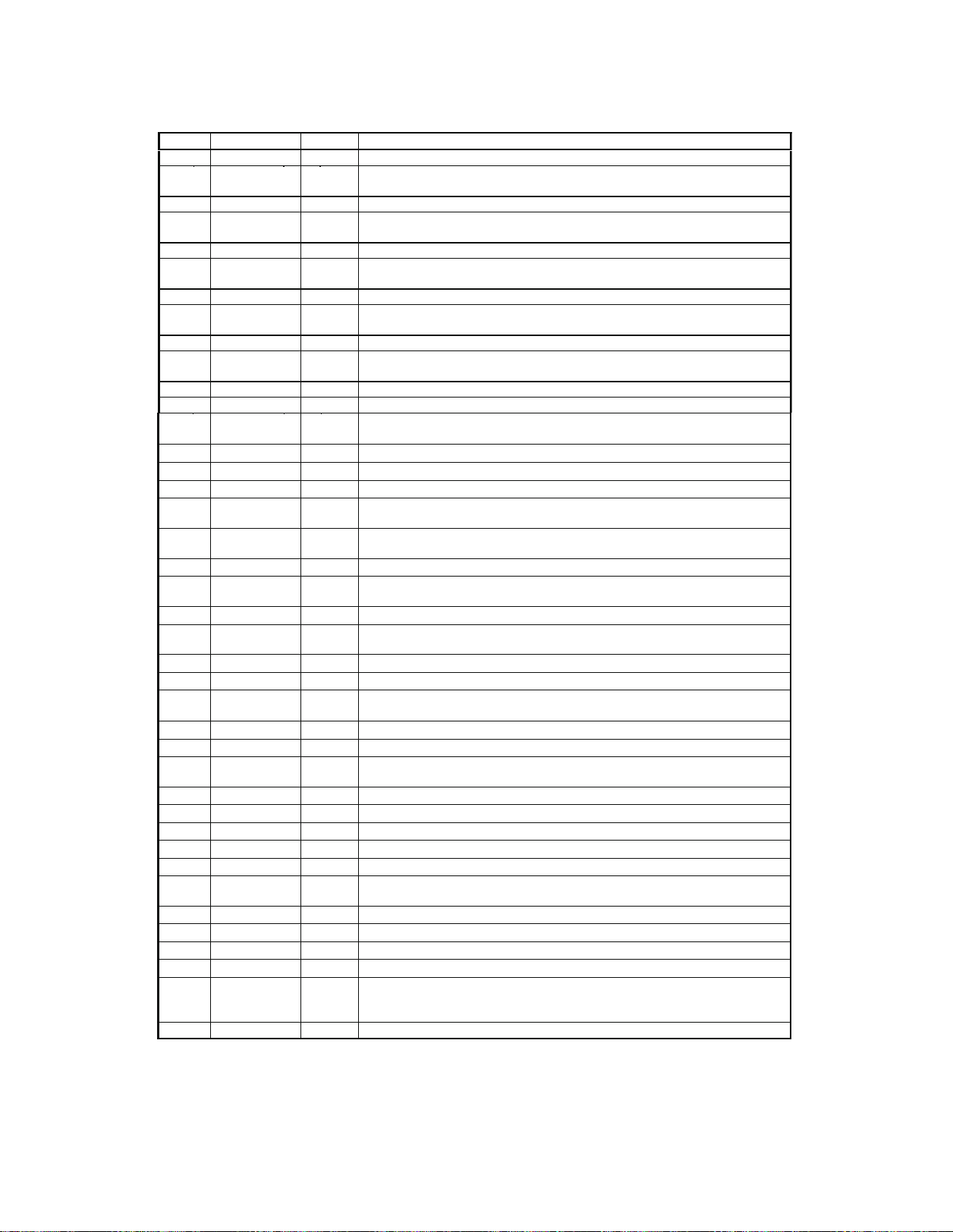

SURROUND BACK AMP SECTION

*SPKR LEVEL: ALL 0dB *SPK SIZE: YES

*EXT IN INPUT *TONE OFF *X-OVER: FULL RANGE

*SPKR LEVEL: ALL 0dB *SPK SIZE: YES

*EXT IN INPUT *TONE OFF *X-OVER: FULL RANGE

*SPKR LEVEL: ALL 0dB *SPK SIZE: YES

*EXT IN INPUT *TONE OFF(TONE DIRECT) *X-OVER: FULL RANGE

SUBWOOFER SECTION

NOITCES OERETS

03±00305±003VmzHk1DC YTIVITISNES TUPNI1

2 CHANNEL BALANCE CD 1kHz R/O TO -40dB dB ±3 ±2

Vm.nim LOVzHk1 ESION LAUDISER3

2.0 1.5

Vm.xam LOVzHk1)TROHS TUPNI(

4 TOTAL HARMONIC DISTORTION 40Hz R/O-3dB %

0.12 0.08

CD(300mV) 1kHz

%

0.12 0.08

kHz02

%

0.2 0.12

5 CONTINUOUS AVERAGE POWER 40Hz 6ohms W 85 90

zHk1DCDHT %1 ta

W 95 100

kHz20

W 85 90

BdO/RzHk1RETLIF A-FHI,OITAR N/S6

85 90

BdBd3-O/RzH001NOITARAPES LENNAHC7

50 65

zHk1)Vm003(DC

dB

55 65

zHk01

dB

40 50

8 FUNCTION CROSSTALK

CD

TAPE IN

1kHz

dB

60 65

zHk01)TROHS TUPNI(

dB

40 45

9 FREQUENCY RESPONSE (-3dB) CD(300mV) 1W Hz~kHz 20~50 20~55

)2±(01±)3±(01±BdW1zH001Bd)01(± , LORTNOC ENOT01

zHk01)NO ENOT(

dB ±10(±3) ±10(±2)

11 HEADPHONE OUTPUT(STEREO) CD(300mV) 1kHz R/O V 3.0±1.0 3.0±0.5

H/P = 64ohms

12

CINEMA EQ (SPK: ALL YES,

X-OVER:FULL RANGE)

CD(300mV) 10kHz 1W dB -4.5±1.5 -4.5±1

CD

CD(300mV)

CD

N

O

DESCRIPTION INPUT FREQ. REMARK UNIT LIMIT L/R

NOMINAL

L/R

1 INPUT SENSITIVITY EXT IN INPUT 1kHz R/O mV 300±50 300±30

2 TOTAL HARMONIC DISTORTION EXT IN INPUT 40Hz R/O-3dB %

0.12 0.08

%Bd3-O/RzHk1)NI OERETS(

0.12 0.08

20kHz R/O-3dB %

0.3 0.2

3 CONTINUOUS AVERAGE POWER EXT IN INPUT 40Hz 6ohms W 85 90

zHk1DHT %1 ta

W 95 100

kHz02

)NI OERETS(

W 85 90

4 S/N RATIO, INPUT SHORT EXT IN INPUT 1kHz R/O dB

85 90

IHF-A FILTER

5 FREQUENCY RESPONSE (-3dB) EXT IN INPUT 1W/1kHz Ref. Hz~kHz 20~50 20~55

NO

DESCRIPTION INPUT FREQ. REMARK UNIT LIMIT L/R

NOMINAL

L/R

NO

DESCRIPTION INPUT FREQ. REMARK UNIT LIMIT L/R

NOMINAL

L/R

1 PRE OUTPUT LEVEL SUB-CH(300mV) 30Hz VOL max. V 3.5±1.0 3.5±0.5

4

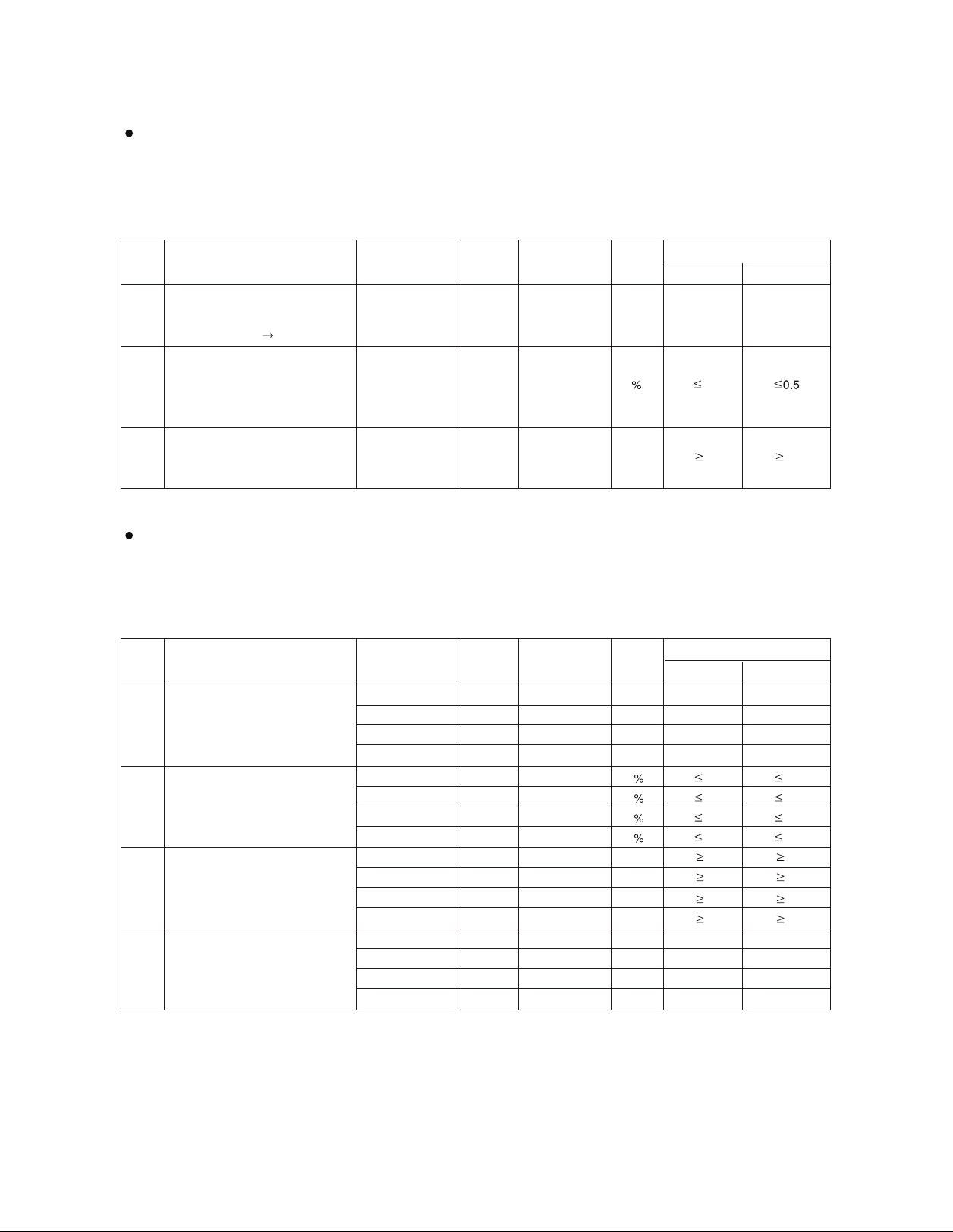

Page 5

IDLE VOLTAG *SPKR LEVEL:ALL 0dB *SPK SIZE:LLLY*EXT. IN

*TONE OFF(TONE DIRECT), *VOL : 60*TEST B'D : AMP

*TEST POINT : R221(FL,FR,SL,SR,C,SBL,SBR) BOTH SIDES VOLTAGE(DC)

7.0±7.25.0±7.2VmLF122R--LF1

7.0±7.25.0±7.2VmRF122R--RF2

7.0±7.25.0±7.2VmLS122R--LS3

7.0±7.25.0±7.2VmRS122R--RS4

7.0±7.25.0±7.2VmC122R--C5

7.0±7.25.0±7.2VmLBS122R--LBS6

7.0±7.25.0±7.2VmRBS422R--RBS7

Sirius(U.S.A Only) SECTION

- INPUT : SIRIUS ANT

-

- SIRIUS PRODUCT MODE: AUDIO ASSIGN+POWER ON

SPK(FL/FR) OUT , SIRIUS FUNCTION

SUIRISLEVEL TUP TUO1

1 kHz

kHz

kHz

Vrms

%

dB

1kHz, 0dB

7±0.5 7±0.8

MASTER VOL.: MAX

SUIRISD.H.T2

1

R/O-3dB

0.1 0.12

1kHz, 0dB

SUIRIS ,OITAR N/S3

1 70 65

1kHz, -20dB

1KHz ON(REF) -> OFF

MASTER VOL.: MAX

IHF-A FILTER

NO

DESCRIPTION INPUT FREQ. REMARK UNIT LIMIT L/R

NOMINAL

L/R

NO

DESCRIPTION INPUT FREQ. REMARK UNIT

NOMI. LIMIT

SPEC

5

Page 6

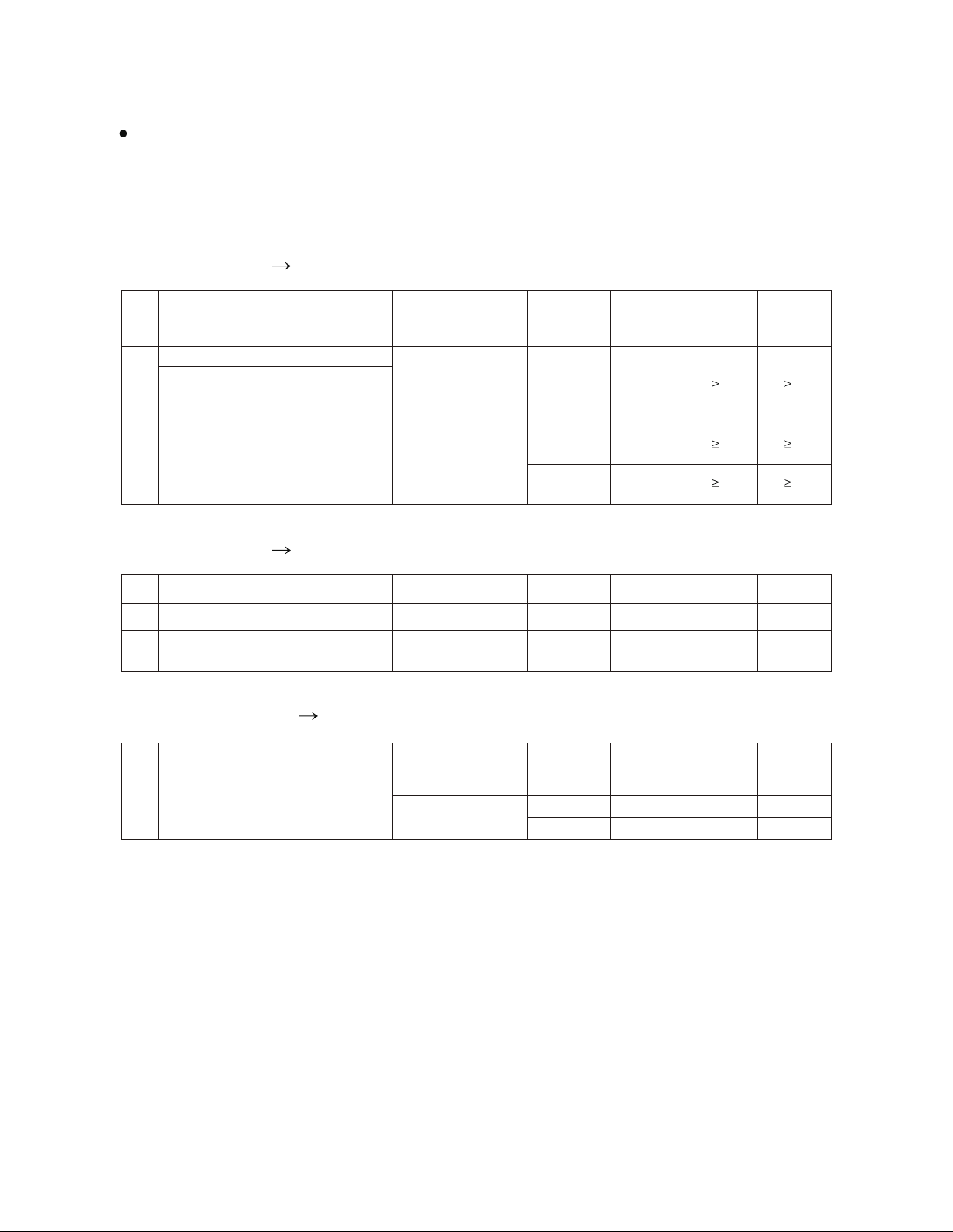

DOLBY DIGITAL INPUT SECTION

- INPUT : COAXIAL (CD DIGITAL)

- SURROUND MODE : DOLBY DIGITAL

- VOLUME POSISTION : 55dB

- CONFIG1:SPK YES BACK-NO/X-OVER:ALL 80HZ

- CONFIG2:SPK YES /SUBWOOFER,BACK-NO/X-OVER:FRONT FULL RANGE,OTHERS 80HZ

- AT SPEAKER OUT Disc : LD VER 1.0

2

±5.91±5.9V21, 8

zH

k

1TNORFLEVEL TUP TUO

2±5.91±5.9V01

zH

k1RETNECBd0 HC llA csiD

SPK MODE:YES,BACK-NO SURR 1kHz 14,16 V 9.5±1 9.5±2

X-OVER:ALL FULL RANGE S/W 30Hz 18 V 1.0±0.5 1.0±0.8

83

zH

k1TNORFD.H.T

0.3 0.5

Disc 0dB LPF(20KHZ) CENTER 1kHz 38

0.3 0.5

SPK MODE:YES,BACK-NO SURR 1kHz 38

0.3 0.5

X-OVER:ALL FULL RANGE S/W 30Hz 18

0.25 0.3

Bd 6zHk1TNORFN/S

65 60

Bd 6zHk1RETNEC)zHK02(FPL3

65 60

JIS-A FILTER,Disc -20dB SURR 1kHz 6 dB

65 60

SPK MODE:YES,BACK-NO S/W 30Hz 18 dB

65 60

DYNAMIC RANGE FRONT 1kHz 38 dB -11±1 -11±2

CENTER 1kHz 38 dB -11±1 -11±2

SURR 1kHz 38 dB -11±1 -11±2

S/W 30Hz 18 dB 0±1 0±2

1±01-5.0±01-Bd34TNORF GOLAID

5

NORMALIZATION CENTER 43 dB -10±0.5 -10±1

SURR 43 dB -10±0.5 -10±1

1±01-5.0±01-Bd34W/S

)fer(83zHk1TNORF1 GIFNOC

02Bd0 zHK1 : feR

6

CENTER 1kHz 38(ref)

20

SURR 1kHz 38(ref)

20

)fer(81zH03W/SBd0 zH03 : feR

22

)fer(83zHk1TNORF2 GIFNOC

7

18

DOWNMIXING TEST CENTER 1kHz 10(ref)

ON>-CSEY:KPS

X-OVER:FULL RANGE SURR.L 1kHz 14

LS->NO

SURR.R 1kHz 16

RS->NO

FRONT 1kHz 6(ref)

ST:ON

-17±3

-17±3

-17±3

6.0±2

dB 7.5±1

dB

5.5±1

dB

dB

dB

1

2

4

8

-17±1dB

-17±1

-17±1

dB -3±0.5

dB -3±0.5

6.0±1

7.5±2

-3±1

-3±1

dB -3±0.5 -3±1

5.5±2

NO

DESCRIPTION INPUT FREQ. CHAP UNIT

NOMI. LIMIT

SPEC

6

Page 7

DOLBY-EX INPUT SECTION

- INPUT : COAXIAL, CD DIGITAL

- SURROUND MODE : DOLBY-EX

- VOLUME POSISTION : 55dB

- AT SPEAKER OUT SPK MODE YES,BACK-YES DOLBY-EX TEST Disc(TRACK 7)

CB

LEVEL TUP TUO

1

2

7 mV 700±70 700±100

Disc : DOLBY-EX -23dB

YES,BACK - L

2CH

71kHz

1kHz

1kHz

CB

D.H.T

0

.3

Disc : DOLBY-EX -23dB

LPF(20KHz)

SPK:YES,BACK - 2CH

CB

N/S

3

STOP dB

65 60

Disc 0dB,JIS "A"

LPF(20KHz)

DTS INPUT SECTION

- INPUT : COAXIAL, CD DIGITAL

- SURROUND MODE : DTS

- VOLUME POSISTION : 55dB

- AT SPEAKER OUT SPK MODE YES BACK-N DTS TEST Disc(TRACK 9,10,11,12,13,14,15)

TNORFLEVEL TUP TUO1

1kHz

1kHz

1kHz

1kHz

1kHz

1kHz

1kHz

1kHz

1kHz

1kHz

1kHz

1kHz

1kHz

10,11 V 10±1 10±2

RETNECBd0 STD : csiD 14 V 10±1 10±2

SPK MODE:YES,BACK-NO SURR 12,13 V 10±1 10±2

X-OVER:ALL FULL RANGE S/W 15 V 1.0±0.6 1.0±0.8

TNORF)ZHK02(FPL DHT2 10,11

0.3 0.5

RETNEC

Bd0 STD : csiD

14

0.3 0.5

SPK MODE:YES,BACK-NO SURR 12,13

0.3 0.5

X-OVER:ALL FULL RANGE S/W

30Hz

30Hz

30Hz

15

0.3 0.5

TNORF N/S3 10,11 dB

65 60

RETNEC"A" SIJ,Bd0 csiD 14 dB

65 60

RRUS)zHK02(FPL 12,13 dB

65 60

W/SN-KCAB,SEY 15 dB

65 60

TNORF6OEN+STD

4

9 V 1.0±0.2 1.0±0.4

RETNECLEVEL TUPTUO 9 V 1.0±0.2 1.0±0.4

Disc:ALL CH(1KHz,-20dB) SURR 9 mV 75±20 75±30

YES,BACK-Y (L 2CH) S-BACK

V 1.0±0.2 1.0±0.4

NO

DESCRIPTION INPUT FREQ. TRACK UNIT

NOMI. LIMIT

SPEC

NO

DESCRIPTION INPUT FREQ. TRACK UNIT

NOMI. LIMIT

SPEC

7

Page 8

VIDEO SECTION

- Load : Video output 75 ohm

- TEST INSTRUMENT : SCOPE,VN30A1

- DISC : TDV - 540 TEST DISC (ABEX)

- MEASUREMENT POSITION : AT MONITOR OUT

OUTPUT : C-VIDEO

p-pVOEDIV-C%001 ETIHW

1

1±0.4 1±0.2

2

HPF 100kHz

LPF 4.2MHz

SC Trap ON

Color S/N (

VN30A1)

HPF 10khz

*ALC:OFF LPF 500kHz

*RANGE:AUTO

*BOTH

OUTPUT : S-VIDEO

p-pV%001 ETIHW1

1±0.4 1±0.2

2

OUTPUT : COMPONENT

WHITE 100%

Y Vp-p 1±0.4 1±0.2

R-Y Vp-p 0.5±0.2 0.5±0.1

B-Y Vp-p 0.5±0.2 0.5±0.1

(3) INPUT:COMPONENT

1 OUTPUT LEVEL

Color Bar Play (Title

2,Chap 1)

C-VIDEO mVp-p 282±100 282±80

(2) INPUT : S-VIDEO

OUTPUT LEVEL

BURST LEVEL

Color Bar Play (Title

2,Chap 1)

45

45

MAGENTA TITLE2

CHAP.17

AM dB

40

PM

Brightness S/N

(VN30A1)

dB

40 45

(1) INPUT : C-VIDEO

OUTPUT LEVEL

S/N RATIO

WHITE 50% TITLE2

CHAP.4

dB

40

NO

DESCRIPTION INPUT REMARK UNIT LIMIT NOMINAL

NO

DESCRIPTION INPUT REMARK UNIT LIMIT NOMINAL

NO

DESCRIPTION INPUT REMARK UNIT LIMIT NOMINAL

8

Page 9

TUNER SECTION

FM SECTION

Measuring methods in confirmity with IEC standard 315

Measurements condition FM : Ref. frequency = ( 98.1MHz), Audio frequency = 1kHz

Reference level = 1mV

Filter = B.P.F at STEREO and MONO MOD : 75kHz(Mono) / 67.5kHz±7.5kHz(ST)

on (75ohms, 300ohms) Deviation :

Test Point:TP1 = 90.1MHz,TP2 = 98.1MHz , TP3 = 106.1MHz (100kHz STEP(A), 50kHz STEP(RDS))

zHMHGIH ~ WOLEGNAR REVOC GNINUT1

zHkLAUNAM/OTUA

P (A)

(RDS)

(A)

(RDS)

(A)

(RDS)

(A)

(RDS)

ETS

uBd1 PTYTIVITISNES ELBASU2

12 15

S/N = 30dB (A)

S/N = 26dB (RDS)

TP 2 dBu

12 15

TP 3 dBu

12 15

8±526±52uBdLEVEL POTS OTUA

3

uBdONOM

OITAR N/S4

5

6

7

8

55 50

uBdOERETS

"A" FHI

50 45

T.H.D

MONO 1kHz

0.7 1.2

STEREO 1kHz 1.0 1.5

OVER LOAD DISTORTION(120dBu,75kHz) MONO dB

2 3

STEREO SEPARATION

250Hz

dBu

30 25

(MAIN 90%,PILOT 10%)

1kHz

dBu

30 25

EXT 19KHz FILTER

6.3kHz

dBu

20 15

FREQUENCY RESPONSE(75us(A), 50us(RDS), -3dB)

TP 2 Hz 60~8k 70~7k

RDS SENSITIVITY TP 2 dBf

Bd

1 PT

NOITCEJER FI9

65 60

75 70

Bd3 PT

NOITCEJER EGAMI01

20 18

75 70

BdkHz)1 %03 MA TA( NOISSERPUS MA1131

40 35

30 35

2 PT

)ONOM(LEVEL TUPUO21

ໜrms

500±100 500±150

280±100 280±150

87.5~108

100 / 100

zHkLAUNAM/OTUA

50 / 50

NO

DESCRIPTION UNIT

NOMI. LIMIT

SPEC

9

Page 10

AM SECTION

Measurements condition AM - MW : Radio. frequency = 1000/999kHz , Audio frequency = 400Hz

Reference level = (74dBu/m),(50)ohms

Modulation = ( 30 )%

Test Point : MW TP 1 = (600)kHz , TP 2 = (1000)kHz , TP 3 = (1400)kHz (A)

MW TP 1 = (594)kHz , TP 2 = (999)kHz , TP 3 = (1404)kHz (RDS)

W kHz

kHz

kHz

kHz

M HGIH~WOLE (A)

(RDS)

(A)

(RDS)

GNAR REVOC GNINUT1

LAUNAM/OTUA

WM HGIH~WOL

LAUNAM/OTUA

PETS

1 PTYTIVITISNES ELBASU2

˺63 ˺65

TP 2

˺63 ˺65

3 PTBd02 = N/S

˺63 ˺65

2 PTOITAR N/S3

˻35 ˻30

(100) dBu/m, (30 )% MOD

dBu/m, (30 )% MOD

2 PTD.H.T4

˺2 ˺3

74

2 PTNOITROTSID DAOL REVO5

˺3 ˺5

100 dBu/m ,80% MOD

K8.1~001K2~08ZHBd6-TA ESNOPSER YCNEUQERF6

(at 74dBu/m, 400Hz)-NO FILTER

2 PTYTIVITCELES7

˻23 ˻20

AT SN: 20dB, ±10kHz(A) / ±9kHz(RDS)

2 PTTIREM FO ERUGIF CGA8

˻50 ˻40

(at100dBμ/m)

3 PTNOITCEJER EGAMI9

˻28 ˻25

%FI2NOITALUDOM ELTSIHW01

11

12

131

˺10 ˺15

(74dBu/m,900kHz)

TUNED LEVEL

dBu/m

dBu/m

55±10 55±15

1000kHz(A) / 999kHz(RDS)

AUTO STOP LEVEL

1000kHz(A)

55±10 55±15

dBu/m

dBu/m

dBu/m

dBu/m

999kHz(RDS)

55±10 55±15

OUTPUT LEVEL

mV rms

200±100 200±150

74dBum, (30)% MOD

10 / 10

520~1710

9 / 9

522~1611

dB

dB

dB

NO

DESCRIPTION UNIT

NOMI. LIMIT

SPEC

10

Page 11

1. Electrical specification

2. Electrical characteristics

3. Adjust Point

Local OSC

Frequency cover range

Standard supply voltage

FM Antenna input Impedance

AM Loop Antenna

AF Output Level

Auto Stop Level

Stereo Separation 1kHz

AF Output Level

Auto Stop Level

98.1 60

75 ohm

40

FM

47Ω Load 98.1 60

MW

47Ω Load 999 74--30 180 ±60

280±100 mV

25 ±6 dBu

1-3

1-4

NO.

9.5uH ( 1kHz ) : S0160BL-25

12.0(±0.5V)

Above the receiving Frequency

M W F M

522 ~1620kHz 87.5 ~ 108.0MHz

ITEMS

S

PECIFICATION

1-1

kHz,%dBu

TEST

CONDITION

T.P.

1-5

Adjustment

1-2

SVR01

UNITSpecification

NO

Non Adjust

98.1 --

TEST ITEMS

MOD.T.L.

999

SVR02

Non Adjust30 55 ±15

25 min dB

mV Non Adjust

dBu

SVR02

SVR01

FM STEREO SEPARATION Adj.

FM AUTO STOP LEVEL Adj.

ALIGNMENT PROCEDURES

11

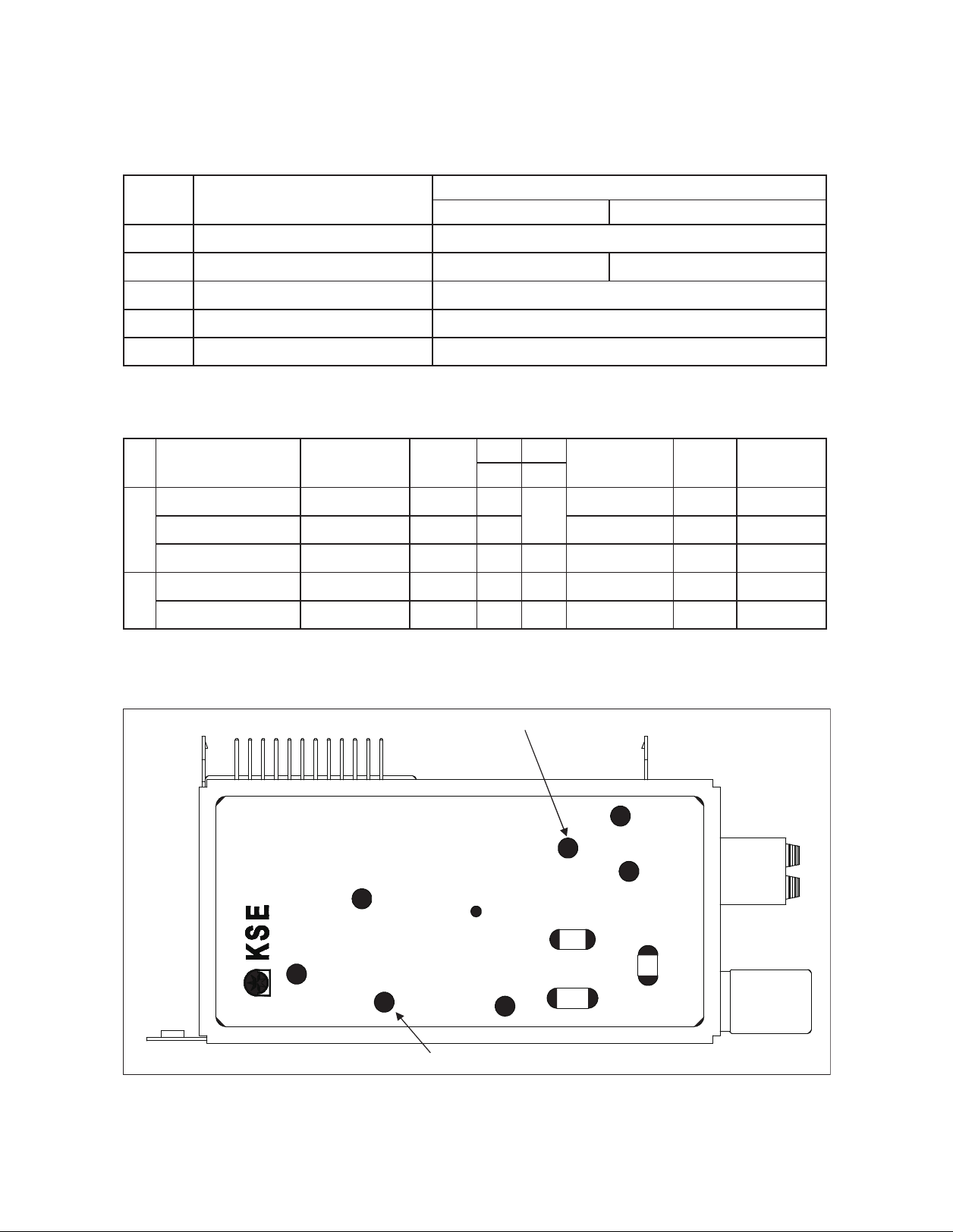

Page 12

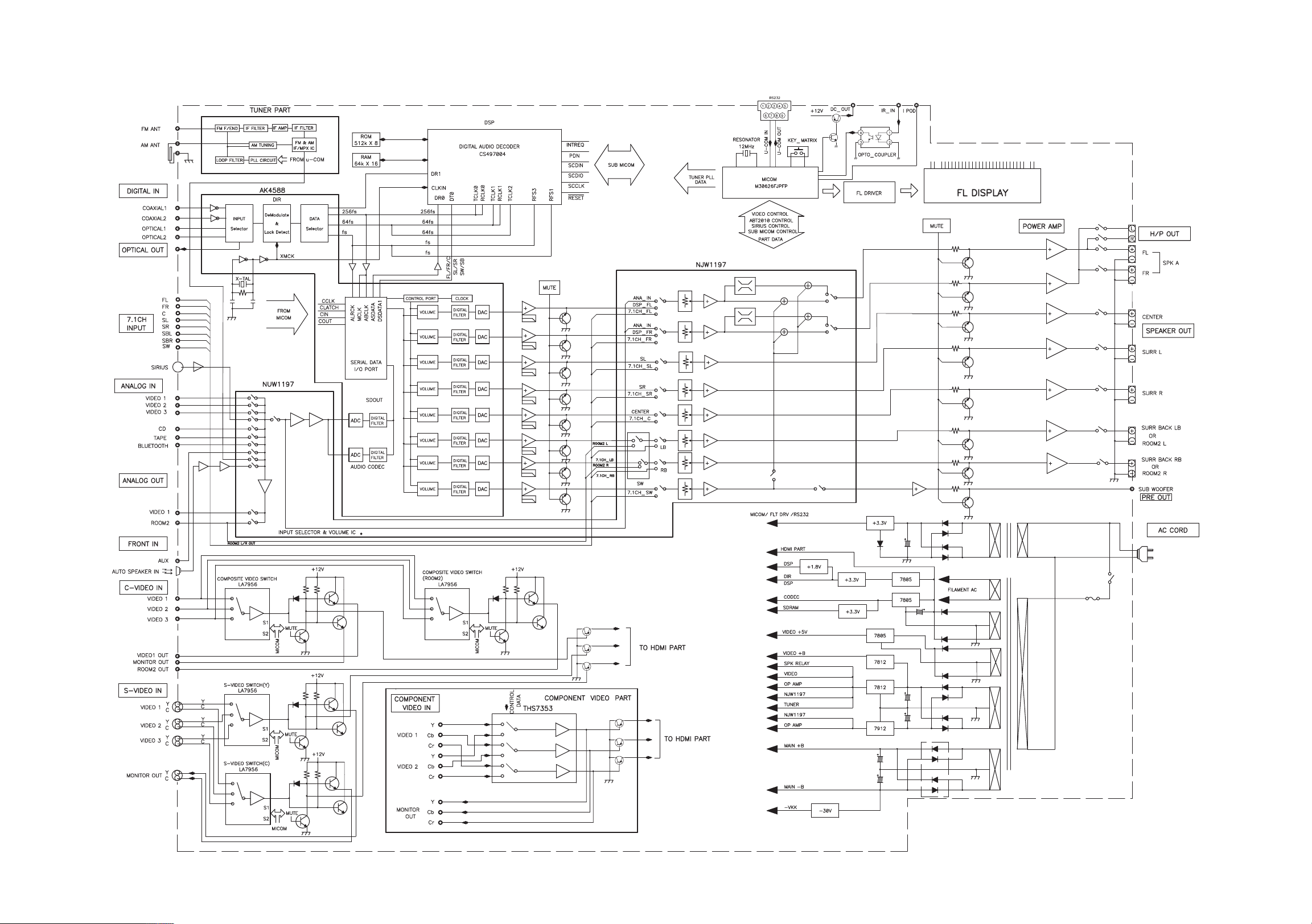

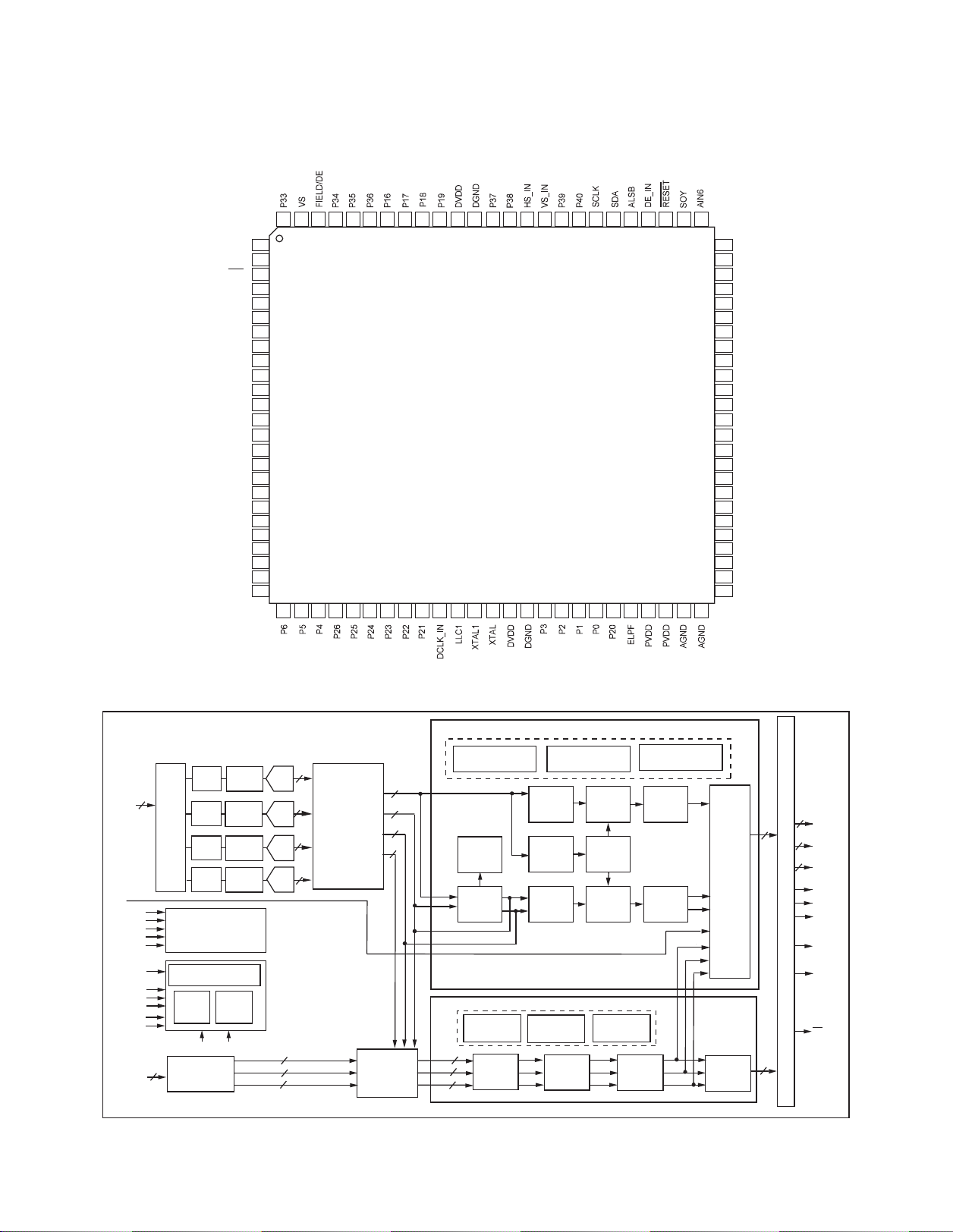

BLOCK DIAGRAM

Model : RD-8504/R-774

12

Page 13

POWER B’D

SPK B’D

MAIN B’D

HDMI B’D

H/P B’D

POWER

SW B’D

DSP B’D

AMP B’D

FRONT B’D

WIRING DIAGRAM

Model : RD-8504/R-774

13

Page 14

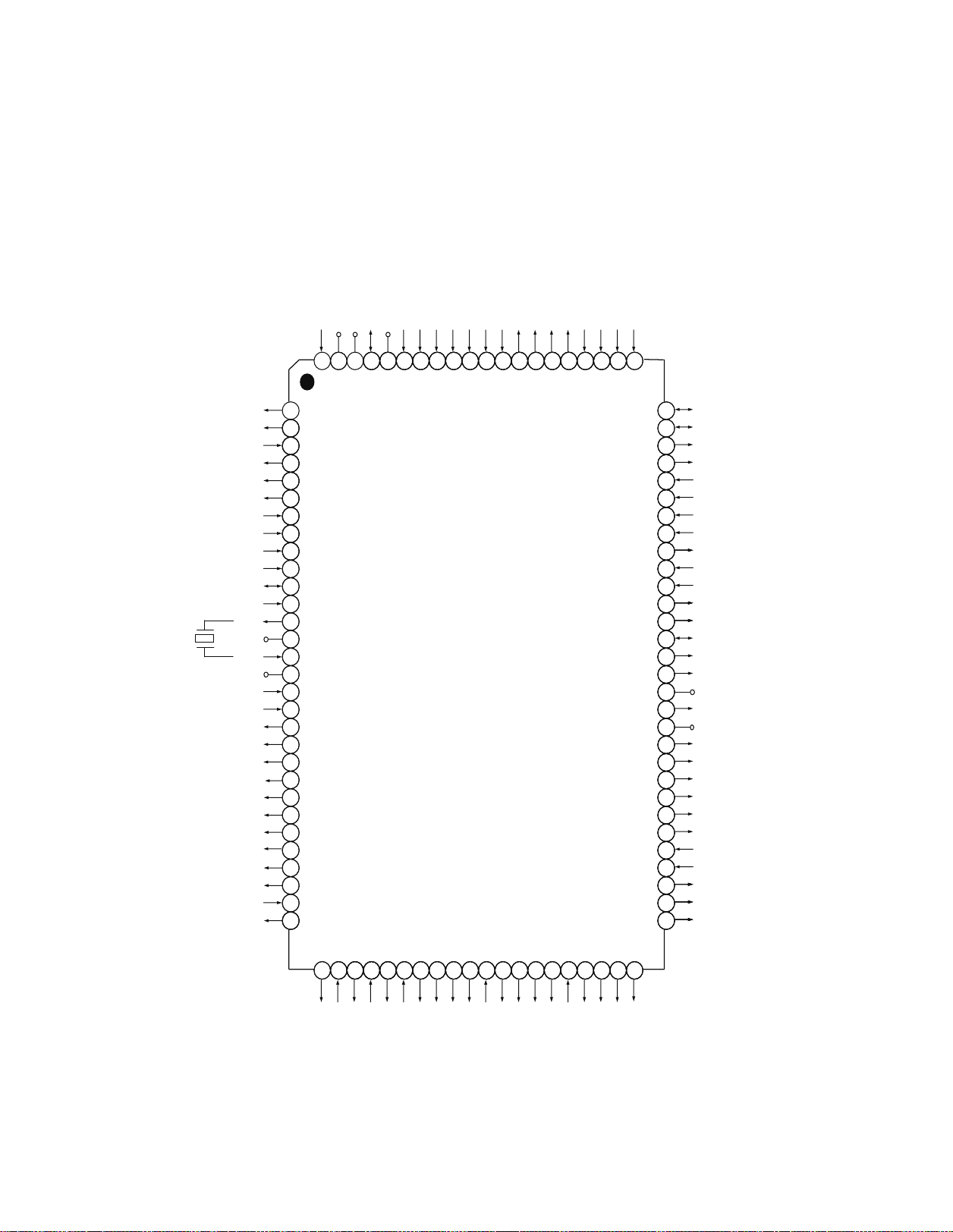

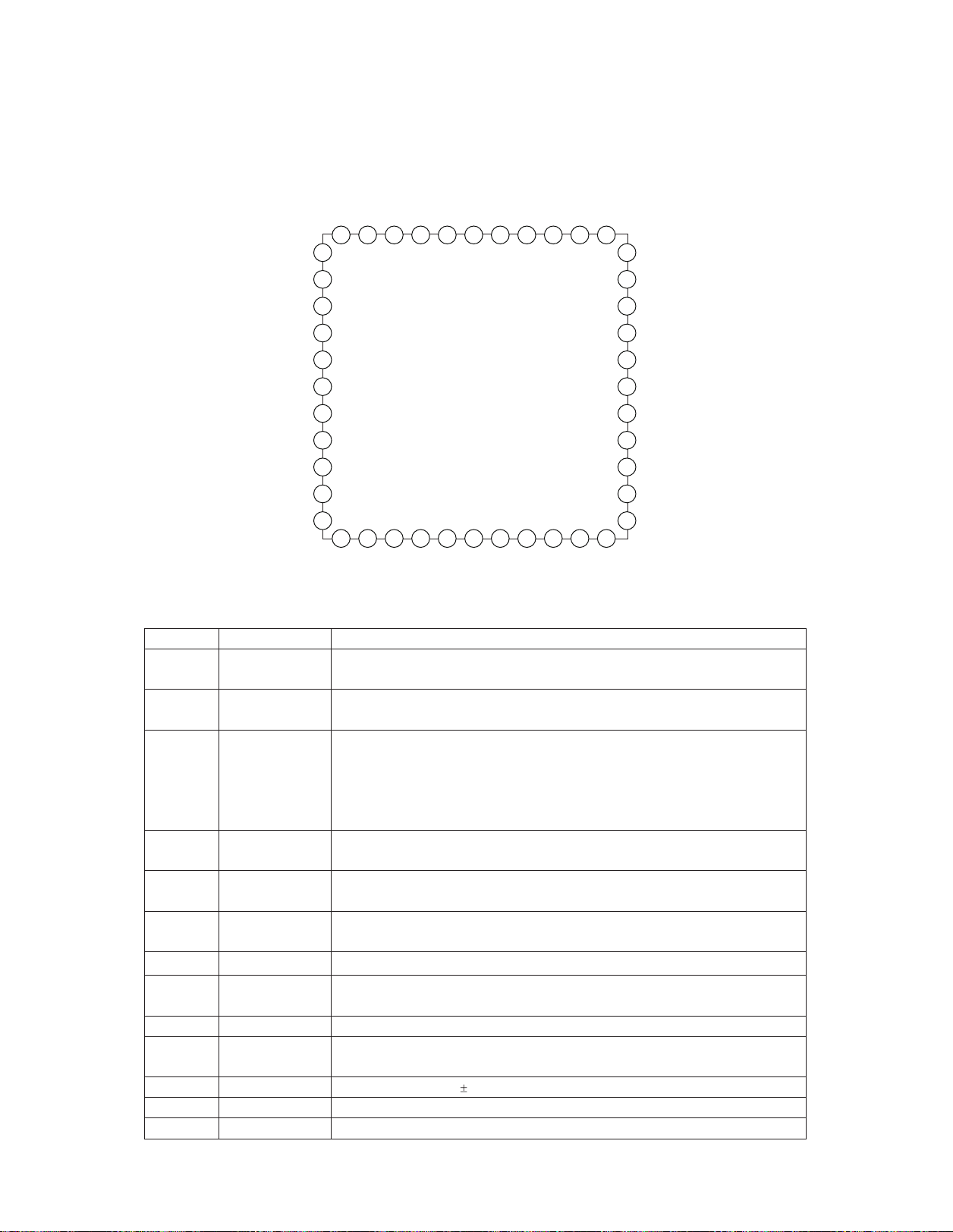

M16C62P : IC402

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

1

80

2

79

3

78

4

77

5

76

6

75

7

74

SUB_IRQ

8

73

ABT2010_IRQ

9

72

PLL_CLK

10

71

11

70

TUNED

12

69

SUBMICOM_RST

13

68

12M

14

67

15

66

7353_SCL

16

65

S2

17

64

18

63

19

62

20

61

21

60

22

59

23

58

24

57

R2_MUTE

25

56

VIDEO_MUTE

26

55

27

54

28

53

29

O.DRAIN

52

30

O.DRAIN

51

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

REC_MUTE

Vcc1=Vcc2=Avcc=VREF:+3V3

NJW1197_CLK

ABT2010_SDI

NJW1197_DATA

SPK_B_RLY

UPGRADE(EPM)

NJW1197_LATCH

UPGRADE(CE)

RS232 TX

ABT2010_SDO

RS232 RX

IPOD_OUT

IPOD_IN

C_RLY

S_RLY

VSS

CVBS_MUTE

S1

VCC1

XIN

SB_RLY

NMI

7353_SDA

VSS

VCC2

OSD_CLK

OSD_CE

R2_S2

R2_S1

SV_DET

OSD_DATA

FL_SW

FUNC_DOWN

VOL_UP

CVBS_DET

AVSS

SUB_DATAIN

AVCC

INPUT_UP

SUB_DATAOUT

SUB_CLK

RESET

ST/BY_RLY

CNVSS(UPGRADE)

SB_MUTE

BLUE_DET

H/P_RLY

S_MUTE

SIRIUS_TX1

F_MUTE

RF_RMC_TX

ABT2010_SCK

ABT2010_CE

R2_MUTE

SW_MUTE

SIRIUS_P/E

SIRIUS_MUTE

4053_CONT

M16C62P

PROTECTION

COMP_DET

INPUT_DN

KEY2

KEY1

POWERDOWN

VREF

FUNC_UP

DC_OUT_SW

SIRIUS_RX1

RED COLOR:These pins must be fixed.

C_MUTE

24C16_SCL

RDS_DATA

F_RLY

BYTE

ST/BY_LED

MAIN_IRQ

FL_CLK

FL_CE

RMC/IR

FL_DATA

XOUT

VOL_DOWN

SUBMICOM_PD

24C16_SDA

RDS_CLK

SV_MUTE

TUNER_DO

PLL_DATA

PLL_CE

1. Pin Description

CIRCUIT DESCRIPTION

14

Page 15

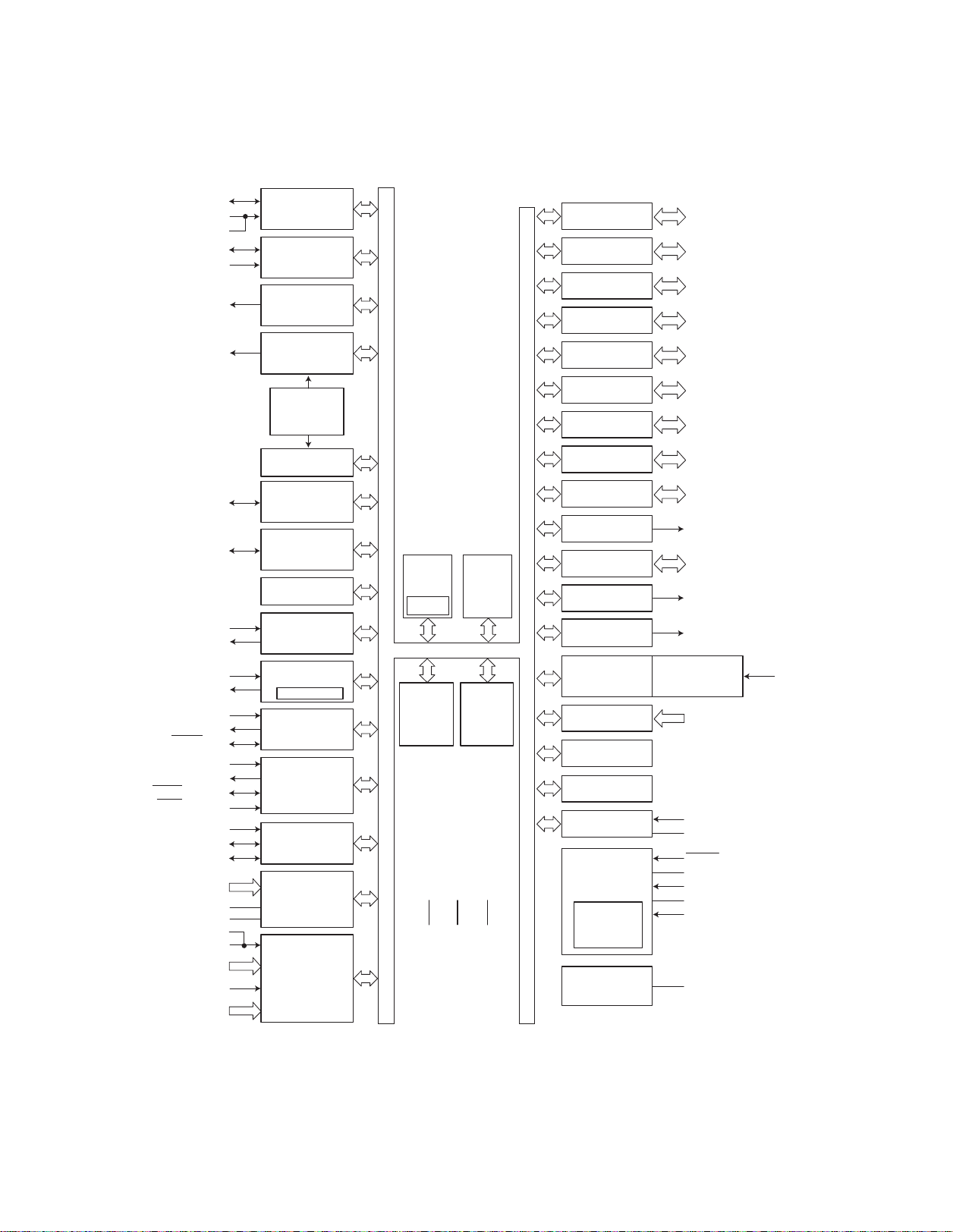

2. Block Diagram

16-bit TIMER/

EVENT COUNTER 00

16-bit TIMER/

EVENT COUNTER 01

TO00/TI010/P01

T

I000/P00 (LINSEL)

RxD6/P14 (LINSEL)

TO01

Note 2

/TI011

Note 2

/P06

TI001

Note 2

/P05

TOH0/P15

TOH1/P16

TI50/TO50/P17

TI51/TO51/P33

RxD0/P11

TxD0/P10

RxD6/P14

TxD6/P13

SI10/P11

SO10/P12

SCK10/P10

8-bit TIMER H0

8-bit TIMER H1

WATCHDOG TIMER

WATCH TIMER

INTERNAL

LOW-SPEED

OSCILLATOR

SERIAL

INTERFACE UART0

78K/0

CPU

CORE

BANK

SERIAL

INTERFACE UART6

LINSEL

SERIAL

INTERFACE CSI10

8-bit TIMER/

EVENT COUNTER 50

8-bit TIMER/

EVENT COUNTER 51

SERIAL

INTERFACE IIC0

A/D CONVERTER

SERIAL INTERFACE

CSI11

Notes 1. Available only in the PD78F0536, 78F0537, and 78F0537D.

2. Available only in the PD78F0534, 78F0535, 78F0536, 78F0537, and 78F0537D.

3. Available only in the PD78F0537D.

Note2

Note2

Note1

Note2

Note2

Note3

8

INTERRUPT

CONTROL

2

4

PORT 0

7

P00 to P06

PORT 1

8

P10 to P17

PORT 2

8

P20 to P27

PORT 3

4

P30 to P33

PORT 4

4

P40 to P43

PORT 5

4

P50 to P53

PORT 6

4

P60 to P63

PORT 7

8

P70 to P77

PORT 12

5

P120 to P124

PORT 13

P130

PORT 14

2

P140, P141

BUZZER OUTPUT

BUZ/P141

CLOCK OUTPUT

CONTROL

PCL/P140

KEY RETURN

8

KR0/P70 to

KR7/P77

RESET CONTROL

MULTIPLIER &

DIVIDER

ON-CHIP DEBUG

SYSTEM

CONTROL

INTERNAL

HIGH-SPEED

OSCILLATOR

VOLTAGE

REGULATOR

POWER ON CLEAR/

LOW VOLTAGE

INDICATOR

EXLVI/P120

RESET

REGC

X1/P121

X2/EXCLK/P122

XT1/P123

XT2/EXCLKS/P124

POC/LVI

CONTROL

FLASH

MEMORY

INTERNAL

HIGH-SPEED

RAM

INTERNAL

EXPANSION

RAM

VDD,

EVDD

VSS,

EVSS

FLMD0

OCD0A

Note 3

/X1, OCD1A

Note 3

/P31

OCD0B

Note 3

/X2, OCD1B

Note 3

/P32

SI11

Note 2

/P03

SO11

Note 2

/P02

SCK11

Note 2

/P04

SSI11

Note 2

/P05

EXSCL0/P62

SDA0/P61

SCL0/P60

ANI0/P20 to

ANI7/P27

AV

REF

AVSS

RxD6/P14 (LINSEL)

INTP0/P120 (LINSEL)

INTP1/P30 to

INTP4/P33

INTP5/P16

INTP6/P140,

INTP7/P141

15

Page 16

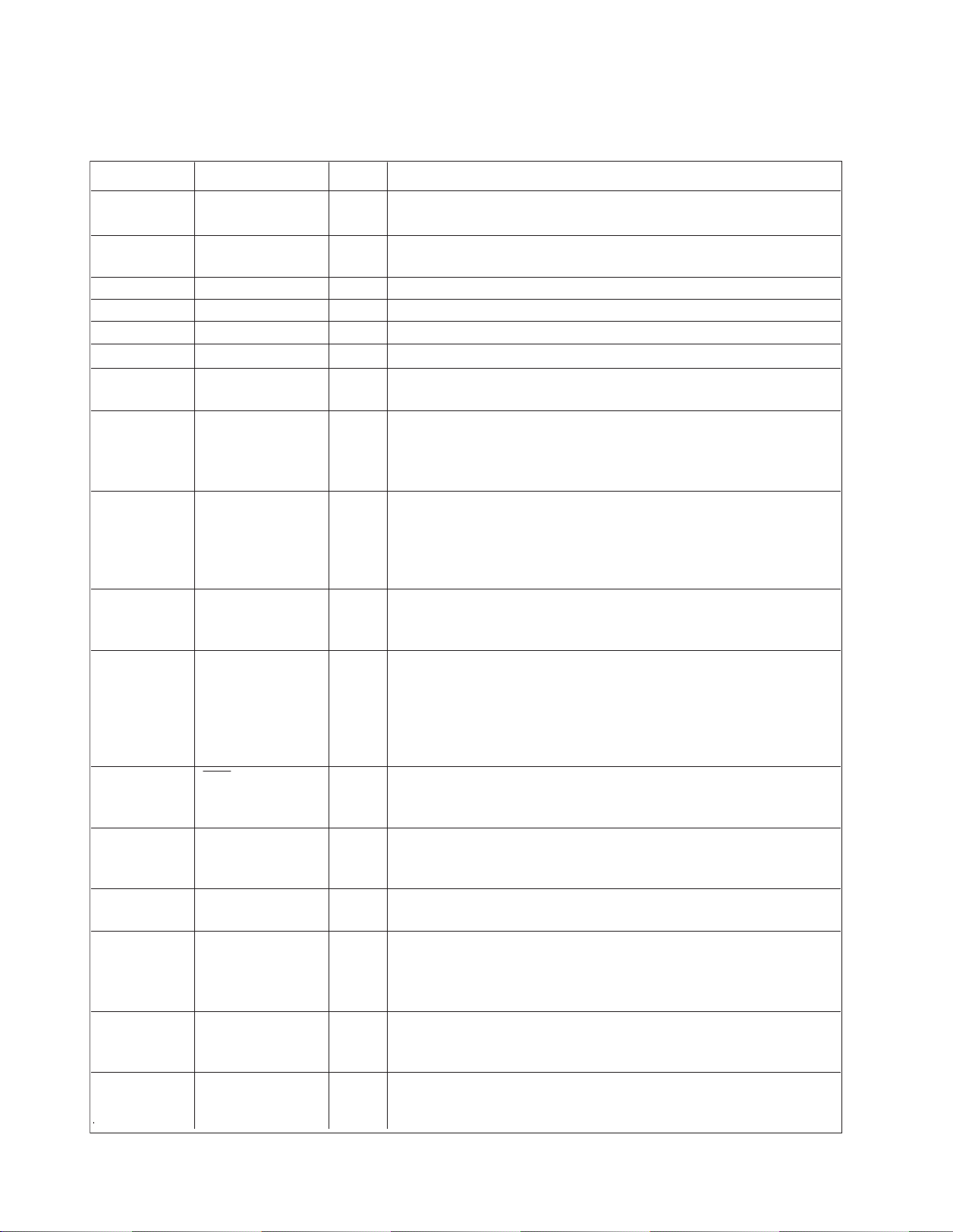

3. Pin Functions

noitpircseDlobmyS.oN niP

1

SUB_SDOUT Serial data signal Output to submicom

2 SUB_CCLK Output Clock Signal for submicom.

3 INPUT_UP Input for input function up.

5

1361CS fo elbane pihc rof tuptuOEC_LF4

51361CS rof tuptuo langis kcolCKLC_LF5

51361CS rof tuptuo langis ataDATAD_LF6

.atad nocomer rof tupnICMR7

"L" dleh si nip siht eht nehw gnol stib 61 si sub atad ehTETYB8

.ecaps yromem lanretxe ni sub atad eht sehctiwSSSVNC9

10 STBY_RLY Output to "STBY Relay ON/OFF" (At "H", it is active)

!desu toNCN11

)evitca si ti ,"L" tA(UPC eht gnitteser rof tupnITESER21

rotallicso latsyrc zHM21 rof tuptuOTUOX31

dnuorGSSV41

rotallicso latsyrc zHM21 rof tupnINIX51

1CCV61

+3.3V power supply

.tpurretni "IMN" eht rof nip tupnIIMN71

)evitca si ti ,"H" tA( "FFO/NO yaleR TNORF" ot tuptuOYLR_F81

)evitca si ti ,"H" tA( "FFO/NO yaleR dnuorruS" ot tuptuOYLR_S91

)evitca si ti ,"H" tA( "FFO/NO yaleR retneC" ot tuptuOYLR_C02

)evitca si ti ,"H" tA( "FFO/NO yaleR kcabdnuorruS" ot tuptuOYLR_BS12

22 BLUE_DET BLUETOOTH DETECT PORT.

)evitca si ti ,"H" tA( "FFO/NO yaleR enohpdaeH" ot tuptuOYLR_PH32

)evitca si ti ,"L" tA(etum lennahc dnuorrus rof tuptuOETUM_S42

25 SB_MUTE Output for surround back channel mute(At "L", it is active)

26 C_MUTE Output for center channel mute(At "L", it is active)

)evitca si ti ,"L" tA(etum lennahc tnorf rof tuptuOETUM_F72

28 DC_OUT Control for "+12V(DC) ON/OFF" (At "H", it is active)

29 SIRIUS_RX Serial data signal Input from SIRIUS.

30 SIRIUS_TX Serial data signal Output to SIRIUS.

31 RS232_TX Serial data signal Output from "ST3232E"

32 RS232_RX Serial data signal Input from "ST3232E"

33 IPOD_OUT Output control data for ipod.

.dopi morf atad lortnoc tupniNI_DOPI43

35 ABT2010_SDO Serial data signal output for ABT2010

36 ABT2010_SDI Serial data signal input from ABT2010

37 ABT2010_SCK Serial Clock signal output for ABT2010

38 ABT2010_CE Output for chip enable of ABT2010

39 ROOM2_MUTE Output for R2 mute(At "L", it is active)

40 SW_MUTE Output for subwoofer channel mute(At "L", it is active)

41 EPM UPGRADE

42 RF_RMC_TX Output data for RF remocon .

43 SPK_B__RLY Output to "Speaker B Relay ON/OFF" (At "H", it is active)

44 SIRIUS_MUTE MUTE signal output for SIRIUS.

45 SIRIUS_PE Output for power enable.

46 UPGRADE_CE UPGRADE

47 1197_LATCH Latch signal output for NJW1197.

48 1197_CLK Clock signal output for NJW1197.

49 1197_DATA Data signal output for NJW1197.

50 REC_MUTE MUTE signal output for NJW1197.

51 OSD_CE Output for chip enable of LC74781

52 OSD_CLK Clock signal output for LC74781

53 OSD_DATA Data signal output for LC74781

54 CVBS_DET Input for detecting "Composite-Video input" condition(At "L", it is active)

16

Page 17

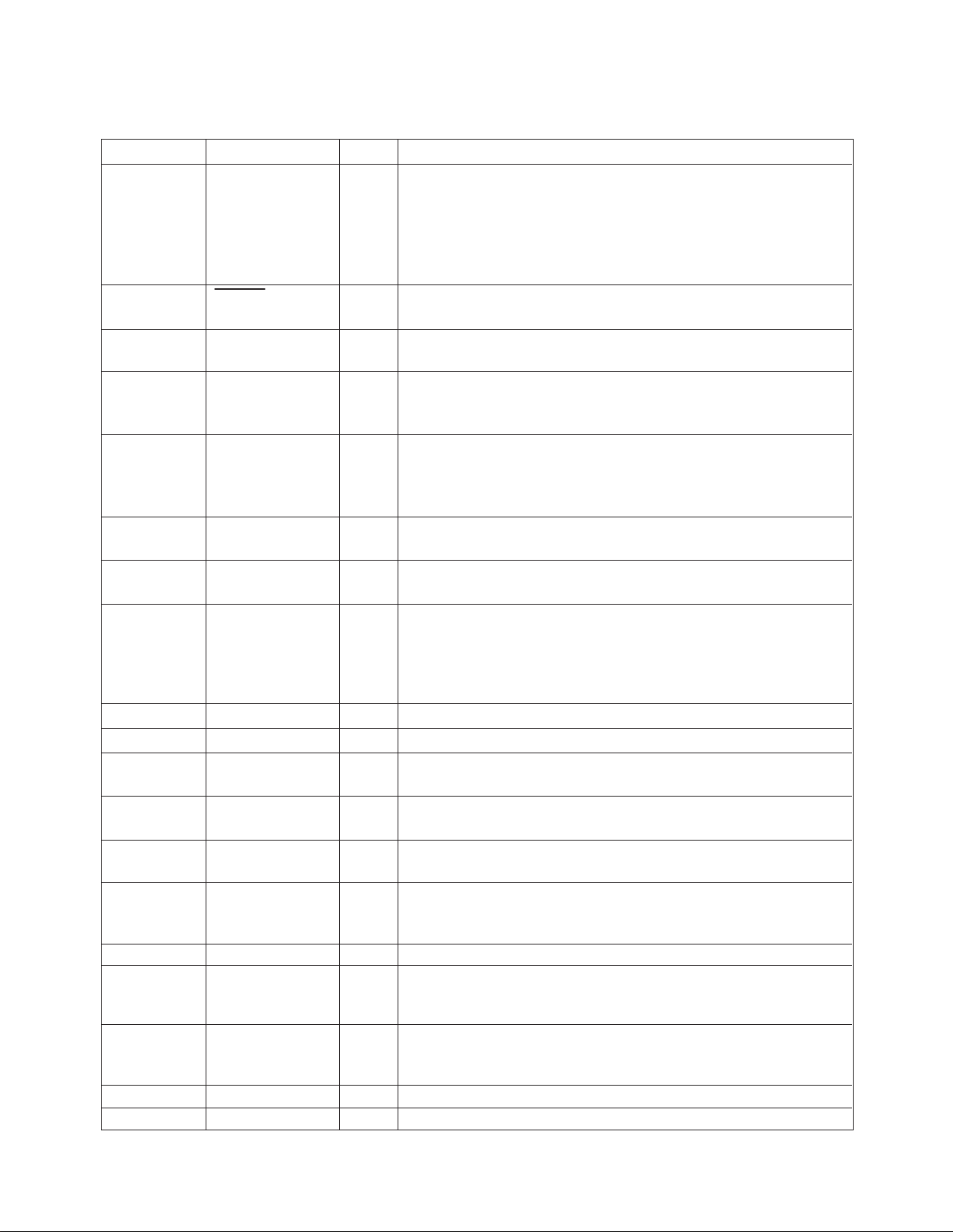

noitpircseDlobmyS.oN niP

)evitca si ti ,"L" tA(noitidnoc "tupni oediV-S" gnitceted rof tupnITED_VS55

56 VIDEO_MUTE Output for control signal of MM74HC4053.

57 R2_MUTE Output for R2 mute(At "L", it is active)

)evitca si ti ,"L" tA(noitidnoc "tupni oediV-etisopmoC" gnitceted rof tupnI1S_2R85

)evitca si ti ,"L" tA(noitidnoc "tupni oediV-S" gnitceted rof tupnI2S_2R95

60 CVBS_MUTE Input for detecting "Component Video input" condition(At "L", it is active)

61 SV_MUTE Output for COMP-VIDEO output mute(At "H", it is active)

62 VCC2 +3.3V power supply

6597AL rof langis lortnoC1S36

64 VSS Ground

6597AL rof langis lortnoC2S56

66 7353_SCL Serial Clock signal for THS7353.

67 7353_SDA Serial data signal for THS7353.

68 SUB_PDN Output PDN DATA for submicom.

69 SUB_RST Output RST DATA for submicom.

)evitca si ti ,"L" tA(noitidnoc "DENUT" gnitceted rof tupnIDENUT07

71 TUNER_DO Data Input from PLL IC

CI LLP ot tuptuo langis kcolCKL_LLP27

73 ABT2010_IRQ Input for ABT2010 Interrupt.

74 SUB_IRQ Input for Submicom Interrupt.

75 RDS_CLK Clock signal input from RDS IC.

76 RDS_DATA Input for RDS data from RDS IC.

77 PLL_DATA Data output to PLL IC

CI LLP fo elbane pihc rof tuptuOEC_LLP87

79 24C16_SCL Clock signal output for M24C16.

80 24C16_SDA Serial data signal for M24C16.

81 FUNC_DN Input for main function down.

82 FUNC_UP Input for main function up.

.pu emulov niam rof tupnIPU_LOV38

.nwod emulov niam rof tupnIND_LOV48

85 STBY_LED Output to drive STAND-BY LED(At "H", it is active)

)evitca si ti ,"H" tA( "FFO/NO +B_LF" ot tuptuOWS_LF68

87 MAIN_IRQ Output Interrupt for Submicom.

88 4053_CONT Output for control signal of 4053.

89 POWERDOWN Input for power down.

.nacs 1yek rof tupni ataD1YEK09

.nacs 2yek rof tupni ataD2YEK19

92 INPUT_DN Input for input function down.

93 COMP_DET Input for detecting "Component Video input" condition(At "L", it is active)

!desu toNCN49

95 PROTECTION Input for detecting "PROTECTION" condition

96 AVSS Ground

!desu toNCN79

98 VREF Reference voltage(Connected to +3.3V, Not VDD)

99 AVCC +3.3V power supply.

100 SUBSDIN Serial data signal Input from submicom

17

Page 18

ADV7401 : IC2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

7

5

74

73

7

2

71

70

69

68

6

7

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

26

27 28 29 30 31 34 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

100

99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76

AIN2

AIN8

AIN1

AIN7

SOG

AIN9

AIN3

TEST1

AGND

CAPY1

CAPY2

AVDD

REFOUT

CML

AGND

BIAS

CAPC1

CAPC2

TEST0

AIN10

AIN4

AIN11

AIN5

AIN12

FB

P11

P32

P31

INT

CS/HS

DGND

DVDDIO

P15

P14

P

13

P

12

DGND

DVDD

P29

P28

SFL/SYNC_OUT

SCLK2

DGND

DVDDIO

SDA2

P10

P9

P8

P27

P7

INPUT

MUX

DATA

PREPROCESSOR

DECIMATION

AND

DOWNSAMPLING

FILTERS

STANDARD DEFINITION PROCESSOR

LUMA

FILTER

OUTPUT FIFO & FORMATTER

10

10

10

AIN1

to

AIN12

SERIAL INTERFACE

CONTROL AND VBI DATA

SCLK

SDA

ALSB

SYNC

EXTRACT

16

HS

8

8

P29-P22

P19-P12

P9-P2

PIXEL

DATA

VS

FIELD/DE

LLC1

SFL/

SYNCOUT

CVBS

S-VIDEO

YPrPb

RGB + CVBS

RGB

12

CHROMA

FILTER

CHROMA

DEMOD

F

SC

RECOVERY

INT

10

LUMA

RESAMPLE

LUMA

2D COMB

(5H MAX)

RESAMPLE

CONTROL

CHROMA

RESAMPLE

CHROMA

2D COMB

(4H MAX)

FAST

BLANK

OVERLAY

CONTROL

FB

Y

Cb

Cr

VBI DATA RECOVERY

MACROVISION

DETECTION

STANDARD

AUTODETECTION

CVBS/Y

C

Cb

Cr

Cb

Y

COLORSPACE

CONVERSION

CVBS

Cr

8

COMPONENT PROCESSOR

SCLK2

SDA2

SSPD

STDI

SYNC PROCESSING AND

CLOCK GENERATION

DCLK_IN

DE_IN

HS_IN

VS_IN

SOG

SOY

DIGITAL INPUT

PORT

DVI or HDMI

XTAL

XTAL1

24

8

8

8

DIGITAL

FINE

CLAMP

GAIN

CONTROL

OFFSET

CONTROL

AV CODE

INSERTION

24

10

10

10

10

10

10

10

ACTIVE PEAK

&

AGC

MACROVISION

DETECTION

CGMS DATA

EXTRACTION

P40-P31

P29-P20

P11-P10

P1-P0

A/DCLAMP

ANTI

ALIAS

FILTER

A/DCLAMP

ANTI

ALIAS

FILTER

A/D

CLAMP

ANTI

ALIAS

FILTER

A/DCLAMP

ANTI

ALIAS

FILTER

1. Pin Description

2. Block Diagram

18

Page 19

3. Pin Functions

Pin No. Mnemonic Type Function

54, 56, 58,

72, 74, 76,

53, 55, 57,

71, 73, 75

AIN1–AIN12 I Analog video input channels.

42, 41, 28,

27, 26, 25,

23, 22, 10,

9, 8, 7, 94,

93, 92, 91

P2–P9, P12–

P19

O Video pixel output port.

33, 32, 31,

30, 29, 24,

14, 13

P22-P29 I/O Video input/output port

44, 43, 21,

20, 45, 34,

2, 1, 100,

97, 96, 95,

88, 87, 84,

83

P0–P1, P10–

P11, P20–P21,

P31–P40

I Video pixel input port.

3

INT

O Interrupt pin, can be active low or active high. When SDP/CP

status bits change this pin will trigger. The set of events which

will trigger an interrupt are under user control.

4 HS/CS O HS is a horizontal synchronization output signal in SDP and

CP modes. CS is a digital composite synchronization signal

that can be selected while in CP mode.

99 VS O VS is a vertical synchronization output signal in SDP and CP

modes.

98 FIELD/DE O FIELD is a field synchronization output signal in all

interlaced video modes. This pin also can be enabled as a DE

(Data Enable) signal in CP mode to allow direct connection to

a HDMI/DVI Tx IC.

81, 19 SDA1, SDA2 I/O I

2

C port serial data input/output pin, SDA1 is the data line for

the Control port and SDA2 is the data line for the VBI

readback port.

82, 16 SCLK1,

SCLK2

I I

2

C port serial clock input (max clock rate of 400 kHz).

SCLK1 is the clock line for the Control port and SCLK2 is

the clock line for the VBI data readback port.

5, 11, 17,

40, 89

DGND G Digital ground

49, 50, 60,

66

AGND G Analog ground

6, 18 DVDDIO P Digital I/O supply voltage (3.3 V).

12, 39, 90 DVDD P Digital core supply voltage (1.8 V).

63 AVDD P Analog supply voltage (3.3 V).

47, 48 PVDD P PLL supply voltage (1.8 V).

51 FB I FB is a fast switch overlay input that switches between CVBS

and RGB analog signals.

19

Page 20

Pin No. Mnemonic Type Function

37 XTAL1 O This pin should be connected to the 28.636363 MHz crystal

or left as a no connect if an external 3.3 V 28.636363 MHz

clock oscillator source is used to clock the ADV7401. In

crystal mode the crystal must be a fundamental crystal.

46 ELPF O The recommend external loop filter must be connected to this

ELPF pin.

70, 59 TEST0 -

TEST1

O These pins should be left unconnected

15 SFL/SYNC_O

UT

O SFL (Subcarrier Frequency Lock); this pin contains a serial

output stream which can be used to lock the subcarrier

frequency when this decoder is connected to any Analog

Devices digital video encoder. SYNC_OUT is the sliced sync

output signal only available in CP mode.

64 REFOUT O Internal voltage reference output.

65 CML O The CML pin is a common-mode level for the internal ADCs.

61, 62 CAPY1–

CAPY2

I ADC capacitor network.

68, 69 CAPC1–

CAPC2

I ADC capacitor network.

67 BIAS O BIAS is an external bias setting pin. Connect the

recommended resistor between pin and ground.

86 HS_IN/CS_IN I Can be configured in CP mode to be either a digital HS input

signal or a digital CS input signal used to extract timing in a

5-wire or 4-wire RGB mode.

85 VS_IN I VS input signal used in CP mode for 5-wire timing mode.

79 DE_IN I DE_IN is a data enable input signal used in 24-bit digital

input port mode, for example,

24-bit RGB data from a DVI Rx IC.

35 DCLK_IN I DCLK_IN is a clock input signal used in 24-bit digital input

mode (e.g. 24-bit RGB data from a DVI Rx IC) and also in

digital CVBS input mode.

52 SOG I SOG is a sync on green input used in embedded sync mode.

77 SOY I SOY is a sync on luma input used in embedded sync mode.

80 ALSB I This pin selects the I

2

C address for the ADV7401 Control and

VBI readback ports. ALSB set to a logic 0 sets the address for

a write to control port of 0x40 and the readback address for

the VBI port of 0x21. ALSB set to a logic high sets the

address for a write to control port of 0x42 and the readback

address for the VBI port of 0x23.

78

RESET

I System reset input, active low. A minimum low reset pulse

width of 5 ms is required to reset the ADV7401 circuitry.

36 LLC1 O LLC1 is a line locked output clock for the pixel data (range is

13.5MHz to 110MHz).

38 XTAL I Input pin for 28.636363 MHz crystal, or can be overdriven by

an external 3.3 V 28.636363 MHz clock oscillator source to

clock the ADV7401.

20

Page 21

AK4588 : IC1008

CCLK/SCL

CDTI/SD

A

CSN

DAUX1

SDTI4

SDTI3

SDTI2

SDTI1

XTL1

XTL0

PDN

MASTER

DZF2

DZF1

LOUT4

NC

ROUT4

NC

LOUT3

NC

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

INT1

BOUT

TVDD

DVDD

DVSS

XTO

XTI

TEST3

MCKO2

MCKO1

COUT

UOUT

VOUT

SDTO2

BICK2

LRCK2

SDTO1

BICK1

LRCK1

CDTO

TEST1

RX1

NC

RX0

A

VSS

A

VDD

VREFH

VCOM

RIN

LIN

NC

ROUT1

NC

LOUT1

NC

ROUT2

NC

LOUT2

NC

ROUT3

INT0

TX1

TX0

MCLK

VIN

DAUX2

I2C

RX7

CAD1

RX6

CAD0

RX5

TEST2

RX4

PVDD

R

PVSS

RX3

NC

RX2

1. Pin Description

21

Page 22

Input

Selecto

r

Clock

R

ecovery

Clock

Generator

DAIF

Decoder

A

C-3/MPEG

Detect

DEM

µP I/F

Audio

I

/F

X'tal

Oscillato

r

PDN

INT0

LRCK2

BICK2

SDTO2

DAUX2

MCKO2

XTOXTI

R

PVDDPVSS

CDTI

CDTO

CCLK

CSN

DVDD

DVSS

TVDD

MCKO1

I2C

R

X0

RX1

RX2

R

X3

RX4

R

X5

R

X6

RX7

D

IT

TX0

Error &

Detect

STATUS

INT1

Q-subcode

b

uffe

r

TX1

B,C,U,

VOUT

8 to 3

VIN

Audio

I/F

LPF

LPF

LPF

LPF

LPF

LPF

LOUT1

ROUT1

LOUT2

ROUT2

LOUT3

ROUT3

DAC

DATT

DEM

ADC

HPF

ADC

HPF

RIN

LIN

LRCK1

BICK1

SDTI1

SDTI2

SDTI3

DAUX1

MCLK

LRCK

BICK

SDOUT

SDIN1

SDIN2

SDIN3

MCLK

SDTO1

Format

Converter

SDTI4

SDIN4

LPF

LPF

LOUT4

ROUT4

DAC

DATT

DEM

DAC

DATT

DEM

DAC

DATT

DEM

DAC

DATT

DEM

DAC

DATT

DEM

DAC

DATT

DEM

DAC

DATT

DEM

AVD D

AVSS

2. Block Diagram

22

Page 23

3. Pin Functions

31 PDN I

Power-Down Mode Pin

When “L”, the AK4588 is powered-down, all output pin goes “L”, all registers are

reset. When CAD1/0 pins are changed, the AK4588 should be reset by PDN pin.

32 MASTER I

Master Mode Select Pin (Internal pull-down pin)

“H”: Master mode, “L”: Slave mode

DZF2 O

Zero Input Detect 2 Pin (Note 1)

When the input data of the group 1 follow total 8192 LRCK cycles with “0” input

data, this pin goes to “H”. And when RSTN bit is “0”, PWDAN bit is “0”, this pin

goes to “H”. It always is in “L” when P/S is “H”.

33

OVF O

Analog Input Overflow Detect Pin (Note 2)

This pin goes to “H” if the analog input of Lch or Rch overflows.

34 DZF1 O

Zero Input Detect 1 Pin (Note 1)

When the input data of the group 1 follow total 8192 LRCK cycles with “0” input

data, this pin goes to “H”. And when RSTN bit is “0”, PWDAN bit is “0”, this pin

goes to “H”. Output is selected by setting DZFE pin when P/S is “H”.

35 LOUT4 O DAC4 Lch Analog Output Pin

Notes:

1. The group 1 and 2 can be selected by DZFM2-0 bits.

2. This pin becomes OVFE bit if OVFE bit is set to 1.

36 NC -

No Connect

No internal bonding.

37 ROUT4 O DAC4 Rch Analog Output Pin

38 NC -

No Connect

No internal bonding.

39 LOUT3 O DAC3 Lch Analog Output Pin

40 NC -

No Connect

No internal bonding.

noitcnuF O/I emaN niP .oN

1 INT1 O Interrupt 1 Pin

2

BOUT O

Block-Start Output Pin for Receiver Input

“H” during first 40 flames.

3 TVDD -

Output Buffer Power Supply Pin, 2.7V∼5.5V

4 DVDD - Digital Power Supply Pin, 3.3V

5 DVSS - Digital Ground Pin

6 XTO O X'tal Output Pin

7 XTI I X'tal Input Pin

8 TEST3 I

Test 3 Pin

This pin should be connected to DVSS.

9 MCKO2 O Master Clock Output 2 Pin

10 MCKO1 O Master Clock Output 1 Pin

11 COUT O C-bit Output Pin for Receiver Input

12 UOUT O U-bit Output Pin for Receiver Input

13 VOUT O V-bit Output Pin for Receiver Input

14 SDTO2 O Audio Serial Data Output Pin(DIR/DIT part)

15 BICK2 I/O Audio Serial Data Clock Pin(DIR/DIT part)

16 LRCK2 I/O Channel Clock Pin(DIR/DIT part)

17 SDTO1 O Audio Serial Data Output Pin(ADC/DAC part)

18 BICK1 I/O Audio Serial Data Clock Pin(ADC/DAC part)

19 LRCK1 I/O Input Channel Clock Pin

20 CDTO O Control Data Output Pin in Serial Mode, I2C= “L”.

CCLK I Control Data Clock Pin in Serial Mode, I2C= “L”

21

SCL I Control Data Clock Pin in Serial Mode, I2C= “H”

CDTI I Control Data Input Pin in Serial Mode, I2C= “L”.

22

SDA I/O Control Data Pin in Serial Mode, I2C= “H”.

I Chip Select Pin in Serial Mode, I2C=”L”.

23 CSN

I This pin should be connected to DVSS, I2C=”H”.

24 DAUX1 I AUX Audio Serial Data Input Pin(ADC/DAC part)

25 SDTI4 I DAC4 Audio Serial Data Input Pin

26 SDTI3 I DAC3 Audio Serial Data Input Pin

27 SDTI2 I DAC2 Audio Serial Data Input Pin

28 SDTI1 I DAC1 Audio Serial Data Input Pin

29 XTL1 I X’tal Frequency Select 0 Pin

30 XTL0 I X’tal Frequency Select 1 Pin

23

Page 24

55 AVDD -

Analog Power Supply Pin, 4.5V∼5.5V

56 AVSS -

Analog Ground Pin, 0V

57 RX0 I

Receiver Channel 0 Pin (Internal biased pin)

This channel is default in serial mode.

58 NC -

No Connect

No internal bonding.

59 RX1 I Receiver Channel 1 Pin (Internal biased pin)

60 TEST1 I

Test 1 Pin

This pin should be connected to PVSS.

61 RX2 I Receiver Channel 2 Pin (Internal biased pin)

62 NC -

No Connect

No internal bonding.

63 RX3 I Receiver Channel 3 Pin (Internal biased pin)

64 PVSS - PLL Ground pin

65 R -

External Resistor Pin

12kΩ +/-1% resistor should be connected to PVSS externally.

66 PVDD - PLL Power supply pin, 5.0V

67 RX4 I Receiver Channel 4 Pin (Internal biased pin)

68 TEST2 I

Test 2 Pin

This pin should be connected to PVSS.

69 RX5 I Receiver Channel 5 Pin (Internal biased pin)

70 CAD0 I

Chip Address 0 Pin (ADC/DAC part)

71 RX6 I Receiver Channel 6 Pin (Internal biased pin)

72 CAD1 I

Chip Address 1 Pin (ADC/DAC part)

73 RX7 I Receiver Channel 7 Pin (Internal biased pin)

74 I2C I

Control Mode Select Pin.

“L”: 4-wire Serial, “H”: I

2

C Bus

75 DAUX2 I Auxiliary Audio Data Input Pin (DIR/DIT part)

76 VIN I V-bit Input Pin for Transmitter Output

77 MCLK I

Master Clock Input Pin

78 TX0 O Transmit Channel (Through Data) Output 0 Pin

79 TX1 O

Transmit Channel Output1 pin

When TX bit = “0”, Transmit Channel (Through Data) Output 1 Pin.

When TX bit = “1”, Transmit Channel (DAUX2 Data) Output Pin (Default).

80 INT0 O Interrupt 0 Pin

Notes:

3. All input pins except internal biased pins and internal pull-down pin should not be left floating.

noitcnuF O/I emaN niP .oN

41 ROUT3 O DAC3 Rch Analog Output Pin

42 NC -

No Connect

No internal bonding.

43 LOUT2 O DAC2 Lch Analog Output Pin

44 NC -

No Connect

No internal bonding.

45 ROUT2 O DAC2 Rch Analog Output Pin

46 NC -

No Connect

No internal bonding.

47 LOUT1 O DAC1 Lch Analog Output Pin

48 NC -

No Connect

No internal bonding.

49 ROUT1 O DAC1 Rch Analog Output Pin

50 NC -

No Connect

No internal bonding.

51 LIN I Lch Analog Input Pin

52 RIN I Rch Analog Input Pin

53 VCOM -

Common Voltage Output Pin

2.2µF capacitor should be connected to PVSS externally.

54 VREFH -

Positive Voltage Reference Input Pin, AVDD

24

Page 25

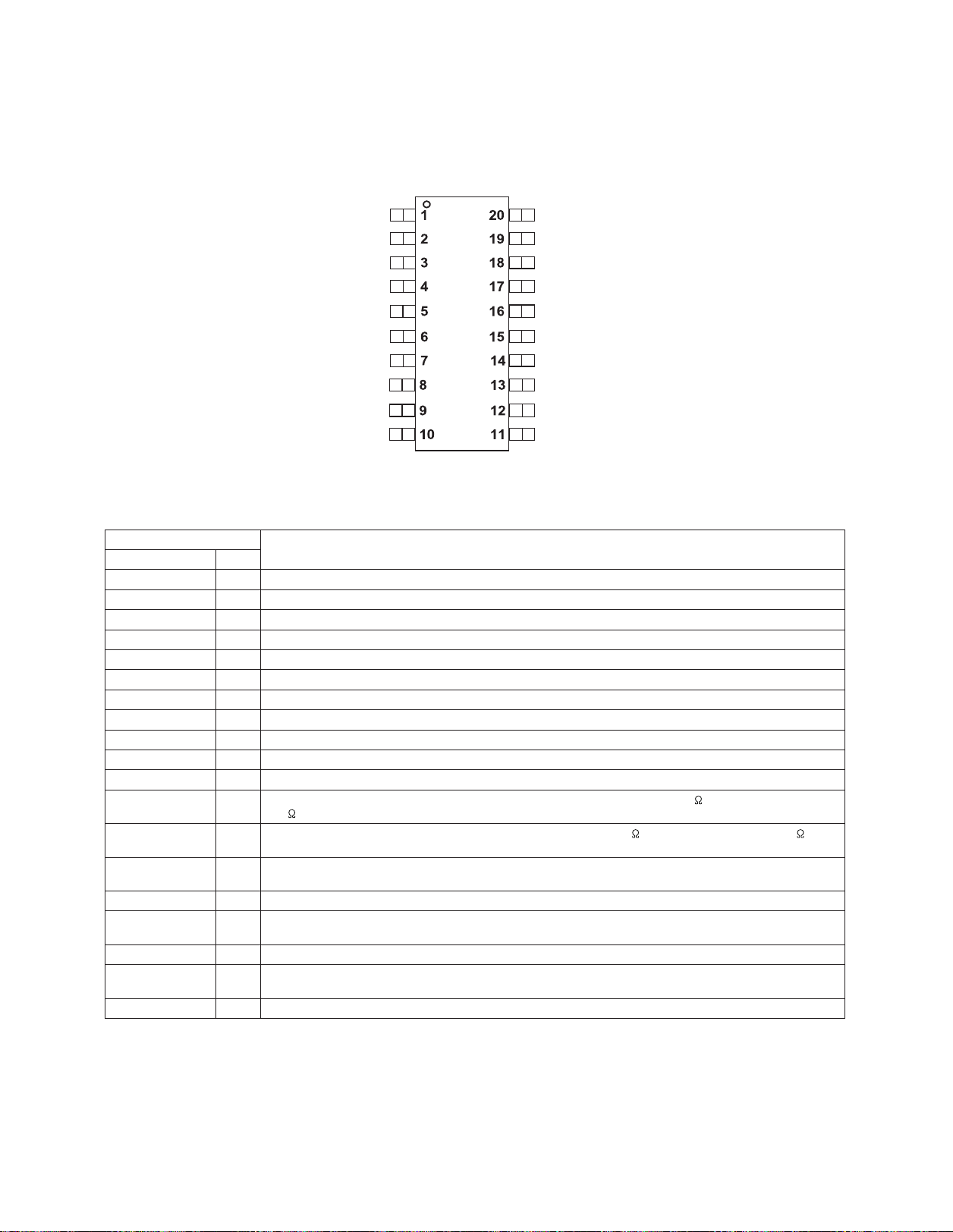

THS7353 : IC206

CH. 2 - INPUT A

CH. 1 - INPUT A

NCNC

CH. 3 - INPUT A

CH. 1 - INPUT B

CH. 2 - INPUT B

CH. 3 - INPUT B

CH. 1 - GAIN ADJ.

CH. 1 - OUTPUT

CH. 2 - OUTPUT

CH. 3 - GAIN ADJ.

CH. 3 - OUTPUT

CH. 3 - GAIN ADJ.

I2C-SCL

I2C-A1

I2C-SDA

I2C-A0

V

S+

GND

TERMINAL

DESCRIPTION

NAME NO.

N/C 1, 20 No Internal Connection. It is recommended, but not required, to connect these pins to GND

CH. 1–INPUT A2Video Input Channel 1. Input A

CH. 2–INPUT A3Video Input Channel 2. Input A

CH. 3–INPUT A4Video Input Channel 3. Input A

CH. 1–INPUT B5Video Input Channel 1. Input B

CH. 2–INPUT B6Video Input Channel 2. Input B

CH. 3–INPUT B7Video Input Channel 3. Input B

I2C-A1 8I

2

C Slave Address Control Bit A1. Connect to Vs+ for a logic 1 preset value or GND for a logic 0 preset value.

I2C-A0 9I2C Slave Address Control Bit A0. Connect to Vs+ for a logic 1 preset value or GND for a logic 0 preset value.

GND 10 Ground reference pin for all internal circuitry

Vs+ 11 Positive Power Supply Input Pin. Connect to 2.7 V to 5V

Serial data line of the I2C bus. Pull-up resistor should have a minimum value = 2-k and a maximum value =

SDA 12

19-k . Pull up to Vs+

I2C bus clock line. Pull-up resistor should have a minimum value = 2-k and a maximum value = 19-k . Pull

SCL 13

up to Vs+

Channel 3 gain adjustment pin. Short to CH. 3-OUTPUT pin for 0-dB gain. Or add external resistors and/or

CH. 3-GAIN ADJ. 14

capacitors to analog ground for signal gain.

CH. 3–OUTPUT 15 Video output channel 3 from either CH. 3–INPUT A or CH. 3–INPUT B

Channel 2 gain adjustment pin. Short to CH. 2-OUTPUT pin for 0-dB gain. Or add external resistors and/or

CH. 2-GAIN ADJ. 16

capacitors to analog ground for signal gain.

CH. 2–OUTPUT 17 Video output channel 2 from either CH. 2–INPUT A or CH. 2–INPUT B

Channel 1 gain adjustment pin. Short to CH. 1-OUTPUT pin for 0-dB gain. Or add external resistors and/or

CH. 1-GAIN ADJ. 18

capacitors to analog ground for signal gain.

CH. 1–OUTPUT 19 Video output channel 1 from either CH. 1–INPUT A or CH. 1–INPUT B

1. Pin Description

25

Page 26

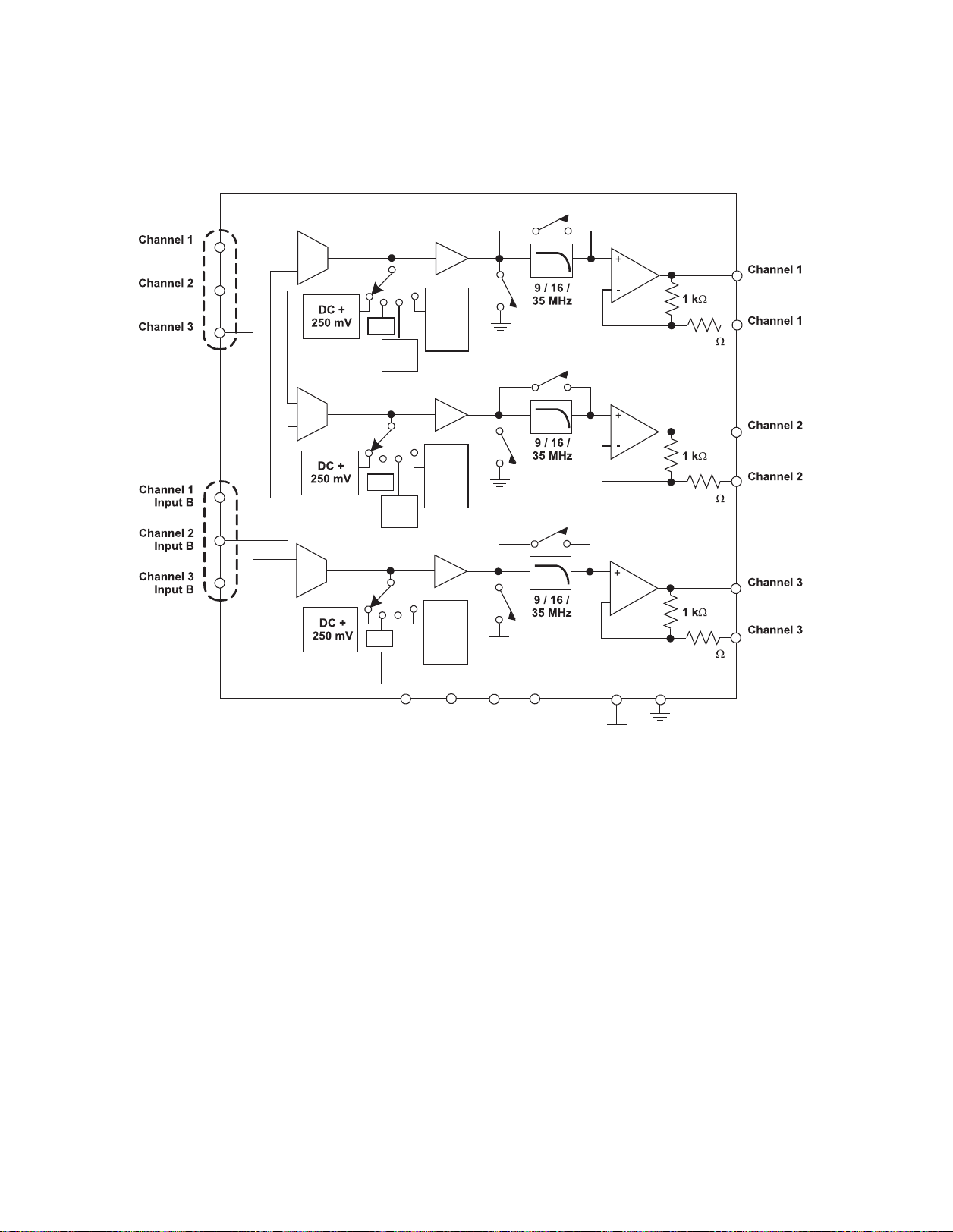

12CSDA

12C-

A1

12C-

A0

12CSCL

LPF

AC

Sync

TIP

Clamp

AC

Sync

TIP

Clamp

AC

Sync

TIP

Clamp

AC-

BIAS

AC-

BIAS

AC-

BIAS

DC

250

250

250

X1

Gain Adjust

Gain Adjust

Gain Adjust

Output

Input A

Input A

Input A

Output

Output

MUTE

Bypass

2:1

LPF

DC

X1

MUTE

Bypass

2:1

LPF

DC

X1

MUTE

Bypass

2:1

Vs+

NOTE: The I2C Address of the THS7353 is 01011(A1)(A0)(R/W)

2. Block Diagram

26

Page 27

NJW1197 : IC401

1 30

31

50

5180

81

100

Multi-Channel Input A

Multi-Channel Input C Multi-Channel Input B

2 Channel Input

LAIN

RAIN

CAIN

LSAIN

RSAIN

LBAIN

RBAIN

SWAIN

DCLA1DCLA2

DCRA1DCRA2

Input Selector

Gain

Input Selector

Gain

Input Selector

REC Output

Selector

SWBIN

RBBIN

LBBIN

RSBIN

LSBIN

CBIN

RBIN

LBIN

FIL_TR

FIL_BR1

FIL_BR2

FIL_TL

FIL_BL1

FIL_BL2

RBCI

LBCIN

RSCIN

LSCIN

FR-

FR+

FL-

FL+

Volume

Output

Gain

BSW

SSW

SWOUT

RBOUT

LBOUT

RSOUT

LSOUT

COUT

ROUT

LOUT

V+

GND

V-

LATCH

DATA

CLOCK

RECA1L

RECA1R

RECA2L

RECA2R

RECA3L

RECA3R

RECA4L

RECA4R

RECB1L

RECB1R

MUTE

ADR

TSW

SW

SW

TONE

Multi-channel

Volume

COM

Interface

Supply

Voltage

TONE

1. Pin Description

2. Block Diagram

27

Page 28

No. SYMBOL FUNCTION No. SYMBOL FUNCTION

1 ROUT Rch output 51 DCR_IN “Multi-channel selector” Rch input

2 COUT Cch output 52 DCR_OUT “Input selector” Rch output

3 LSOUT LSch output 53 GND Ground

4 RSOUT RSch output 54 DCL_IN “Multi-channel selector” Lch input

5 LBOUT LBch output 55 DCL_OUT “Input selector” Lch output

6 RBOUT RBch output 56 GND Ground

7 SWOUT SWch output 57 REC_B1R “Input selector” Rch REC output B1

8 GND Ground 58 REC_B1L “Input selector” Lch REC output B1

9 FIL_BL2 Lch Bass filter terminal 2 59 REC_A4R “Input selector” Rch REC output A4

10 FIL_BL1 Lch Bass filter terminal 1 60 REC_A4L “Input selector” Lch REC output A4

11 FIL_TL Lch Treble filter terminal 61 REC_A3R “Input selector” Rch REC output A3

12 TCAP Switching noise rejection capacitor 62 REC_A3L “Input selector” Lch REC output A3

13 FIL_BR2 Rch Bass filter terminal 2 63 REC_A2R “Input selector” Rch REC output A2

14 FIL_BR1 Rch Bass filter terminal 1 64 REC_A2L “Input selector” Lch REC output A2

15 FIL_TR Rch Treble filter terminal 65 REC_A1R “Input selector” Rch REC output A1

16 V+ + Power supply voltage input 66 REC_A1L “Input selector” Lch REC output A1

17 ADR Chip address select input 67 VDDOUT Internal Digital +Power Supply Output

18 V- - Power supply voltage input 68 DATA Control data signal input

19 L1IN “Input selector” Lch input 1 69 CLOCK Clock signal input

20 DCCAP_SW Switching noise rejection capacitor 70 LATCH Latch signal input

21 R1IN “Input selector” Rch input 1 71 MUTE External mute control

22 DCCAP_RB Switching noise rejection capacitor 72 FL+ “Input selector gain control” Lch no-inverted output

23 L2IN “Input selector” Lch input 2 73 FL- “Input selector gain control” Lch inverted output

24 DCCAP_LB Switching noise rejection capacitor 74 FR+ “Input selector gain control” Rch no-inverted output

25 R2IN “Input selector” Rch input 2 75 FR- “Input selector gain control” Rch inverted output

26 DCCAP_RS Switching noise rejection capacitor 76 GND Ground

27 L3IN “Input selector” Lch input 3 77 LSCIN Multi-channel LSch input C

28 DCCAP_LS Switching noise rejection capacitor 78 RSCIN Multi-channel RSch input C

29 R3IN “Input selector” Rch input 3 79 LBCIN Multi-channel LBch input C

30 DCCAP_C Switching noise rejection capacitor 80 RBCIN Multi-channel RBch input C

31 L4IN “Input selector” Lch input 4 81 GND Ground

32 DCCAP_R Switching noise rejection capacitor 82 LAIN Multi-channel Lch input A

33 R4IN “Input selector” Rch input 4 83 RAIN Multi-channel Rch input A

34 DCCAP_L Switching noise rejection capacitor 84 CAIN Multi-channel Cch input A

35 L5IN “Input selector” Lch input 5 85 LSAIN Multi-channel LSch input A

36 GND Ground 86 RSAIN Multi-channel RSch input A

37 R5IN “Input selector” Rch input 5 87 LBAIN Multi-channel LBch input A

38 GND Ground 88 RBAIN Multi-channel RBch input A

39 L6IN “Input selector” Lch input 6 89 SWAIN Multi-channel SWch input A

40 L9IN “Input selector” Lch input 9 90 GND Ground

41 R6IN “Input selector” Rch input 6 91 LBIN Multi-channel Lch input B

42 R9IN “Input selector” Rch input 9 92 RBIN Multi-channel Rch input B

43 L7IN “Input selector” Lch input 7 93 CBIN Multi-channel Cch input B

44 L10IN “Input selector” Lch input 10 94 LSBIN Multi-channel LSch input B

45 R7IN “Input selector” Rch input 7 95 RSBIN Multi-channel RSch input B

46 R10IN “Input selector” Rch input 10 96 LBBIN Multi-channel LBch input B

47 L8IN “Input selector” Lch input 8 97 RBBIN Multi-channel RBch input B

48 L11IN “Input selector” Lch input 11 98 SWBIN Multi-channel SWch input B

49 R8IN “Input selector” Rch input 8 99 GND Ground

50 R11IN “Input selector” Rch input 11 100 LOUT Lch output

3. Pin Functions

28

Page 29

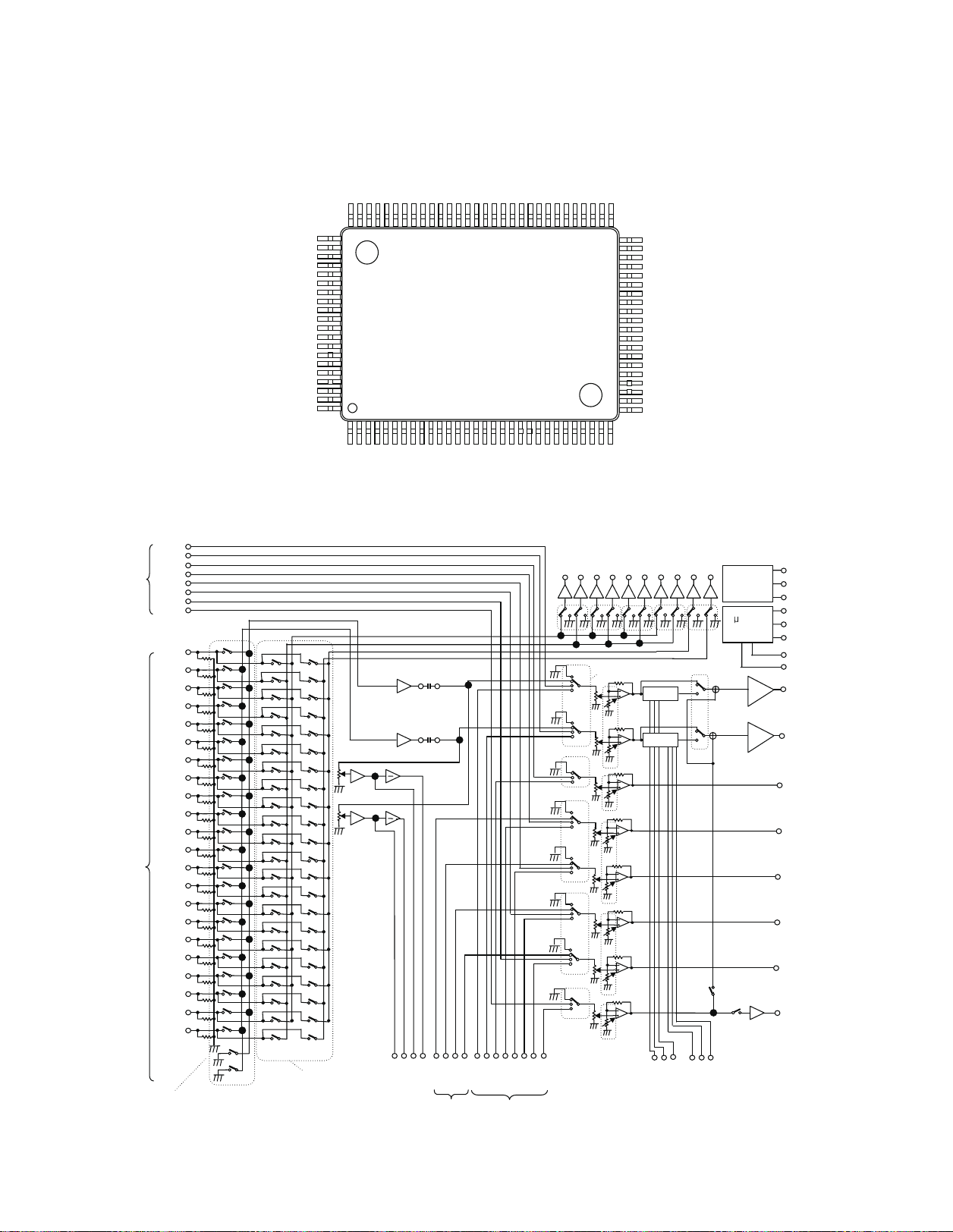

XC95288XL : U1

In-System Programming Controller

JTAG

Controller

I/O

Blocks

Function

Block 1

Macrocells

1 to 18

Macrocells

1 to 18

JTAG Port

3

54

I/O/GTS

I/O/GSR

I/O/GCK

I/O

I/O

I/O

I/O

4

1

I/O

I/O

I/O

I/O

3

1

Function

Block 2

54

18

18

Function

Block 3

Macrocells

1 to 18

Macrocells

1 to 18

54

Function

Block 16

54

18

18

Function

Block 4

Macrocells

1 to 18

54

18

Fast CONNECT II Switch Matrix

29

Page 30

SC16315 : IC701

Pin No. Pin Name Description

7D

IN

Data input pin. Input serial data at rising edge of shift clock, starting from the low

order bit.

6D

OUT

Data output pin. Output serial data at the falling edge of the shift clock, starting

from low order bit. This is N-ch open-drain output pin.

9 STB

Strobe pin. Initializes serial interface at the rising or falling edge of the SC16315.

It then waits for reception of a command. Data input after STB has fallen is

processed as a command. While command data is processed, current

processing is stopped, and the serial interface is initialized. While STB is high,

CLK is ignored.

8 CLK

Clock input pin. Reads serial data at the rising edge, and outputs data at the

falling edge.

5OSC

Oscillator pin. Determine the oscillation frequency by the resistor connecting this

pin and GND (V

SS

).

14 ~ 29

Seg1/KS1

to Seg16/KS16

High-voltage output (segment). Segment output pins (Dual function as key

source).

39~42Grid1 to Grid4 High-voltage output (grid). Grid output pins.

31~38

Seg17/Grid12

to Seg24/Grid5

High-voltage output (segment/grid). Segment or gri d driving.

1 ~4 LED1 to LED4LED output pin. CMOS output. +20mA max.

10 ~ 11 KEY1 to KEY2

Key data input. Data input to these pins is latched at the end of the display

cycle.

13, 43VDDLogic power pin. 5V 10%

12, 44VSSLogic ground. Connect this pin to system GND.

30 V

EE

Pull-down level. VDD-35V max.

44

1

Vss

LED 1

2

L

ED 2

3

L

ED 3

4

LED 4

SC16315

5

O

SC

6

DOUT

7

DIN

8

CLK

9

STB

1

0

K

EY 1

11

3

3

3

2

31

3

0

2

9

28

2

7

26

25

2

4

23

KEY 2

Seg19/Grid 10

S

eg18/Grid 11

S

eg17/Grid 12

V

E

E

S

eg16/KS16

Seg15/KS15

Seg14/KS14

Seg13/KS13

Seg12/KS12

S

eg11/KS11

Seg10/KS10

43

VDD42Grid141Grid240Grid339Grid438Seg24/Grid 537Seg23/Grid 636Seg22/Grid 735Seg21/Grid 8

34

12 13 14 15 16 17 18 19 20 21 22

Seg20/Grid 9

Vss

V

DD

Seg1/ KS1

Seg2/ KS2

Seg3/ KS3

Seg4/ KS4

Seg5/ KS5

Seg6/ KS6

Seg7/ KS7

Seg8/ KS8

Seg9/ KS9

30

Page 31

ABT2010 : U15

Picture

Controls

Input

Format/

Color Space

Decoder

Processor

Interface &

Control

Registers

Memory Controller

FIFO

V

ideo Timing

Generator

HD

Deinterlacer

Test Pattern

Generator

Dynamic

R

ange

Expansion

DDR2

Input Video

36

30

1

6 or 32

C

lock

Generation

30MHz

(optional) Video

output clock

3

0MHz

1

75MHz

Video Out Clk

I2C

ABT Serial

PReP

HD Scaler

S

ync Generator

T

ri-Sync

Generator

On Screen

Display

Gamma Look

Up Table/

3x3 Matrix

Audio

Delay

AudioInAudio

Out

Noise

Reduction

Detail

Enhancement

CUE/

Sharpness/

YC Delay

Border Gen.

Masking Gen.

Panorama

400MHz

Output Format/

Color Space

Converter

Pin

Mapping

Pin

Mapping

FIFO FIFO

Frame Rate

C

onversion

FIFO

Dynamic

Range

Compression

Scaler Bypass

Pin to Pin Bypass

12 12

12

10

12

10

1

0

10

10

10

12

12

10-bits on Y;

10-bits on C

12-bits on Y;

12-bits on C

Output Video

31

Page 32

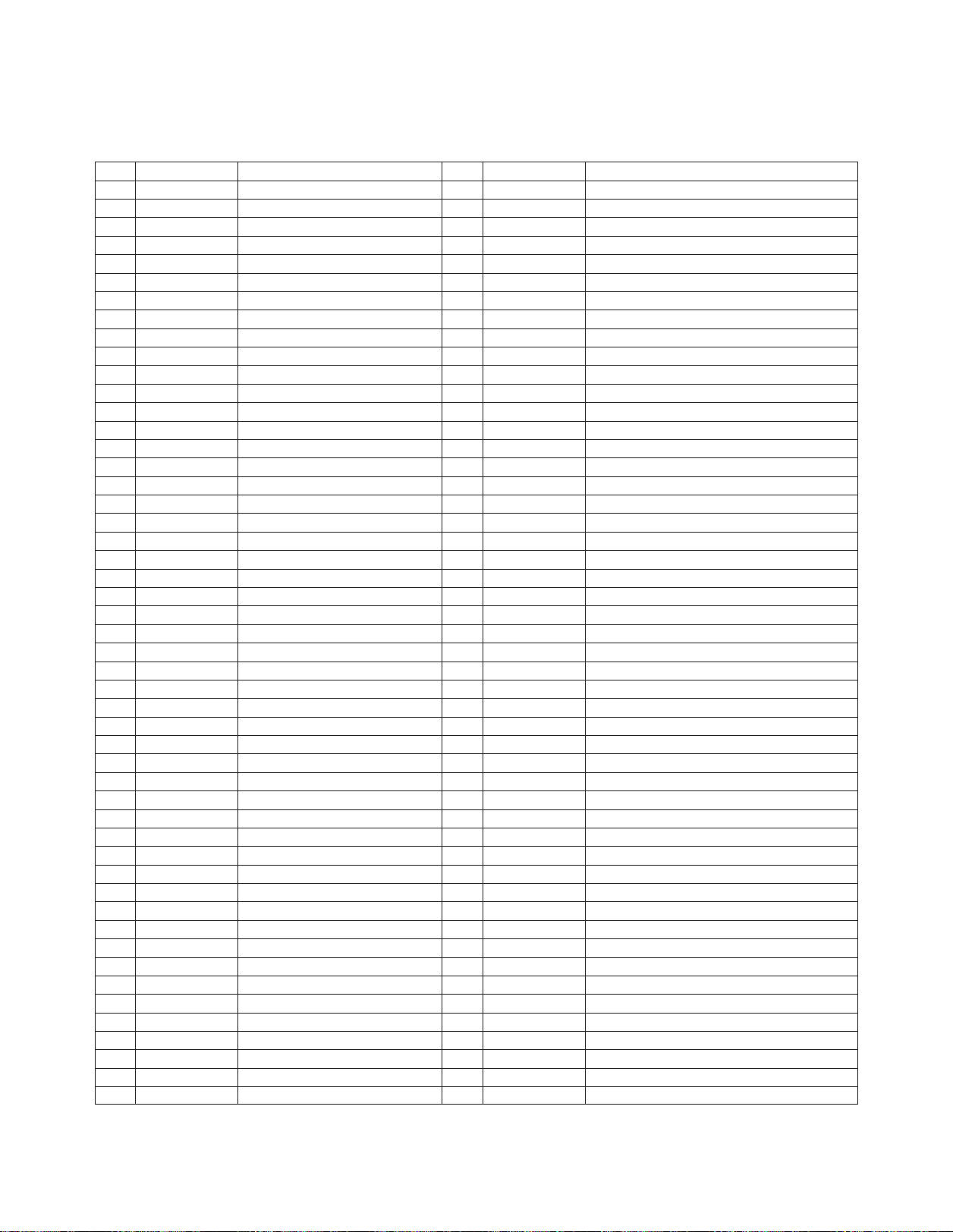

CS49700 : IC1005

Serial

Control 1

12 Ch, Audio In/

6 Ch, SACE In

Serial

Control 2

Parallel

Control

UART GPIO Debug

STC

TMR1

TMR2

PLL

Ext. Memory Controller

D

M

A

32 bit

DSP A

PXY

32 bit

DSP B

PXY

SPDIF SPDIF

16 Ch PCM

Audio Out

1

VIDEO

OUT

6dB

amp

Video switch

(4 input 1 output)

driver

control

2

A

3

B

4

VIN15GND6VIN27VCC8VIN39VIN4

LA7956 : IC200, IC201, IC203, IC205

32

Page 33

TROUBLESHOOTING

R

ef No.

Power On Failure A) AC-Cord check.

1. FLT does not light up. B) Power Trans (Main/ST-BY) check.

)103 ( F.kcehc noitcennocsid s'esuF )C.pu thgil ton seod DEL YB-TS .2

.noitcnujsid ro noitcennocsid s'rotcennoC )D

Change or close insertion of the connector. CN301,FPC401

)007(WS.hctiws yB-TS roirefnI )E

F) VFD Driver I.C & Resonator check. I.C701 SC16315

1. VFD Driver I.C VCC(+3.3)V check. I.C701 Pin No13

2. VFD Driver clock pulse check. I.C701 Pin No5

Fuse Disconnection. A) Inferior transformer.

) RS ,LS ,C ,RF ,LF (602Q)RT REWOP( .tuo RT evird PMA )B)nO rewoP(

C) AMP drive TR out. ( POWER TR ) Q205 ( FL, FR, C, SL, SR )

D) B+_B- voltage check.

.kcehc dehsup gnieb s'yeK )A.redrosiD yeK

B) Key signal input components inferior.

) 19,09( .oN niP 204C.I.kcehc TROP yeK )C

D) Ր-COM I.C inferior.

1. Ր-COM IC VCC +3.3V check.

I.C401 Pin No. ( 16,62,98,99 )

)V3.3_IP7111AIK( 003 C.I.tuo C.I rotalugeR )A.ces 3~2 ni ffO rewoP

.kcehc TUO/NI langiS .1.nO rewoP retfa

B) Drive transistor out. ( POWER TR ) Q205 ( FL, FR, C, SL, SR )

Q206( FL, FR, C, SL, SR )

C) Protection circuit check.

1. Output DC check.

2. Ր-COM I.C protection terminal check.

u-COM Pin No. ( 95 )

D) Connector's disconnection or disjunction CP (401)

E) SLEEP MODE cancellation.

) 115( Q.roirefni dna tuo s'rotsisnart etuM TNORF )A dnuoS pmuB

(During input-select switch's change.)

Ր-Com front mute control PORT check.

IC101 Pin No. ( 27 )

B) CENTER Mute transistor's out and inferior. Q ( 509 )

Ր-Com center mute control PORT check.

IC101 Pin No. ( 26 )

C) SURROUND Mute transistor's out and inferior. Q ( 510 )

Ր-Com center mute control PORT check.

IC101 Pin No. ( 24 )

D) SURR-BACK Mute transistor's out and inferior.

Q ( 507 )

Ր-Com surround mute control PORT check.

IC101 Pin No. ( 25 )

Cause and RemedySymptom

33

Page 34

R

ef

N

o.

1

0

4C

.

I.kc

e

hc

C

I

e

m

ul

o

V

)

A.

e

r

uli

a

F

l

o

r

t

n

oC

el

b

e

r

T

/

ss

a

B

1

.

Re

sist

e

r

/

Ca

p

a

cit

o

r

co

r

r

e

ct

i

o

n

f

ig

u

r

e

ch

e

ck.

(

B

a

ss)

I

.

C4

0

1

P

I

N

No

.

(

9

,

1

0

,

1

3

,

1

4

)

2

.

R

e

si

st

e

r

/

C

a

p

a

ci

t

o

r

c

o

rre

c

t

i

o

n

f

i

g

u

re

ch

e

ck

.

(T

re

b

l

e

)

I

.

C4

0

1

P

I

N

No

.

(

1

1

,

1

5

)

1

1

5

Q

,

0

1

5

Q

,

9

0

5

Q

,

7

0

5

Q

.

r

oi

r

e

f

ni

s'R

T

e

t

u

M

l

a

n

gi

S

)

A

.

d

a

eD

d

n

u

o

S

P

M

A

1

.

"L

E

F

T

"

Ch

a

n

n

e

l

d

e

a

d

.

B

)

Co

n

n

e

c

t

o

r

d

isco

n

n

e

ct

io

n

&

d

isju

n

ct

io

n

.

CP

(

4

0

1

)

2

.

"RI

G

HT

"

Ch

a

n

n

e

l

d

e

a

d

.

Ch

a

n

g

e

o

r

clo

se

in

se

r

t

io

n

o

f

t

h

e

c

o

n

n

e

ct

o

r

.

3

.

"CE

NT

E

R"

Ch

a

n

n

e

l

d

e

a

d

.

C)

S

p

e

a

ke

r

wir

e

's

d

isju

n

ct

io

n

.

4

.

"RE

A

R"

Ch

a

n

n

e

l

d

e

a

d

.

Clo

se

in

se

r

t

io

n

o

f

t

h

e

sp

e

a

ke

r

wir

e

.

)

1

0

4

(

.

oN

C

.

I

.kc

e

hc

C

I

e

m

ul

o

V

)D

1

.

I

.

C

vo

lt

a

g

e

c

h

e

ck

+

7

.

5

V

,

-

7

.

5

V

I

.

C

P

in

No

.

(

1

6

,

1

8

)

)

0

7

,

9

6

,

8

6

(

.

oN

N

I

P

C

.

I.kc

e

hc

a

t

a

d

l

o

r

t

n

oc

C

.

I

.

2

3

.

I

.

C

s

i

g

n

a

l

I

N/

O

UT

ch

e

ck

.

A

C-

3

/

DTS

Fa

ilu

re

. A

)

I

.

C

Re

g

u

la

t

o

r

ch

e

ck.

5

1

0

1C

.

I

+1

.

8

V

ER

OC

P

SD

)

e

d

oM

d

n

u

o

S

P

SD(

CO

DE

C

+

5

V

,

CO

DE

C

/

DS

P

I

/

O

+3

.

3

V

I

.

C

1

1

2

6

,

I

.

C1

0

1

6

8

0

0

1C

.

I

.kc

e

hc

R

ID

)

B

)

0

0

0

1

(

L

AT-

X.kc

e

h

c

C

S

O

.

1

2

.

B

I

CK

,

L

RCK

,

RDA

TA

C

h

e

ck.

I

.

C

P

in

No

.

(

1

5

)

(

1

6

)

(

1

4

)

3

.

Mico

m

I

n

t

e

rf

a

c

e

P

o

r

t

Ch

e

ck

.

I

.

C

P

in

No

.

(

2

1

,

2

2

,

3

1

)

)

5

0

0

1

(

.

oN

C

.

I

.kc

e

hC

P

SD

)C

)

2

2

(

.

oN

n

i

P

C

.

I.kc

e

hC

KCR

L

.

1

2

.

Mico

m

I

n

t

e

rf

a

c

e

P

o

r

t

Ch

e

ck

.

I

.

C

P

in

No

.

(9

3

,

9

5

,

9

6

,

9

7

,

9

9

,

1

0

0

,

1

0

2

)

)

5

3

1

,

4

3

1

,

2

3

1

,

1

3

1

(

.

oN

ni

P

C

.

I

.

kc

e

hC

4

,

3

,

2

,

1

AT

AD

S

.

3

)

8

0

0

1

(

.

oN

C

.

I

.kc

e

h

C

A

/D

)D

)

9

1

,

8

1

,

7

1

(

.

oN

ni

P

C

.

I

.kc

e

hc

AT

AD

S

/

KC

B

/

KCR

L

.

1

)

5

3

,

7

3

,

9

3

,

1

4

,

3

4

,

5

4

,

7

4

,

9

4

(

.

oN

n

i

P

C

.

I

.k

c

e

hc

t

u

o

l

a

n

g

i

S

.

2

Vi

deo Outpu

t Dead. A)

Vi

deo Regulator

v

ol

tage chec

k.

)5

02

,3

02

,1

02,0

02

(

.oN C.

I+12V

.

kceh

c

e

ga

tlov CD

.

1

) 56,36,95

,

85

( .oN

niP C

.I.

kceh

c

atad lo

rtno

c

mociM )B

C)

Vid

eo Mu

te(MONTO

R,

V

1

O

UT) po

r

t

c

h

ec

k.(IC10

1

)

I.

C Pin

No

.

(

56,57,60,61)

Remote

Contr

ol

l

er

Fai

l

ur

e

. A) Batt

ery

c

heck

.

B) RMC I.

C & Resonator

inferi

o

r

.

1.

Ր

-COM I.C B+( 3.3 )V check.

)7 ( .oN niP C.I / )204( .ON C.I.kcehc atad NOCOME

R .2

C

ause

and

R

em

edy

S

ym

pt

om

34

Page 35

B

)

F

RO

NT

-

E

ND

in

f

e

r

io

r

.

C)

F

M

DE

T

CO

I

L

in

f

e

r

io

r

.

D)

P

L

L

&

M

P

X

I

C

ch

e

ck.

1

.

P

L

L

&

M

P

X

I

.

C

B

+

(

5

)

V

,

B

+

(

3

.

3

)

V

ch

e

ck

. I

.

C

NO

.

(

1

)

/

I

.

C

P

in

No

.

(

8

,

2

1

)

2

.

P

L

L

co

n

t

r

o

l

d

a

t

a

ch

e

ck

.

(

Da

t

a

/

CE

/

Clo

ck

)

E

)

T

UNE

R

B

+

vo

l

t

a

g

e

in

f

e

r

io

r

.

F

)

Ր

-

CO

M

I

.

C

&

Re

so

n

a

t

o

r

in

f

e

r

io

r

.

I

.

C

No

.

(

4

0

2

)

1

.

Ր

-

CO

M

I

.

C

B

+

(

3

.

3

)

V

ch

e

ck

.

)

8

7

,

7

7

,

2

7

,

1

7

,

0

7

(

.

oN

ni

P

C

.

I

.kc

e

hc

a

t

a

d

l

o

r

t

n

oc

m

oci

M

.

2

.kc

e

hc

C

I

X

PM

&

L

L

P

)

A

.

er

ul

i

aF

M

A

1

.

P

L

L

&

MP

X

I

.

C

B

+(

5

)V

,

B

+(

3

.

3

)V

ch

e

ck. I

.

C

NO

.

(1

)

/

I

.

C

P

in

No

.

(

8

,

2

1

)

2

.

P

L

L

co

n

t

ro

l

d

a

t

a

ch

e

ck

(Da

t

a

/

CE

/

Clo

c

k)

B

)

TUNE

R

B

+

vo

lt

a

g

e

i

n

f

e

ri

o

r.

C)

A

M

O

S

C

CO

I

L

in

f

e

rio

r

.

D)

Ր

-CO

M

I

.

C

&

Re

so

n

a

t

o

r

in

f

e

rio

r.

I

.

C

No

.

(4

0

2

)

1

.

Ր

-CO

M

I

.

C

B

+(

3

.

3

)V

ch

e

c

k.

)

8

7

,

7

7

,

2

7

,

1

7

,

0

7

(

.

oN

ni

P

C

.

I

.k

c

e

hc

a

t

a

d

l

or

t

n

oc

m

ociM

.

2

S

t

e

re

o

E

f

f

e

ct

Fa

ilu

re

. A

)

FM

DE

T

CO

I

L

I

n

f

e

r

io

r.

S

t

e

re

o

d

o

e

s

n

o

t

lig

h

t

u

p

.

B

)

P

L

L

&

MP

X

I

C

ch

e

c

k.

1

.

P

L

L

&

MP

X

I

.

C

B

+(

5

)V

,

B

+(

3

.

3

)V

ch

e

ck.

2

.

MP

X

co

n

t

ro

l

d

a

t

a

ch

e

ck

.

C)

Ր

-CO