QUICK LOGIC QL24x32B-0PF144C, QL24x32B-0PF144I, QL24x32B-0PF144M, QL24x32B-0PQ208C, QL24x32B-0PQ208I Datasheet

...

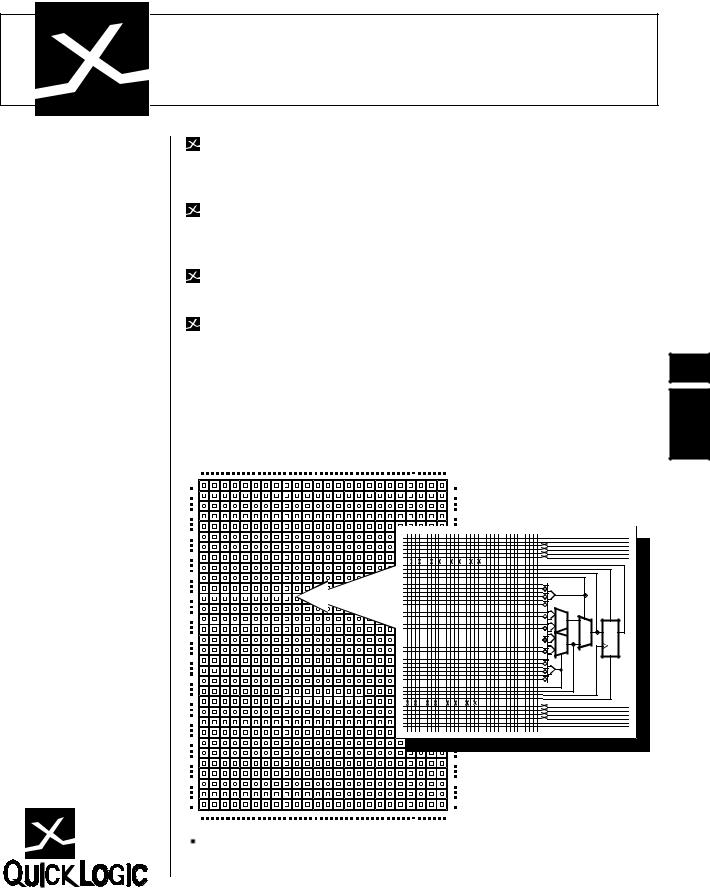

pASIC HIGHLIGHTS

…8,000 usable ASIC gates,

180 I/O pins

QL24x32B

Block Diagram

768 Logic Cells

QL24x32B

pASIC® 1 Family

Very-High-Speed CMOS FPGA

Very High Speed – ViaLink ® metal-to-metal programmable–via antifuse technology, allows counter speeds over 150 MHz and logic cell delays of under 2 ns.

High Usable Density – An 24-by-32 array of 768 logic cells provides 8,000 usable ASIC gates (14,000 PLD gates) in 144-pin TQFP, 208-pin PQFP and 208-pin CQFP packages.

PCI-Output Drive – Fully PCI 2.1 compliant input/output capability. (including drive current)

Low-Cost, Easy-to-Use Design Tools – Designs entered and |

|

|

simulated using QuickLogic's new QuickWorks® |

development |

|

environment, or with third-party CAE tools including Viewlogic, |

4 |

|

Synopsys, Mentor, Cadence and Veribest. Fast, fully automatic place |

|

|

and route on PC and workstation platforms using |

QuickLogic |

1pASIC |

software. |

|

|

|

|

|

= Up to 172 prog. I/O cells, 6 Input high-drive cells, 2 Input/Clk (high-drive) cells

4-31

QL24x32B

PRODUCT SUMMARY

FEATURES

The QL24x32B is a member of the pASIC 1 Family of very-high-speed CMOS user-programmable ASIC devices. The 768 logic cell fieldprogrammable gate array (FPGA) offers 8,000 usable ASIC gates (equivalent to 14,000 PLD gates) of high-performance general-purpose logic in 144-pin TQFP and 208-pin PQFP and CQFP packages.

Low-impedance, metal-to-metal, ViaLink interconnect technology provides nonvolatile custom logic capable of operating above 150 MHz. Logic cell delays under 2 ns, combined with input delays of under 1.5 ns and output delays under 3 ns, permit high-density programmable devices to be used with today’s fastest microprocessors and DSPs.

Designs can be entered using QuickLogic’s Quick Works Toolkit or most populart third-party CAE tools. QuickWorks combines Verilog/VHDL design entry and simulation tools with device-specific place & route and programming software. Ample on-chip routing channels allow fast, fully automatic place and route of designs using up to 100% of the logic and I/O cells, while maintaining fixed pin-outs

Total of 180 I/O pins

–172 Bidirectional Input/Output pins

–6 Dedicated Input/High-Drive pins

–2 Clock/Dedicated input pins with fanout-independent, low-skew clock networks

–PCI 2.1 Compliant I/Os

Input + logic cell + output delays under 6 ns

Chip-to-chip operating frequencies up to 110 MHz

Internal state machine frequencies up to 150 MHz

Clock skew < 0.5 ns

Input hysteresis provides high noise immunity

Built-in scan path permits 100% factory testing of logic and I/O cells and functional testing with Automatic Test Vector Generation (ATVG) software after programming

144-pin TQFP compatible with QL16x24B

0.65µ CMOS process with ViaLink programming technology

4-32

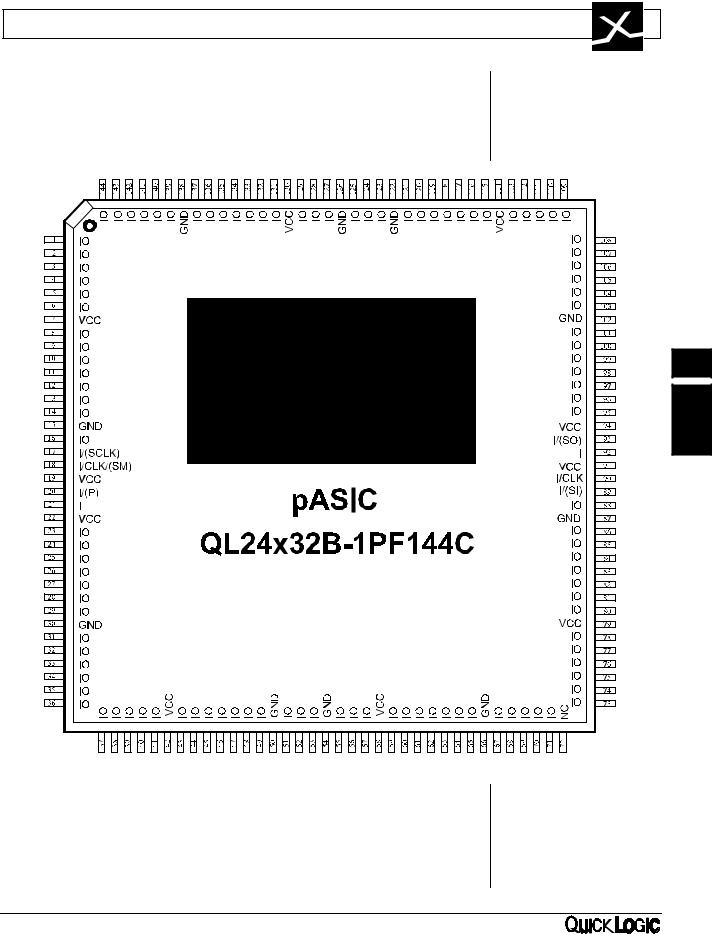

QL24x32B

Pinout

Diagram

144-pin TQFP

4 |

1 pASIC |

4-33

Loading...

Loading...