NEC UPA572T Datasheet

DATA SHEET

5 4

1 2 3

1.

2.

3.

4.

5.

Marking: DB

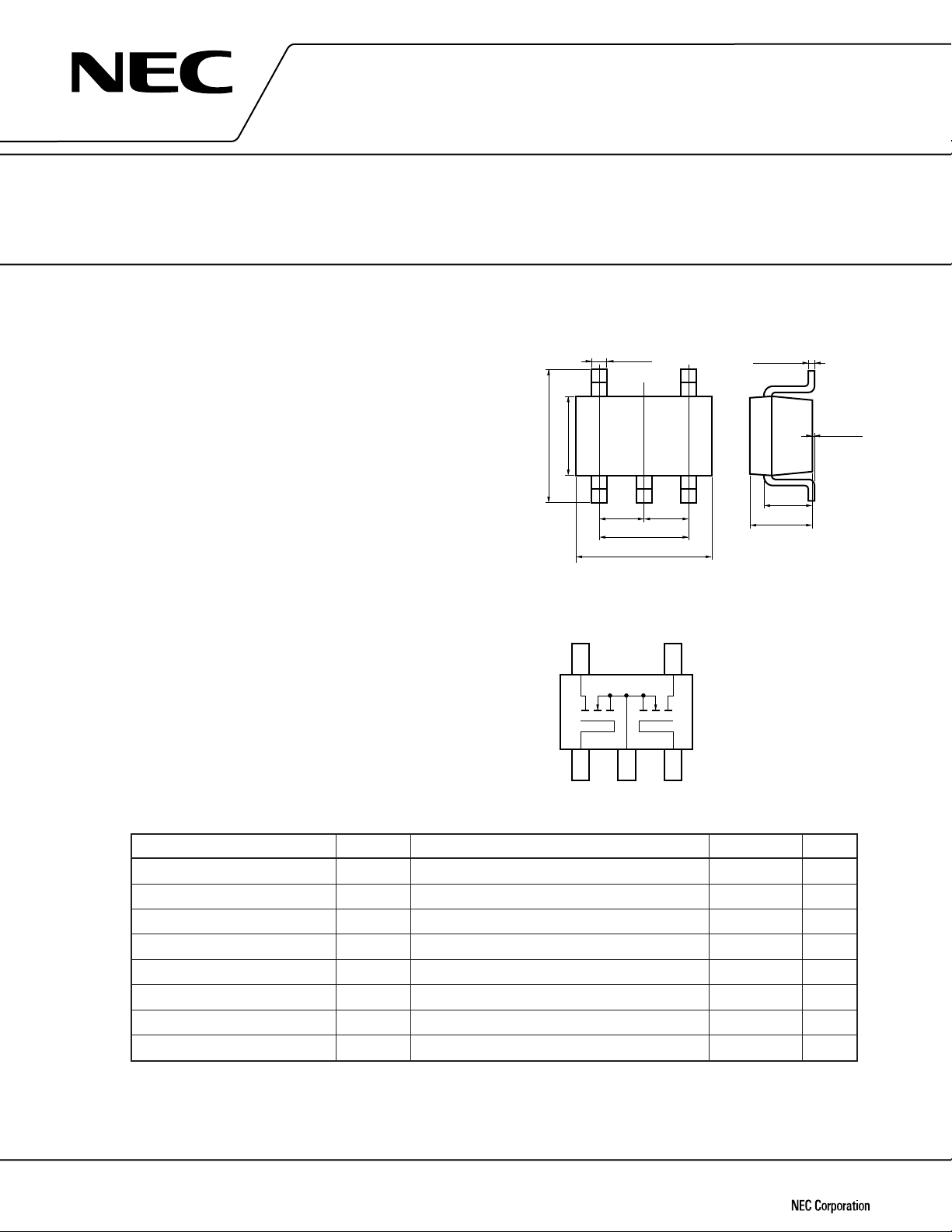

PIN CONNECTION

(G1)

(common)

(G2)

(D2)

(D1)

Gate 1

Source

Gate 2

Drain 2

Drain 1

MOS FIELD EFFECT TRANSISTOR

µ

N-CHANNEL MOS FET (5-PIN 2 CIRCUITS)

FOR SWITCHING

PA572T

The µPA572T is a super-mini-mold device provided with

two MOS FET circuits. It achieves high-density mounting

and saves mounting costs.

FEATURES

• Two source common MOS FET circuits in package the

same size as SC-70

• Directly driven by 3 V power supply

• Automatic mounting supported

PACKAGE DIMENSIONS (in millimeters)

2.1 ±0.1

1.25 ±0.1

+0.1

0.2

–0

0.65 0.65

1.3

2.0 ±0.2

0.15

0.9 ±0.1

+0.1

–0.05

0.7

0 to 0.1

EQUIVALENT CIRCUIT

Document No. G11244EJ1V0DS00 (1st edition)

Date Published June 1996 P

Printed in Japan

ABSOLUTE MAXIMUM RATINGS (TA = 25 ˚C)

PARAMETER SYMBOL TEST CONDITIONS RATINGS UNIT

Drain to Source Voltage VDSS V GS = 0 30 V

Gate to Source Voltage VGSS VDS = 0 ±7V

Drain Current (DC) ID(DC) ±100 mA

Drain Current (pulse) ID(pulse) PW ≤ 10 ms, Duty Cycle ≤ 50 % ±200 mA

Total Power Dissipation PT 200 (Total) mW

Channel Temperature Tch 150 ˚C

Operating Temperature Topt –55 to +80 ˚C

Storage Temperature Tstg –55 to +150 ˚C

©

1996

µ

PA572T

ELECTRICAL CHARACTERISTICS (TA = 25 ˚C)

PARAMETER SYMBOL TEST CONDITIONS MIN. TYP. MAX. UNIT

Drain Cut-off Current IDSS VDS = 30 V, VGS = 0 1.0

Gate Leakage Current IGSS VGS = ±5 V, VDS = 0 ±3.0

Gate Cut-off Voltage VGS(off) VDS = 3 V, ID = 10 µA 0.8 1.0 1.5 V

Forward Transfer Admittance |yfs|VDS = 3 V, ID = 10 mA 20 50 mS

Drain to Source On-State Resistance

Drain to Source On-State Resistance

RDS(on)1 VGS = 2.5 V, ID = 1 mA 7 13 Ω

RDS(on)2 VGS = 4.0 V, ID = 10 mA 5 8 Ω

Input Capacitance Ciss VDS = 5.0 V, VGS = 0, f = 1 MHz 16 pF

Output Capacitance Coss 14 pF

Reverse Transfer Capacitance Crss 2pF

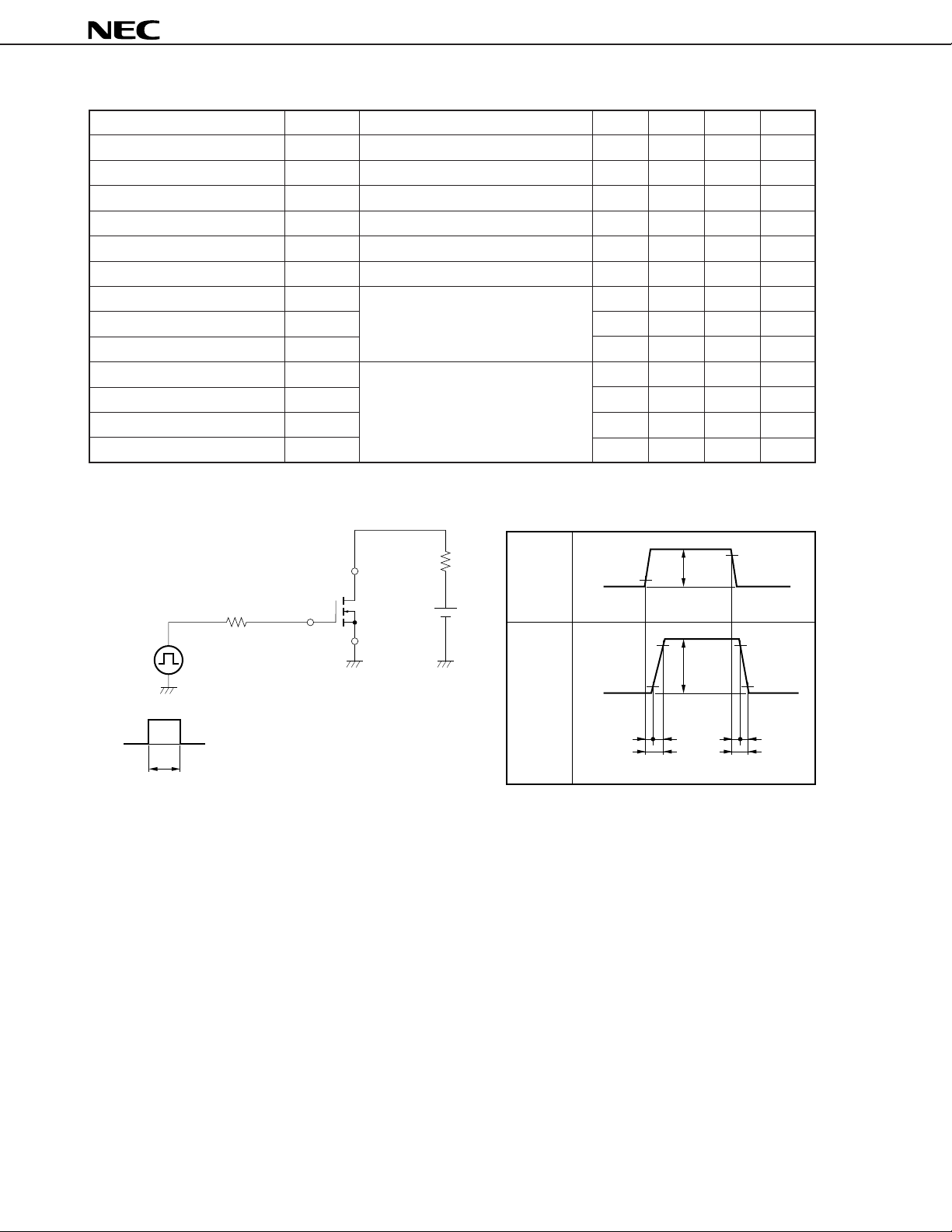

Turn-On Delay Time td(on) VDD = 5 V, ID = 10 mA, VGS(on) = 5 V, 15 ns

Rise Time tr

RG = 10 Ω, RL = 500 Ω

20 ns

Turn-Off Delay Time td(off) 100 ns

Fall Time tf 100 ns

µ

A

µ

A

SWITCHING TIME MEASUREMENT CIRCUIT AND CONDITIONS (RESISTANCE LOADED)

V

PG.

GS

V

0

τ

τ = 1 s

µ

Duty Cycle ≤ 1 %

GS

R

DUT

L

V

G

R

Gate

voltage

waveform

DD

Drain

current

10 %

0

I

D

10 % 10 %

0

90 %

V

I

D

waveform

t

d(on)

t

r

t

t

on

GS(on)

d(off)

t

off

90 %

90 %

t

r

2

Loading...

Loading...