NEC UPA1523BH Datasheet

DATA SHEET

COMPOUND FIELD EFFECT POWER TRANSISTOR

P-CHANNEL POWER MOS FET ARRAY

SWITCHING

INDUSTRIAL USE

DESCRIPTION

The µPA1523B is P-channel Power MOS FET Array that built

in 4 circuits designed for solenoid, motor and lamp driver.

µ

PA1523B

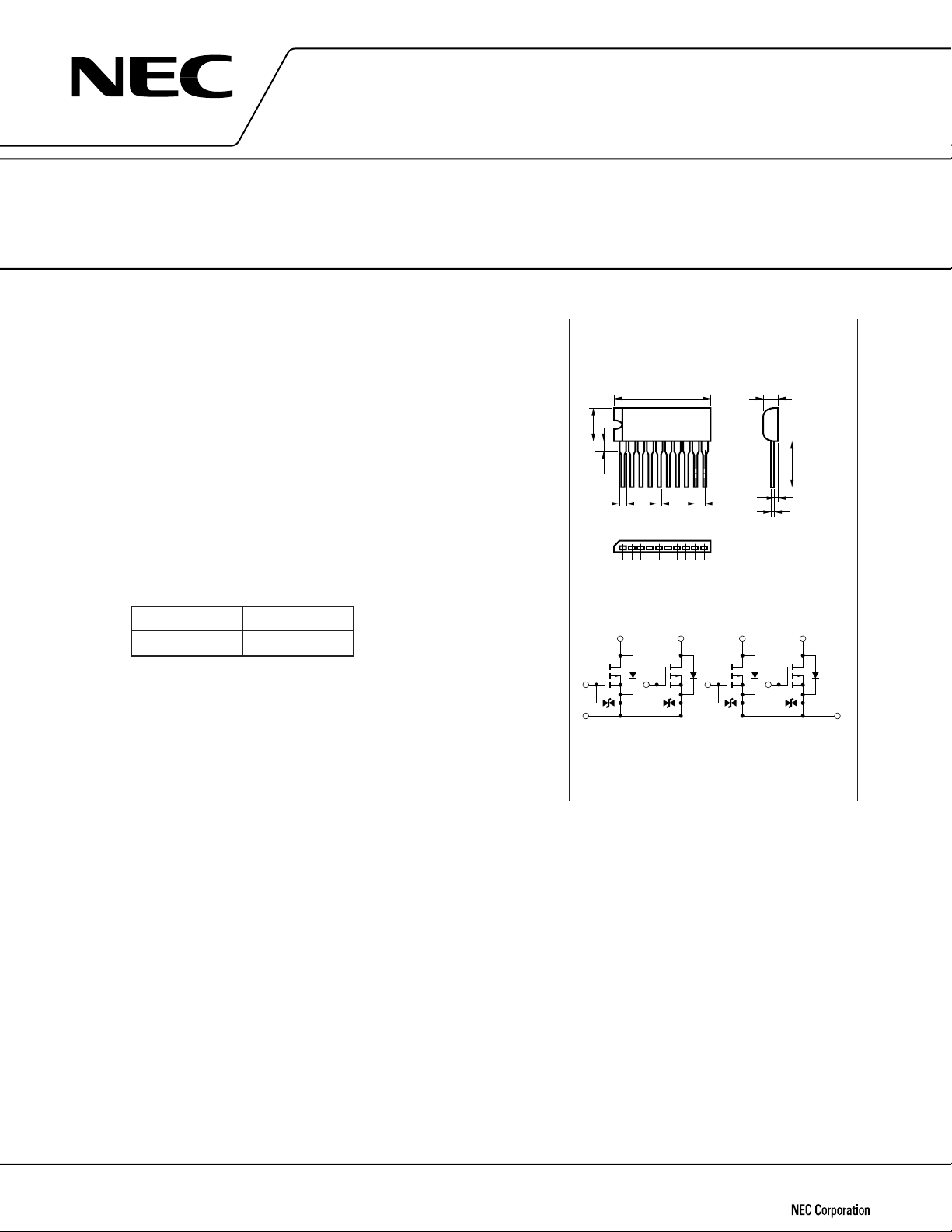

PACKAGE DIMENSIONS

in millimeters

FEATURES

• Full Mold Package with 4 Circuits

• –4 V driving is possible

• Low On-state Resistance

DS(on)1 = 0.8 Ω MAX. (@VGS = –10 V, ID = –1 A)

R

DS(on)2 = 1.3 Ω MAX. (@VGS = –4 V, ID = –1 A)

R

• Low Input Capacitance Ciss = 190 pF TYP.

ORDERING INFORMATION

Type Number Package

µ

PA1523BH 10 Pin SIP

ABSOLUTE MAXIMUM RATINGS (TA = 25 ˚C)

Drain to Source Voltage (VGS = 0)

Gate to Source Voltage (VDS = 0)

Drain Current (DC) I

Drain Current (pulse) ID(pulse) *1 8.0 A/unit

Total Power Dissipation PT1 *2 28 W

Total Power Dissipation P

Channel Temperature TCH 150 ˚C

Storage Temperature Tstg –55 to + 150 ˚C

Single Avalanche Current I

Single Avalanche Energy EAS *4 0.4 mJ

VDSS –60 V

VGSS(AC) 20 V

D(DC) 2.0 A/unit

T2 *3 3.5 W

AS *4 –2.0 A

±

±

±

26.8 MAX.

10

2.5

1.4 0.6 ± 0.1

12345678910

2.54

CONNECTION DIAGRAM

3

2

1

5

4

6

ELECTRODE CONNECTION

2, 4, 6, 8

3, 5, 7, 9

1, 10

4.0

7

8

: Gate

: Drain

: Source

10 MIN.

1.4

0.5 ± 0.1

9

10

*1 PW ≤ 10

*3 4 Circuits, TA = 25 ˚C *4 Starting TCH = 25 ˚C, VDD = –30 V, VGS = –20 V → 0, RG = 25 Ω,

Document No. G11331EJ1V0DS00

Date Published May 1996 P

Printed in Japan

µ

In case high voltage over V

s, Duty Cycle ≤ 1% *2 4 Circuits, T C = 25 ˚C

L = 100 µH

Build-in Gate Diodes are for protection from static electricity in handing.

GSS is applied, please append gate protection circuits.

The information in this document is subject to change without notice.

©

1996

µ

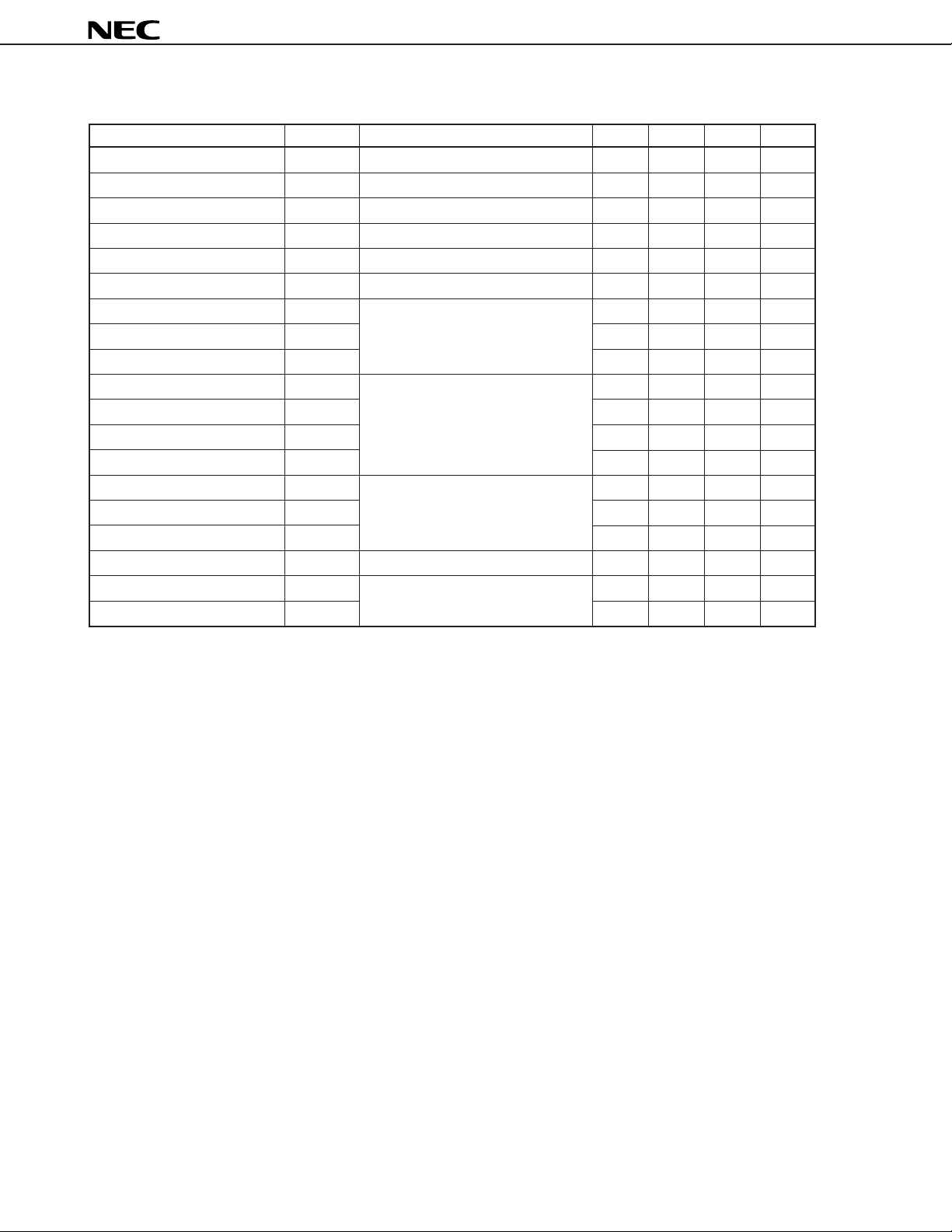

ELECTRICAL CHARACTERISTICS (TA = 25 ˚C)

CHARACTERISTIC SYMBOL TEST CONDITIONS MIN. TYP. MAX. UNIT

Drain Leakage Current IDSS VDS = –60 V, VGS = 0 –10

Gate Leakage Current IGSS VGS = 20 V, VDS = 0 10

Gate Cutoff Voltage VGS(off) VDS = –10 V, ID = –1.0 mA –1.0 –2.0 V

Forward Transfer Admittance | Yfs |VDS = –10 V, ID = –1.0 A 0.8 S

Drain to Source ON-Resistance RDS(on)1 VGS = –10 V, ID = –1.0 A 0.5 0.8 Ω

Drain to Source ON-Resistance RDS(on)2 VGS = –4.0 V, ID = –1.0 A 0.8 1.3 Ω

Input Capacitance Ciss VDS = –10 V, VGS = 0, f = 1.0 MHz 190 pF

Output Capacitance Coss 115 pF

Reverse Transfer Capacitance Crss 43 pF

Turn-on Delay Time td(on) ID = –1.0 A, VGS(on) = –10 V, 8 ns

Rise Time tr VDD = –30 V, RL = 30 Ω 53 ns

Turn-off Delay Time td(off) 400 ns

Fall Time tf 230 ns

Total Gate Charge QG VGS = –10 V, ID = –2.0 A, VDD = –48 V 10 nC

Gate to Source Charge QGS 1.1 nC

Gate to Drain Charge QGD 3.5 nC

Body Diode Forward Voltage VF(S-D) IF = 2.0 A, VGS = 0 1.0 V

Reverse Recovery Time trr IF = 2.0 A, VGS = 0, di/dt = 50 A/µs 180 ns

Reverse Recovery Charge Qrr 250 nC

±

.

.

±

PA1523B

µ

A

µ

A

2

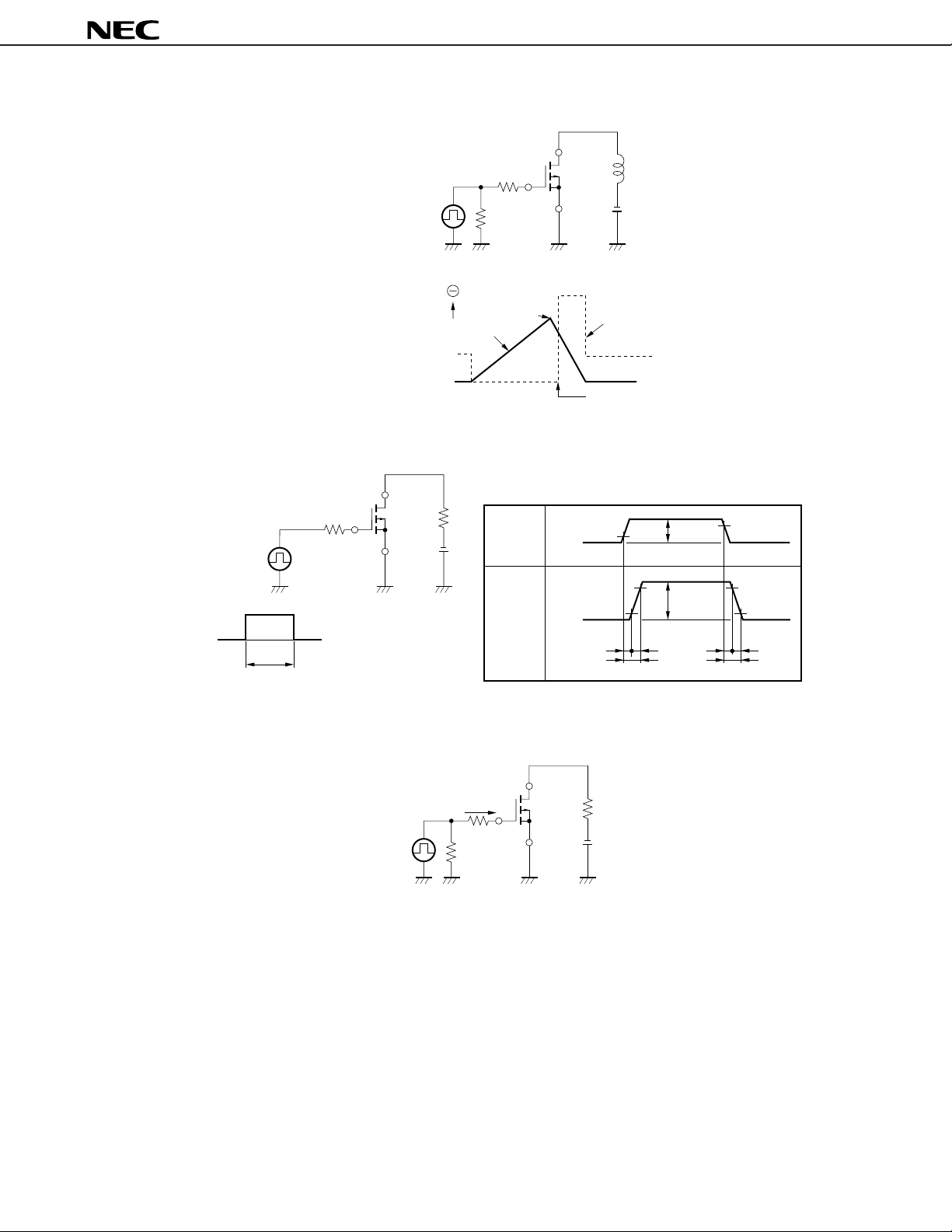

Test Circuit 1 Avalanche Capability

R

G

= 25 Ω

D.U.T.

µ

PA1523B

L

Test Circuit 2 Switching Time

R

PG.

V

GS

0

t = 1 s

µ

Duty cycle ≤ 1 %

RG = 10 Ω

t

V

GS

= –20 V → 0

D.U.T.

G

PG.

50 Ω

BV

DSS

I

AS

I

D

V

DD

R

L

VGS

Wave

V

Form

DD

I

D

Wave

V

GS

0

(—)

I

D

0

Form

V

V

DS

Starting T

10 %

10 %

t

d(on)

DD

t

on

CH

90 %

V

GS(on)

90 %

90 %

I

D

t

r

t

d(off)

10 %

t

f

t

off

Test Circuit 3 Gate Charge

PG.

I

G

= 2 mA

50 Ω

D.U.T.

L

R

V

DD

3

Loading...

Loading...