查询UPD45128163G5-A10供应商

DATA SHEET

MOS INTEGRATED CIRCUIT

PD45128441, 45128841, 45128163

µµµµ

128M-bit Synchronous DRAM

4-bank, LVTTL

Description

The µPD45128441, 45128841, 45128163 are high-speed 134,217,728-bit synchronous dynamic random-access

memories, organized as 8,388,608 × 4 × 4, 4,194,304 × 8 × 4, 2,097,152 × 16 × 4 (word × bit × bank), respectively.

The synchronous DRAMs achieved high-speed data transfer using the pipeline architecture.

All inputs and outputs are synchronized with the positive edge of the clock.

The synchronous DRAMs are compatible with Low Voltage TTL (LVTTL).

These products are packaged in 54-pin TSOP (II).

Features

Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge

•

Pulsed interface

•

Possible to assert random column address in every cycle

•

Quad internal banks controlled by BA0(A13) and BA1(A12)

•

Byte control (×16) by LDQM and UDQM

•

Programmable Wrap sequence (Sequential / Interleave)

•

Programmable burst length (1, 2, 4, 8 and full page)

•

Programmable /CAS latency (2 and 3)

•

Automatic precharge and controlled precharge

•

CBR (Auto) refresh and self refresh

•

4, ×8, ×16 organization

• ×

Single 3.3 V ± 0.3 V power supply

•

LVTTL compatible inputs and outputs

•

4,096 refresh cycles / 64 ms

•

Burst termination by Burst stop command and Precharge command

•

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. M12650EJBV0DS00 (11th edition)

Date Published April 2000 NS CP (K)

Printed in Japan

The mark

••••

shows major revised points.

©

1997

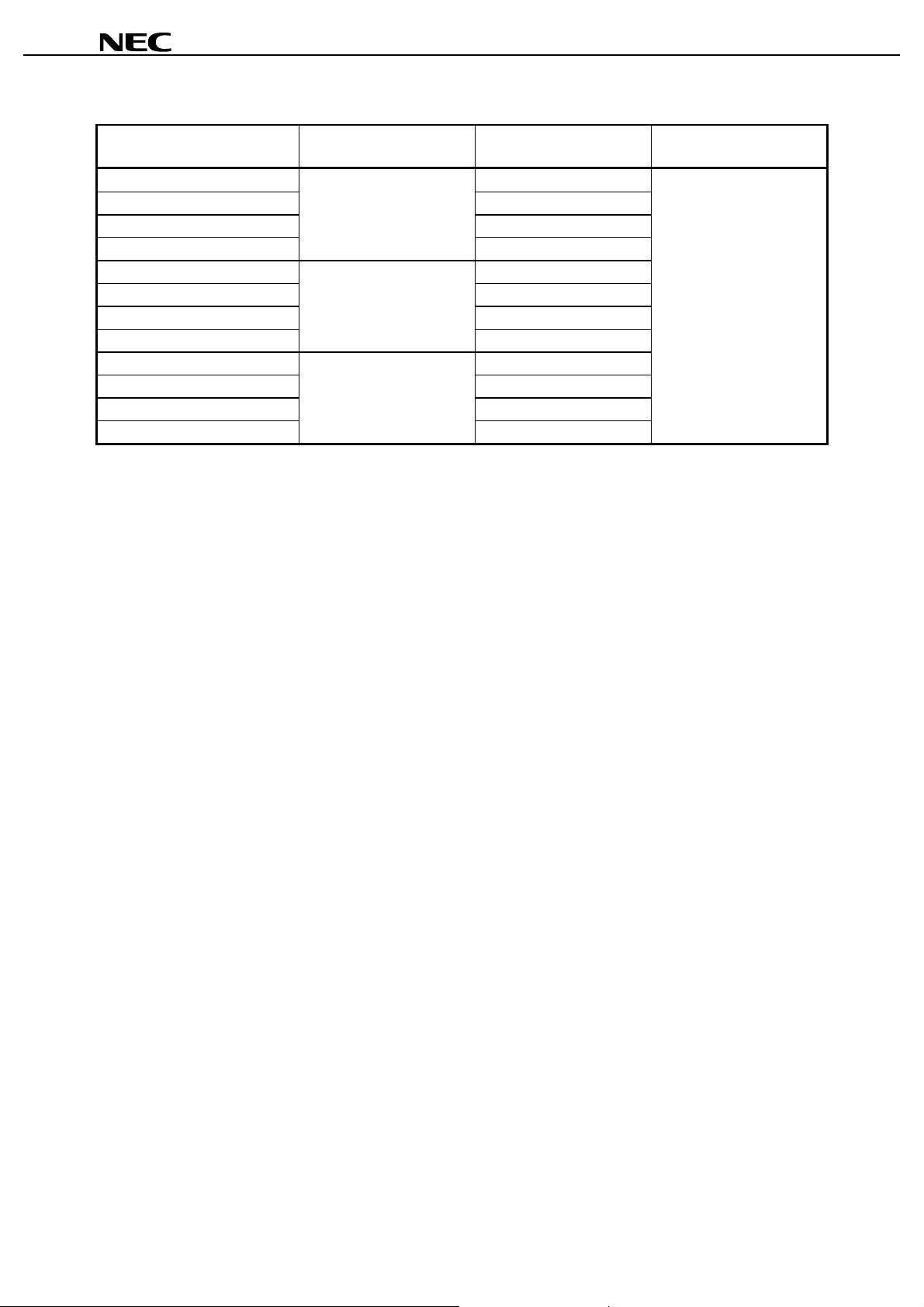

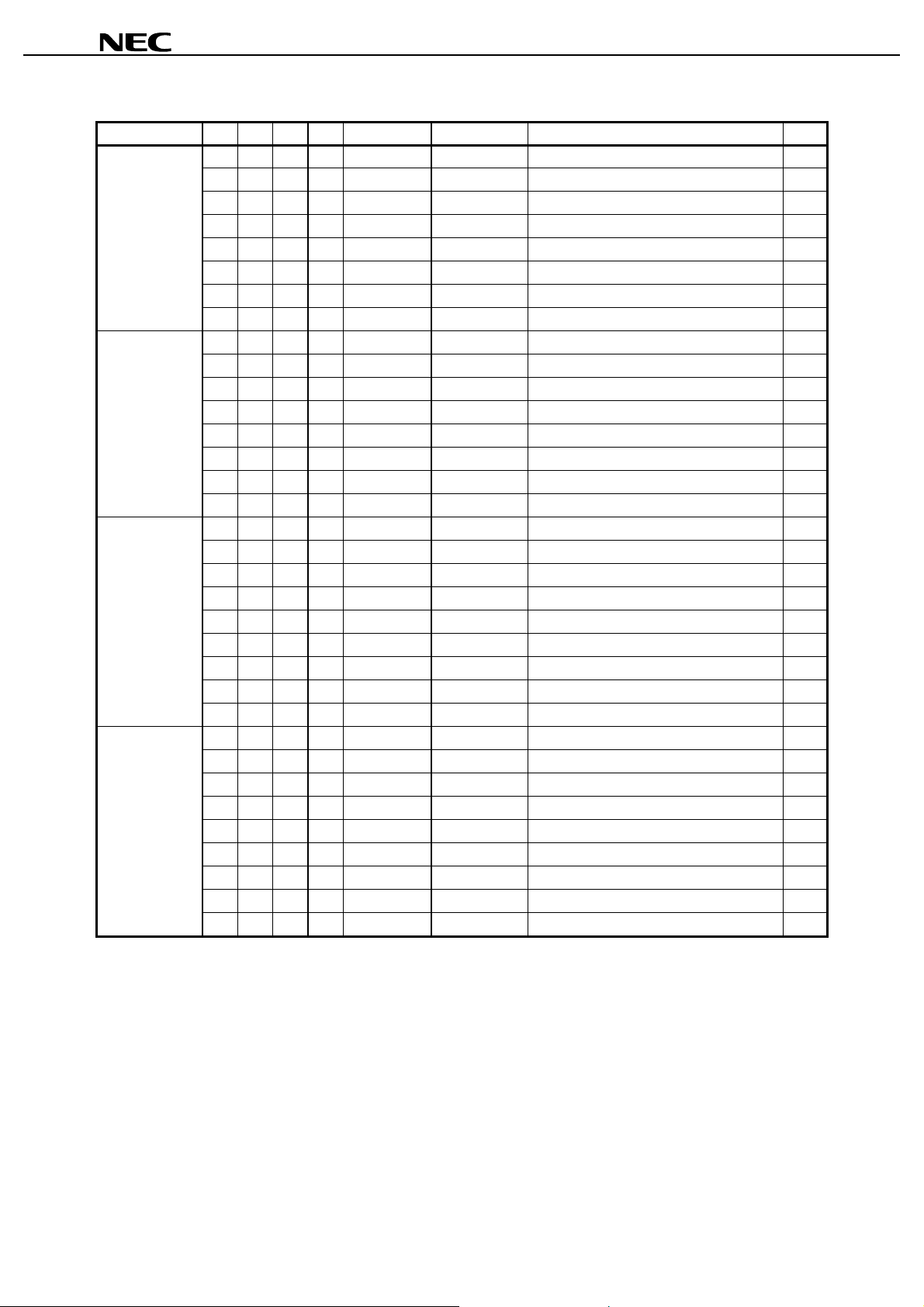

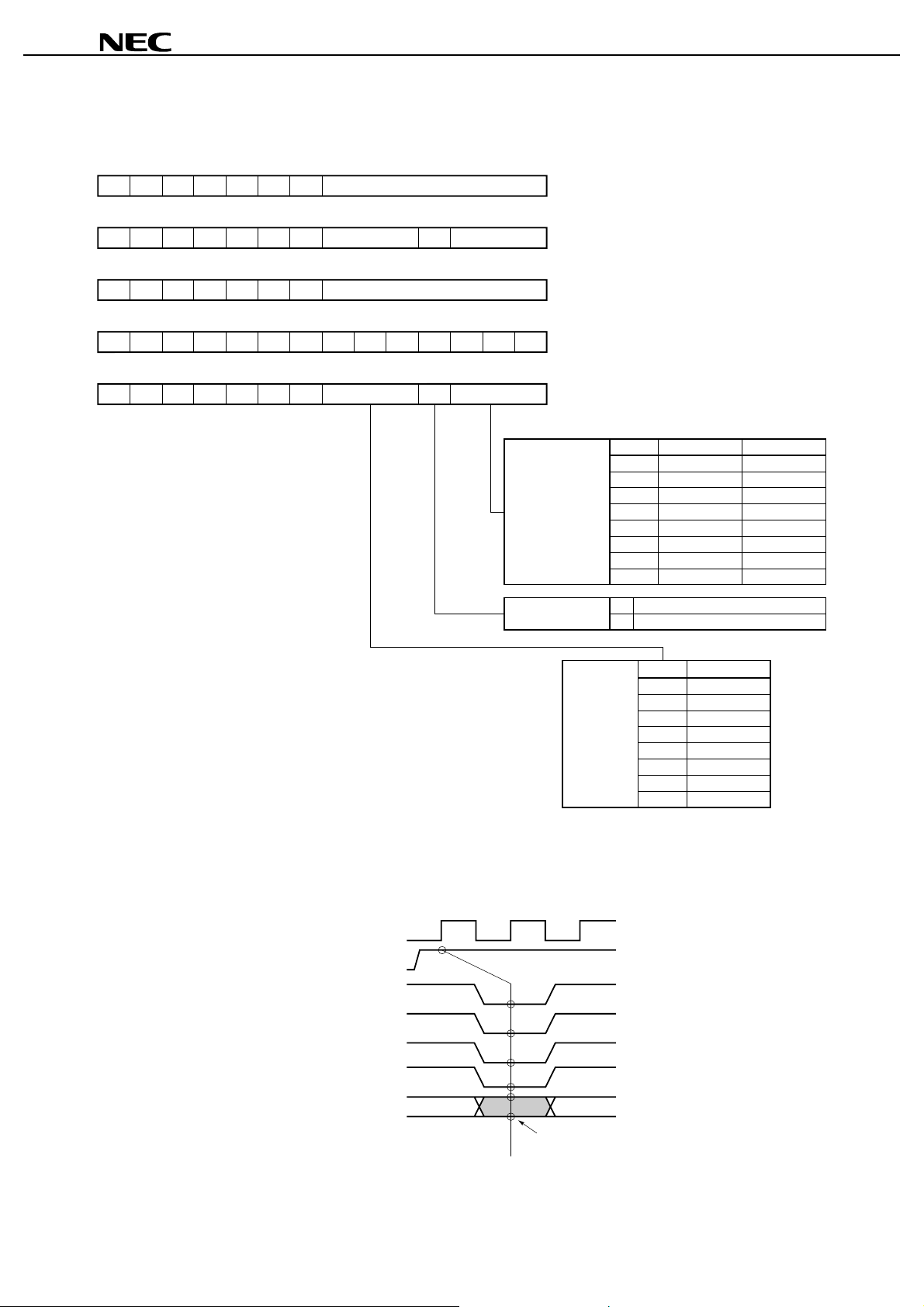

Ordering Information

µµµµ

PD45128441, 45128841, 45128163

Part number

PD45128441G5-A75-9JF 8M × 4 × 4 133 54-pin Plastic TSOP (II )

µ

PD45128441G5-A80-9JF 125 (10.16mm (400))

µ

PD45128441G5-A10-9JF 100

µ

PD45128441G5-A10B-9JF 100

µ

PD45128841G5-A75-9JF 4M × 8 × 4 133

µ

PD45128841G5-A80-9JF 125

µ

PD45128841G5-A10-9JF 100

µ

PD45128841G5-A10B-9JF 100

µ

PD45128163G5-A75-9JF 2M × 16 × 4 133

µ

PD45128163G5-A80-9JF 125

µ

PD45128163G5-A10-9JF 100

µ

PD45128163G5-A10B-9JF 100

µ

Organization

(word × bit × bank)

Clock frequency

MHz (MAX.)

Package

2

Data Sheet M12650EJBV0DS00

Part Number

[ x4, x8 ]

µ

NEC Memory

Synchronous DRAM

Memory density

µµµµ

PD45128441, 45128841, 45128163

PD45128841G5 - A75

128 : 128M bits

Organization

Number of banks

4 : 4 banks

Interface

1 : LVTTL

[ x16 ]

4 : x4

8 : x8

163

Minimum cycle time

75 : 7.5 ns (133 MHz)

80 : 8 ns (125 MHz)

10 : 10 ns (100 MHz)

10B: 10 ns (100 MHz)

Low voltage

A : 3.3 V

Package

G5 : TSOP (II)

±

0.3 V

Organization

16 : x16

Number of banks

and Interface

3 : 4 banks, LVTTL

Data Sheet M12650EJBV0DS00

3

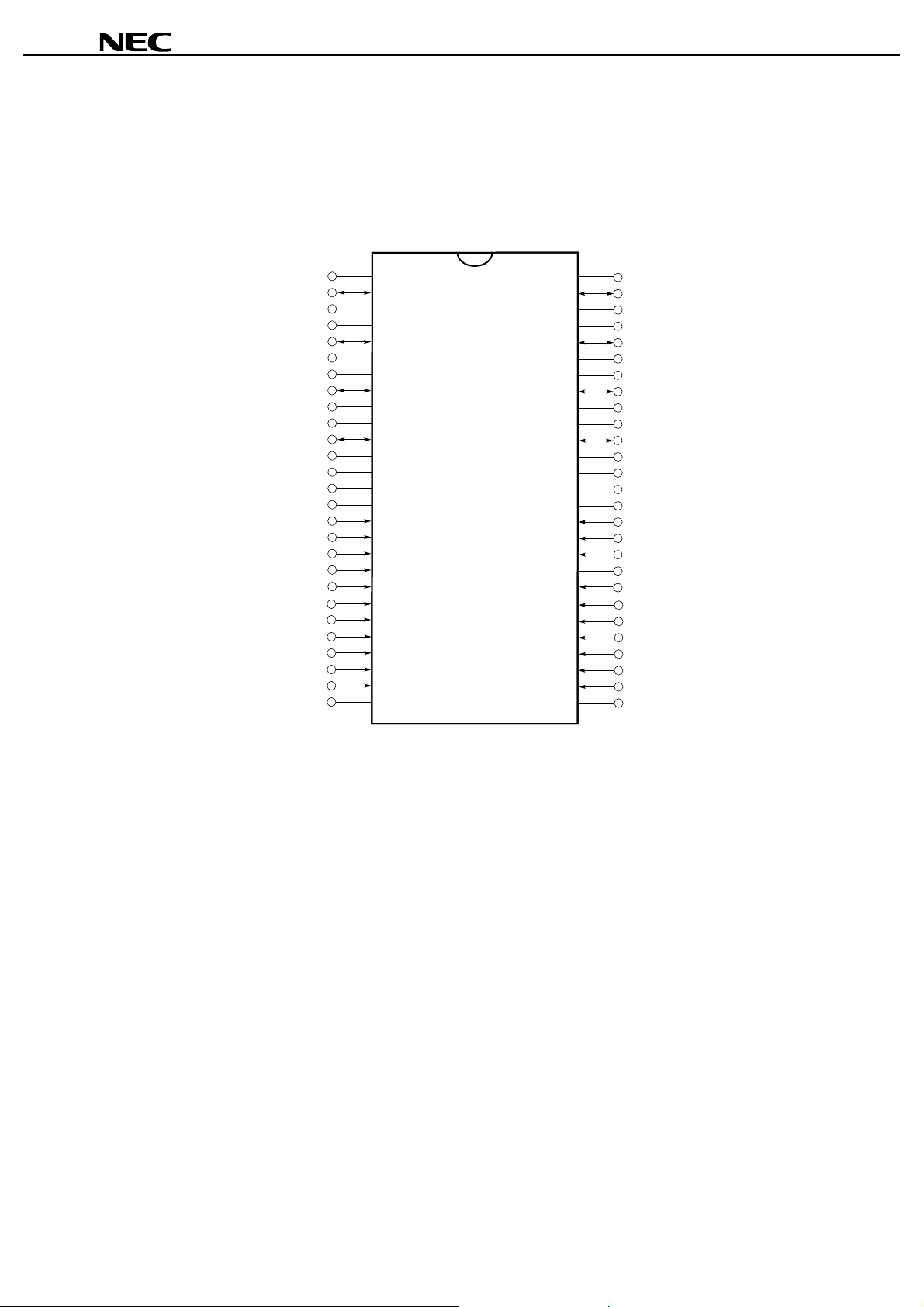

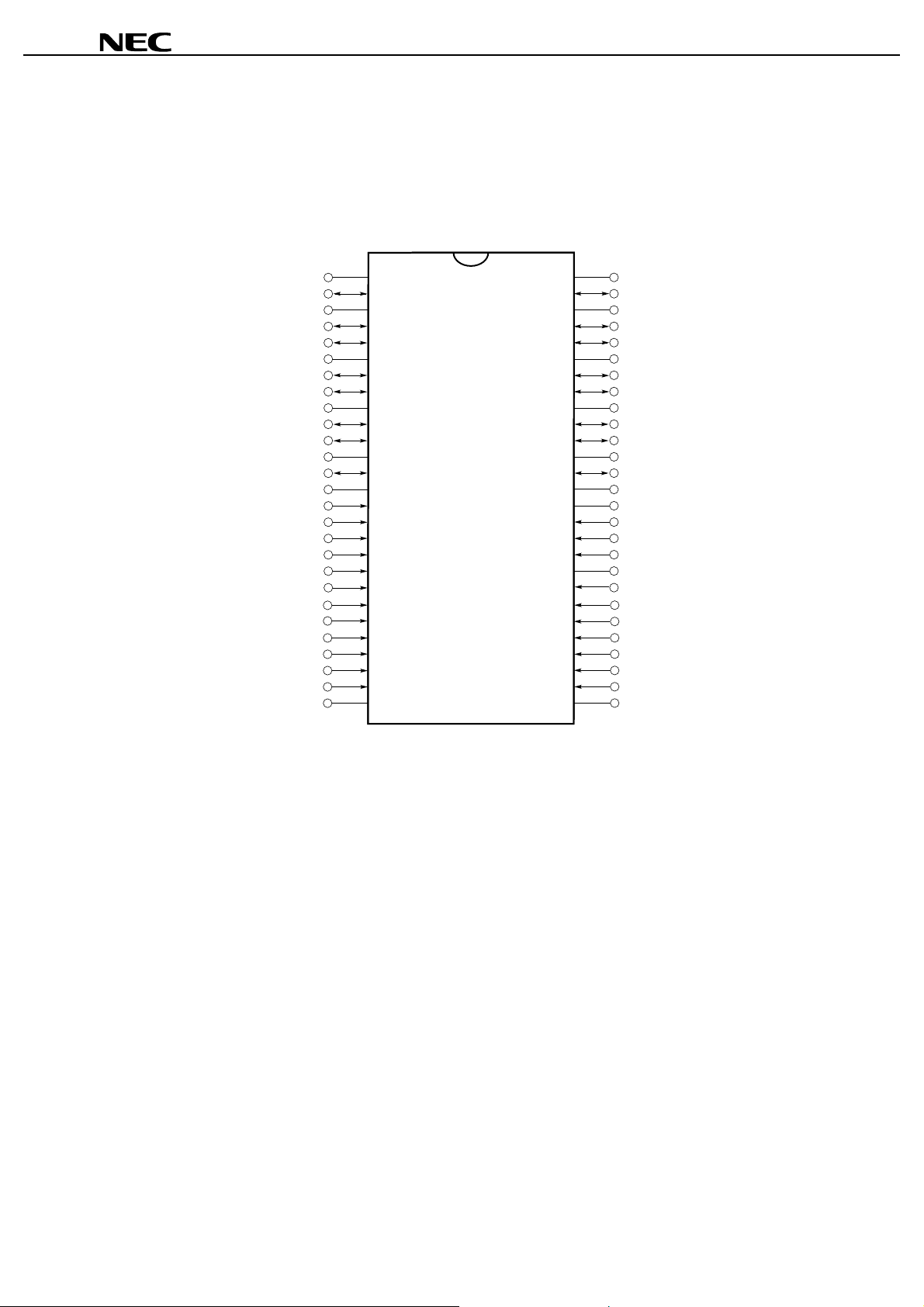

Pin Configurations

/xxx indicates active low signal.

µµµµ

PD45128441, 45128841, 45128163

PD45128441]

[

µµµµ

54-pin Plastic TSOP (II) (10.16mm (400))

8M words

4 bits

××××

4 banks

××××

V

NC

CC

V

NC

DQ0

SS

V

NC

NC

CC

V

NC

DQ1

SS

V

NC

V

NC

/WE

/CAS

/RAS

/CS

BA0(A13)

BA1(A12)

A10

A0

A1

A2

A3

V

CC

Q

Q

Q

Q

CC

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

Vss

NC

VssQ

NC

DQ3

VccQ

NC

NC

VssQ

NC

DQ2

VccQ

NC

Vss

NC

DQM

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

Vss

A0 to A11

Note

: Address inputs

BA0(A13), BA1(A12): Bank select

DQ0 to DQ3 : Data inputs / outputs

CLK : Clock input

CKE : Clock enable

/CS : Chip select

/RAS : Row address strobe

/CAS : Column address strobe

/WE : Write enable

DQM : DQ mask enable

CC

V

SS

V

CC

Q : Supply voltage for DQ

V

SS

Q : Ground for DQ

V

: Supply voltage

: Ground

Note

A0 to A11 : Row address inputs

A0 to A9, A11 : Column address inputs

NC : No connection

4

Data Sheet M12650EJBV0DS00

V

DQ0

CC

V

NC

DQ1

SS

V

NC

DQ2

CC

V

NC

DQ3

SS

V

NC

V

NC

/WE

/CAS

/RAS

/CS

BA0(A13)

BA1(A12)

A10

A0

A1

A2

A3

V

µµµµ

PD45128441, 45128841, 45128163

[

PD45128841]

µµµµ

54-pin Plastic TSOP (II) (10.16mm (400))

4M words

CC

Q

Q

Q

Q

CC

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

8 bits

××××

4 banks

××××

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

Vss

DQ7

VssQ

NC

DQ6

VccQ

NC

DQ5

VssQ

NC

DQ4

VccQ

NC

Vss

NC

DQM

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

Vss

A0 to A11

Note

: Address inputs

BA0(A13), BA1(A12): Bank select

DQ0 to DQ7 : Data inputs / outputs

CLK : Clock input

CKE : Clock enable

/CS : Chip select

/RAS : Row address strobe

/CAS : Column address strobe

/WE : Write enable

DQM : DQ mask enable

CC

V

SS

V

CC

Q : Supply voltage for DQ

V

SS

Q : Ground for DQ

V

: Supply voltage

: Ground

NC : No connection

Data Sheet M12650EJBV0DS00

Note

A0 to A11 : Row address inputs

A0 to A9 : Column address inputs

5

V

DQ0

CC

V

DQ1

DQ2

SS

V

DQ3

DQ4

CC

V

DQ5

DQ6

SS

V

DQ7

V

LDQM

/WE

/CAS

/RAS

/CS

BA0(A13)

BA1(A12)

A10

A0

A1

A2

A3

V

µµµµ

PD45128441, 45128841, 45128163

[

PD45128163]

µµµµ

54-pin Plastic TSOP (II) (10.16mm (400))

2M words

CC

Q

Q

Q

Q

CC

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

16 bits

××××

4 banks

××××

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

Vss

DQ15

VssQ

DQ14

DQ13

VccQ

DQ12

DQ11

VssQ

DQ10

DQ9

VccQ

DQ8

Vss

NC

UDQM

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

Vss

A0 to A11

Note

: Address inputs

BA0(A13), BA1(A12): Bank select

DQ0 to DQ15 : Data inputs / outputs

CLK : Clock input

CKE : Clock enable

/CS : Chip select

/RAS : Row address strobe

/CAS : Column address strobe

/WE : Write enable

LDQM : Lower DQ mask enable

UDQM : Upper DQ mask enable

CC

V

SS

V

CC

Q : Supply voltage for DQ

V

SS

Q : Ground for DQ

V

: Supply voltage

: Ground

Note

A0 to A11 : Row address inputs

A0 to A8 : Column address inputs

NC : No connection

6

Data Sheet M12650EJBV0DS00

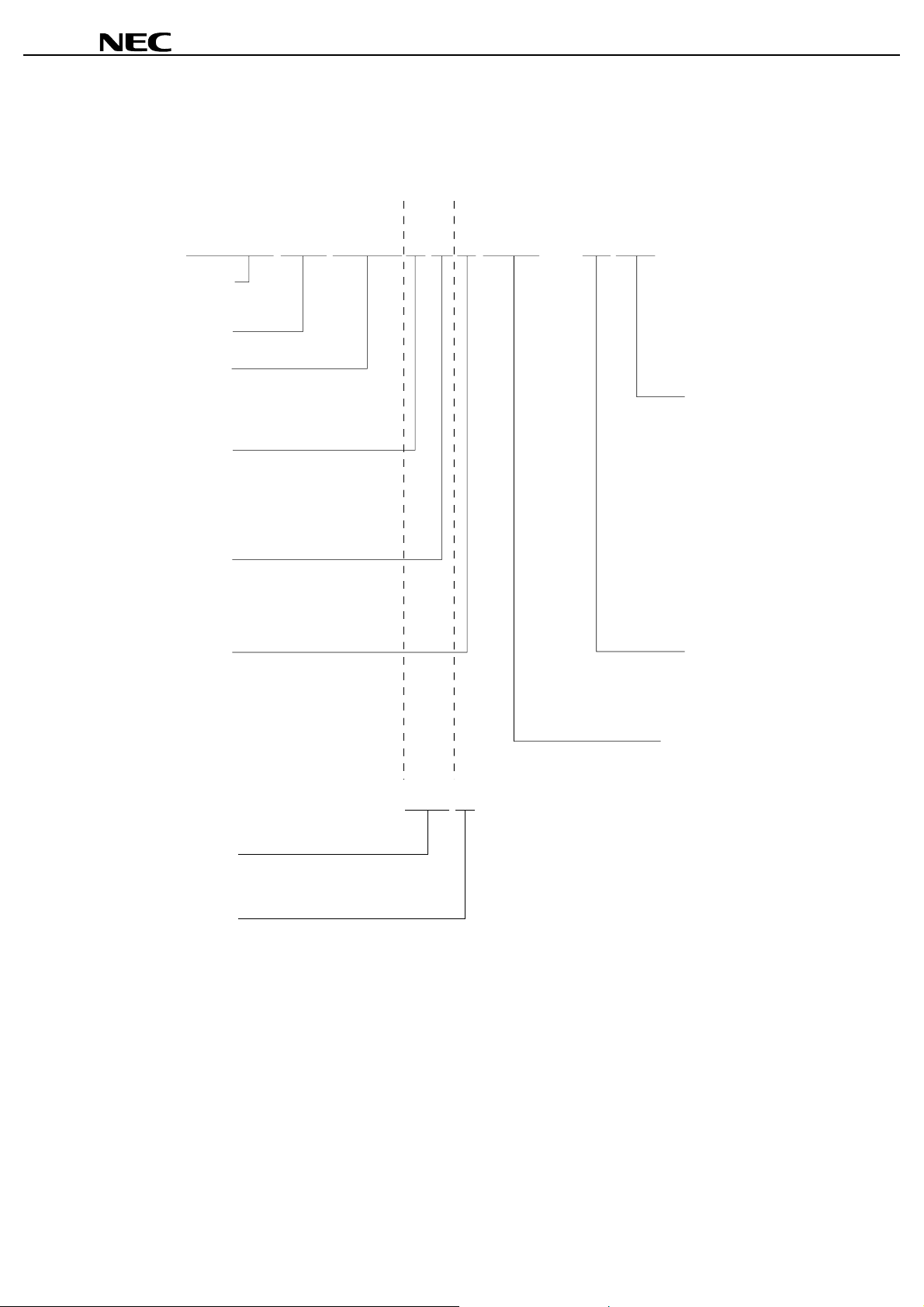

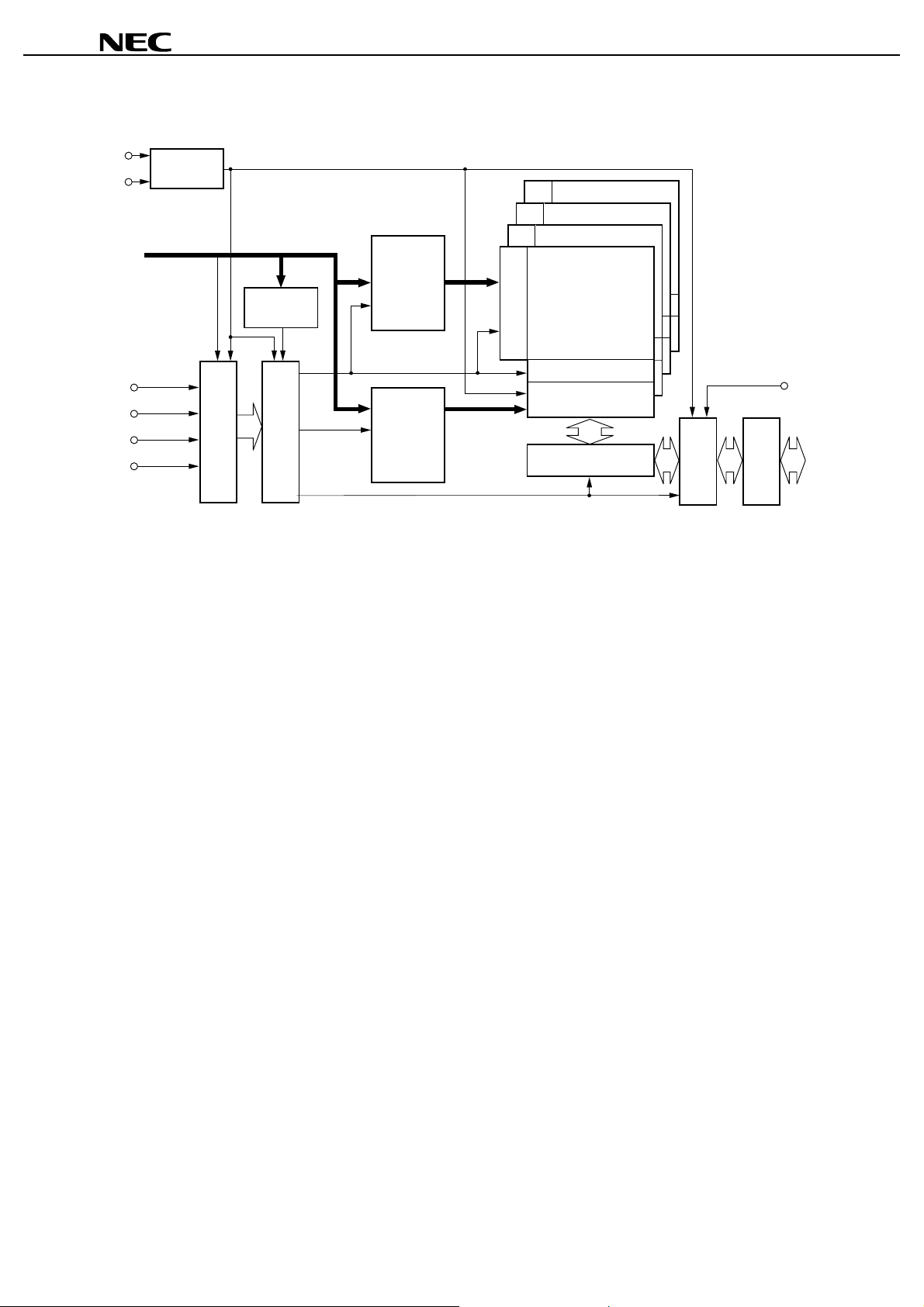

Block Diagram

µµµµ

PD45128441, 45128841, 45128163

CLK

CKE

Address

/CS

/RAS

/CAS

/WE

Clock

Generator

Mode

Register

Control Logic

Command Decoder

Row

Address

Buffer

&

Refresh

Counter

Column

Address

Buffer

&

Burst

Counter

Bank B

Bank A

Row Decoder

Sense Amplifier

Column Decoder &

Latch Circuit

Data Control Circuit

Bank D

Bank C

Latch Circuit

DQM

DQ

Input & Output

Buffer

Data Sheet M12650EJBV0DS00

7

µµµµ

PD45128441, 45128841, 45128163

CONTENTS

1. Input / Output Pin Function ............................................................................................................ 10

2. Commands ....................................................................................................................................... 11

3. Simplified State Diagram ................................................................................................................ 14

4. Truth Table ....................................................................................................................................... 15

4.1 Command Truth Table............................................................................................................................. 15

4.2 DQM Truth Table...................................................................................................................................... 15

4.3 CKE Truth Table....................................................................................................................................... 15

4.4 Operative Command Table .................................................................................................................... 16

4.5 Command Truth Table for CKE ............................................................................................................. 19

5. Initialization ...................................................................................................................................... 20

6. Programming the Mode Register ................................................................................................... 21

7. Mode Register .................................................................................................................................. 22

7.1 Burst Length and Sequence .................................................................................................................. 23

8. Address Bits of Bank-Select and Precharge ................................................................................ 24

9. Precharge ......................................................................................................................................... 25

10. Auto Precharge ................................................................................................................................ 26

10.1 Read with Auto Precharge .................................................................................................................. 26

10.2 Write with Auto Precharge .................................................................................................................. 27

11. Read / Write Command Interval ..................................................................................................... 28

11.1 Read to Read Command Interval ........................................................................................................ 28

11.2 Write to Write Command Interval ....................................................................................................... 28

11.3 Write to Read Command Interval ........................................................................................................ 29

11.4 Read to Write Command Interval ........................................................................................................ 30

12. Burst Termination ........................................................................................................................... 31

12.1 Burst Stop Command .......................................................................................................................... 31

12.2 Precharge Termination ........................................................................................................................ 32

12.2.1 Precharge Termination in READ Cycle .................................................................................... 32

12.2.2 Precharge Termination in WRITE Cycle .................................................................................. 33

8

Data Sheet M12650EJBV0DS00

µµµµ

PD45128441, 45128841, 45128163

13. Electrical Specifications ................................................................................................................. 34

13.1 AC Parameters for Read Timing ......................................................................................................... 39

13.2 AC Parameters for Write Timing ......................................................................................................... 41

13.3 Relationship between Frequency and Latency ................................................................................. 42

13.4 Mode Register Set ................................................................................................................................ 43

13.5 Power on Sequence and CBR (Auto) Refresh ................................................................................... 44

13.6 /CS Function ......................................................................................................................................... 45

13.7 Clock Suspension during Burst Read (using CKE Function) .......................................................... 46

13.8 Clock Suspension during Burst Write (using CKE Function) .......................................................... 48

13.9 Power Down Mode and Clock Mask ................................................................................................... 50

13.10 CBR (Auto) Refresh ............................................................................................................................. 51

13.11 Self Refresh (Entry and Exit) ............................................................................................................... 52

13.12 Random Column Read (Page with Same Bank) ................................................................................ 53

13.13 Random Column Write (Page with Same Bank) ................................................................................ 55

13.14 Random Row Read (Ping-Pong Banks) ............................................................................................. 57

13.15 Random Row Write (Ping-Pong Banks) ............................................................................................. 59

13.16 Read and Write ..................................................................................................................................... 61

13.17 Interleaved Column Read Cycle .......................................................................................................... 63

13.18 Interleaved Column Write Cycle ......................................................................................................... 65

13.19 Auto Precharge after Read Burst ........................................................................................................ 67

13.20 Auto Precharge after Write Burst ....................................................................................................... 69

13.21 Full Page Read Cycle ........................................................................................................................... 71

13.22 Full Page Write Cycle ........................................................................................................................... 73

13.23 Byte Write Operation ............................................................................................................................ 75

13.24 Burst Read and Single Write (Option) ................................................................................................ 77

13.25 Full Page Random Column Read ........................................................................................................ 79

13.26 Full Page Random Column Write ....................................................................................................... 81

13.27 PRE (Precharge) Termination of Burst ............................................................................................... 83

14. Package Drawing ............................................................................................................................. 85

15. Recommended Soldering Conditions ........................................................................................... 86

16. Revision History .............................................................................................................................. 87

Data Sheet M12650EJBV0DS00

9

µµµµ

PD45128441, 45128841, 45128163

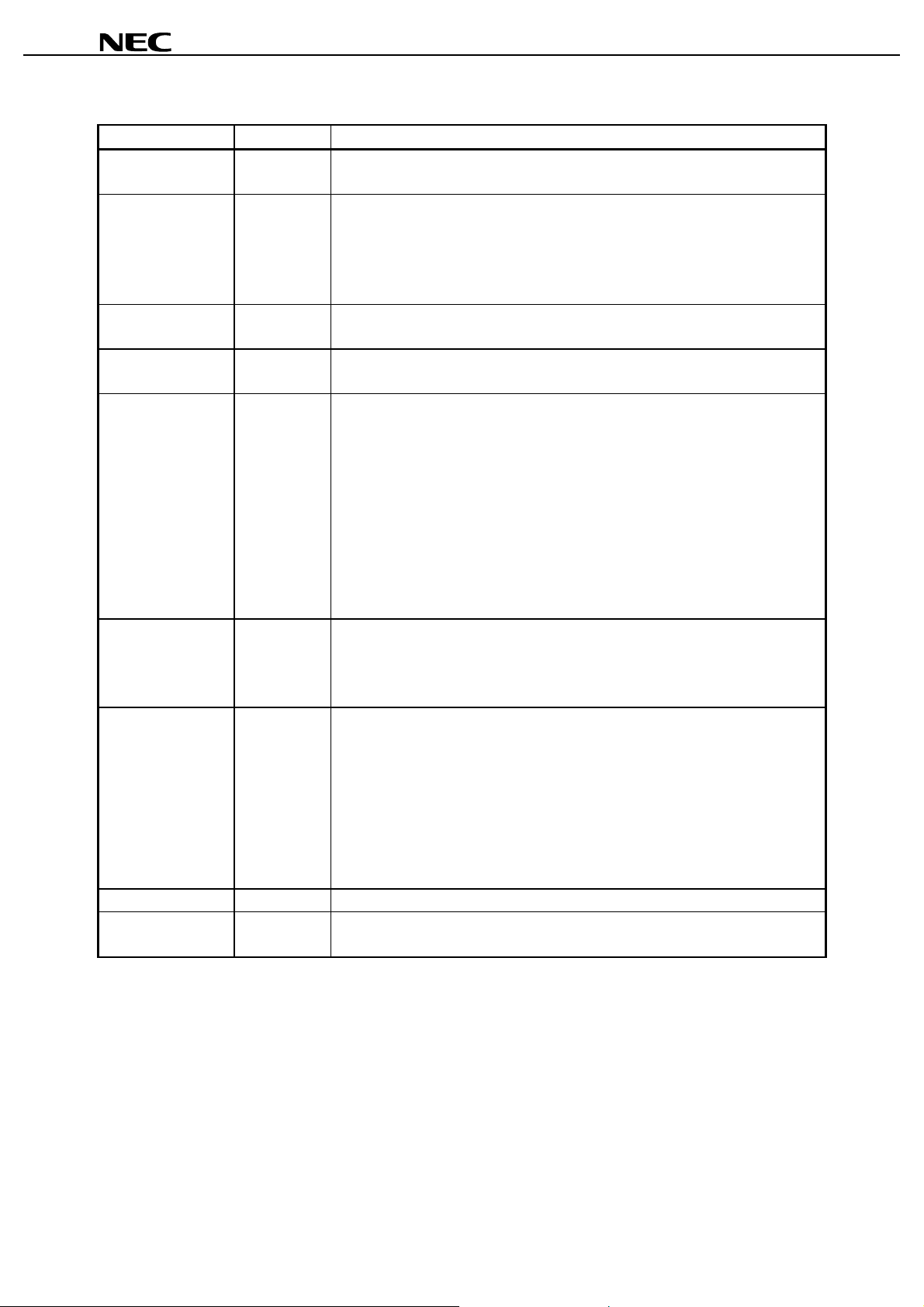

1. Input / Output Pin Function

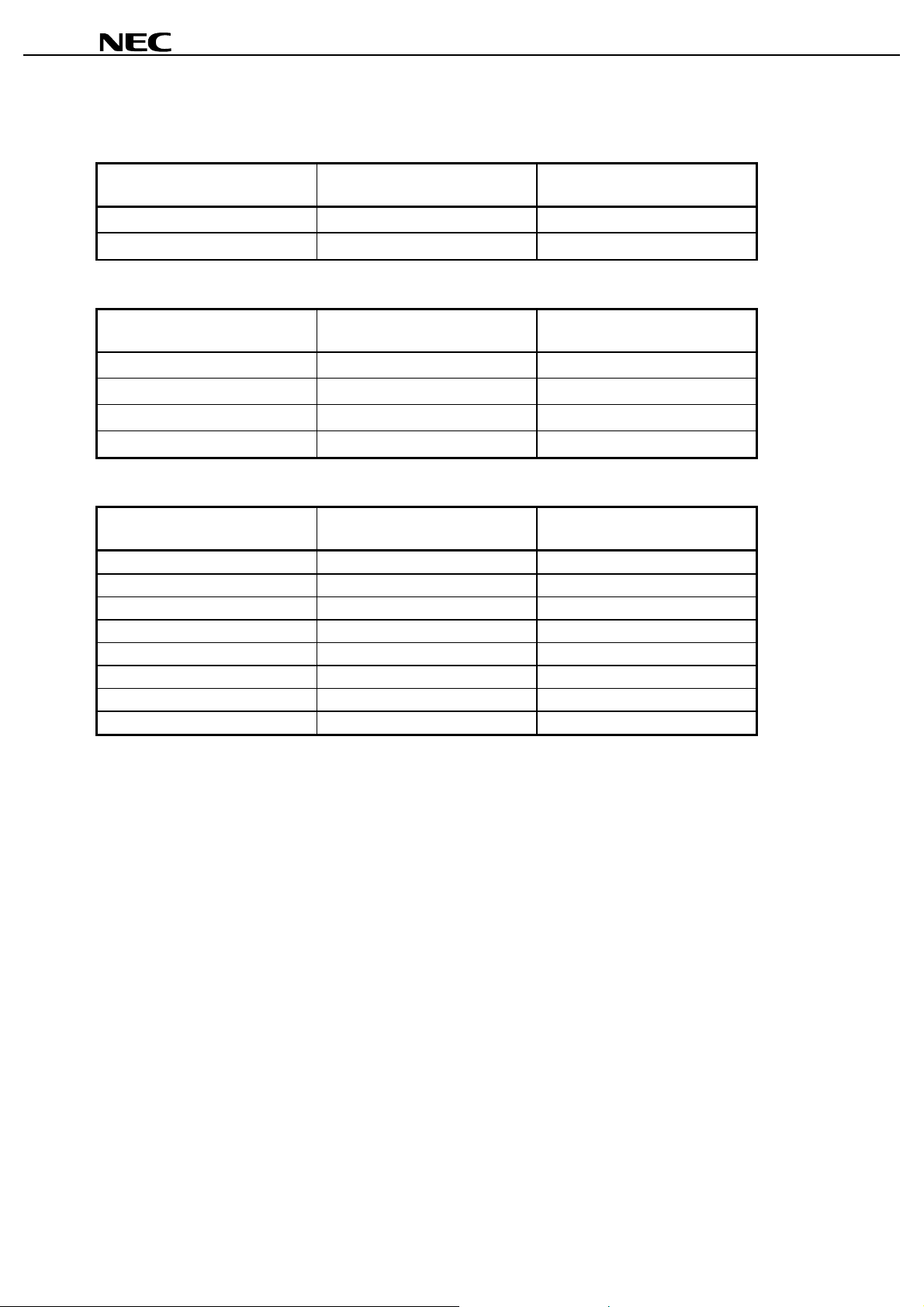

Pin name Input / Output Function

CLK Input CLK is the master clock input. Other inputs s i gnal s are referenced to the CLK rising

edge.

CKE Input CKE determine validity of the next CLK (clock). If CKE i s high, the next CLK rising edge

is valid; otherwise it is i nval i d. If the CLK rising edge is inval i d, the internal clock is not

issued and the

When the

power down mode. During power down mode, CKE must rem ai n l ow.

/CS Input /CS low starts the com mand input cycle. When /CS is high, com mands are ignored but

operations continue.

/RAS, /CAS, /WE Input /RAS, /CAS and /WE have the same symbols on conventional DRAM but diff erent

functions. For details, refer to the comm and table.

A0 - A11 Input

BA0, BA1 Input BA0(A13) and BA1(A12) are the bank select signal. In command cycle, BA0(A13) and

DQM, UDQM, LDQM Input

DQ0 - DQ15 Input / Output DQ pins have the same function as I/O pins on a conventional DRAM.

VCC, VSS, VCCQ, VSSQ (Power supply) VCC and VSS are power supply pins for internal circui t s. VCCQ and VSSQ are power

Row Address is determined by A0 - A 11 at the CLK (clock) rising edge in the active

command cycle. It does not depend on the bit organization.

Column Address is det ermined by A0 - A9, A11 at the CLK rising edge in the read or

write command cycle. It depends on the bit organization: A0 - A9, A11 for ×4 device, A0

- A9 for ×8 device, A0 - A8 for ×16 device.

A10 defines the precharge mode. When A10 is high in t he precharge command cycle,

all banks are precharged; when A10 is low, only the bank selected by BA0(A13) and

BA1(A12)

When A10 is high i n read or write c ommand cycle, the precharge starts automatic al l y

after the burst acces s.

BA1(A12) low select bank A, B A0(A13) high and BA1(A12) low select bank B, BA0(A13)

low and BA1(A12) high select bank C and then BA0(A13) and BA1(A12) high select

bank D.

DQM controls I/O buffers. In ×16 products, UDQM and LDQM control upper byte and

lower byte I/O buffers, respectively.

In read mode, DQM controls the output buffers like a conventi onal /OE pin.

DQM high and DQM low turn the output buffers off and on, respectively.

The DQM latency for the read is two clocks.

In write mode, DQM controls the word m ask. Input data is written to t he memory cell if

DQM is low but not if DQM is high.

The DQM latency for the write is zero.

supply pins for the output buf f ers.

PD45128xxx sus pends operation.

µ

PD45128xxx is not in b urst mode and CKE is negated, the devi ce enters

µ

is precharged.

10

Data Sheet M12650EJBV0DS00

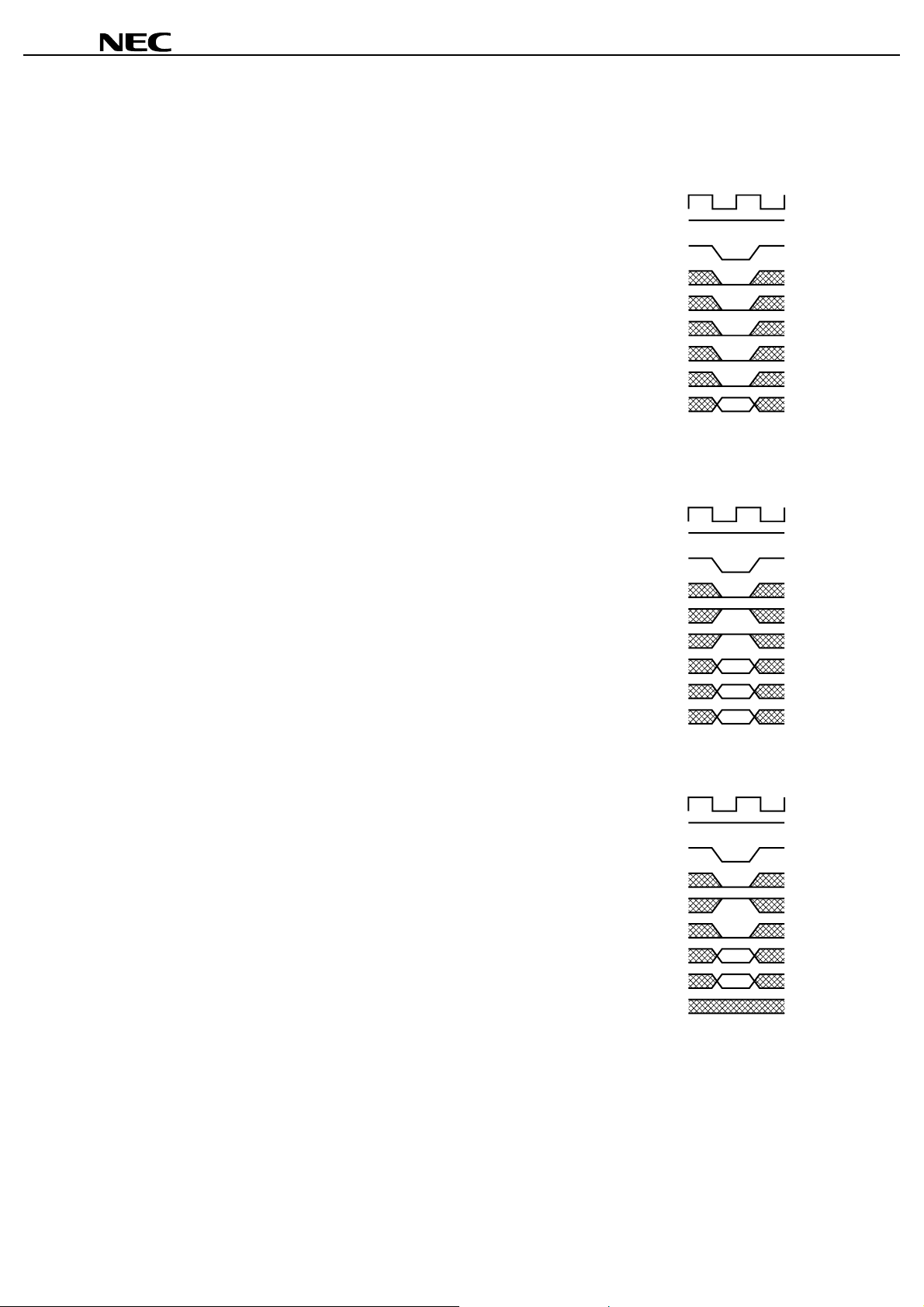

2. Commands

µµµµ

PD45128441, 45128841, 45128163

Mode register set command

(/CS, /RAS, /CAS, /WE = Low)

The

PD45128xxx has a mode register that defines how the device

µ

operates. In this command, A0 through A11, BA0(A13) and BA1(A12)

are the data input pins. After power on, the mode register set

command must be executed to initialize the device.

The mode register can be set only when all banks are in idle state.

RSC

During 2 CLK (t

) following this command, the µPD45128xxx

cannot accept any other commands.

Activate command

(/CS, /RAS = Low, /CAS, /WE = High)

The

PD45128xxx has four banks, each with 4,096 rows.

µ

This command activates the bank selected by BA0(A13) and

BA1(A12) and a row address selected by A0 through A11.

This command corresponds to a conventional DRAM’s /RAS falling.

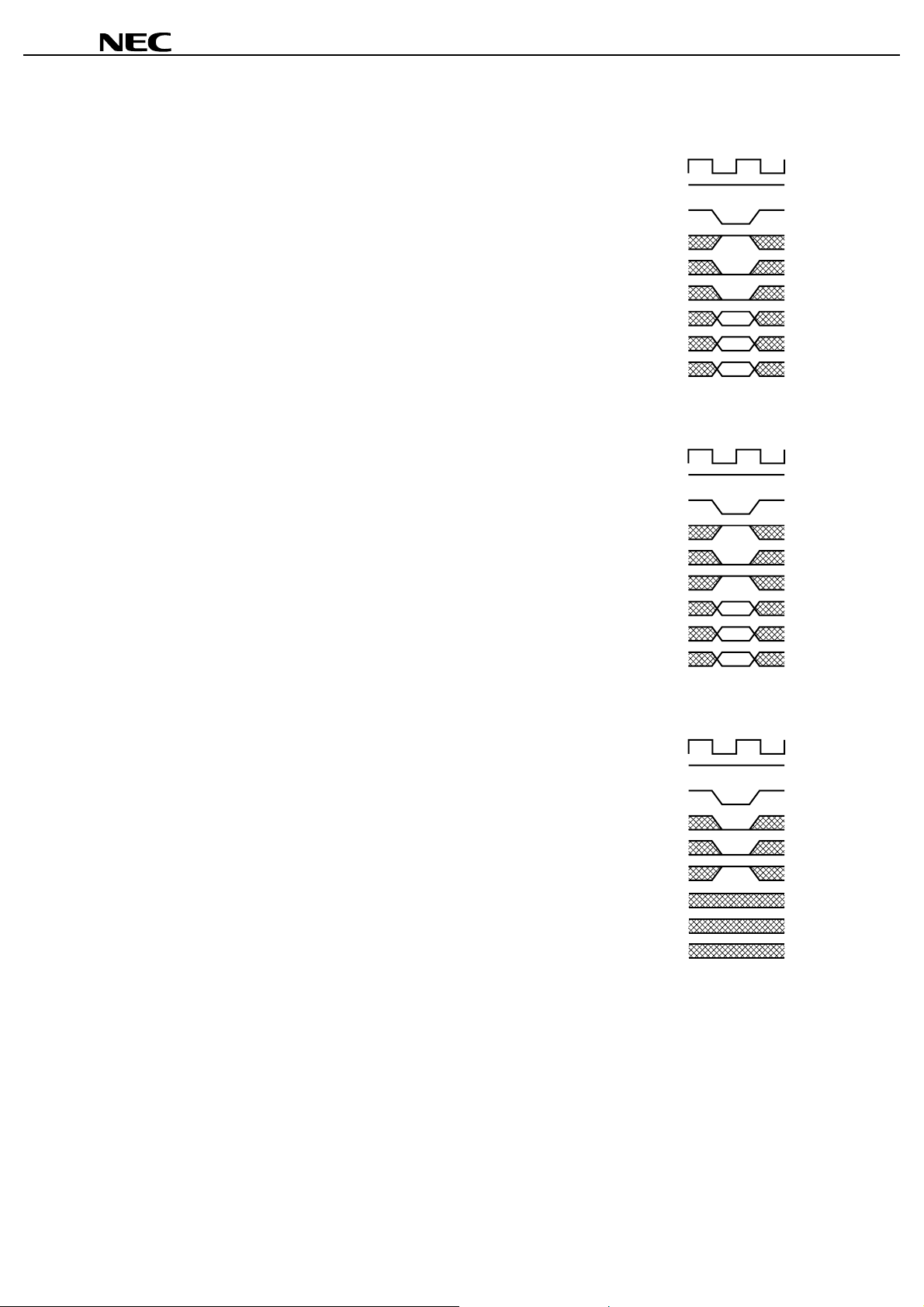

Fig.1 Mode register set command

CLK

CKE

H

/CS

/RAS

/CAS

/WE

BA0(A13), BA1(A12)

A10

Add

Fig.2 Row address strobe and

bank activate command

CLK

CKE

H

/CS

/RAS

/CAS

/WE

BA0(A13), BA1(A12)

A10

Add

Row

Row

Precharge command

(/CS, /RAS, /WE = Low, /CAS = High)

This command begins precharge operation of the bank selected by

BA0(A13) and BA1(A12). When A10 is High, all banks are

precharged, regardless of BA0(A13) and BA1(A12). When A10 is

Low, only the bank selected by BA0(A13) and BA1(A12) is

precharged.

After this command, the

command to the precharging bank during t

PD45128xxx can’t accept the activate

µ

RP

(precharge to activate

command period).

This command corresponds to a conventional DRAM’s /RAS rising.

Data Sheet M12650EJBV0DS00

Fig.3 Precharge command

CLK

CKE

H

/CS

/RAS

/CAS

/WE

BA0(A13), BA1(A12)

(Precharge select)

A10

Add

11

µµµµ

PD45128441, 45128841, 45128163

Write command

(/CS, /CAS, /WE = Low, /RAS = High)

If the mode register is in the burst write mode, this command sets the

burst start address given by the column address to begin the burst

write operation. The first write data in burst mode can input with this

command with subsequent data on following clocks.

Read command

(/CS, /CAS = Low, /RAS, /WE = High)

Read data is available after /CAS latency requirements have been

met. This command sets the burst start address given by the column

address.

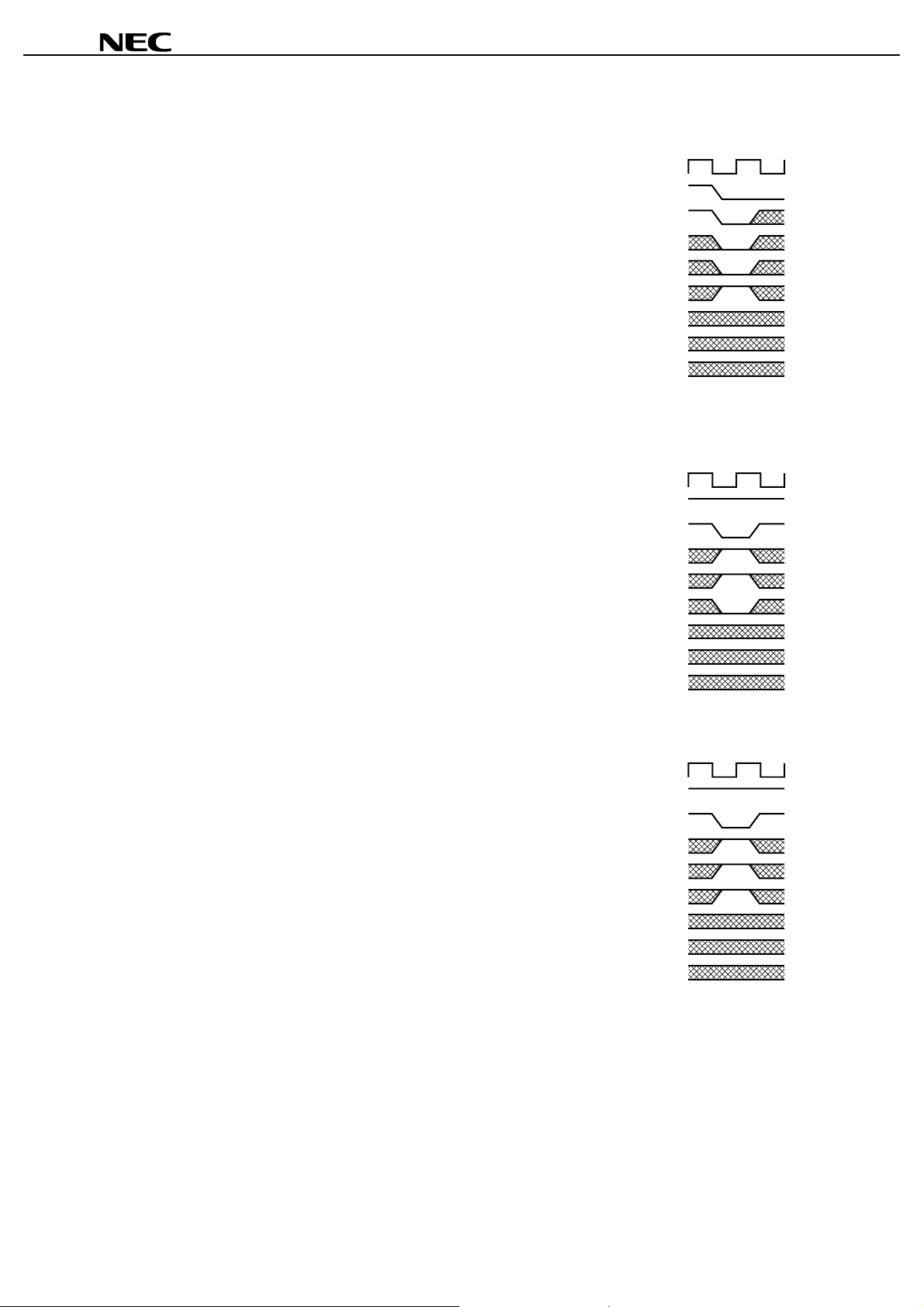

Fig.4 Column address and write command

CLK

CKE

H

/CS

/RAS

/CAS

/WE

BA0(A13), BA1(A12)

A10

Add

Col.

Fig.5 Column address and read command

CLK

CKE

H

/CS

/RAS

/CAS

/WE

BA0(A13), BA1(A12)

A10

Add

Col.

CBR (auto) refresh command

(/CS, /RAS, /CAS = Low, /WE, CKE = High)

This command is a request to begin the CBR (auto) refresh

operation. The refresh address is generated internally.

Before executing CBR (auto) refresh, all banks must be precharged.

After this cycle, all banks will be in the idle (precharged) state and

ready for a row activate command.

RC

During t

command), the

period (from refresh command to refresh or activate

PD45128xxx cannot accept any other command.

µ

Fig.6 CBR (auto) refresh command

CLK

CKE

H

/CS

/RAS

/CAS

/WE

BA0(A13), BA1(A12)

A10

Add

12

Data Sheet M12650EJBV0DS00

µµµµ

PD45128441, 45128841, 45128163

Self refresh entry command

(/CS, /RAS, /CAS, CKE = Low, /WE = High)

After the command execution, self refresh operation continues while

CKE remains low. When CKE goes high, the

PD45128xxx exits the

µ

self refresh mode.

During self refresh mode, refresh interval and refresh operation are

performed internally, so there is no need for external control.

Before executing self refresh, all banks must be precharged.

Burst stop command

(/CS, /WE = Low, /RAS, /CAS = High)

This command can stop the current burst operation.

Fig.7 Self refresh entry command

CLK

CKE

/CS

/RAS

/CAS

/WE

BA0(A13), BA1(A12)

A10

Add

Fig.8 Burst stop command in Full Page

Mode

CLK

CKE

H

/CS

/RAS

/CAS

/WE

BA0(A13), BA1(A12)

A10

Add

No operation

(/CS = Low, /RAS, /CAS, /WE = High)

This command is not an execution command. No operations begin

or terminate by this command.

Fig.9 No operation

CLK

CKE

/CS

/RAS

/CAS

/WE

BA0(A13), BA1(A12)

A10

Add

H

Data Sheet M12650EJBV0DS00

13

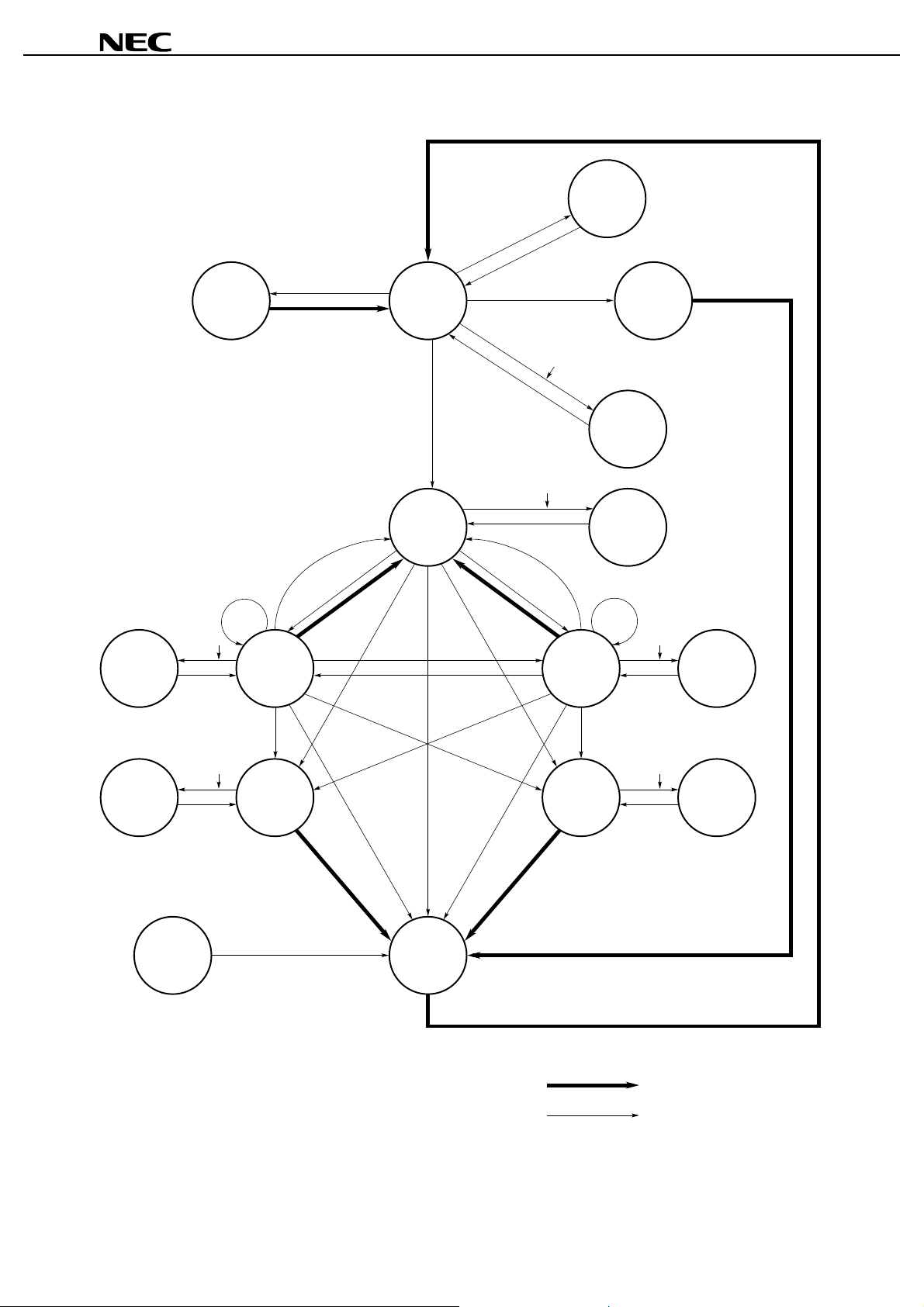

3. Simplified State Diagram

µµµµ

PD45128441, 45128841, 45128163

Self

Refresh

SELF

WRITE

SUSPEND

CKE

CKE

Mode

Register

Set

Write

WRITE

BST

MRS

Write

IDLE

ROW

ACTIVE

Write with

Read

Auto precharge

ACT

Auto precharge

PRE

Write

Read

Read with

SELF exit

REF

CKE

CKE

CKE

CKE

BST

READ

CBR (Auto)

Refresh

Power

Down

Active

Power

Down

Read

CKE

CKE

READ

SUSPEND

WRITEA

SUSPEND

14

POWER

ON

CKE

CKE

WRITEA

Precharge

PRE (Precharge termination)

PRE (Precharge termination)

Precharge

Data Sheet M12650EJBV0DS00

READA

CKE

CKE

READA

SUSPEND

Automatic sequence

Manual input

4. Truth Table

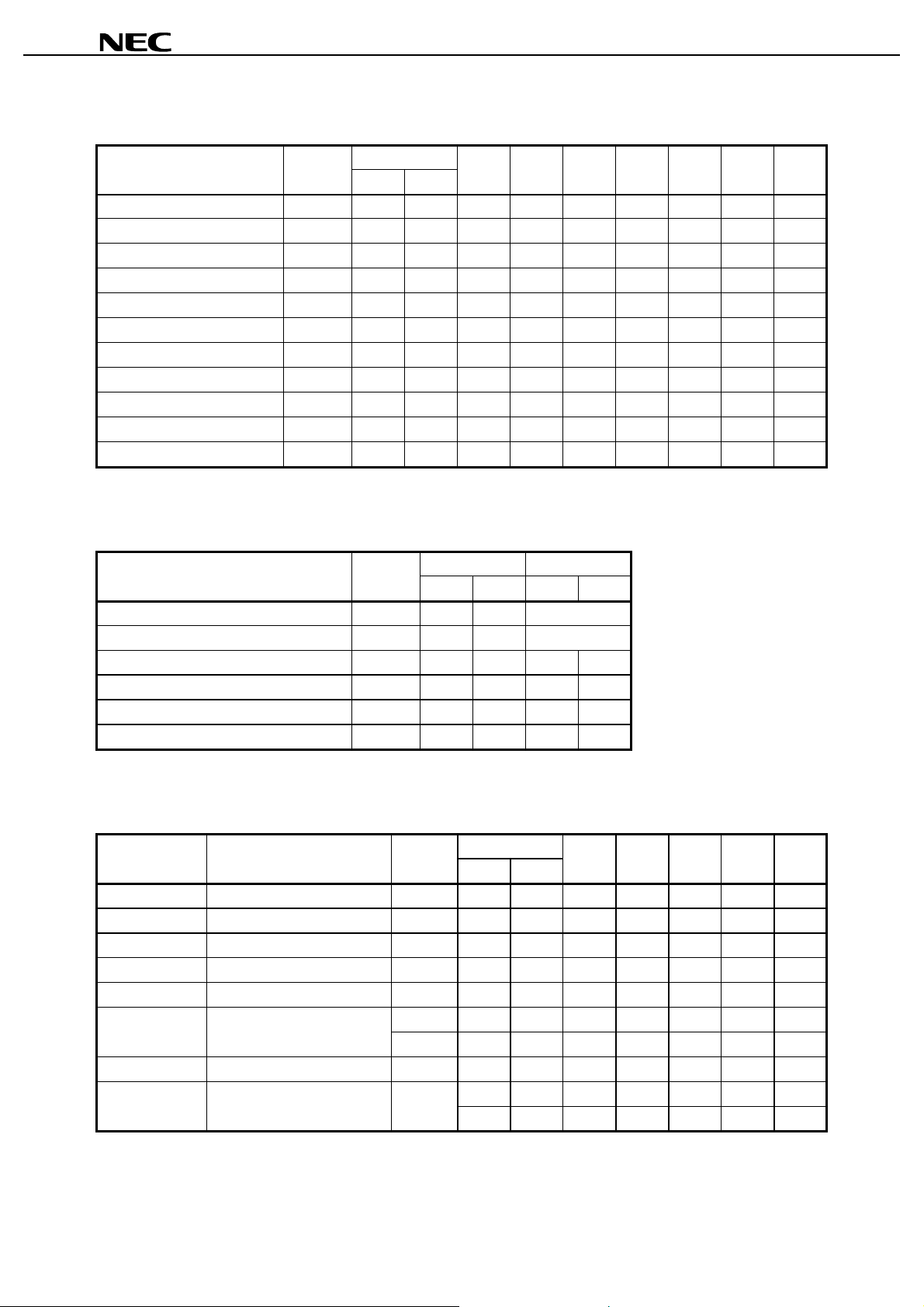

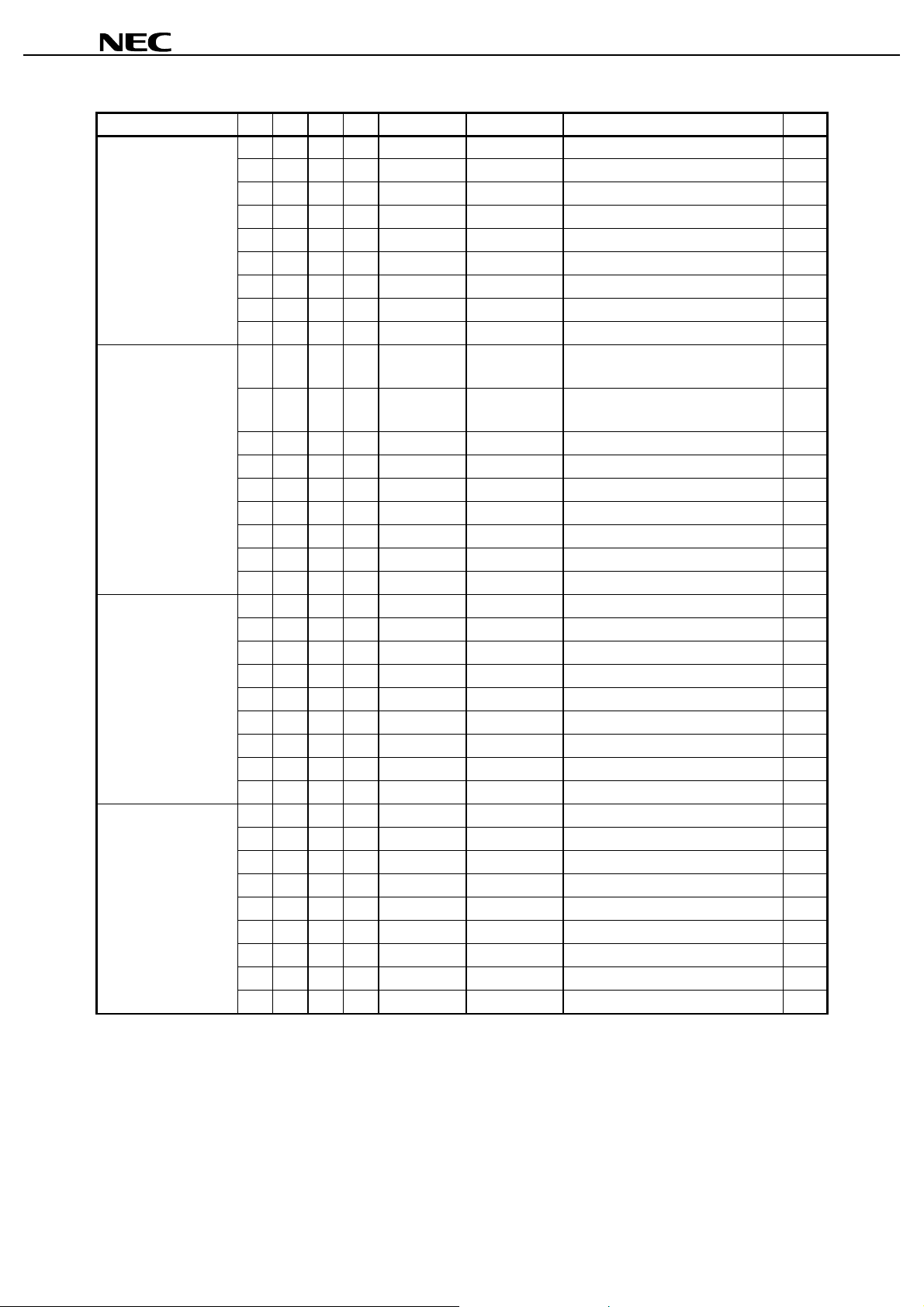

4.1 Command Truth Table

Function Symbol CKE /CS /RAS /CAS /WE BA1, A10 A11,

Device deselect DESL H

No operation NOP H

Burst stop BST H

Read READ H

Read with auto precharge READA H

Write WRIT H

Write with auto precharge WRITA H

Bank activate ACT H

Precharge select bank PRE H

Precharge all banks PALL H

Mode register set MRS H

µµµµ

PD45128441, 45128841, 45128163

n – 1 n BA0 A9 - A0

×

×

×

×

×

×

×

×

×

×

×

H

LHHH

LHHL

LHLHVLV

LHLHVHV

LHLLVLV

LHLLVHV

LLHHVVV

LLHLVL

LLHL

LLLLLLV

ЧЧЧЧЧЧ

×××

×××

×

×

H

×

Remark

H = High level, L = Low level, × = High or Low level (Don't care), V = Valid data input

4.2 DQM Truth Table

Function Symbol CKE DQM

n – 1 n U L

Data write / output enable ENB H

Data mask / output di sable MASK H

Upper byte write enable / output enable ENBU H

Lower byte write enable / output enable ENBL H

Upper byte write inhibit / output disable MASKU H

Lower byte write inhibit / output disable MASKL H

Remark

H = High level, L = Low level, × = High or Low level (Don't care)

×

×

×

××

×

××

L

H

L

H

×

L

×

H

4.3 CKE Truth Table

Current state F unction Symbol CKE /CS /RAS /CAS /WE Address

n – 1 n

Activating Clock sus pend mode entry H L

Any Clock suspend mode L L

Clock suspend Clock suspend mode exit L H

Idle CBR (auto) refresh command REF H H L L L H

Idle Self refresh entry SELF H L L L L H

Self refresh Self ref resh exit L H L H H H

LHH

Idle Power down entry H L

Power down Power down exit L H H

LHLHHH

ЧЧЧЧЧ

ЧЧЧЧЧ

ЧЧЧЧЧ

××××

ЧЧЧЧЧ

××××

×

×

×

×

Remark

H = High level, L = Low level, × = High or Low level (Don't care)

Data Sheet M12650EJBV0DS00

15

µµµµ

PD45128441, 45128841, 45128163

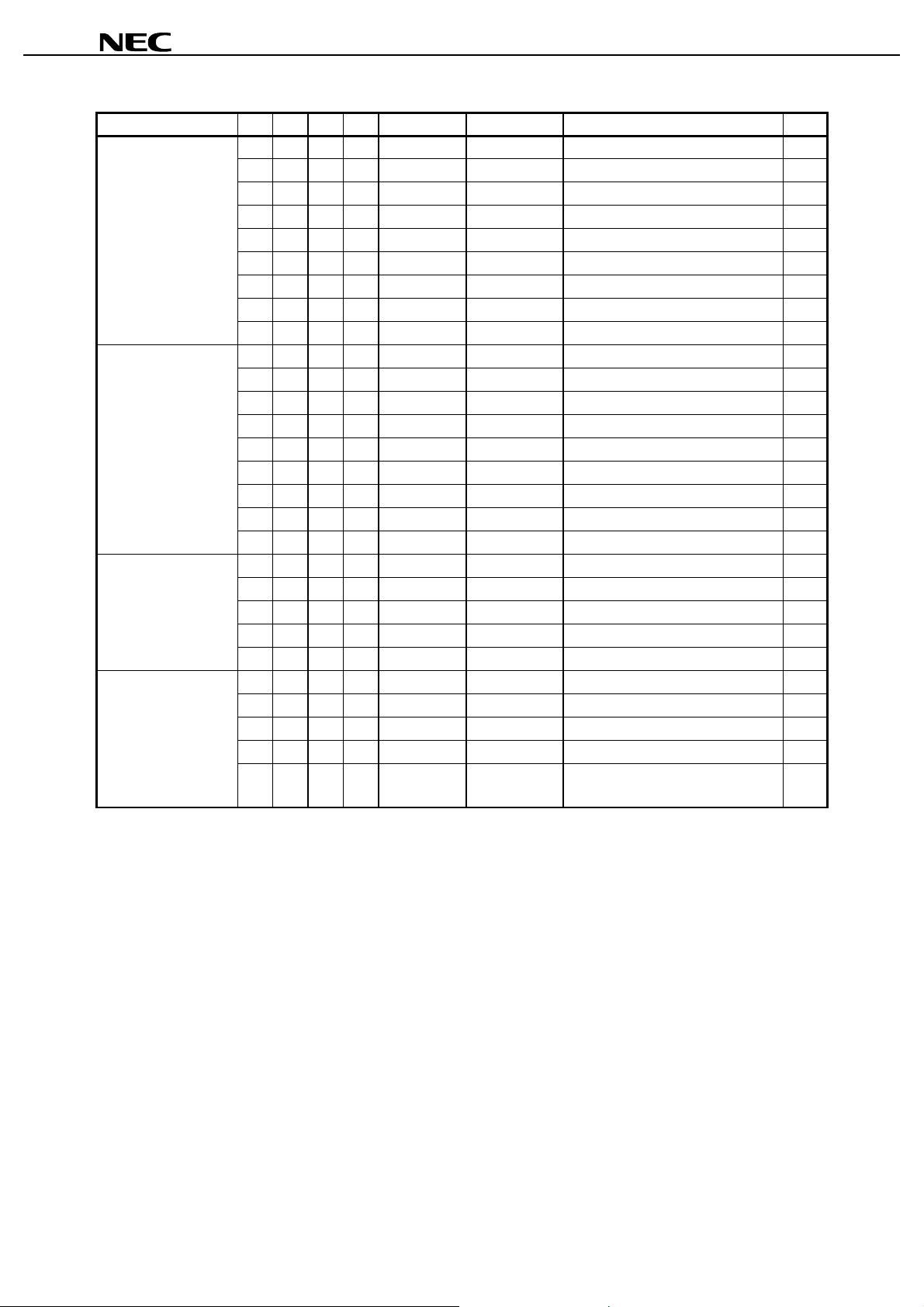

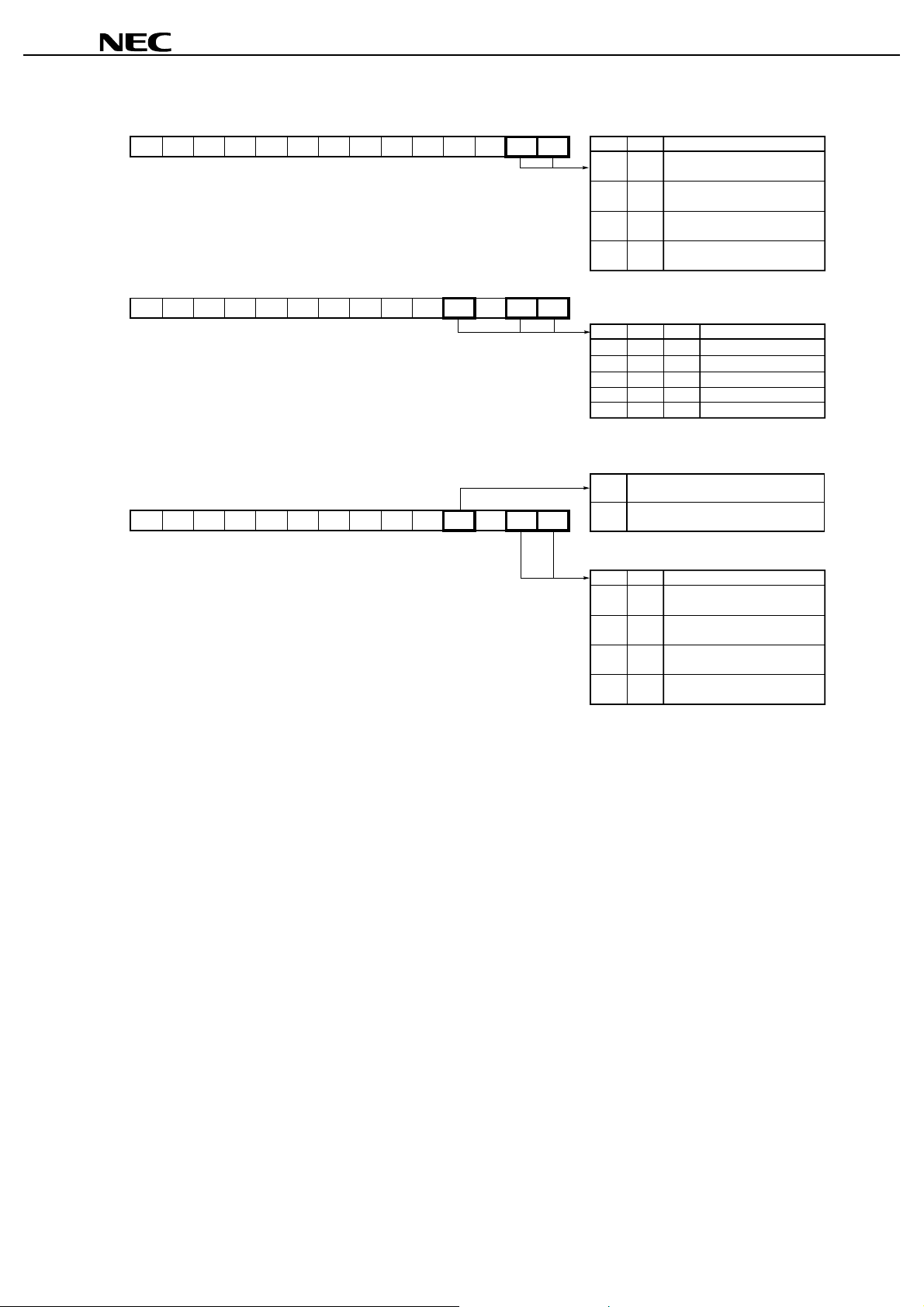

4.4 Operative Command Table

Current state /CS /RAS /CAS /WE Address Command Action Notes

Idle H

Row active H

Read H

Write H

××××

LHH

L H L H BA, CA, A10 READ/READA ILLEGAL 3

L H L L BA, CA, A10 WRIT/W RITA ILLEGAL 3

L L H H BA, RA ACT Row activating

L L H L BA, A10 PRE/PALL Nop

LLLH

L L L L Op-Code MRS Mode register accessing

××××

LHH

L H L H BA, CA, A10 READ/READA B egi n read : Determine AP 5

L H L L BA, CA, A10 WRIT/WRITA Begin write : Determine AP 5

L L H H BA, RA ACT ILLEGAL 3

L L H L BA, A10 PRE/PALL Precharge 6

LLLH

L L L L Op-Code MRS ILLEGAL

××××

LHHH

LHHL

L H L H BA, CA, A10 READ/READA T erminate burst, new read : Determine AP 7

L H L L BA, CA, A10 WRIT/WRITA Terminate burst, start write : Determine AP 7, 8

L L H H BA, RA ACT ILLEGAL 3

L L H L BA, A10 PRE/PALL Terminate burst, precharging

LLLH

L L L L Op-Code MRS ILLEGAL

××××

LHHH

LHHL

L H L H BA, CA, A10 READ/READA T erminate burst, start read : Determine AP 7, 8

L H L L BA, CA, A10 WRIT/WRITA Terminate burst, new write : Determine AP 7

L L H H BA, RA ACT ILLEGAL 3

L L H L BA, A10 PRE/PALL Terminate burst, precharging 9

LLLH

L L L L Op-Code MRS ILLEGAL

Note1

××

××

DESL Nop or power down 2

NOP or BST Nop or power down 2

×

×

×

×

×

×

×

×

REF/SELF CBR (aut o) ref resh or self refresh 4

DESL Nop

NOP or BST Nop

REF/SELF ILLEGAL

DESL Conti nue burst to end → Row active

NOP Continue burst t o end → Row active

BST Burst stop → Row active

REF/SELF ILLEGAL

DESL Conti nue burst to end → Write recoveri ng

NOP Continue burst t o end → Write recoveri ng

BST Burst stop → Row active

REF/SELF ILLEGAL

(1/3)

16

Data Sheet M12650EJBV0DS00

µµµµ

PD45128441, 45128841, 45128163

Current state /CS /RAS /CAS /WE Address Command Act i on Notes

Read with auto H

××××

precharge L H H H

LHHL

×

×

DESL Conti nue burst to end → Precharging

NOP Continue burst t o end → Precharging

BST ILLEGAL

L H L H BA, CA, A10 READ/READA ILLEGAL 3

L H L L BA, CA, A10 WRIT/W RITA ILLEGAL 3

L L H H BA, RA ACT ILLEGAL 3

L L H L BA, A10 PRE/PALL ILLEGAL 3

LLLH

×

REF/SELF ILLEGAL

LLLLOp-Code MRS ILLEGAL

Write with auto

precharge

H

××××

LHHH

DESL Conti nue burst to end → Write

recovering with auto precharge

×

NOP Continue burst t o end → Write

recovering with auto precharge

LHHL

×

BST ILLEGAL

L H L H BA, CA, A10 READ/READA ILLEGAL 3

L H L L BA, CA, A10 WRIT/W RITA ILLEGAL 3

L L H H BA, RA ACT ILLEGAL 3

L L H L BA, A10 PRE/PALL ILLEGAL 3

LLLH

×

REF/SELF ILLEGAL

LLLLOp-Code MRS ILLEGAL

Precharging H

××××

LHHH

LHHL

DESL Nop → Enter idle after t

×

×

NOP Nop → Enter idle after t

BST ILLEGAL

RP

RP

L H L H BA, CA, A10 READ/READA ILLEGAL 3

L H L L BA, CA, A10 WRIT/W RITA ILLEGAL 3

L L H H BA, RA ACT ILLEGAL 3

L L H L BA, A10 PRE/PALL Nop → Enter idle after t

LLLH

×

REF/SELF ILLEGAL

RP

LLLLOp-Code MRS ILLEGAL

Row activating H

××××

LHHH

LHHL

DESL Nop → Enter bank active aft er t

×

×

NOP Nop → Enter bank active aft er t

BST ILLEGAL

RCD

RCD

L H L H BA, CA, A10 READ/READA ILLEGAL 3

L H L L BA, CA, A10 WRIT/W RITA ILLEGAL 3

L L H H BA, RA ACT ILLEGAL 3, 10

L L H L BA, A10 PRE/PALL ILLEGAL 3

LLLH

×

REF/SELF ILLEGAL

LLLLOp-Code MRS ILLEGAL

(2/3)

Data Sheet M12650EJBV0DS00

17

µµµµ

PD45128441, 45128841, 45128163

Current state /CS /RAS /CAS /WE Address Command Act i on Notes

Write recoveri ng H

××××

LHHH

LHHL

DESL Nop → Enter row active after t

×

×

NOP Nop → Enter row active after t

BST Nop → Enter row active after t

DPL

DPL

DPL

L H L H BA, CA, A10 READ/READA Start read, Determine AP 8

L H L L BA, CA, A10 WRIT/W RITA New write, Determine AP

L L H H BA, RA ACT ILLEGAL 3

L L H L BA, A10 PRE/PALL ILLEGAL 3

LLLH

×

REF/SELF ILLEGAL

LLLLOp-Code MRS ILLEGAL

Write recoveri ng H

××××

with auto precharge L H H H

LHHL

DESL Nop → Enter precharge after t

×

×

NOP Nop → Enter precharge after t

BST Nop → Enter precharge after t

DPL

DPL

DPL

L H L H BA, CA, A10 READ/READA ILLEGAL 3, 8

L H L L BA, CA, A10 WRIT/W RITA ILLEGAL 3

L L H H BA, RA ACT ILLEGAL 3

L L H L BA, A10 PRE/PALL ILLEGAL

LLLH

×

REF/SELF ILLEGAL

LLLLOp-Code MRS ILLEGAL

Refreshing H

××××

LHH

LHL

LLH

LLL

Mode register H

××××

accessing L H H H

LHHL

LHL

LL

×××

××

××

××

××

×

×

××

DESL Nop → Enter idle after t

NOP/BST Nop → Enter idle after t

READ/WRIT ILLEGAL

ACT/PRE/PALL

REF/SELF/MRS

ILLEGAL

ILLEGAL

DESL Nop → Enter idle after t

NOP Nop → Enter idle after t

BST ILLEGAL

READ/WRIT ILLEGAL

ACT/PRE/PALL/

REF/SELF/MRS

ILLEGAL

RC

RC

RSC

RSC

(3/3)

Notes 1.

Remark

18

All entries assume that CKE was active (High level) during the preceding clock cycle.

2.

If all banks are idle, and CKE is inactive (Low level),

PD45128xxx will enter Power down mode.

µ

All input buffers except CKE will be disabled.

3.

Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address (BA),

depending on the state of that bank.

4.

If all banks are idle, and CKE is inactive (Low level), µPD45128xxx will enter Self refresh mode. All input

buffers except CKE will be disabled.

5.

Illegal if t

6.

Illegal if t

7.

Must satisfy burst interrupt condition.

8.

Must satisfy bus contention, bus turn around, and/or write recovery requirements.

9.

Must mask preceding data which don't satisfy t

10.

Illegal if t

RCD

is not satisfied.

RAS

is not satisfied.

RRD

is not satisfied.

DPL

.

H = High level, L = Low level, × = High or Low level (Don’t care), V = Valid data

Data Sheet M12650EJBV0DS00

µµµµ

PD45128441, 45128841, 45128163

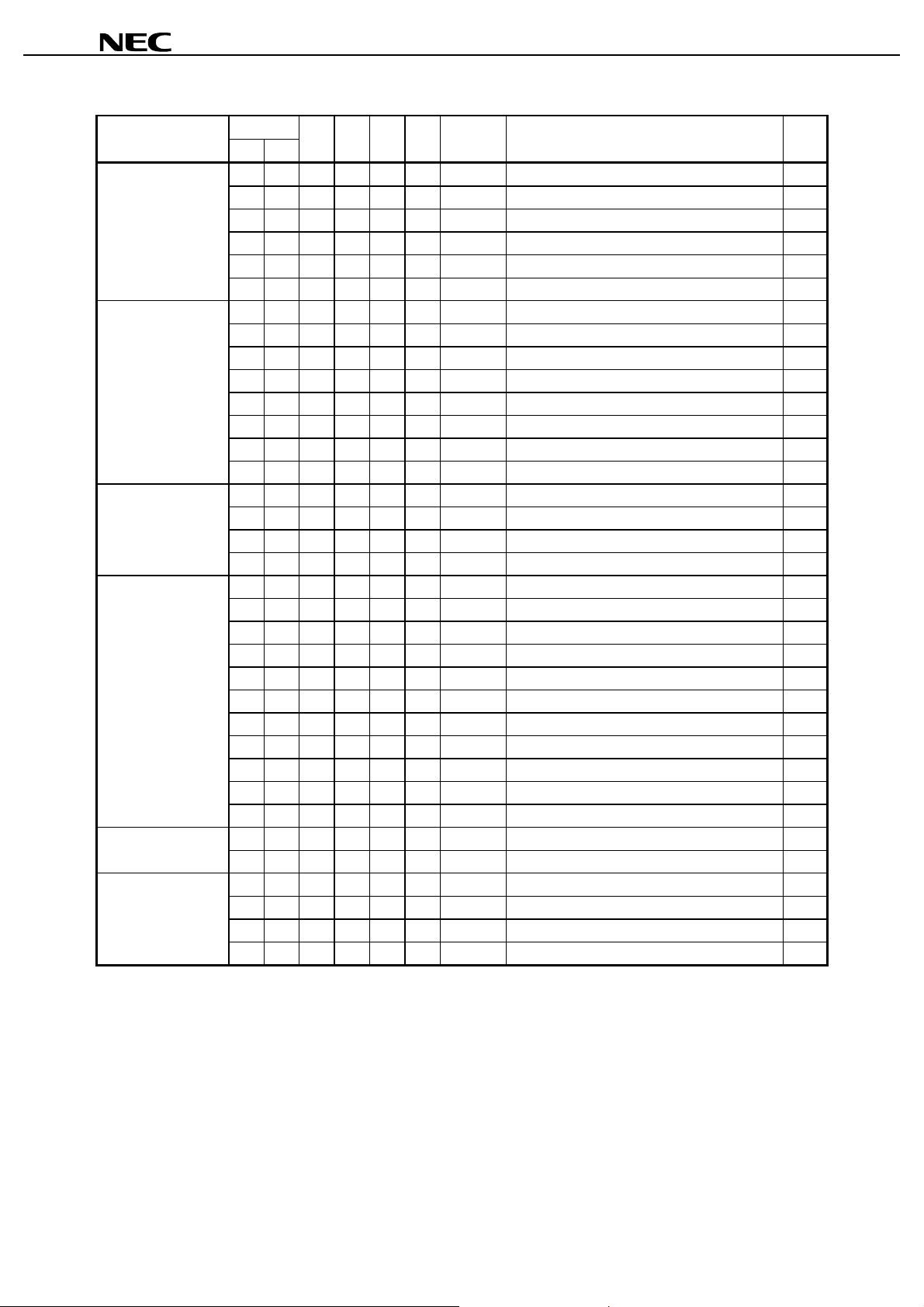

4.5 Command Truth Table for CKE

Current State CKE /CS /RAS /CAS /WE Address A ction Notes

n – 1 n

Self refresh H

Self refresh recovery H H H

Power down H

All banks idle H H H

Row active H

Any state other than H H

listed above H L

ЧЧЧЧЧЧ

LHH

LHLHH

LHLHL

LHLL

LL

HHLHH

HHLHL

HHLL

HLH

HLLHH

HLLHL

HLLL

ЧЧЧЧЧ

LHH

LHLHHH

LL

HHLH

HHLLH

HHLLLH

H H L L L L Op-Code Refer to operations in Operative Command Table

HLH

HLLH

HLLLH

HLLLLH

HLLLLLOp-CodeRefer to operations in Operative Command Table

L

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

L

ЧЧЧЧЧЧ

LH

LL

××××

××

××

×××

ЧЧЧЧЧ

××××

××

××

×××

××××

××

××

×××

××××

×

ЧЧЧЧЧ

×××

××

×

×

×××

××

×

×

ЧЧЧЧ

ЧЧЧЧЧ

ЧЧЧЧЧ

ЧЧЧЧЧ

INVALID, CLK (n – 1) would exit self refres h

Self refresh recovery

Self refresh recovery

ILLEGAL

ILLEGAL

Maintain self refresh

Idle after t

Idle after t

ILLEGAL

ILLEGAL

ILLEGAL

ILLEGAL

ILLEGAL

ILLEGAL

INVALID, CLK (n – 1) would exit power down

EXIT power down → Idle

EXIT power down → Idle

Maintain power down mode

Refer to operations in Operative Command Table

Refer to operations in Operative Command Table

Refer to operations in Operative Command Table

CBR (auto) Refresh

Refer to operations in Operative Command Table

Refer to operations in Operative Command Table

Refer to operations in Operative Command Table

Self refresh 1

Power down 1

Refer to operations in Operative Command Table

Power down 1

Refer to operations in Operative Command Table

Begin clock suspend next cyc l e 2

Exit clock suspend next cycl e

Maintain clock suspend

RC

RC

Notes 1.

Remark

Self refresh can be entered only from the all banks idle state. Power down can be entered only from all

banks idle or row active state.

2.

Must be legal command as defined in Operative Command Table.

H = High level, L = Low level, × = High or Low level (Don't care)

Data Sheet M12650EJBV0DS00

19

µµµµ

PD45128441, 45128841, 45128163

5. Initialization

The synchronous DRAM is initialized in the power-on sequence according to the following.

(1) To stabilize internal circuits, when power is applied, a 100

(2) After the pause, all banks must be precharged using the Precharge command (The Precharge all banks

command is convenient).

(3) Once the precharge is completed and the minimum t

RSC

After the mode register set cycle, t

(4) Two or more CBR (Auto) refresh must be performed.

Remarks 1.

The sequence of Mode register programming and Refresh above may be transposed.

2.

CKE and DQM must be held high until the Precharge command is issued to ensure data-bus Hi-Z.

(2 CLK minimum) pause must be satisfied as well.

s or longer pause must precede any signal toggling.

µ

RP

is satisfied, the mode register can be programmed.

20

Data Sheet M12650EJBV0DS00

µµµµ

PD45128441, 45128841, 45128163

6. Programming the Mode Register

The mode register is programmed by the Mode register set command using address bits A11 through A0, BA0(A13)

and BA1(A12) as data inputs. The register retains data until it is reprogrammed or the device loses power.

The mode register has four fields;

Options : A11 through A7, BA0(A13), BA1(A12)

/CAS latency : A6 through A4

Wrap type : A3

Burst length : A2 through A0

Following mode register programming, no command can be issued before at least 2 CLK have elapsed.

/CAS Latency

/CAS latency is the most critical of the parameters being set. It tells the device how many clocks must elapse

before the data will be available.

The value is determined by the frequency of the clock and the speed grade of the device.

between Frequency and Latency

the device.

shows the relationship of /CAS latency to the clock period and the speed grade of

13.3 Relationship

Burst Length

Burst Length is the number of words that will be output or input in a read or write cycle. After a read burst is

completed, the output bus will become Hi-Z.

The burst length is programmable as 1, 2, 4, 8 or full page.

Wrap Type (Burst Sequence)

The wrap type specifies the order in which the burst data will be addressed. This order is programmable as either

“Sequential” or “Interleave”. The method chosen will depend on the type of CPU in the system.

Some microprocessor cache systems are optimized for sequential addressing and others for interleaved

addressing.

Both sequences support bursts of 1, 2, 4 and 8. Additionally, sequence supports the full page length.

7.1 Burst Length and Sequence

shows the addressing sequence for each burst length using them.

Data Sheet M12650EJBV0DS00

21

7. Mode Register

BA1

BA0

(A12)

(A13)

00

BA1

BA0

(A12)

(A13)

xx

BA1

BA0

(A12)

(A13)

BA1

BA0

(A12)

(A13)

xx

BA1

BA0

(A12)

(A13)

00

µµµµ

PD45128441, 45128841, 45128163

A0A1A2A3A4A5A7 A6A8A9A10A11

10000 JEDEC Standard Test Set (refresh counter test)

A0A1A2A3A4A5A7 A6A8A9A10A11

BLWTLTMODE001xx Burst Read and Single Write

01 Use in future

BLWTLTMODE00000 Mode Register Set

(for Write Through Cache)

A0A1A2A3A4A5A7 A6A8A9A10A11

A0A1A2A3A4A5A7 A6A8A9A10A11

VVVVVV1V1xxx Vender Specific

A0A1A2A3A4A5A7 A6A8A9A10A11

V = Valid

x = Don’t care

Burst length

Wrap type

Latency

Remark R : Reserved

Mode Register Set Timing

mode

Bits2-0

000

001

010

011

100

101

110

111

0

1

Full page

Sequential

Interleave

Bits6-4

000

001

010

011

100

101

110

111

WT = 0

1

2

4

8

R

R

R

/CAS latency

WT = 1

1

2

4

8

R

R

R

R

R

R

2

3

R

R

R

R

22

CLK

CKE

/CS

/RAS

/CAS

/WE

A0 - A11,

BA0(13), BA1(A12)

Mode Register Set

Data Sheet M12650EJBV0DS00

7.1 Burst Length and Sequence

[Burst of Two]

Starting address

(column address A0, binary)

0 0, 1 0, 1

1 1, 0 1, 0

[Burst of Four]

Starting address

(column address A1 - A 0, binary)

00 0, 1, 2, 3 0, 1, 2, 3

01 1, 2, 3, 0 1, 0, 3, 2

10 2, 3, 0, 1 2, 3, 0, 1

11 3, 0, 1, 2 3, 2, 1, 0

µµµµ

Sequential addressing sequence

(decimal)

Sequential addressing sequence

(decimal)

PD45128441, 45128841, 45128163

Interleave addressing sequence

(decimal)

Interleave addressing sequence

(decimal)

[Burst of Eight]

Starting address

(column address A2 - A 0, binary)

000 0, 1, 2, 3, 4, 5, 6, 7 0, 1, 2, 3, 4, 5, 6, 7

001 1, 2, 3, 4, 5, 6, 7, 0 1, 0, 3, 2, 5, 4, 7, 6

010 2, 3, 4, 5, 6, 7, 0, 1 2, 3, 0, 1, 6, 7, 4, 5

011 3, 4, 5, 6, 7, 0, 1, 2 3, 2, 1, 0, 7, 6, 5, 4

100 4, 5, 6, 7, 0, 1, 2, 3 4, 5, 6, 7, 0, 1, 2, 3

101 5, 6, 7, 0, 1, 2, 3, 4 5, 4, 7, 6, 1, 0, 3, 2

110 6, 7, 0, 1, 2, 3, 4, 5 6, 7, 4, 5, 2, 3, 0, 1

111 7, 0, 1, 2, 3, 4, 5, 6 7, 6, 5, 4, 3, 2, 1, 0

Sequential addressing sequence

(decimal)

Interleave addressing sequence

(decimal)

Full page burst is an extension of the above tables of sequential addressing, with the length being 2,048 (for 32M ×4

device), 1,024 (for 16M ×8 device), and 512 (for 8M ×16 device).

Data Sheet M12650EJBV0DS00

23

8. Address Bits of Bank-Select and Precharge

(Activate command)

(Precharge command)

(/CAS strobes)

µµµµ

PD45128441, 45128841, 45128163

BA1

(A12)

BA1

(A12)

BA1

(A12)

BA0

(A13)

BA0

(A13)

BA0

(A13)

A11A10A9A8A7A6A4 A5A3A2A1A0Row

A11A10A9A8A7A6A4 A5A3A2A1A0

xA10A9A8A7A6A4 A5A3A2A1A0Col.

BA1(A12) BA0(A13)

0

0

1

0

1

0

1

1

BA1(A12) BA0(A13)

A10

0

0

0

0

0

1

0

1

1

x

x : Don’t care

disables Auto-Precharge

0

(End of Burst)

enables Auto-Precharge

1

(End of Burst)

Result

Select Bank A

“Activate” command

Select Bank B

“Activate” command

Select Bank C

“Activate” command

Select Bank D

“Activate” command

Result

Precharge Bank A

0

Precharge Bank B

1

Precharge Bank C

0

Precharge Bank D

1

Precharge All Banks

x

BA1(A12) BA0(A13)

0

0

1

0

1

0

1

1

Result

enables Read/Write

commands for Bank A

enables Read/Write

commands for Bank B

enables Read/Write

commands for Bank C

enables Read/Write

commands for Bank D

24

Data Sheet M12650EJBV0DS00

9. Precharge

µµµµ

PD45128441, 45128841, 45128163

The precharge command can be issued anytime after t

RAS (MIN.)

is satisfied.

Soon after the precharge command is issued, precharge operation performed and the synchronous DRAM enters

RP

the idle state after t

is satisfied. The parameter tRP is the time required to perform the precharge.

The earliest timing in a read cycle that a precharge command can be issued without losing any data in the burst is

as follows.

It is depending on the /CAS latency and clock cycle time.

Burst length=4

/CAS latency = 2

Command

/CAS latency = 3

Command

CLK

DQ

DQ

T0 T1 T2 T3 T4 T5 T6 T7

READ

Q1 Q2 Q3 Q4

READ

Q1 Q2 Q3 Q4

PRE

PRE

T8

Hi-Z

Hi-Z

RAS must be satisfied)

(t

In order to write all data to the memory cell correctly, the asynchronous parameter “t

(MIN.)

specification defines the earliest time that a precharge command can be issued. Minimum number of clocks is

DPL (MIN.)

calculated by dividing t

with clock cycle time.

DPL

” must be satisfied. The t

In summary, the precharge command can be issued relative to reference clock that indicates the last data word is

valid. In the following table, minus means clocks before the reference; plus means time after the reference.

/CAS latency Read Write

2–1+t

3–2+t

DPL (MIN.)

DPL (MIN.)

DPL

Data Sheet M12650EJBV0DS00

25

µµµµ

PD45128441, 45128841, 45128163

10. Auto Precharge

During a read or write command cycle, A10 controls whether auto precharge is selected. A10 high in the Read or

Write command (Read with Auto precharge command or W rite with Auto precharge command), auto precharge is

selected and begins automatically.

RAS

The t

next activate command to the bank being precharged cannot be executed until the precharge cycle ends.

In read cycle, once auto precharge has started, an activate command to the bank can be issued after t

satisfied.

In write cycle, the t

The timing that begins the auto precharge cycle depends on both the /CAS latency programmed into the mode

register and whether read or write cycle.

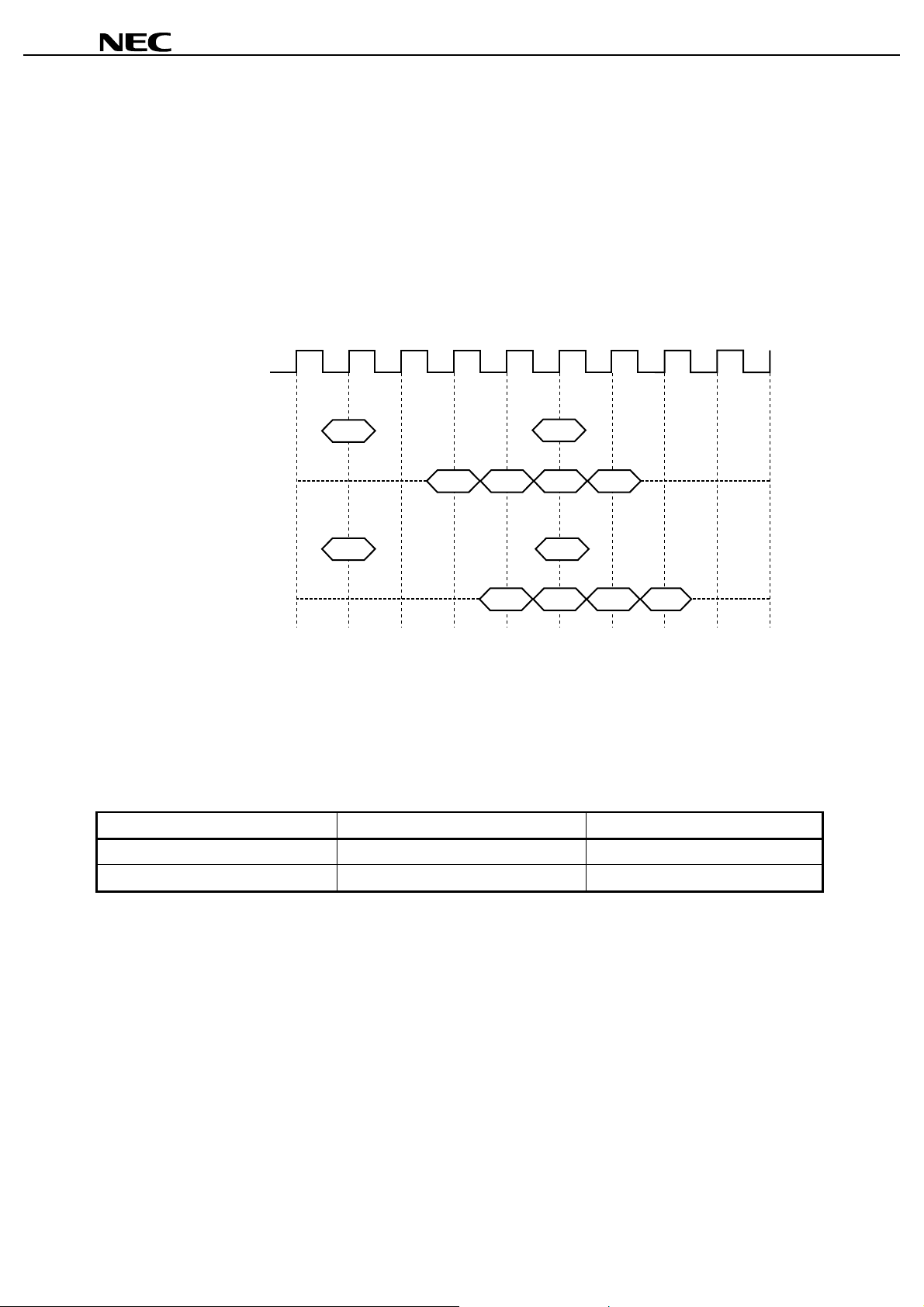

10.1 Read with Auto Precharge

During a read cycle, the auto precharge begins one clock earlier (/CAS latency of 2) or two clocks earlier (/CAS

latency of 3) the last data word output.

must be satisfied with a read with auto precharge or a write with auto precharge operation. In addition, the

RP

has been

DAL

must be satisfied to issue the next activate command to the bank being precharged.

CLK

/CAS latency = 2

Command

DQ

/CAS latency = 3

Command

DQ

T0 T2T1 T3 T4 T5 T6 T7 T8

READA B

QB1 QB2 QB3 QB4

READA B

Auto precharge starts

Auto precharge starts

QB1 QB2 QB3 QB4

RAS

(t

Burst length = 4

T9

Hi-Z

Hi-Z

must be satisfied)

Remark

26

READA means Read with Auto precharge

Data Sheet M12650EJBV0DS00

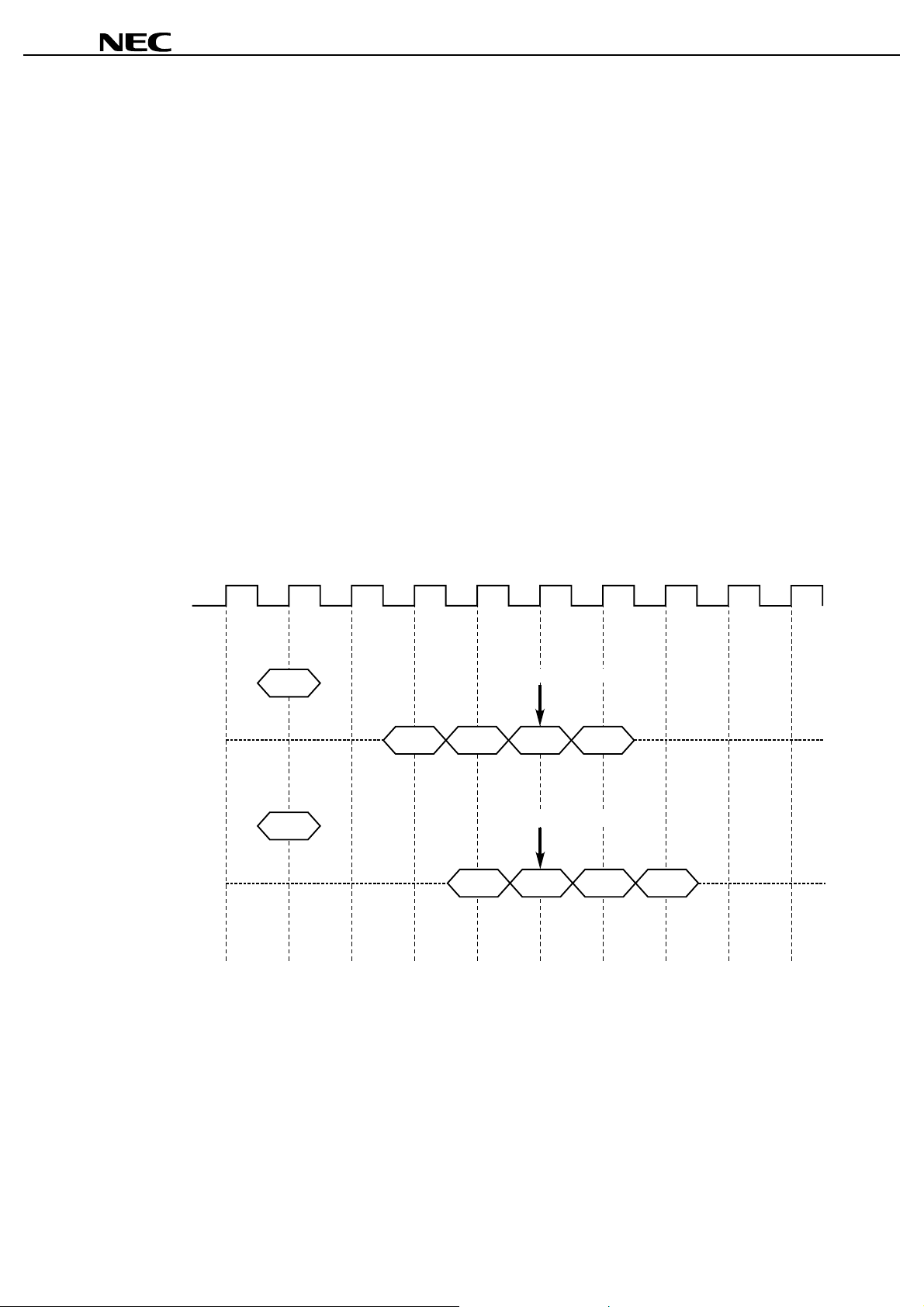

10.2 Write with Auto Precharge

µµµµ

PD45128441, 45128841, 45128163

During a write cycle, the auto precharge starts at the timing that is equal to the value of the t

data word input to the device.

T0 T2T1 T3 T4 T5 T6 T7 T8

CLK

/CAS latency = 2

Command

DQ

/CAS latency = 3

Command

DQ

WRITA B

DB1 DB2 DB3 DB4

WRITA B

DB1 DB2 DB3 DB4

Auto precharge starts

t

DPL(MIN.)

Auto precharge starts

t

DPL(MIN.)

DPL (MIN.)

Hi-Z

Hi-Z

after the last

Burst length = 4

(t

RAS

must be satisfied)

Remark

WRITA means Write with Auto Precharge

In summary, the auto precharge begins relative to a reference clock that indicates the last data word is valid.

In the table below, minus means clocks before the reference; plus means after the reference.

/CAS latency Read Write

2–1+t

3–2+t

DPL (MIN.)

DPL (MIN.)

Data Sheet M12650EJBV0DS00

27

µµµµ

PD45128441, 45128841, 45128163

11. Read / Write Command Interval

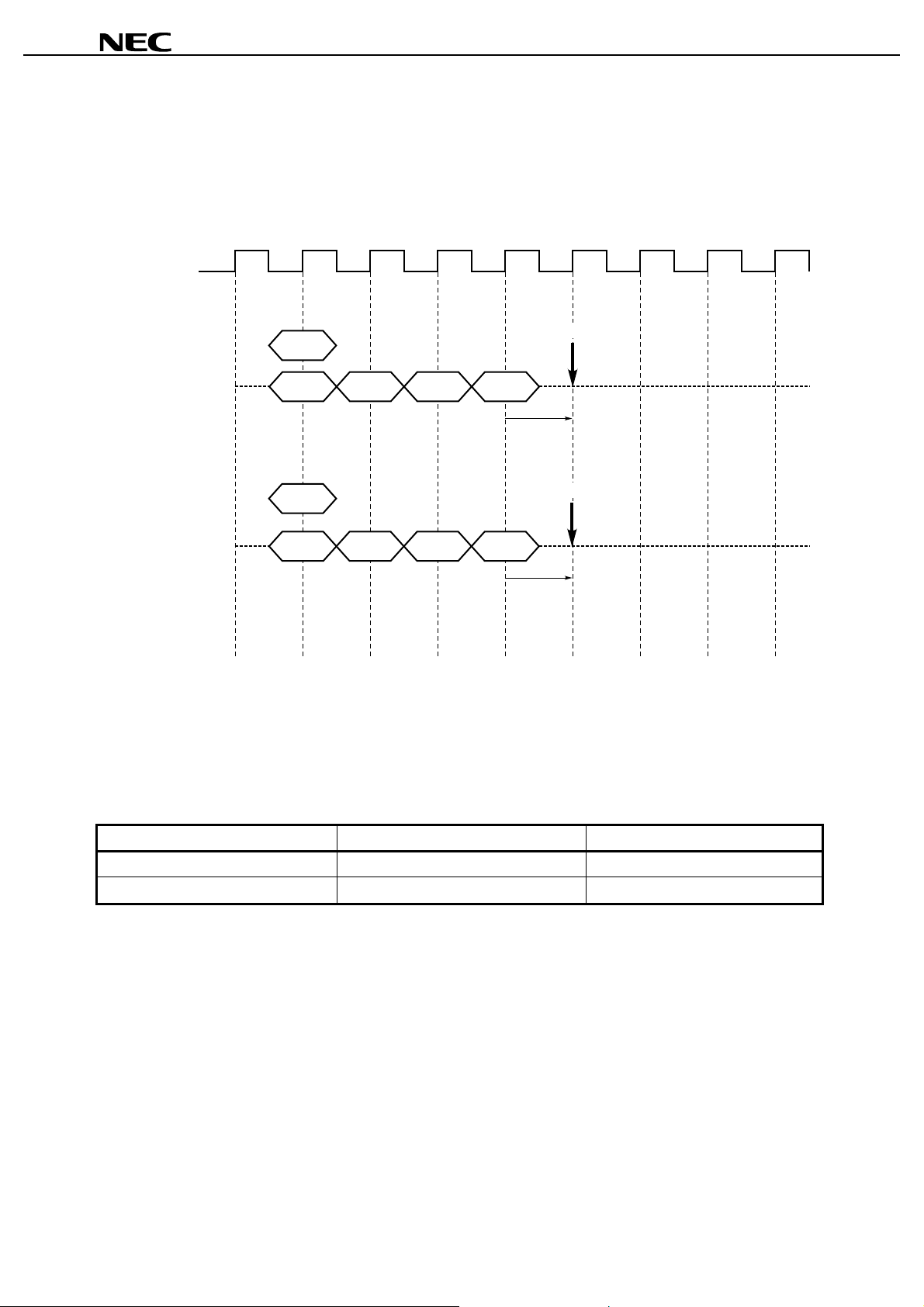

11.1 Read to Read Command Interval

During a read cycle, when new Read command is issued, it will be effective after /CAS latency, even if the previous

read operation does not completed. READ will be interrupted by another READ.

The interval between the commands is 1 cycle minimum. Each Read command can be issued in every clock

without any restriction.

Burst length = 4, /CAS latency = 2

T0 T2T1 T3 T4 T5 T6 T7 T8

CLK

T9

Command

DQ

READ A

1cycle

READ B

QA1

QB1 QB2 QB3 QB4

Hi-Z

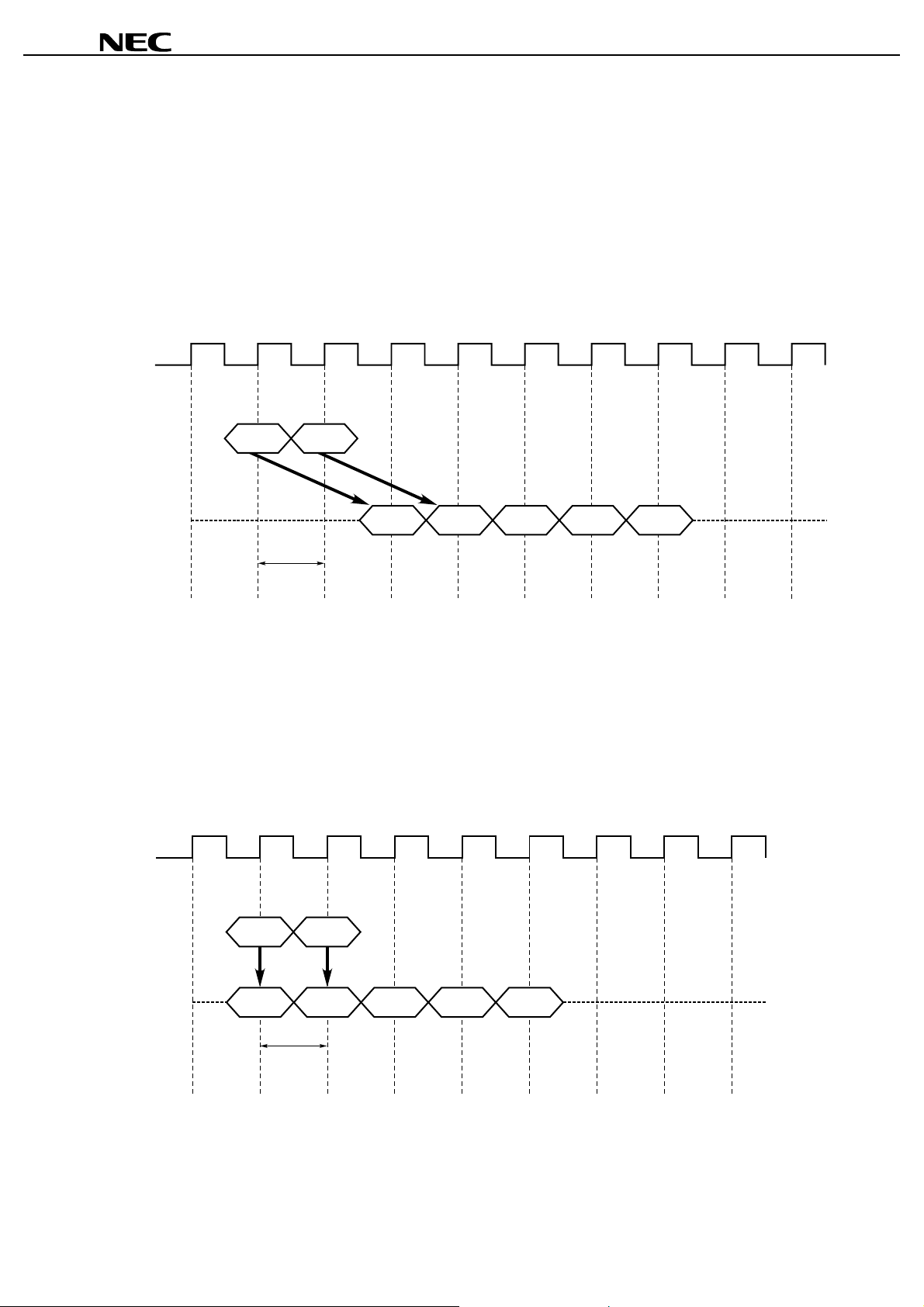

11.2 Write to Write Command Interval

During a write cycle, when a new Write command is issued, the previous burst will terminate and the new burst will

begin with a new Write command. WRITE will be interrupted by another W RITE.

The interval between the commands is minimum 1 cycle. Each Write command can be issued in every clock

without any restriction.

Burst length = 4, /CAS latency = 2

T0 T2T1 T3 T4 T5 T6 T7 T8

CLK

Command

DQ

28

WRITE A

DA1

WRITE B

DB1 DB2 DB3 DB4

1cycle

Data Sheet M12650EJBV0DS00

Hi-Z

Loading...

Loading...