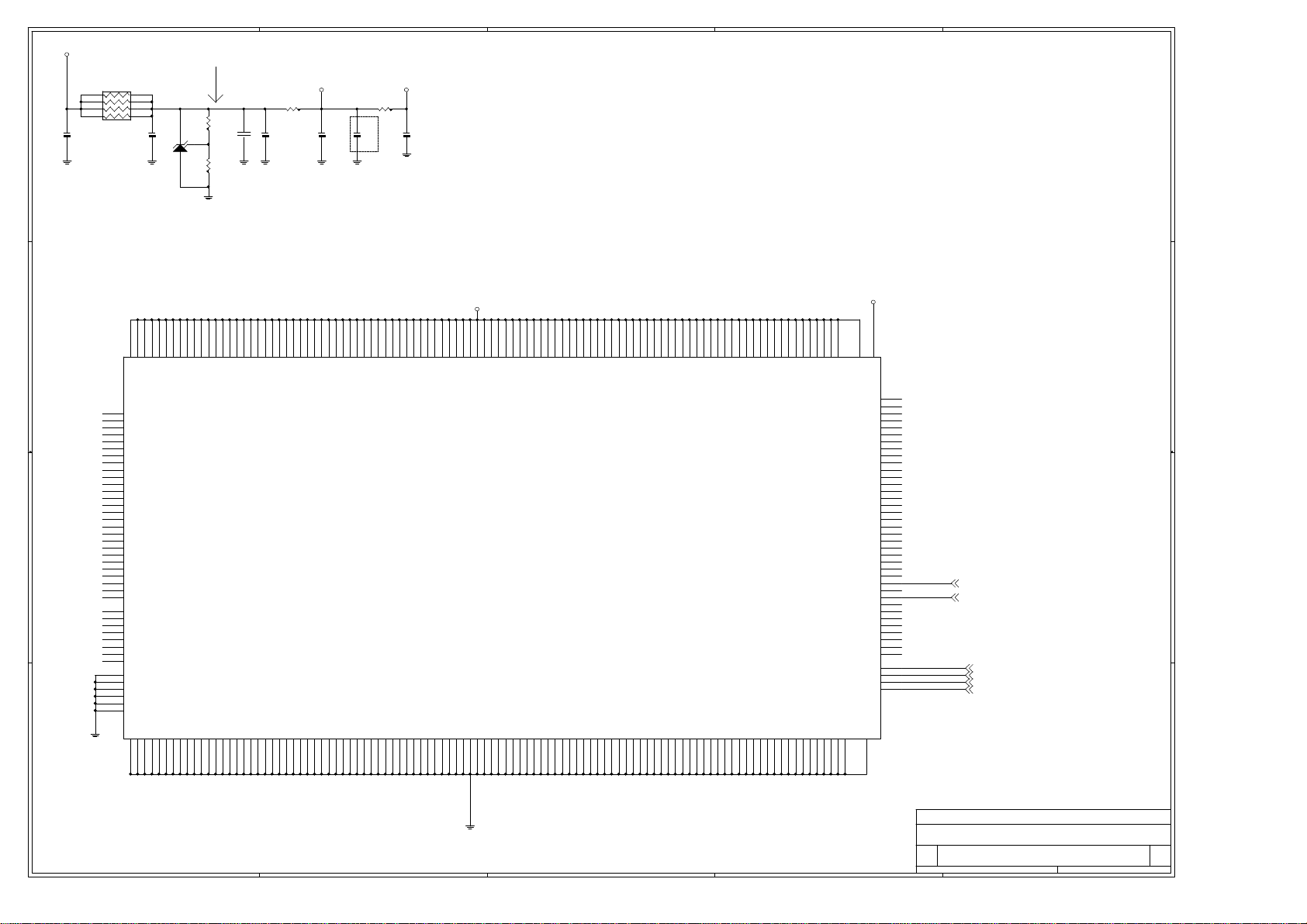

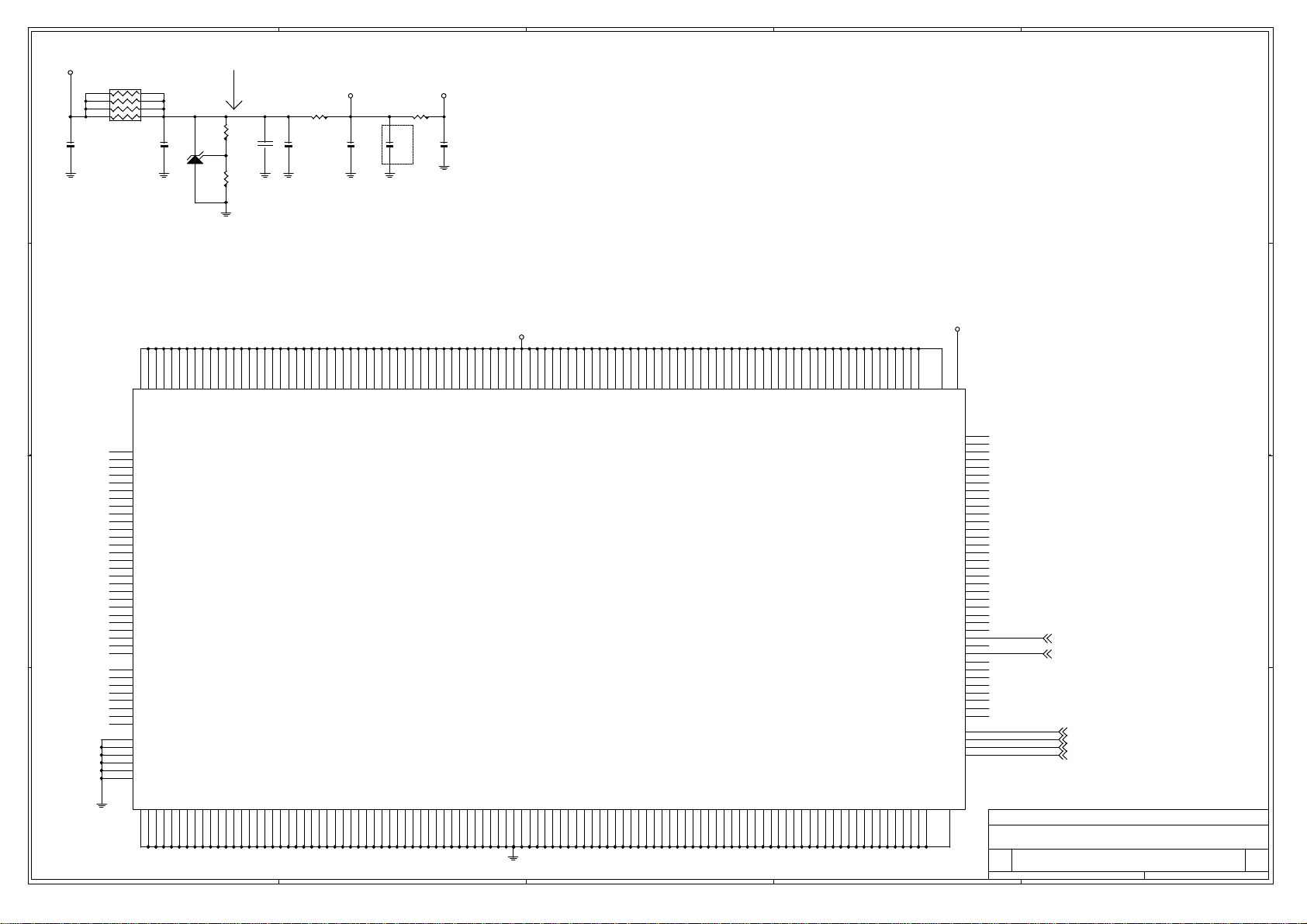

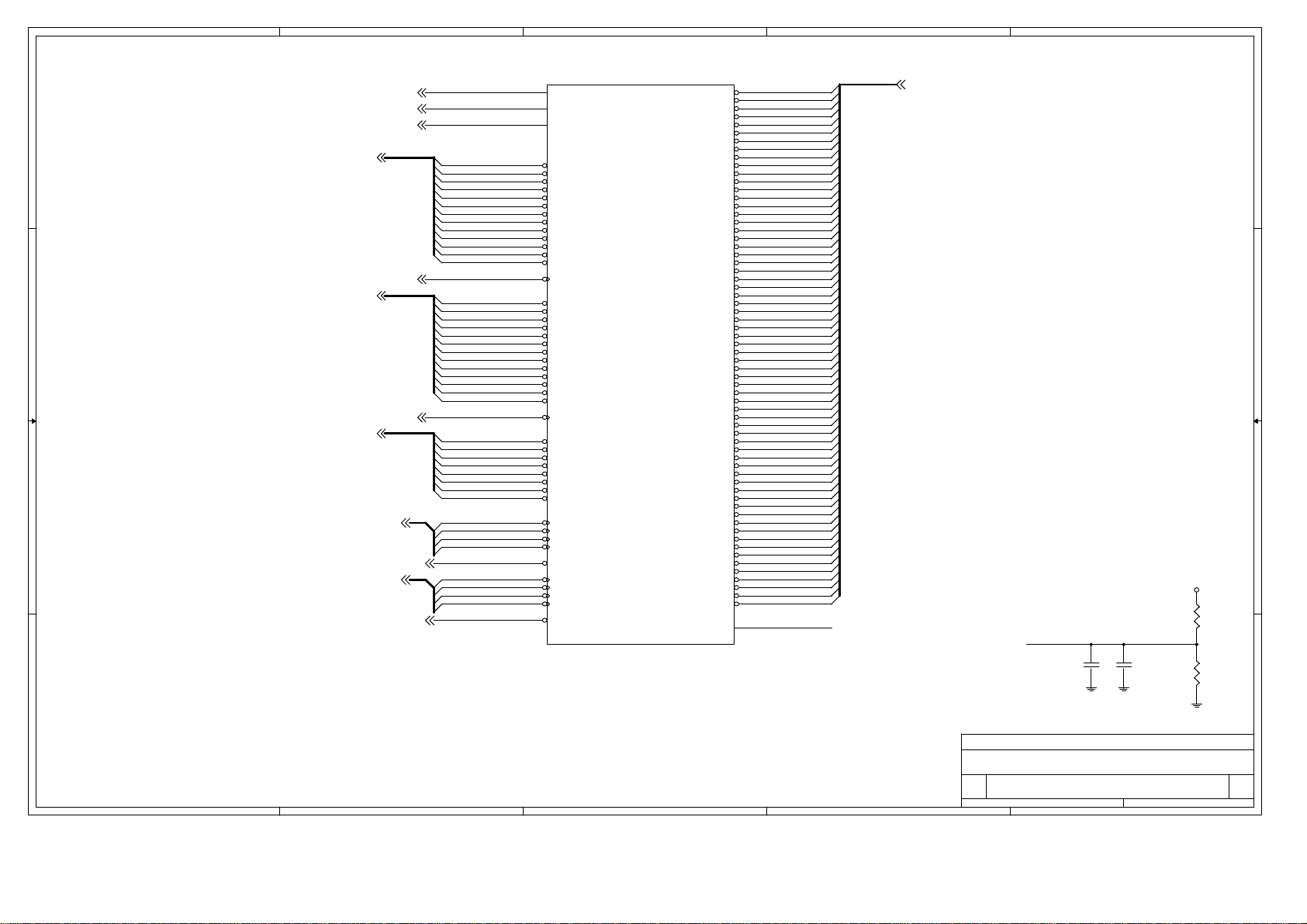

MSI MS-6501 Schematics

1

Cover Sheet

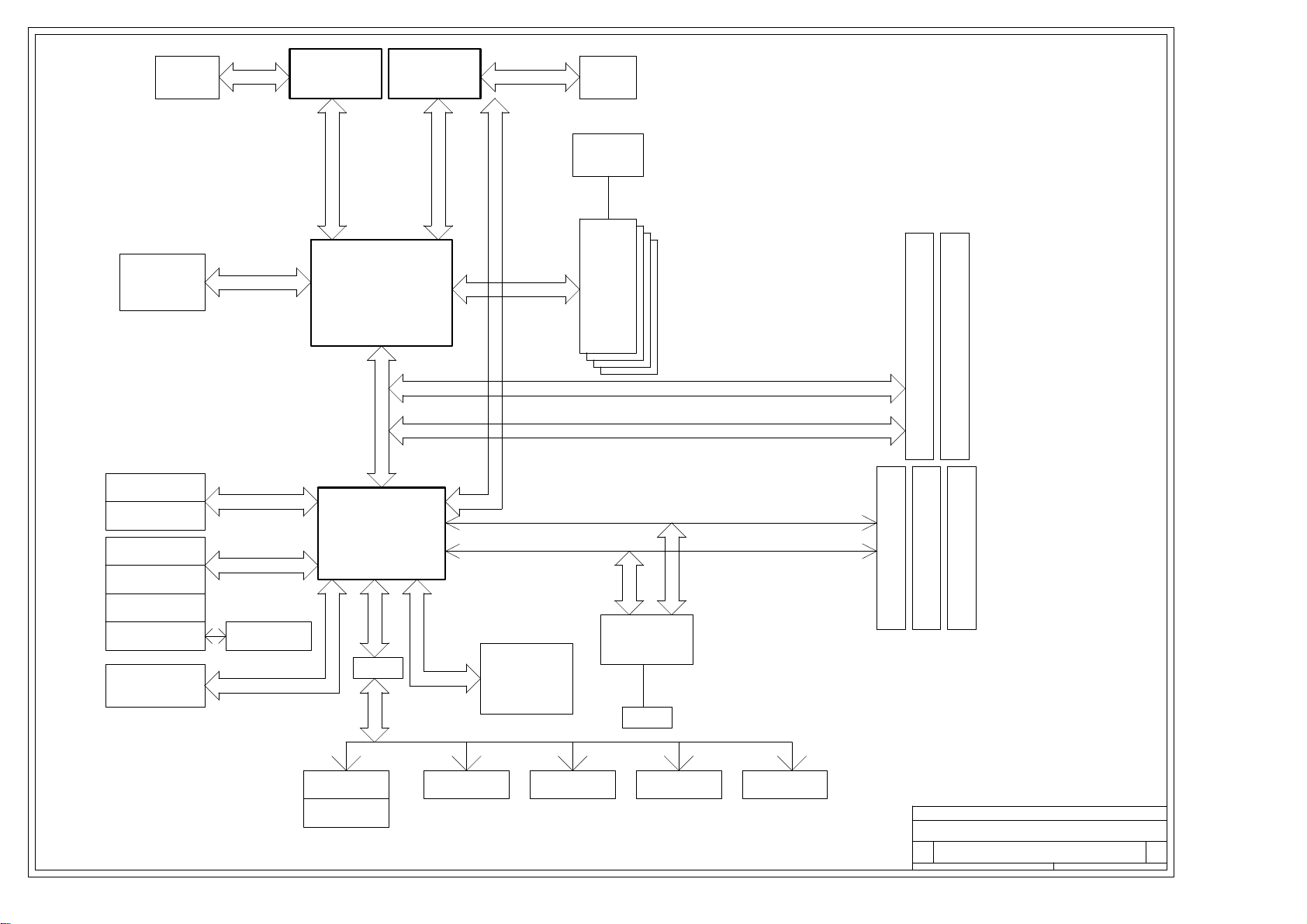

Block Diagram

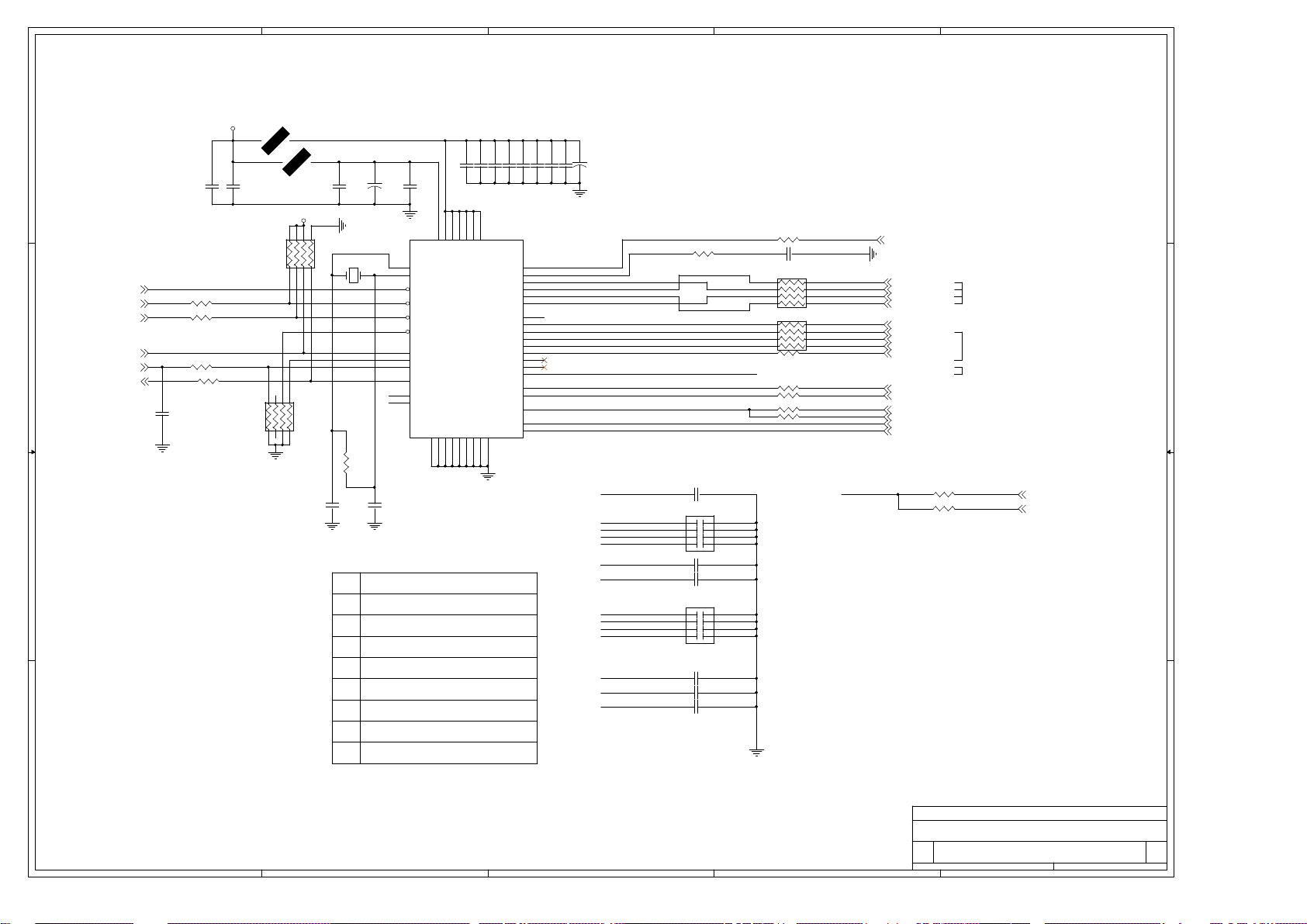

Clock Synthesizer

AMD 762--------North Bridge

DDR DIMM-184

AGP 4X SLOT

PCI Connectors

1

2

3

4,5,6,7PGA462 Socket A CPU0/CPU1

8,9,10,11,12

13,14

15

16,17,18,19

MS-6501 ATX

Last Update xx/xx/2000

CPU:

Version

0A

Dual AMD Socket-462 Processors

20,21AMD 768--------South Bridge

LPC SuperI/O

ATA66/100 Connectors

Parallel / Serial Port

Keyboard & Mouse

22

23

24

25

System Chipset:

AMD 762(North Bridge)

AMD 768 (South Bridge)

BIOS & FANs 26

A A

Front Panel

USB Conector

AC'97 Codec

Audio/Game Port

DDR Regulator & STR LDO

27

28

29

30

31

Expansion Slots:

AGP-Pro SLOT * 1

PCI2.2 PCI/64/66 SLOT * 2

PCI2.2 PCI/32/33 SLOT * 3

LAN

MS-3

VRM

DDR Terminator

IGD4 PCI Strappings

OPUS PCI Strappings

Bypass Capacitors

32

33

34

35

36

37

38

39Mounting Hole

On Board:

LAN 82559ER

AC97 Codec

PC 2 PC

1

Title

Size Document Number Rev

Custom

Date: Sheet of

MICRO-STAR

Cover Sheet

MS-6501

1 39Tuesday, July 17, 2001

0A

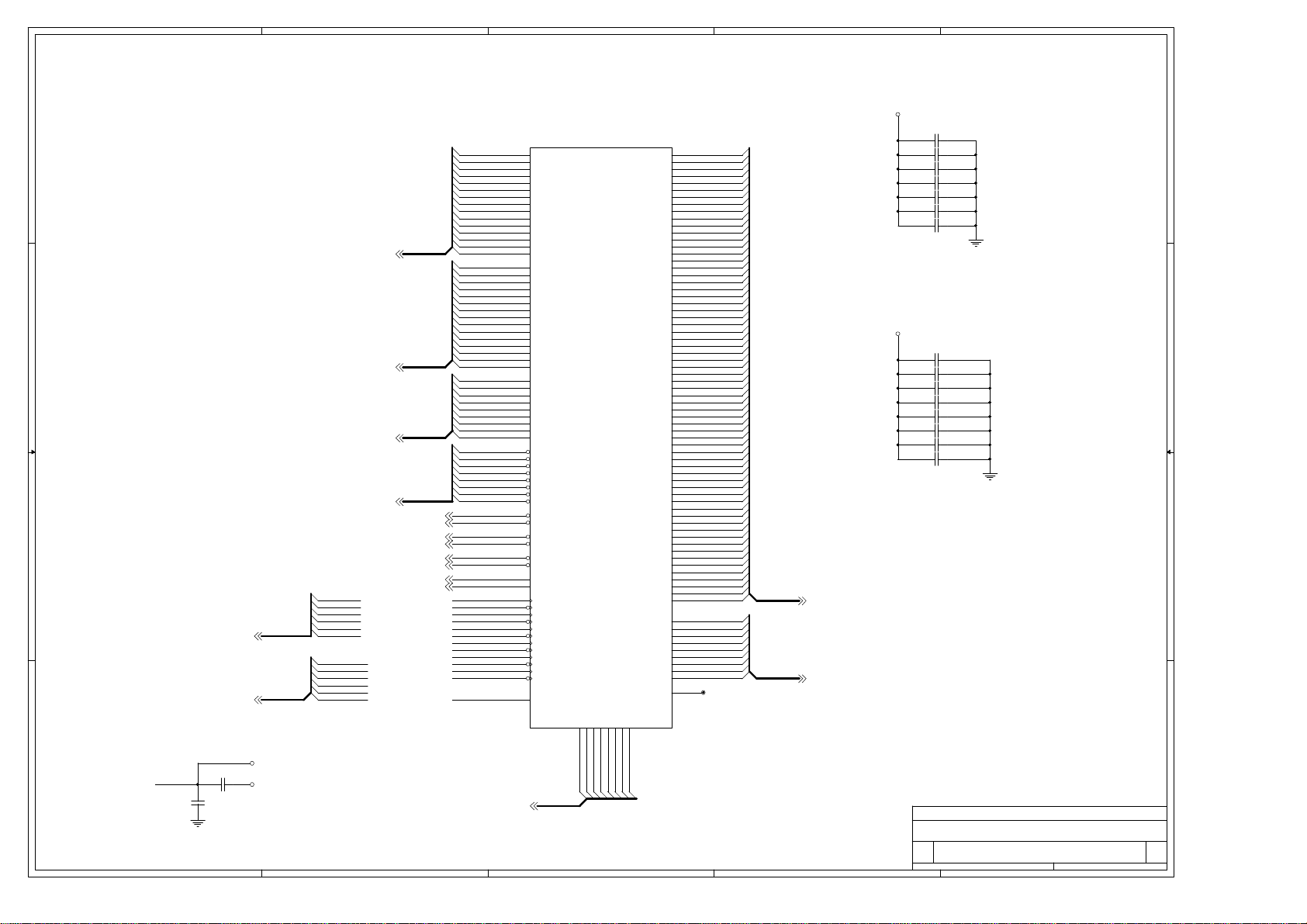

1

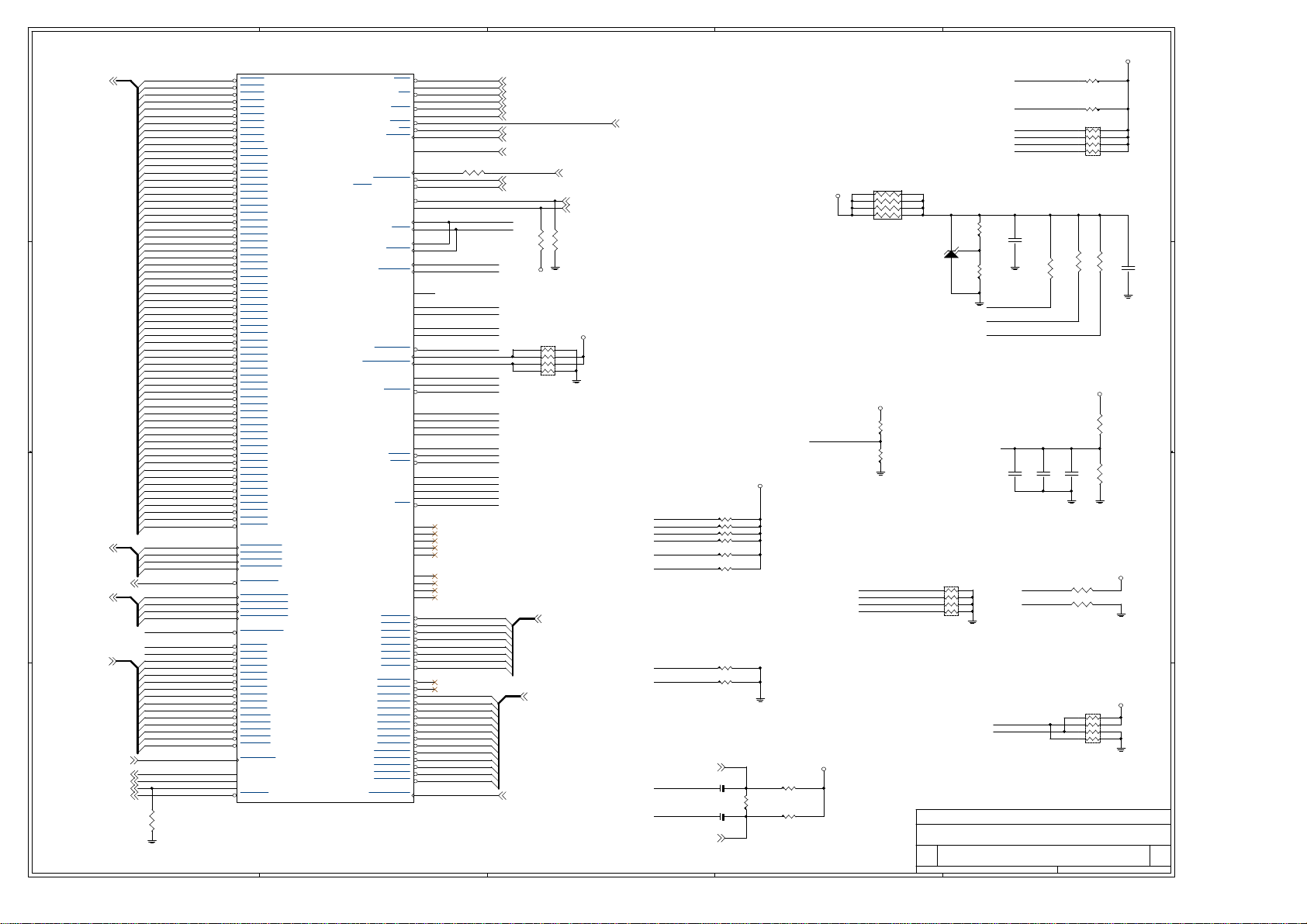

K7 462-Pin

VRM Clock

AGP PRO

2X/4X

A A

UltraDMA

IDE Primary

33/66/100

Socket

Processor

AMD SYSTEM BUS

AMD762

North Bridge

K7 462-Pin

Socket

Processor

AMD SYSTEM BUS

VTT 1.25V

Regulator

4

Register

DDR

DIMM

Modules

PCI CNTRL

PCI ADDR/DATA

Block Diagram

PCI Conn 1

PCI Conn 2

IDE Secondary

USB Port 1

USB Port 2

USB Port 3

USB Port 4

Onboard

AC'97 Codec

USB

PC 2 PC

AC'97

Link

AMD 768

South

Bridge

LPC

Super I/O

Keyboard SerialParallel

Mouse

Bus

BIOS

INTEL

82559ER

LAN

10/100Mbps

Conn.

1

PCI CNTRL

PCI ADDR/DATA

PCI Conn 3

PCI Conn 4

PCI Conn 5

Game ConnFloopy

Title

Size Document Number Rev

Custom

Date: Sheet of

MICRO-STAR

Block Diagram

MS-6501

2 39Tuesday, July 17, 2001

0A

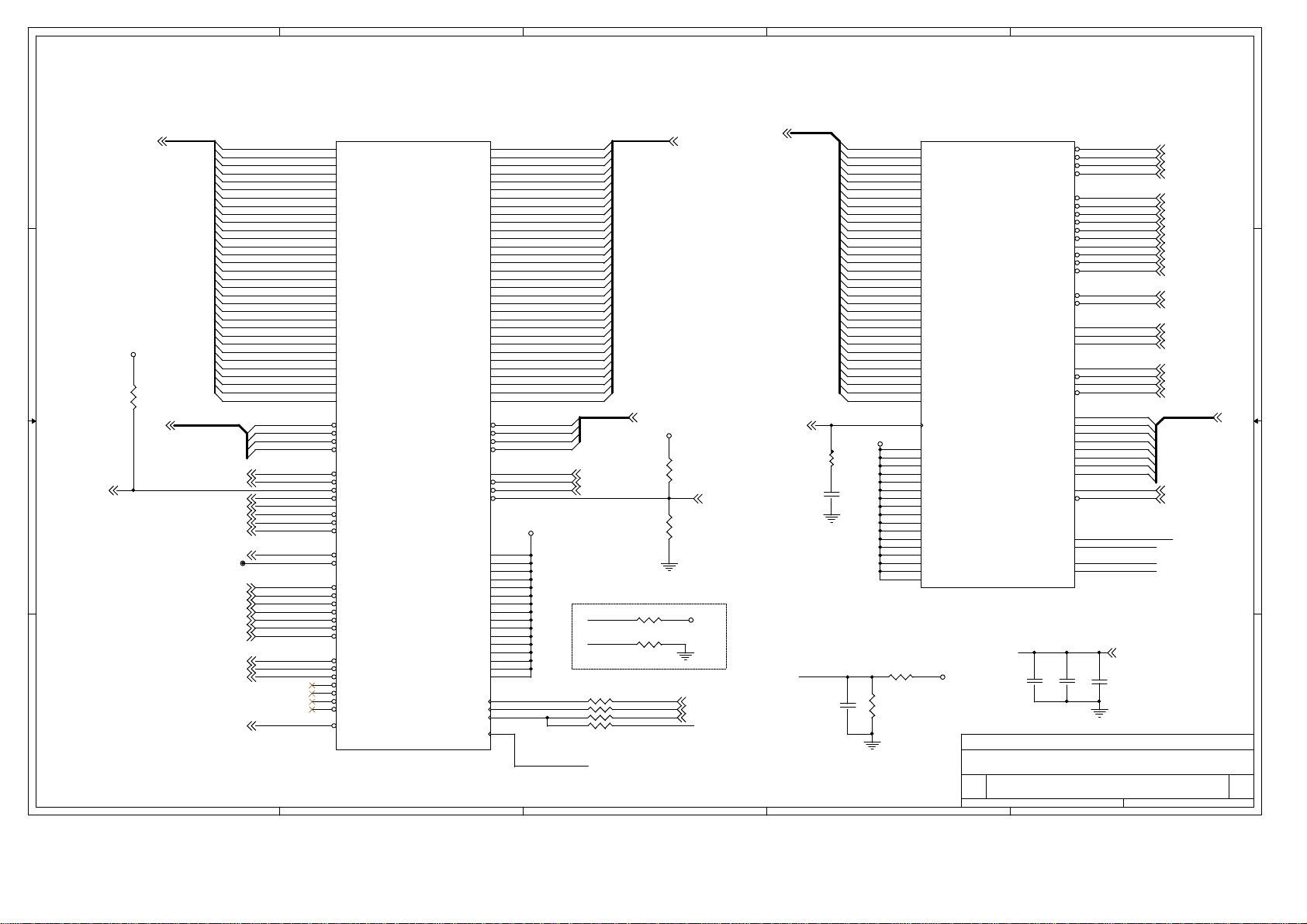

5

* 25 mils Trace on Layer 6

with GND copper around it

* Put close to every power pin

VCC3

D D

C376

0.01u

PCISTP-<21>

CPUSTOP-<21>

FP_RST-<27,33>

C C

100/133-<33,36>

SIO_CLK48<22>

OSC<21>

R335 22-REV

R340 22-REV

R295 22

R616 22

C326

10p

FB16

80-0805

C371

0.01u

FB15

80-0805

1 2

VCC3

RN77

10K

1 2

3 4

5 6

7 8

RN68

10K

3 4

5 6

7 8

4

+

C354

0.01u

10u

Y3

14M-16pf-HC49S-D

R298

1M-REV

EC42

4

X1

5

X2

32

PCI_STOP_L

31

CPU_STOP_L

30

PD_L

29

SPREAD_L

28

FS2

2

FS1

1

FS0

24

24MHZ/48MHZ#

35

RSVD2

44

RSVD1

C358

330p

3422189154845

GND

6

VDD

GND

12

VDDSD

VDDREF

GND

GND

21253

C337330p

VDDAGP

VDDPCI1

VDDPCI2

GND

GND

GND

333841

C5380.01u

C339330p

VDD48

CPUCLKT2

CPUCLKC2

CPUCLKT1

CPUCLKC1

CPUCLKT0

CPUCLKC0

SDRAM_OUT

PCICLK6

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK1

PCICLK0

PCICLK_F0

SDATA

GND

GND

ICS 9248-153

47

AGP1

AGP0

USB0

SCLK

C5330.01u

U24

C5290.01u

3

2

1

Clock Synthesizer

10u

EC44

+

C5370.01u

C3730.01u

C3720.01u

CPUCLKT2

42

CPUCLKC2

43

CPUCLKT1

39

CPUCLKC1

40

CPUCLKT0

36

CPUCLKC0

37

46

17

16

14

13

11

10

8

7

20

19

23

26

27

PCICLK6

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK_FB

AGP1

AGP0

USB0

R435 33 C564 0.01u

R302 0

RN72 10

1 2

3 4

5 6

7 8

RN75 22

1 2

3 4

5 6

7 8

R671 22

R333 22

R332 22

R336 10

R488 10

CPUCLK2 <8>

CPUCLK-1 <6>

CPUCLK1 <6>

CPUCLK-0 <4>

CPUCLK0 <4>

LANCLK <32>

PCLK5 <19>

PCLK4 <18>

PCLK3 <18>

PCLK2 <26>

GCLK1 <15>

GCLK0 <11>

USBCLK <21>

PC2PCCLK <28>

SMBCLK <13,14,21,22,33>

SMBDATA <13,14,21,22,33>

Length = X"

Length = X" - 1"

Length = X"

Length = X" - 2.5"

Length = X"

Length = X"

Length = X" - 4.5"

(5 mil trace / 20 mil clearance)

(20/5/5/5/20)

(5 mil trace / 20 mil clearance)

(5 mil trace / 20 mil clearance)

(5 mil trace / 20 mil clearance)

(5 mil trace / 20 mil clearance)

(5 mil trace / 20 mil clearance)

C336

C335

22p

22p

NOPOP

NOPOP

B B

WIDTH/SPACE LENGTH

CPUCLK0&CPUCLK0#:

CPUCLK1&CPUCLK1#:

CPUCLK2&GCLK0 X

GCLK1 X-4.5

NBCLK&SBCLK

PCICLK GROUP X-2.5

* X MEANS THE SHORTEST LENGTH FOR MAINTAIN

PROPAGATION DELAY

* CPUCLK1'S TERMINATION CKT MUST BE PLACED

NEAR TO NB

A A

5/20 5 FOR DIFF. PAIR X-1 INCH

5/20 5 FOR DIFF. PAIR X-1 INCH

5/20

5/20

5/20

X

5/20

5

FS2 FS1

0

0

0

0

1

1

1

000

1

1 1

0

0

1 1

4

*Put GND copper under Clock Gen.

connect to every GND pin

CPU

SDRAM

PCI AGP

FS0

133.3 33.3 66.7

1

95.0

31.67

0

100.99

33.66

115.0

38.33

0

100.7

33.57

1

103.0

34.33

105.0 35.0011 0 60.0

110.0

36.67

63.33

67.33

76.67

67.13

66.6

66.6

CPUCLKT2

CPUCLKC1

CPUCLKT1

CPUCLKC0

CPUCLKT0

SIO_PCLK

SBCLK

PCICLK6

PCICLK5

PCICLK4

PCICLK3

AGP1

AGP0

USB0

Close to clock generator

3

C346 20p

CN15 20p

7 8

5 6

3 4

1 2

C845 10p

C846 10p

CN16 10p

7 8

5 6

3 4

1 2

C369 10p

C367 10p

C374 10p

NOPOP

NOPOP

NOPOP

NOPOP

NOPOP

NOPOP

PCICLK_FB

2

R654 10

R655 10

Title

Size Document Number Rev

Custom

Date: Sheet of

SIO_PCLK <22>

SBCLK <21>

MICRO-STAR

Clock Synthesizer

MS-6501

1

3 39Wednesday, July 25, 2001

0A

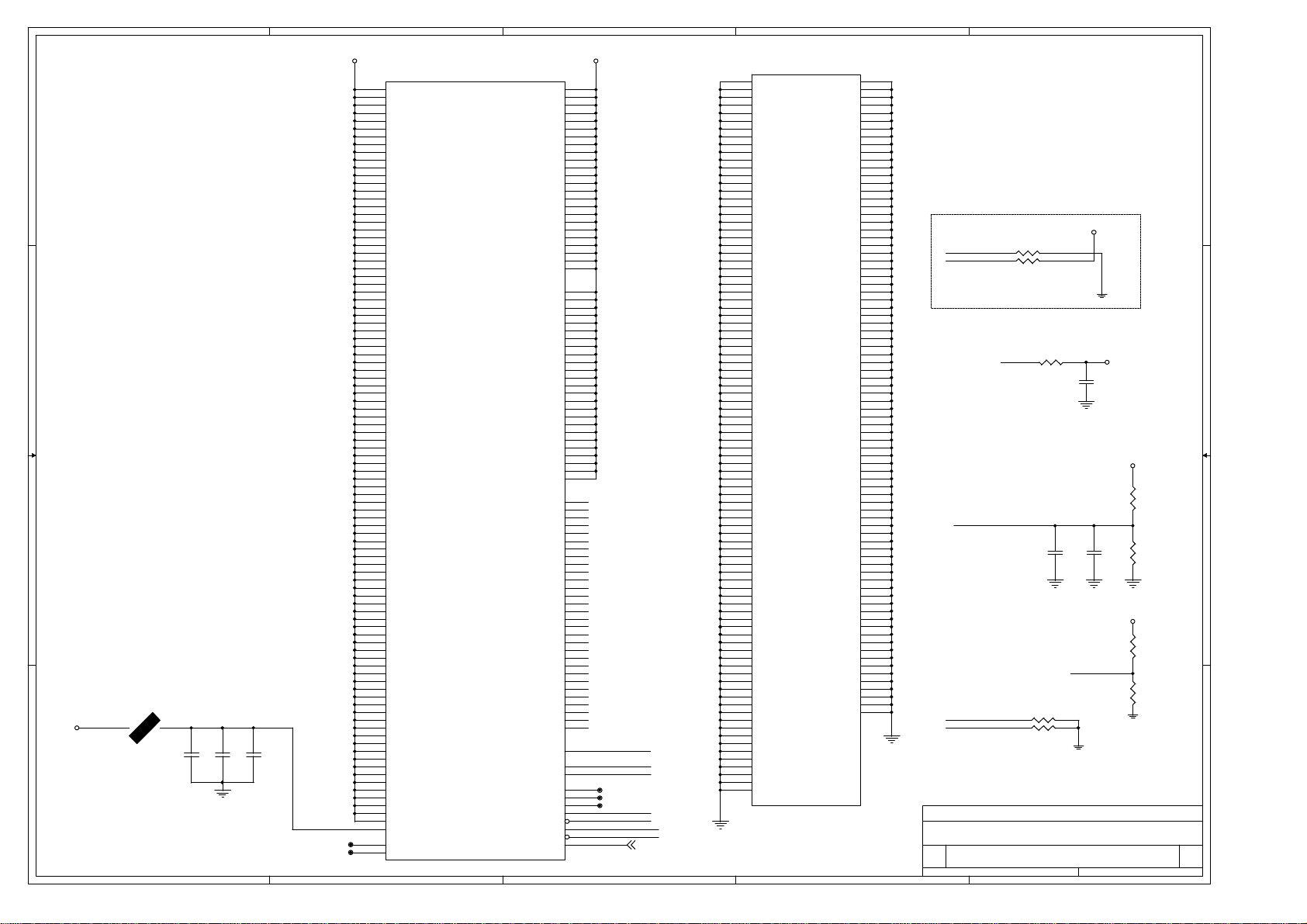

A

B

C

D

E

C319

0.047u

100

RN80

510

VCORE

RN59

4 39Wednesday, July 25, 2001

12

34

56

78

VCORE

78

56

34

12

VCORE

R283

100

R281

100

VCORE

0A

CPU1A

P0_SDATA-0

P0_SDATA-[0..63]<8>

4 4

3 3

P0_DICLK-[0..3]<8>

2 2

P0_DIVAL-<8>

P0_DOCLK-[0..3]<8>

P0_SDATA-1

P0_SDATA-2

P0_SDATA-3

P0_SDATA-4

P0_SDATA-5

P0_SDATA-6

P0_SDATA-7

P0_SDATA-8

P0_SDATA-9

P0_SDATA-10

P0_SDATA-11

P0_SDATA-12

P0_SDATA-13

P0_SDATA-14

P0_SDATA-15

P0_SDATA-16

P0_SDATA-17

P0_SDATA-18

P0_SDATA-19

P0_SDATA-20

P0_SDATA-21

P0_SDATA-22

P0_SDATA-23

P0_SDATA-24

P0_SDATA-25

P0_SDATA-26

P0_SDATA-27

P0_SDATA-28

P0_SDATA-29

P0_SDATA-30

P0_SDATA-31

P0_SDATA-32

P0_SDATA-33

P0_SDATA-34

P0_SDATA-35

P0_SDATA-36

P0_SDATA-37

P0_SDATA-38

P0_SDATA-39

P0_SDATA-40

P0_SDATA-41

P0_SDATA-42

P0_SDATA-43

P0_SDATA-44

P0_SDATA-45

P0_SDATA-46

P0_SDATA-47

P0_SDATA-48

P0_SDATA-49

P0_SDATA-50

P0_SDATA-51

P0_SDATA-52

P0_SDATA-53

P0_SDATA-54

P0_SDATA-55

P0_SDATA-56

P0_SDATA-57

P0_SDATA-58

P0_SDATA-59

P0_SDATA-60

P0_SDATA-61

P0_SDATA-62

P0_SDATA-63

P0_DICLK-0

P0_DICLK-1

P0_DICLK-2

P0_DICLK-3

P0_DIVALP0_DOCLK-0

P0_DOCLK-1

P0_DOCLK-2

P0_DOCLK-3

P0_DOVALP0_AIN-0

P0_AIN-1

P0_AIN-2

P0_AIN-[2..14]<8>

1 1

P0_AINCLK-<8>

P0_CFWDRST<8>

P0_CONNECT<8>

P0_PROCRDY<8>

P0_SFILLVAL-<8>

P0_AIN-3

P0_AIN-4

P0_AIN-5

P0_AIN-6

P0_AIN-7

P0_AIN-8

P0_AIN-9

P0_AIN-10

P0_AIN-11

P0_AIN-12

P0_AIN-13

P0_AIN-14

P0_CFWDRST

P0_CONNECT

P0_PROCRDY

P0_SFILLVAL-

AA35

W37

W35

AA33

AE37

AC33

AC37

AA37

AC35

W33

AN33

AE35

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

Y35

U35

U33

S37

S33

Y37

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

E9

A13

C9

A9

C21

A21

E19

C19

C17

A11

A17

A15

J35

E27

E15

C37

A33

C11

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

A20M

FERR

INTR

IGNNE

RESET

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

INIT

NMI

SMI

ZN

ZP

TCK

TDI

TDO

TMS

R266

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

PGA-D462

A20MFERR_P0

CPUINITINTR

IGNNENMI

CPURSTSMISTPCLK-

R315 100

APICD0APICD1-

P0_COREFBP0_COREFB

P0_CLKOUT

P0_CLKOUT-

P0_VREFMODE

P0_VREF_SYS

P0_ZN

P0_ZP

P0_PLLBP-

P0_PLLMON1

P0_PLLMON2

P0_PLLTEST-

P0_SCANCLK1

P0_SCANCLK2

P0_SINTVAL

P0_SSHIFTEN

P0_DBREQP0_FLUSH-

P0_CPU_TCK

P0_CPU_TDI

P0_CPU_TDO

P0_CPU_TMS

P0_CPU_TRST-

P0_VID0

P0_VID1

P0_VID2

P0_VID3

P0_VID4

P0_FID0

P0_FID1

P0_FID2

P0_FID3

P0_SCHECK-0

P0_SCHECK-1

P0_SCHECK-2

P0_SCHECK-3

P0_SCHECK-4

P0_SCHECK-5

P0_SCHECK-6

P0_SCHECK-7

P0_AOUT-2

P0_AOUT-3

P0_AOUT-4

P0_AOUT-5

P0_AOUT-6

P0_AOUT-7

P0_AOUT-8

P0_AOUT-9

P0_AOUT-10

P0_AOUT-11

P0_AOUT-12

P0_AOUT-13

P0_AOUT-14

CPUCLK0_R

CPUCLK-0_R

The farest VCORE and GND

A20M- <6,21>

FERR_P0 <21>

CPUINIT- <6,21>

INTR <6,21>

IGNNE- <6,21>

NMI <6,21>

SMI- <6,21>

STPCLK- <6,21>

CPU_PG <6,27>

APICCLK

APICD0- <6,21>

APICD1- <6,21>

R293

100

P0_VID0 <33>

P0_VID1 <33>

P0_VID2 <33>

P0_VID3 <33>

P0_VID4 <33>

P0_FID0 <33>

P0_FID1 <33>

P0_FID2 <33>

P0_FID3 <33>

P0_AOUTCLK- <8>

10K

A

B

**All CPU interface are 2.5V tolerant**

APICCLK <3,6,21>

P0_COREFB- <34>

P0_COREFB <34>

R285

100

AMD use 100ohm

VCORE

VCORE

RN63

78

56

34

12

100

P0_SCHECK-[0..7] <8>

P0_AOUT-[2..14] <8>

C351

4700p-REV

C

CPURST- <6,21>

INTR

CPUINITNMI

SMI-

IGNNECPURSTA20MSTPCLK-

P0_PLLMON1

P0_PLLMON2

P0_FLUSHP0_PLLBP-

P0_AIN-0

P0_AIN-1

P0_DOVALP0_SFILLVAL-

CPUCLK0_R

CPUCLK-0_R

CPUCLK-0<3>

CPUCLK0<3>

RN76

7 8

5 6

3 4

1 2

680

RN66

1 2

3 4

5 6

7 8

680

R286 56

R284 56

R314 680

R267 680

R247 680

R253 680

R241 270

R236 270

680pC311

680pC307

P0_DBREQ-

R313 510

P0_PLLTEST-

VCORE

P0_VREFMODE

VCORE

for internal VREFSYS

R280

1K-REV

R282

270

0.5 * VCORE

P0_VREF_SYSP0_CPU_DBRDY

VREFMODE=Low=No voltage scaling

P0_SCANCLK1

P0_SSHIFTEN

P0_SINTVAL

P0_SCANCLK2

RN79

1 2

3 4

5 6

7 8

10K

VCORE

R276 60.4

21

R274

301

R272 60.4

21

Near socket-A

D

Title

Size Document Number Rev

Custom

Date: Sheet of

P0_ZN

P0_ZP

P0_CLKOUT

P0_CLKOUT-

* Trace lengths of CLKOUT

and -CLKOUT are between

2" and 3"

MICRO-STAR

SocketA (Part 1)

R305 510

P0_CPU_TCK

P0_CPU_TMS

P0_CPU_TRSTP0_CPU_TDI

C320

C321

1000p

39p

R279 40.2

R278 40.2

match the transmission line

Push-Pull compensation circuit

MS-6501

E

A

VCC3

C253

4 4

39p

2 1

Max 150mA,

Design for

100mA

* 25 mils Trace/ 12 mils Space

RN55

7 8

5 6

3 4

1 2

33

C271

39p

2 1

VR6

CSK-2-SOT23-150mA

2.5V

R250

0

C281

0.01u

2

R264

3 1

0-REV

Used when

spec.

change

C266

39p

2 1

NOPOP

VCCA_PLL trace length from the VR1 to the PGA must be 0.75".

Place al filters close to the PGA.

Keep all power and signal trce away from the VR1.

Place a cut in the GND plane around the VCCA_PLL regulator circuit.

2 1

C291

39p

NOPOP

B

R257 10R259 0

C289

39p

2 1

Place

inside CPU

socket

C

P0_VCCA_PLL1P0_VCCA_PLL

Power Up Strappings :

D

E

AD[3:0] => CPU Clock Multiplier

0000 3

0001 3.5

C272

39p

2 1

0010 4

0011 4.5

0100 5

0101 5.5

0110 6

0111 6.5

1000 7

1001 7.5

1010 8

1011 8.5

1100 9

1101 9.5

1110 10

1111 Reserved

B12B8B4

AJ5

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VSS99

VSS100

VSS101

VSS102

VSS103

AM4

AK6

P0_VCCA_PLL

AC7

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS104

AM6

VCC_Z

NC1

NC2

NC3

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

VSS_Z

AE7

AJ23

VCC_A

0~100 mA,

2.25~2.75V

CPU1B

PGA-D462

AA31

AC31

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

S7

U31

U7

W31

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

P0_THERMADA <22>

P0_THERMADC <22>

P0_BP0 <33>

P0_BP1 <33>

P0_BP2 <33>

P0_BP3 <33>

The presence pin is only connected to GND

through the processor

VCORE

3 3

2 2

1 1

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AK8

AM8

AN7

G25

G17

AG7

AG15

AG29

AO1

AO2

AO3

AO4

XX1

XX2

AJ9

AL9

F30

H10

H28

H30

H32

K30

AJ7

AL7

F8

H6

H8

K8

G9

N7

Y7

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

EMI

EMI

EMI

EMI

EMI

EMI

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VSS1

VSS2

VSS3

VSS4

VSS5

H14

H18

H22

H26

M30P8R30T8V30X8Z30

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VSS6

VSS7

VSS8

VSS9

AF14

AF18

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VSS10

VSS11

VSS12

VSS13

VSS14

AB8

AF12

AF16

AF22

AF26

AM34

AK36

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VSS15

VSS16

VSS17

VSS18

AF20

AF24

AM36

AK32

AK34

AK30

AK26

AK22

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VSS19

VSS20

VSS21

VSS22

AK28

AK24

AK20

AK16

AK18

AK14

AK10

AL5

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VSS23

VSS25

VSS26

VSS27

AK12

AK4

AK2

AH36

AH26

AM30

AH22

AH18

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VSS28

VSS29

VSS30

VSS31

AM32

AH34

AH32

AH28

AH14

AH10

AH4

AH2

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VSS32

VSS33

VSS34

VSS35

AH24

AH20

AH16

AH12

AF36

AF34

AD6

AM26

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VSS37

VSS38

VSS39

VSS40

AF4

AF2

AD36

AD34

AD4

AD2

AB36

AB34

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VSS41

VSS42

VSS43

VSS44

AD32

AB6

AB4

AB2

AB32Z6Z4Z2X36

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VSS45

VSS46

VSS47

VSS48

Z36

Z34

Z32X6AM28X4X2

X34

AM22

X32V6V4V2T36

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VSS49

VSS50

VSS51

VSS52

VSS53

V36

V34

T34

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VSS54

VSS55

VSS56

VSS57

V32T6T4T2R36

T32R6R4R2AM18

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VSS58

VSS59

VSS60

VSS61

VSS62

R34

AM24

R32P6P4P2M36

P36

P34

P32M4M6M2K36

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VSS63

VSS64

VSS65

VSS66

M34

K34

K32H4H2

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VSS67

VSS68

VSS69

VSS70

VSS71

M32K6K4K2AM20

AM14

F36

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VSS72

VSS73

VSS74

VSS75

H36

H34

F26

F22

F34

F32

F28

F24

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VSS76

VSS77

VSS78

VSS79

F18

F14

F10F6F4F2AM16

F20

F16

F12

D32

VCC_CORE78

VCC_CORE79

VCC_CORE80

VCC_CORE81

VSS80

VSS81

VSS82

VSS83

D36

D28

AM10

D24

D20

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VSS84

VSS85

VSS86

VSS87

D34

D30

D26

D22

D16

D12D8D4D2B36

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VSS88

VSS89

VSS90

VSS91

D18

D14

D10D6B34

B32

AM2

B28

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VSS92

VSS93

VSS94

VSS95

VSS96

AM12

B30

B26

B22

B24

B20

B16

VCC_CORE95

VCC_CORE96

VSS97

VSS98

B18

B14

B10B6B2

Title

Size Document Number Rev

Custom

A

B

C

D

Date: Sheet of

MICRO-STAR

SocketA (Part 2)

MS-6501

E

5 39Wednesday, July 25, 2001

0A

A

B

C

D

E

C141

0.047u

100

RN31

510

R484

160R487

VCORE

RN36

6 39Wednesday, July 25, 2001

12

34

56

78

0.01u

VCORE

VCORE

78

56

34

12

VCORE

C608

R112

100

R117

100

0A

CPU2A

P1_SDATA-0

P1_SDATA-[0..63]<9>

4 4

3 3

P1_DICLK-[0..3]<9>

2 2

P1_DIVAL-<9>

P1_DOCLK-[0..3]<9>

P1_SDATA-1

P1_SDATA-2

P1_SDATA-3

P1_SDATA-4

P1_SDATA-5

P1_SDATA-6

P1_SDATA-7

P1_SDATA-8

P1_SDATA-9

P1_SDATA-10

P1_SDATA-11

P1_SDATA-12

P1_SDATA-13

P1_SDATA-14

P1_SDATA-15

P1_SDATA-16

P1_SDATA-17

P1_SDATA-18

P1_SDATA-19

P1_SDATA-20

P1_SDATA-21

P1_SDATA-22

P1_SDATA-23

P1_SDATA-24

P1_SDATA-25

P1_SDATA-26

P1_SDATA-27

P1_SDATA-28

P1_SDATA-29

P1_SDATA-30

P1_SDATA-31

P1_SDATA-32

P1_SDATA-33

P1_SDATA-34

P1_SDATA-35

P1_SDATA-36

P1_SDATA-37

P1_SDATA-38

P1_SDATA-39

P1_SDATA-40

P1_SDATA-41

P1_SDATA-42

P1_SDATA-43

P1_SDATA-44

P1_SDATA-45

P1_SDATA-46

P1_SDATA-47

P1_SDATA-48

P1_SDATA-49

P1_SDATA-50

P1_SDATA-51

P1_SDATA-52

P1_SDATA-53

P1_SDATA-54

P1_SDATA-55

P1_SDATA-56

P1_SDATA-57

P1_SDATA-58

P1_SDATA-59

P1_SDATA-60

P1_SDATA-61

P1_SDATA-62

P1_SDATA-63

P1_DICLK-0

P1_DICLK-1

P1_DICLK-2

P1_DICLK-3

P1_DIVALP1_DOCLK-0

P1_DOCLK-1

P1_DOCLK-2

P1_DOCLK-3

P1_DOVALP1_AIN-0

P1_AIN-1

P1_AIN-2

P1_AIN-[2..14]<9>

1 1

P1_AINCLK-<9>

P1_CFWDRST<9>

P1_CONNECT<9>

P1_PROCRDY<9>

P1_SFILLVAL-<9>

P1_AIN-3

P1_AIN-4

P1_AIN-5

P1_AIN-6

P1_AIN-7

P1_AIN-8

P1_AIN-9

P1_AIN-10

P1_AIN-11

P1_AIN-12

P1_AIN-13

P1_AIN-14

P1_CFWDRST

P1_CONNECT

P1_PROCRDY

P1_SFILLVAL-

AA35

W37

W35

AA33

AE37

AC33

AC37

AA37

AC35

W33

AN33

AE35

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

Y35

U35

U33

S37

S33

Y37

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

E9

A13

C9

A9

C21

A21

E19

C19

C17

A11

A17

A15

J35

E27

E15

C37

A33

C11

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

A20M

FERR

INTR

IGNNE

RESET

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

INIT

NMI

SMI

ZN

ZP

TCK

TDI

TDO

TMS

R156

10K

A

B

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

PGA-D462

A20MFERR_P1

CPUINITINTR

IGNNENMI

CPURSTSMISTPCLK-

R62 100

APICD0APICD1-

P1_COREFBP1_COREFB

CPUCLK1_R

CPUCLK-1_R

P1_CLKOUT

P1_CLKOUT-

P1_VREFMODE

P1_VREF_SYS

P1_ZN

P1_ZP

P1_PLLBP-

P1_PLLMON1

P1_PLLMON2

P1_PLLTEST-

P1_SCANCLK1

P1_SCANCLK2

P1_SINTVAL

P1_SSHIFTEN

P1_CPU_DBRDY

P1_DBREQP1_FLUSH-

P1_CPU_TCK

P1_CPU_TDI

P1_CPU_TDO

P1_CPU_TMS

P1_CPU_TRST-

P1_SCHECK-0

P1_SCHECK-1

P1_SCHECK-2

P1_SCHECK-3

P1_SCHECK-4

P1_SCHECK-5

P1_SCHECK-6

P1_SCHECK-7

P1_AOUT-2

P1_AOUT-3

P1_AOUT-4

P1_AOUT-5

P1_AOUT-6

P1_AOUT-7

P1_AOUT-8

P1_AOUT-9

P1_AOUT-10

P1_AOUT-11

P1_AOUT-12

P1_AOUT-13

P1_AOUT-14

A20M- <4,21>

FERR_P1 <21>

CPUINIT- <4,21>

INTR <4,21>

IGNNE- <4,21>

NMI <4,21>

SMI- <4,21>

STPCLK- <4,21>

**All CPU interface are 2.5V tolerant**

CPU_PG <4,27>

APICCLK

APICD0- <4,21>

APICD1- <4,21>

The farest VCORE and GND

R97

100

VCORE

RN33

R103

100

78

56

34

12

APICCLK <3,4,21>

P1_COREFB- <34>

P1_COREFB <34>

VCORE

100

P1_SCHECK-[0..7] <9>

P1_AOUT-[2..14] <9>

P1_AOUTCLK- <9>

CPURST- <4,21>

C

P1_PLLMON1

P1_PLLMON2

P1_FLUSHP1_PLLBP-

P1_AIN-0

P1_AIN-1

P1_DOVALP1_SFILLVAL-

CPUCLK1_R

CPUCLK-1_R

CPUCLK-1<3>

CPUCLK1<3>

R101 56

R95 56

R89 680

R157 680

R172 680

R173 680

R180 270

R406 270

Reserved

680pC154

680pC158

P1_DBREQ-

R75 510

VCC3

RN187

1 2

3 4

5 6

7 8

33

2

3 1

VR8

CSK-2-SOT23-150mA

R486

0 C607

0.01u

0-REV

P1_PLLTEST-

APICCLK

P1_CPU_TCK

P1_CPU_TMS

P1_CPU_TRSTP1_CPU_TDI

R485

62

R81 510

R483

160

APICD0APICD1-

VCORE

for internal VREFSYS

R118

1K

R113

270

P1_SCANCLK1

P1_SSHIFTEN

P1_SINTVAL

P1_SCANCLK2

RN30

7 8

5 6

3 4

1 2

VCORE

P1_VREFMODE

VREFMODE=Low=No voltage scaling

10K

VCORE

R136 60.4

21

R140

301

R143 60.4

21

Near socket-A

D

Title

Size Document Number Rev

Custom

Date: Sheet of

0.5 * VCORE

P1_VREF_SYS

C142

C143

1000p

39p

P1_ZN

R119 40.2

P1_ZP

R120 40.2

match the transmission line

Push-Pull compensation circuit

P1_CLKOUT

P1_CLKOUT-

* Trace lengths of CLKOUT

and -CLKOUT are between

2" and 3"

MICRO-STAR

SocketA (Part 1)

MS-6501

E

A

B

C

D

E

VCC3

7 8

5 6

3 4

1 2

4 4

C122

39p

2 1

Max 150mA,

Design for

100mA

* 25 mils Trace/ 12 mils Space

RN32

33

C133

39p

2 1

3 1

VR5

CSK-2-SOT23-150mA

R102

0

2

R122

0-REV

C134

0.01u

Used when

spec.

change

2.5V

C144

39p

2 1

NOPOP

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

C175

39p

2 1

NOPOP

R167 10R114 0

C173

39p

2 1

Place

inside CPU

socket

P1_VCCA_PLL1P1_VCCA_PLL

C189

39p

2 1

Power Up Strappings :

AD[3:0] => CPU Clock Multiplier

0000 3

0001 3.5

0010 4

0011 4.5

0100 5

0101 5.5

0110 6

0111 6.5

1000 7

1001 7.5

1010 8

1011 8.5

1100 9

1101 9.5

1110 10

1111 Reserved

Place al filters close to the PGA.

Keep all power and signal trce away from

the VR1.

Place a cut in the GND plane around the

VCCA_PLL regulator circuit.

AJ5

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS100

VSS101

VSS102

VSS103

VSS104

AM4

AK6

AM6

D

P1_VCCA_PLL

0~100 mA,

2.25~2.75V

CPU2B

AC7

AJ23

PGA-D462

VCC_Z

VCC_A

AA31

NC1

AC31

NC2

AE31

NC3

AG23

NC6

AG25

NC7

AG31

NC8

AG5

NC9

AJ11

NC10

AJ15

NC11

AJ17

NC12

AJ19

NC13

AJ27

NC15

AL11

NC16

AN11

NC17

AN9

NC18

G11

NC19

G13

NC20

G27

NC21

G29

NC22

G31

NC23

J31

NC24

J5

NC25

L31

NC27

N31

NC28

Q31

NC29

S31

NC30

S7

NC31

U31

NC32

U7

NC33

W31

NC34

W7

NC35

Y31

NC36

Y5

NC37

AG19

NC42

G21

NC43

AG21

NC44

G19

NC45

AN27

AL27

AN25

AL25

VSS_Z

AE7

P1_THERMADA <22>

P1_THERMADC <22>

P1_BP0 <33>

P1_BP1 <33>

P1_BP2 <33>

P1_BP3 <33>

MICRO-STAR

Title

Size Document Number Rev

Custom

Date: Sheet of

SocketA (Part 2)

MS-6501

E

7 39Wednesday, July 25, 2001

0A

VCORE

3 3

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

H14

VSS1

H18

VSS2

H22

A

VCC_CORE6

VSS3

VSS4

VSS5

VSS6

H26

M30P8R30T8V30X8Z30

AD30

VCC_SRAM1

AD8

VCC_SRAM2

AF10

VCC_SRAM3

AF28

VCC_SRAM4

AF30

VCC_SRAM5

AF32

VCC_SRAM6

AF6

VCC_SRAM7

AF8

VCC_SRAM8

AH30

VCC_SRAM9

AH8

VCC_SRAM11

AJ9

VCC_SRAM13

AK8

VCC_SRAM14

AL9

VCC_SRAM16

AM8

VCC_SRAM17

2 2

1 1

F30

H10

H28

H30

H32

K30

AJ7

AL7

AN7

G25

G17

AG7

AG15

AG29

AO1

AO2

AO3

AO4

XX1

XX2

F8

H6

H8

K8

G9

N7

Y7

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

EMI

EMI

EMI

EMI

EMI

EMI

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

VSS7

VSS8

VSS9

VSS10

VSS11

AF14

AF18

AF22

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VSS12

VSS13

VSS14

VSS15

AB8

AF12

AF16

AF20

AF26

AM34

AK36

AK34

AK30

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VSS16

VSS17

VSS18

VSS19

AF24

AM36

AK32

AK28

AK24

AK26

AK22

AK18

AK14

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VSS20

VSS21

VSS22

VSS23

VSS25

AK20

AK16

AK12

AK4

AK10

AL5

AH26

AM30

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VSS26

VSS27

VSS28

VSS29

AK2

AH36

AM32

AH34

AH22

AH18

AH14

AH10

AH4

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VSS30

VSS31

VSS32

VSS33

AH32

AH28

AH24

AH20

AH16

AH2

AF36

AF34

AD6

AM26

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VSS34

VSS35

VSS37

VSS38

VSS39

AH12

AF4

AF2

AD36

AD34

B

AD4

AD2

AB36

AB34

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VSS40

VSS41

VSS42

VSS43

VSS44

AD32

AB6

AB4

AB2

AB32Z6Z4Z2X36

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VSS45

VSS46

VSS47

VSS48

Z36

Z34

Z32X6AM28X4X2

X34

AM22

X32V6V4V2T36

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VSS49

VSS50

VSS51

VSS52

VSS53

V36

V34

T34

T32R6R4R2AM18

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VSS54

VSS55

VSS56

VSS57

V32T6T4T2R36

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VSS58

VSS59

VSS60

VSS61

VSS62

R34

AM24

R32P6P4P2M36

P36

P34

P32M4M6M2K36

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VSS63

VSS64

VSS65

VSS66

M34

M32K6K4K2AM20

K34

K32H4H2

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VSS67

VSS68

VSS69

VSS70

VSS71

C

AM14

F36

F34

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VSS72

VSS73

VSS74

VSS75

H36

H34

F26

F22

F18

F32

F28

F24

F20

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VSS76

VSS77

VSS78

VSS79

VSS80

F14

F10F6F4F2AM16

F16

F12

D32

D28

AM10

VCC_CORE79

VCC_CORE80

VCC_CORE81

VCC_CORE82

VSS81

VSS82

VSS83

VSS84

D36

D34

D30

D24

D20

D16

D12D8D4D2B36

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VSS85

VSS86

VSS87

VSS88

VSS89

D26

D22

D18

D14

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VSS90

VSS91

VSS92

VSS93

D10D6B34

AM12

B32

AM2

B28

B24

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VSS94

VSS95

VSS96

VSS97

B30

B26

B22

B18

B20

B16

B12B8B4

VCC_CORE96

VCC_CORE97

VSS98

VSS99

B14

B10B6B2

5

D D

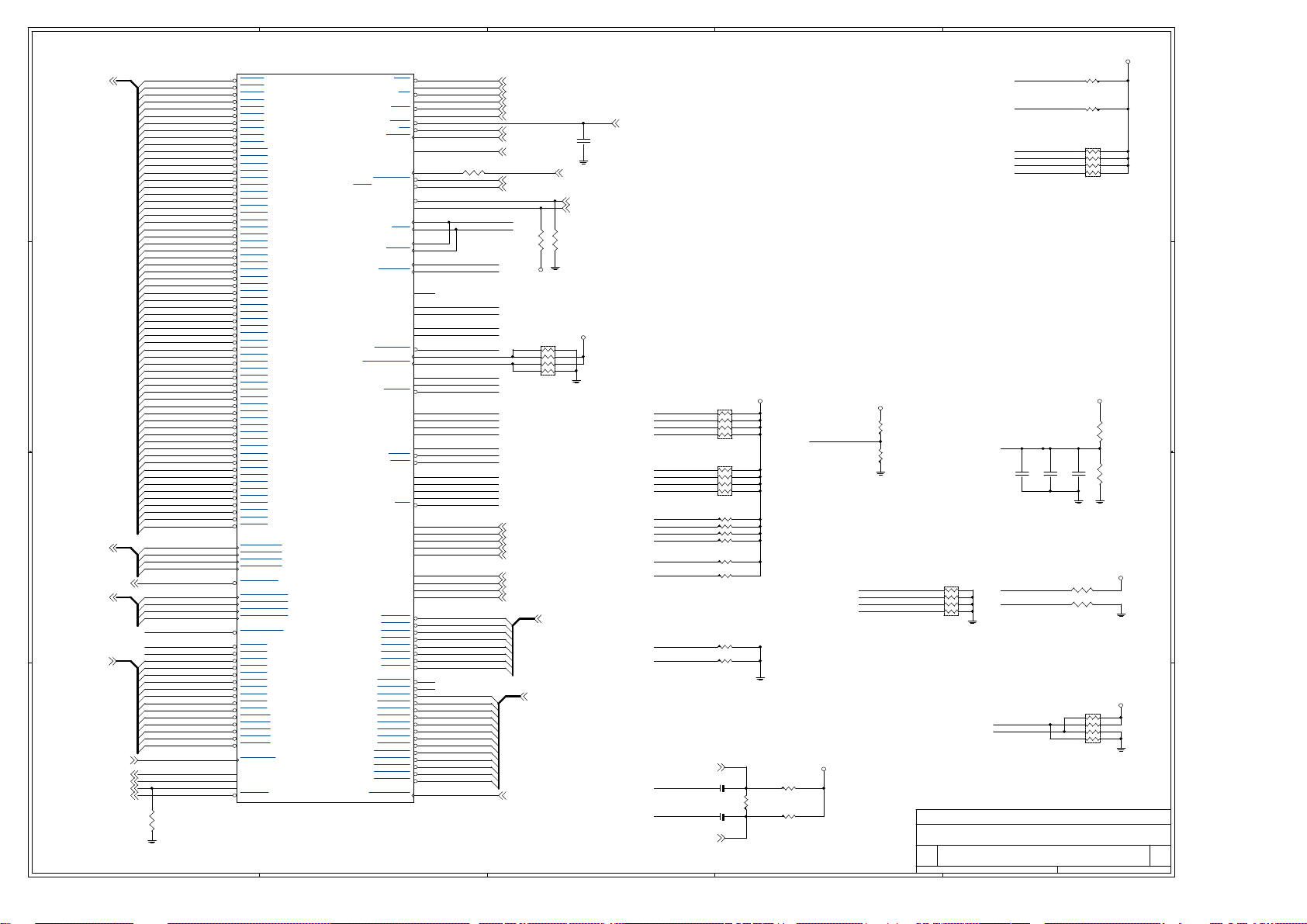

BELONG TO CLKFWD GROUP[SADDIN] MATCH

W/IN +/-50MILS OF GROUP 5/10,

CLK:5/20

BELONG TO CLKFWD GROUP[SADDOUT] MATCH

C C

W/IN +/-50MILS OF GROUP 5/10,

CLK:5/20

BELONG TO CLKFWD GROUP;MATCHED TO

INDIVIDUAL CLKFWD GROUP

RESPECTIVELY.[SDATA0], [SDATA1],

[SDATA2],[SDATA3] W/IN+/-50MILS OF

GROUP

B B

P0_AIN-[2..14]<4>

--------------------------------

P0_AOUT-[2..14]<4>

--------------------------------

P0_SCHECK-[0..7]<4>

----------------------

P0_DICLK-[0..3]<4>

P0_DOCLK-[0..3]<4>

4

System Bus 0

P0_CFWDRST<4>

P0_CONNECT<4>

P0_PROCRDY<4>

CPUCLK2<3>

P0_AINCLK-<4>

P0_AOUTCLK-<4>

P0_DIVAL-<4>

P0_SFILLVAL-<4>

P0_CFWDRST

P0_CONNECT

P0_PROCRDY

CPUCLK2

P0_AIN-2

P0_AIN-3

P0_AIN-4

P0_AIN-5

P0_AIN-6

P0_AIN-7

P0_AIN-8

P0_AIN-9

P0_AIN-10

P0_AIN-11

P0_AIN-12

P0_AIN-13

P0_AIN-14

P0_AINCLK-

P0_AOUT-2

P0_AOUT-3

P0_AOUT-4

P0_AOUT-5

P0_AOUT-6

P0_AOUT-7

P0_AOUT-8

P0_AOUT-9

P0_AOUT-10

P0_AOUT-11

P0_AOUT-12

P0_AOUT-13

P0_AOUT-14

P0_AOUTCLK-

P0_SCHECK-0

P0_SCHECK-1

P0_SCHECK-2

P0_SCHECK-3

P0_SCHECK-4

P0_SCHECK-5

P0_SCHECK-6

P0_SCHECK-7

P0_DICLK-0

P0_DICLK-1

P0_DICLK-2

P0_DICLK-3

P0_DIVALP0_DOCLK-0

P0_DOCLK-1

P0_DOCLK-2

P0_DOCLK-3

U23A

AC5

P0_CLKFWDRST

AC4

P0_CONNECT

AC6

P0_PROCRDY

AH20

SYSCLK

Y4

P0_SADDIN2#

AA2

P0_SADDIN3#

AA6

P0_SADDIN4#

Y5

P0_SADDIN5#

AA4

P0_SADDIN6#

AA3

P0_SADDIN7#

AA5

P0_SADDIN8#

AB3

P0_SADDIN9#

AB5

P0_SADDIN10#

Y6

P0_SADDIN11#

AD1

P0_SADDIN12#

AC3

P0_SADDIN13#

AC1

P0_SADDIN14#

AA7

P0_SADDINCLK#

G1

P0_SADDOUT2#

H2

P0_SADDOUT3#

G3

P0_SADDOUT4#

F4

P0_SADDOUT5#

H4

P0_SADDOUT6#

E1

P0_SADDOUT7#

F3

P0_SADDOUT8#

F2

P0_SADDOUT9#

F5

P0_SADDOUT10#

G5

P0_SADDOUT11#

F1

P0_SADDOUT12#

E2

P0_SADDOUT13#

D1

P0_SADDOUT14#

E3

P0_SADDOUTCLK#

V7

P0_SCHECK0#

V8

P0_SCHECK1#

P8

P0_SCHECK2#

T1

P0_SCHECK3#

N7

P0_SCHECK4#

N1

P0_SCHECK5#

J3

P0_SCHECK6#

K3

P0_SCHECK7#

U5

P0_SDATAINCLK0#

R1

P0_SDATAINCLK1#

M1

P0_SDATAINCLK2#

H3

P0_SDATAINCLK3#

AB1

P0_SDATAINVALID#

W5

P0_SDATAOUTCLK0#

R8

P0_SDATAOUTCLK1#

N5

P0_SDATAOUTCLK2#

H1

P0_SDATAOUTCLK3#

J8

P0_SYSFILLVALID#

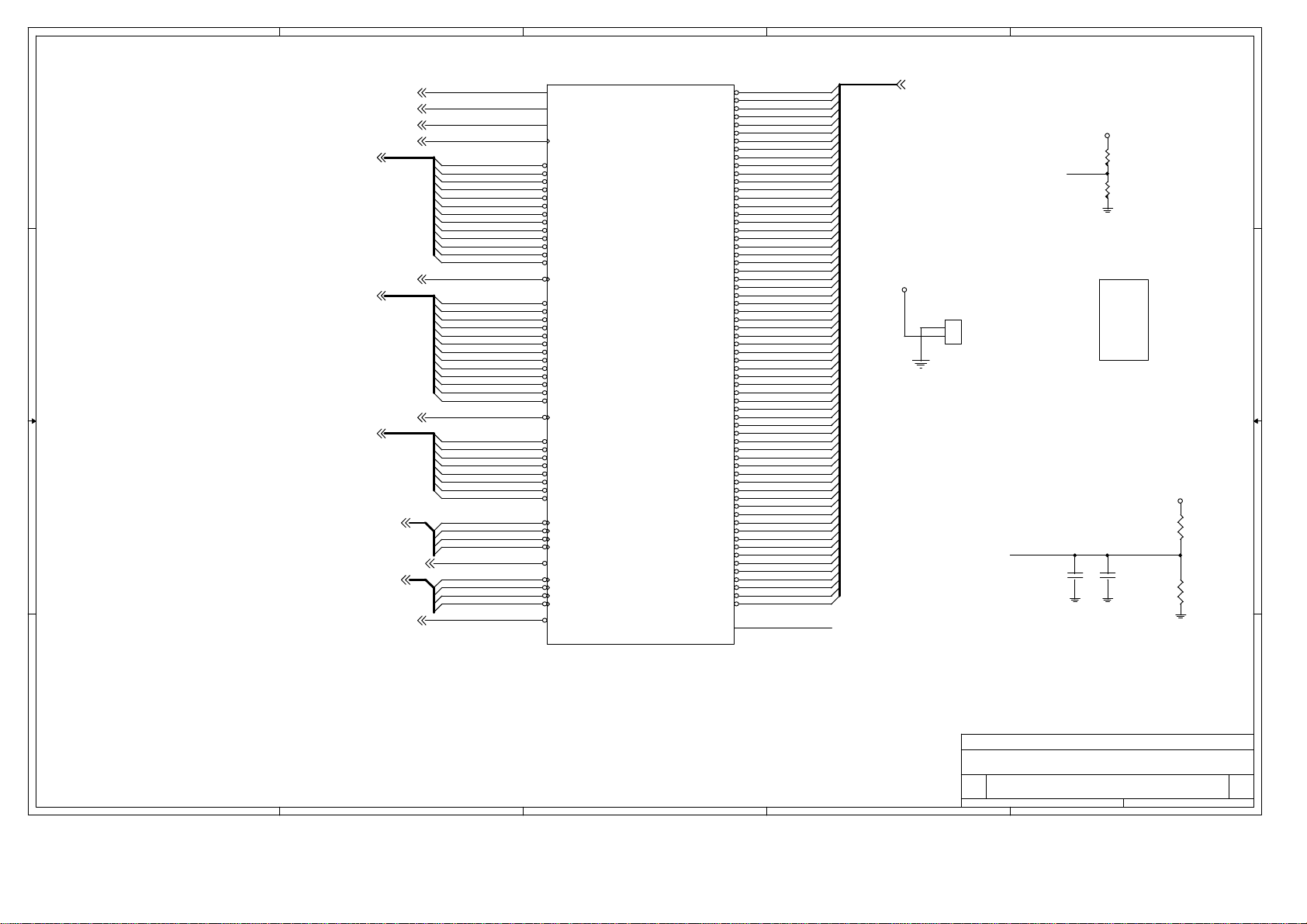

AMD-AMD762

AMD-762

3

P0_SDATA0#

P0_SDATA1#

P0_SDATA2#

P0_SDATA3#

P0_SDATA4#

P0_SDATA5#

P0_SDATA6#

P0_SDATA7#

P0_SDATA8#

P0_SDATA9#

P0_SDATA10#

P0_SDATA11#

P0_SDATA12#

P0_SDATA13#

P0_SDATA14#

P0_SDATA15#

P0_SDATA16#

P0_SDATA17#

P0_SDATA18#

P0_SDATA19#

P0_SDATA20#

P0_SDATA21#

P0_SDATA22#

P0_SDATA23#

P0_SDATA24#

P0_SDATA25#

P0_SDATA26#

P0_SDATA27#

P0_SDATA28#

P0_SDATA29#

P0_SDATA30#

P0_SDATA31#

P0_SDATA32#

P0_SDATA33#

P0_SDATA34#

P0_SDATA35#

P0_SDATA36#

P0_SDATA37#

P0_SDATA38#

P0_SDATA39#

P0_SDATA40#

P0_SDATA41#

P0_SDATA42#

P0_SDATA43#

P0_SDATA44#

P0_SDATA45#

P0_SDATA46#

P0_SDATA47#

P0_SDATA48#

P0_SDATA49#

P0_SDATA50#

P0_SDATA51#

P0_SDATA52#

P0_SDATA53#

P0_SDATA54#

P0_SDATA55#

P0_SDATA56#

P0_SDATA57#

P0_SDATA58#

P0_SDATA59#

P0_SDATA60#

P0_SDATA61#

P0_SDATA62#

P0_SDATA63#

P0_VREF

W3

V4

V3

V5

V6

U4

U3

U8

Y1

Y3

AA1

Y7

W1

W7

Y2

U6

U7

R7

R6

R5

R3

R4

R2

U2

T7

V1

T5

V2

T3

U1

P6

P1

P2

P4

M8

M6

L3

L7

M4

L6

P7

P5

N3

P3

M5

M7

L5

M3

K7

J6

J7

K5

J4

J2

H6

H5

M2

L4

L2

L1

K1

H7

J5

J1

AC2

P0_SDATA-0

P0_SDATA-1

P0_SDATA-2

P0_SDATA-3

P0_SDATA-4

P0_SDATA-5

P0_SDATA-6

P0_SDATA-7

P0_SDATA-8

P0_SDATA-9

P0_SDATA-10

P0_SDATA-11

P0_SDATA-12

P0_SDATA-13

P0_SDATA-14

P0_SDATA-15

P0_SDATA-16

P0_SDATA-17

P0_SDATA-18

P0_SDATA-19

P0_SDATA-20

P0_SDATA-21

P0_SDATA-22

P0_SDATA-23

P0_SDATA-24

P0_SDATA-25

P0_SDATA-26

P0_SDATA-27

P0_SDATA-28

P0_SDATA-29

P0_SDATA-30

P0_SDATA-31

P0_SDATA-32

P0_SDATA-33

P0_SDATA-34

P0_SDATA-35

P0_SDATA-36

P0_SDATA-37

P0_SDATA-38

P0_SDATA-39

P0_SDATA-40

P0_SDATA-41

P0_SDATA-42

P0_SDATA-43

P0_SDATA-44

P0_SDATA-45

P0_SDATA-46

P0_SDATA-47

P0_SDATA-48

P0_SDATA-49

P0_SDATA-50

P0_SDATA-51

P0_SDATA-52

P0_SDATA-53

P0_SDATA-54

P0_SDATA-55

P0_SDATA-56

P0_SDATA-57

P0_SDATA-58

P0_SDATA-59

P0_SDATA-60

P0_SDATA-61

P0_SDATA-62

P0_SDATA-63

P0_S2K_VREF

2

P0_SDATA-[0..63] <4>

+12V

NBFAN1

2

1

D1x2-WH

1

VCC2_5

R408

U3_X

_

100

R410

150

CPUCLK2

Put these two res. very

close to N.B.

Set S2K_VREF to 50% of VCORE

P0_S2K_VREF

C265

C270

0.047u

0.039u

VCORE

R248

100

R251

100

A A

Title

Size Document Number Rev

B

5

4

3

2

Date: Sheet of

North Bridge AMD762-CPU0

MICRO-STAR

MS-6501

1

8 39Monday, July 23, 2001

0A

5

D D

BELONG TO CLKFWD GROUP[SADDIN] MATCH

W/IN +/-50MILS OF GROUP 5/10,

CLK:5/20

BELONG TO CLKFWD GROUP[SADDOUT] MATCH

C C

W/IN +/-50MILS OF GROUP 5/10,

CLK:5/20

BELONG TO CLKFWD GROUP;MATCHED TO

INDIVIDUAL CLKFWD GROUP

RESPECTIVELY.[SDATA0], [SDATA1],

[SDATA2],[SDATA3] W/IN+/-50MILS OF

GROUP

B B

P1_AIN-[2..14]<6>

--------------------------------

P1_AOUT-[2..14]<6>

--------------------------------

P1_SCHECK-[0..7]<6>

----------------------

P1_DICLK-[0..3]<6>

P1_DOCLK-[0..3]<6>

4

P1_CFWDRST<6>

P1_CONNECT<6>

P1_PROCRDY<6>

P1_AINCLK-<6>

P1_AOUTCLK-<6>

P1_DIVAL-<6>

P1_SFILLVAL-<6>

P1_CFWDRST

P1_CONNECT

P1_PROCRDY

P1_AIN-2

P1_AIN-3

P1_AIN-4

P1_AIN-5

P1_AIN-6

P1_AIN-7

P1_AIN-8

P1_AIN-9

P1_AIN-10

P1_AIN-11

P1_AIN-12

P1_AIN-13

P1_AIN-14

P1_AINCLK-

P1_AOUT-2

P1_AOUT-3

P1_AOUT-4

P1_AOUT-5

P1_AOUT-6

P1_AOUT-7

P1_AOUT-8

P1_AOUT-9

P1_AOUT-10

P1_AOUT-11

P1_AOUT-12

P1_AOUT-13

P1_AOUT-14

P1_AOUTCLK-

P1_SCHECK-0

P1_SCHECK-1

P1_SCHECK-2

P1_SCHECK-3

P1_SCHECK-4

P1_SCHECK-5

P1_SCHECK-6

P1_SCHECK-7

P1_DICLK-0

P1_DICLK-1

P1_DICLK-2

P1_DICLK-3

P1_DIVALP1_DOCLK-0

P1_DOCLK-1

P1_DOCLK-2

P1_DOCLK-3

P1_SFILLVAL-

U23B

AL19

P1_CLKFWDRST

AJ19

P1_CONNECT

AE19

P1_PROCRDY

AG17

P1_SADDIN2#

AH18

P1_SADDIN3#

AL18

P1_SADDIN4#

AL17

P1_SADDIN5#

AF17

P1_SADDIN6#

AG16

P1_SADDIN7#

AG18

P1_SADDIN8#

AD17

P1_SADDIN9#

AK18

P1_SADDIN10#

AK17

P1_SADDIN11#

AG19

P1_SADDIN12#

AE18

P1_SADDIN13#

AF18

P1_SADDIN14#

AJ18

P1_SADDINCLK#

AJ2

P1_SADDOUT2#

AK3

P1_SADDOUT3#

AE3

P1_SADDOUT4#

AG3

P1_SADDOUT5#

AF3

P1_SADDOUT6#

AD7

P1_SADDOUT7#

AJ3

P1_SADDOUT8#

AF2

P1_SADDOUT9#

AD5

P1_SADDOUT10#

AD6

P1_SADDOUT11#

AF1

P1_SADDOUT12#

AH1

P1_SADDOUT13#

AG2

P1_SADDOUT14#

AG1

P1_SADDOUTCLK#

AG14

P1_SCHECK0#

AL15

P1_SCHECK1#

AH12

P1_SCHECK2#

AJ10

P1_SCHECK3#

AL9

P1_SCHECK4#

AG8

P1_SCHECK5#

AF6

P1_SCHECK6#

AL7

P1_SCHECK7#

AE15

P1_SDATAINCLK0#

AD12

P1_SDATAINCLK1#

AJ8

P1_SDATAINCLK2#

AK5

P1_SDATAINCLK3#

AE17

P1_SDATAINVALID#

AH15

P1_SDATAOUTCLK0#

AH11

P1_SDATAOUTCLK1#

AG9

P1_SDATAOUTCLK2#

AJ4

P1_SDATAOUTCLK3#

AL20

P1_SYSFILLVALID#

AMD-AMD762

3

AMD-762

System Bus 1

P1_SDATA0#

P1_SDATA1#

P1_SDATA2#

P1_SDATA3#

P1_SDATA4#

P1_SDATA5#

P1_SDATA6#

P1_SDATA7#

P1_SDATA8#

P1_SDATA9#

P1_SDATA10#

P1_SDATA11#

P1_SDATA12#

P1_SDATA13#

P1_SDATA14#

P1_SDATA15#

P1_SDATA16#

P1_SDATA17#

P1_SDATA18#

P1_SDATA19#

P1_SDATA20#

P1_SDATA21#

P1_SDATA22#

P1_SDATA23#

P1_SDATA24#

P1_SDATA25#

P1_SDATA26#

P1_SDATA27#

P1_SDATA28#

P1_SDATA29#

P1_SDATA30#

P1_SDATA31#

P1_SDATA32#

P1_SDATA33#

P1_SDATA34#

P1_SDATA35#

P1_SDATA36#

P1_SDATA37#

P1_SDATA38#

P1_SDATA39#

P1_SDATA40#

P1_SDATA41#

P1_SDATA42#

P1_SDATA43#

P1_SDATA44#

P1_SDATA45#

P1_SDATA46#

P1_SDATA47#

P1_SDATA48#

P1_SDATA49#

P1_SDATA50#

P1_SDATA51#

P1_SDATA52#

P1_SDATA53#

P1_SDATA54#

P1_SDATA55#

P1_SDATA56#

P1_SDATA57#

P1_SDATA58#

P1_SDATA59#

P1_SDATA60#

P1_SDATA61#

P1_SDATA62#

P1_SDATA63#

P1_VREF

AE14

AJ14

AE16

AD14

AJ15

AL14

AK15

AE13

AL16

AD15

AG15

AF15

AJ16

AH17

AJ17

AH14

AF14

AF12

AE12

AK12

AJ11

AE11

AG11

AF11

AK14

AL13

AL12

AG13

AJ13

AG12

AJ12

AL11

AG7

AF9

AK11

AL10

AK8

AL8

AH8

AK9

AE10

AE9

AD11

AG10

AJ9

AH9

AF8

AJ7

AF4

AG5

AF5

AK6

AH4

AJ5

AL4

AH3

AE8

AE7

AG6

AL6

AJ6

AE5

AH6

AL5

AB7

P1_SDATA-0

P1_SDATA-1

P1_SDATA-2

P1_SDATA-3

P1_SDATA-4

P1_SDATA-5

P1_SDATA-6

P1_SDATA-7

P1_SDATA-8

P1_SDATA-9

P1_SDATA-10

P1_SDATA-11

P1_SDATA-12

P1_SDATA-13

P1_SDATA-14

P1_SDATA-15

P1_SDATA-16

P1_SDATA-17

P1_SDATA-18

P1_SDATA-19

P1_SDATA-20

P1_SDATA-21

P1_SDATA-22

P1_SDATA-23

P1_SDATA-24

P1_SDATA-25

P1_SDATA-26

P1_SDATA-27

P1_SDATA-28

P1_SDATA-29

P1_SDATA-30

P1_SDATA-31

P1_SDATA-32

P1_SDATA-33

P1_SDATA-34

P1_SDATA-35

P1_SDATA-36

P1_SDATA-37

P1_SDATA-38

P1_SDATA-39

P1_SDATA-40

P1_SDATA-41

P1_SDATA-42

P1_SDATA-43

P1_SDATA-44

P1_SDATA-45

P1_SDATA-46

P1_SDATA-47

P1_SDATA-48

P1_SDATA-49

P1_SDATA-50

P1_SDATA-51

P1_SDATA-52

P1_SDATA-53

P1_SDATA-54

P1_SDATA-55

P1_SDATA-56

P1_SDATA-57

P1_SDATA-58

P1_SDATA-59

P1_SDATA-60

P1_SDATA-61

P1_SDATA-62

P1_SDATA-63

P1_S2K_VREF

2

P1_SDATA-[0..63] <6>

1

Set S2K_VREF to 50% of VCORE

P1_S2K_VREF

C261

C250

0.047u

0.039u

VCORE

R242

100

R244

100

A A

Title

Size Document Number Rev

B

5

4

3

2

Date: Sheet of

North Bridge AMD762-CPU1

MICRO-STAR

MS-6501

1

9 39Thursday, July 19, 2001

0A

5

D D

C C

B B

CLKOUT[0..5]<35>

CLKOUT-[0..5]<35>

A A

DDR_REF

5

C530

0.1u

C532

0.1u

(near the chip)

DDR_VREF

VCC2_5

CLKOUT0

CLKOUT1

CLKOUT2

CLKOUT3

CLKOUT4

CLKOUT5

CLKOUT-0

CLKOUT-1

CLKOUT-2

CLKOUT-3

CLKOUT-4

CLKOUT-5

4

U23E

MAA0

F17

MAA0

MAA1

G15

MAA1

MAA2

E15

MAA2

MAA3

G14

MAA3

MAA4

F14

MAA4

MAA5

E11

MAA5

MAA6

G12

MAA6

MAA7

G9

MAA7

MAA8

G11

MAA8

MAA9

G10

MAA9

MAA10

F18

MAA10

MAA11

H11

MAA11

MAA12

F9

MAA12

MAA13

G19

MAA13

MAA14

MAA[0..14]<35>

MAB[0..14]<35>

DM[0..8]<35>

CS-[0..7]<35>

RASA-<35>

RASB-<35>

CASA-<35>

CASB-<35>

WEA-<35>

WEB-<35>

CKEA<35>

CKEB<35>

DDR_REF

4

G18

MAA14

MAB0

H17

MAB0

MAB1

H15

MAB1

MAB2

F15

MAB2

MAB3

H14

MAB3

MAB4

E14

MAB4

MAB5

E12

MAB5

MAB6

G13

MAB6

MAB7

H12

MAB7

MAB8

F12

MAB8

MAB9

F11

MAB9

MAB10

H18

MAB10

MAB11

H9

MAB11

MAB12

E9

MAB12

MAB13

E20

MAB13

MAB14

E18

MAB14

DM0

B5

DM0

DM1

D8

DM1

DM2

A11

DM2

DM3

D14

DM3

DM4

E19

DM4

DM5

A22

DM5

DM6

D24

DM6

DM7

A28

DM7

DM8

C17

DM8

CS-0

H21

CS0#

CS-1

E23

CS1#

CS-2

F21

CS2#

CS-3

F23

CS3#

CS-4

H23

CS4#

CS-5

G23

CS5#

CS-6

G24

CS6#

CS-7

F24

CS7#

RASA-

G20

RASA#

RASB-

F20

RASB#

CASA-

G22

CASA#

CASB-

G21

CASB#

WEA- MDAT57

E21

WEA#

WEB-

H20

WEB#

CKEA

G8

CKEA

CKEB

F8

CLKOUT0

CLKOUT-0

CLKOUT1

CLKOUT-1

CLKOUT2

CLKOUT-2

CLKOUT3

CLKOUT-3

CLKOUT4

CLKOUT-4

CLKOUT5

CLKOUT-5

CKEB

G16

CLKOUT0

G17

CLKOUT#0

E6

CLKOUT1

F6

CLKOUT#1

E24

CLKOUT2

E25

CLKOUT#2

E16

CLKOUT3

E17

CLKOUT#3

E7

CLKOUT4

E8

CLKOUT#4

E26

CLKOUT5

F26

CLKOUT#5

D4

DDR_REF

MECC[0..7]<35>

3

AMD-762

DDR Interface

PDL_OUTPUT_TEST

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

C15

A16

A17

D17

C14

D15

MECC0

MECC1

MECC5

MECC4

MECC2

MECC3

3

MECC6

B17

A18

MECC7

MECC6

MECC7

MDAT0

MDAT1

MDAT2

MDAT3

MDAT4

MDAT5

MDAT6

MDAT7

MDAT8

MDAT9

MDAT10

MDAT11

MDAT12

MDAT13

MDAT14

MDAT15

MDAT16

MDAT17

MDAT18

MDAT19

MDAT20

MDAT21

MDAT22

MDAT23

MDAT24

MDAT25

MDAT26

MDAT27

MDAT28

MDAT29

MDAT30

MDAT31

MDAT32

MDAT33

MDAT34

MDAT35

MDAT36

MDAT37

MDAT38

MDAT39

MDAT40

MDAT41

MDAT42

MDAT43

MDAT44

MDAT45

MDAT46

MDAT47

MDAT48

MDAT49

MDAT50

MDAT51

MDAT52

MDAT53

MDAT54

MDAT55

MDAT56

MDAT57

MDAT58

MDAT59

MDAT60

MDAT61

MDAT62

MDAT63

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

AMD-AMD762

2

VCC2_5

MDAT0

C4

MDAT1

A4

MDAT2

B6

MDAT3

D6

MDAT4

C3

MDAT5

B3

MDAT6

C5

MDAT7

A6

MDAT8

C6

MDAT9

C7

MDAT10

A9

MDAT11

D9

MDAT12

A7

MDAT13

B8

MDAT14

C8

MDAT15

B9

MDAT16

E10

MDAT17

A10

MDAT18

D11

MDAT19

B12

MDAT20

C9

MDAT21

B11

MDAT22

C11

MDAT23

D12

MDAT24

A12

MDAT25

E13

MDAT26

A14

MDAT27

B15

MDAT28

C12

MDAT29

A13

MDAT30

B14

MDAT31

A15

MDAT32

B18

MDAT33

A19

MDAT34

A20

MDAT35

D20

MDAT36

C18

MDAT37

D18

MDAT38

B20

MDAT39

C20

MDAT40

B21

MDAT41

D21

MDAT42

E22

MDAT43

B23

MDAT44

A21

MDAT45

C21

MDAT46

A23

MDAT47

C23

MDAT48

D23

MDAT49

B24

MDAT50

B26

MDAT51

C26

MDAT52

A24

MDAT53

C24

MDAT54

A25

MDAT55

A26

MDAT56

C27

B27

MDAT58

C29

MDAT59

C30

MDAT60

A27

MDAT61

D26

MDAT62

D28

MDAT63

B29

DQS0

A5

DQS1

A8

DQS2

C10

DQS3

C13

DQS4

C19

DQS5

C22

DQS6

C25

DQS7

C28

DQS8

C16

TP3

D3

Place near IGD4 for VCC2_5 decoupling

MDAT[0..63] <35>

DQS[0..8] <35>

2

C542 0.1u

C541 0.1u

C540 0.1u

C361 0.1u

C357 0.1u

C539 0.1u

C360 0.1u

VCC2_5

C528 100p

C513 100p

C519 0.1u

C524 0.1u

C511 0.1u

C518 1000p

C525 0.1u

C527 0.1u

Place under IGD4 (NOPOP)

Title

Size Document Number Rev

Custom

Date: Sheet of

North Bridge AMD762-DDR

1

MICRO-STAR

MS-6501

1

10 39Wednesday, July 25, 2001

0A

5

4

3

2

1

AMD-762

D D

C C

B B

A A

A_AD[0..31]<16,17,33,36> A_AD[32..63] <16,17>

VCC3

R287

4.7K

A_CBE-[0..3]<16,17,36>

A_CBE-[0..3]

5

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE-0

A_CBE-1

A_CBE-2

A_CBE-3

A_DEVSEL-<16,17>

A_FRAME-<16,17>

A_IRDY-<16,17>

A_PAR<16,17,36>

A_SERR-<16,17>

A_STOP-<16,17>

A_TRDY-<16,17>

A_ISAREQ-<21>

TP29

A_REQ-0<17,21>

A_REQ-1<16,17>

A_REQ-2<16,17>

A_REQ-3<17>

A_REQ-4<17>

A_REQ-5<17>

A_REQ-6<17>

A_GNT-0<21>

A_GNT-1<16>

A_GNT-2<16>

PCIRST-2<13,23,32,33>

WSC-

P27

R29

P30

T25

P31

U24

R26

U25

T29

R31

V24

T27

R30

T31

U26

U27

V27

W29

V26

Y28

W31

Y29

W27

Y25

Y31

AA28

AA31

Y30

AA30

Y27

Y26

AA27

R27

V25

W25

Y24

V28

V31

H28

V29

U31

U29

U30

V30

E30

F30

H25

H27

F29

G27

E29

D31

E31

G29

H26

F28

F27

D29

AF21

J24

J25

U23C

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE0#

CBE1#

CBE2#

CBE3#

DEVSEL#

FRAME#

WSC#

IRDY#

PAR

SERR#

STOP#

TRDY#

SBREQ#

SBGNT#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

REQ5#

REQ6#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

GNT5#

GNT6#

RESET#

AMD-AMD762

PCI Bus

4

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AD39

AD40

AD41

AD42

AD43

AD44

AD45

AD46

AD47

AD48

AD49

AD50

AD51

AD52

AD53

AD54

AD55

AD56

AD57

AD58

AD59

AD60

AD61

AD62

AD63

CBE4

CBE5

CBE6

CBE7

PAR64

ACK64#

REQ64#

M66

VDD_PCI0

VDD_PCI1

VDD_PCI2

VDD_PCI3

VDD_PCI4

VDD_PCI5

VDD_PCI6

VDD_PCI7

VDD_PCI8

VDD_PCI9

VDD_PCI10

VDD_PCI20

VDD_PCI21

VDD_PCI22

VDD_PCI23

VDD_PCI24

PCI66_CLK0

PCI66_CLK1

PCI66_CLK2

PCICLK

F31

K25

G31

L24

H30

J26

H31

J28

J30

J29

J31

L25

J27

M24

K27

K29

L26

L28

L27

L29

K31

M28

L30

M25

L31

P24

M26

M29

M27

N25

N27

R24

R25

M31

N29

N31

M30

R28

P26

U28

D30

G30

K26

K30

N26

N30

T26

T30

W26

W30

G26

L23

N23

R23

U23

W23

SR_PCI66CLK0

P25

SR_PCI66CLK1

P28

SR_PCI66CLK2

P29

AH21

A_AD32

A_AD33

A_AD34

A_AD35

A_AD36

A_AD37

A_AD38

A_AD39

A_AD40

A_AD41

A_AD42

A_AD43

A_AD44

A_AD45

A_AD46

A_AD47

A_AD48

A_AD49

A_AD50

A_AD51

A_AD52

A_AD53

A_AD54

A_AD55

A_AD56

A_AD57

A_AD58

A_AD59

A_AD60

A_AD61

A_AD62

A_AD63

A_CBE-4

A_CBE-5

A_CBE-6

A_CBE-7

PAR64

ACK64REQ64-

A_M66EN

VCC3

PLL_PICCLK

PAR64 <16,17>

ACK64- <16,17>

REQ64- <16,17>WSC-<21>

AGP_CAL-

AGP_CAL

R501 47

R503 47

R504 22

R645 22

A_CBE-[4..7] <16,17>

VCC3

R273

4.7K

R275

4.7K

NOPOP

R252 27.4_1%

R268 34.8_1%

PLL_PICCLK

3

VDDQ

PCI_66CLK0 <16>

PCI_66CLK1 <16>

PCI_66CLK2 <21>

GAD[0..31]<15>

A_M66EN <16,21>

GAD[0..31]

GCLK0<3>

AGP_VREF2X

(near the chip)

R237

100

Reserved

C239

100p

Reserved

C259

0.01u

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

VDDQ

R249 150

R245

100

2

AB31

AA26

AC31

AA25

AC30

AB29

AD31

AC26

AC27

AG31

AC29

AH31

AB25

AD29

AC28

AE29

AD26

AH28

AJ30

AG29

AK29

AF27

AH29

AG27

AL28

AJ26

AD25

AF24

AG26

AG24

AF23

AE25

AJ21

AA23

AB26

AB30

AC23

AF22

AE26

AE30

AH30

AK22

AK25

AK28

AF25

Y22

AB22

AC21

AB20

U23D

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

AGPCLK

VDD_AGP0

VDD_AGP1

VDD_AGP2

VDD_AGP3

VDD_AGP4

VDD_AGP5

VDD_AGP6

VDD_AGP7

VDD_AGP8

VDD_AGP9

VDD_AGP10

VDD_AGP11

VDD_AGP12

VDD_AGP13

VDD_AGP14

VDD_AGP15

AMD-AMD762

AMD-762

VDDQ

AGP Bus

GDEVSEL#

AGP_VREF4X

AGP_VREF

AGP_CAL#VDD_AGP15

AB27

GCBE0#

AD28

GCBE1#

AJ29

GCBE2#

AF26

GCBE3#

AC24

AF29

GFRAME#

AE27

GSERR#

AK27

GSTOP#

AF30

GTRDY#

AF28

GIRDY#

AD27

GPAR

AK26

WBF#

AL25

PIPE#

AL26

RBF#

AL23

GGNT#

AK23

GREQ#

AK24

ST0

AL24

ST1

AJ23

ST2

AE31

ADSTB0

AD30

ADSTB0#

AJ27

ADSTB1

AJ28

ADSTB1#

AG23

SBA0

AE23

SBA1

AJ25

SBA2

AD23

SBA3

AE24

SBA4

AG25

SBA5

AL27

SBA6

AH26

SBA7

AJ24

SBSTB

AH24

SBSTB#

AC25

AG30

AA24

AGP_CAL

AF31AA21

AGP_VREF4X_IN

C257

C262

1u

0.01u

GCBE0- <15>

GCBE1- <15>

GCBE2- <15>

GCBE3- <15>

GDEVSEL- <15>

GFRAME- <15>

GSERR- <15>

GSTOP- <15>

GTRDY- <15>

GIRDY- <15>

GPAR <15>

WBF- <15>

PIPE- <15>

RBF- <15>

GGNT- <15>

GREQ- <15>

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SBSTB

SBSTB-

AGP_VREF4X_IN

AGP_VREF2X

AGP_CAL

AGP_CAL-

AGP_VREF4X_IN <15>

C254

0.1u

SBSTB <15>

SBSTB- <15>

ST0 <15>

ST1 <15>

ST2 <15>

ADSTB0 <15>

ADSTB0- <15>

ADSTB1 <15>

ADSTB1- <15>

SBA[0..7]

MICRO-STAR

Title

Size Document Number Rev

B

Date: Sheet of

AMD-762 (PCI & AGP)

MS-6501

1

11 39Wednesday, July 25, 2001

SBA[0..7] <15>

0A

5

D D

C C

B B

FB21

VCC2_5

600_0805

A A

Power for clock PLL.

MUST close to

AMD-762

5

C495

100p

C492

4.7u-0805

C491

4.7u-0805

TP2

TP1

4

AMD-762

U23F

AA11 D2

VDD_CORE P0_K7_VCORE0

AA13

VDD_CORE

AA15

VDD_CORE

AA17

VDD_CORE

AA19

VDD_CORE

B10

VDD_CORE

B13

VDD_CORE

B16

VDD_CORE

B19

VDD_CORE

B22

VDD_CORE

B25

VDD_CORE

B28

VDD_CORE

B4

VDD_CORE

B7

VDD_CORE

F10

VDD_CORE

F13

VDD_CORE

F16

VDD_CORE

F19

VDD_CORE

F22

VDD_CORE

F25

VDD_CORE

J11

VDD_CORE

J13

VDD_CORE

J15

VDD_CORE

J17

VDD_CORE

J19

VDD_CORE

J21

VDD_CORE

J23

VDD_CORE

J9

VDD_CORE

K10

VDD_CORE

K12

VDD_CORE

K14

VDD_CORE

K16

VDD_CORE

K18

VDD_CORE

K20

VDD_CORE

K22

VDD_CORE

L11

VDD_CORE

L13

VDD_CORE

L15

VDD_CORE

L17

VDD_CORE

L19

VDD_CORE

L21

VDD_CORE

M12

VDD_CORE

M14

VDD_CORE

M16

VDD_CORE

M18

VDD_CORE

M20

VDD_CORE

M22

VDD_CORE

N11

VDD_CORE

N13

VDD_CORE

N15

VDD_CORE

N17

VDD_CORE

N19

VDD_CORE

N21

VDD_CORE

P12

VDD_CORE

P14

VDD_CORE

P16

VDD_CORE

P18

VDD_CORE

P20

VDD_CORE

P22

VDD_CORE

R11

VDD_CORE

R13

VDD_CORE

R15

VDD_CORE

R17

VDD_CORE

R19

VDD_CORE

R21

VDD_CORE

T12

VDD_CORE

T14

VDD_CORE

T16

VDD_CORE

T18

VDD_CORE

T20

VDD_CORE

T22

VDD_CORE

U11

VDD_CORE

U13

VDD_CORE

U15

VDD_CORE

U17

VDD_CORE

U19

VDD_CORE

U21

VDD_CORE

V12

VDD_CORE

V14

VDD_CORE

V16

VDD_CORE

V18

VDD_CORE

V20

VDD_CORE

V22

VDD_CORE

W11

VDD_CORE

W13

VDD_CORE

W15

VDD_CORE

W17

VDD_CORE

W19

VDD_CORE

W21

VDD_CORE

Y12

VDD_CORE

Y14

VDD_CORE

Y16

VDD_CORE

Y18

VDD_CORE

Y20

VDD_CORE

F7

VDD_CORE

AG22

AVDD

AE1

SI_VDD

AD2

SI_VSS

4

POWER

P0_K7_VCORE1

P0_K7_VCORE2

P0_K7_VCORE3

P0_K7_VCORE4

P0_K7_VCORE5

P0_K7_VCORE6

P0_K7_VCORE7

P0_K7_VCORE8

P0_K7_VCORE9

P0_K7_VCORE10

P0_K7_VCORE11

P0_K7_VCORE12

P0_K7_VCORE13

P0_K7_VCORE14

P0_K7_VCORE15

P0_K7_VCORE16

P0_K7_VCORE17

P0_K7_VCORE18

P0_K7_VCORE19

P0_K7_VCORE20

P0_K7_VCORE21

P0_K7_VCORE22

P0_K7_VCORE23

P1_K7_VCORE0

P1_K7_VCORE1

P1_K7_VCORE2

P1_K7_VCORE3

P1_K7_VCORE4

P1_K7_VCORE5

P1_K7_VCORE6

P1_K7_VCORE7

P1_K7_VCORE8

P1_K7_VCORE9

P1_K7_VCORE10

P1_K7_VCORE11

P1_K7_VCORE12

P1_K7_VCORE13

P1_K7_VCORE14

P1_K7_VCORE15

P1_K7_VCORE16

P1_K7_VCORE17

P1_K7_VCORE18

P1_K7_VCORE19

P1_K7_VCORE20

P1_K7_VCORE21

P1_K7_VCORE22

P1_K7_VCORE23

P1_K7_VCORE24

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC26

NC27

NC28

NC31

NC32

REF_5V

ROM_SDA

ROM_SCK

DEBUG0

DEBUG1

DEBUG2

PX_CAL

PX_CAL#

SYSCLKREF

TEST#

DCSTOP#

AMD-AMD762

G2

K2

N2

T2

W2

AB2

G6

K6

N6

T6

W6

AB6

L9

N9

R9

U9

W9

AA9

Y10

V10

T10

P10

M10

AE2

AH2

AK4

AK7

AK10

AK13

AK16

AK19

AF7

AF10

AF13

AF16

AF19

AC9

AC11

AC13

AC15