Mitsubishi M30612M8A-XXXGP, M30612M8A-XXXFP, M30612M4A-XXXGP, M30612M4A-XXXFP, M30612E4GP Datasheet

...

|

Mitsubishi microcomputers |

Description |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

Description

The M16C/61 group of single-chip microcomputers are built using the high-performance silicon gate CMOS process using a M16C/60 Series CPU core and are packaged in a 100-pin plastic molded QFP. These single-chip microcomputers operate using sophisticated instructions featuring a high level of instruction efficiency. With 1M bytes of address space, they are capable of executing instructions at high speed. They also feature a built-in multiplier and DMAC, making them ideal for controlling office, communications, industrial equipment, and other high-speed processing applications.

The M16C/61 group includes a wide range of products with different internal memory types and sizes and various package types.

Features

• Memory capacity ............................................ |

ROM (See Figure 1.1.4. ROM Expansion) |

|

RAM 4K to 10K bytes |

• Shortest instruction execution time ................ |

100ns (f(XIN)=10MHZ) |

• Supply voltage ............................................... |

4.0 to 5.5V (f(XIN)=10MHZ) |

|

2.7 to 5.5V (f(XIN)=7MHZ with software one-wait) |

• Low power consumption ................................ |

18mW ( f(XIN)=7MHZ, with software one-wait, VCC = 3V) |

• Interrupts........................................................ |

20 internal and 5 external interrupt sources, 4 software |

|

interrupt sources; 7 levels (including key input interrupt) |

• Multifunction 16-bit timer ................................ |

5 output timers + 3 input timers |

• Serial I/O (UART or clock synchronous) ........ |

3 channels |

• DMAC ............................................................ |

2 channels (trigger: 16 sources) |

• A-D converter................................................. |

10 bits X 8 channels |

|

(Expandable up to 10 channels) |

• D-A converter................................................. |

8 bits X 2 channels |

• CRC calculation circuit ................................... |

1 circuit |

• Watchdog timer .............................................. |

1 line |

• Programmable I/O ......................................... |

87 lines |

• Input port |

_______ |

1 line (P85 shared with NMI pin) |

|

• Memory expansion ........................................ |

Available (to a maximum of 1M bytes) |

• Chip select output .......................................... |

4 lines |

• Clock generating circuit ................................. |

2 built-in clock generation circuits |

|

(built-in feedback resistor, and external ceramic or quartz oscillator) |

Applications |

|

Audio, cameras, office equipment, communications equipment, portable equipment

------Table of Contents------

Central Processing Unit (CPU) ..................... |

11 |

Reset ............................................................. |

14 |

Processor Mode ............................................ |

19 |

Clock Generating Circuit ............................... |

30 |

Protection ...................................................... |

39 |

Interrupts ....................................................... |

40 |

Watchdog Timer ............................................ |

59 |

DMAC ........................................................... |

61 |

Timer ............................................................. |

70 |

Serial I/O ....................................................... |

87 |

A-D Converter ............................................. |

114 |

D-A Converter ............................................. |

124 |

CRC Calculation Circuit .............................. |

126 |

Programmable I/O Ports ............................. |

128 |

Electrical Characteristics ............................. |

142 |

1

|

Mitsubishi microcomputers |

Description |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

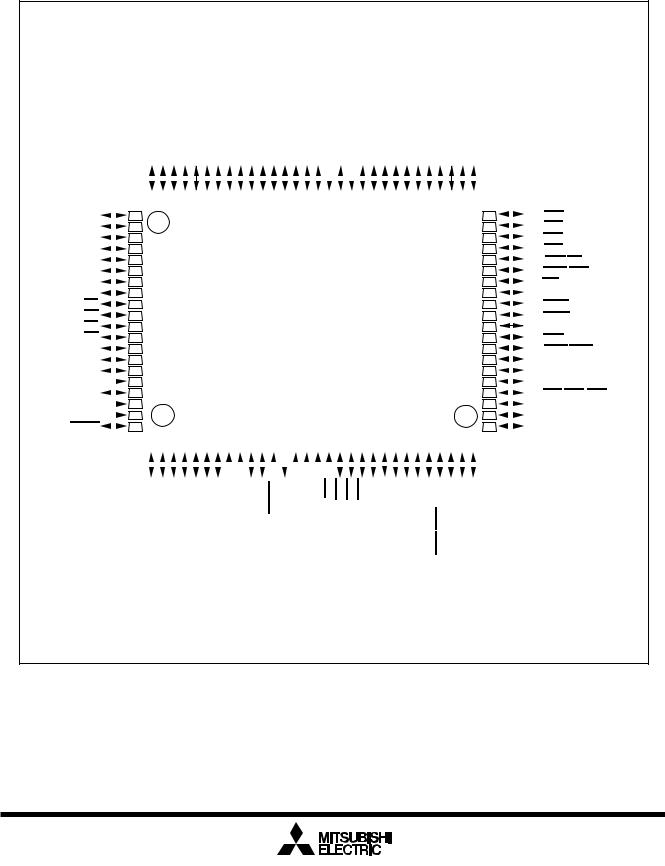

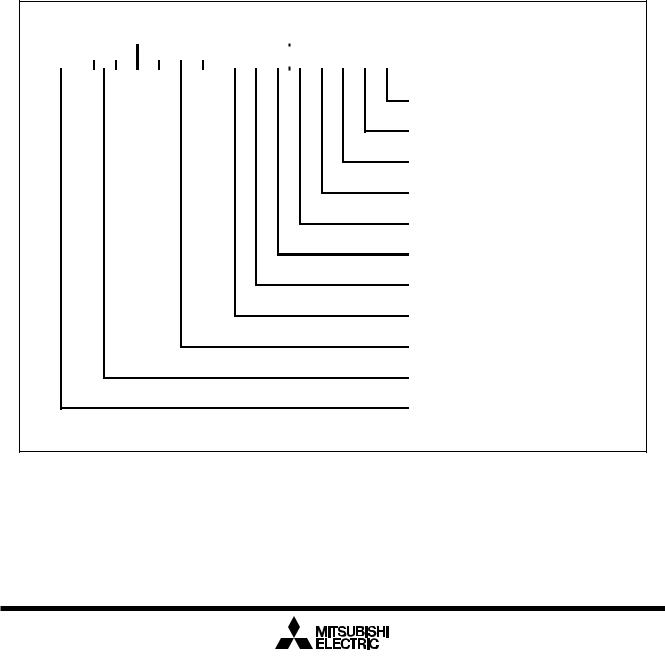

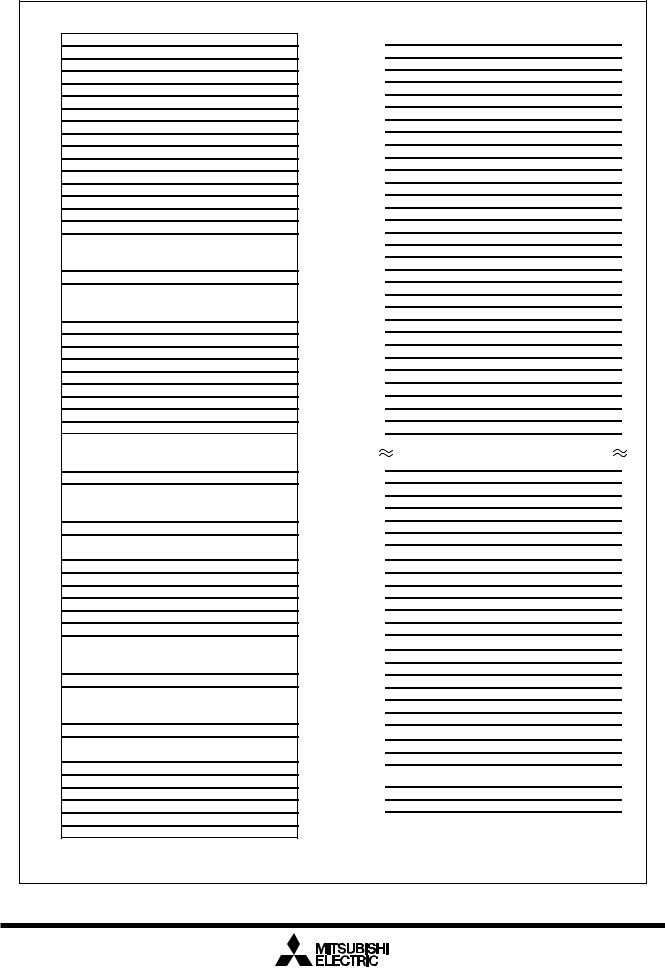

Pin Configuration

Figures 1.1.1 and 1.1.2 show the pin configurations (top view).

PIN CONFIGURATION (top view)

|

|

|

|

|

|

|

|

P1/D08 |

P1/D19 |

P1/D210 |

/DP1311 |

P1/D412 |

P1/D513 |

P1/D614 |

P1/D715 |

P2/A(/D/-)000 |

P2/A(/D/D)1011 |

/A(/D/D)P22122 |

/A(/D/D)P22333 |

/A(/D/D)P24443 |

(/D/D)P2/A5554 |

/D)P2/A(/D6665 |

/D)P2/A(/D7776 |

Vss P3/A(/-/D)087 |

Vcc |

P3/A91 |

P3/A210 |

P3/A311 |

P3/A412 |

/AP3513 |

/AP3614 |

P3/A715 |

P4/A016 |

P4/A117 |

P4/A218 |

P4/A193 |

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

80 |

79 |

78 |

77 |

76 |

75 |

74 |

73 |

72 |

71 |

70 |

69 |

68 |

67 |

66 |

65 |

64 |

63 |

62 |

61 |

60 |

59 |

58 |

57 |

56 |

55 |

54 |

53 |

52 |

51 |

|

|

|

|

|

|||||||||||||||||||||||||||||||

P07/D7 |

|

|

|

81 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

|

|

P44/CS0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

P06/D6 |

|

|

|

82 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

|

|

P45/CS1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

P05/D5 |

|

|

|

83 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

|

P46/CS2 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

P04/D4 |

|

|

|

84 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

|

P47/CS3 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

P03/D3 |

|

|

|

85 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

|

P50/WRL/WR |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

P02/D2 |

|

|

|

86 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

|

P51/WRH/BHE |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P01/D1 |

|

|

|

87 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

|

P52/RD |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

P00/D0 |

|

|

|

88 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

|

|

P53/BCLK |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P107/AN7/KI3 |

89 |

|

|

|

|

|

|

|

|

|

|

|

|

|

M16C/61 Group |

|

|

|

|

|

|

|

|

|

|

|

|

|

42 |

|

|

P54/HLDA |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||

P106/AN6/KI2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

|

|

P56/ALE |

|||||||||||||||||||||||||||||||||||||

|

|

|

90 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

|

|

P55/HOLD |

|||

P105/AN5/KI1 |

|

|

|

91 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

P104/AN4/KI0 |

|

|

|

92 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

|

P57/RDY/CLKOUT |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P103/AN3 |

|

|

|

93 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

|

P60/CTS0/RTS0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P102/AN2 |

|

|

|

94 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

P61/CLK0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

P101/AN1 |

|

|

|

95 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

|

P62/RxD0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

AVSS |

|

|

|

96 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

|

P63/TXD0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P100/AN0 |

|

|

97 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

|

|

P64/CTS1/RTS1/CTS0/CLKS1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

VREF |

|

|

|

98 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

P65/CLK1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

AVcc |

|

|

|

|

99 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

P66/RxD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

P97/ADTRG |

|

|

100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

|

P67/TXD1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

30 |

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

P9/ANEX16 |

P9/ANEX05 |

P9/DA41 |

/DAP930 |

P9/TB2IN2 |

P9/TB11IN |

P9/TB00IN |

BYTE |

CNVss |

P8/X7CIN |

P8/X6COUT |

RESET |

XOUT |

VSS |

XIN |

VCC |

P8/NMI5 |

P8/INT24 |

P8/INT31 |

P8/INT20 |

P8/TA41IN |

/TA4P80OUT |

P7/TA3IN7 |

P7/TA36OUT |

P7/TA25IN |

P7/TA24OUT |

/RTS/TA1P7/CTS322IN |

P7/CLK/TA1OUT22 |

(Note)P7/RxD/TA012IN |

/TxD/TA0(Note)P702OUT |

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Package: 100P6S-A |

|||

Note: P70 and P71 are N channel open-drain output pin.

Figure 1.1.1. Pin configuration (top view)

2

|

Mitsubishi microcomputers |

Description |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

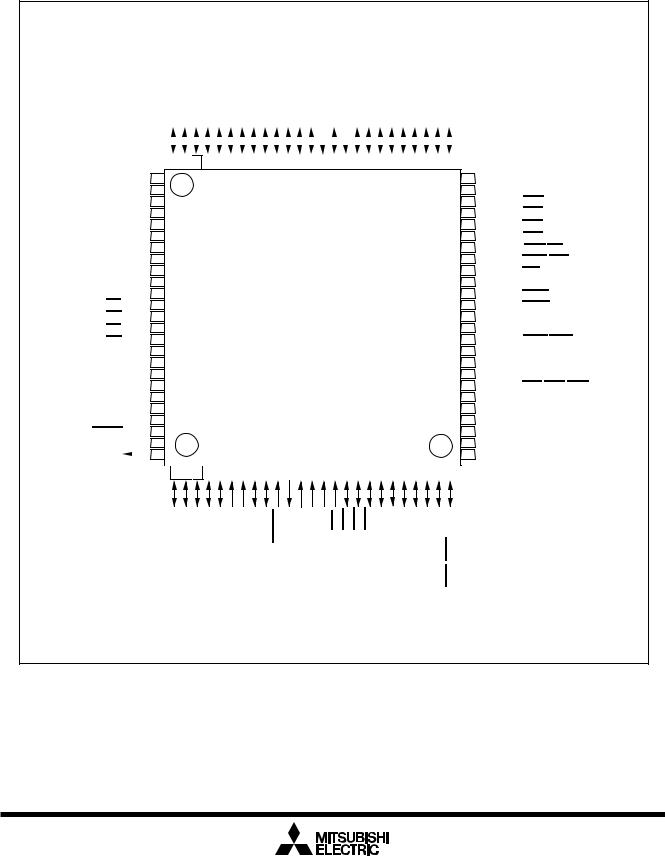

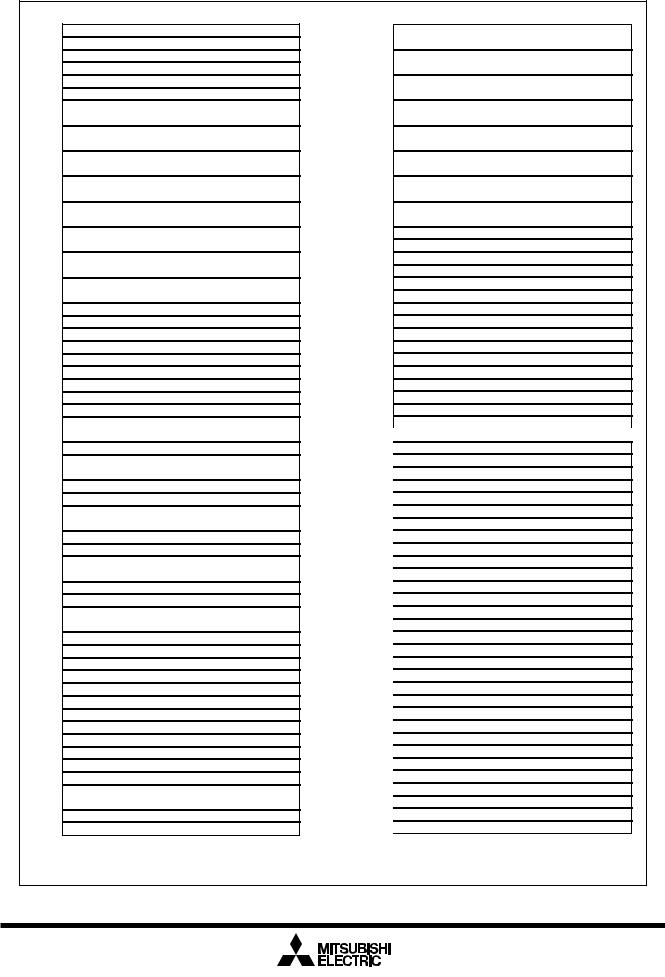

PIN CONFIGURATION (top view)

P1/D311 |

P1/D412 |

P1/D513 |

|||

|

|

|

|

|

|

|

|

|

|

73 |

|

75 |

74 |

||||

P12/D10

76

76

P11/D9

77

77

P10/D8

78

78

P07/D7

79

79

P06/D6

80

80

P05/D5

81

81

P04/D4

82

82

P03/D3

83

83

P02/D2

84

84

P01/D1

85

85

P00/D0

86

86

P107/AN7/KI3

87

87

P106/AN6/KI2

88

88

P105/AN5/KI1

89

89

P104/AN4/KI0

90

90

P103/AN3

91

91

P102/AN2

92

92

P101/AN1

93

93

AVSS  94

94

P100/AN0

95

95

VREF  96

96

AVcc 97

97

P97/ADTRG

98

98

P96/ANEX1

99

99

P95/ANEX0  100

100

1

2

2

3

3

/DA1 /DA0 /TB2IN P94 P93 2 P9

P1/D614 |

P1/D715 |

P2/A(/D/-)000 |

)P2/A(/D/D1110 |

/A(/D/D)P22221 |

/A(/D/D)P23332 |

P2/A(/D/D)4344 |

/A(/D/D)P25554 |

/D)P2/A(/D6665 |

P2/A(/D/D)6777 |

Vss |

(/-/D)P3/A087 |

Vcc |

/AP319 |

P3/A210 |

P3/A311 |

/AP3412 |

P3/A135 |

P3/A614 |

P3/A715 |

P4/A016 |

P4/A117 |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

72 |

71 |

70 |

69 |

68 |

67 |

66 |

65 |

64 |

63 |

62 |

61 |

60 |

59 |

58 |

57 |

56 |

55 |

54 |

53 |

52 |

51 |

||||||||||||||||||||||

M16C/61 Group

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

P9/TB11IN |

P9/TB00IN |

BYTE CNVss P8/X7CIN |

P8/X6COUT |

RESET XOUT |

VSS |

XIN |

VCC |

P8/NMI5 |

/INTP842 |

P8/INT31 |

P8/INT20 |

P8/TA41IN |

P8/TA40OUT |

P7/TA37IN |

P7/TA36OUT |

P7/TA2IN5 |

/TA2P74OUT |

/RTS/TA1IN2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P7/CTS32 |

50

P42/A18

P42/A18

49

P43/A19

P43/A19

48

P44/CS0

P44/CS0

47

P45/CS1

P45/CS1

46

P46/CS2

P46/CS2

45

P47/CS3

P47/CS3

44

P50/WRL/WR

P50/WRL/WR

43

P51/WRH/BHE

P51/WRH/BHE

42

P52/RD

P52/RD

41

P53/BCLK

P53/BCLK

40

P54/HLDA

P54/HLDA

39

P55/HOLD

P55/HOLD

38

P56/ALE

P56/ALE

37

P57/RDY/CLKOUT

P57/RDY/CLKOUT

36

P60/CTS0/RTS0 35

P60/CTS0/RTS0 35

P61/CLK0

P61/CLK0

34

P62/RxD0

P62/RxD0

33

P63/TXD0

P63/TXD0

32

P64/CTS1/RTS1/CTS0/CLKS1

P64/CTS1/RTS1/CTS0/CLKS1

31

P65/CLK1

P65/CLK1

30

P66/RxD1

P66/RxD1

29

P67/TXD1

P67/TXD1

28

P70/TxD2/TA0OUT(Note)

P70/TxD2/TA0OUT(Note)

27

P71/RxD2/TA0IN(Note)

P71/RxD2/TA0IN(Note)

26

P72/CLK2/TA1OUT

P72/CLK2/TA1OUT

Package: 100P6Q-A

Note: P70 and P71 are N channel open-drain output pin.

Figure 1.1.2. Pin configuration (top view)

3

|

Mitsubishi microcomputers |

Description |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

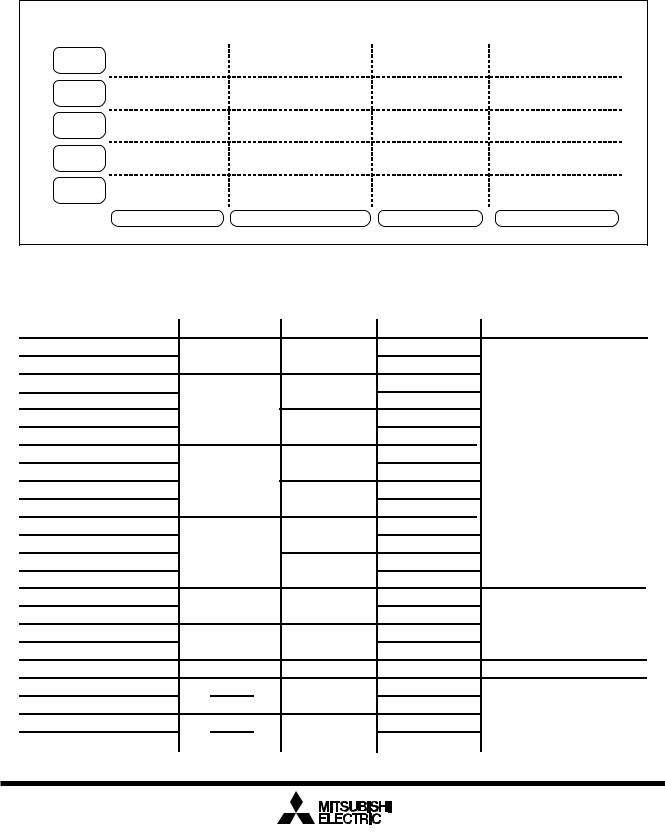

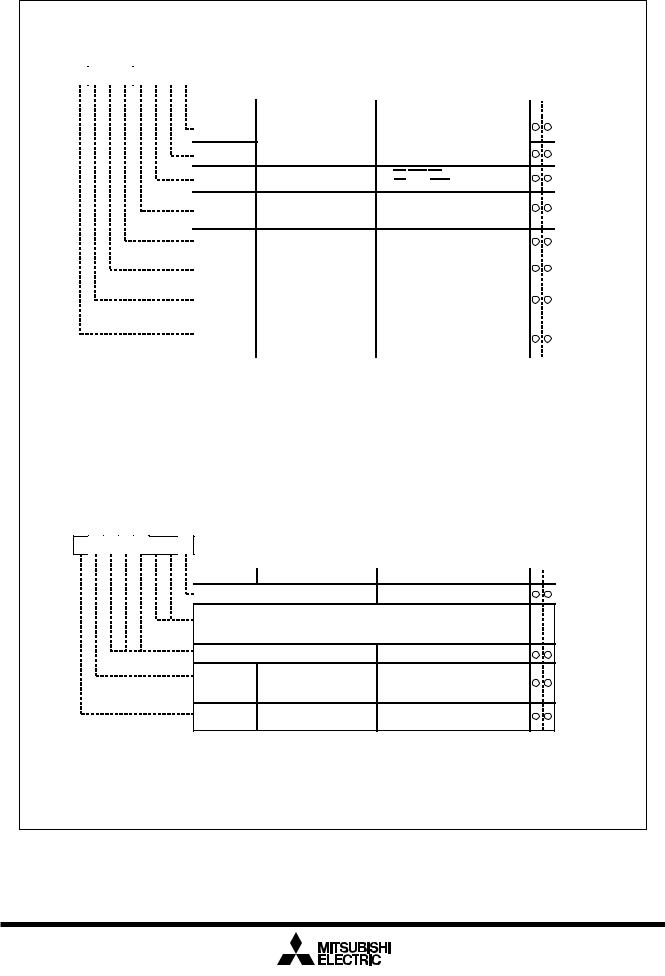

Block Diagram

Figure 1.1.3 is a block diagram of the M16C/61 group.

Block diagram of the M16C/61 group

I/O ports

|

8 |

|

8 |

8 |

|

8 |

|

8 |

|

|

8 |

|

8 |

||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Port P0 |

|

Port P1 |

|

Port P2 |

|

Port P3 |

|

Port P4 |

|

Port P5 |

|

Port P6 |

|||||||

Internal peripheral functions |

A-D converter |

System clock generator |

|||

|

|||||

Timer |

(10 bits X 8 channels |

|

XIN-XOUT |

||

Timer TA0 (16 bits) |

Expandable up to 10 channels) |

XCIN-XCOUT |

|||

|

|

|

|

|

|

Timer TA1 (16 bits) |

|

|

|

|

|

Timer TA2 (16 bits) |

UART/clock synchronous SI/O |

|

|||

Timer TA3 (16 bits) |

(8 bits X 3channels) (Note 3) |

|

|||

|

|

|

|

|

|

Timer TA4 (16 bits) |

CRC arithmetic circuit (CCITT ) |

|

|||

Timer TB0 (16 bits) |

|

||||

Timer TB1 (16 bits) |

(Polynomial : X16+X12+X5+1) |

|

|||

|

|

|

|

|

|

Timer TB2 (16 bits) |

M16C/60 series16-bit CPU core |

Memory |

|||

|

|||||

|

Registers |

Program counter |

ROM |

||

Watchdog timer |

|

|

(Note 1) |

||

R0H |

R0L |

|

PC |

||

(15 bits) |

R0H |

R0L |

|

|

RAM |

R1H |

R1L |

|

|

||

|

R1H |

R1L |

|

Vector table |

(Note 2) |

|

R2 |

|

|||

DMAC |

|

R2 |

|

INTB |

|

|

R3 |

|

|

||

|

R3 |

|

|

|

|

(2 channels) |

A0 |

|

Stack pointer |

|

|

|

A0 |

|

|

||

|

A1 |

|

|

|

|

|

|

A1 |

|

ISP |

|

D-A converter |

FB |

|

|

||

|

FB |

|

USP |

Multiplier |

|

(8 bits X 2 channels) |

|

|

|

||

|

|

|

|

||

|

|

SB |

|

FLG |

|

Note 1: ROM size depends on MCU type.

Note 2: RAM size depends on MCU type.

Note 3: One of serial I/O can use for SIM interface.

P7Port |

|

8 |

|

P8Port |

|

7 |

|

5P8Port |

|

|

|

P9Port |

|

8 |

|

P10Port |

|

8 |

Figure 1.1.3. Block diagram of M16C/61 group

4

|

Mitsubishi microcomputers |

Description |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

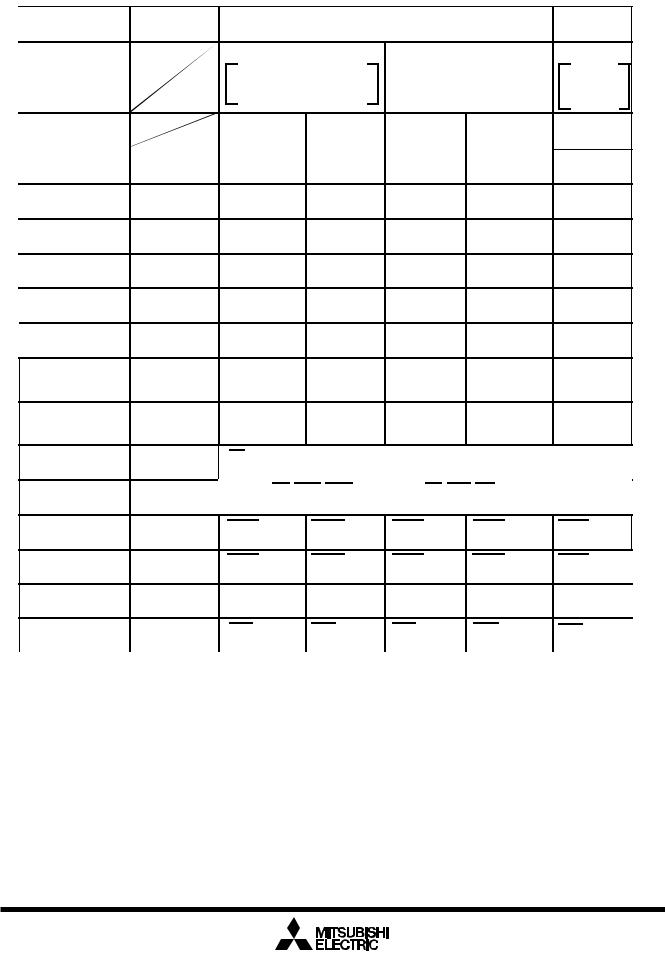

Performance Outline

Table 1.1.1 is a performance outline of M16C/61 group.

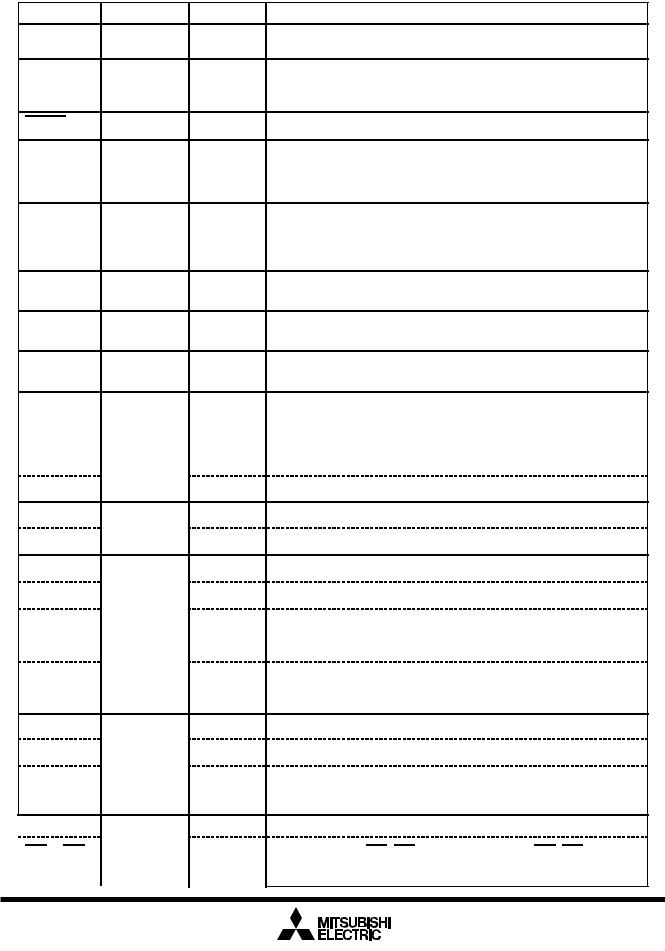

Table 1.1.1. Performance outline of M16C/61 group

|

|

Item |

Performance |

|

|

|

|

Number of basic instructions |

91 instructions |

||

|

|

|

|

Shortest instruction execution time |

100ns(f(XIN)=10MHZ) |

||

|

|

|

|

Memory |

|

ROM |

(See the Figure 4. ROM Expansion) |

|

|

|

|

capacity |

|

RAM |

4K to 10K bytes |

|

|

|

|

I/O port |

|

P0 to P10 (except P85) |

8 bits x 10, 7 bits x 1 |

|

|

|

|

Input port |

|

P85 |

1 bit x 1 |

|

|

|

|

Multifunction |

|

TA0, TA1, TA2, TA3, TA4 |

16 bits x 5 |

|

|

|

|

timer |

|

TB0, TB1, TB2 |

16 bits x 3 |

|

|

|

|

Serial I/O |

|

UART0, UART1, UART2 |

(UART or clock synchronous) x 3 |

|

|

|

|

A-D converter |

|

10 bits x (8 + 2) channels |

|

|

|

|

|

D-A converter |

|

8 bits x 2 |

|

|

|

|

|

DMAC |

|

2 channels (trigger: 16 sources) |

|

|

|

|

|

CRC calculation circuit |

CRC - CCITT |

||

|

|

|

|

Watchdog timer |

|

15 bits x 1 (with prescaler) |

|

|

|

|

|

Interrupt |

|

20 internal and 5 external sources, 4 software sources, 7 levels |

|

|

|

|

|

Clock generating circuit |

2 built-in clock generation circuits |

||

|

|

|

(built-in feedback resistor, and external ceramic or quartz oscillator) |

|

|

|

|

Supply voltage |

|

4.0 to 5.5V (f(XIN ) = 10MHZ) |

|

|

|

|

2.7 to 5.5V(f(XIN)=7MHZ with software one-wait) |

|

|

|

|

Power consumption |

|

18mW (f(XIN) = 7MHZ with software one-wait,VCC = 3V) |

|

|

|

|

|

I/O |

|

I/O withstand voltage |

5V |

characteristics |

|

|

|

|

Output current |

5mA |

|

|

|

|

|

Memory expansion |

|

Available (to a maximum of 1M bytes) |

|

|

|

|

|

Device configuration |

|

CMOS silicon gate |

|

|

|

|

|

Package |

|

100-pin plastic mold QFP |

|

|

|

|

|

5

|

Mitsubishi microcomputers |

Description |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

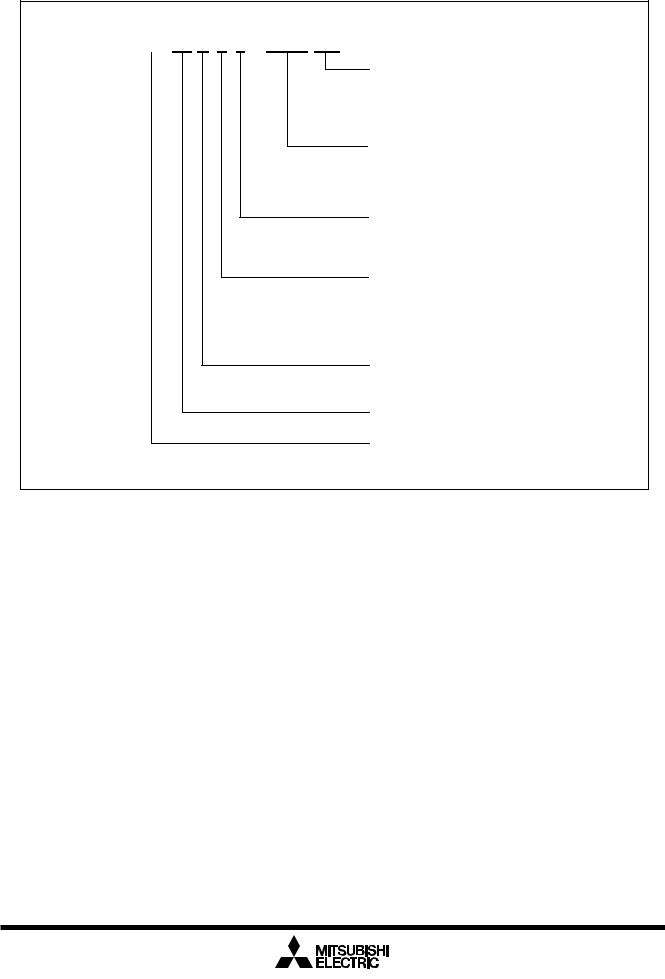

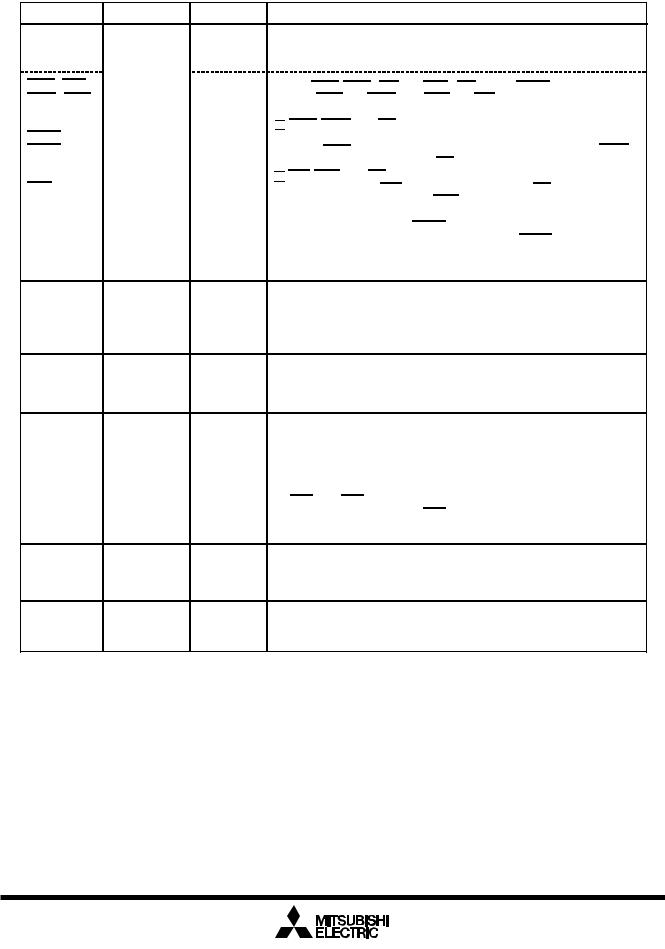

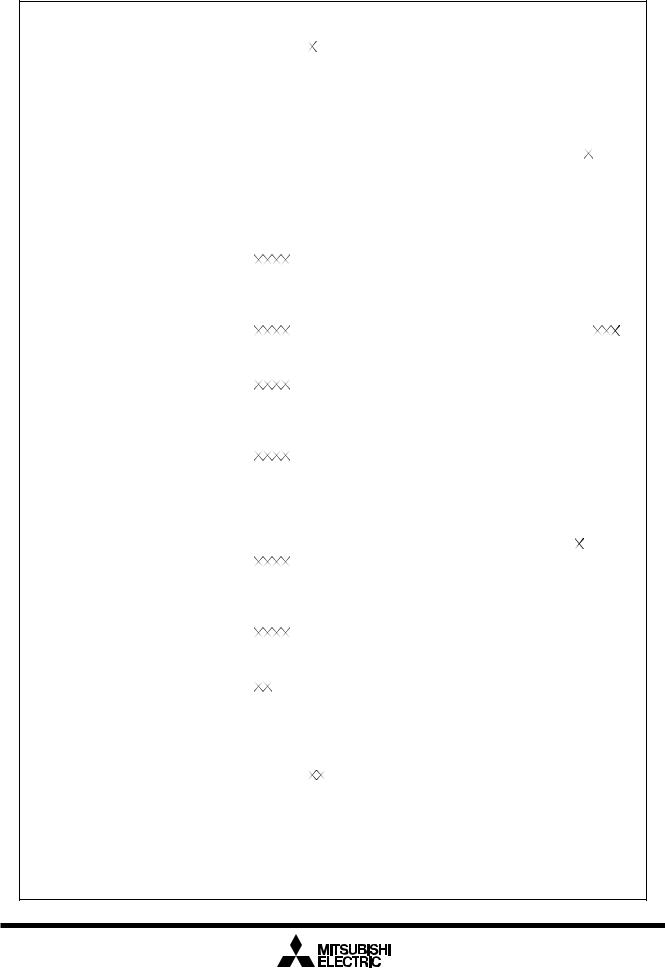

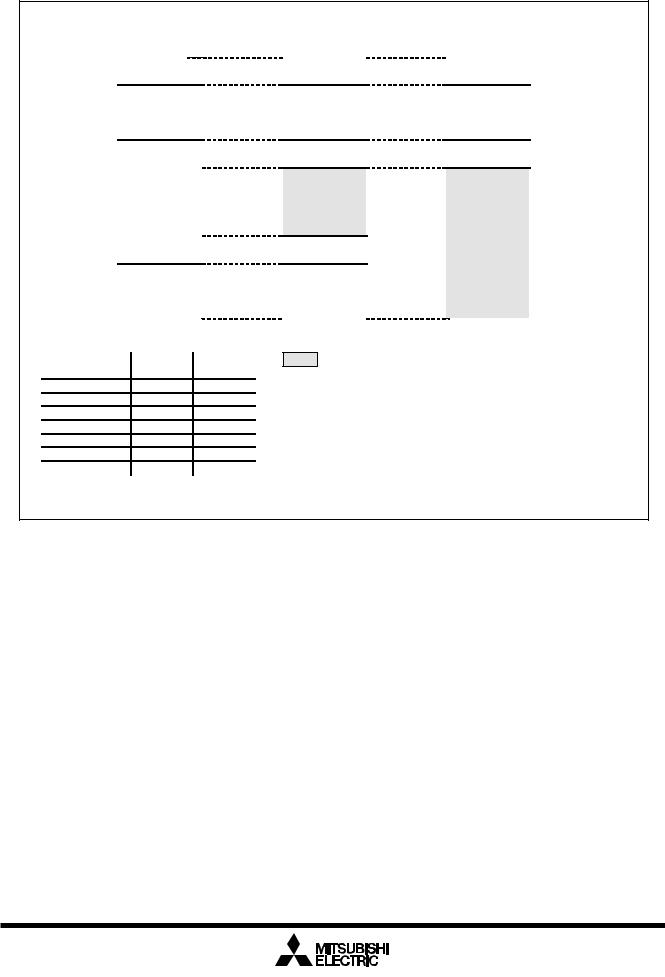

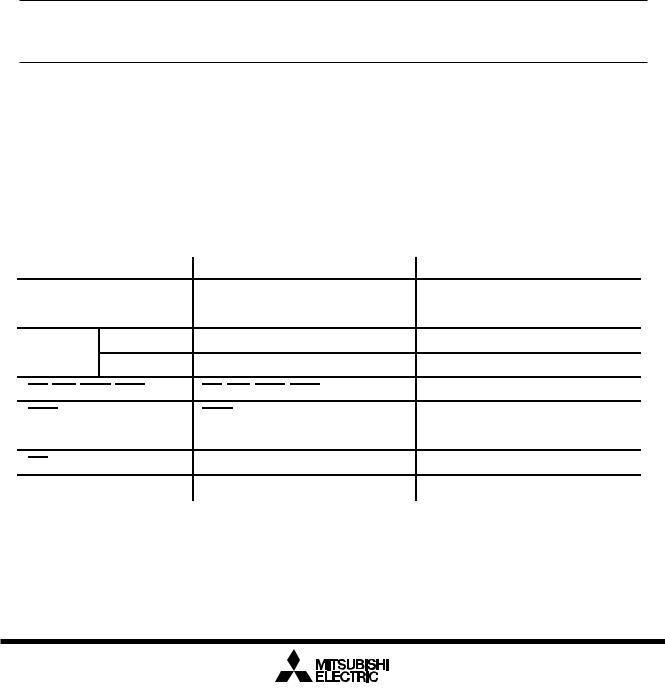

Mitsubishi plans to release the following products in the M16C/61 group:

(1)Support for mask ROM version, external ROM version, one-time PROM version, and EPROM version

(2)ROM capacity

(3)Package

100P6S-A : Plastic molded QFP (mask ROM version and one-time PROM version) 100P6Q-A : Plastic molded QFP (mask ROM version and one-time PROM version) 100D0 : Ceramic LCC (EPROM version)

ROM |

|

|

|

|

Size(Byte) |

|

|

|

|

External |

|

|

|

M30612SAFP/GP |

ROM |

|

|

|

M30610SAFP/GP |

128 K |

M30610MCA-XXXFP/GP |

M30610ECFP/GP |

M30610ECFS |

|

M30612MCA-XXXFP/GP |

|

|||

|

|

|

|

|

96 K |

M30610MAA-XXXFP/GP |

|

|

|

M30612MAA-XXXFP/GP |

|

|

|

|

64 K |

M30610M8A-XXXFP/GP |

|

|

|

M30612M8A-XXXFP/GP |

|

|

|

|

|

|

|

|

|

32 K |

M30612M4A-XXXFP/GP |

M30612E4FP/GP |

|

|

|

Mask ROM version |

One-time PROM version |

EPROM version |

External ROM version |

Figure 1.1.4. ROM expansion

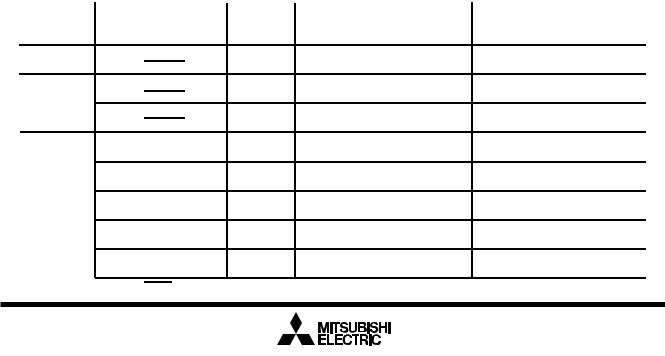

The M16C/61 group products currently supported are listed in Table 2.

Table 1.1.2. M16C/61 group |

|

|

Apr. 1999 |

||

Type No |

ROM capacity |

RAM capacity |

Package type |

Remarks |

|

M30612M4A-XXXFP |

32K byte |

4K byte |

100P6S-A |

|

|

|

|||||

M30612M4A-XXXGP |

100P6Q-A |

|

|||

|

|||||

|

|

|

|||

M30610M8A-XXXFP |

|

10K byte |

100P6S-A |

|

|

|

|

||||

M30610M8A-XXXGP |

64K byte |

100P6Q-A |

|

||

|

|||||

|

|

||||

M30612M8A-XXXFP |

4K byte |

100P6S-A |

|

||

|

|||||

|

|

||||

M30612M8A-XXXGP |

|

100P6Q-A |

|

||

|

|

||||

|

|

|

|||

M30610MAA-XXXFP |

|

10K byte |

100P6S-A |

|

|

|

|

||||

M30610MAA-XXXGP |

96K byte |

100P6Q-A |

Mask ROM version |

||

|

|||||

M30612MAA-XXXFP |

4K byte |

100P6S-A |

|||

|

|

||||

M30612MAA-XXXGP |

|

100P6Q-A |

|

||

|

|

||||

|

|

|

|||

M30610MCA-XXXFP |

|

10K byte |

100P6S-A |

|

|

|

|

||||

M30610MCA-XXXGP |

128K byte |

100P6Q-A |

|

||

|

|||||

|

|

||||

M30612MCA-XXXFP |

5K byte |

100P6S-A |

|

||

|

|||||

|

|

||||

M30612MCA-XXXGP |

|

100P6Q-A |

|

||

|

|

||||

|

|

|

|||

M30612E4FP |

32K byte |

4K byte |

100P6S-A |

|

|

|

|||||

M30612E4GP |

100P6Q-A |

One-time PROM version |

|||

|

|

||||

M30610ECFP |

128K byte |

10K byte |

100P6S-A |

||

|

|||||

M30610ECGP |

100P6Q-A |

|

|||

|

|||||

|

|

|

|||

M30610ECFS |

128K byte |

10K byte |

100D0 |

EPROM version (Note) |

|

M30610SAFP |

|

10K byte |

100P6S-A |

|

|

|

|

||||

M30610SAGP |

|

100P6Q-A |

External ROM version |

||

|

|||||

|

|

||||

M30612SAFP |

|

4K byte |

100P6S-A |

||

|

|||||

|

|

||||

M30612SAGP |

|

100P6Q-A |

|

||

|

|

||||

|

|

|

|||

|

|

|

|

|

|

Note: Do not use the EPROM version for mass production, because it is a tool for program development (for evaluation).

6

|

Mitsubishi microcomputers |

Description |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

Type No. M 3 0 6 1 2 M 4 – X X X F P

Package type: |

|

|

FP |

: Package |

100P6S-A |

GP |

: |

100P6Q-A |

FS |

: |

100D0 |

ROM No.

Omitted for blank one-time PROM version and EPROM version

ROM capacity: |

|

4 : 32K bytes |

A : 96K bytes |

8 : 64K bytes |

C : 128K bytes |

Memory type:

M : Mask ROM version

E : EPROM or one-time PROM version

S : External ROM version

Shows RAM capacity, pin count, etc (The value itself has no specific meaning)

M16C/61 Group

M16C Family

Figure 1.1.5. Type No., memory size, and package

7

Mitsubishi microcomputers

M16C / 61 Group

Pin Description |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

Pin Description

Pin name |

Signal name |

I/O type |

VCC, VSS |

Power supply |

|

|

input |

|

CNVSS |

CNVSS |

Input |

RESET |

Reset input |

Input |

XIN |

Clock input |

Input |

XOUT |

Clock output |

Output |

BYTE |

External data |

Input |

|

bus width |

|

|

select input |

|

AVCC |

Analog power |

|

|

supply input |

|

AVSS |

Analog power |

|

|

supply input |

|

VREF |

Reference |

Input |

|

voltage input |

|

P00 to P07 |

I/O port P0 |

Input/output |

|

D0 to D7 |

|

Input/output |

|

P10 to P17 |

I/O port P1 |

Input/output |

|

D8 to D15 |

|

Input/output |

|

P20 to P27 |

I/O port P2 |

Input/output |

|

A0 to A7 |

|

Output |

|

A0/D0 to |

|

Input/output |

|

A7/D7 |

|

|

|

A0, A1/D0 |

|

Output |

|

to A7/D6 |

|

Input/output |

|

P30 to P37 |

I/O port P3 |

Input/output |

|

A8 to A15 |

|

Output |

|

A8/D7, |

|

Input/output |

|

A9 to A15 |

|

Output |

|

P40 to P47 |

I/O port P4 |

Input/output |

|

|||

|

CS0 to CS3, |

|

Output |

|

A16 to A19 |

|

Output |

|

|

|

|

Function

Supply 2.7 to 5.5 V to the VCC pin. Supply 0 V to the VSS pin.

This pin switches between processor modes. Connect it to the VSS pin when operating in single-chip or memory expansion mode. Connect it to the VCC pin when in microprocessor mode.

A “L” on this input resets the microcomputer.

These pins are provided for the main clock generating circuit.Connect a ceramic resonator or crystal between the XIN and the XOUT pins. To use an externally derived clock, input it to the XIN pin and leave the XOUT pin open.

This pin selects the width of an external data bus. A 16-bit width is selected when this input is “L”; an 8-bit width is selected when this input is “H”. This input must be fixed to either “H” or “L”. When operating in single-chip mode,connect this pin to VSS.

This pin is a power supply input for the A-D converter. Connect this pin to VCC.

This pin is a power supply input for the A-D converter. Connect this pin to VSS.

This pin is a reference voltage input for the A-D converter.

This is an 8-bit CMOS I/O port. It has an input/output port direction register that allows the user to set each pin for input or output individually. When used for input in single-chip mode, the port can be set to have or not have a pull-up resistor in units of four bits by software. In memory expansion and microprocessor modes, selection of the internal pull-resistor is not available.

When set as a separate bus, these pins input and output data (D0–D7).

This is an 8-bit I/O port equivalent to P0.

When set as a separate bus, these pins input and output data (D8–D15).

This is an 8-bit I/O port equivalent to P0.

These pins output 8 low-order address bits (A0–A7).

If the external bus is set as an 8-bit wide multiplexed bus, these pins input and output data (D0–D7) and output 8 low-order address bits (A0–A7) separated in time by multiplexing.

If the external bus is set as a 16-bit wide multiplexed bus, these pins input and output data (D0–D6) and output address (A1–A7) separated in time by multiplexing. They also output address (A0).

This is an 8-bit I/O port equivalent to P0.

These pins output 8 middle-order address bits (A8–A15).

If the external bus is set as a 16-bit wide multiplexed bus, these pins input and output data (D7) and output address (A8) separated in time by multiplexing. They also output address (A9–A15).

This is an 8-bit I/O port equivalent to P0.

These pins output CS0–CS3 signals and A16–A19. CS0–CS3 are chip select signals used to specify an access space. A16–A19 are 4 highorder address bits.

8

|

Mitsubishi microcomputers |

Pin Description |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

Pin Description

Pin name |

Signal name |

I/O type |

P50 to P57 |

I/O port P5 |

Input/output |

WRL / WR, |

|

Output |

WRH / BHE, |

|

Output |

RD, |

|

Output |

BCLK, |

|

Output |

HLDA, |

|

Output |

HOLD, |

|

Input |

ALE, |

|

Output |

RDY |

|

Input |

P60 to P67 |

I/O port P6 |

Input/output |

P70 to P77 |

I/O port P7 |

Input/output |

P80 to P84, |

I/O port P8 |

Input/output |

P86, |

|

Input/output |

P87, |

|

Input/output |

P85 |

I/O port P85 |

Input |

P90 to P97 |

I/O port P9 |

Input/output |

P100 to P107 |

I/O port P10 |

Input/output |

Function

This is an 8-bit I/O port equivalent to P0. In single-chip mode, P57 in this port outputs a divide-by-8 or divide-by-32 clock of XIN or a clock of the same frequency as XCIN as selected by software.

Output WRL, WRH (WR and BHE), RD, BCLK, HLDA, and ALE signals. WRL and WRH, and BHE and WR can be switched using software control.

WRL, WRH, and RD selected

WRL, WRH, and RD selected

With a 16-bit external data bus, data is written to even addresses when the WRL signal is “L” and to the odd addresses when the WRH signal is “L”. Data is read when RD is “L”.

WR, BHE, and RD selected

WR, BHE, and RD selected

Data is written when WR is “L”. Data is read when RD is “L”. Odd addresses are accessed when BHE is “L”. Use this mode when using an 8-bit external data bus.

While the input level at the HOLD pin is “L”, the microcomputer is placed in the hold state. While in the hold state, HLDA outputs a “L” level. ALE is used to latch the address. While the input level of the RDY pin is “L”, the microcomputer is in the ready state.

This is an 8-bit I/O port equivalent to P0. When used for input in singlechip, memory expansion, and microprocessor modes, the port can be set to have or not have a pull-up resistor in units of four bits by software. Pins in this port also function as UART0 and UART1 I/O pins as selected by software.

This is an 8-bit I/O port equivalent to P6 (P70 and P71 are N channel open-drain output). Pins in this port also function as timer A0–A3 or UART2 I/O pins as selected by software.

P80 to P84, P86, and P87 are I/O ports with the same functions as P6. Using software, they can be made to function as the I/O pins for timer A4 and the input pins for external interrupts. P86 and P87 can be set using software to function as the I/O pins for a sub clock generation circuit. In this case, connect a quartz oscillator between P86 (XCOUT pin) and P87 (XCIN pin). P85 is an input-only port that also functions for NMI. The NMI interrupt is generated when the input at this pin

changes from “H” to “L”. The NMI function cannot be cancelled using software. The pull-up cannot be set for this pin.

This is an 8-bit I/O port equivalent to P6. Pins in this port also function as Timer B0–B2 input pins, D-A converter output pins, A-D converter extended input pins, or A-D trigger input pins as selected by software.

This is an 8-bit I/O port equivalent to P6. Pins in this port also function as A-D converter input pins. Furthermore, P104–P107 also function as input pins for the key input interrupt function.

9

|

Mitsubishi microcomputers |

Memory |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

Operation of Functional Blocks

The M16C/61 group accommodates certain units in a single chip. These units include ROM and RAM to store instructions and data and the central processing unit (CPU) to execute arithmetic/logic operations. Also included are peripheral units such as timers, serial I/O, D-A converter, DMAC, CRC calculation circuit, A-D converter, and I/O ports.

The following explains each unit.

Memory

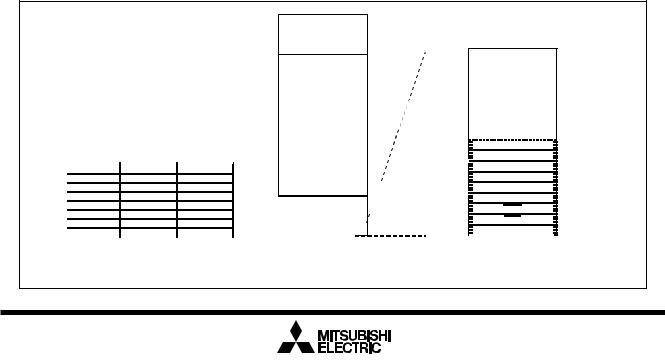

Figure 1.4.1 is a memory map of the M16C/61 group. The address space extends the 1M bytes from address 0000016 to FFFFF16. From FFFFF16 down is ROM. For example, in the M30612M4A-XXXFP,

there is 32K bytes of internal ROM from F800016 to FFFFF16. The vector table for fixed interrupts such as

_______

the reset and NMI are mapped to FFFDC16 to FFFFF16. The starting address of the interrupt routine is stored here. The address of the vector table for timer interrupts, etc., can be set as desired using the internal register (INTB). See the section on interrupts for details.

From 0040016 up is RAM. For example, in the M30612M4A-XXXFP, 4K bytes of internal RAM is mapped to the space from 0040016 to 013FF16. In addition to storing data, the RAM also stores the stack used when calling subroutines and when interrupts are generated.

The SFR area is mapped to 0000016 to 003FF16. This area accommodates the control registers for peripheral devices such as I/O ports, A-D converter, serial I/O, and timers, etc. Any part of the SFR area that is not occupied is reserved and cannot be used for other purposes.

The special page vector table is mapped to FFE0016 to FFFDB16. If the starting addresses of subroutines or the destination addresses of jumps are stored here, subroutine call instructions and jump instructions can be used as 2-byte instructions, reducing the number of program steps.

In memory expansion mode and microprocessor mode, a part of the spaces are reserved and cannot be used. For example, in the M30612M4A-XXXFP, the following spaces cannot be used.

•The space between 0140016 and 03FFF16

•The space between D000016 and F7FFF16 (When external area do not expand in memory expansion mode)

Do not expand the external area in single chip mode. A part of internal memory cannot be used depending

on MCU.

0000016

SFR area

For details, see Figure

1.7.1 and Figure 1.7.2

FFE0016

0040016

|

|

|

|

Internal RAM area |

|

|

Special page |

|

|

|

|

XXXXX16 |

|

|

|

|

|

|

|

|

|

|

|

|

vector table |

|

|

|

|

|

Internal reserved |

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

area (Note 1) |

|

|

|

|

|

|

|

0400016 |

|

|

FFFDC16 |

|

Undefined instruction |

|

|

|

External area |

|

||||

|

|

|

|

|

||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Overflow |

Type No. |

Address XXXXX16 |

Address YYYYY16 |

|

|

|

|

|

BRK instruction |

M30610M8A |

02BFF16 |

F000016 |

D000016 |

|

|

|

|

Address match |

Internal reserved |

|

|||||||

M30610MAA |

02BFF16 |

E800016 |

|

|

Single step |

|||

|

area (Note 2) |

|

|

|||||

M30610MCA/EC |

02BFF16 |

E000016 |

YYYYY16 |

|

|

|

|

Watchdog timer |

M30612M4A/E4 |

013FF16 |

F800016 |

|

Internal ROM area |

|

|

DBC |

|

M30612M8A |

013FF16 |

F000016 |

|

|

|

|||

|

|

|

||||||

|

|

|

NMI |

|||||

M30612MAA |

013FF16 |

E800016 |

|

|

|

|

|

|

|

|

|

|

|

Reset |

|||

M30612MCA |

017FF16 |

E000016 |

FFFFF16 |

|

|

FFFFF16 |

|

|

|

|

|

||||||

Note 1: During memory expansion and microprocessor modes, can not be used.

Note 2: When external area do not expand in memory expansion mode.

Figure 1.4.1. Memory map

10

|

Mitsubishi microcomputers |

CPU |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

Central Processing Unit (CPU)

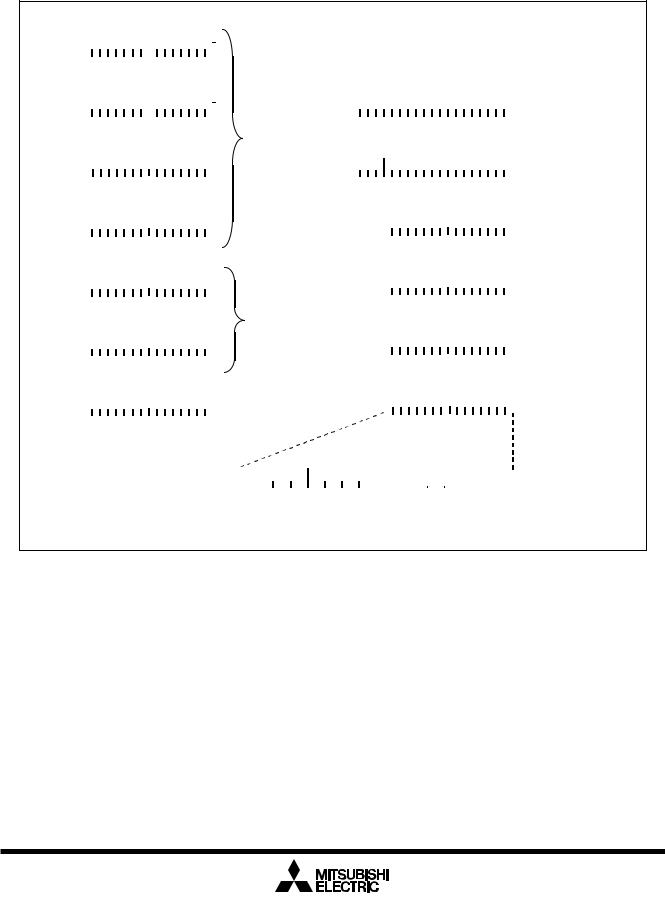

The CPU has a total of 13 registers shown in Figure 1.5.1. Seven of these registers (R0, R1, R2, R3, A0, A1, and FB) come in two sets; therefore, these have two register banks.

|

b15 |

|

b8 b7 |

|

|

b0 |

|

|||

R0(Note) |

|

|

|

H |

|

|

L |

|

||

|

|

|

|

|

|

|||||

|

b15 |

|

b8 b7 |

|

|

b0 |

|

|||

R1(Note) |

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

L |

|

|||

|

|

|

|

|||||||

b15 |

|

|

|

|

|

b0 |

|

|||

R2(Note) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

b15 |

|

|

|

|

|

b0 |

|

|||

R3(Note) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b15 |

|

|

|

|

|

b0 |

|

|||

A0(Note) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

b15 |

|

|

|

|

|

b0 |

|

|||

A1(Note) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

b15 |

|

|

|

|

|

b0 |

|

|||

FB(Note) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

b19 |

|

|

|

b0 |

||||

PC |

|

|

|

|

|

|

|

|

Program counter |

Data |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

registers |

b19 |

|

|

|

b0 |

||||

|

|

|

|

||||||

INTB |

|

H |

|

L |

|

|

|

|

Interrupt table |

|

|

|

|

|

|

|

|

|

register |

|

|

|

b15 |

|

|

|

|

||

|

|

|

|

b0 |

|||||

|

USP |

|

|

|

|

|

|

User stack pointer |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

b15 |

|

b0 |

||||

|

ISP |

|

|

|

|

|

|

Interrupt stack |

|

|

|

|

|

|

|

||||

Address |

|

|

|

|

|

|

|

|

pointer |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

registers |

|

|

b15 |

|

b0 |

||||

|

SB |

|

|

|

|

|

|

Static base |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

register |

|

|

|

b15 |

|

|

|

|||

|

|

|

|

|

b0 |

||||

Frame base |

FLG |

|

|

|

|

|

|

Flag register |

|

|

|

|

|

|

|

||||

registers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IPL |

U |

I |

O |

B |

S |

Z |

D |

C |

|

|

|

|

|

|

|

|

|

|

Note: These registers consist of two register banks.

Figure 1.5.1. Central processing unit register

(1) Data registers (R0, R0H, R0L, R1, R1H, R1L, R2, and R3)

Data registers (R0, R1, R2, and R3) are configured with 16 bits, and are used primarily for transfer and arithmetic/logic operations.

Registers R0 and R1 each can be used as separate 8-bit data registers, high-order bits as (R0H/R1H), and low-order bits as (R0L/R1L). In some instructions, registers R2 and R0, as well as R3 and R1 can use as 32-bit data registers (R2R0/R3R1).

(2) Address registers (A0 and A1)

Address registers (A0 and A1) are configured with 16 bits, and have functions equivalent to those of data registers. These registers can also be used for address register indirect addressing and address register relative addressing.

In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

11

|

Mitsubishi microcomputers |

CPU |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

(3) Frame base register (FB)

Frame base register (FB) is configured with 16 bits, and is used for FB relative addressing.

(4) Program counter (PC)

Program counter (PC) is configured with 20 bits, indicating the address of an instruction to be executed.

(5) Interrupt table register (INTB)

Interrupt table register (INTB) is configured with 20 bits, indicating the start address of an interrupt vector table.

(6) Stack pointer (USP/ISP)

Stack pointer comes in two types: user stack pointer (USP) and interrupt stack pointer (ISP), each configured with 16 bits.

Your desired type of stack pointer (USP or ISP) can be selected by a stack pointer select flag (U flag). This flag is located at the position of bit 7 in the flag register (FLG).

(7) Static base register (SB)

Static base register (SB) is configured with 16 bits, and is used for SB relative addressing.

(8) Flag register (FLG)

Flag register (FLG) is configured with 11 bits, each bit is used as a flag. Figure 1.5.2 shows the flag register (FLG). The following explains the function of each flag:

•Bit 0: Carry flag (C flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

•Bit 1: Debug flag (D flag)

This flag enables a single-step interrupt.

When this flag is “1”, a single-step interrupt is generated after instruction execution. This flag is cleared to “0” when the interrupt is acknowledged.

•Bit 2: Zero flag (Z flag)

This flag is set to “1” when an arithmetic operation resulted in 0; otherwise, cleared to “0”.

•Bit 3: Sign flag (S flag)

This flag is set to “1” when an arithmetic operation resulted in a negative value; otherwise, cleared to “0”.

•Bit 4: Register bank select flag (B flag)

This flag chooses a register bank. Register bank 0 is selected when this flag is “0” ; register bank 1 is selected when this flag is “1”.

•Bit 5: Overflow flag (O flag)

This flag is set to “1” when an arithmetic operation resulted in overflow; otherwise, cleared to “0”.

•Bit 6: Interrupt enable flag (I flag)

This flag enables a maskable interrupt.

An interrupt is disabled when this flag is “0”, and is enabled when this flag is “1”. This flag is cleared to “0” when the interrupt is acknowledged.

12

|

Mitsubishi microcomputers |

CPU |

M16C / 61 Group |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

|

|

|

•Bit 7: Stack pointer select flag (U flag)

Interrupt stack pointer (ISP) is selected when this flag is “0” ; user stack pointer (USP) is selected when this flag is “1”.

This flag is cleared to “0” when a hardware interrupt is acknowledged or an INT instruction of software interrupt Nos. 0 to 31 is executed.

•Bits 8 to 11: Reserved area

•Bits 12 to 14: Processor interrupt priority level (IPL)

Processor interrupt priority level (IPL) is configured with three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than the processor interrupt priority level (IPL), the interrupt is enabled.

•Bit 15: Reserved area

The C, Z, S, and O flags are changed when instructions are executed. See the software manual for

details.

b15 |

|

|

|

|

|

|

|

|

b0 |

|

||

|

IPL |

|

|

U |

I |

O |

B |

S |

Z |

D |

C |

Flag register (FLG) |

|

|

|

|

|

|

|

|

|

|

|

|

Carry flag |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Debug flag |

|

|

|

|

|

|

|

|

|

|

|

|

Zero flag |

|

|

|

|

|

|

|

|

|

|

|

|

Sign flag |

|

|

|

|

|

|

|

|

|

|

|

|

Register bank select flag |

|

|

|

|

|

|

|

|

|

|

|

|

Overflow flag |

|

|

|

|

|

|

|

|

|

|

|

|

Interrupt enable flag |

|

|

|

|

|

|

|

|

|

|

|

|

Stack pointer select flag |

|

|

|

|

|

|

|

|

|

|

|

|

Reserved area |

|

|

|

|

|

|

|

|

|

|

|

|

Processor interrupt priority level |

|

|

|

|

|

|

|

|

|

|

|

|

Reserved area |

Figure 1.5.2. Flag register (FLG)

13

Mitsubishi microcomputers

M16C / 61 Group

Reset |

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

|

|

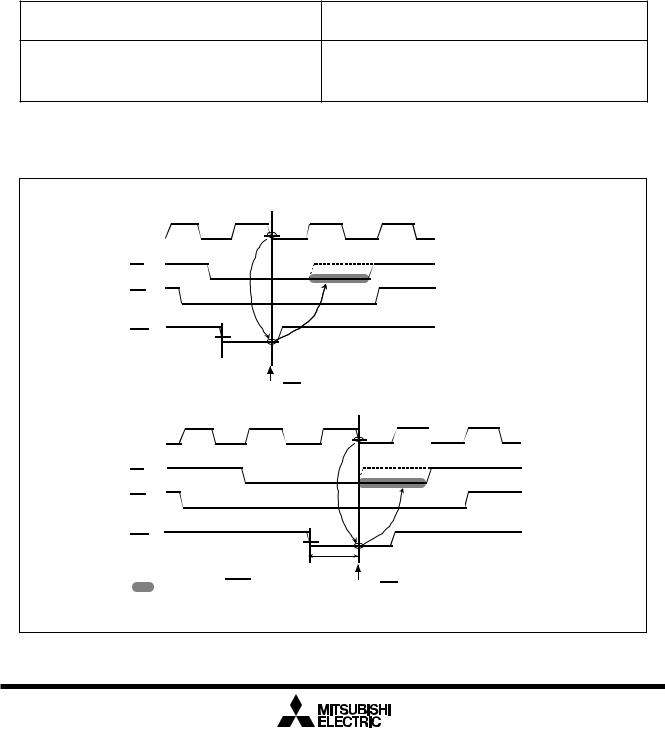

Reset

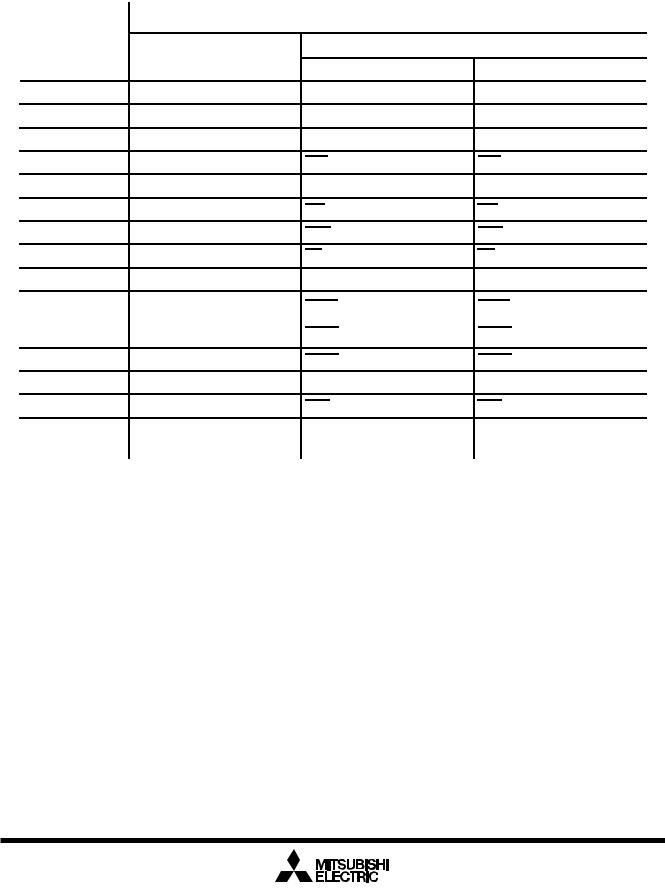

There are two kinds of resets; hardware and software. In both cases, operation is the same after the reset. (See “Software Reset” for details of software resets.) This section explains on hardware resets.

When the supply voltage is in the range where operation is guaranteed, a reset is effected by holding the reset pin level “L” (0.2VCC max.) for at least 20 cycles. When the reset pin level is then returned to the “H” level while main clock is stable, the reset status is cancelled and program execution resumes from the address in the reset vector table.

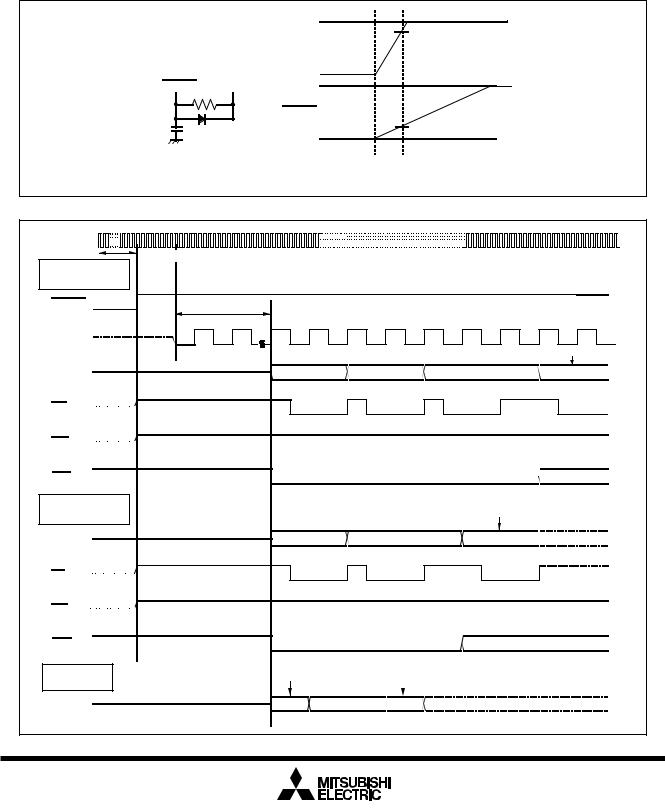

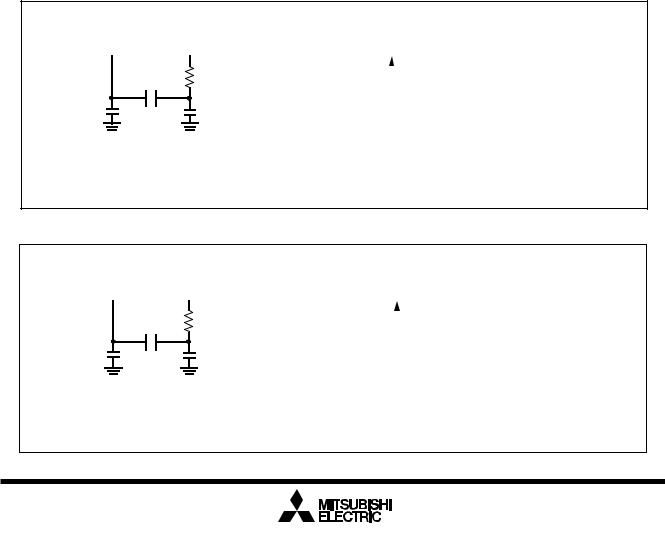

Figure 1.6.1 shows the example reset circuit. Figure 1.6.2 shows the reset sequence.

|

|

5V |

|

|

4.0V |

|

|

VCC |

|

|

0V |

RESET |

VCC |

5V |

RESET

0.8V

0V

Example when VCC = 5V.

Figure 1.6.1. Example reset circuit

XIN |

|

|

|

|

|

More than 20 cycles are needed |

|

|

|

Microprocessor |

|

|

|

|

mode BYTE = “H” |

|

|

|

|

RESET |

BCLK |

24cycles |

|

|

|

|

|

||

BCLK |

|

|

|

|

|

|

|

|

Content of reset vector |

Address |

|

FFFFC16 |

FFFFD16 |

FFFFE16 |

RD |

|

|

|

|

WR |

|

|

|

|

CS0 |

|

|

|

|

Microprocessor |

|

|

|

Content of reset vector |

mode BYTE = “L” |

|

|

|

|

Address |

|

FFFFC16 |

FFFFE16 |

|

RD |

|

|

|