Page 1

R

Intel® 815 Chipset: Graphics

Controller

Programmer’s Reference Manual (PRM)

July 2000

Order Number: 298237-001

Page 2

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

A

R

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness

for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in

medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future

definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

®

The Intel

characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I

of the I

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

www.intel.com

or call 1-800-548-4725

*Third-party brands and names are the property of their respective owners.

Copyright © Intel Corporation 2000

815 chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current

2

C is a 2-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel. Implementations

2

C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

lert On LAN* is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Intel Corporation

2

Page 3

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

Contents

1. Introduction ................................................................................................................................ 15

1.1. Terminology................................................................................................................... 15

1.2. Reference Documents .................................................................................................. 16

2. Intel® 815 Chipset Overview....................................................................................................... 17

2.1. I/O Controller Hub ......................................................................................................... 18

2.2. Intel® 82815 Chipset GMCH Overview.......................................................................... 18

2.2.1. Host Interface .............................................................................................. 19

2.2.2. System Memory Interface ........................................................................... 20

2.2.3. Multiplexed AGP and Display Cache Interface ........................................... 20

2.2.4. Hub Interface............................................................................................... 21

2.2.5. Intel® 82815 Chipset GMCH Integrated Graphics Support ......................... 21

2.2.6. System Clocking.......................................................................................... 22

2.2.7. GMCH Power Delivery ................................................................................ 22

2.3. Three PCI Devices on GMCH ....................................................................................... 22

2.3.1. Multi-Mode Capability Requirements .......................................................... 23

2.3.1.1. Supported Single Monitor and Multi-monitor Configurations .......... 23

2.3.1.2. System Startup ............................................................................... 25

2.3.1.3. Software Start-Up Sequence .......................................................... 26

2.3.1.4. Switching Device modes ................................................................ 28

3. System Address Map ................................................................................................................. 29

3.1. Memory and I/O Space Registers ................................................................................. 30

3.2. GC Register Memory Address Map .............................................................................. 32

3.3. VGA and Extended VGA Register Map......................................................................... 36

3.3.1. VGA and Extended VGA I/O and Memory Register Map............................ 37

3.4. Indirect VGA and Extended VGA Register Indices ....................................................... 38

3.4.1. Graphics Address Translation..................................................................... 41

3.4.2. Memory Buffers for GC’s Instruction Interface............................................ 42

4. Graphics Translation Table (GTT) Range Definition.................................................................. 43

5. Basic Initialization Procedures ................................................................................................... 45

5.1. Initialization Sequence................................................................................................... 45

5.2. Hardware Detection (Probe).......................................................................................... 45

5.3. Frame Buffer Initialization.............................................................................................. 46

5.4. Hardware Register Initialization..................................................................................... 47

5.4.1. Color vs. Monochrome Monitors ................................................................. 47

5.4.2. Protect Registers: Locking and Unlocking .................................................. 47

5.4.3. Checking Memory Frequency ..................................................................... 47

5.5. Hardware State.............................................................................................................. 47

5.6. Saving the Hardware State............................................................................................ 48

5.7. Restoring the Hardware State ....................................................................................... 49

6. Blt Engine Programming ............................................................................................................ 53

6.1. BLT Engine Programming Considerations .................................................................... 53

6.1.1. When the Source and Destination Locations Overlap ................................ 53

6.2. Basic Graphics Data Considerations............................................................................. 57

6.2.1. Contiguous vs. Discontinuous Graphics Data ............................................. 57

3

Page 4

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

Source Data................................................................................................. 58

6.2.2.

R

6.2.3. Monochrome Source Data ........................................................................... 59

6.2.4. Pattern Data................................................................................................. 60

6.2.5. Destination Data ..........................................................................................62

6.3. BLT Programming Examples.........................................................................................63

6.3.1. Pattern Fill -- A Very Simple BLT .................................................................63

6.3.2. Drawing Characters Using a Font Stored in System Memory .....................66

7. Initialization Registers.................................................................................................................69

7.1. Standard VGA Registers................................................................................................ 69

7.2. SMRAM Registers .........................................................................................................69

7.2.1. SMRAM—System Management RAM Control Register (Device 0) ...........69

7.3. Display, I/O, GPIO, Clock, LCD, and Pixel Pipeline Registers ......................................72

7.4. 2D Graphics Controller Registers (3CEh / 3CFh) ..........................................................73

7.5. 2D CRT Controller Registers (3B4h/3D4h/3B5h/3D5h).................................................73

7.6. Initialization Values for VGA Registers ..........................................................................74

8. Frame Buffer Access ..................................................................................................................77

9. VGA and Extended VGA Registers ............................................................................................79

9.1. General Control & Status Registers...............................................................................79

9.1.1. ST00Input Status 0 ..................................................................................80

9.1.2. ST01Input Status 1 ..................................................................................81

9.1.3. FCRFeature Control.................................................................................82

9.1.4. MSRMiscellaneous Output.......................................................................83

9.2. Sequencer Registers .....................................................................................................84

9.2.1. SRXSequencer Index............................................................................... 84

9.2.2. SR00Sequencer Reset ............................................................................85

9.2.3. SR01Clocking Mode ................................................................................86

9.2.4. SR02Plane/Map Mask .............................................................................87

9.2.5. SR03Character Font ................................................................................88

9.2.6. SR04Memory Mode Register ................................................................... 89

9.2.7. SR07Horizontal Character Counter Reset ...............................................90

9.3. Graphics Controller Registers........................................................................................90

9.3.1. GRXGRX Graphics Controller Index Register .........................................90

9.3.2. GR00Set/Reset Register.......................................................................... 91

9.3.3. GR01Enable Set/Reset Register .............................................................91

9.3.4. GR02Color Compare Register .................................................................92

9.3.5. GR03Data Rotate Register ......................................................................92

9.3.6. GR04Read Plane Select Register............................................................ 93

9.3.7. GR05Graphics Mode Register .................................................................93

9.3.8. GR06Miscellaneous Register................................................................... 96

9.3.9. GR07Color Don’t Care Register............................................................... 97

9.3.10. GR08Bit Mask Register............................................................................ 97

9.3.11. GR10Address Mapping............................................................................ 98

9.3.12. GR11Page Selector .................................................................................99

9.3.13. GR[14:1F]Software Flags....................................................................... 100

9.4. Attribute Controller Registers.......................................................................................101

9.4.1. ARXAttribute Controller Index Register..................................................101

9.4.2. AR[00:0F]Palette Registers [0:F] ...........................................................102

9.4.3. AR10Mode Control Register ..................................................................102

9.4.4. AR11Overscan Color Register............................................................... 104

4

Page 5

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

9.4.5.

AR12Memory Plane Enable Register .................................................... 104

9.4.6. AR13Horizontal Pixel Panning Register ................................................ 105

9.4.7. AR14Color Select Register.................................................................... 106

9.5. VGA Color Palette Registers....................................................................................... 106

9.5.1. DACMASKPixel Data Mask Register..................................................... 107

9.5.2. DACSTATEDAC State Register ............................................................ 108

9.5.3. DACRXPalette Read Index Register ..................................................... 108

9.5.4. DACWXPalette W rite Index Register .................................................... 108

9.5.5. DACDATAPalette Data Register ........................................................... 109

9.6. CRT Controller Register .............................................................................................. 109

9.6.1. CRXCRT Controller Index Register ....................................................... 110

9.6.2. CR00Horizontal Total Register .............................................................. 111

9.6.3. CR01Horizontal Display Enable End Register....................................... 111

9.6.4. CR02Horizontal Blanking Start Register................................................ 111

9.6.5. CR03Horizontal Blanking End Register................................................. 112

9.6.6. CR04Horizontal Sync Start Register...................................................... 112

9.6.7. CR05Horizontal Sync End Register....................................................... 113

9.6.8. CR06Vertical Total Register .................................................................. 114

9.6.9. CR07Overflow Register ......................................................................... 114

9.6.10. CR08Preset Row Scan Register ........................................................... 117

9.6.11. CR09Maximum Scan Line Register ...................................................... 118

9.6.12. CR0AText Cursor Start Register ........................................................... 119

9.6.13. CR0BText Cursor End Register ............................................................ 119

9.6.14. CR0CStart Address High Register ........................................................ 120

9.6.15. CR0DStart Address Low Register ......................................................... 121

9.6.16. CR0EText Cursor Location High Register ............................................. 121

9.6.17. CR0FText Cursor Location Low Register .............................................. 122

9.6.18. CR10Vertical Sync Start Register.......................................................... 122

9.6.19. CR11Vertical Sync End Register........................................................... 123

9.6.20. CR12Vertical Display Enable End Register........................................... 124

9.6.21. CR13Offset Register ............................................................................. 124

9.6.22. CR14Underline Location Register ......................................................... 125

9.6.23. CR15Vertical Blanking Start Register.................................................... 126

9.6.24. CR16Vertical Blanking End Register ..................................................... 126

9.6.25. CR17CRT Mode Control........................................................................ 127

9.6.26. CR18Line Compare Register ................................................................ 131

9.6.27. CR22Memory Read Latch Data Register .............................................. 131

9.6.28. CR24 Test Register for Toggle State of Attribute Controller Register ... 132

9.6.29. CR30Extended Vertical Total Register .................................................. 132

9.6.30. CR31Extended Vertical Display End Register....................................... 133

9.6.31. CR32Extended Vertical Sync Start Register ......................................... 134

9.6.32. CR33Extended Vertical Blanking Start Register.................................... 135

9.6.33. CR35 Extended Horizontal Total Time Register.................................... 136

9.6.34. CR39Extended Horizontal Blank Time Register.................................... 136

9.6.35. CR40Extended Start Address Register ................................................. 137

9.6.36. CR41Extended Offset Register ............................................................. 138

9.6.37. CR42Extended Start Address High Register......................................... 138

9.6.38. CR70Interlace Control Register............................................................. 139

9.6.39. CR80I/O Control .................................................................................... 139

9.6.40. CR81Reserved ...................................................................................... 140

9.6.41. CR82Blink Rate Control......................................................................... 140

5

Page 6

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

Programming Interface .............................................................................................................141

10.

10.1. Reserved Bits and Software Compatibility................................................................... 141

10.2. Overview ...................................................................................................................... 141

10.3. GC Register Programming ..........................................................................................142

10.4. GC Instruction Streams ...............................................................................................142

10.4.1. Instruction Use........................................................................................... 142

10.4.2. Instruction Transport Overview.................................................................. 142

10.4.3. Instruction Parser....................................................................................... 143

10.4.4. Ring Buffers (RB)....................................................................................... 144

10.4.4.1. Ring Buffer Registers ....................................................................144

10.4.4.2. Ring Buffer Initialization.................................................................145

10.4.4.3. Ring Buffer Use.............................................................................145

10.4.5. Batch Buffers .............................................................................................146

10.4.6. Instruction Arbitration ................................................................................. 147

10.4.6.1. Arbitration Rationale...................................................................... 147

10.4.6.2. Wait Instructions ...........................................................................147

10.4.6.3. Instruction Arbitration Points .........................................................148

10.4.6.4. Instruction Arbitration Rules ..........................................................148

10.4.6.5. Batch Buffer Protected Mode ........................................................148

10.5. Instruction Format ........................................................................................................ 149

10.5.1. Instruction Parser Instructions ...................................................................149

10.5.2. 2D Instructions........................................................................................... 149

10.5.3. 3D Instructions........................................................................................... 150

R

11. Instruction Parser Instructions ..................................................................................................153

11.1. Introduction ..................................................................................................................153

11.2. Instruction Descriptions................................................................................................ 153

11.2.1. GFXCMDPARSER_NOP_IDENTIFICATION ............................................153

11.2.2. GFXCMDPARSER_BREAKPOINT_INTERRUPT .................................... 154

11.2.3. GFXCMDPARSER_USER_INTERRUPT.................................................. 154

11.2.4. GFXCMDPARSER_WAIT_FOR_EVENT.................................................. 155

11.2.5. GFXCMDPARSER_FLUSH....................................................................... 156

11.2.6. GFXCMDPARSER_CONTEXT _SEL .......................................................156

11.2.7. GFXCMDPARSER _DEST_BUFFER_INFO.............................................157

11.2.8. GFXCMDPARSER _FRONT_BUFFER_INFO ..........................................158

11.2.9. GFXCMDPARSER _Z_BUFFER_INFO ....................................................159

11.2.10. GFXCMDPARSER_REPORT_HEAD .......................................................159

11.2.11. GFXCMDPARSER_ARB_ON_OFF ..........................................................160

11.2.12. GFXCMDPARSER_OVERLAY_FLIP........................................................ 160

11.2.13. GFXCMDPARSER_LOAD_SCAN_LINES_INCL ......................................160

11.2.14. GFXCMDPARSER_LOAD_SCAN_LINES_EXCL ..................................... 161

11.2.15. GFXCMDPARSER_STORE_DWORD_IMM.............................................161

11.2.16. GFXCMDPARSER_STORE_DWORD_INDEX.........................................161

11.2.17. GFXCMDPARSER_BATCH_BUFFER...................................................... 162

12. 2D Instructions..........................................................................................................................163

12.1. BLTs To and From Cacheable Memory.......................................................................163

12.2. BLT Engine Instructions...............................................................................................163

12.2.1. SETUP_BLT ..............................................................................................164

12.2.2. SETUP_MONO_PATTERN_SL_BLT ........................................................ 166

12.2.3. PIXEL_BLT ................................................................................................ 167

12.2.4. SCANLINE_BLT ........................................................................................167

12.2.5. TEXT_BLT ................................................................................................. 168

6

Page 7

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

12.2.6.

TEXT_Immediate_BLT ............................................................................. 169

12.2.7. COLOR_BLT ............................................................................................. 170

12.2.8. PAT_BLT................................................................................................... 171

12.2.9. MONO_PAT_BLT ..................................................................................... 172

12.2.10. SRC_COPY_BLT ...................................................................................... 173

12.2.11. MONO_SRC_COPY_BLT......................................................................... 174

12.2.12. MONO_SRC_COPY_IMMEDIATE_BLT................................................... 175

12.2.13. FULL_BLT ................................................................................................. 177

12.2.14. FULL_MONO_SRC_BLT .......................................................................... 178

12.2.15. FULL_MONO_PATTERN_BLT ................................................................. 180

12.2.16. FULL_MONO_PATTERN_MONO_SRC_BLT .......................................... 182

12.3. BLT Engine Instruction Definitions .............................................................................. 184

12.3.1. BR00—BLT Opcode and Control .............................................................. 184

12.3.2. BR01—Setup BLT Raster OP, Control, and Destination Offset................ 186

12.3.3. BR02—Clip Rectangle Y1 Address........................................................... 188

12.3.4. BR03—Clip Rectangle Y2 Address........................................................... 188

12.3.5. BR04—Clip Rectangle X1 and X2............................................................. 189

12.3.6. BR05—Setup Expansion Background Color............................................. 190

12.3.7. BR06—Setup Expansion Foreground Color ............................................. 190

12.3.8. BR07—Setup Color Pattern Address ........................................................ 191

12.3.9. BR08—Destination X1 and X2 .................................................................. 192

12.3.10. BR09—Destination Address and Destination Y1 Address ........................ 193

12.3.11. BR10—Destination Y2 Address ................................................................ 193

12.3.12. BR11—BLT Source Pitch (Offset) or Monochrome Source Quadwords .. 194

12.3.13. BR12—Source Address ............................................................................ 195

12.3.14. BR13—BLT Raster OP, Control, and Destination Pitch............................ 196

12.3.15. BR14—Destination Width & Height........................................................... 198

12.3.16. BR15—Color Pattern Address .................................................................. 199

12.3.17. BR16—Pattern Expansion Background & Solid Pattern Color.................. 200

12.3.18. BR17—Pattern Expansion Foreground Color ........................................... 200

12.3.19. BR18—Source Expansion Background, and Destination Color................ 201

12.3.20. BR19—Source Expansion Foreground Color ........................................... 201

12.3.21. S_SLADD—Source Scan Line Address.................................................... 202

12.3.22. D_SLH—Destination Scan Line Height..................................................... 202

12.3.23. D_SLRADD—Destination Scan Line Read Address................................. 203

13. Rendering Engine Instructions ................................................................................................. 205

13.1. GFXPRIMITIVE ........................................................................................................... 205

13.1.1. Axis Aligned Rectangles............................................................................ 205

13.1.2. Primitive Winding Order ............................................................................ 205

13.1.3. Position Mask ............................................................................................ 206

13.1.4. Bias ...................................................................................................... 206

13.1.5. Primitive Rendering Instruction Format..................................................... 206

13.1.6. Variable Length Vertex Formats for Rendering Instructions ..................... 207

13.1.7. GFXVERTEX ............................................................................................ 208

13.2. GFXRENDERSTATE_VERTEX_FORMAT ................................................................ 209

13.3. GFXBLOCK................................................................................................................. 210

13.3.1. Motion Vector Format................................................................................ 213

13.4. Non-pipelined State Variables ..................................................................................... 213

13.5. GFXRENDERSTATE_MAP_TEXELS ........................................................................ 214

13.6. GFXRENDERSTATE_MAP_COORD_SETS ............................................................. 215

13.7. GFXRENDERSTATE_MAP_INFO.............................................................................. 217

13.8. GFXRENDERSTATE_MAP_FILTER .......................................................................... 222

7

Page 8

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

GFXRENDERSTATE_MAP_LOD_LIMITS.................................................................. 224

13.9.

13.10. GFXRENDERSTATE_MAP_LOD_CONTROL............................................................225

13.11. GFXRENDERSTATE_MAP_PALETTE_LOAD ...........................................................226

13.12. GFXRENDERSTATE_MAP_COLOR_BLEND_STAGES ...........................................227

13.13. GFXRENDERSTATE_MAP_ALPHA_BLEND_STAGES ............................................230

13.14. GFXRENDERSTATE_COLOR_FACTOR ................................................................... 232

13.15. GFXRENDERSTATE_COLOR_CHROMA_KEY.........................................................233

13.16. GFXRENDERSTATE_SRC_DST_BLEND_MONO.....................................................235

13.17. GFXRENDERSTATE_Z_BIAS_ALPHA_FUNC_REF .................................................238

13.18. GFXRENDERSTATE_LINE_WIDTH_CULL_SHADE_ MODE ...................................239

13.19. GFXRENDERSTATE_BOOLEAN_ENA_1 ..................................................................241

13.20. GFXRENDERSTATE_BOOLEAN_ENA_2 ..................................................................242

13.21. GFXRENDERSTATE_FOG_COLOR .......................................................................... 243

13.22. GFXRENDERSTATE_DRAWING_RECTANGLE_INFO ............................................243

13.23. GFXRENDERSTATE_SCISSOR_ENABLE ................................................................245

13.24. GFXRENDERSTATE_SCISSOR_RECTANGLE_INFO..............................................246

13.25. Stipple Pattern ......................................................................................................247

13.26. GFXRENDERSTATE_ANTI_ALIASING ......................................................................248

13.27. GFXRENDERSTATE_PROVOKING_VTX_PIXELIZATION_RULE............................249

13.28. GFXRENDERSTATE_DEST_BUFFER_VARIABLES.................................................251

13.29. Programming Hints/Rules ............................................................................................253

R

14. Clock Control Registers ............................................................................................................ 257

14.1. Programming Notes ..................................................................................................... 257

14.2. DCLK_0D—Display Clock 0 Divisor Register ..............................................................258

14.3. DCLK_1D—Display Clock 1 Divisor Register ..............................................................259

14.4. DCLK_2D—Display Clock 2 Divisor Register ..............................................................260

14.5. LCD_CLKD—LCD Clock Divisor Register ................................................................... 261

14.6. DCLK_0DS—Display & LCD Clock Divisor Select Register ........................................262

14.7. PWR_CLKC—Power Management and Miscellaneous Clock Control ....................... 264

15. Overlay Registers .....................................................................................................................265

15.1. OV0ADD—Overlay 0 Register Update Address Register............................................ 267

15.2. DOV0STA—Display/Overlay 0 Status Register...........................................................268

15.3. Gamma Correction ......................................................................................................269

15.3.1.1. GAMC[5:0]—Gamma Correction Registers .................................. 269

15.3.1.2. Mathematical Gamma Correction For Overlay .............................271

15.4. Memory Offset Registers ............................................................................................. 274

15.4.1. Overlay Buffer Pointer Registers ...............................................................274

15.4.1.1. OBUF_0Y—Overlay Buffer 0 Y Pointer Register .......................... 274

15.4.1.2. OBUF_1Y—Overlay Buffer 1 Y Pointer Register .......................... 275

15.4.1.3. OBUF_0U—Overlay Buffer 0 U Pointer Register..........................275

15.4.1.4. OBUF_0V—Overlay Buffer 0 V Pointer Register ..........................276

15.4.1.5. OBUF_1U—Overlay Buffer 1 U Pointer Register..........................276

15.4.1.6. OBUF_1V—Overlay Buffer 1 V Pointer Register ..........................277

15.4.2. Overlay Stride Registers ............................................................................ 277

15.4.2.1. OV0STRIDE—Overlay 0 Stride Register ......................................277

15.4.3. Overlay Initial Phase Registers..................................................................278

15.4.3.1. YRGB_VPH—Y/RGB Vertical Phase Register .............................278

15.4.3.2. UV_VPH—UV Vertical Phase Register......................................... 279

8

Page 9

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

15.4.3.3.

HORZ_PH—Horizontal Phase Register ....................................... 279

15.4.3.4. INIT_PH—Initial Phase Register .................................................. 280

15.4.4. Overlay Destination Window Position/Size Registers ............................... 281

15.4.4.1. DWINPOS—Destination Window Position Register..................... 281

15.4.4.2. DWINSZ—Destination W indow Size Register ............................. 281

15.4.5. Overlay Source Size Registers.................................................................. 282

15.4.5.1. SWID—Source W idth Register .................................................... 282

15.4.5.2. SWIDQW —Source Width In QWords Register ........................... 283

15.4.5.3. SHEIGHT—Source Height Register ............................................. 284

15.4.6. Overlay Scale Factor Registers................................................................. 285

15.4.6.1. YRGBSCALE—Y/RGB Scale Factor Register ............................. 285

15.4.6.2. UVSCALE—UV Scale Factor Register......................................... 286

15.4.7. Overlay Color Correction Registers........................................................... 287

15.4.7.1. OV0CLRC0—Overlay 0 Color Correction 0 Register ................... 287

15.4.7.2. OV0CLRC1—Overlay 0 Color Correction 1 Register ................... 287

15.4.8. Overlay Destination Color Key Registers .................................................. 288

15.4.8.1. DCLRKV—Destination Color Key Value Register ........................ 288

15.4.8.2. DCLRKM—Destination Color Key Mask Register ........................ 289

15.4.9. Overlay Source Color Key Registers......................................................... 290

15.4.9.1. SCLRKVH—Source Color Key Value High Register .................... 290

15.4.9.2. SCLRKVL—Source Color Key Value Low Register ..................... 291

15.4.9.3. SCLRKM—Source Color Key Mask Register............................... 291

15.4.10. Overlay Configuration Registers ............................................................... 293

15.4.10.1. OV0CONF—Overlay Configuration Register ............................... 293

15.4.11. OV0CMD—Overlay Command Register ................................................... 294

15.4.12. Overlay Alpha Blend Window Position/Size Registers .............................. 298

15.4.12.1. AWINPOS—Alpha Blend Window Position Register ................... 298

15.4.12.2. AWINSZ—Alpha Blend Window Size Register ............................ 299

15.5. Overlay Flip Instruction................................................................................................ 299

16. Instruction, Memory, and Interrupt Control Registers .............................................................. 301

16.1. Instruction Control Registers ....................................................................................... 301

16.1.1. FENCE—Graphics Memory Fence Table Registers ................................. 301

16.1.2. PGTBL_CTL—Page Table Control Register............................................. 303

16.1.3. PGTBL_ER—Page Table Error Register .................................................. 304

16.1.4. PGTBL_ERRMSK—Page Table Error Mask Register .............................. 306

16.1.5. RINGBUF—Ring Buffer Registers ............................................................ 308

16.1.6. HWS_PGA—Hardware Status Page Address Register............................ 310

16.1.7. IPEIR—Instruction Parser Error Identification Register (debug) ............... 311

16.1.8. IPEHR—Instruction Parser Error Header Register (debug)...................... 311

16.1.9. INSTDONE—Instruction Stream Interface Done Register........................ 312

16.1.10. NOPID—NOP Identification Register ........................................................ 313

16.1.11. INSTPM—Instruction Parser Mode Register ............................................ 314

16.1.12. INSTPS—Instruction Parser State Register (debug) ................................ 315

16.1.13. BBP_PTR—Batch Buffer Parser Pointer Register (debug)....................... 317

16.1.14. ABB_STR—Active Batch Buffer Start Address Register (debug) ............. 317

16.1.15. ABB_END—Active Batch Buffer End Address Register (debug).............. 318

16.1.16. DMA_FADD—DMA Engine Fetch Address (debug) ................................. 318

16.1.17. MEM_MODE—Memory Interface Mode Register (debug)........................ 319

16.2. Interrupt Control Registers .......................................................................................... 320

16.2.1. HWSTAM—Hardware Status Mask Register............................................ 322

16.2.2. IER—Interrupt Enable Register................................................................. 323

16.2.3. IIR—Interrupt Identity Register.................................................................. 324

16.2.4. IMR—Interrupt Mask Register................................................................... 325

9

Page 10

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

16.2.5.

ISR—Interrupt Status Register ..................................................................326

R

16.2.6. Error Identity, Mask and Status Registers .................................................327

16.2.6.1. Page Table Error handling in Intel® 815 Chipset........................... 327

16.2.6.2. Resetting the Page Table Error..................................................... 328

16.2.6.3. EIR—Error Identity Register.......................................................... 329

16.2.6.4. EMR—Error Mask Register ..........................................................329

16.2.6.5. ESR—Error Status Register..........................................................330

16.3. Display Interface Control..............................................................................................331

16.3.1. FW_BLC—FIFO W atermark and Burst Length Control ............................331

17. LCD / TV-Out Register Description ..........................................................................................333

17.1. HTOTAL—Horizontal Total Register ........................................................................... 333

17.2. HBLANK—Horizontal Blank Register ..........................................................................334

17.3. HSYNC—Horizontal Sync Register ............................................................................. 335

17.4. VTOTAL—Vertical Total Register................................................................................336

17.5. VBLANK—Vertical Blank Register............................................................................... 337

17.6. VSYNC—Vertical Sync Register.................................................................................. 338

17.7. LCDTV_C—LCD/TV-Out Control Register .................................................................. 339

17.8. OVRACT—Overlay Active Register.............................................................................342

17.9. BCLRPAT— Border Color Pattern Register ................................................................342

18. Local Memory Interface ............................................................................................................343

18.1. DRT—DRAM Row Type .............................................................................................. 343

18.2. DRAMCL—DRAM Control Low ...................................................................................344

18.3. DRAMCH—DRAM Control High .................................................................................. 345

19. I/O Control Registers ................................................................................................................ 347

19.1. HVSYNC—HSYNC/VSYNC Control Register..............................................................347

19.2. GPIO Registers............................................................................................................348

19.2.1. GPIOAGeneral Purpose I/O Control Register A ....................................348

19.2.2. GPIOBGeneral Purpose I/O Control Register B ....................................350

20. Display And Cursor Registers...................................................................................................353

20.1. DISP_SL—Display Scan Line Count ...........................................................................353

20.2. DISP_SLC—Display Scan Line Count Range Compare ............................................. 354

20.3. Pixel Pipeline Control................................................................................................... 355

20.3.1. PIXCONF—Pixel Pipeline Configuration ...................................................355

20.3.2. BLTCNTL—BLT Control ............................................................................357

20.3.3. SWF[1:3]—Software Flag Registers.......................................................... 357

20.3.4. DPLYBASE—Display Base Address Register...........................................358

20.3.5. DPLYSTAS—Display Status Select Register ............................................ 359

20.4. Hardware Cursor..........................................................................................................361

20.4.1. CURCNTR—Cursor Control Register........................................................361

20.4.2. CURBASE—Cursor Base Address Register .............................................362

20.4.3. CURPOS—Cursor Position Register.........................................................362

21. Appendix A: Mode Parameters.................................................................................................363

10

Page 11

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

Figures

Figure 1. Intelâ 815 Chipset System Block Diagram ......................................................... 18

Figure 2. Intel® 82815 Chipset GMCH Block Diagram ...................................................... 19

Figure 3. Conceptual Platform PCI Configuration Diagram .............................................. 23

Figure 4. Device Mode Auto-Detect Flowchart ................................................................. 25

Figure 5. System Memory Address Map........................................................................... 29

Figure 6. Detailed Memory System Address Map............................................................. 29

Figure 7. Graphics Controller Register Memory and I/O Map........................................... 30

Figure 8. GTT Mapping ..................................................................................................... 42

Figure 9. Source Corruption in BLT with Overlapping Source and Destination Locations 54

Figure 10. Correctly Performed BLT with Overlapping Source and Destination Locations. 55

Figure 11. Suggested Starting Points for Possible Source & Destination Overlap

Situations ...................................................................................................... 56

Figure 12. Representation of On-Screen Single 6-Pixel Line in the Frame Buffer ............. 57

Figure 13. Representation of On-Screen 6x4 Array of Pixels in the Frame Buffer ............. 58

Figure 14. Pattern Data -- Always an 8x8 Array of Pixels ................................................... 60

Figure 15. 8bpp Pattern Data -- Occupies 64 Bytes (8 quadwords) ................................... 61

Figure 16. 16bpp Pattern Data -- Occupies 128 Bytes (16 quadwords) ............................. 61

Figure 17. 24bpp Pattern Data -- Occupies 256 Bytes (32 quadwords) ............................. 61

Figure 18. 2bpp Pattern Data -- Occupies 256 Bytes (32 quadwords) ............................... 62

Figure 19. On-Screen Destination for Example Pattern Fill BLT ........................................ 63

Figure 20. Pattern Data for Example Pattern Fill BLT ......................................................... 64

Figure 21. Results of Example Pattern Fill BLT .................................................................. 65

Figure 22. On-Screen Destination for Example Character Drawing BLT............................ 66

Figure 23. Source Data in System Memory for Example Character Drawing BLT ............. 66

Figure 24. Results of Example Character Drawing BLT ..................................................... 68

Figure 25 Display Fields and Dimensions CRxx Control Registers ................................. 110

Figure 26. Graphics Controller Instruction Interface ......................................................... 143

Figure 27. Ring Buffers .................................................................................................... 144

Figure 28. Batch Buffer Sequence .................................................................................... 146

Figure 29. Instruction Format For First DWord ................................................................. 150

Figure 30. Rectangle Vertices ........................................................................................... 205

Figure 31. State Variable Relationships ............................................................................ 214

Figure 32. State Variable Relationships ........................................................................... 215

Figure 33. State Variable Relationships ............................................................................ 217

Figure 34 Mip-map Surface Organization Example ......................................................... 218

Figure 35. State Variable Relationships ............................................................................ 222

Figure 36. State Variable Relationships ............................................................................ 224

Figure 37. State Variable Relationships ............................................................................ 225

Figure 38. State Variable Relationships ............................................................................ 226

Figure 39. State Variable Relationships ............................................................................ 227

Figure 40. State Variable Relationships ............................................................................ 230

Figure 41. Gamma Correction Unit Block Diagram........................................................... 271

11

Page 12

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

Tables

Table 1. Supported System Bus and System Memory Bus Frequencies.........................22

Table 2. Memory-Mapped Registers ................................................................................32

Table 3. I/O and Memory Register Map................................................................................37

Table 4. 2D Sequence Registers (3C4h / 3C5h) ..............................................................38

Table 5. 2D Graphics Controller Registers (3CEh / 3CFh) ..............................................38

Table 6. 2D Attribute Controller Registers (3C0h / 3C1h) ................................................39

Table 7. 2D CRT Controller Registers (3B4h / 3D4h / 3B5h / 3D5h) ...............................39

Table 8. CRT Display Sync Polarities...............................................................................84

Table 9. VGA Address Range ..........................................................................................99

Table 10. Memory Address Counter Address Bits [15:0] .................................................129

Table 11. Frame Buffer Address Decoder........................................................................130

Table 12. Ring Buffer Characteristics...............................................................................145

Table 13. Graphics Controller Instructions .......................................................................151

Table 14. Summary of Source Surface Formats with Filter Output Channel Mappings...217

Table 15. Selecting Specular Mode..................................................................................235

Table 16. Overlay Register/Instruction Categories ...........................................................266

Table 17. Bit Definition For Interrupt Control Registers....................................................320

R

12

Page 13

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

Revision History

Rev. Description Date

1.0 • Initial Release July 2000

13

Page 14

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

This page is intentionally left blank.

R

14

Page 15

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

1. Introduction

The Intelâ 815 chipset is a highly flexible chipset designed to extend from the basic graphics/multimedia

PC platform up to the mainstream performance desktop platform. The chipset consists of an Intel

chipset Graphics and Memory Controller Hub (GMCH), an I/O Controller Hub (ICH) for the I/O

subsystem, and a Firmware* Hub (FWH). For this chipset, the graphics capability resides in the Graphics

and Memory Controller Hub (GMCH) chip.

The GMCH’s Graphics Controller (GC) contains an extensive set of registers and instructions for

configuration, 2D, 3D, and Video systems. This document describes the Intel

registers/instructions and provides detailed bit/field descriptions.

This Programmer’s Reference Manual (PRM) is intended for hardware, software, and Firmware*

designers who seek to implement or utilize the graphic functions of the Intel

with 2D and 3D graphics programming is assumed.

1.1. Terminology

Term Description

AGP Mode The GMCH is using its capability to interface with and AGP card. The internal

GPA Card Graphics Performance Accelerator Card. This is a new implementation which

CSI Command Stream Interface (same as instruction stream interface)

GC Graphics Controller

GFX Mode The GMCH is using its internal graphics capability. This means that the ability to

GMCH The Graphics and Memory Controller Hub component that contains the

Group 0 Protection (register) As per the original IBM VGA specification, CRT Controller registers CR[0:7] can

Instruction The GC has a set of graphics instructions. In some documents the term

IP Instruction Parser

MBZ Must Be Zero

®

82815

®

815 chipset

â

815 chipset. Familiarity

graphics controller is disabled in this mode.

allows local memory devices to be placed on a card that plugs into the AGP slot.

When an AGP card is not present, an GPA card can be added to improve

performance by acting as a display cache, for the Z-buffer only, of up to 4 MB.

The GPA card was previously known as the AIMM (Add-In Memory Module).

interface with an AGP card is disabled.

functionality of an MCH plus an internal graphics controller.

be write-protected via CR11[bit 7]. In BIOS code, this write protection is set

following each mode change. Note that other group protection levels have no

current use and are not supported by the GC. Only Group 0 Protection is

supported.

“command” is used for instruction.

15

Page 16

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

Term Description

MCH The Memory Controller Hub component that contains the processor interface,

DRAM controller, and AGP interface. The MCH communicates with the ICH over

a proprietary interconnect called the hub interface (previously known as

HubLink). The MCH was called the North Bridge (NB) in previous chip sets.

MCH will be used to refer to non-graphics portion of the GMCH.

MM Memory Mapped address space.

MMIO Memory Mapped I/O space.

QW Quad Word = 64 bits = 8 Bytes.

R/W (register) Read/Write. A register with this attribute can be read and written.

R/WC (register) Read/Write Clear. A register bit with this attribute can be read and written.

However, a write of 1 clears (sets to 0) the corresponding bit and a write of 0 has

no effect.

R/WO (register) Read/Write Once. A register bit with this attribute can be written to only once

after power up. After the first write, the bit becomes read only.

RO (register) Read Only. In some cases, if a register is read only, writes to this register

location have no effect. However, in other cases, two separate registers are

located at the same location where a read accesses one of the registers and a

write accesses the other register. See the I/O and memory map tables for

details.

WO (register) Write Only. In some cases, If a register is write only, reads to this register

location have no effect. However, in other cases, two separate registers are

located at the same location where a read accesses one of the registers and a

write accesses the other register. See the I/O and memory map tables for

details.

R

1.2. Reference Documents

The following documents should be available for reference when using this specification:

®

• Intel

• Intel

• Intel

• Intel

815 Chipset: Intel® 82815 chipset Graphics and Memory Controller Hub (GMCH) External

Design Specification (EDS)

®

82801AA (ICH) and Intel® 82801AB (ICH0) I/O Controller Hub Datasheet

®

82801BA (ICH2) I/O Controller Hub External Design Specification (EDS)

®

82802AB/82802AC Firmware* Hub (FWH) Datasheet

16

Page 17

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

2. Intel® 815 Chipset Overview

The chipset consists of an Intel® 82815 chipset Graphics and Memory Controller Hub (GMCH), an I/O

Controller Hub (ICH) for the I/O subsystem, and a Firmware* Hub (FWH). The GMCH integrates a

system memory SDRAM controller that supports a 64-bit 100/133 MHz SDRAM array. The Intel

chipset family includes:

• Intel

ââââ

815 chipset: This chipset consists of the Intel® 82815 chipset GMCH, the 82801AA ICH,

and the 82802AB/82802AC FWH.

ââââ

• Intel

815E chipset: This chipset consists of the Intel® 82815 chipset GMCH, the 82801BA ICH2,

and the 82802AB/82802AC FWH.

â

815

The Intel

®

82815 chipset GMCH integrates a Display Cache SDRAM controller that supports a 32-bit

133 MHz SDRAM array for enhanced integrated 2D and 3D graphics performance. Multiplexed with the

display cache interface is an AGP controller interface to enable graphics configuration and upgrade

flexibility with the Intel

â

815 chipset. The AGP interface and the internal graphics device are mutually

exclusive. When the AGP port is populated with an AGP graphics card, the integrated graphics is

disabled; thus, the display cache interface is not needed.

The Intel

bridge hub and the I/O Controller Hub (ICH) as the I/O hub. The Intel

82801AA ICH and the Intel

â

815 chipset family uses a hub architecture with the Intel® 82815 chipset GMCH as the host

â

815E chipset supports the 82801BA ICH2. The ICH is a highly integrated

â

815 chipset supports the

multifunctional I/O Controller Hub that provides the interface to the PCI Bus and integrates many of the

functions needed in today’s PC platforms. The GMCH and ICH communicate over a dedicated hub

interface.

17

Page 18

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

A

A

A

A

A

A

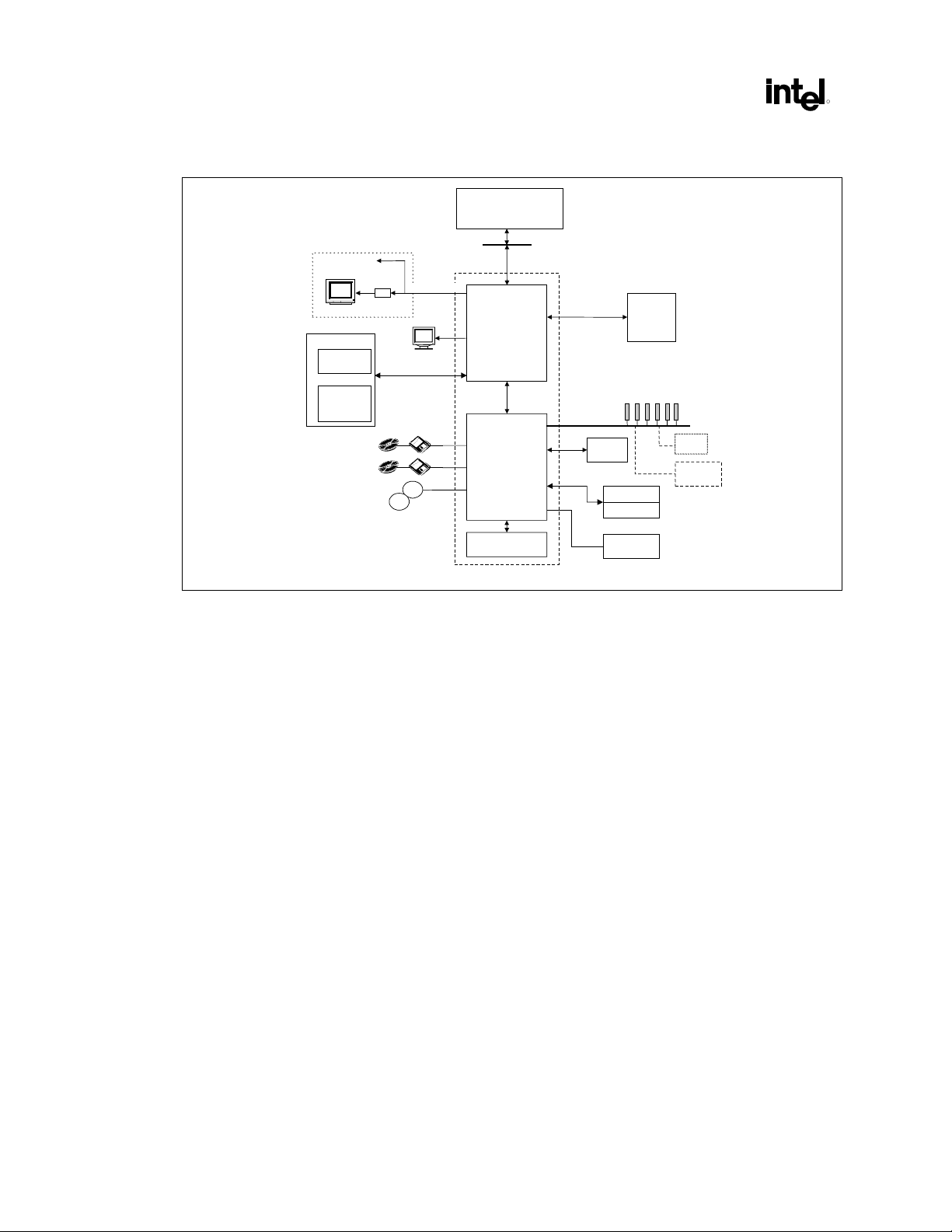

Figure 1. Intel

ââââ

815 Chipset System Block Diagram

Intel®Pentium®III Processor

®

Intel

Celeron™ Processor

Digital Video Out

Encoder

Digital Video Out

TV

GP Connector

GP Graphics

Or

Display Cache

(4 MB SDRAM,

133 MHz Only)

2 IDE Ports

Ultra ATA/66 (ICH);

Ultra ATA/100 (ICH2)

2 USB Ports (ICH);

4 USB Ports (ICH2)

USB

nalog Display

USB

(Graphics and Memory

Controller Hub)

- Memory Controller

- AGP Contoller

- Graphcs Controller

- 3D Engine

- 2D Engine

- Video Engine

I/O Controller Hub

(Firmware Hub)

or

System Bus (66/100/133 MHz)

GMCH

FWH

100/133 MHz Only

LPC

64 Bit /

PCI Bus

C'97

(ICH=6 Req/Gnt pairs)

Super

I/O

udio Codec

Modem Codec

LAN Controller

(ICH2)

System

Memory

PCI Slots

IS

Option

LAN Option

(for ICH)

815_SysBlk

R

2.1. I/O Controller Hub

The 82801AA ICH/82801BA ICH2 functions and capabilites are listed below. Unless otherwise

specified, the function/capability applies to both ICH and ICH2.

• PCI Rev 2.2 compliant with support for 33 MHz PCI operations

• ICH supports up to 6 Req/Gnt pairs

• Power Management Logic Support

• Enhanced DMA Controller, Interrupt Controller & Timer Functions

• Integrated IDE controller; ICH supports Ultra ATA/66 (ICH); Ultra ATA/100/66/33 (ICH2)

• Integrated LAN Controller (ICH2 only)

• USB host interface with support for two USB ports (ICH); Four ports (ICH2)

2

• System Management Bus (SMBus) compatible with most I

C devices

• AC’97 2.1 Compliant Link for Audio and Telephony CODECs

• Low Pin Count (LPC) interface

• Firmware* Hub (FWH) interface support

• Alert On LAN*

2.2. Intel® 82815 Chipset GMCH Overview

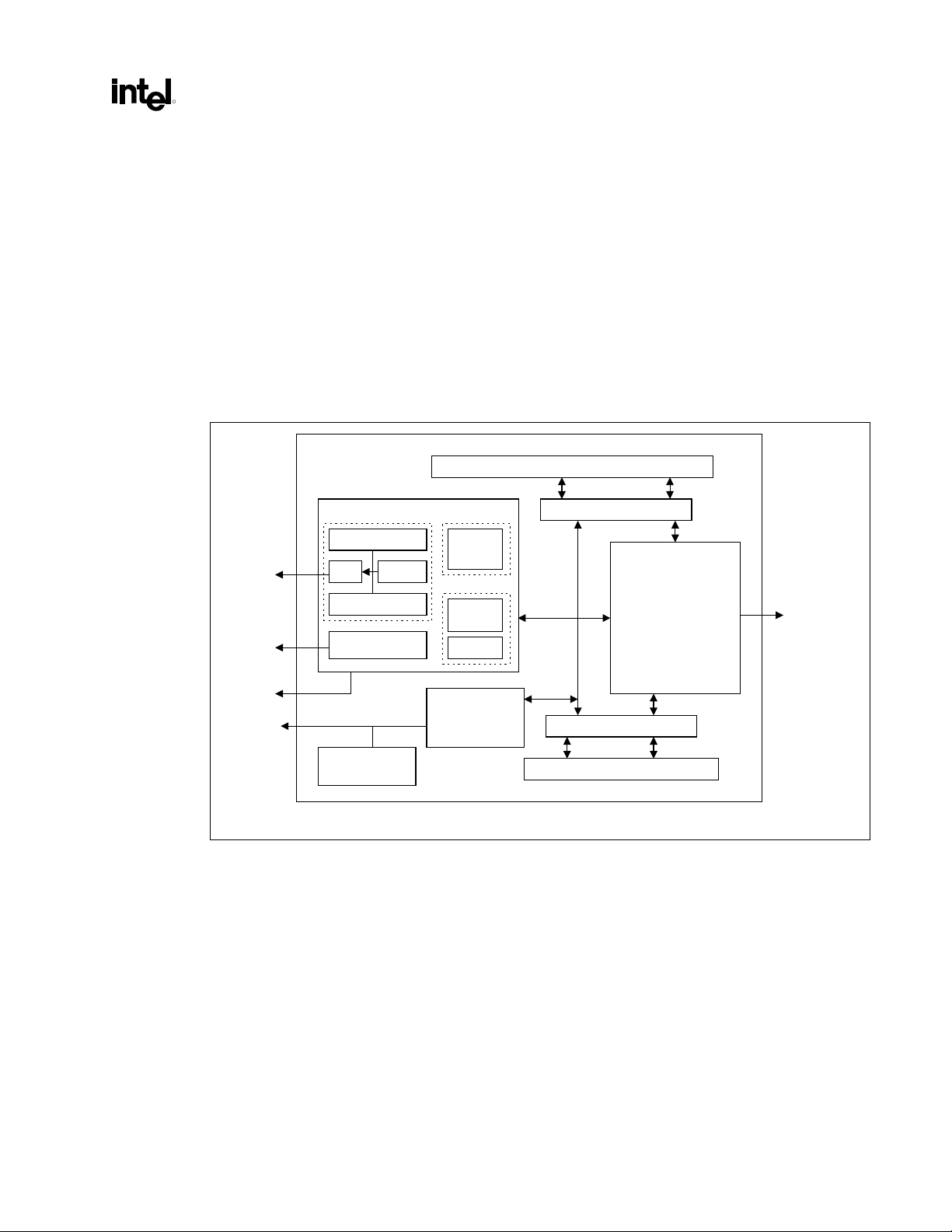

Figure 2 is a block diagram of the GMCH illustrating the various interfaces and integrated functions. The

functions and capabilities include:

18

Page 19

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

• Support for a single processor configuration

• 64-bit AGTL+ based System Bus Interface at 66/100/133 MHz

• 32-bit Host Address Support

• 64-bit System Memory Interface with optimized support for SDRAM at 100/133 MHz

• Integrated 2D & 3D Graphics Engines

• Integrated H/W Motion Compensation Engine

• Integrated 230 MHz DAC

• Integrated Digital Video Out Port

• 133 MHz Display Cache

• AGP 1X/2X/4X Controller

Figure 2. Intel® 82815 Chipset GMCH Block Diagram

System Bus Interface

Display Engine 3D Engine

HW Motion Comp

Analog

Display

Out

Digital

Video

Out

DDC/

2

I

AGP/

Display

Cache

Pins

C

DAC Overlay

HW Cursor

Digital Video Out

Port

Local Memory

Interface

2.2.1. Host Interface

The host interface of the GMCH is optimized to support the Intel Pentium® III processor and Intel

Celeron

bus interfaces within a single device. The GMCH supports a 4-deep in-order queue (i.e., supports

pipelining of up to 4 outstanding transaction requests on the host bus). Host bus addresses are decoded

by the GMCH for accesses to system memory, PCI memory and PCI I/O (via hub interface), PCI

configuration space and Graphics memory. The GMCH takes advantage of the pipelined addressing

capability of the processor to improve the overall system performance.

TM

processor in the FC-PGA package. The GMCH implements the host address, control, and data

3D

Engine

2D Engine

Stretch

BLT Eng

BLT Eng

AGP Interface

Buffer

Memory Interface

Buffer

Hub Interface

System

Memory

gmch_blk2.vsd

The Intel

®

82815 chipset GMCH supports the 370-pin socket processor.

19

Page 20

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

• 370-pin socket (PGA370). The PGA370 is a zero insertion force (ZIF) socket that a processor in

the FC-PGA package will use to interface with a system board.

2.2.2. System Memory Interface

The GMCH integrates a system memory controller that supports a 64-bit 100/133 MHz SDRAM array.

The only DRAM type supported is industry standard Synchronous DRAM (SDRAM). The SDRAM

controller interface is fully configurable through a set of control registers.

The GMCH supports industry standard 64-bit wide DIMMs with SDRAM devices. The thirteen

multiplexed address lines, SMAA[12:0], along with the two bank select lines, SBS[1:0], allow the

GMCH to support 2M, 4M, 8M, 16M, and 32M x64 DIMMs. Only asymmetric addressing is supported.

The GMCH has six SCS# lines (two copies of each for electrical loading), enabling the support of up to

six 64-bit rows of SDRAM. The GMCH targets SDRAM with CL2 and CL3 and supports both single

and double-sided DIMMs. Additionally, the GMCH also provides a 1024 entry deep refresh queue. The

GMCH can be configured to keep up to 4 pages open within the memory array. Pages can be kept open

in any one bank of memory.

SCKE[5:0] are used in configurations requiring powerdown mode for the SDRAM.

2.2.3. Multiplexed AGP and Display Cache Interface

R

The Intel® 82815 chipset GMCH multiplexes an AGP interface with a display cache interface for internal

3D graphics performance improvement. The display cache is used only in the internal graphics. When an

AGP card is installed in the system, the GMCH internal graphics will be disabled and the AGP controller

will be enabled.

AGP Interface

A single AGP connector is supported by the GMCH AGP interface. The AGP buffers operate in one of

two selectable modes in order to support the AGP Universal Connector:

• 3.3V drive, not 5 volt safe: This mode is compliant to the AGP 1.0 and 2.0 specifications.

• 1.5V drive, not 3.3 volt safe: This mode is compliant with the AGP 2.0 specification.

The following table shows the AGP Data Rate and the Signaling Levels supported by the GMCH.

Signaling Level Data Rate

1.5V 3.3V

1x AGP Yes Yes

2x AGP Yes Yes

4x AGP Yes No

The AGP interface supports 4x AGP signaling. AGP semantic (PIPE# or SBA[7:0]) cycles to SDRAM

are not snooped on the host bus. AGP FRAME# cycles to SDRAM are snooped on the host bus. The

GMCH supports PIPE# or SBA[7:0] AGP address mechanisms, but not both simultaneously. Either the

PIPE# or the SBA[7:0] mechanism must be selected during system initialization. High priority accesses

are supported. Only memory writes from the hub interface to AGP are allowed. No transactions from

AGP to the hub interface are allowed.

20

Page 21

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

Display Cache Interface

The GMCH supports a Display Cache SDRAM controller with a 32-bit 133 MHz SDRAM array. The

DRAM type supported is industry standard Synchronous DRAM (SDRAM) like that of the system

memory. The local memory SDRAM controller interface is fully configurable through a set of control

registers.

2.2.4. Hub Interface

The hub interface is a private interconnect between the GMCH and the ICH.

2.2.5. Intel® 82815 Chipset GMCH Integrated Graphics Support

The GMCH includes a highly integrated graphics accelerator. Its architecture consists of dedicated multimedia engines executing in parallel to deliver high performance 3D, 2D and motion compensation video

capabilities. The 3D and 2D engines are managed by a 3D/2D pipeline preprocessor allowing a sustained

flow of graphics data to be rendered and displayed. The deeply pipelined 3D accelerator engine provides

3D graphics quality and performance via per-pixel 3D rendering and parallel data paths which allow each

pipeline stage to simultaneously operate on different primitives or portions of the same primitive. The

GMCH graphics accelerator engine supports perspective-correct texture mapping, trilinear and

anisotropic Mip-Map filtering, Gouraud shading, alpha-blending, fogging and Z-buffering. A rich set of

3D instructions permit these features to be independently enabled or disabled.

For the GMCH, a Display Cache (DC) can be used for the Z-buffer (textures and display buffer(s) are

located only in system memory). If the display cache is not used, the Z-buffer is located in system

memory.

The GMCH integrated graphics accelerator’s 2D capabilities include BLT and arithmetic STRBLT

engines, a hardware cursor and an extensive set of 2D registers and instructions. The high performance

64-bit BitBLT engine provides hardware acceleration for many common Windows* operations.

In addition to its 2D/3D capabilities, the GMCH integrated graphics accelerator also supports full

MPEG-2 motion compensation for software-assisted DVD video playback, a VESA DDC2B compliant

display interface and a digital video out port which may support (via an external video encoder) NTSC

and PAL broadcast standards and (via an external TMDS transmitter) digital Flat Panel or Digital CRT

displays.

Display, Digital Video Out, and LCD/Flat Panel/Digital CRT

The GMCH provides interfaces to a standard progressive scan monitor, TV-Out device, and TMDS

transmitter. These interfaces are only active when running in internal graphics mode.

• The GMCH directly drives a standard progressive scan monitor up to a resolution of 1600x1200

pixels.

• The GMCH provides a Digital Video Out interface to connect an external device to drive a

1280x1024 resolution non-scalar DDP digital Flat Panel with appropriate EDID 1.2 data or digital

CRTs. The interface has 1.8V signaling to allow it to operate at higher frequencies. This interface

can also connect to a 1.8V TV-Out encoder.

21

Page 22

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

2.2.6. System Clocking

The Intel® 82815 chipset GMCH has a new type of clocking architecture. It has integrated SDRAM

buffers that run at either 100 or 133 MHz, independent of the system bus frequency. See table below for

supported system bus and system memory bus frequencies. The system bus frequency is selectable

between 66 MHz, 100 MHz or 133 MHz. The GMCH uses a copy of the USB clock as the DOT Clock

input for the graphics pixel clock PLL.

Table 1. Supported System Bus and System Memory Bus Frequencies

Front Side Bus

Frequency

66 MHz 100 MHz 133 MHz or DVMT

100 MHz 100 MHz 133 MHz or DVMT

133 MHz 100 MHz 133 MHz or DVMT

133 MHz 133 MHz 133 MHz or DVMT

System Memory

Bus Frequency

Display Cache Interface

Frequency

2.2.7. GMCH Power Delivery

R

The Intel® 82815 chipset GMCH core voltage is 1.85V. System Memory runs off of a 3.3V supply.

Display cache memory runs off of the AGP 3.3V supply. AGP 1X/2X I/O can run off of either a 3.3V or

a 1.5V supply. AGP 4X I/O require a 1.5V supply. The AGP interface voltage is determined by the

VDDQ generation on the motherboard.

2.3. Three PCI Devices on GMCH

The Intel® 82815 chipset GMCH contains three PCI Devices. The management of active devices is

controlled via bit 0 of the APCONT register (See the Intel

Controller (GMCH) EDS for details on PCI configuration registers).

• Device 0 = Host Bridge = PCI bus #0 interface, Main Memory Controller, Graphics Aperture

controller

• Device 1 = AGP Bridge = AGP 2X/4X interface (AGP Mode)

• Device 2 = Internal Graphics Device (GFX Mode)

Note: Devices 1 and 2 are mutually exclusive. Only one of these two devices can be active at any given time.

Device selection is performed during the start-up sequence and can only be set once. The lock bit must

be set after device selection.

The following diagram shows more detail at a platform level. The GMCH is shown in both AGP Mode

(left side) and GFX Mode (right side). Only one mode can be active at any given time. The processor and

ICH functions remain unchanged by the GMCH mode of operation.

®

815 Chipset: 82815 Graphics and Memory

22

Page 23

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

Figure 3. Conceptual Platform PCI Configuration Diagram

Processor

AGP/

Secondary PCI

(Bus #A -

programmable)

AGP

Master

AGP

Bridge

Bus #0

Dev #

PCI Config uration

Window in I/O Space

1

Hub Interface

AGP Mode

DRAM* Control/

Host Bridge

Bus #0

Dev #0

Hub Interface

LPC Device

Bus #0

Dev #31

Fcn #0

= Logical PCI Bus #0

2.3.1. Multi-Mode Capability Requirements

PCI Configuration

Window in I/O Space

Internal

Graphics

Bus #0

Dev #

2

Hub Interface

Hub Interface 0

(Logical PCI Bus #0)

ICH

Hub I/F - PCI

Bridge (P2P)

PBus #0

Dev #30

Fcn #0

GFX Mode

DRAM* Control/

Host Bridge

Bus #0

Dev #0

PCI

Devices

Primary PCI

(Bus #B - programmable)

There are multiple Device Modes that are supported by the three PCI devices within this component:

1. AGP Mode – The AGP slot is populated with an AGP graphics card and the AGP interface device

is active. The internal graphics controller is inactive.

2. GFX Mode with Local Memory – The internal graphics device is active. The AGP slot is

populated with a GPA card and the AGP interface device is inactive.

3. GFX Mode with Shared Memory – The internal graphics device is active. The AGP slot is not

populated with a GPA card or an AGP graphics card and the AGP interface device is inactive.

4. PCI Mode – The internal graphics controller and the AGP interface device are both inactive. The

display data cycles are routed through the hub interface to the PCI display device.

2.3.1.1. Supported Single Monitor and Multi-monitor Configurations

For modern operating systems that have multiple monitor support, the primary graphics device must not

be the Intel

can serve only as secondary graphics devices in a multi-monitor configuration. It is important to

understand that there is no support for simultaneous operation of the internal graphics device and an

AGP graphics card.

23

®

815 chipset internal graphics controller or an AGP graphics card. These graphics devices

Page 24

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

To support a PCI graphics device, the Intel

®

815 chipset simply passes all of that device’s cycles to the

hub interface as it would for any other PCI device.

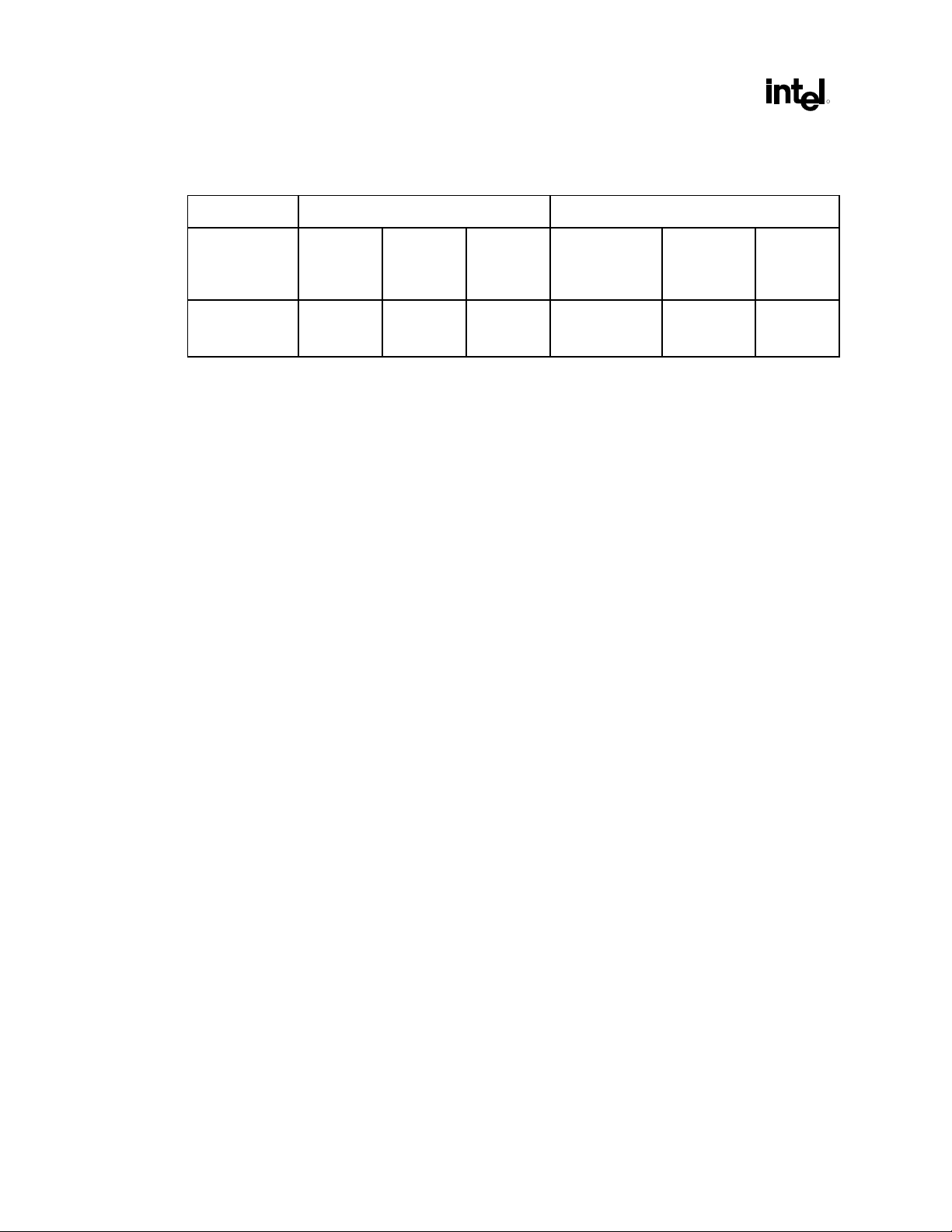

Configuration Single Monitor Multi-monitor

Primary

Graphics

Device

Secondary

Graphics

Device

Internal

Graphics

(with LM or

UMA)

None None None Internal

AGP

Graphics

Card

Non-AGP

Graphics

Card (PCI)

Non-AGP

Graphics Card

(PCI)

Graphics (with

LM or UMA)

Non-AGP

Graphics

Card (PCI)

AGP

Graphics

Card

Non-AGP

Graphics

Card (PCI)

Non-AGP

Graphics

Card (PCI)

R

24

Page 25

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

R

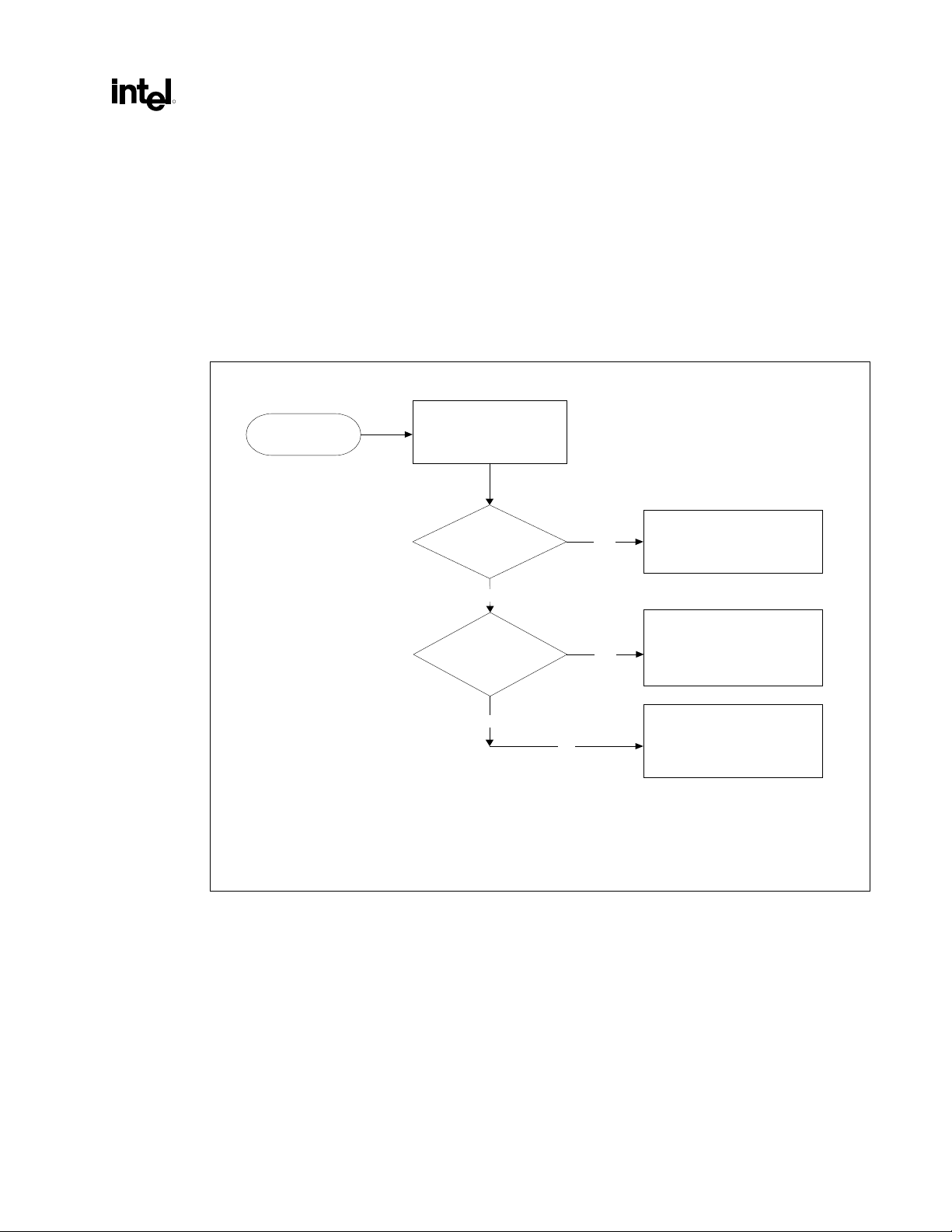

2.3.1.2. System Startup

The Intel® 815 chipset has multiple possible device modes. The selection of which mode will be autodetected is represented in the following flow chart. The software requirements for implementing this high

level flow are detailed in the next section.

Multi-monitor configurations are not addressed, as that is a function of the operating system when

supported. System BIOS also provides the ability to select any of the display devices as the primary

display device.

Figure 4. Device Mode Auto-Detect Flowchart

System Reset

Memory and Basic

chipset Initialization

AGP Card

Detected?

No

Display Cache

(GPA Card)

Detected?

No

Yes

Yes

No

DEV#0, REG53H, Bit1=0

Display Cache on GPA

DEV#0, REG53H, BIT1=1

DEV#0, REG53H, BIT1=1

REG70H, BIT7:6=11 or 10

Mode 1

(AGP Card)

Mode 2

(Internal Graphics with

Card)

Mode 3

(Internal Graphics with

Shared Memory)

25

Page 26

Intel® 815 Chipset: Graphics Controller PRM, Rev 1.0

2.3.1.3. Software Start-Up Sequence

The following sequence of events will occur during the initialization of an Intel® 815 chipset-based

system:

1. The ICH asserts PCIRST# either in response to an initial assertion of PWROK or a write to an I/O

Port.

2. System BIOS runs basic POST code to test the processor.

3. System BIOS initializes the minimum set of Intel

initiate a PCI configuration cycle towards the AGP/PCI interface (e.g., bus #1). Note that

following a system reset condition, the Intel

Graphics disabled).

4. System BIOS detects if an AGP graphics card is present by attempting a configuration read cycle

to the Intel

®

815 chipset AGP/PCI interface. If the configuration cycle completes successfully, then

it is assumed that an external graphics device is present on the AGP interface, and the Intel

chipset remains in “AGP Mode” (APCONT[0] = 0). If the AGP/PCI configuration cycle results in

a Master Abort, then it is assumed no external AGP graphics device is present, and the System

BIOS programs the Intel

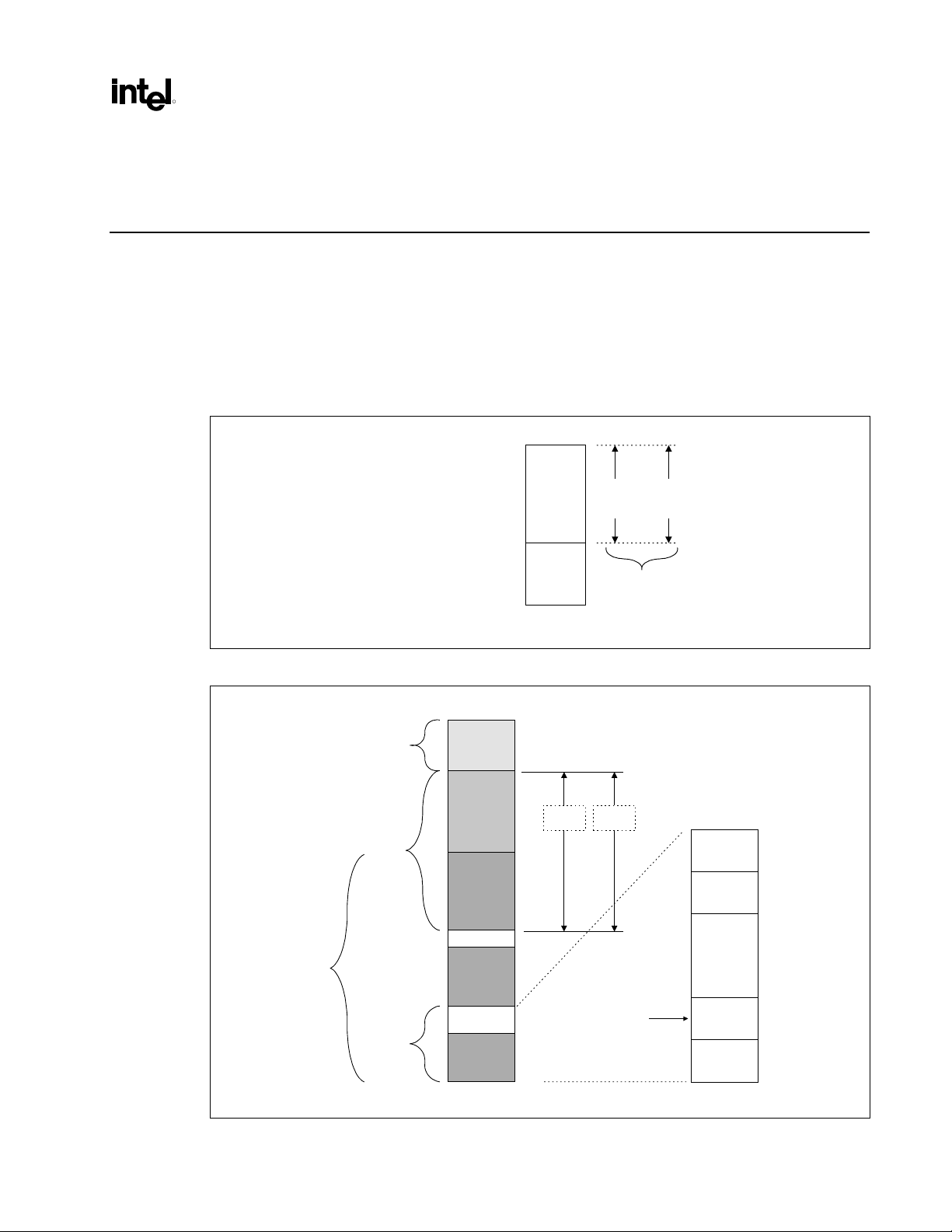

®