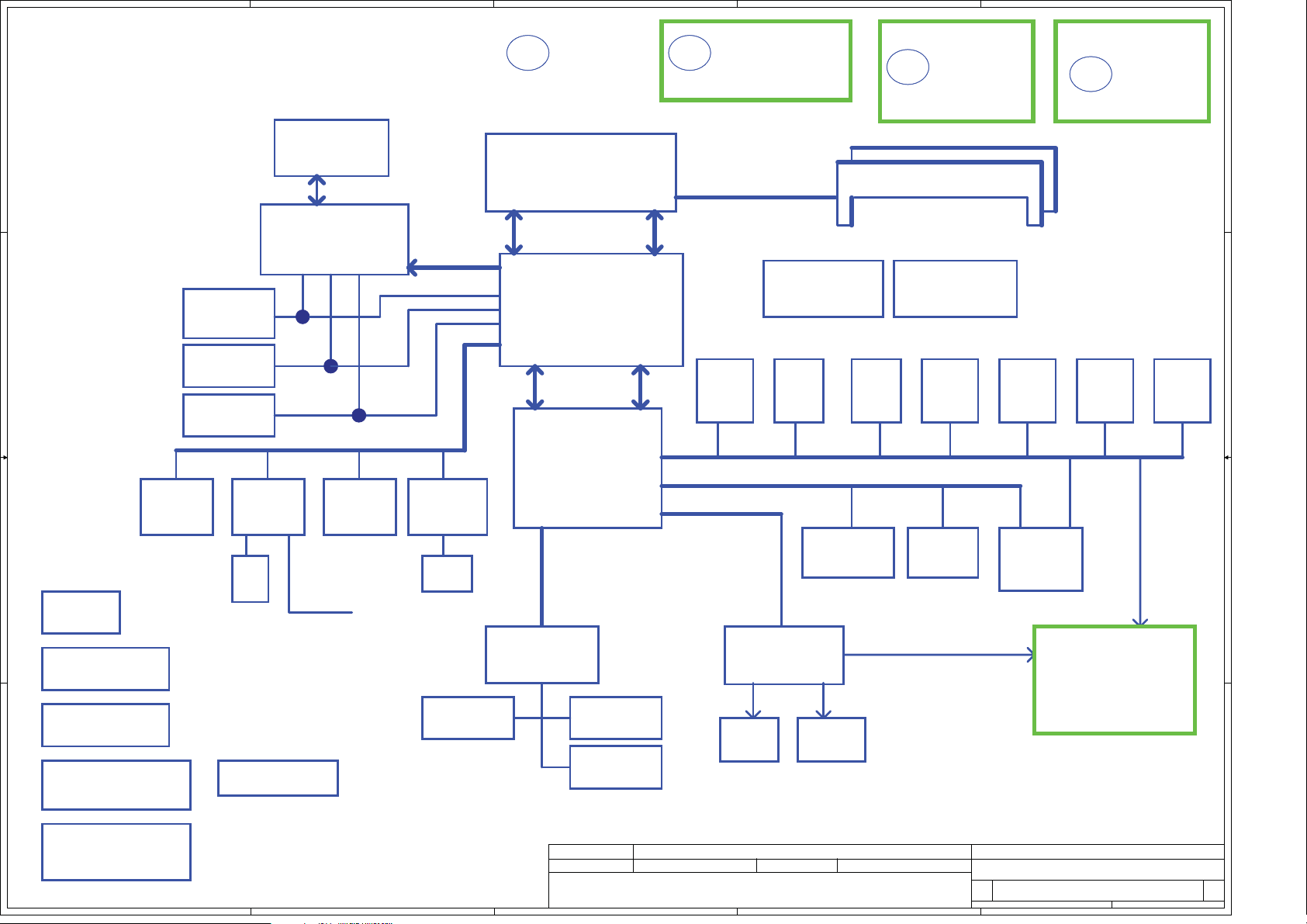

Compal LA-5754P NAWE6 AMD Danube, G565, IdeaPad Z565 Schematic

A

B

C

D

E

http://hobi-elektronika.net

1 1

Compal Confidential

2 2

NAWE6 Schematics Document

AMD Danube

Champlain Processor with RS880M/SB820/Park VGA

2010-02-24

3 3

LA5754 REV: 0.2

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2010/03/12

2008/10/06 2010/03/12

2008/10/06 2010/03/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

NAWE6 LA-5754P

NAWE6 LA-5754P

NAWE6 LA-5754P

E

0.2

0.2

0.2

of

of

of

147Monday, March 01, 2010

147Monday, March 01, 2010

147Monday, March 01, 2010

A

Compal Confidential

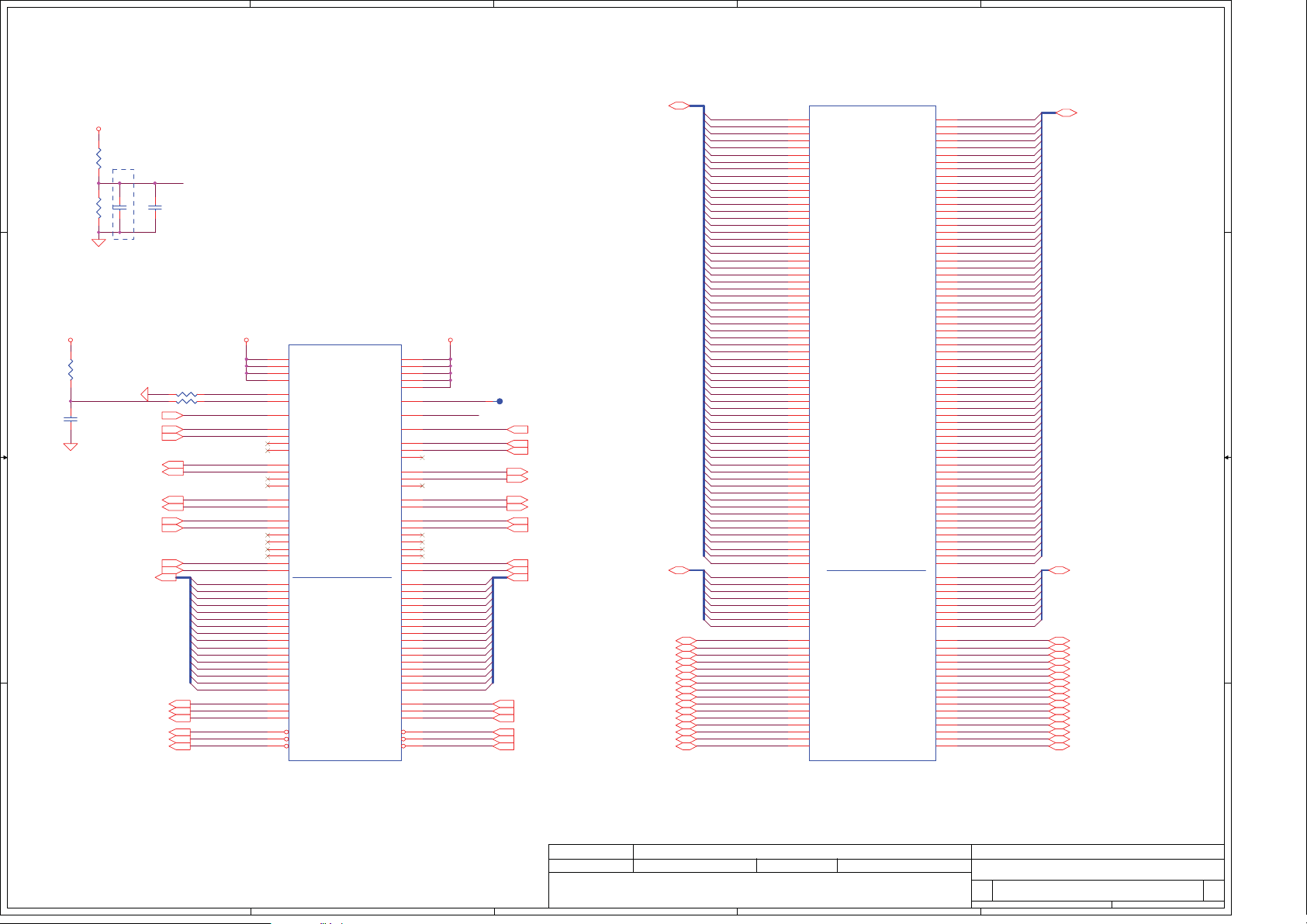

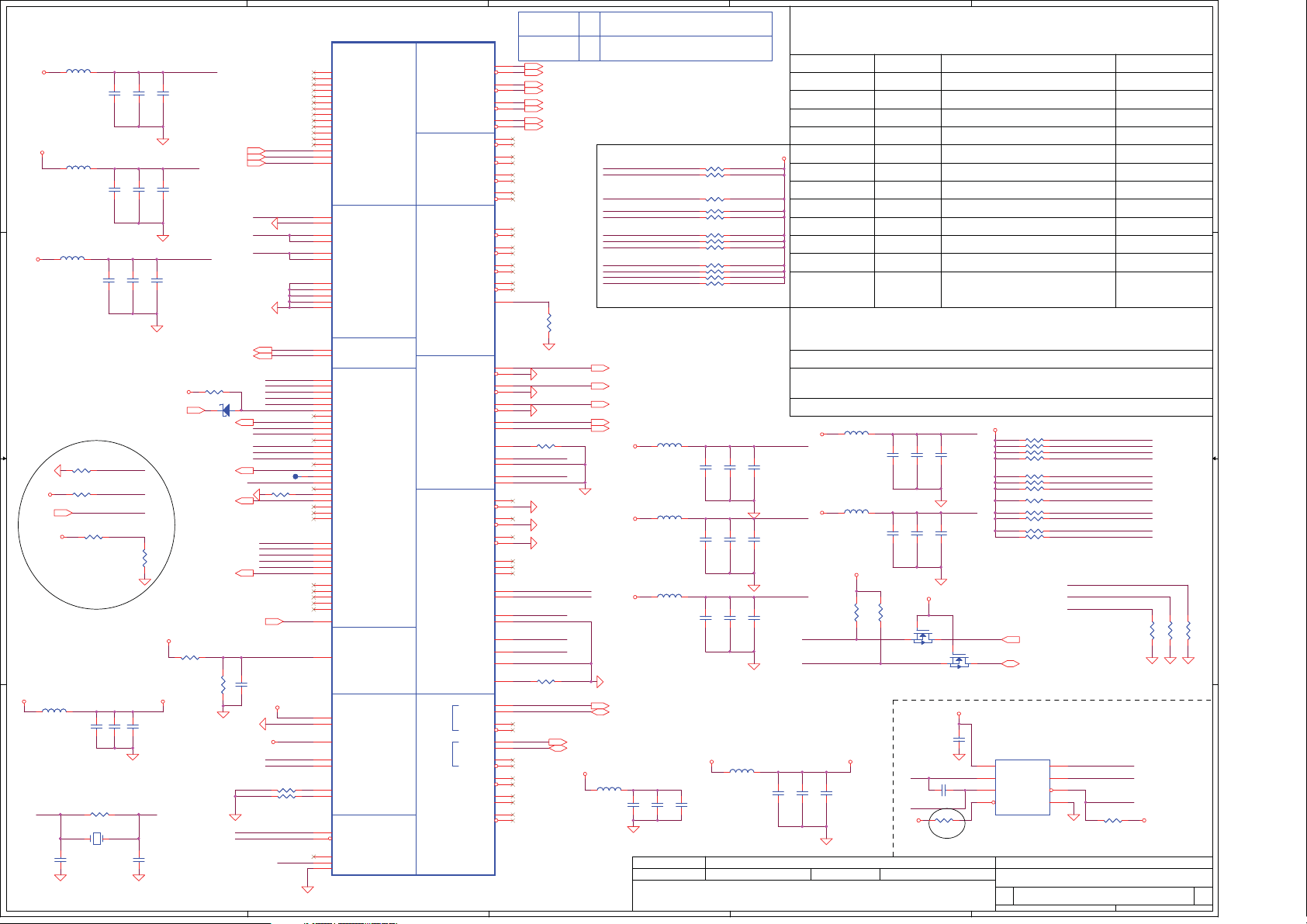

Model Name : AMD Danube + Park

1 1

VRAM 512MB

64M16 x 4

ATI M93-S3

Park - S3

uFCBGA-631

Page 13,14,15,16,17

LVDS

page 27

2 2

page 18

DDR3

B

PCI-Express x 16

ZZZ1

ZZZ1

LA5754P

LA5754P

DAZ@

DAZ@

DA80000IP00

DA80000IP00

Danube

AMD S1G4 Processor

uPGA-638 Package

Champlain

Hyper Transport Link

16 x 16

Gen2

ATI RS880M

uFCBGA-528

page 10,11,12,13

C

page 4,5,6,7

ZZZ2

POWER BD:

LS-5758P

@

DA40000TD00

POWER BTN

NOVO BTN

POWER MANAGE BTN

Memory BUS(DDR3)

Dual Channel

1.5V DDRIII 800~1333MHz

page 37

D

CAP SENSOR BD:

ZZZ3

ZZZ3

LS5756P

LS5756P

@

@

DA40000T300

DA40000T300

4 layer

VOLUME UP

VOLUME DOWN

MUTE

AUDIO ENHANCE

BUTTON & LED

204pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

Thermal Sensor

ADM1032

page 37 page 27 page 37 page 28

page 6 page 19

Clock Generator

ICS9LPRS488

page 8,9

E

CARD READER BD:

ZZZ4

ZZZ4

LS5753P

LS5753P

@

@

DA40000Q210

DA40000Q210

page 28

RTS5159

HP JACK

MIC JACK

page 28

CRT

page 25

A link Express2

Gen1

HDMI Conn.

page 26

ATI SB820M

New Card

WLAN

page 28

GPP3

3 3

LED

page 36

3G/WWAN

MINI Card

page 28

GPP2

SIM

Card

page28

MINI Card

USB(WWAN)

WLAN

page 28

LID SW / IO BD

page 32

Power On/Off CKT.

page 32

DC/DC Interface CKT.

4 4

page 38

Fan Control

page 31

LAN(GbE)

Atheros

AR8151/8152

page 29

GPP0GPP1

RJ45

page 30

Touch Pad

page 35

ENE KB926

uFCBGA-605

page 20,21,22,23,24

LPC BUS

page 34

Int.KBD

page 35

BIOS

page 34

USB

PORT

(LEFT)

USB port 0

3.3V 48MHz

3.3V 24.576MHz/48M hz

HD Audio

Audio Codec

Realtec ALC259

Analog

MIC_Int

USB

conn

(Right)

CMOS

Camera

USB port 5USB port 12 USB port 11

USB

SATA HDD

Conn.

page 32

port 0

page33

2Channel

Speaker

page33 page33

Bluetooth

Conn

<Option>

USB port 6

S-ATA

CDROM

Conn.

port 1

page 32

Gen2

ESATA &

USB

Combine CON

Mini

card

(WL)X1

3G/GPS

WWAN

<Option>

USB port 10

USB port 4

page28

Card Reader /

Audio Jack SB CONN

RTS5159-GR

MS/MS

pro/SD/SD

pro/mmc/XD

New Card

USB port 7

USB port 2

HP X 1+

MIC_Ext X1

page38

Power Circuit

page 39,40,41,42,43,

44,45,46,47,48,49

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2009/10/06

2008/10/06 2009/10/06

2008/10/06 2009/10/06

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

NAWE6 LA-5754P

NAWE6 LA-5754P

NAWE6 LA-5754P

E

0.2

0.2

0.2

of

of

of

247Monday, March 01, 2010

247Monday, March 01, 2010

247Monday, March 01, 2010

A

B

C

D

E

http://hobi-elektronika.net

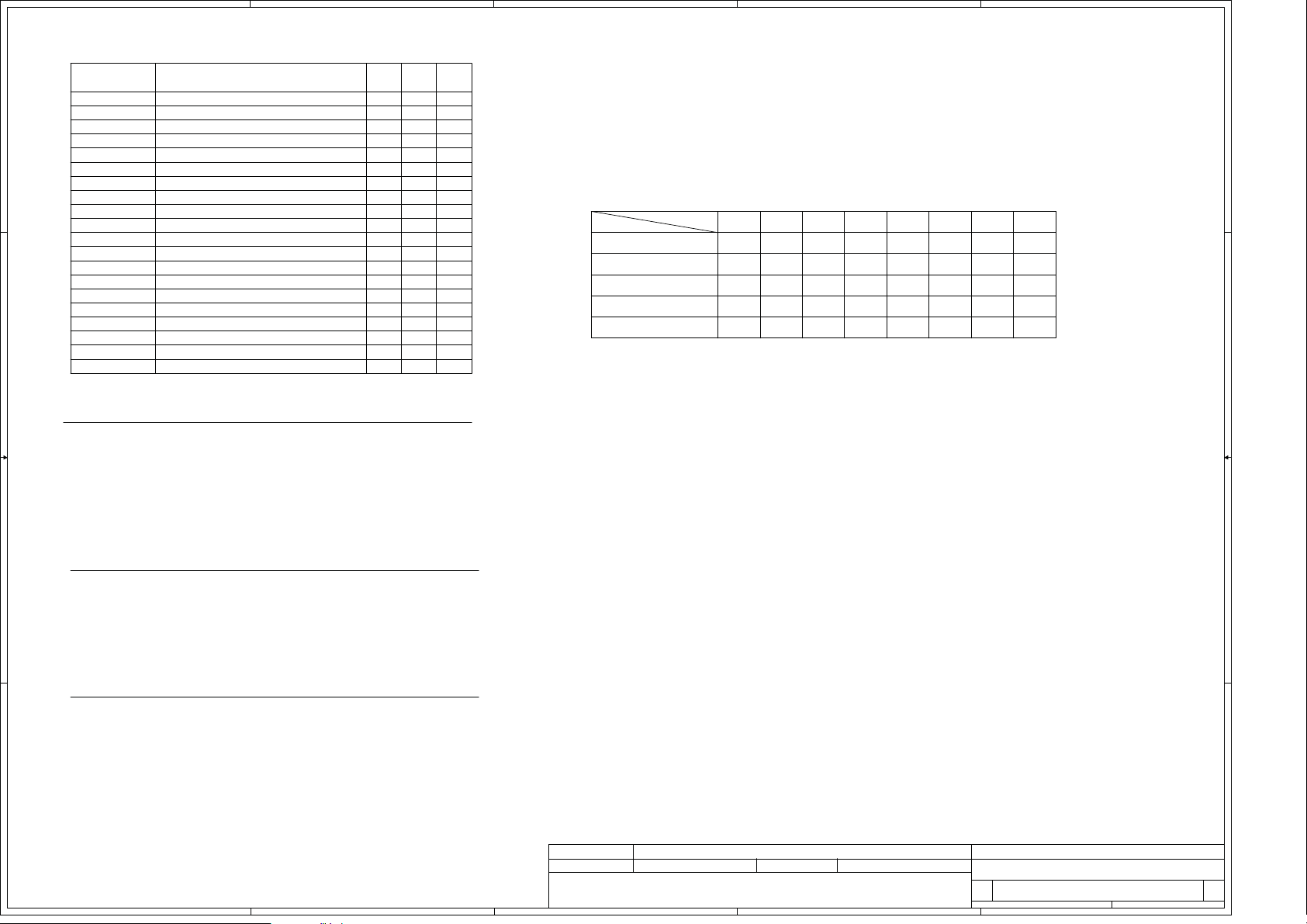

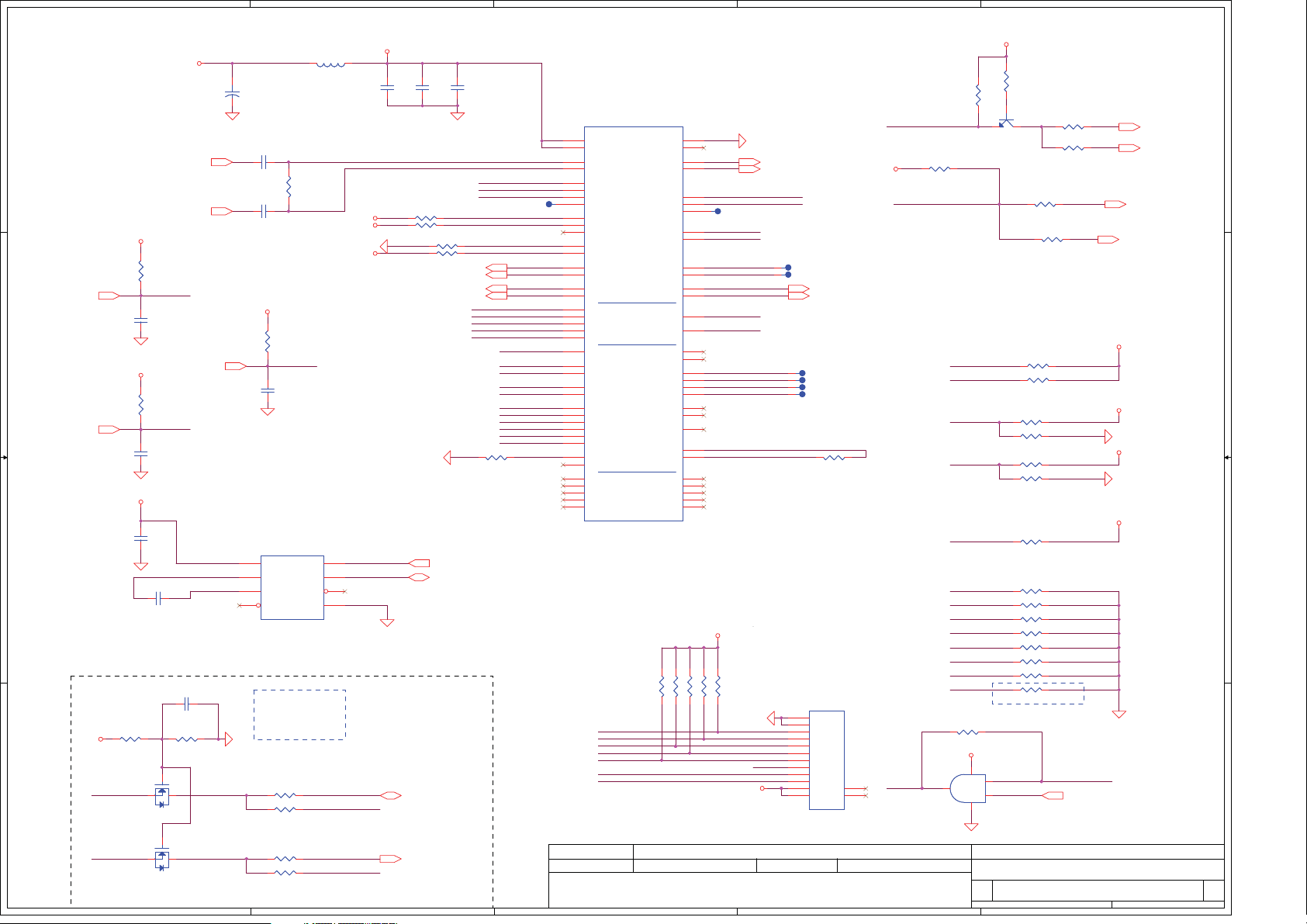

Voltage Rails

Power Plane Description

VIN

1 1

B+

+CPU_CORE_0

+CPU_CORE_1 Core voltage for CPU (0.7-1.2V)

+CPU_CORE_NB Voltage for On-die Nor thbridge of CPU(0.8-1 .1V)

+0.75VS +0.75VS LDO powe r rail for DDR3 VTT

+1.1VS

Adapter power supply (19V)

AC or battery power r ail for power cir cuit.

Core voltage for CPU (0.7-1.2V)

1.1V switched powe r rail for NB VDDC & VGA

S1 S3 S5

N/A N/A N/A

ON OFF

ON OFF OFF

ON OFF OFF

ON

ON OFF OFF

ON

N/AN/AN/A

OFF

OFF

+VGA_CORE

+1.5VS

+1.5V

+1.8VS 1.8V switched power rail

+2.5VS

+3VALW

+3V_LAN 3.3V power rail for LAN ON ON ON

+3VS

+5VALW

2 2

+5VS

+VSB VSB always on power rail ON ON*

+RTCVCC RTC power

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

0.95-1.2V switched power rail

1.5V power rail for PCIE Card

1.5V power r ail for CPU VDDIO a nd DDR

2.5V for CP U_VDDA

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFFOFFON

OFF OFF

ON

OFF

OFF

OFF

OFF

OFF

ON ON*

OFF

OFF

ON*

ON

OFFON

OFF

ONON

STATE

SIGNAL

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SLP_S1# SLP_S3#

SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

HIGH

LOW

LOWLOWLOW

LOW LOW LOW LOW

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

OFF

OFF

ON ON

ON

OFF

OFF

OFF

LOW

OFF

OFF

OFF

ON

ON

ON

ON

ON

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

3 3

EC SM Bus1 address

Device

Smart Battery

Address

0001 011X b

HEX

16H

EC SM Bus2 address

Device

EMC1402-1 (CPU)

EMC1412-A (GPU)

EMC1403-2 (DDR,WWAN)

Address

100_1100b

111_1100b

100_1101b

HEX

4CH

7CH

4DH

SB820

SM Bus 0 address

Device

Clock Generator

(SILEGO SLG8SP626)

DDR DIMM1

DDR DIMM2

4 4

Address

1101 001Xb

1001 000Xb

1001 010Xb

HEX

D2

90

94

SB820

SM Bus 1 address

Device Address

BOM Config

UMA only SKU: UMA@

DIS ONLY (Park S3): DIS@

EXT CLK Mode:EXT@

INT CLK mode:INT@

LAN GIGA: 8151@

LAN 100: 8152@

CMOS@

BT@

3G@

S@

H@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2010/03/12

2008/10/06 2010/03/12

2008/10/06 2010/03/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Notes List

Notes List

Notes List

NAWE6 LA-5754P

NAWE6 LA-5754P

NAWE6 LA-5754P

E

0.2

0.2

0.2

of

of

of

347Monday, March 01, 2010

347Monday, March 01, 2010

347Monday, March 01, 2010

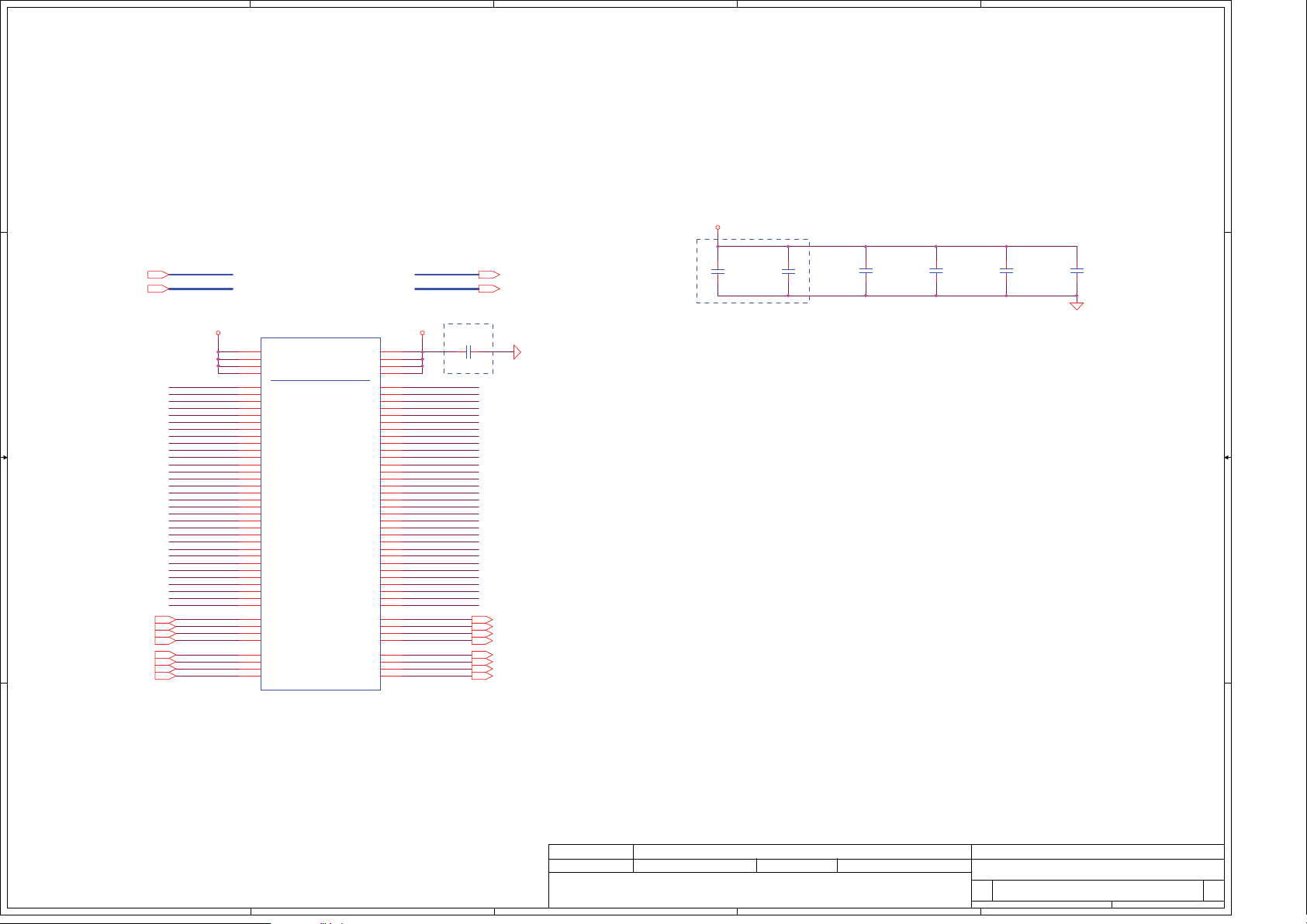

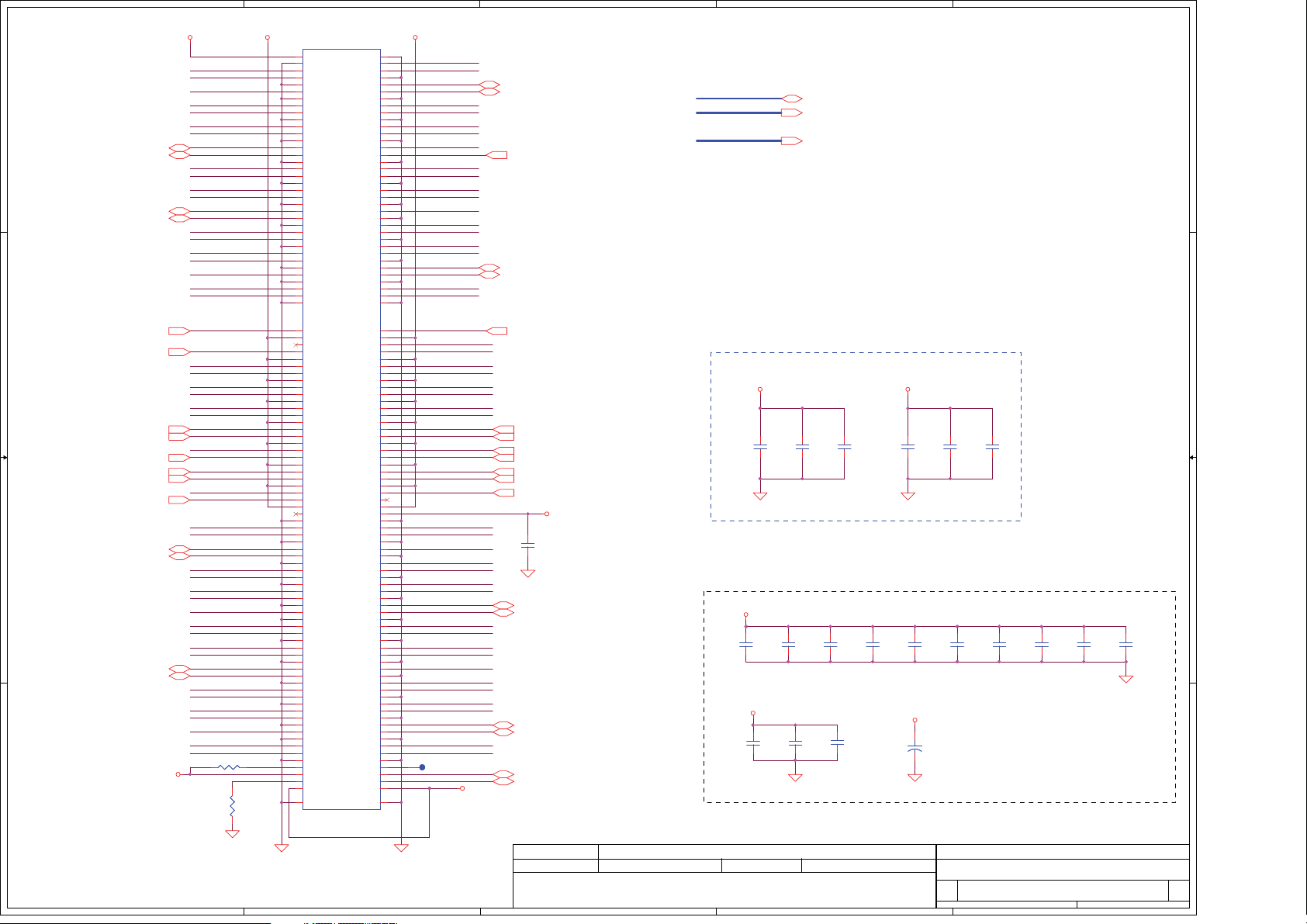

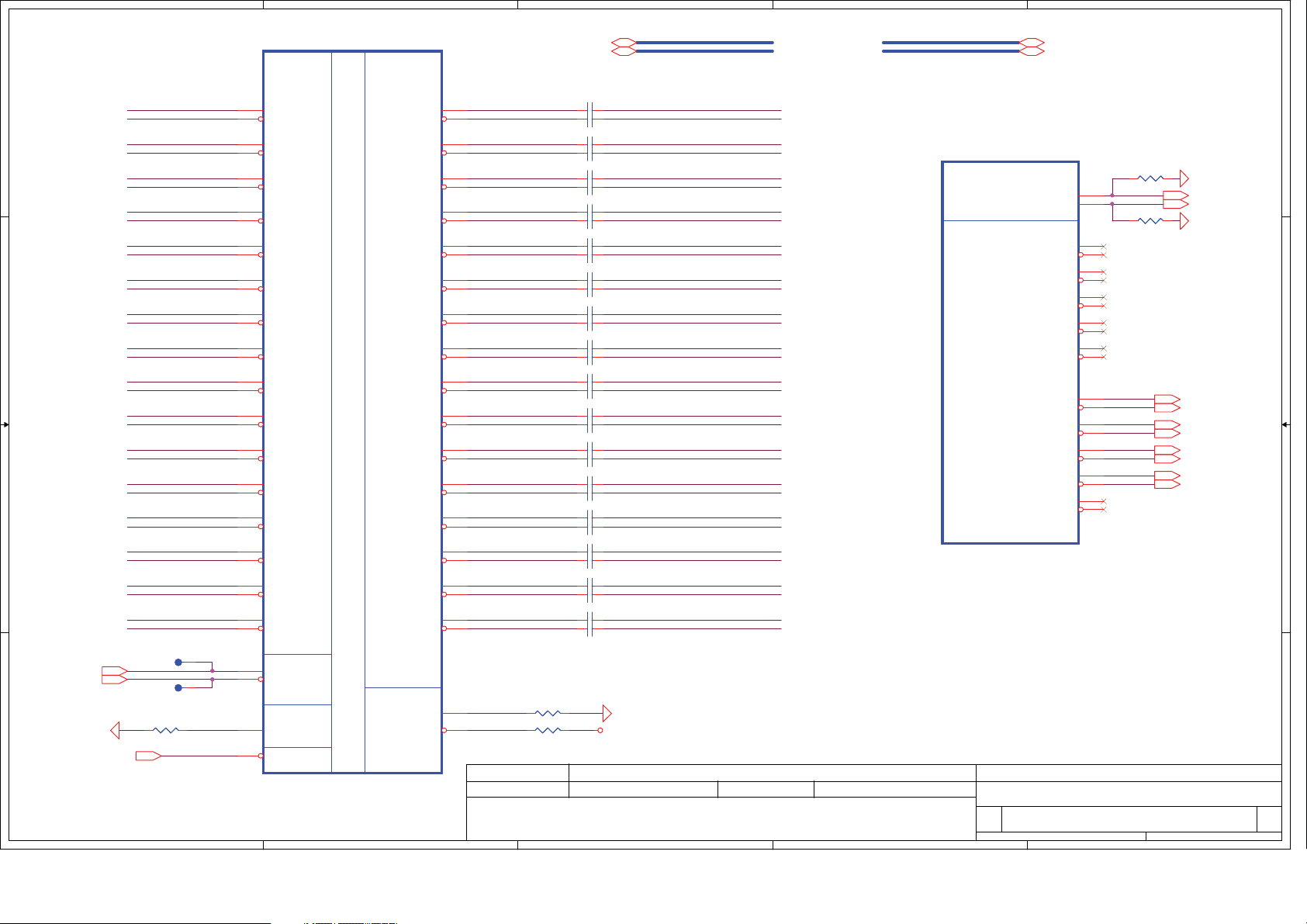

A

1 1

B

C

D

E

+1.1VS

250 mil

2

C1

H_CADIP[0..15][10]

H_CADIP[0..15]

H_CADIN[0..15]

H_CADOP[0..15]

H_CADON[0..15]

H_CADOP[0..15] [10]

H_CADON[0..15] [10]H_CADIN[0..15][10]

C1

10U_0805_10V4Z

10U_0805_10V4Z

1

2

C2

C2

10U_0805_10V4Z

10U_0805_10V4Z

1

VLDT CAP.

1

C3

C3

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

2

C4

C4

0.22U_0603_16V4Z

0.22U_0603_16V4Z

1

C5

C5

180P_0402_50V8J

180P_0402_50V8J

2

1

C6

C6

180P_0402_50V8J

180P_0402_50V8J

2

Near CPU Socket

+1.1VS

2 2

H_CADIP0

H_CADIN0

H_CADIP1

H_CADIN1

H_CADIP2

H_CADIN2

H_CADIP3

H_CADIN3

H_CADIP4

H_CADIN4

H_CADIP5

H_CADIN5

H_CADIP6

H_CADIN6

H_CADIP7

H_CADIN7

H_CADIP8

H_CADIN8

H_CADIP9

H_CADIN9

H_CADIP10

H_CADIN10

H_CADIP11

H_CADIN11

H_CADIP12

H_CADIN12

3 3

H_CLKIP0[10]

H_CLKIN0[10]

H_CLKIP1[10]

H_CLKIN1[10]

H_CTLIP0[10]

H_CTLIP1[10] H_CTLOP1 [10]

H_CTLIN1[10]

H_CADIP13

H_CADIN13

H_CADIP14

H_CADIN14

H_CADIP15

H_CADIN15

JCPU1A

JCPU1A

TBD

D1

VLDT_A0

D2

VLDT_A1

D3

VLDT_A2

D4

VLDT_A3

E3

L0_CADIN_H0

E2

L0_CADIN_L0

E1

L0_CADIN_H1

F1

L0_CADIN_L1

G3

L0_CADIN_H2

G2

L0_CADIN_L2

G1

L0_CADIN_H3

H1

L0_CADIN_L3

J1

L0_CADIN_H4

K1

L0_CADIN_L4

L3

L0_CADIN_H5

L2

L0_CADIN_L5

L1

L0_CADIN_H6

M1

L0_CADIN_L6

N3

L0_CADIN_H7

N2

L0_CADIN_L7

E5

L0_CADIN_H8

F5

L0_CADIN_L8

F3

L0_CADIN_H9

F4

L0_CADIN_L9

G5

L0_CADIN_H10

H5

L0_CADIN_L10

H3

L0_CADIN_H11

H4

L0_CADIN_L11

K3

L0_CADIN_H12

K4

L0_CADIN_L12

L5

L0_CADIN_H13

M5

L0_CADIN_L13

M3

L0_CADIN_H14

M4

L0_CADIN_L14

N5

L0_CADIN_H15

P5

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

ME@

ME@

HT LINK

HT LINK

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

+1.1VS

H_CADOP0

H_CADON0

H_CADOP1

H_CADON1

H_CADOP2

H_CADON2

H_CADOP3

H_CADON3

H_CADOP4

H_CADON4

H_CADOP5

H_CADON5

H_CADOP6

H_CADON6

H_CADOP7

H_CADON7

H_CADOP8

H_CADON8

H_CADOP9

H_CADON9

H_CADOP10

H_CADON10

H_CADOP11

H_CADON11

H_CADOP12

H_CADON12

H_CADOP13

H_CADON13

H_CADOP14

H_CADON14

H_CADOP15

H_CADON15

C7

C7

12

10U_0805_10V4Z

10U_0805_10V4Z

H_CLKOP0 [10]

H_CLKON0 [10]

H_CLKOP1 [10]

H_CLKON1 [10]

H_CTLOP0 [10]

H_CTLON0 [10]H_CTLIN0[10]

H_CTLON1 [10]

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2010/03/12

2008/10/06 2010/03/12

2008/10/06 2010/03/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

AMD CPU S1G4 HT I/F

AMD CPU S1G4 HT I/F

AMD CPU S1G4 HT I/F

NAWE6 LA-5754P

NAWE6 LA-5754P

NAWE6 LA-5754P

E

0.2

0.2

0.2

of

of

of

447Monday, March 01, 2010

447Monday, March 01, 2010

447Monday, March 01, 2010

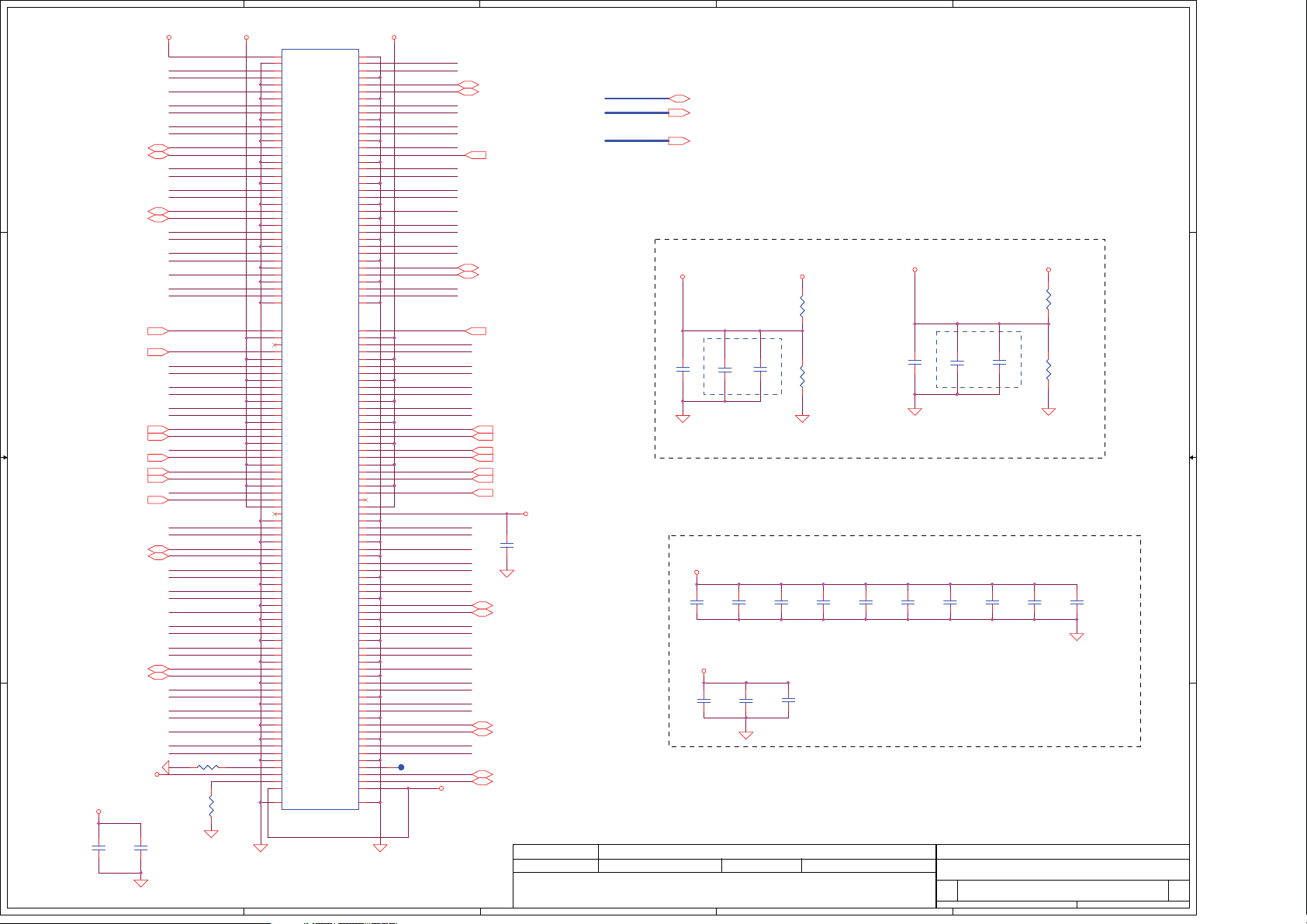

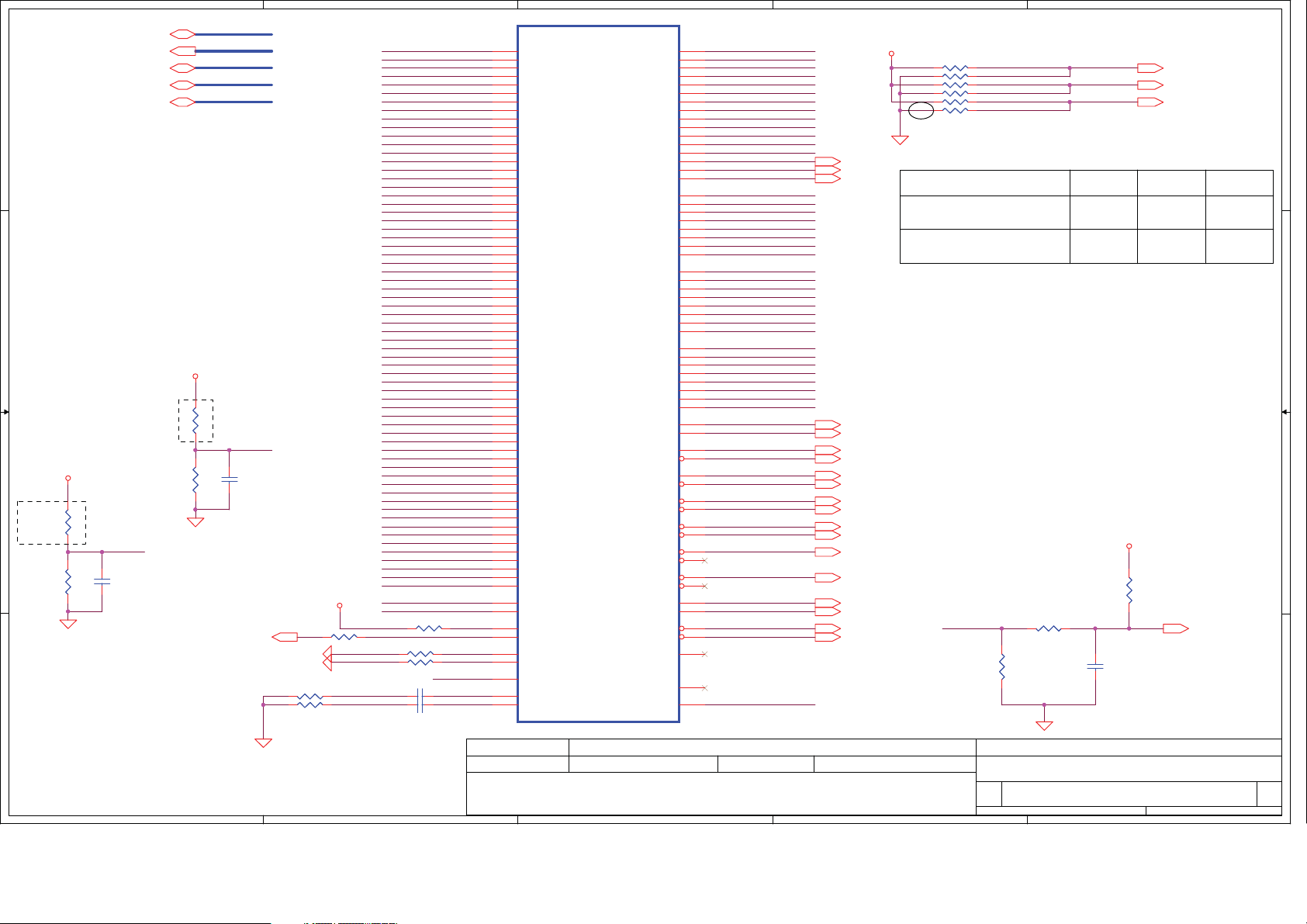

A

B

C

D

E

Processor DDR3 Memory Interface

JCPU1C

DDRB_SDQ[63..0][9]

1 1

2 2

0_0402_5%

0_0402_5%

10U_0805_10V4Z

10U_0805_10V4Z

3 3

4 4

+1.5V

R1

R1

1K_0402_1%

1K_0402_1%

1 2

R2

R2

1K_0402_1%

1K_0402_1%

1 2

+1.5V

R368

R368

1 2

2

C588

C588

1

@

@

DDRA_SMA[15..0][8] DDRB_SMA[15..0] [9]

MEM_VREF

1

1

2

MEM_MA_RST#[8 ]

DDRA_ODT0[8]

DDRA_ODT1[8]

DDRA_SCS0#[8]

DDRA_SCS1#[8] DDRB_SCS0# [9]

DDRA_CKE0[8]

DDRA_CKE1[8]

DDRA_CLK0[8]

DDRA_CLK0#[8]

DDRA_CLK1[8]

DDRA_CLK1#[8]

DDRA_SBS0#[8]

DDRA_SBS1#[8]

DDRA_SBS2#[8]

DDRA_SRAS#[8]

DDRA_SCAS#[8]

DDRA_SWE#[8]

C9

0.01U_0402_25V7KC90.01U_0402_25V7K

C8

C8

2

1000P_0402_50V7K

1000P_0402_50V7K

JCPU1B

Place them

close to CPU

within 1"

R4 39.2_0402_1%R4 39.2_0402_1%

1 2

1 2

R5 39.2_0402_1%R5 39.2_0402_1%

DDRA_SCS0#

DDRA_SCS1# DDRB_SCS0#

DDRA_CKE0

DDRA_CKE1

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

DDRA_CLK1#

MEM_MA_RST#

DDRA_ODT0

DDRA_ODT1

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SMA13

DDRA_SMA14

DDRA_SMA15

DDRA_SBS0#

DDRA_SBS1#

DDRA_SBS2#

DDRA_SRAS#

DDRA_SCAS#

DDRA_SWE#

MEMZP

MEMZN

JCPU1B

1.5A

D10

VDDR1

C10

VDDR2

B10

VDDR3

AD10

VDDR4

AF10

MEMZP

AE10

MEMZN

H16

MA_RESET_L

T19

MA0_ODT0

V22

MA0_ODT1

U21

MA1_ODT0

V19

MA1_ODT1

T20

MA0_CS_L0

U19

MA0_CS_L1

U20

MA1_CS_L0

V20

MA1_CS_L1

J22

MA_CKE0

J20

MA_CKE1

N19

MA_CLK_H5

N20

MA_CLK_L5

E16

MA_CLK_H1

F16

MA_CLK_L1

Y16

MA_CLK_H7

AA16

MA_CLK_L7

P19

MA_CLK_H4

P20

MA_CLK_L4

N21

MA_ADD0

M20

MA_ADD1

N22

MA_ADD2

M19

MA_ADD3

M22

MA_ADD4

L20

MA_ADD5

M24

MA_ADD6

L21

MA_ADD7

L19

MA_ADD8

K22

MA_ADD9

R21

MA_ADD10

L22

MA_ADD11

K20

MA_ADD12

V24

MA_ADD13

K24

MA_ADD14

K19

MA_ADD15

R20

MA_BANK0

R23

MA_BANK1

J21

MA_BANK2

R19

MA_RAS_L

T22

MA_CAS_L

T24

MA_WE_L

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

ME@

ME@

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

VDDR_SENSE

MEMVREF

MB_RESET_L

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

VDDR5

VDDR6

VDDR7

VDDR8

VDDR9

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

+CPU_VDDR+CPU_VDDR

FOR DDR3 1066, VDDR is 0.9V

FOR DDR3 1333, VDDR it should be 1.05V

VTT_SENSE

MEM_VREF

MEM_MB_RST#

DDRB_ODT0

DDRB_ODT1

DDRB_SCS1#

DDRB_CKE0

DDRB_CKE1

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#

DDRB_SMA0

DDRB_SMA1

DDRB_SMA2

DDRB_SMA3

DDRB_SMA4

DDRB_SMA5

DDRB_SMA6

DDRB_SMA7

DDRB_SMA8

DDRB_SMA9

DDRB_SMA10

DDRB_SMA11

DDRB_SMA12

DDRB_SMA13

DDRB_SMA14

DDRB_SMA15

DDRB_SBS0#

DDRB_SBS1#

DDRB_SBS2#

DDRB_SRAS#

DDRB_SCAS#

DDRB_SWE#

T1PAD T1PAD

MEM_MB_RST# [9]

DDRB_ODT0 [9]

DDRB_ODT1 [9]

DDRB_SCS1# [9]

DDRB_CKE0 [9]

DDRB_CKE1 [9]

DDRB_CLK0 [9]

DDRB_CLK0# [9]

DDRB_CLK1 [9]

DDRB_CLK1# [9]

DDRB_SBS0# [9]

DDRB_SBS1# [9]

DDRB_SBS2# [9]

DDRB_SRAS# [9]

DDRB_SCAS# [9]

DDRB_SWE# [9]

DDRB_SDM[7..0][9] DDRA_SDM[7..0] [8]

DDRB_SDQS0[9]

DDRB_SDQS0#[9]

DDRB_SDQS1[9]

DDRB_SDQS1#[9]

DDRB_SDQS2[9]

DDRB_SDQS2#[9]

DDRB_SDQS3[9]

DDRB_SDQS3#[9]

DDRB_SDQS4[9]

DDRB_SDQS4#[9]

DDRB_SDQS5[9]

DDRB_SDQS5#[9]

DDRB_SDQS6[9]

DDRB_SDQS6#[9]

DDRB_SDQS7[9]

DDRB_SDQS7#[9]

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQ26

DDRB_SDQ27

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQ30

DDRB_SDQ31

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ52

DDRB_SDQ53

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDQ58

DDRB_SDQ59

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

DDRB_SDM0

DDRB_SDM1

DDRB_SDM2

DDRB_SDM3

DDRB_SDM4

DDRB_SDM5

DDRB_SDM6

DDRB_SDM7

DDRB_SDQS0

DDRB_SDQS0#

DDRB_SDQS1

DDRB_SDQS1#

DDRB_SDQS2

DDRB_SDQS2#

DDRB_SDQS3

DDRB_SDQS3#

DDRB_SDQS4

DDRB_SDQS4#

DDRB_SDQS5

DDRB_SDQS5#

DDRB_SDQS6

DDRB_SDQS6#

DDRB_SDQS7

DDRB_SDQS7#

JCPU1C

MEM:DATA

C11

MB_DATA0

A11

MB_DATA1

A14

MB_DATA2

B14

MB_DATA3

G11

MB_DATA4

E11

MB_DATA5

D12

MB_DATA6

A13

MB_DATA7

A15

MB_DATA8

A16

MB_DATA9

A19

MB_DATA10

A20

MB_DATA11

C14

MB_DATA12

D14

MB_DATA13

C18

MB_DATA14

D18

MB_DATA15

D20

MB_DATA16

A21

MB_DATA17

D24

MB_DATA18

C25

MB_DATA19

B20

MB_DATA20

C20

MB_DATA21

B24

MB_DATA22

C24

MB_DATA23

E23

MB_DATA24

E24

MB_DATA25

G25

MB_DATA26

G26

MB_DATA27

C26

MB_DATA28

D26

MB_DATA29

G23

MB_DATA30

G24

MB_DATA31

AA24

MB_DATA32

AA23

MB_DATA33

AD24

MB_DATA34

AE24

MB_DATA35

AA26

MB_DATA36

AA25

MB_DATA37

AD26

MB_DATA38

AE25

MB_DATA39

AC22

MB_DATA40

AD22

MB_DATA41

AE20

MB_DATA42

AF20

MB_DATA43

AF24

MB_DATA44

AF23

MB_DATA45

AC20

MB_DATA46

AD20

MB_DATA47

AD18

MB_DATA48

AE18

MB_DATA49

AC14

MB_DATA50

AD14

MB_DATA51

AF19

MB_DATA52

AC18

MB_DATA53

AF16

MB_DATA54

AF15

MB_DATA55

AF13

MB_DATA56

AC12

MB_DATA57

AB11

MB_DATA58

Y11

MB_DATA59

AE14

MB_DATA60

AF14

MB_DATA61

AF11

MB_DATA62

AD11

MB_DATA63

A12

MB_DM0

B16

MB_DM1

A22

MB_DM2

E25

MB_DM3

AB26

MB_DM4

AE22

MB_DM5

AC16

MB_DM6

AD12

MB_DM7

C12

MB_DQS_H0

B12

MB_DQS_L0

D16

MB_DQS_H1

C16

MB_DQS_L1

A24

MB_DQS_H2

A23

MB_DQS_L2

F26

MB_DQS_H3

E26

MB_DQS_L3

AC25

MB_DQS_H4

AC26

MB_DQS_L4

AF21

MB_DQS_H5

AF22

MB_DQS_L5

AE16

MB_DQS_H6

AD16

MB_DQS_L6

AF12

MB_DQS_H7

AE12

MB_DQS_L7

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

ME@

ME@

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

DDRA_SDM0

DDRA_SDM1

DDRA_SDM2

DDRA_SDM3

DDRA_SDM4

DDRA_SDM5

DDRA_SDM6

DDRA_SDM7

DDRA_SDQS0

DDRA_SDQS0#

DDRA_SDQS1

DDRA_SDQS1#

DDRA_SDQS2

DDRA_SDQS2#

DDRA_SDQS3

DDRA_SDQS3#

DDRA_SDQS4

DDRA_SDQS4#

DDRA_SDQS5

DDRA_SDQS5#

DDRA_SDQS6

DDRA_SDQS6#

DDRA_SDQS7

DDRA_SDQS7#

DDRA_SDQ[63..0] [8]

DDRA_SDQS0 [8]

DDRA_SDQS0# [8]

DDRA_SDQS1 [8]

DDRA_SDQS1# [8]

DDRA_SDQS2 [8]

DDRA_SDQS2# [8]

DDRA_SDQS3 [8]

DDRA_SDQS3# [8]

DDRA_SDQS4 [8]

DDRA_SDQS4# [8]

DDRA_SDQS5 [8]

DDRA_SDQS5# [8]

DDRA_SDQS6 [8]

DDRA_SDQS6# [8]

DDRA_SDQS7 [8]

DDRA_SDQS7# [8]

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2010/03/12

2008/10/06 2010/03/12

2008/10/06 2010/03/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

AMD CPU S1G4 DDRII I/F

AMD CPU S1G4 DDRII I/F

AMD CPU S1G4 DDRII I/F

NAWE6 LA-5754P

NAWE6 LA-5754P

NAWE6 LA-5754P

547Monday, March 01, 2010

547Monday, March 01, 2010

547Monday, March 01, 2010

E

0.2

0.2

0.2

of

of

of

A

B

C

D

E

Champlain: C1E

C1E: LDT_REQ# no connect

CLMC: LDT_REQ# connect to NB

LDT_RES# / MEMHOT#

no support in S1g4

1K_0402_5%

1K_0402_5%

JCPU1D

JCPU1D

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

C6

LDTREQ_L

AF4

SIC

AF5

SID

AE6

ALERT_L

R6

HT_REF0

P6

HT_REF1

F6

VDD0_FB_H

E6

VDD0_FB_L

Y6

VDD1_FB_H

AB6

VDD1_FB_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

AD7

TEST23

H10

TEST18

G9

TEST19

E9

TEST25_H

E8

TEST25_L

AB8

TEST21

AF7

TEST20

AE7

TEST24

AE8

TEST22

AC8

TEST12

AF8

TEST27

C2

TEST9

AA6

TEST6

A3

RSVD1

A5

RSVD2

B3

RSVD3

B5

RSVD4

C1

RSVD5

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

ME@

ME@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

CPU_DBREQ#

CPU_TCK

CPU_TDI

CPU_TMS

CPU_TRST#

CPU_DBRDY

CPU_TDO

C

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

M11

VSS

W18

RSVD11

MEMHOT_L

THERMDC

THERMDA

DBREQ_L

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST10

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

CPU_SVC

A6

SVC

CPU_SVD

A4

SVD

AF6

AC7

AA8

THERMDC_CPU

W7

THERMDA_CPU

W8

VDDIO_FB_H

W9

VDDIO_FB_L

Y9

CPU_VDDNB_FB_H

H6

CPU_VDDNB_FB_L

G6

CPU_DBREQ#

E10

CPU_TDO

AE9

TDO

J7

H8

CPU_TEST17

D7

CPU_TEST16

E7

CPU_TEST15

F7

CPU_TEST14

C7

C3

TEST7

K8

C4

TEST8

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

H18

H19

AA7

D5

C5

+1.5V

R39300_0402_5%

R39300_0402_5%

R38220_0402_5%

R38220_0402_5%

R36220_0402_5%

R36220_0402_5%

R37220_0402_5%

R37220_0402_5%

12

12

12

12

@

@

@

@

@

@

@

@

2008/10/06 2010/03/12

2008/10/06 2010/03/12

2008/10/06 2010/03/12

CPU_SVC [47]

CPU_SVD [47]

CPU_THERMTRIP#_R

H_PROCHOT#

T3PAD T3PAD

R40300_0402_5% R40300_0402_5%

1 2

HDT_RST#

+1.5V

Compal Secret Data

Compal Secret Data

Compal Secret Data

CPU_VDDNB_FB_H [47]

CPU_VDDNB_FB_L [47]

R25 80.6_0402_1%R25 80.6_0402_1%

JP17

JP17

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

ACES_87212-12G0

ACES_87212-12G0

ME@

ME@

Deciphered Date

Deciphered Date

Deciphered Date

PROCHOT:

Input: For HTC Function

Output: Over Temperature Condition

T14PAD T14PAD

T16PAD T16PAD

T5PAD T5PAD

T6PAD T6PAD

T7PAD T7PAD

T8PAD T8PAD

GND

GND

12

13

14

+1.5V

D

CPU_THERMTRIP#_R

1 2

R11 300_0402_5%R11 300_0402_5%

H_PROCHOT#

HDT_RST#

VB

U2

U2

4

1 2

@

@

+1.1VS

EC_SMB_CK2

8

EC_SMB_DA2

7

6

5

SB_SID

EC_SMB_DA2

SB_SIC

EC_SMB_CK2

+2.5VDDA

3300P_0402_50V7K

3300P_0402_50V7K

1

C124.7U_0805_10V4Z C124.7U_0805_10V4Z

2

+1.5V

+1.5V

1 2

R12 1K_0402_5%R12 1K_0402_5%

1 2

R14 1K_0402_5%R14 1K_0402_5%

R15 44.2_0402_1%R15 44.2_0402_1%

R16 44.2_0402_1%R16 44.2_0402_1%

SB_SID [21]

SB_SIC [21]

B

1

1

C13

C13

2

2

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

1 2

1 2

CPU_VDD0_FB_H[47]

CPU_VDD0_FB_L[47]

CPU_VDD1_FB_H[47]

CPU_VDD1_FB_L[47]

EC_SMB_CK2 [14,31,34]

EC_SMB_DA2 [14,31,34]

VDDA=0.25A

C14

C14

0.22U_0603_16V4Z

0.22U_0603_16V4Z

LDT_RST#

H_PWRGD

LDT_STOP#

T2 PADT2 PAD

CPU_SIC

CPU_SID

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST21

CPU_TEST20

CPU_TEST24

CPU_TEST22

CPU_TEST12

CPU_TEST27

1 2

R24 0_0402_5%R24 0_0402_5%

T0 SB

TO EC

T0 SB

TO EC

CPU_HTREF0

CPU_HTREF1

CPU_TEST23

CPU_TEST18

CPU_TEST19

CPU_TEST25H

CPU_TEST25L

L1

+2.5VS

1 1

CLK_CPU_BCLK[19]

CLK_CPU_BCLK#[19]

+1.5VS

R17

R17

300_0402_5%

300_0402_5%

1 2

LDT_RST#[20]

2 2

H_PWRGD[20]

3 3

LDT_RST#

1

C17

C17

0.01U_0402_25V4Z

0.01U_0402_25V4Z

@

@

2

+1.5VS

+3VS

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C21 3300P_0402_50V7KC21 3300P_0402_50V7K

LDT_STOP#[11,20]

R21

R21

300_0402_5%

300_0402_5%

1 2

H_PWRGD

1

C19

C19

0.01U_0402_25V4Z

0.01U_0402_25V4Z

@

@

2

1

C20

C20

2

1 2

TI

TMP411ADGKR MSOP 8P

SA00002DE10

Address: 100 1100

THERMDA_CPU

THERMDC_CPU

CPU internal thermal sensor

1 2

R41

R41

@

@

+3VS

20K_0402_5%

20K_0402_5%

4 4

CPU_SID

CPU_SIC

C22 0.1U_0402_16V4Z@C22 0.1U_0402_16V4Z@

R42

@R42

@

12

34.8K_0402_1%

34.8K_0402_1%

G

G

2

13

D

S

D

S

Q2 FDV301N_NL_SOT23-3

Q2 FDV301N_NL_SOT23-3

@

@

G

G

2

13

D

S

D

S

Q3 FDV301N_NL_SOT23-3

Q3 FDV301N_NL_SOT23-3

@

@

A

12

EC_SMB_DA

EC_SMB_CK

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

1

+

+

C11

C11

150U_B_6.3VM_R40M

150U_B_6.3VM_R40M

2

1 2

C16

C16

1 2

C15 3900P_0402_50V7KC15 3900P_0402_50V7K

+1.5VS

1 2

LDT_STOP#

1

C18

C18

0.01U_0402_25V4Z

0.01U_0402_25V4Z

2

U1

U1

1

VDD

2

D+

3

D-

THERM#4GND

EMC1402-1-ACZL-TR-MSOP-8P

EMC1402-1-ACZL-TR-MSOP-8P

EMC1402-1

(SA00001Z700)

Address 100_1100b

S IC EMC1402-1-AC ZL-TR MSOP 8P SENSOR

VB

FDV301N, the Vgs is:

min = 0.65V

Typ = 0.85V

Max = 1.5V

2.09V for Gate

1 2

R44 0_0402_5%

R44 0_0402_5%

1 2

R45 0_0402_5%

R45 0_0402_5%

1 2

R46 0_0402_5%

R46 0_0402_5%

1 2

R47 0_0402_5%

R47 0_0402_5%

1 2

3900P_0402_50V7K

3900P_0402_50V7K

12

R10

R10

169_0402_1%

169_0402_1%

R18

R18

300_0402_5%

300_0402_5%

@

@

SCLK

SDATA

ALERT#

@

@

@

@

@

@

@

@

L1

+1.5V

12

R6

R6

10K_0402_5%

R7

R7

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

CPU_SVC

CPU_SVD

CPU_TEST25H

CPU_TEST25L

CPU_TEST27

CPU_TEST12

CPU_TEST18

CPU_TEST19

CPU_TEST20

CPU_TEST21

CPU_TEST22

CPU_TEST24

CPU_TEST23

R43

R43

+3VS

Y

10K_0402_5%

B

B

2

1 2

Q1

Q1

E

E

3 1

R22 510_0402_5%R22 510_0402_5%

R23 510_0402_5%@R23 510_0402_5%@

R26 510_0402_5%@R26 510_0402_5%@

R27 510_0402_5%R27 510_0402_5%

R28 1K_0402_5%R28 1K_0402_5%

1 2

C

C

R8 0_0402_5%R8 0_0402_5%

1 2

R9 0_0402_5%@R9 0_0402_5%@

1 2

R13 0_0402_5%R13 0_0402_5%

1 2

R71 0_0402_5%@R71 0_0402_5%@

1 2

R19 1K_0402_5%R19 1K_0402_5%

1 2

R20 1K_0402_5%R20 1K_0402_5%

1 2

1 2

1 2

1 2

1 2

H_THERMTRIP# [21]

MAINPWON [39,40,42]

H_PROCHOT_R# [20]

EC_PROCHOT# [34]

+1.5V

+1.5V

+1.5V

+1.5V

For SCAN connect use

1 2

R29 1K_0402_5%R29 1K_0402_5%

1 2

R30 1K_0402_5%R30 1K_0402_5%

1 2

R31 1K_0402_5%R31 1K_0402_5%

1 2

R32 1K_0402_5%R32 1K_0402_5%

1 2

R33 1K_0402_5%R33 1K_0402_5%

1 2

R34 1K_0402_5%R34 1K_0402_5%

1 2

R35 1K_0402_5%R35 1K_0402_5%

1 2

R265 1K_0402_5%R265 1K_0402_5%

0_0402_5%@

0_0402_5%@

5

2

P

B

1

A

G

NC7SZ08P5X_NL_SC70-5

NC7SZ08P5X_NL_SC70-5

3

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

LDT_RST#

SB_PWRGD [11,21,34]

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

AMD CPU S1G4 CTRL

AMD CPU S1G4 CTRL

AMD CPU S1G4 CTRL

NAWE6 LA-5754P

NAWE6 LA-5754P

NAWE6 LA-5754P

E

647Tuesday, March 02, 2010

647Tuesday, March 02, 2010

647Tuesday, March 02, 2010

0.2

0.2

0.2

of

of

of

A

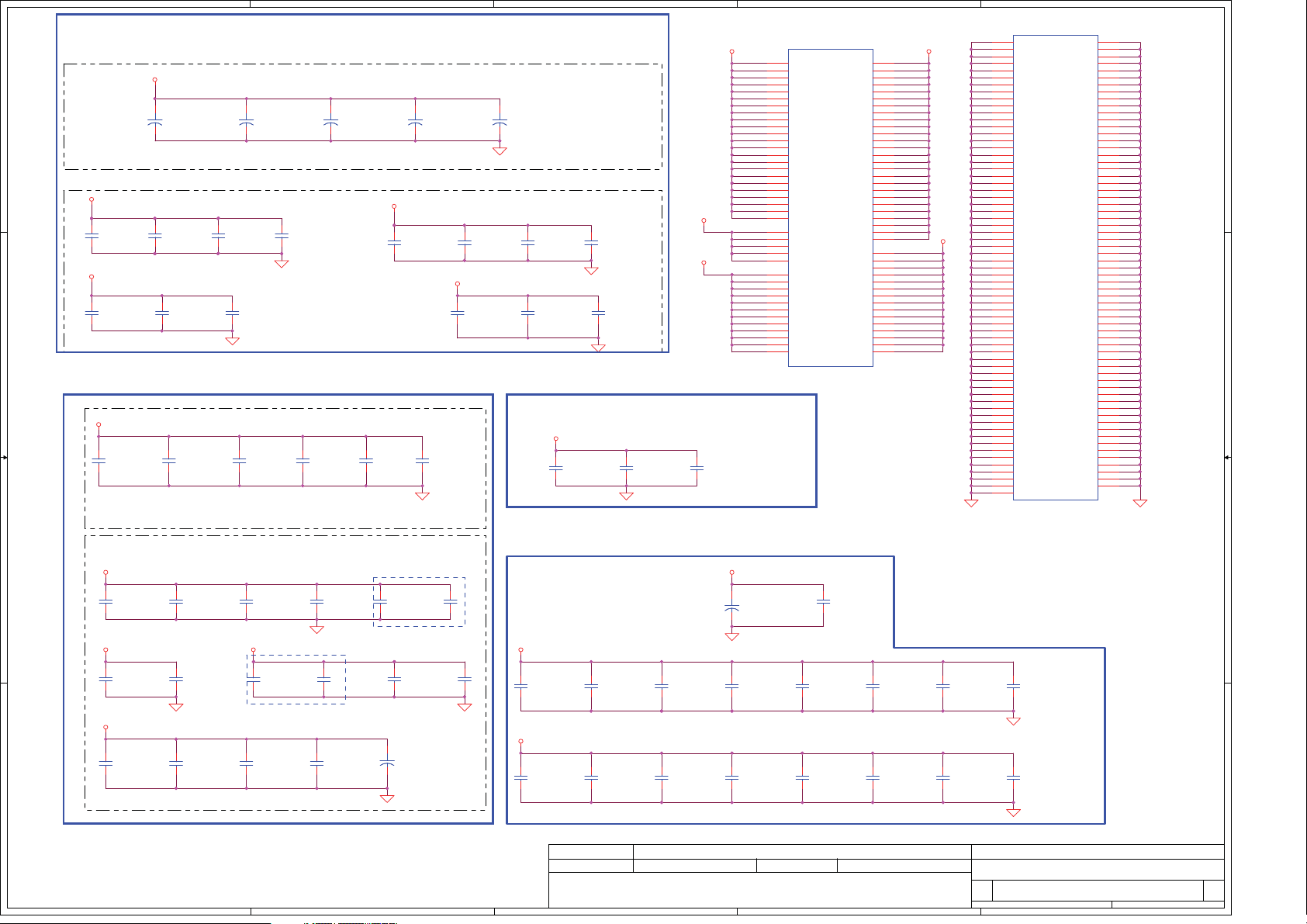

VDD(+CPU_CORE) decoupling.

+CPU_CORE

1

+

+

C23

1 1

C23

330U_X_2VM_R6M

330U_X_2VM_R6M

2

1

+

C24

@+C24

@

330U_X_2VM_R6M

330U_X_2VM_R6M

2

Near CPU Socket

+CPU_CORE

1

C28

C28

22U_0805_6.3V6M

22U_0805_6.3V6M

2

+CPU_CORE

1

C36

C36

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

2 2

1

C29

C29

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C37

C37

0.01U_0402_25V4Z

0.01U_0402_25V4Z

2

1

C30

C30

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C38

C38

180P_0402_50V8J

180P_0402_50V8J

2

1

C35

C35

22U_0805_6.3V6M

22U_0805_6.3V6M

2

Under CPU Socket

VDDIO decoupling.

+1.5V

1

C44

C44

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C45

C45

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C46

C46

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

Under CPU Socket

1

C47

C47

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

+

+

C25

C25

330U_X_2VM_R6M

330U_X_2VM_R6M

2

B

+CPU_CORE

1

C31

C31

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C48

C48

180P_0402_50V8J

180P_0402_50V8J

2

1

+

+

C26

C26

330U_X_2VM_R6M

330U_X_2VM_R6M

2

+CPU_CORE

1

C50

C50

180P_0402_50V8J

180P_0402_50V8J

2

1

C32

C32

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C39

C39

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

C

1

+

+

C27

C27

330U_X_2VM_R6M

330U_X_2VM_R6M

2

1

2

1

2

C33

C33

22U_0805_6.3V6M

22U_0805_6.3V6M

C40

C40

0.01U_0402_25V4Z

0.01U_0402_25V4Z

1

C34

C34

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C41

C41

180P_0402_50V8J

180P_0402_50V8J

2

+CPU_CORE

+CPU_CORE_NB

+1.5V

4A

G4

H2

J11

J13

J15

K6

K10

K12

K14

L11

L13

L15

M2

M6

M8

M10

N7

N9

N11

K16

M16

P16

T16

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

Athlon 64 S1

Processor Socket

+CPU_CORE_NB decoupling.

+CPU_CORE_NB

1

C42

C42

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C43

C43

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C49

C49

22U_0805_6.3V6M

22U_0805_6.3V6M

2

JCPU1E

JCPU1E

VDD0_1

VDD0_2

J9

VDD0_3

VDD0_4

VDD0_5

VDD0_6

VDD0_7

VDD0_8

VDD0_9

VDD0_10

L4

VDD0_11

L7

VDD0_12

L9

VDD0_13

VDD0_14

VDD0_15

VDD0_16

VDD0_17

VDD0_18

VDD0_19

VDD0_20

VDD0_21

VDD0_22

VDD0_23

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

ME@

ME@

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

D

JCPU1F

JCPU1F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

Athlon 64 S1

ME@

ME@

Processor Socket

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

36A

TBD

+CPU_CORE

+1.5V

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

E

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

3 3

4 4

+1.5V

1

C51

C51

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

+1.5V +1.5V

1

C64

C64

0.01U_0402_25V4Z

0.01U_0402_25V4Z

2

+1.5V

1

2

Between CPU Socket and DIMM

C71

C71

4.7U_0805_10V4Z

4.7U_0805_10V4Z

1

C52

C52

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C65

C65

0.01U_0402_25V4Z

0.01U_0402_25V4Z

2

1

C72

C72

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C53

C53

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

180PF Qt'y follow the distance between

CPU socket and DIMM0. <2.5inch>

2

C66

C66

0.1U_0402_16V7K

0.1U_0402_16V7K

1

1

C73

C73

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C54

C54

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

2

C67

C67

0.1U_0402_16V7K

0.1U_0402_16V7K

1

1

C74

C74

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C354

C354

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C68

C68

180P_0402_50V8J

180P_0402_50V8J

2

1

+

+

C75

C75

330U_X_2VM_R6M

330U_X_2VM_R6M

2

1

C355

C355

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C69

C69

180P_0402_50V8J

180P_0402_50V8J

2

VDDR decoupling.

+CPU_VDDR

1

C57

C57

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

+CPU_VDDR

1

C76

C76

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C58

C58

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C59

C59

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

Near CPU Socket Right side.

1

C77

C77

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C78

C78

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

+CPU_VDDR

Near Power Supply

1

+

+

C56

C56

150U_B_6.3VM_R40M

150U_B_6.3VM_R40M

2

1

C60

C60

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C79

C79

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C55

C55

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C61

C61

1000P_0402_50V7K

1000P_0402_50V7K

2

1

C80

C80

1000P_0402_50V7K

1000P_0402_50V7K

2

1

C62

C62

1000P_0402_50V7K

1000P_0402_50V7K

2

1

C81

C81

1000P_0402_50V7K

1000P_0402_50V7K

2

1

C63

C63

180P_0402_50V8J

180P_0402_50V8J

2

1

C82

C82

180P_0402_50V8J

180P_0402_50V8J

2

1

C70

C70

180P_0402_50V8J

180P_0402_50V8J

2

1

C83

C83

180P_0402_50V8J

180P_0402_50V8J

2

Near CPU Socket Left side.

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/10/06 2010/03/12

2008/10/06 2010/03/12

2008/10/06 2010/03/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

AMD CPU S1G4 PWR & GND

AMD CPU S1G4 PWR & GND

AMD CPU S1G4 PWR & GND

NAWE6 LA-5754P

NAWE6 LA-5754P

NAWE6 LA-5754P

E

of

of

of

747Monday, March 01, 2010

747Monday, March 01, 2010

747Monday, March 01, 2010

0.2

0.2

0.2

A

B

C

D

E

DQ4

DQ5

VSS3

DQ6

DQ7

DM1

DM2

CK1

CK1#

BA1

NC2

DM4

DM6

SDA

SCL

VTT2

+1.5V

2

DDRA_SDQ4

4

DDRA_SDQ5

6

8

DDRA_SDQS0#

10

DDRA_SDQS0

12

14

DDRA_SDQ6

16

DDRA_SDQ7

18

20

DDRA_SDQ12

22

DDRA_SDQ13

24

26

DDRA_SDM1

28

MEM_MA_RST#

30

32

DDRA_SDQ14

34

DDRA_SDQ15

36

38

DDRA_SDQ20

40

DDRA_SDQ21

42

44

DDRA_SDM2

46

48

DDRA_SDQ22

50

DDRA_SDQ23

52

54

DDRA_SDQ28

56

DDRA_SDQ29

58

60

DDRA_SDQS3#

62

DDRA_SDQS3

64

66

DDRA_SDQ30

68

DDRA_SDQ31

70

72

DDRA_CKE1

74

76

DDRA_SMA15

78

A15

A14

A11

A7

A6

A4

A2

A0

S0#

G2

B

DDRA_SMA14

80

82

DDRA_SMA11

84

DDRA_SMA7

86

88

DDRA_SMA6

90

DDRA_SMA4

92

94

DDRA_SMA2

96

DDRA_SMA0

98

100

DDRA_CLK1

102

DDRA_CLK1#

104

106

DDRA_SBS1#

108

DDRA_SRAS#

110

112

DDRA_SCS0#

114

116

118

DDRA_ODT1

120

122

124

126

128

DDRA_SDQ36

130

DDRA_SDQ37

132

134

DDRA_SDM4

136

138

DDRA_SDQ38

140

DDRA_SDQ39

142

144

DDRA_SDQ44

146

DDRA_SDQ45

148

150

DDRA_SDQS5#

152

DDRA_SDQS5

154

156

DDRA_SDQ46

158

DDRA_SDQ47

160

162

DDRA_SDQ52

164

DDRA_SDQ53

166

168

DDRA_SDM6

170

172

DDRA_SDQ54

174

DDRA_SDQ55

176

178

DDRA_SDQ60

180

DDRA_SDQ61

182

184

DDRA_SDQS7#

186

DDRA_SDQS7

188

190

DDRA_SDQ62

192

DDRA_SDQ63

194

196

198

200

202

204

206

T10PAD T10PAD

+0.75VS

DDRA_SDQS0# [5]

DDRA_SDQS0 [5]

MEM_MA_RST# [5]

DDRA_SDQS3# [5]

DDRA_SDQS3 [5]

DDRA_CKE1 [5]

DDRA_CLK1 [5]

DDRA_CLK1# [5]

DDRA_SBS1# [5]

DDRA_SRAS# [5]

DDRA_SCS0# [5]

DDRA_ODT1 [5]

+VREF_CA

1

C89

C89

1000P_0402_50V7K

1000P_0402_50V7K

2

DDRA_SDQS5# [5]

DDRA_SDQS5 [5]

DDRA_SDQS7# [5]

DDRA_SDQS7 [5]

SB_SMDAT0 [9,19,21,28]

SB_SMCLK0 [9,19,21,28]

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DDRA_SDQ[0..63]

DDRA_SDM[0..7]

DDRA_SMA[0..15]

2008/10/06 2010/03/12

2008/10/06 2010/03/12

2008/10/06 2010/03/12

C

+VREF_DQ

1

2

4.7U_0805_10V4Z

4.7U_0805_10V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDRA_SDQ[0..63] [5]

DDRA_SDM[0..7] [5]

DDRA_SMA[0..15] [5]

+VREF_DQ

0.01U_0402_25V7K

0.01U_0402_25V7K

2

C85

C85

C84

C84

@

@

1

+1.5V

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

2

C87

C87

1

1

+0.75VS

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

2

C830

C830

1

1

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

1

C10

C10

2

1000P_0402_50V7K

1000P_0402_50V7K

C840

C840

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C835

C835

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

2

1

+1.5V

R48

R48

1K_0402_1%

1K_0402_1%

1 2

R49

R49

1K_0402_1%

1K_0402_1%

1 2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C88

C88

1

C961

C961

2

2

C839

C839

1

D

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C836

C836

1

1

C235

C235

@

@

2

4.7U_0805_10V4Z

4.7U_0805_10V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C833

C833

1

+1.5V+VREF_CA

R310

R310

1K_0402_1%

1K_0402_1%

C838

C838

2

C837

C837

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1 2

R315

R315

1K_0402_1%

1K_0402_1%

1 2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C834

C834

2

C832

C832

1

+VREF_CA

0.01U_0402_25V7K

0.01U_0402_25V7K

2

C485

C485

1

2

C831

C831

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

1000P_0402_50V7K

1000P_0402_50V7K

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

Place near DIMM1

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

DDRII SO-DIMM 1

DDRII SO-DIMM 1

DDRII SO-DIMM 1

NAWE6 LA-5754P

NAWE6 LA-5754P

NAWE6 LA-5754P

E

of

of

of

847Monday, March 01, 2010

847Monday, March 01, 2010

847Monday, March 01, 2010

0.2

0.2

0.2

+VREF_DQ

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDM0

DDRA_SDQ2

1 1

DDRA_SDQS1#[5]

DDRA_SDQS1[5]

DDRA_SDQS2#[5]

DDRA_SDQS2[5]

DDRA_CKE0[5]

2 2

3 3

4 4

2.2U_0603_6.3V4Z

2.2U_0603_6.3V4Z

DDRA_SBS2#[5]

DDRA_CLK0[5]

DDRA_CLK0#[5]

DDRA_SBS0#[5]

DDRA_SWE#[5]

DDRA_SCAS#[5] DDRA_ODT0 [5]

DDRA_SCS1#[5]

DDRA_SDQS4#[5]

DDRA_SDQS4[5]

DDRA_SDQS6#[5]

DDRA_SDQS6[5]

+3VS

1

C90

C90

C91

C91

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

DDRA_SDQ3

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQS1#

DDRA_SDQS1

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQS2#

DDRA_SDQS2

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDM3

DDRA_SDQ26

DDRA_SDQ27

DDRA_CKE0

DDRA_SBS2#

DDRA_SMA12

DDRA_SMA9

DDRA_SMA8

DDRA_SMA5

DDRA_SMA3

DDRA_SMA1

DDRA_CLK0

DDRA_CLK0#

DDRA_SMA10

DDRA_SBS0#

DDRA_SWE#

DDRA_SCAS# DDRA_ODT0

DDRA_SMA13

DDRA_SCS1#

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQS4#

DDRA_SDQS4

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDM5

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQS6#

DDRA_SDQS6

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDM7

DDRA_SDQ58

DDRA_SDQ59

R50 10K_0402_5%

R50 10K_0402_5%

+3VS

1

2

1 2

R51

+1.5V

JDIMM1

JDIMM1

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

12

R51

10K_0402_5%

10K_0402_5%

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

99

VDD9

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

FOX_AS0A626-U4RN-7F

FOX_AS0A626-U4RN-7F

ME@

ME@

DQS#0

DQS0

VSS6

VSS8

DQ12

DQ13

VSS10

DQ14

DQ15

DQ20

DQ21

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

DIMM_A Rervse H:4mm

<Address: 00>

A

A

B

C

D

E

DQ4

DQ5

VSS3

DQ6

DQ7

DM1

DM2

CK1

CK1#

BA1

NC2

DM4

DM6

SDA

SCL

VTT2

+1.5V+1.5V

2

DDRB_SDQ4

4

DDRB_SDQ5

6

8

DDRB_SDQS0#

10

DDRB_SDQS0

12

14

DDRB_SDQ6

16

DDRB_SDQ7

18

20

DDRB_SDQ12

22

DDRB_SDQ13

24

26

DDRB_SDM1

28

MEM_MB_RST#

30

32

DDRB_SDQ14

34

DDRB_SDQ15

36

38

DDRB_SDQ20

40

DDRB_SDQ21

42

44

DDRB_SDM2

46

48

DDRB_SDQ22

50

DDRB_SDQ23

52

54

DDRB_SDQ28

56

DDRB_SDQ29

58

60

DDRB_SDQS3#

62

DDRB_SDQS3

64

66

DDRB_SDQ30

68

DDRB_SDQ31

70

72

DDRB_CKE1

74

76

DDRB_SMA15

78

A15

A14

A11

A7

A6

A4

A2

A0

S0#

G2

DDRB_SMA14

80

82

DDRB_SMA11

84

DDRB_SMA7

86

88

DDRB_SMA6

90

DDRB_SMA4

92

94

DDRB_SMA2

96

DDRB_SMA0

98

100

DDRB_CLK1

102

DDRB_CLK1#

104

106

DDRB_SBS1#

108

DDRB_SRAS#

110

112

DDRB_SCS0#

114

DDRB_ODT0DDRB_SCAS#

116

118

DDRB_ODT1

120

122

124

126

128

DDRB_SDQ36

130

DDRB_SDQ37

132

134

DDRB_SDM4

136

138

DDRB_SDQ38

140

DDRB_SDQ39

142

144

DDRB_SDQ44

146

DDRB_SDQ45

148

150

DDRB_SDQS5#

152

DDRB_SDQS5

154

156

DDRB_SDQ46

158

DDRB_SDQ47

160

162

DDRB_SDQ52

164

DDRB_SDQ53

166

168

DDRB_SDM6

170

172

DDRB_SDQ54

174

DDRB_SDQ55

176

178

DDRB_SDQ60

180

DDRB_SDQ61

182

184

DDRB_SDQS7#

186

DDRB_SDQS7

188

190

DDRB_SDQ62

192

DDRB_SDQ63

194

196