5

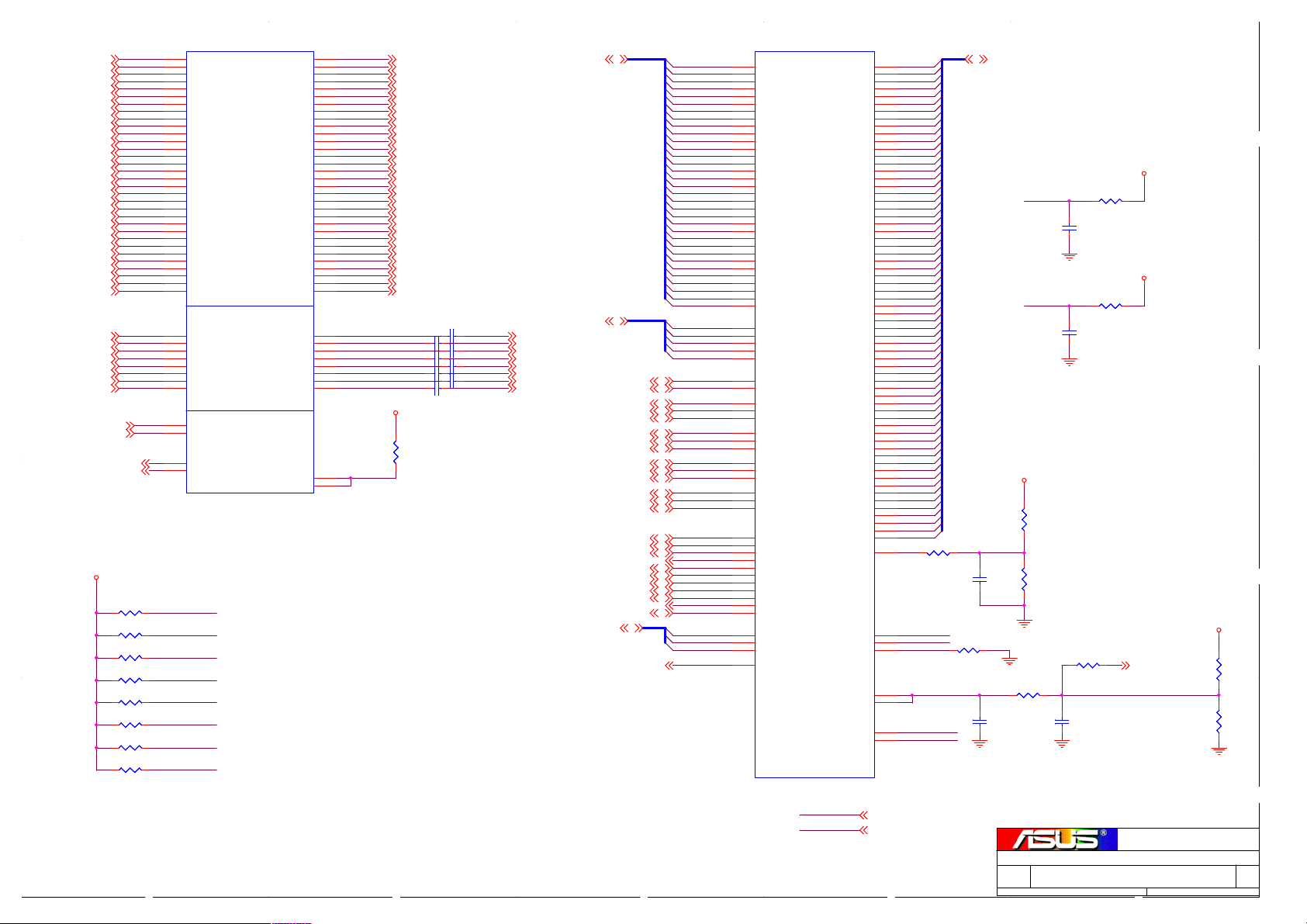

P5KPL-VM/SI

4

3

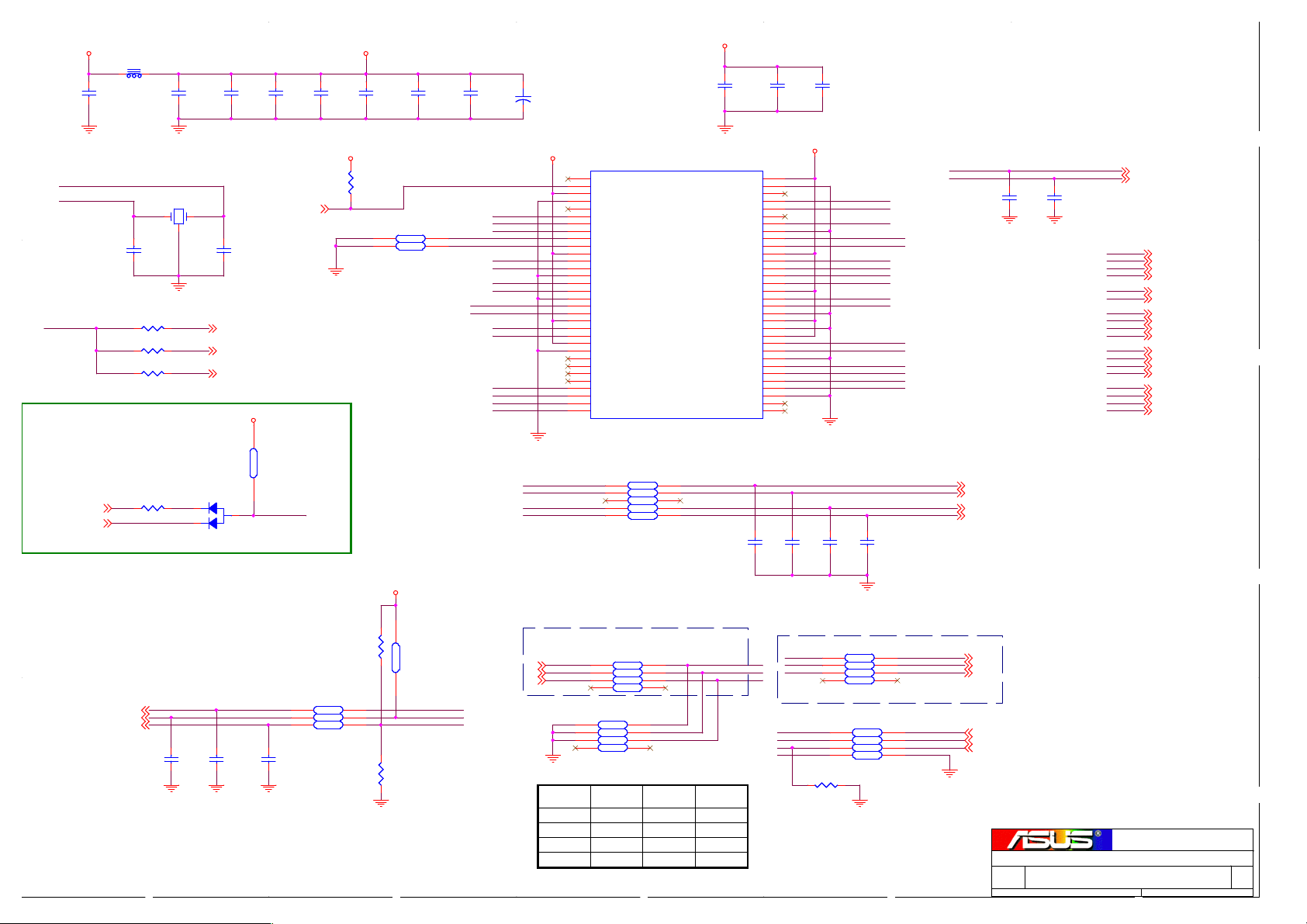

01.BLOCK DIAGRAM

TITLE

2

1

VERSION

1.00G

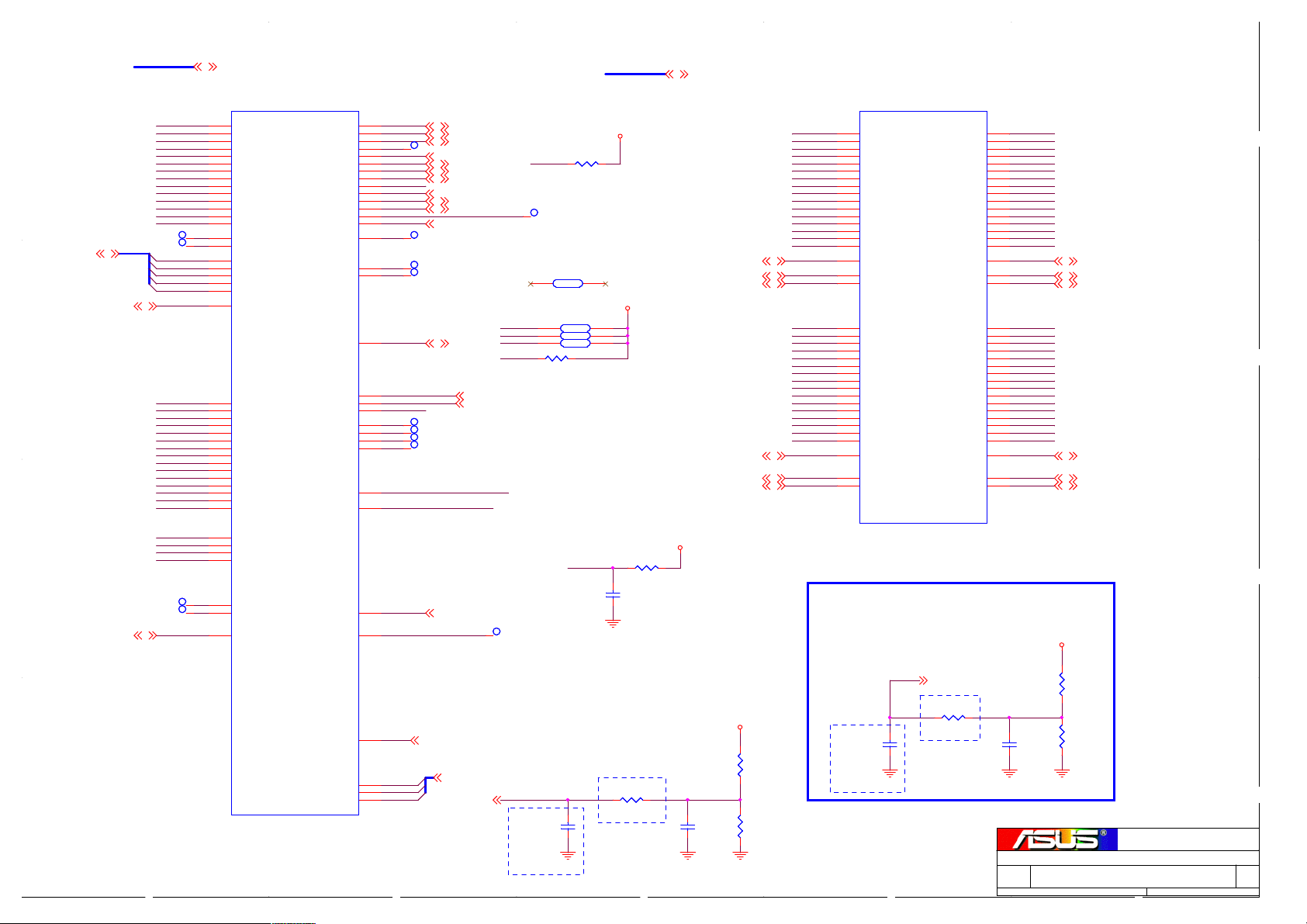

02.NAMING RULE

03.POWER SEQUENCE

04.POWER FLOW

05.CLOCK DIAGRAM

D D

Intel LGA775

Pentium 4(90/65nm)

R4.01G

2007/7/15

3.8GHz + CPU

06.CPU TIMING

07.CLOCK GEN

08.LGA775-1

09.LGA775-2

10.LGA775-3

11.LGA775-4

FSB 800/1066/1333MHz

DDR2 x 1

DDR2 x 1

12.LGA775-5

13.BROADWATER-1

14.BROADWATER-2

1.00G

15.BROADWATER-3

16.BROADWATER-4

Intel G31

VGA

C C

PCI-EX x 16

VGA

MCH

Bearlake

(North Bridge)

Channel A

DDR2 667/800

Non-ECC

DDR2 DIMM B1

DDR2 DIMM A1

Channel B

PCI-EX x16 Slot

PCI-EX x1 Slot

LAN

8ch

Audio

ATHEROS

REALTEK

ALC662

B B

PCI-EX x 1

PCI-EX x 1

Azalia

DMI BUS

Intel

ICH7

(Sourth Bridge)

SATA

IDE

USB

USB

SATA1

SATA2

SATA3

SATA4

IDE X1

USB2.0

8 ports

WIFI

4 x SATA150,300

ports

/X

17.BROADWATER-5

18.BROADWATER-6

19.DDR2 A

20.DDR2 B

21.DDR TERM RES

22.ASM4131

23.PCI-E X16

24.VGA

25.ICH7-1

26.ICH7-2

27.ICH7-3

28.ICH7-4

29.PCI-E X1

30.PCI SLOT 1 2

31.AUDIO-ALC888T

32.AZA CONNECTOR

33.IDE AND SATA

34.SIO W83627DHG-A

35.I/O CONNECTOR

36.SPI, TPM

37.FAN CONTROL

38.LAN ATTANSIC

39.USB PORT,WIFI

40.FRONT PANEL

1.00G

1.00G

1.00G

1.00G

1.00G

41.VCORE CONTROLLER

42.VCORE DRIVER

43.+1.8VDUAL&VTTDDR

44.+3VSB&+5V_DUAL&+3V_DUAL

SPI

BIOS Flash

ROM (SPI)

45.+1.25V_MCH&+1.5V&+1.05V

46.VTT_CPU

47.LAN_2.5V&LAN_1.5V

A A

LPC BUS

W83627DHG-A

SUPER I/O

1 x Parallel

1 x Floppy

1 x Serial

KB & MS

PCI Slot1

PCI Slot2

5

PCI BUS 33MHz

4

3

48.EMI

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

Date: Sheet

Date: Sheet

Date: Sheet

,

,

2

,

16, 2007

16, 2007

16, 2007

1.00G

1.00G

1.00G

1.00G

1.00G

Title :

Title :

Title :

Engin eer:

Engin eer:

Engin eer:

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Kimi_wang

Kimi_wang

Kimi_wang

1

of

of

of

1 49

1 49

1 49

Rev

Rev

Rev

4.01G

4.01G

4.01G

5

Reference Naming Rule

4

3

2

1

A

Audio DDR2

D D

H

CPU

Q

X1

PCI-E X1

C C

Net Naming Rules

B

I

IDE

R

RAID

Y

TPM

CK

Clock

J

S

SB

Z

ITP

D

DMI

K

T

SATA

SPI

D1

DDR1

L

LAN

U

USB 2.0

D2

M

VGA

E

EMI

N

NB

W

H/W Monitor

F

O

Super I/O

X16

PCI-E X16

G

P

PCI

X4V

PCI-E X4

1.When a net passes a resistor, add R_ to net name to identify the shorter route.

2.When a net passes a capacitor, add C_ to net name to identify the shorter route.

3.Use function as a net main name. If there're inflictions, please add _(destination) to identify.

(e.g. R_CK_33M_PCI1, C_EXP16_TXP0, RESETCON#_SIO)

Jumper Naming Rule refer to Version 2.0.

B B

A A

Naming Rule

Naming Rule

Naming Rule

Title :

Title :

Title :

Engin eer:

Engin eer:

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

16, 2007

16, 2007

16, 2007

Engin eer:

Kimi_wang

Kimi_wang

Kimi_wang

of

of

of

2 49

2 49

2 49

Rev

Rev

Rev

4.01G

4.01G

4.01G

5

4

10

3

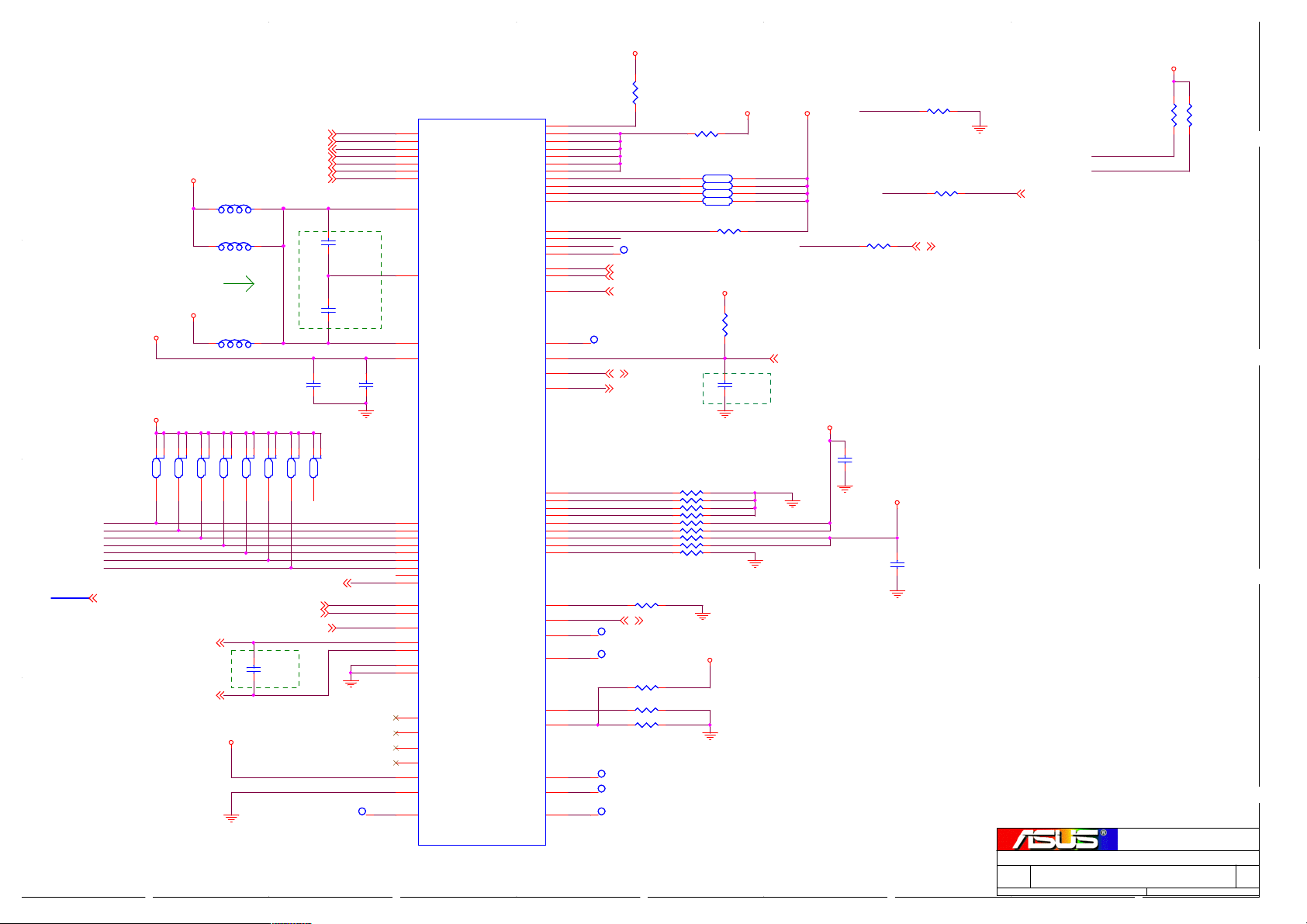

2

1

D D

13

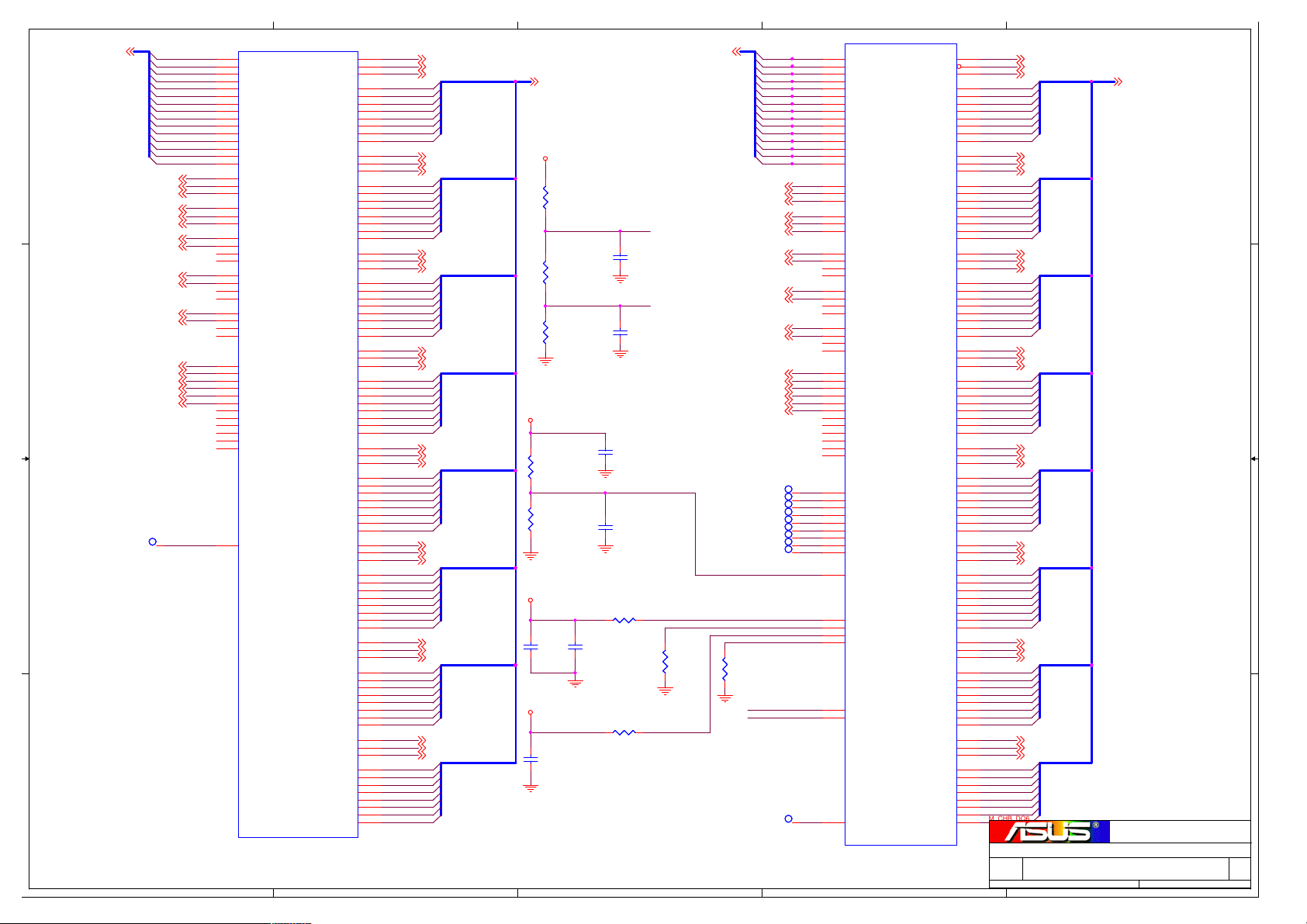

Intel 82946GZ

MCH

Bearlake

(North Bridge)

Power

MCH_PWRO K

8

Supply

IDE

PCI-EX x16

PWROK_NB

Press

10

Ctrl + Alt + Del

SUPER I/O

PWRBTN#

C C

Press

Power

3

W83627DHG-A

Button

2

4

RSMRST#

RST_KB

PSON#

7

Buffer out

SLP_S4#

5

PWROK_PS

11

11

11

7

8

PWROK_SB

IDE_RST#

PCIRST#_PCIEX16

PCIRST#_PCIEX1

+3.3V

0OHM

CLOCK GEN

WIFI

PCI-EX x1

6

SLP_S3#

IO_PWRBTN#

5

PCI Slot

Press

Reset

RSTCON#

Button

B B

13

9

Clear

CMOS

1

RTCRST#

Intel 82801G

ICH7

(Sourth Bridge)

10

10

S_PLTRST#

PCI_RST#

10

10

CPURST#

CPUPWRGD

Intel LGA775

Pentium 4 (90/65nm)

LAN

ATHEROS

HINIT#

10

3.8GHz + CPU

A A

Vcore

VCORE_PG

Controller

Pow er Sequence

Pow er Sequence

Pow er Sequence

Title :

Title :

Title :

Engin eer:

Engin eer:

ASUSTeK COMPUTER INC

ASUSTeK COMPUTER INC

ASUSTeK COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

16, 2007

,

16, 2007

,

16, 2007

Engin eer:

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

Kimi_wang

Kimi_wang

Kimi_wang

3 49

3 49

3 49

of

of

of

Rev

Rev

Rev

4.01G

4.01G

4.01G

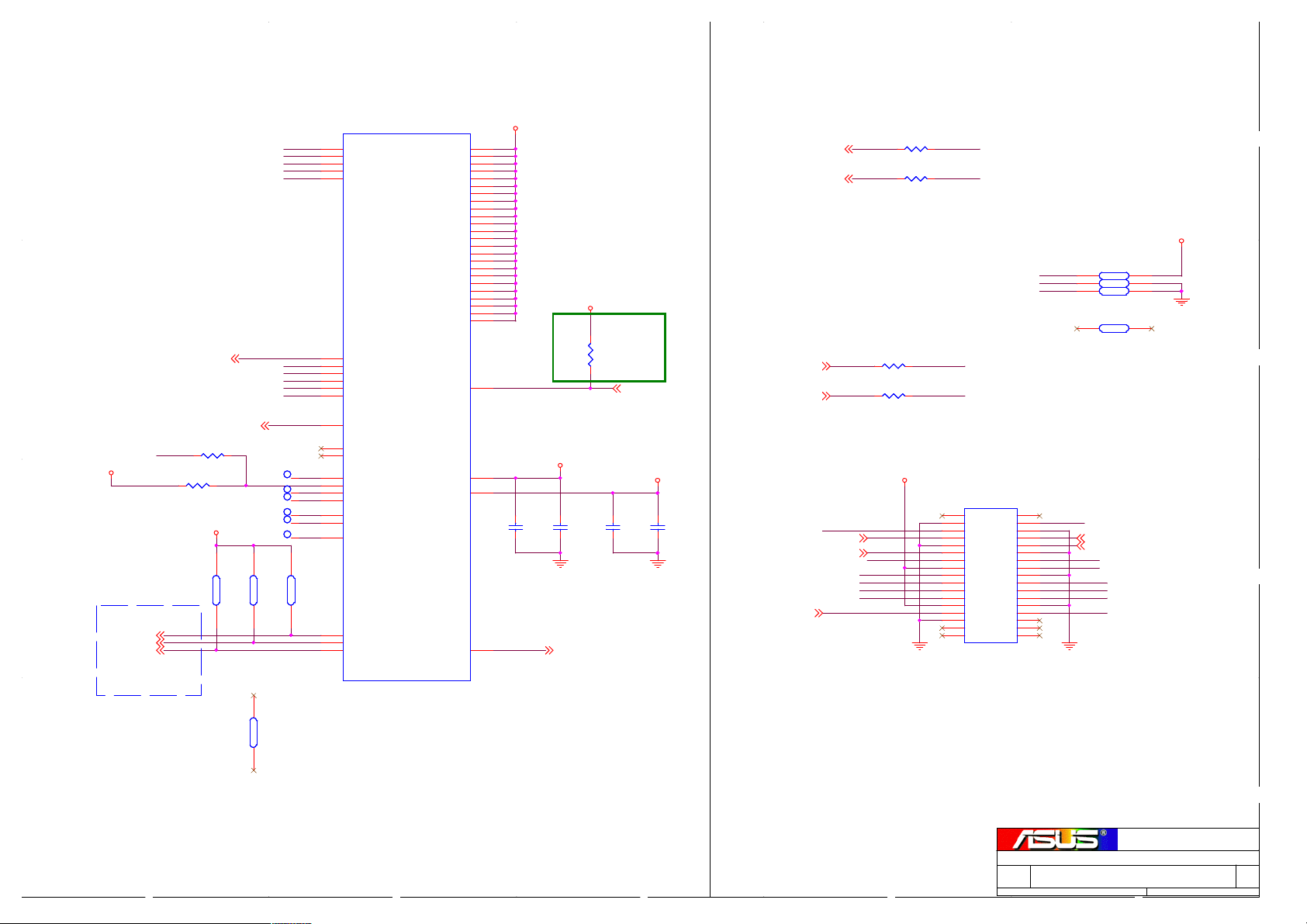

5

4

3

2

1

VR PROCHOT CKT

D D

+12V

RT8800A+RT9401A+RT9401B

+RT9605B *3 PHASE

VCORE/125A

S0/S1

RT9173CPSP

VTT_DDR

S0/S1

0.195A

only 1.8V_DUAL 5A

+5V

AP70T03GH+

P3055G

C C

+5VSB

L1085

L1117

+5V_DUAL

+3VSB

S0/S1/S3/S4/S5

LAN_2.5V

APW7120+Hi-side

AP70T03GH*1+Low-side

AP70T03GH*2

S0/S1/S3

+1.8V_DUAL

11.5A

S0/S1

OP+AP9T15GH*2

OP+AP9452*1

+1.25V_GMCH

5.79A

+1.05V

0.51A

S0/S1/S3

S0/S1

LAN_1.5V

L1085

B B

S0/S1/S3

+3V

L1117

+1.8V

S0/S1

0.143A

OP+AP70T03G*2

+1.5V

S0/S1

1.37A

A A

OP+AP70T03G*1

VTT_CPU

S0/S1

0.6A

Title :

Title :

Title :

POWER FLOW

POWER FLOW

POWER FLOW

Engin eer:

Engin eer:

ASUSTek Inc.

ASUSTek Inc.

ASUSTek Inc.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

16, 2007

16, 2007

16, 2007

Engin eer:

Kimi_W ang

Kimi_W ang

Kimi_W ang

4 49

4 49

4 49

of

of

of

Rev

Rev

Rev

4.01G

4.01G

4.01G

5

4

3

2

1

D D

MCHHCLK

CK_100M_MCH

CK_96M_DREF

266/200/ 133MHz

100 MHz

96MHz

Intel G31

MCH

Bearlake

(North Bridge)

DDR2 CHA 1

DDR2 CHB 1

VGA

CK_100M_PCIEX16

CK_100M_PCIEX1

C C

Intel LGA775

Pentium 4(90/65nm)

3.8GHz + CPU

266/200/ 133MHz

CPUHCLK

CLOCK

CK_100M_ICH

CK_100M_SATA

CK_33M_ICH

CK_48M_USB

CK_14M_ICH

ITP

266/200/ 133MHz

ICS PRS552

CK_33M_SL1

CK_33M_SL2

CK_100M_LAN

CK_25M_LAN

100 MHz

100 MHz

100 MHz

100 MHz

33 MHz

48 MHz

14.318 MHz

33 MHz

33 MHz

100MHz

25MHz

PCI-EX x16 Slot

PCI-EX x1 Slot

Intel 82801G

ICH7

(Sourth Bridge)

PCI Slot1

PCI Slot2

/X

ATHEROS

LAN

24 MHz

REALTEK

ALC662

B B

CK_100M_WIFI

CK_48M_SIO

A A

CK_33M_SIO

100MHz

48 MHz

33 MHz

SUPER I/O

W83627DHG-A

UBC

WIFI

Title :

Title :

Title :

Engin eer:

Engin eer:

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

16, 2007

16, 2007

16, 2007

Engin eer:

CLOCK DIAGRAM

CLOCK DIAGRAM

CLOCK DIAGRAM

Kimi_W ang

Kimi_W ang

Kimi_W ang

of

of

of

5 49

5 49

5 49

Rev

Rev

Rev

4.01G

4.01G

4.01G

5

4

3

2

1

D D

C C

B B

A A

CPU Timing

CPU Timing

CPU Timing

Title :

Title :

Title :

Engin eer:

Engin eer:

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

P5B-MX

P5B-MX

P5B-MX

16, 2007

16, 2007

16, 2007

Engin eer:

Lazy Li

Lazy Li

Lazy Li

of

of

of

6 49

6 49

6 49

Rev

Rev

Rev

4.01G

4.01G

4.01G

5

2.03G:del +3V_DUAL circuit

+3VSB

CL2 120Ohm/100MhzCL2 120Ohm/100Mhz

21

12

CC13

CC13

27PF/50V

27PF/50V

1 2

CR17 0Ohm

CR17 0Ohm

/X

/X

1 2

CR20 0OhmCR20 0Ohm

1 2

CR24 0Ohm

CR24 0Ohm

/X

/X

12

GNDGND

CX1

CX1

1 2

1 2

GND

GND

3

3

GND

14.318Mhz

14.318Mhz

12

CC46

CC46

0.1UF/16V

0.1UF/16V

c0402

c0402

/X

/X

D D

OSC_CK14M_XTALOUT

OSC_CK14M_XTALIN

CK_RESET#

C C

CC1

CC1

10UF/6.3V

10UF/6.3V

c0805_h57

c0805_h57

RSTCON# (10,26,40)

IO_RESET# (34)

PWROK_SB (26,34)

12

12

27PF/50V

27PF/50V

CC2

CC2

0.1UF/16V

0.1UF/16V

c0402

c0402

CC14

CC14

12

CC3

CC3

0.1UF/16V

0.1UF/16V

c0402

c0402

SLP_S4#(26,34)

12

CC4

CC4

0.1UF/16V

0.1UF/16V

c0402

c0402

CLKVCC3

GND

divide voltage

because 25M of L1 must be 1.5V

CD2

CD2

BAT54AW

BAT54AW

3

CLKVCC3

7 8

CRN1D

CRN1D

8.2KOHM

8.2KOHM

C_PG

3/3 Add CR46

VCORE_PG(26,41)

SLP_S3#(26,34)

1 2

CR46 0OhmCR46 0Ohm

1

2

B B

8.2KOhm

8.2KOhm

/X

/X

GNDGNDGND

12

10PF/50V

10PF/50V

/X

/X

CC23

CC23

7 8

33OHM

33OHM

7 8

5 6

CRN6D33OHM CRN6D33OHM

CRN6C33OHM CRN6C33OHM

CK_14M_ICH(26)

CK_48M_USB(25)

CK_48M_SIO(34)

12

12

10PF/50V

10PF/50V

/X

/X

CC21

CC21

CC22

CC22

10PF/50V

10PF/50V

/X

/X

A A

CLKVCC3

12

CR43

CR43

2.7KOhm

2.7KOhm

/X

/X

1 2

CR41

CR41

CRN7D

CRN7D

4

CC45

CC45

0.1UF/16V

0.1UF/16V

c0402

c0402

1 2

3 4

CLKVCC3

1 2

CR42

CR42

1 2

GND

12

0.1UF/16V

0.1UF/16V

c0402

c0402

8.2KOHM

8.2KOHM

8.2KOHM

8.2KOHM

CRN1C

CRN1C

8.2KOHM

8.2KOHM

5 6

FSLC

R_CK_48M_USB

R_CK_48M_SIO

8.2KOhm

8.2KOhm

/X

/X

CC8

CC8

CRN1A

CRN1A

CRN1B

CRN1B

12

CC9

CC9

0.1UF/16V

0.1UF/16V

c0402

c0402

FSD

FSLA

FSLB

DOC1

DOC2

R_CK_48M_SIO

R_CK_48M_USB

C_PG

CK_RESET#

CK_96M_DREF

CK_96M_DREF#

CK_100M_SATA

CK_100M_SATA#

CK_100M_PCIEX16

CK_100M_PCIEX16#

CK_100M_LAN

CK_100M_LAN#

O_GPBSEL0(37)

O_GPBSEL1(37)

O_GPBSEL2(37)

3

12

+

+

2.03G:change POCE11 to 100uf

POCE11

POCE11

100UF/16V

100UF/16V

/X

/X

CLKVCC3

GND

R_CK_33M_SL1

R_CK_33M_SL2

FSD

FSLA

2.03G:change CR30,CR31,CR32,CR40

to resistor array.10/17

2.03G:Change CRN6,CRN7 to 0402

array resistor.10/20

CU1

CU1

1

25Mhz

2

**RLATCH

3

VDDPCI

4

GND1

5

PCICLK3_2x

6

FSD/PCICLK4_2x

7

FSLA/PCICLK5

8

FSLB/PCICLK6

9

**DOC_1

10

**DOC_2

11

VDD48

12

**SEL24_48#/24_48MHz

13

**GSEL/48MHz

14

GND2

15

Vtt_PwrGd/WOL_STOP#

16

Reset#

17

GND3

18

DOT96T_LR/SATAT_LR

19

DOT96C_LR/SATAC_LR

20

VDDSATA

21

SATAT_LR/PCIeT_LR0

22

SATAC_LR/PCIeC_LR0

23

VDDPCIEX

24

GND4

25

PCIeT_LR1

26

PCIeC_LR1

27

PCIeT_LR2

28

PCIeC_LR2

29

PCIeT_LR3

30

PCIeC_LR3

31

PCIeT_LR7

32

PCIeC_LR7

ICS9LPRS552AGLF_T

ICS9LPRS552AGLF_T

3 4

33OHM

33OHM

1 2

33OHM

33OHM

5 6

33OHM

33OHM

MCH INPUT IS 1.5V CMOS LEVEL

/GPOStrap CRN2D

/GPOStrap

7 8

/GPOStrap CRN2B

/GPOStrap

3 4

/GPOStrap CRN2A

/GPOStrap

1 2

/GPOStrap CRN2C

/GPOStrap

5 6

/GPOStrap CRN4A

/GPOStrap

1 2

4.7KOHM

/GPOStrap CRN4B

/GPOStrap

/GPOStrap CRN4C

/GPOStrap

/GPOStrap CRN4D

/GPOStrap

GND

4.7KOHM

3 4

4.7KOHM

4.7KOHM

5 6

4.7KOHM

4.7KOHM

7 8

4.7KOHM

4.7KOHM

4.7KOHM

4.7KOHM

4.7KOHM

4.7KOHM

4.7KOHM

4.7KOHM

4.7KOHM

4.7KOHM

CRN4A

CRN4B

CRN4C

CRN4D

CRN2D

CRN2B

CRN2A

CRN2C

PCICLK7_REF0/SELPCI_REF#**

12

34

2.03G:del TPM

CLOCK.10/16

del 1394clock

CRN7B

CRN7B

CRN7A

CRN7A

CRN7C

CRN7C

CRN6A33OHM CRN6A33OHM

CRN6B33OHM CRN6B33OHM

CLKVCC3

12

0.1UF/16V

0.1UF/16V

c0402

c0402

GND

VDD25Mhz

PCICLK2

PCICLK1

PCICLK0

REF1/FSLC

VDDREF

CPUT_LR0

CPUC_LR0

VDDCPU

CPUT_LR1

CPUC_LR1

PCIeT_LR6

PCIeC_LR6

PCIeT_LR5

PCIeC_LR5

PCIeT_LR4

PCIeC_LR4

PCIeT_LR8

PCIeC_LR8

M_HBSEL0

M_HBSEL1

M_HBSEL2

CC6

CC6

GND5

GND6

SCLK

SDATA

GND7

VDDI/O

GNDA

VDDA

GND8

GND9

X1

X2

12

10PF/50V

10PF/50V

/X

/X

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

CC16

CC16

12

12

CC7

CC7

0.1UF/16V

0.1UF/16V

c0402

c0402

CLKVCC3

OSC_CK14M_XTALIN

OSC_CK14M_XTALOUT

GND

12

CC17

CC17

10PF/50V

10PF/50V

/X

/X

MOUNT WHEN

USE CPU

STRAP

HBSEL0

HBSEL1

HBSEL2

FSLA

FSLB

FSLC

FSD

R15

R15

1%

1%

/1333/X

/1333/X

CC5

CC5

0.1UF/16V

0.1UF/16V

c0402

c0402

R_CK_33M_SL2

R_CK_33M_SL1

FSLC

SMBCLK_CLK

SMBDATA_CLK

CPUHCLK

CPUHCLK#

MCHHCLK

MCHHCLK#

CK_100M_MCH

CK_100M_MCH#

CK_100M_PCIEX1

CK_100M_PCIEX1#

CK_100M_ICH

CK_100M_ICH#

12

12

CC19

CC19

10PF/50V

10PF/50V

10PF/50V

10PF/50V

/X

/X

/X

/X

GND

7 8

4.7KOHM

4.7KOHM

3 4

4.7KOHM

4.7KOHM

5 6

4.7KOHM

4.7KOHM

1 2

4.7KOHM

4.7KOHM

3 4

8.2KOHM

8.2KOHM

5 6

8.2KOHM

8.2KOHM

1 2

8.2KOHM

8.2KOHM

7 8

8.2KOHM

8.2KOHM

1KOhm

1KOhm

12

GND

CC20

CC20

2

CRN3D

CRN3B

CRN3C

CRN3A

CRN5B

CRN5B

CRN5C

CRN5C

CRN5A

CRN5A

CRN5D

CRN5D

/CPUStrap/XCRN3D

/CPUStrap/X

/CPUStrap/XCRN3B

/CPUStrap/X

/CPUStrap/XCRN3C

/CPUStrap/X

/CPUStrap/XCRN3A

/CPUStrap/X

CK_33M_SL1 (30)

CK_33M_SL2 (30)

CK_33M_ICH (25)

CK_33M_SIO (34)

GND

12

12

CC11

CC11

CC12

CC12

10PF/50V

10PF/50V

10PF/50V

10PF/50V

/x

/x

/x

/x

GND GND

2.03G:del caps for

differential signals

10/16

M_HBSEL0 (15)

M_HBSEL1 (15)

M_HBSEL2 (15)

HBSEL0 (10)

HBSEL1 (10)

HBSEL2 (10)

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

16, 2007

16, 2007

16, 2007

1

SMBDATA_CLK (26)

SMBCLK_CLK (26)

Title :

Title :

Title :

Engin eer:

Engin eer:

Engin eer:

MCHHCLK (13)

MCHHCLK# (13)

CPUHCLK (9,10)

CPUHCLK# (9,10)

CK_100M_PCIEX1 (29)

CK_100M_PCIEX1# (29)

CK_96M_DREF (15)

CK_96M_DREF# (15)

CK_100M_SATA (25)

CK_100M_SATA# (25)

CK_100M_MCH (13)

CK_100M_MCH# (13)

CK_100M_ICH (25)

CK_100M_ICH# (25)

CK_100M_PCIEX16 (23)

CK_100M_PCIEX16# (23)

CK_100M_LAN (38)

CK_100M_LAN# (38)

CLOCK GEN

CLOCK GEN

CLOCK GEN

Kimi_W ang

Kimi_W ang

Kimi_W ang

7 49

7 49

7 49

of

of

of

Rev

Rev

Rev

4.01G

4.01G

4.01G

5

4

3

2

1

HA#[35..3] (13)

LGA775A

HA#3

HA#4

HT3 /XHT3 /X

HT5 /XHT5 /X

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

D D

HREQ#[4..0](13)

HADSTB#0(13)

C C

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HA#34

HA#35

B B

HT12 /XHT 12 /X

HT13 /XHT 13 /X

HADSTB#1(13)

A A

LGA775A

L5

A03#

P6

A04#

M5

A05#

L4

A06#

M4

A07#

R4

A08#

T5

A09#

U6

A10#

T4

A11#

U5

A12#

U4

A13#

V5

A14#

V4

A15#

W5

A16#

N4

1

RSVD1

1

P5

RSVD2

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

R6

ADSTB0#

AB6

A17#

W6

A18#

Y6

A19#

Y4

A20#

AA4

A21#

AD6

A22#

AA5

A23#

AB5

A24#

AC5

A25#

AB4

A26#

AF5

A27#

AF4

A28#

AG6

A29#

AG4

A30#

AG5

A31#

AH4

A32#

AH5

A33#

AJ5

A34#

AJ6

A35#

1

AC4

RSVD3

1

AE4

RSVD4

AD5

ADSTB1#

SOCKET775

SOCKET775

GTLREF_SEL

ADS#

BNR#

HIT#

RSP#

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

BINIT#

DEFER#

MCERR#

AP0#

AP1#

BR0#

TESTHI08

TESTHI09

TESTHI10

DP0#

DP1#

DP2#

DP3#

GTLREF0

GTLREF1

GTLREF2

RESET#

RS0#

RS1#

RS2#

D2

C2

D4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

AD3

G7

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

H1

H2

1

HIERR#

1

1

1

HTESTHI10

1

1

1

1

HADS# (13)

HBNR# (13)

HHIT# (13)

HT1 /xHT1 /x

HBPRI# (13)

HDBSY# (13)

HDRDY# (13)

HHITM# (13)

HINIT# (25)

HLOCK# (13)

HTRDY# (13)

HDEFER# (13)

HT4 /XHT4 /X

HT6 /XHT6 /X

HT7 /XHT7 /X

HBR#0 (13)

HT8 /XHT8 /X

HT9 /XHT9 /X

HT10 /XHT 10 /X

HT11 /XHT 11 /X

HCPU_GTLREF02

HCPU_GTLREF13

HTESTHI08

HTESTHI09

HTESTHI10

HBR#0

HTESTHI08 (10)

HTESTHI09 (10)

1

1 2

HIERR#

1 2

HR1 62OhmHR1 62Ohm

HT2 /XHT2 /X

1 2

51Ohm

51Ohm

3 4

51Ohm

51Ohm

5 6

51Ohm

51Ohm

7 8

51Ohm

51Ohm

HR2 62OhmHR2 62Ohm

H_VTT_OUT_R

HRN1A

HRN1A

H_VTT_OUT_L

HRN1B

HRN1B

HRN1C

HRN1C

HRN1D

HRN1D

Omit 0ohm resister between GTLREF0&1

HCPURST#

E24

H29

G23

B3

F5

A3

HRS#0

HRS#1

HRS#2

CPU_MCH_GTLREF (13)

H_GTLREF_SEL

HCPURST# (10,13)

HCPU_GTLREF02(9)

1

HRS#[2..0] (13)

HT73 /xHT73 /x

CPU_GTLREF0 Voltage Divider

* CPU_GTLREF = 0.63 * VTT = 0.8V

** Divider Should be within 1.5 in. of the

GTLREF0 Pin

*** Layout : W/S = 10/5

HR65 = 10 Ohm to Support NWD CPU

HR65 = 62 Ohm ( Original )

HCPU_GTLREF02

HC3

HC3

220PF/50V

220PF/50V

/X

/X

Close to CPU

GND

Close to

Divider

HR10 10OhmHR10 10Ohm

12

GND GND GND

1 2

HR3 62OhmHR3 62Ohm

12

HC14

HC14

10PF/50V

10PF/50V

/X

/X

1 2

HD#[63..0] (13)

H_VTT_OUT_R

HCPU_GTLREF0_R

12

HC4

HC4

1UF/10V

1UF/10V

HDBI#0(13)

HDSTBN#0(13)

HDSTBP#0(13)

HDBI#1(13)

HDSTBN#1(13)

HDSTBP#1(13)

H_VTT_OUT_R

HR9

HR9

115OHM

115OHM

1%

1%

1 2

HR11

HR11

200Ohm

200Ohm

1%

1%

1 2

LGA775B

LGA775B

HD#0

B4

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

CPU_GTLREF1 Voltage Divider

* CPU_GTLREF = 0.63 * VTT = 0.8V

** Divider Should be within 1.5 in. of the

GTLREF1 Pin

*** Layout : W/S = 10/5

HR65 = 10 Ohm to Support NWD CPU

HR65 = 62 Ohm ( Original )

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

A10

D08#

A11

D09#

B10

D10#

C11

D11#

D8

D12#

B12

D13#

C12

D14#

D11

D15#

A8

DBI0#

C8

DSTBN0#

B9

DSTBP0#

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

E10

D21#

D10

D22#

F11

D23#

F12

D24#

D13

D25#

E13

D26#

G13

D27#

F14

D28#

G14

D29#

F15

D30#

G15

D31#

G11

DBI1#

G12

DSTBN1#

E12

DSTBP1#

SOCKET775

SOCKET775

220PF/50V

220PF/50V

Close to CPU

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

HCPU_GTLREF13 (9)

HCPU_GTLREF13

Close to

Divider

1 2

HR7 10OhmHR7 10Ohm

12

HC1

HC1

/X

/X

GND GND GND

2.04G:add HR7,HC2,HR8,HR6 for future CPU.

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

HD#33

E15

HD#34

E16

HD#35

G18

HD#36

G17

HD#37

F17

HD#38

F18

HD#39

E18

HD#40

E19

HD#41

F20

HD#42

E21

HD#43

F21

HD#44

G21

HD#45

E22

HD#46

D22

HD#47

G22

D19

G20

G19

HD#48

D20

HD#49

D17

HD#50

A14

HD#51

C15

HD#52

C14

HD#53

B15

HD#54

C18

HD#55

B16

HD#56

A17

HD#57

B18

HD#58

C21

HD#59

B21

HD#60

B19

HD#61

A19

HD#62

A22

HD#63

B22

C20

A16

C17

HCPU_GTLREF1_R

12

HC2

HC2

1UF/10V

1UF/10V

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

HDBI#2 (13)

HDSTBN#2 (13)

HDSTBP#2 (13)

HDBI#3 (13)

HDSTBN#3 (13)

HDSTBP#3 (13)

H_VTT_OUT_R

HR6

HR6

115OHM

115OHM

1%

1%

1 2

HR8

HR8

200Ohm

200Ohm

1%

1%

1 2

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

16, 2007

16, 2007

16, 2007

HD#32

G16

Title :

Title :

Title :

Engin eer:

Engin eer:

Engin eer:

LGA775-1

LGA775-1

LGA775-1

Kimi_W ang

Kimi_W ang

Kimi_W ang

8 49

8 49

8 49

Rev

Rev

Rev

4.01G

4.01G

4.01G

of

of

of

5

D D

+VTT_CPU

HL1 10UH /XHL1 10UH /X

HL2 10UH /XHL2 10UH /X

2.03G:del 0ohm

HR16,HR18

+VTT_CPU

HVCC_PLL

C C

2.03G:HC8 /X

HL3 10UHHL3 10UH

add circuit to control this timing

H_VTT_OUT_R

CPU VID Termination

10

10

10

10

(CPU Side)

RP1A2.7KOHM RP1A2.7KOHM

RP1B2.7KOHM RP1B2.7KOHM

RP1D2.7KOHM RP1D2.7KOHM

RP1C2.7KOHM RP1C2.7KOHM

4 5

2 5

3 5

HVID0

HVID1

HVID2

HVID3

HVID4

HVID5

HVID6

1 5

B B

HVID[6..0] (41)

HTHERMDA(34,37)

2.02G

HTHERMDC(34)

VCORE

HSMI#(25)

HA20M#(25)

HFERR#(25)

HINTR(25)

HNMI(25)

HIGNNE#(25)

HSTPCLK#(25)

21

HC5

HC5

21

21

10

10

RP1E2.7KOHM RP1E2.7KOHM

7 5

6 5

CPUHCLK(7,10)

CPUHCLK#(7,10)

12

HC17

HC17

100PF/50V

100PF/50V

/X

/X

12

10UF/6.3V

10UF/6.3V

12

HC6

HC6

10UF/6.3V

10UF/6.3V

HVCC_PLL

12

HC7

HC7

10UF/6.3V

10UF/6.3V

/X

/X

10

10

RP1F2.7KOHM RP1F2.7KOHM

RP1G2.7KOHM RP1G2.7KOHM

RP1H2.7KOHM RP1H2.7KOHM

8 5

9 5

VID_SEL(41,46)

H_SKTOCC#(34)

H_SKTOCC#

GND

A A

HT22 /XHT 22 /X

GND

HVSSA

12

HC8

HC8

0.01UF/50V

0.01UF/50V

/X

/X

1

4

LGA775C

LGA775C

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0/INTR

L1

LINT1/NMI

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

C23

VCCIOPLL

D23

VCC_PLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

VID6

AM7

VID7

AN7

VID_SECECT

F28

BCLK0

G28

BCLK1

AE8

SKTOCC#

AL1

THERMDA

AK1

THERMDC

AJ7

RSVD7

AH7

RSVD8

AN3

VCC_SENSE

AN4

VSS_SENSE

AN5

VCC_MB_REGULATION

AN6

VSS_MB_REGULATION

AL8

VCC_D_SENSE

AL7

VSS_D_SENSE

F29

RSVD9

SOCKET775

SOCKET775

TESTHI_0

TESTHI_2

TESTHI_3

TESTHI_4

TESTHI_5

TESTHI_6

TESTHI_7

TESTHI_1

TESTHI_11

TESTHI_12

TESTHI_13

RSVD33

RSVD34

RSVD35

RSVD36

FC5/GTLREF2

RSVD14/GTLREF3

FORCEPR#

RSVD12

PWRGOOD

PROCHOT#

THERMTRIP#

COMP0

COMP1

COMP2

COMP3

COMP4

COMP5

COMP6

COMP7

COMP8

IMPSEL

PECI

RSVD21

MSID1

MSID0

BOOTSELECT

LL_ID0

LL_ID1

3

+VTT_CPU

HR12

HR12

49.9Ohm

49.9Ohm

1

HCPU_GTLREF13 (8)

HCPU_GTLREF02 (8)

HFORCEPH# (44)

HT17 /XHT17 /X

HTHERMTRIP# (25)

HCOMP0

HCOMP1

HCOMP2

HCOMP3

HCOMP4

HCOMP5

HCOMP6

HCOMP7

HCOMP8

HT18 /XHT 18 /X

1

HT19 /XHT 19 /X

1

HT20 /XHT20 /X

1

HT21 /XHT21 /X

1

HT23 /XHT23 /X

1

1 2

HT16 /XHT16 /X

HPROCHOT# (44)

1 2

HR28 49.9OhmHR28 49.9Ohm

HPECI (34)

1 2

HR30 51Ohm

HR30 51Ohm

/X

/X

1 2

HR31 49.9OhmHR31 49.9Ohm

1 2

HR32 49.9OhmHR32 49.9Ohm

HR13 49.9OhmHR13 49.9Ohm

5 6

1 2

3 4

7 8

1 2

HR19 49.9Ohm 1%HR19 49.9Ohm 1%

1 2

HR20 49.9Ohm 1%HR20 49.9Ohm 1%

1 2

HR21 49.9Ohm 1%HR21 49.9Ohm 1%

1 2

HR22 49.9Ohm 1%HR22 49.9Ohm 1%

1 2

HR23 49.9Ohm 1%HR23 49.9Ohm 1%

1 2

HR24 49.9Ohm 1%HR24 49.9Ohm 1%

1 2

HR25 49.9Ohm 1%HR25 49.9Ohm 1%

1 2

HR26 49.9Ohm 1%HR26 49.9Ohm 1%

1 2

HR27 24.9Ohm 1%HR27 24.9Ohm 1%

HTESTHI00

F26

HTESTHI02

F25

HTESTHI03

G25

HTESTHI04

G27

HTESTHI05

G26

HTESTHI06

G24

HTESTHI07

F24

HTESTHI01

W3

HTESTHI11

P1

HTESTHI12

W2

HTESTHI13

L2

HTP_G1

G1

HTESTHI12

U1

RSVD35

A24

E29

F2

G10

AK6

1

AH2

N1

AL2

M2

A13

T1

G2

R1

J2

T2

Y3

AE3

B13

F6

G5

AL3

NC

G6

V1

W1

Y1

V2

AA2

12

51Ohm

51Ohm

51Ohm

51Ohm

51Ohm

51Ohm

51Ohm

51Ohm

1 2

H_VTT_OUT_L

12

12

GNDGND

GND

H_VTT_OUT_R

GND

+VTT_CPU

HRN2C

HRN2C

HRN2A

HRN2A

HRN2B

HRN2B

HRN2D

HRN2D

/X

HR17

HR17

100Ohm

100Ohm

/X

/X

HC9

HC9

27PF/50V

27PF/50V

GND

H_VTT_OUT_L

HR5051Ohm/XHR5051Ohm

HTP_G1

HCPU_PWRGD (10,26)

2.03G:change the value from

33pf to 27pf for combine components

H_VTT_OUT_L

GND

GND

RSVD35

1 2

HR14 0Ohm /XHR14 0Ohm /X

12

HC15

HC15

0.1UF/16V

0.1UF/16V

c0603

c0603

/X

/X

2

HTESTHI13

H_VTT_OUT_R

12

HC16

HC16

0.1UF/16V

0.1UF/16V

c0603

c0603

/X

/X

GND

HR49

HR49

1 2

1KOhm

1KOhm

/X

/X

1 2

HR53 0Ohm /XHR53 0Ohm /X

HBPM#0 (10)

GND

HCPUSLP# (25)

HFORCEPH#

HPROCHOT#

2.03G:change HR12,HR13,HR28,

HR31,HR32 to 49.9ohm for

combine components.

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

16, 2007

16, 2007

16, 2007

1

130Ohm

130Ohm

Title :

Title :

Title :

Engin eer:

Engin eer:

Engin eer:

H_VTT_OUT_R

HR46

HR46

1%

1%

LGA775-2

LGA775-2

LGA775-2

12

12

HR47

HR47

130Ohm

130Ohm

1%

1%

Kimi_W ang

Kimi_W ang

Kimi_W ang

9 49

9 49

9 49

of

of

of

Rev

Rev

Rev

4.01G

4.01G

4.01G

5

4

3

2

1

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

+VTT_CPU

3/3 Change to 62 for time short

H_VTT_OUT_R

HR48

HR48

62Ohm

62Ohm

/X

/X

1 2

H_VTT_OUT_R

12

12

0.1UF/16V

0.1UF/16V

/X

/X

HC10

HC10

HC11

HC11

0.1UF/16V

0.1UF/16V

GND

VTT_SELECT (43)

VTT_PWRGD (41,44)

H_VTT_OUT_L

12

12

HC12

HC12

0.1UF/16V

0.1UF/16V

/X

/X

GND

HC13

HC13

0.1UF/16V

0.1UF/16V

c0603

c0603

HR51

1 2

HR36

1 2

HTCK

HTDO

HBPM#0

HBPM#2

HBPM#4

1 2

HR33 0Ohm /ITP/XHR33 0Ohm /ITP/X

1 2

HR34 0Ohm /ITP/XHR34 0Ohm /ITP/X

0OhmHR51

0Ohm

ITP_CLK

/ITP/X

/ITP/X

0OhmHR36

0Ohm

ITP_CLK#

/ITP/X

/ITP/X

H_VTT_OUT_R

GND

HBPM#2

ITP

ITP

31

SIDE1

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

21

21

23

23

25

25

27

27

29

29

32

SIDE2

FPC_CON_30P

FPC_CON_30P

/X

/X

SIDE4

SIDE3

H_VTT_OUT_R

HBPM#5

1 2

HTCK

3 4

HTRST#

5 6

7 8

34

ITP_CLK

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

33

SMBDATA_OTHER (23,26,29,38)

HCPURST# (8,13)

HTMS

HTDI

HBPM#1

HBPM#3

HBPM#5

HTRST#

GND

62OHM

62OHM

62OHM

62OHM

62OHM

62OHM

62OHM

62OHM

HRN3A

HRN3A

HRN3B

HRN3B

HRN3C

HRN3C

HRN3D

HRN3D

GND

HTESTHI08(8)

HTESTHI09(8)

CPUHCLK(7,9)

CPUHCLK#(7,9)

ITP_CLK#

SMBCLK_OTHER(23,26,29,38)

RSTCON#(7,26,40)

HCPU_PWRGD(9,26)

LGA775D

HRN6A

HRN6A

1KOHM

1KOHM

AD1

AF1

AC1

AG1

AD2

AG2

AF2

AG3

AC2

AK3

AE6

D16

E23

G29

H30

G30

AE1

AJ2

AJ1

AJ3

N5

C9

E7

A20

LGA775D

TCK

TDI

TDO

TMS

TRST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLKOUT0

ITPCLKOUT1

RSVD17

RSVD18

RSVD19

RSVD20

RSVD22

RSVD23

RSVD31

BSEL0

BSEL1

BSEL2

SOCKET775

SOCKET775

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTTPWRGD

VTT_OUT_R

VTT_OUT_L

VTT_SEL

D D

HBPM#1

HBPM#0(9)

RSTCON#(7,26,40)

1 2

HR37 0Ohm

HR37 0Ohm

1 2

HR38 49.9OhmHR38 49.9Ohm

+VTT_CPU

HRN6B

HRN6B

1KOHM

1KOHM

/ITP/X

/ITP/X

3 4

C C

H_VTT_OUT_L

2.03G:change HR38 51ohm to

49.9ohm for combining component

B B

HBSEL0(7)

HBSEL1(7)

HBSEL2(7)

USE 1K SERIES RES

TO ISOLATE CLOCK

HTCK HBPM#3

HTDI

HTDO

HTMS

HTRST#

HBPM#0

HBPM#1

HBPM#2

HBPM#3

HBPM#4

HBPM#5

HT24 /XHT 24 /X

1

HTP_C9

HT25 /XHT 25 /X

1

HT26 /XHT 26 /X

1

HT27 /XHT 27 /X

1

HT28 /XHT 28 /X

1

HT29 /XHT 29 /X

1

HRN6C

HRN6C

1KOHM

1KOHM

5 6

1 2

HRN6D

HRN6D

1KOHM

1KOHM

7 8

A A

Title :

Title :

Title :

LGA775-3

LGA775-3

Engin eer:

Engin eer:

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

16, 2007

16, 2007

16, 2007

Engin eer:

LGA775-3

Kimi_W ang

Kimi_W ang

Kimi_W ang

10 49

10 49

10 49

Rev

Rev

Rev

4.01G

4.01G

4.01G

of

of

of

5

4

3

VCORE

2

1

D D

K24

K25

K26

K27

K28

K29

K30

K8

Y8

Y30

Y29

Y28

Y27

Y26

Y25

Y24

Y23

W8

C C

B B

W30

W29

W28

W27

W26

W25

W24

W23

U30

U29

U28

U27

U26

U25

U24

U23

T30

T29

T28

T27

T26

T25

T24

T23

N30

N29

N28

N27

N26

N25

N24

N23

M30

M29

M28

M27

M26

M25

M24

M23

V8

U8

T8

R8

P8

N8

M8

L8

K23

VCC161

VCC162

VCC163

VCC164

VCC165

VCC166

VCC167

VCC168

VCC169

VCC170

VCC171

VCC172

VCC173

VCC174

VCC175

VCC176

VCC177

VCC178

VCC179

VCC180

VCC181

VCC182

VCC183

VCC184

VCC185

VCC186

VCC187

VCC188

VCC189

VCC190

VCC191

VCC192

VCC193

VCC194

VCC195

VCC196

VCC197

VCC198

VCC199

VCC200

VCC201

VCC202

VCC203

VCC204

VCC205

VCC206

VCC207

VCC208

VCC209

VCC210

VCC211

VCC212

VCC213

VCC214

VCC215

VCC216

VCC217

VCC218

VCC219

VCC220

VCC221

VCC222

VCC223

VCC224

VCC225

VCC226

VCC1

AA8

AB8

J29

J30

VCC156

VCC157

VCC158J8VCC159J9VCC160

VCC2

VCC3

VCC4

VCC5

AC23

AC24

AC25

J22

J23

J24

J25

J26

J27

J28

VCC149

VCC150

VCC151

VCC152

VCC153

VCC154

VCC155

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

AC8

AC26

AC27

AC28

AC29

AC30

AD23

J13

J14

J15

J18

J19

J20

J21

VCC142

VCC143

VCC144

VCC145

VCC146

VCC147

VCC148

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AN29

AN30

AN8

AN9

J10

J11

J12

VCC135

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

AD8

AE11

AE12

AE14

AE15

AE18

AE19

AN15

AN18

AN19

AN21

AN22

AN25

AN26

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC134

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

AE9

AF11

AF12

AF14

AE21

AE22

AE23

AM29

AM30

AM8

AM9

AN11

AN12

AN14

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

AF8

AF9

AF15

AF18

AF19

AF21

AF22

LGA775E

LGA775E

AM25

AM26

SOCKET775

SOCKET775

VCC119

VCC120

VCC121

VCC40

VCC41

AG11

VCC118

VCC117

VCC116

VCC115

VCC114

VCC113

VCC112

VCC111

VCC110

VCC108

VCC107

VCC106

VCC105

VCC104

VCC103

VCC102

VCC101

VCC100

VCC99

VCC98

VCC97

VCC96

VCC95

VCC94

VCC93

VCC92

VCC91

VCC90

VCC89

VCC88

VCC87

VCC86

VCC85

VCC84

VCC83

VCC82

VCC81

VCC80

VCC79

VCC78

VCC77

VCC76

VCC75

VCC74

VCC73

VCC72

VCC71

VCC70

VCC69

VCC68

VCC67

VCC66

VCC65

VCC64

VCC63

VCC62

VCC61

VCC60

VCC59

VCC58

VCC57

VCC56

VCC55

VCC54

VCC53

VCC52

VCC51

VCC50

VCC49

VCC48

VCC47

VCC46

VCC45

VCC42

VCC43

AG12

AG14

AM22

AM21

AM19

AM18

AM15

AM14

AM12

AM11

AL9

AL30

AL29

AL26

AL25

AL22

AL21

AL19

AL18

AL15

AL14

AL12

AL11

AK9

AK8

AK26

AK25

AK22

AK21

AK19

AK18

AK15

AK14

AK12

AK11

AJ9

AJ8

AJ26

AJ25

AJ22

AJ21

AJ19

AJ18

AJ15

AJ14

AJ12

AJ11

AH9

AH8

AH30

AH29

AH28

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

VCC44

AG15

A A

Title :

Title :

Title :

Engin eer:

Engin eer:

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

16, 2007

16, 2007

16, 2007

Engin eer:

LGA775-4

LGA775-4

LGA775-4

Kimi_W ang

Kimi_W ang

Kimi_W ang

11 49

11 49

11 49

Rev

Rev

Rev

4.01G

4.01G

4.01G

of

of

of

5

LGA775F

LGA775F

AF28

VSS60

AF27

VSS59

AF26

VSS58

AF25

VSS57

AF24

VSS56

AF23

VSS55

AF20

VSS54

D D

GND

AF17

AF16

AF13

AF10

AE7

AE5

AE30

AE29

AE28

AE27

AE26

AE25

AE24

AE20

AE2

AE17

AE16

AE13

AE10

AD7

AD4

AC7

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

C C

HT30/XHT30/X

HT31/XHT31/X

HTP_E5

HT32/XHT32/X

HT33/XHT33/X

HTP_J3

HR44

HR44

HR45

HR45

1KOhm

1KOhm

1KOhm

1KOhm

/X

/X

/X

B B

1 2

1 2

GNDGND

Place at

bottom

/X

D1

1

1

1

1

D14

E5

E6

F23

J3

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

SOCKET775

SOCKET775

4

4

A12

VSS1

A15

VSS2

A18

VSS3

A2

VSS4

A21

VSS5

A6

VSS7

A9

VSS8

AA23

VSS9

AA24

VSS10

AA25

VSS11

AA26

VSS12

AA27

VSS13

AA28

VSS14

AA29

VSS15

AA3

VSS16

AA30

VSS17

AA6

VSS18

AA7

VSS19

AB1

VSS20

AB23

VSS21

AB24

VSS22

AB25

VSS23

AB26

VSS24

AB27

VSS25

AB28

VSS26

AB29

VSS27

AB30

VSS28

AB7

VSS29

AC3

VSS30

AC6

VSS31

GND

post_nc11post_nc22post_nc33post_nc4

3

H24

H25

H26

H27

K5

K7

VSS218

L23

VSS219

L24

VSS220

L25

VSS221

L26

VSS222

L27

VSS223

L28

VSS224

L29

VSS225

L3

VSS226

L30

VSS227

L6

VSS228

L7

VSS229

M1

VSS230

M7

VSS231

N3

VSS232

N6

VSS233

N7

VSS234

P23

VSS235

P24

VSS236

P25

VSS237

P26

VSS238

P27

VSS239

P28

VSS240

P29

VSS241

P30

VSS242

P4

VSS243

P7

VSS244

R2

VSS245

R23

VSS246

R24

VSS247

R25

VSS248

R26

VSS249

R27

VSS250

R28

VSS251

R29

VSS252

R30

VSS253

R5

VSS254

R7

VSS255

T3

VSS256

T6

VSS257

T7

VSS258

U7

VSS260

V23

VSS261

V24

VSS262

V25

VSS263

V26

VSS264

V27

VSS265

V28

VSS266

V29

VSS267

V3

VSS268

V30

VSS269

V6

VSS270

V7

VSS271

W4

VSS272

W7

VSS273

Y2

VSS274

Y5

VSS275

Y7

VSS276

VSS61

VSS62

VSS63

VSS64

VSS65

AF3

AF6

AF7

AF29

AF30

H28

VSS204

VSS205

VSS206

VSS207

VSS209H3VSS210H6VSS211H7VSS212H8VSS213H9VSS214J4VSS215J7VSS216K2VSS217

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AH1

AG7

AH10

AG10

AG13

AG16

AG17

AH13

AG20

AG23

AG24

2

LGA775G

LGA775G

E11

E14

E17

E20

E25

E26

E27

E28

F10

F13

F16

F19

F22

H10

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

VSS171D9VSS172

VSS173

VSS174

VSS175E2VSS176

VSS177

VSS178

VSS179

VSS180

VSS182E8VSS183

VSS184

VSS185

VSS186

VSS187

VSS188F4VSS189F7VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS164

VSS163

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

AJ4

AH3

AH6

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AH16

AH17

AH20

AH23

AH24

AJ30

AK2

AK10

AK13

AK16

AK17

AK20

AK23

AK24

AK27

AK28

AK29

SOCKET775

SOCKET775

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

B14

B11

B1

AN28

AN27

AN24

AN23

AN20

AN2

AN17

AN16

AN13

AN10

AN1

AM4

AM28

AM27

AM24

AM23

AM20

AM17

AM16

AM13

AM10

AM1

AL28

AL27

AL24

AL23

AL20

AL17

AL16

AL13

AL10

AK7

AK5

AK30

1

GND

A A

Title :

Title :

Title :

LGA775-5

LGA775-5

Engin eer:

Engin eer:

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

16, 2007

16, 2007

16, 2007

Engin eer:

LGA775-5

Kimi_W ang

Kimi_W ang

Kimi_W ang

12 49

12 49

12 49

Rev

Rev

Rev

4.01

4.01

4.01

of

of

of

5

NU1A

NU1A

X16_RXP0(23)

X16_RXN0(23)

X16_RXP1(23)

X16_RXN1(23)

X16_RXP2(23)

X16_RXN2(23)

X16_RXP3(23)

X16_RXN3(23)

X16_RXP4(23)

X16_RXN4(23)

D D

C C

B B

A A

X16_RXP5(23)

X16_RXN5(23)

X16_RXP6(23)

X16_RXN6(23)

X16_RXP7(23)

X16_RXN7(23)

X16_RXP8(23)

X16_RXN8(23)

X16_RXP9(23)

X16_RXN9(23)

X16_RXP10(23)

X16_RXN10(23)

X16_RXP11(23)

X16_RXN11(23)

X16_RXP12(23)

X16_RXN12(23)

X16_RXP13(23)

X16_RXN13(23)

X16_RXP14(23)

X16_RXN14(23)

X16_RXP15(23)

X16_RXN15(23)

DMI_RXP0(25)

DMI_RXN0(25)

DMI_RXP1(25)

DMI_RXN1(25)

DMI_RXP2(25)

DMI_RXN2(25)

DMI_RXP3(25)

DMI_RXN3(25)

CK_100M_MCH(7)

CK_100M_MCH#(7)

SDVO_CTRL_DATA(23)

SDVO_CTRL_CLK(23)

+1.25V_GMCH

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CLOSE

TO

MCH

F15

G15

K15

J15

F12

E12

J12

H12

J11

H11

C2

D2

G6

G5

M8

M9

M4

M5

M6

R9

R10

T4

R4

R6

R7

W2

AA7

AA6

AB3

AA4

B12

B13

G17

E17

NR56 5.1KOhmNR56 5.1KOhm

NR57 5.1KOhm /XNR57 5.1KOhm /X

NR58 5.1KOhmNR58 5.1KOhm

NR59 5.1KOhm /XNR59 5.1KOhm /X

NR60 5.1KOhmNR60 5.1KOhm

NR61 5.1KOhm /XNR61 5.1KOhm /X

NR62 5.1KOhmNR62 5.1KOhm

NR63 5.1KOhm /XNR63 5.1KOhm /X

EXP_RXP0

EXP_RXN0

EXP_RXP1

EXP_RXN1

EXP_RXP2

EXP_RXN2

EXP_RXP3

EXP_RXN3

EXP_RXP4

EXP_RXN4

F7

EXP_RXP5

E7

EXP_RXN5

E5

EXP_RXP6

F6

EXP_RXN6

EXP_RXP7

EXP_RXN7

EXP_RXP8

EXP_RXN8

L9

EXP_RXP9

L8

EXP_RXN9

EXP_RXP10

EXP_RXN10

EXP_RXP11

L4

EXP_RXN11

EXP_RXP12

EXP_RXN12

EXP_RXP13

EXP_RXN13

EXP_RXP14

EXP_RXN14

EXP_RXP15

EXP_RXN15

DMI_RXP0

V1

DMI_RXN0

Y8

DMI_RXP1

Y9

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

GCLKP

GCLKN

SDVO_CTRLDATA

SDVO_CTRLCLK

G31

G31

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

DMI

DMI

PCIE

PCIE

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_COMPO

EXP_COMPI

EXP_TXP0

EXP_TXN0

EXP_TXP1

EXP_TXN1

EXP_TXP2

EXP_TXN2

EXP_TXP3

EXP_TXN3

EXP_TXP4

EXP_TXN4

EXP_TXP5

EXP_TXN5

EXP_TXP6

EXP_TXN6

EXP_TXP7

EXP_TXN7

EXP_TXP8

EXP_TXN8

EXP_TXP9

EXP_TXN9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

D11

D12

B11

A10

C10

D9

B9

B7

D7

D6

B5

B6

B3

B4

F2

E2

F4

G4

J4

K3

L2

K1

N2

M2

P3

N4

R2

P1

U2

T2

V3

U4

V7

V6

W4

Y4

AC8

AC9

Y2

AA2

AC11

AC12

C_M_TXP0

C_M_TXN0

C_M_TXP1

C_M_TXN1

C_M_TXP2

C_M_TXN2

C_M_TXP3

C_M_TXN3

4

X16_TXP0 (23)

X16_TXN0 (23)

X16_TXP1 (23)

X16_TXN1 (23)

X16_TXP2 (23)

X16_TXN2 (23)

X16_TXP3 (23)

X16_TXN3 (23)

X16_TXP4 (23)

X16_TXN4 (23)

X16_TXP5 (23)

X16_TXN5 (23)

X16_TXP6 (23)

X16_TXN6 (23)

X16_TXP7 (23)

X16_TXN7 (23)

X16_TXP8 (23)

X16_TXN8 (23)

X16_TXP9 (23)

X16_TXN9 (23)

X16_TXP10 (23)

X16_TXN10 (23)

X16_TXP11 (23)

X16_TXN11 (23)

X16_TXP12 (23)

X16_TXN12 (23)

X16_TXP13 (23)

X16_TXN13 (23)

X16_TXP14 (23)

X16_TXN14 (23)

X16_TXP15 (23)

X16_TXN15 (23)

NC88 0.1UF/16Vc0402 NC88 0.1UF/16Vc0402

NC89 0.1UF/16Vc0402 NC89 0.1UF/16Vc0402

NC90 0.1UF/16Vc0402 NC90 0.1UF/16Vc0402

NC91 0.1UF/16Vc0402 NC91 0.1UF/16Vc0402

NC92 0.1UF/16Vc0402 NC92 0.1UF/16Vc0402

NC93 0.1UF/16Vc0402 NC93 0.1UF/16Vc0402

NC94 0.1UF/16Vc0402 NC94 0.1UF/16Vc0402

NC95 0.1UF/16Vc0402 NC95 0.1UF/16Vc0402

+1.25V_GMCH

NR1

NR1

24.9Ohm

24.9Ohm

1 2

3

NU1B

N32

N34

M38

N37

M36

R34

N35

N38

U37

N39

R37

R39

R38

U36

U33

R35

AA37

G43

M34

U34

M43

M40

G35

H33

G27

H27

G29

D38

W40

W41

U42

AA42

W42

G39

U40

U41

AA41

U39

C31

J42

L39

J40

L37

L36

K42

P42

V36

V33

V35

Y34

V42

V38

Y36

Y38

Y39

F40

L35

L38

J37

L40

J33

B38

E33

Y40

T43

Y43

V41

NU1B

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HA34#

HA35#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HADSTB0#

HADSTB1#

HDSTBP0#

HDSTBN0#

HDINV0#

HDSTBP1#

HDSTBN1#

HDINV1#

HDSTBP2#

HDSTBN2#

HDINV2#

HDSTBP3#

HDSTBN3#

HDINV3#

HADS#

HTRDY#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HRS0#

HRS1#

HRS2#

HCPURST#

G31

G31

FSB

FSB

HSCOMP#

HACCVREF

HA#[35..3](8)

12

12

12

12

12

12

12

12

HREQ#[4..0](8)

DMI_TXP0 (25)

DMI_TXN0 (25)

DMI_TXP1 (25)

DMI_TXN1 (25)

DMI_TXP2 (25)

DMI_TXN2 (25)

DMI_TXP3 (25)

DMI_TXN3 (25)

HADSTB#0(8)

HADSTB#1(8)

HDSTBP#0(8)

HDSTBN#0(8)

HDBI#0(8)

HDSTBP#1(8)

HDSTBN#1(8)

HDBI#1(8)

HDSTBP#2(8)

HDSTBN#2(8)

HDBI#2(8)

HDSTBP#3(8)

HDSTBN#3(8)

HDBI#3(8)

HADS#(8)

HTRDY#(8)

HDRDY#(8)

HDEFER#(8)

HHITM#(8)

HHIT#(8)

HLOCK#(8)

HBR#0(8)

HBNR#(8)

HBPRI#(8)

HDBSY#(8)

HRS#[2..0](8)

HCPURST#(8,10)

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HA#34

HA#35 HD#32

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HSWING

HSCOMP

HRCOMP

HDVREF

HCLKP

HCLKN

2

HD#0

R40

HD#1

P41

HD#2

R41

HD#3

N40

HD#4

R42

HD#5

M39

HD#6

N41

HD#7

N42

HD#8

L41

HD#9

J39

HD#10

L42

HD#11

J41

HD#12

K41

HD#13

G40

HD#14

F41

HD#15

F42

HD#16

C42

HD#17

D41

HD#18

F38

HD#19

G37

HD#20

E42

HD#21

E39

HD#22

E37

HD#23

C39

HD#24

B39

HD#25

G33

HD#26

A37

HD#27

F33

HD#28

E35

HD#29

K32

HD#30

H32

HD#31

B34

J31

HD#33

F32

HD#34

M31

HD#35

E31

HD#36

K31

HD#37

G31

HD#38

K29

HD#39

F31

HD#40

J29

HD#41

F29

HD#42

L27

HD#43

K27

HD#44

H26

HD#45

L26

HD#46

J26

HD#47

M26

HD#48

C33

HD#49

C35

HD#50

E41

HD#51

B41

HD#52

D42

HD#53

C40

HD#54

D35

HD#55

B40

HD#56

C38

HD#57

D37

HD#58

B33

HD#59

D33

HD#60

C34

HD#61

B35

HD#62

A32

HD#63

D32

BR4 49.9Ohm 1%BR4 49.9Ohm 1%

B25

HSCOMP

C25

HSCOMP#

D25

HRCOMP

D23

D24

B24

MCHHCLK

R32

MCHHCLK#

U32

MCHHCLK (7)

MCHHCLK# (7)

1 2

MCH_GTLREF

HD#[63..0] (8)

HSCOMP

HSCOMP#

+VTT_CPU

BR3

BR3

301Ohm

301Ohm

1%

1%

1 2

12

BC3

BC3

BR5

BR5

100Ohm

100Ohm

1%

1%

0.1UF/16V

0.1UF/16V

c0603

c0603

1 2

/X

/X

12

GND

12

BC4

BC4

220PF/50V

220PF/50V

/X

/X

GND

GND

BR10 49.9OhmBR10 49.9Ohm

1 2

1%

1%

BR7 16.5OHM

BR7 16.5OHM

2.03G:change BR10 51ohm to

49.9ohm for combining

component

ASUSTEK

ASUSTEK

ASUSTEK

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

,

BR1

BR1

49.9Ohm

49.9Ohm

12

BC1

BC1

10PF/50V

10PF/50V

/X

/X

GND

BR2

BR2

49.9Ohm

49.9Ohm

12

BC2

BC2

10PF/50V

10PF/50V

/X

/X

GND

2.03G:Del BR8

BR8 0Ohm N/ABR8 0Ohm N/A

1 2

12

BC5

BC5

1UF/10V

1UF/10V

GND

P5KPL-VM/SI

P5KPL-VM/SI

P5KPL-VM/SI

17, 2008

17, 2008

17, 2008

1

+VTT_CPU

12

1%

1%

+VTT_CPU

12

1%

1%

CPU_MCH_GTLREF (8)

Title :

Title :

Title :

Engin eer:

Engin eer:

Engin eer:

+VTT_CPU

BR9

BR9

100Ohm

100Ohm

1%

1%

1 2

BR11

BR11

200Ohm

200Ohm

1%

1%

1 2

GND

BROADWATER-1

BROADWATER-1

BROADWATER-1

Kimi_W ang

Kimi_W ang

Kimi_W ang

13 49

13 49

13 49

of

of

of

Rev

Rev

Rev

2.01G

2.01G

2.01G

5

NU1C

M_CHA_MAA[14..0](19,21)

D D

C C

HT36 /x

HT36 /x

B B

A A

M_CHA_MAA0

M_CHA_MAA1

M_CHA_MAA2

M_CHA_MAA3

M_CHA_MAA4

M_CHA_MAA5

M_CHA_MAA6

M_CHA_MAA7

M_CHA_MAA8

M_CHA_MAA9

M_CHA_MAA10

M_CHA_MAA11

M_CHA_MAA12

M_CHA_MAA13

M_CHA_MAA14

M_CHA_WE#(19,21)

M_CHA_CAS#(19,21)

M_CHA_RAS#(19,21)

M_CHA_BA0(19,21)

M_CHA_BA1(19,21)

M_CHA_BA2(19,21)

M_CHA_CS#0(19,21)

M_CHA_CS#1(19,21)

M_CHA_CKE0(19,21)

M_CHA_CKE1(19,21)

M_CHA_ODT0(19,21)

M_CHA_ODT1(19,21)

M_CHA_CLK0(19)

M_CHA_CLK0#(19)

M_CHA_CLK1(19)

M_CHA_CLK1#(19)

M_CHA_CLK2(19)

M_CHA_CLK2#(19)

TP_BW_AN21

1

TPC26b

TPC26b

5

BA31

BB25

BA26

BA25

AY25

BA23

AY24

AY23

BB23

BA22

AY33

BB22

AW21

AY38

BA21

BB34

AY35

BB33

BA33

AW32

BB21

AW35

BA35

BA34

BB38

BC20

AY20

AY21

BA19

AY37

BA38

BB35

BA39

AU31

AR31

AP27

AN27

AV33

AW33

AP29

AP31

AM26

AM27

AT33

AU33

AN21

NU1C

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

SMA_A13

SMA_A14

SWE_A#

SCAS_A#

SRAS_A#

SBS_A0

SBS_A1

SBS_A2

SCS_A0#

SCS_A1#

RESERVED1

RESERVED2

SCKE_A0

SCKE_A1

RESERVED3

RESERVED4

SODT_A0

SODT_A1

RESERVED5

RESERVED6

SCLK_A0

SCLK_A0#

SCLK_A1

SCLK_A1#

SCLK_A2

SCLK_A2#

RESERVED7

RESERVED8

RESERVED9

RESERVED10

RESERVED11

RESERVED12

RESERVED13

DDR_A

DDR_A

G31

G31

SDQS_A0

SDQS_A0#

SDM_A0

SDQ_A0

SDQ_A1

SDQ_A2

SDQ_A3

SDQ_A4

SDQ_A5

SDQ_A6

SDQ_A7

SDQS_A1

SDQS_A1#

SDM_A1

SDQ_A8

SDQ_A9

SDQ_A10

SDQ_A11

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQS_A2

SDQS_A2#

SDM_A2

SDQ_A16

SDQ_A17

SDQ_A18

SDQ_A19

SDQ_A20

SDQ_A21

SDQ_A22

SDQ_A23

SDQS_A3

SDQS_A3#

SDM_A3

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_A31

SDQS_A4

SDQS_A4#

SDM_A4

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQS_A5

SDQS_A5#

SDM_A5

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQS_A6

SDQS_A6#

SDM_A6

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_A54

SDQ_A55

SDQS_A7

SDQS_A7#

SDM_A7

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

4

AU4

AR3

AR2

AR5

AR4

AV3

AV2

AP3

AP2

AU1

AV4

BB3

BA4

BA2

AY2

AY3

BB5

AY6

AW2

AW3

BA5

BB4

BB9

BA9

AY9

AY7

BC7

AW11

AY11

BB6

BA6

BA10

BB10

AT20

AU18

AN18

AT18

AR18

AU21

AT21

AP17

AN17

AP20

AV20

AR41

AR40

AU43

AV42

AU40

AP42

AN39

AV40

AV41

AR42

AP41

AL41

AL40

AM43

AN41

AM39

AK42

AK41

AN40

AN42

AL42

AL39

AG42

AG41

AG40

AJ40

AH43

AF39

AE40

AJ42

AJ41

AF41

AF42

AC42

AC41

AC40

AD40

AD43

AB41

AA40

AE42

AE41

AC39

AB42

M_CHA_DQS0 (19)

M_CHA_DQS0# (19)

M_CHA_DM0 (19)

M_CHA_DQ0

M_CHA_DQ1

M_CHA_DQ2

M_CHA_DQ3

M_CHA_DQ4

M_CHA_DQ5

M_CHA_DQ6

M_CHA_DQ7 M_CHB_DQ7

M_CHA_DQS1 (19)

M_CHA_DQS1# (19)

M_CHA_DM1 (19)

M_CHA_DQ8

M_CHA_DQ9

M_CHA_DQ10

M_CHA_DQ11

M_CHA_DQ12

M_CHA_DQ13

M_CHA_DQ14

M_CHA_DQ15

M_CHA_DQS2 (19)

M_CHA_DQS2# (19)

M_CHA_DM2 (19)

M_CHA_DQ16

M_CHA_DQ17

M_CHA_DQ18

M_CHA_DQ19

M_CHA_DQ20

M_CHA_DQ21

M_CHA_DQ22

M_CHA_DQ23

M_CHA_DQS3 (19)

M_CHA_DQS3# (19)

M_CHA_DM3 (19)

M_CHA_DQ24

M_CHA_DQ25

M_CHA_DQ26

M_CHA_DQ27

M_CHA_DQ28

M_CHA_DQ29

M_CHA_DQ30

M_CHA_DQ31

M_CHA_DQS4 (19)

M_CHA_DQS4# (19)

M_CHA_DM4 (19)

M_CHA_DQ32

M_CHA_DQ33

M_CHA_DQ34

M_CHA_DQ35

M_CHA_DQ36

M_CHA_DQ37

M_CHA_DQ38

M_CHA_DQ39

M_CHA_DQS5 (19)

M_CHA_DQS5# (19)

M_CHA_DM5 (19)

M_CHA_DQ40

M_CHA_DQ41

M_CHA_DQ42

M_CHA_DQ43

M_CHA_DQ44

M_CHA_DQ45

M_CHA_DQ46

M_CHA_DQ47

M_CHA_DQS6 (19)

M_CHA_DQS6# (19)

M_CHA_DM6 (19)

M_CHA_DQ48

M_CHA_DQ49

M_CHA_DQ50

M_CHA_DQ51

M_CHA_DQ52

M_CHA_DQ53

M_CHA_DQ54

M_CHA_DQ55

M_CHA_DQS7 (19)

M_CHA_DQS7# (19)

M_CHA_DM7 (19)

M_CHA_DQ56

M_CHA_DQ57

M_CHA_DQ58

M_CHA_DQ59

M_CHA_DQ60

M_CHA_DQ61

M_CHA_DQ62

M_CHA_DQ63

4

M_CHA_DQ[63..0] (19)

+1.8V_DUAL

BR12

BR12

1KOhm

1KOhm

1%

1%

1 2

BR13

BR13

3KOhm

3KOhm

1%

1%

1 2

BR14

BR14

1KOhm

1KOhm

1%

1%

1 2

GND

+1.8V_DUAL

BR15

BR15

1KOhm

1KOhm

1%

1%

1 2

BR16

BR16

1KOhm

1KOhm

1%

1%

1 2

GND

+1.8V_DUAL

12

BC10

BC10

0.1UF/16V

0.1UF/16V

c0603

c0603

/X

/X

+1.8V_DUAL

12

BC12

BC12

0.1UF/16V

0.1UF/16V

c0603

c0603

/X

/X

GND

2.03G:change BR13 3.01Kohm to

3Kohm for combining component

M_DDR_COMPVOH

M_DDR_COMPVOL

12

BC11

BC11

0.1UF/16V

0.1UF/16V

c0603

c0603

/X

/X

GND

12

GND

12

GND

12

BC8

BC8

0.1UF/16V

0.1UF/16V

c0603

c0603

/X

/X

GND

M_SVREF

12

BC9

BC9

0.1UF/16V

0.1UF/16V

c0603

c0603

/X

/X

GND

BR17

BR17

1 2

20Ohm

20Ohm

BR20

BR20

1 2

20Ohm

20Ohm

3

BC6

BC6

0.1UF/16V

0.1UF/16V

c0603

c0603

/X

/X

BC7

BC7

0.1UF/16V

0.1UF/16V

c0603

c0603

/X

/X

1%

1%

1%

1%

3

GND

1 2

M_CHB_MAA[14..0](20,21)

BR18

BR18

20Ohm

20Ohm

1%

1%

M_CHB_WE#(20,21)

M_CHB_CAS#(20,21)

M_CHB_RAS#(20,21)

M_CHB_BA0(20,21)

M_CHB_BA1(20,21)

M_CHB_BA2(20,21)

M_CHB_CS#0(20,21)

M_CHB_CS#1(20,21)

M_CHB_CKE0(20,21)

M_CHB_CKE1(20,21)

M_CHB_ODT0(20,21)

M_CHB_ODT1(20,21)

M_CHB_CLK0(20)

M_CHB_CLK0#(20)

M_CHB_CLK1(20)

M_CHB_CLK1#(20)

M_CHB_CLK2(20)

M_CHB_CLK2#(20)

M_DDR_COMPXPU

M_DDR_COMPXPD

M_DDR_COMPYPU

M_DDR_COMPYPD

BR19

BR19

20Ohm

20Ohm

1%

1%

1 2

GND

M_CHB_MAA0

M_CHB_MAA1

M_CHB_MAA2

M_CHB_MAA3

M_CHB_MAA4

M_CHB_MAA5

M_CHB_MAA6

M_CHB_MAA7

M_CHB_MAA8

M_CHB_MAA9

M_CHB_MAA10

M_CHB_MAA11

M_CHB_MAA12

M_CHB_MAA13

M_CHB_MAA14

HT37/x TPC26bHT 37/x TPC26b

1

HT38/x TPC26bHT 38/x TPC26b

1

HT39/x TPC26bHT 39/x TPC26b

1

HT40/x TPC26bHT 40/x TPC26b

1

HT41/x TPC26bHT 41/x TPC26b

1

HT42/x TPC26bHT 42/x TPC26b

1

HT43/x TPC26bHT 43/x TPC26b

1

HT44/x TPC26bHT 44/x TPC26b

1

HT45/x TPC26bHT 45/x TPC26b

1

M_SVREF

M_DDR_COMPVOH

M_DDR_COMPVOL

HT46 /x

HT46 /x

1

TPC26b

TPC26b

BB17

AY17

BA17

BC16

AW15

BA15

BB15

BA14

AY15

BB14

AW18

BB13

BA13

AY29

AY13

BA27

AW29

AW26

AY19

BA18

BC12

BB27

BB30

AY27

AY31

AY12

AW12

BB11

BA11

BA29

BA30

BB29

BB31

AV31

AW31

AU27

AT27

AV32

AT32

AU29

AR29

AV29

AW27

AN33

AP32

BB2

AW42

AN32

AM31

AG32

AF32

AP21

AA39

AM21

AM6

AN3

AN2

BA40

BB40

AM10

AM8

BB19

NU1D

NU1D

SMA_B0

SMA_B1

SMA_B2

SMA_B3

SMA_B4

SMA_B5

SMA_B6