Page 1

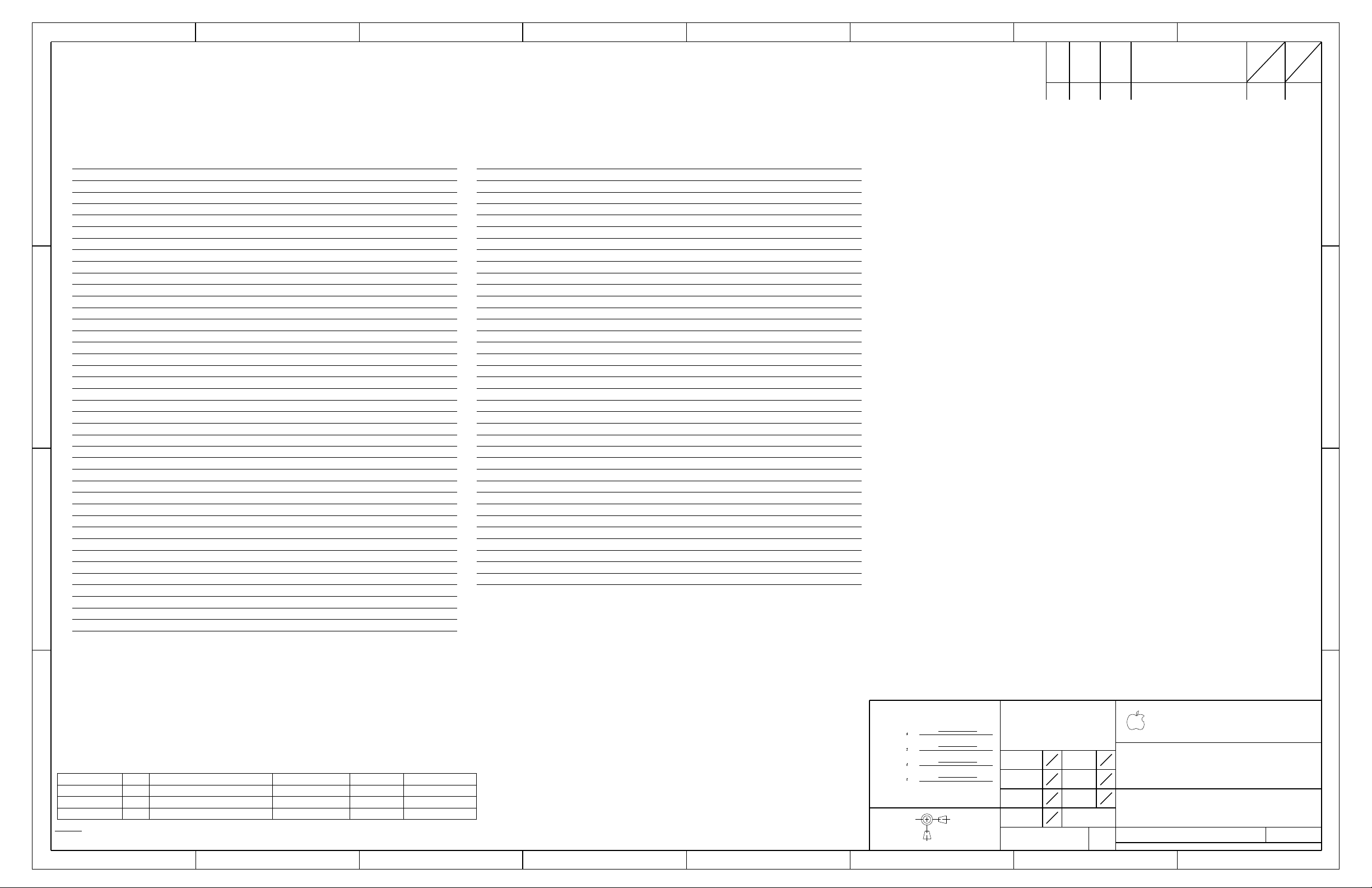

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_TABLEOFCONTENTS_ITEM

DRAWING

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEADTABLE_TABLEOFCONTENTS_HEAD

ANGLES

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

DATE

APPD

ENG

DATE

APPD

CK

ECN

ZONE

REV

DO NOT SCALE DRAWING

X.XXX

X.XX

XX

DIMENSIONS ARE IN MILLIMETERS

THIRD ANGLE PROJECTION

D

SIZE

APPLICABLE

NOTED AS

MATERIAL/FINISH

NONE

SCALE

DESIGNER

MFG APPD

DESIGN CK

RELEASE

QA APPD

ENG APPD

DRAFTER

METRIC

OF

SHT

DRAWING NUMBER

TITLE

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

Apple Computer Inc.

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

DESCRIPTION OF CHANGE

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

Pansy Build - 08/10/2005

Schematic / PCB #’s

Mullet

M1 MLB

45

(MASTER)

(MASTER)

40

FireWire Port Power

44

M42

07/26/2005

39

FIREWIRE CONTROLLER

42

(MASTER)

(MASTER)

38

Ethernet Connector

41

M42

08/04/2005

37

ETHERNET CONTROLLER

38

(MASTER)

(MASTER)

36

PATA Connector

37

(MASTER)

(MASTER)

35

Mobile Clocking

34

(MASTER)

(MASTER)

34

Clock Termination

33

M42

08/04/2005

33

CLOCKS

32

(MASTER)

(MASTER)

32

DDR2 VRef

31

(MASTER)

(MASTER)

31

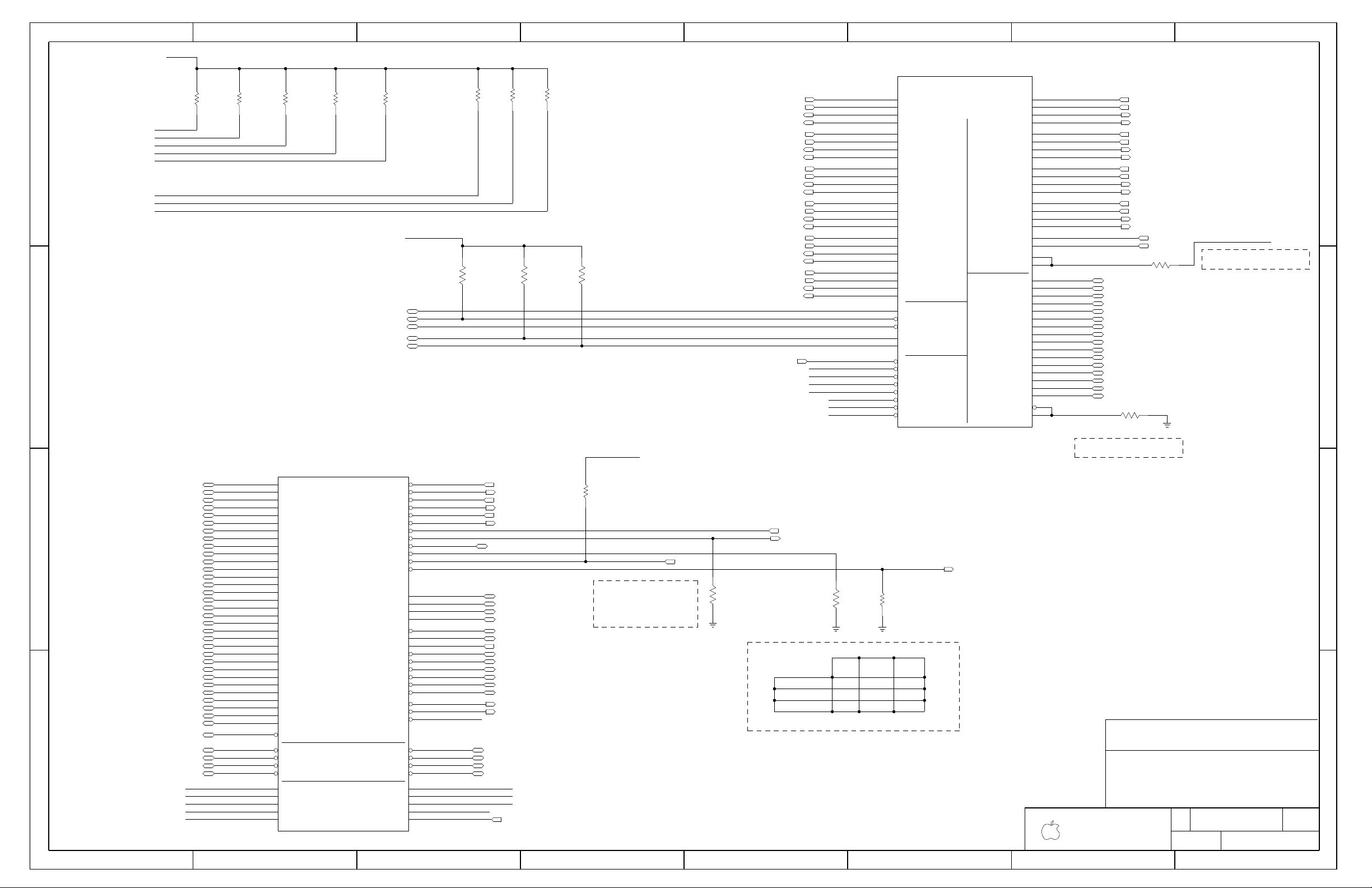

Memory Vtt Supply

30

(MASTER)

(MASTER)

30

Memory Active Termination

29

(MASTER)

(MASTER)

29

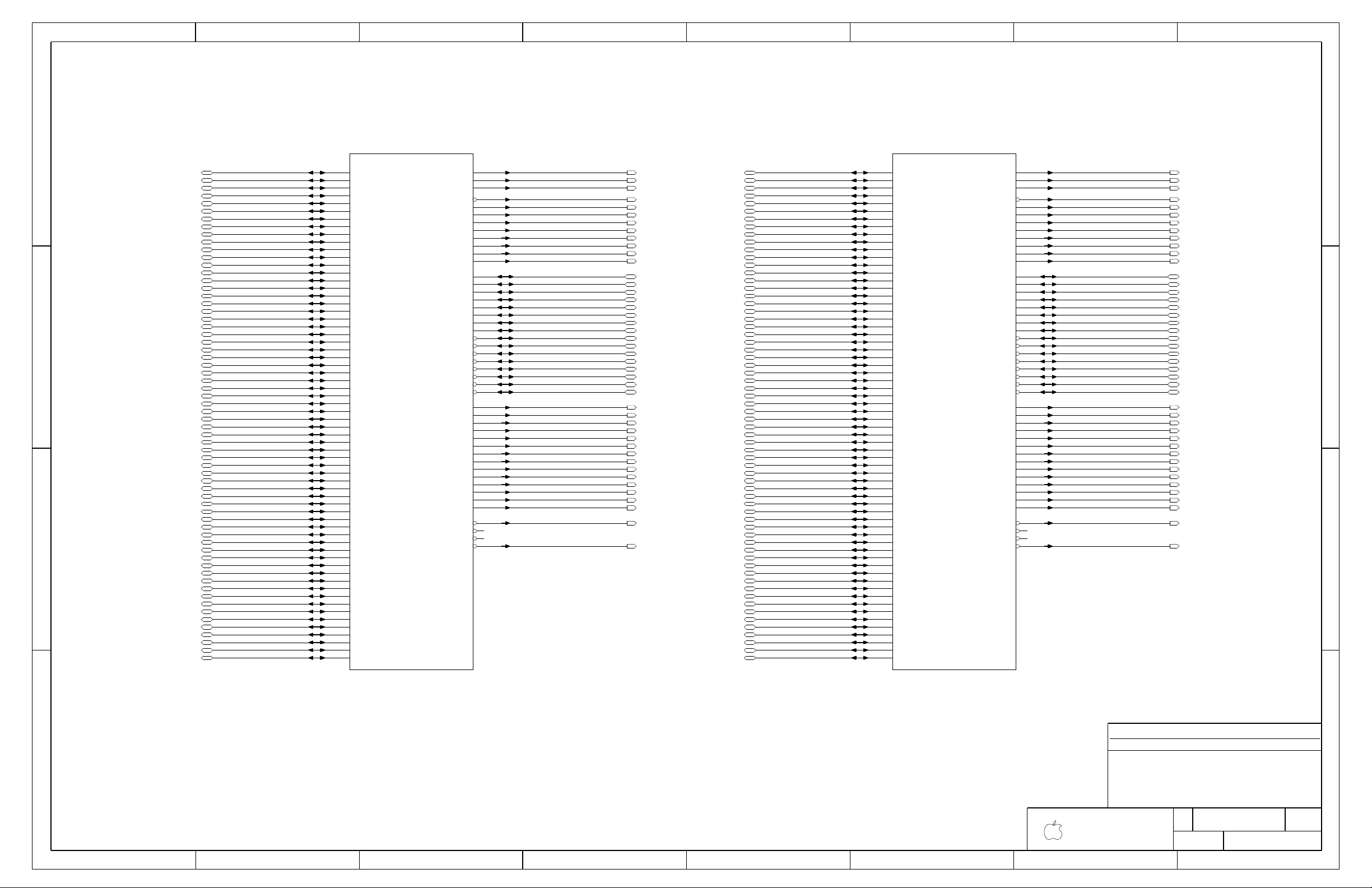

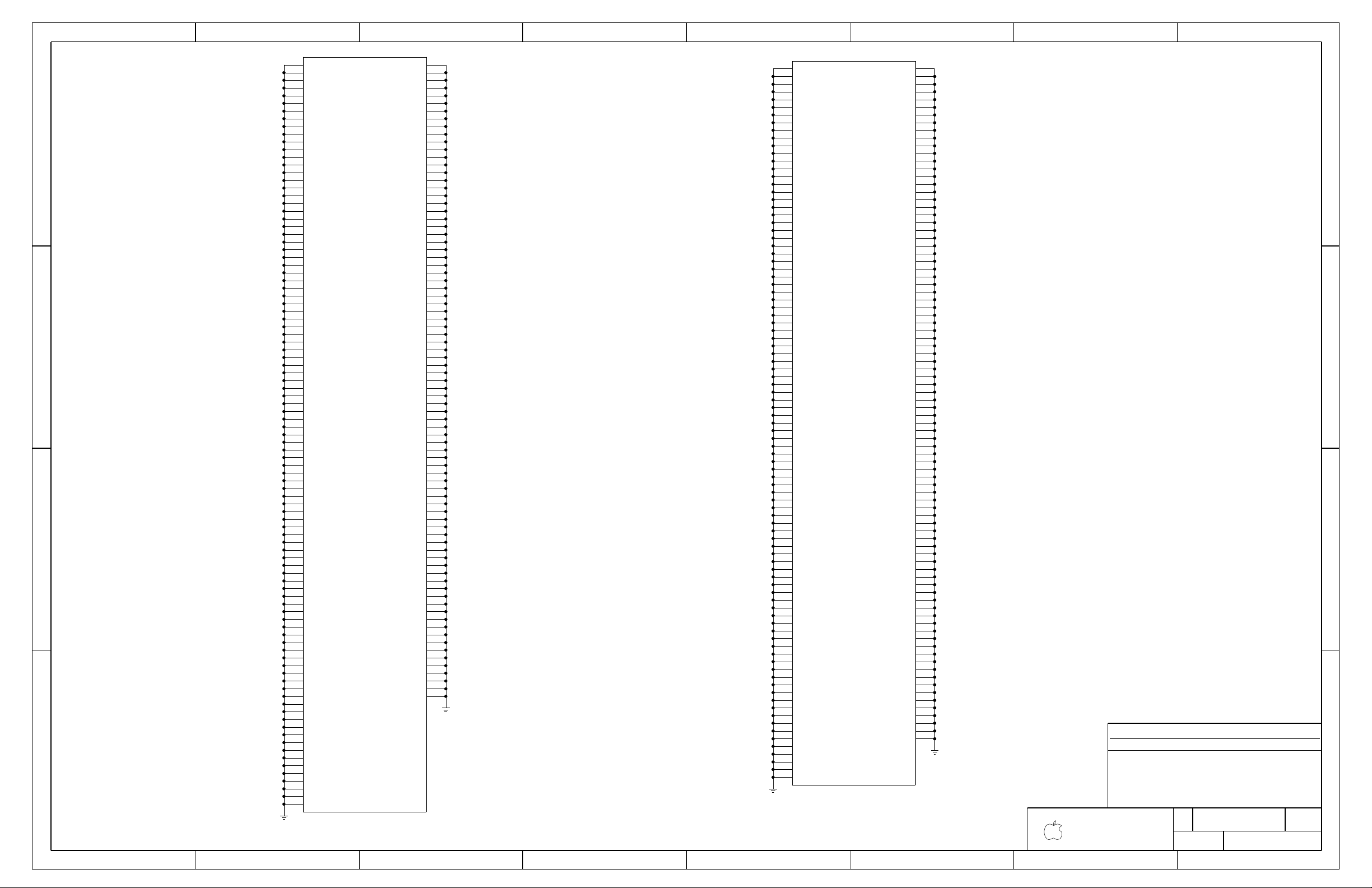

DDR2 SO-DIMM Connector B

28

(MASTER)

(MASTER)

28

DDR2 SO-DIMM Connector A

27

(MASTER)

(MASTER)

27

M1 SMBus Connections

26

(MASTER)

(MASTER)

26

SB Misc

25

M38

08/04/2005

25

24

M38

07/26/2005

24

23

M38

07/29/2005

23

22

M38

07/26/2005

22

21

M38

07/26/2005

21

20

(MASTER)

(MASTER)

20

NB Config Straps

19

(MASTER)

(MASTER)

19

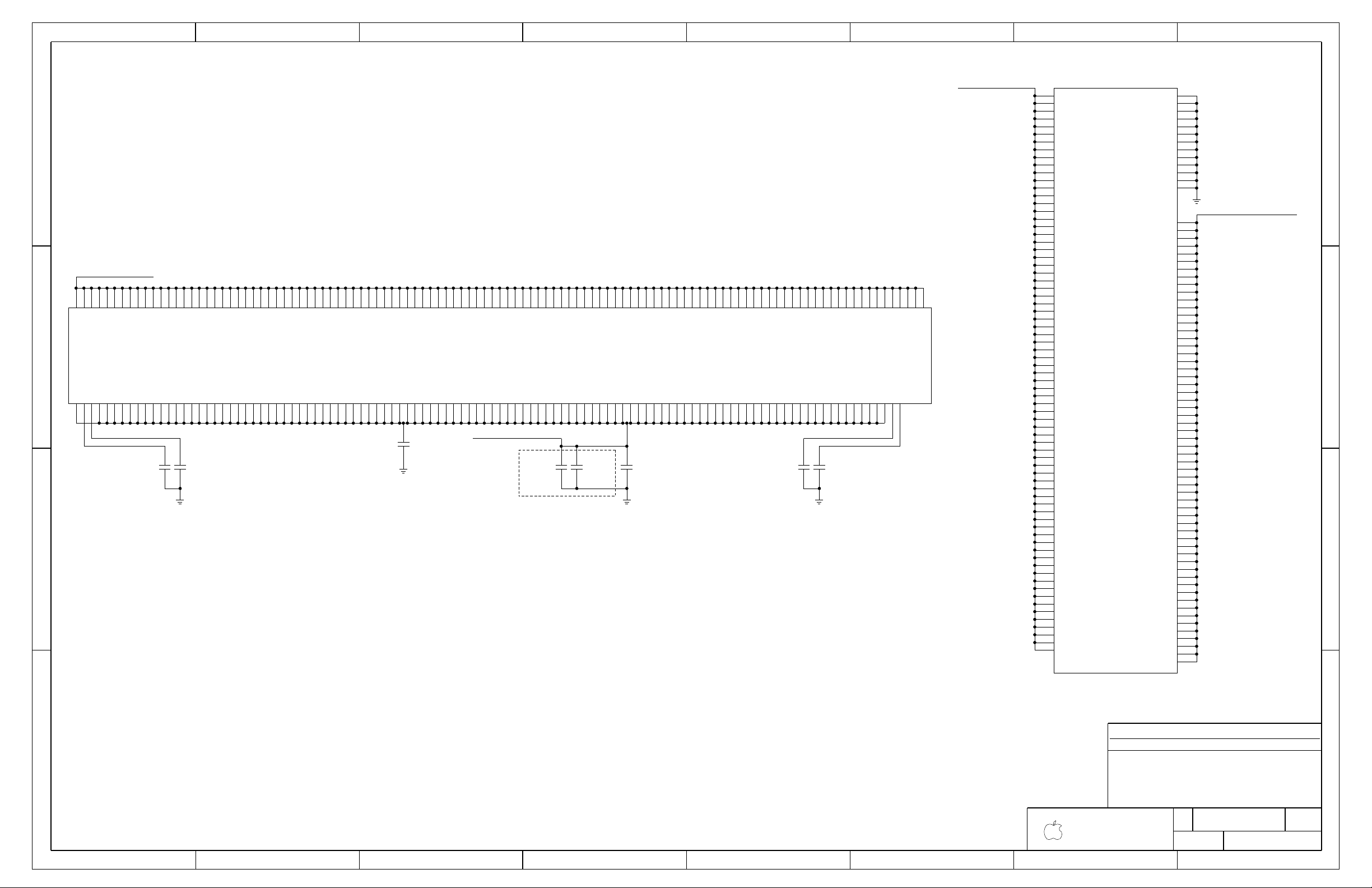

NB (GM) Decoupling

18

(MASTER)

(MASTER)

18

NB Grounds

17

(MASTER)

(MASTER)

17

NB Power 2

16

(MASTER)

(MASTER)

16

NB Power 1

15

(MASTER)

(MASTER)

15

NB DDR2 Interfaces

14

(MASTER)

(MASTER)

14

NB Misc Interfaces

13

(MASTER)

(MASTER)

13

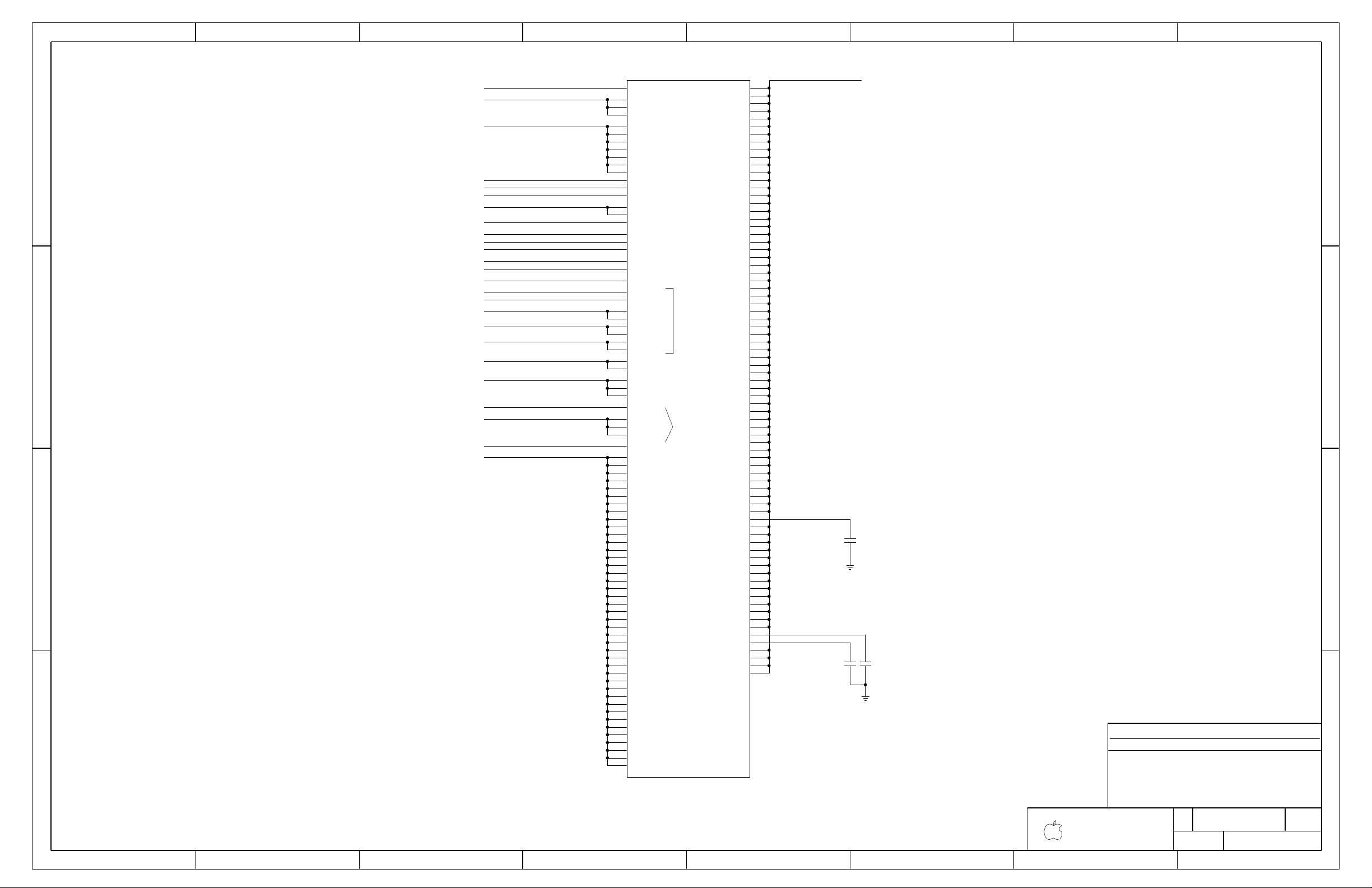

NB PEG / Video Interfaces

12

(MASTER)

(MASTER)

12

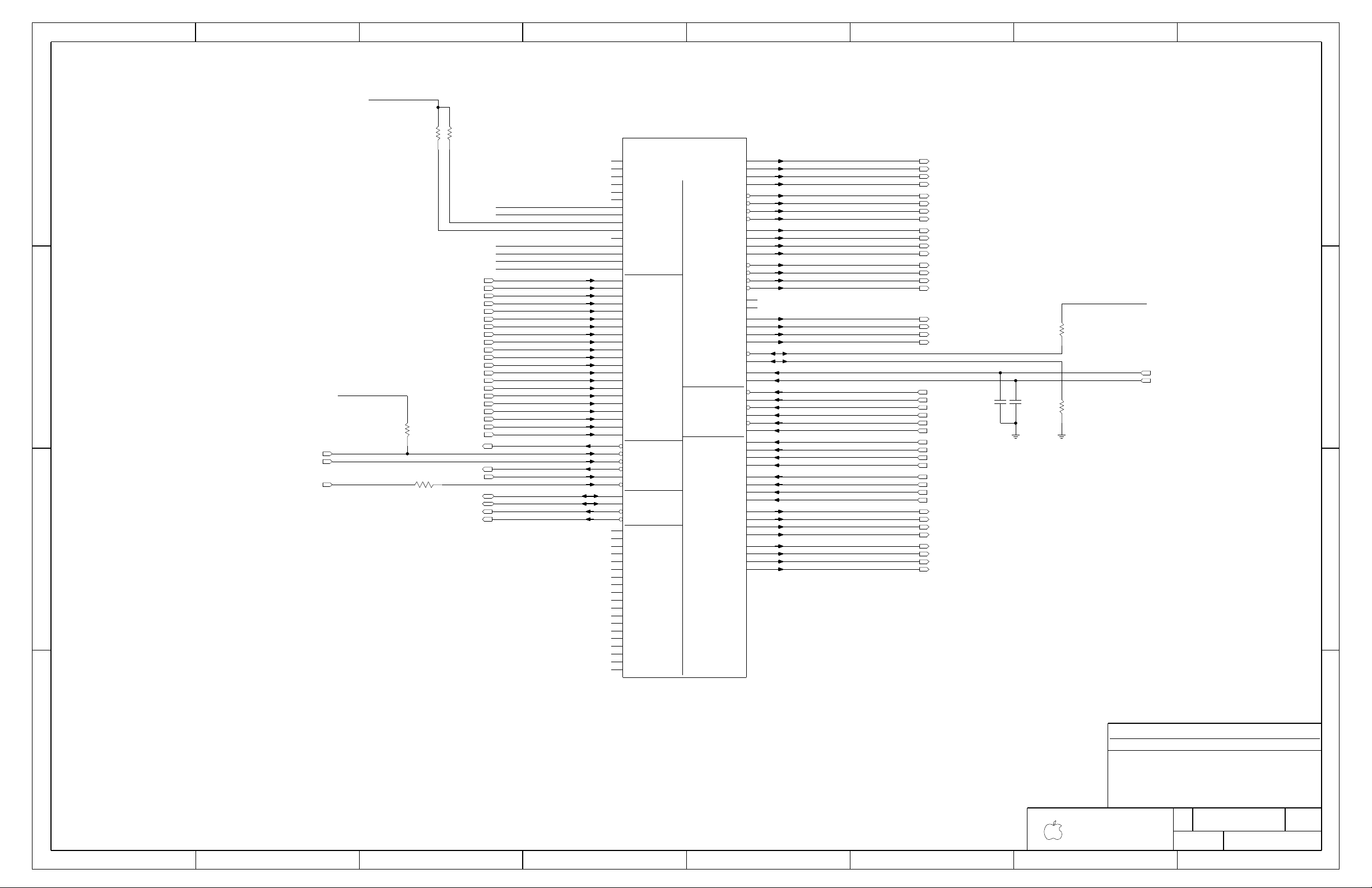

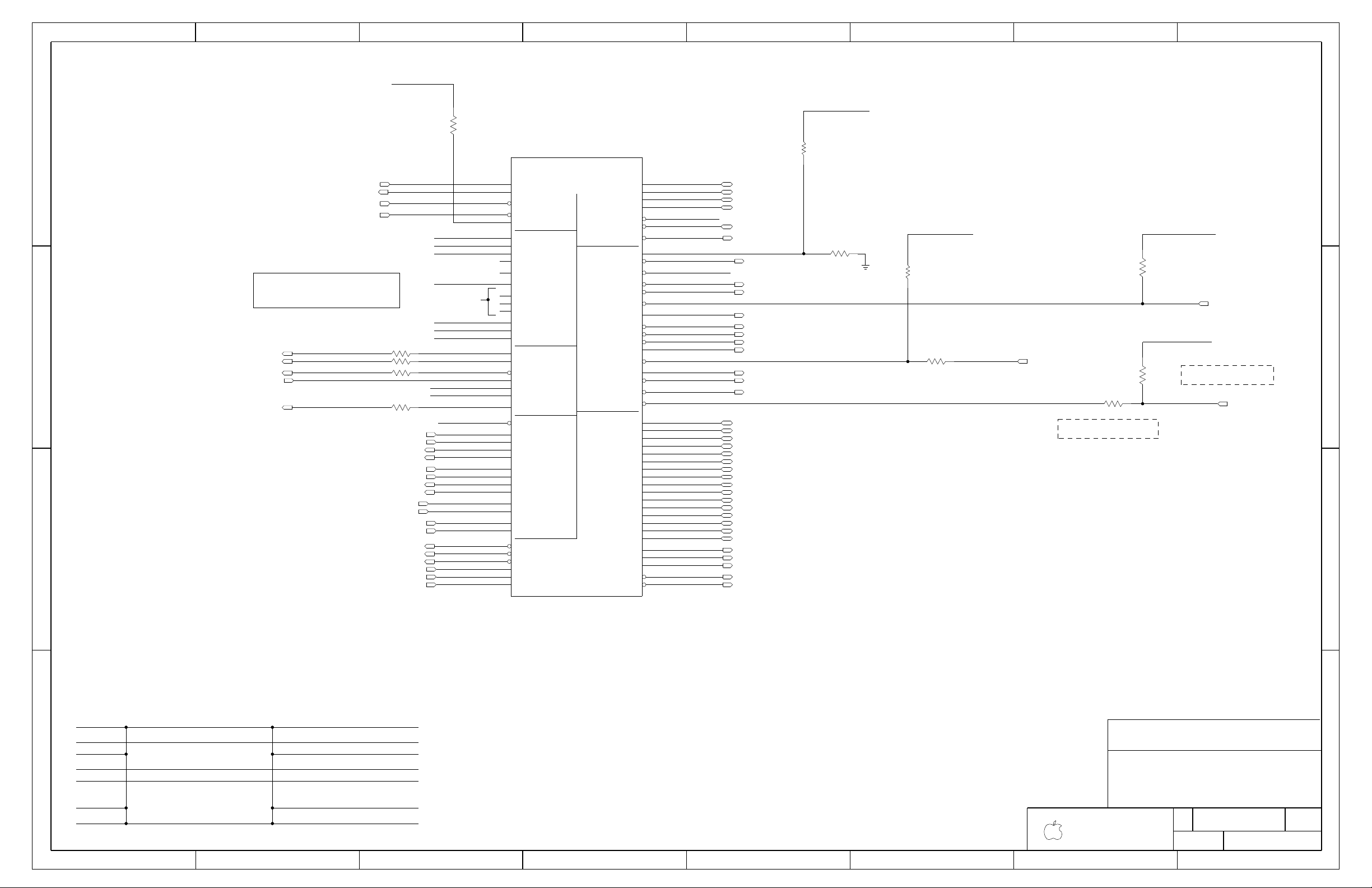

NB CPU Interface

11

M42

07/26/2005

11

CPU ITP700FLEX DEBUG

10

M42

08/04/2005

10

CPU MISC1-TEMP SENSOR

9

(MASTER)

(MASTER)

9

CPU Decoupling & VID

8

M42

07/26/2005

8

CPU 2 OF 2-PWR/GND

7

M42

07/26/2005

7

CPU 1 OF 2-FSB

6

N/A

N/A

6

Signal Aliases

5

N/A

N/A

5

Functional / ICT Test

4

N/A

N/A

4

BOM Configuration

3

N/A

N/A

3

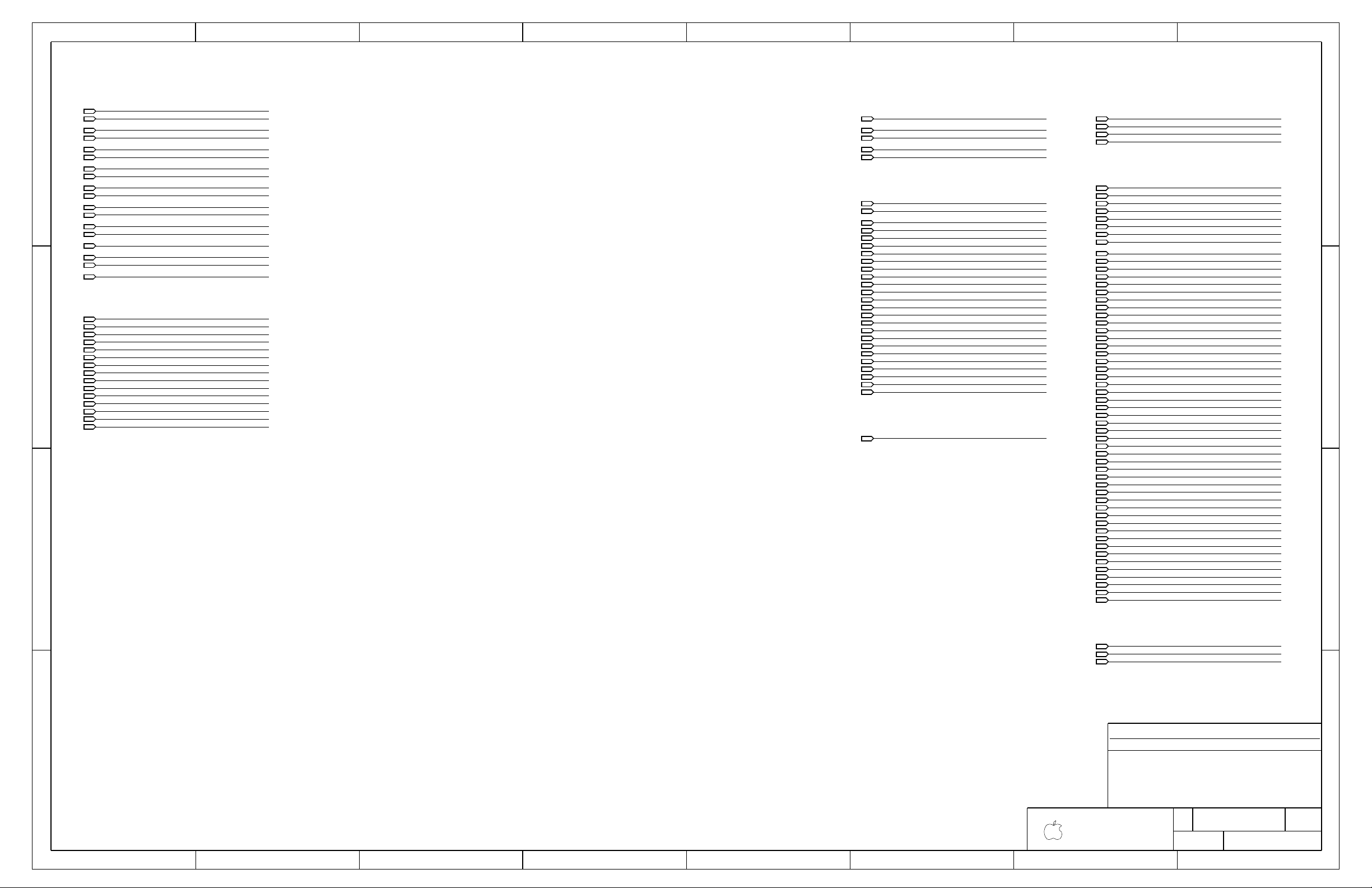

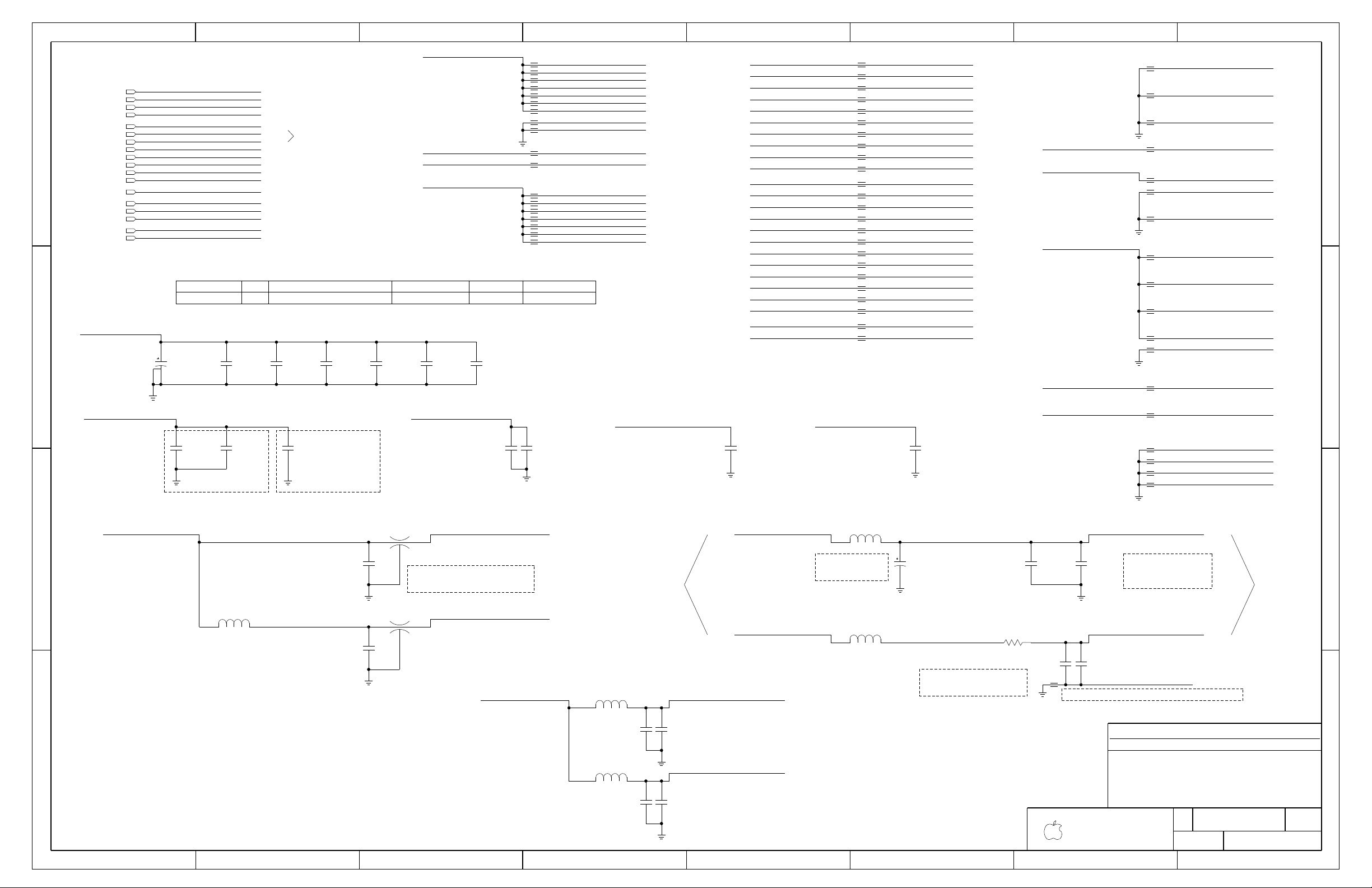

Power Block Diagram

2

N/A

N/A

2

System Block Diagram

M1 Net Properties

(MASTER)

(MASTER)

103

76

External Display Connector

(MASTER)

(MASTER)

97

75

Internal Display Connectors

(MASTER)

(MASTER)

94

74

ATI M56 Video Interfaces

(MASTER)

(MASTER)

93

73

ATI M56 GPIO/DVO/Misc

(MASTER)

(MASTER)

91

72

GDDR3 Frame Buffer B

(MASTER)

(MASTER)

90

71

GDDR3 Frame Buffer A

(MASTER)

(MASTER)

89

70

GPU Straps

(MASTER)

(MASTER)

88

69

ATI M56 Frame Buffer I/F

(MASTER)

(MASTER)

87

68

ATI M56 Core Power

(MASTER)

(MASTER)

86

67

GPU (M56) Core Supplies

(MASTER)

(MASTER)

85

66

ATI M56 PCI-E

(MASTER)

(MASTER)

84

65

S3/S0 FETs & Power Control

(MASTER)

(MASTER)

83

64

PBus-In & Battery Connectors

(MASTER)

(MASTER)

82

63

Power Aliases

(MASTER)

(MASTER)

81

62

3.3V G3Hot Supply

(MASTER)

(MASTER)

80

61

3.3V / 1.05V Power Supplies

(MASTER)

(MASTER)

79

60

1.8V Supply

(MASTER)

(MASTER)

78

59

2.5V & 1.2V Regulators

(MASTER)

(MASTER)

77

58

5V / 1.5V Power Supply

(MASTER)

(MASTER)

76

57

IMVP6 CPU VCore Regulator

(MASTER)

(MASTER)

75

56

08/04/2005

M38

67

55

SMS

07/26/2005

M42

66

54

Fan Connectors

(MASTER)

(MASTER)

65

53

ALS Support

(MASTER)

(MASTER)

64

52

SPI BOOTROM

07/26/2005

M42

63

51

Current & Voltage Sensing

(MASTER)

(MASTER)

62

50

Thermal Sensors

(MASTER)

(MASTER)

61

49

LPC+ Debug Connector

07/20/2005

M42

60

48

SMC Support

(MASTER)

(MASTER)

59

47

07/26/2005

M38

58

46

PCI-E Connections

(MASTER)

(MASTER)

57

45

Left I/O Board Connector

(MASTER)

(MASTER)

55

44

External USB Connector

(MASTER)

(MASTER)

52

43

Internal USB Connections

(MASTER)

(MASTER)

49

42

1

N/A

N/A

1

Table of Contents

TITLE=MULLET

ABBREV=DRAWING

LAST_MODIFIED=Wed Aug 10 08:42:29 2005

826-4393

1

CRITICAL

[EEE:TSQ]

LBL,P/N LABEL,PCB,28MM X 6 MM

FireWire Ports

(MASTER)

(MASTER)

46

41

SyncPage

(.csa)

Contents

Date

820-1881

PCB

1

PCBF,MULLET,M1

Page

Date

Sync

(.csa)

Contents

051-6941

SCH

1

SCHEM,MULLET,M1

SCHEM,MULLET,M1

03

1

103

08/10/05

394758ENGINEERING RELEASED

03

?

051-6941

Page 2

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

103

2

051-6941

03

SYNC_MASTER=N/A

SYNC_DATE=N/A

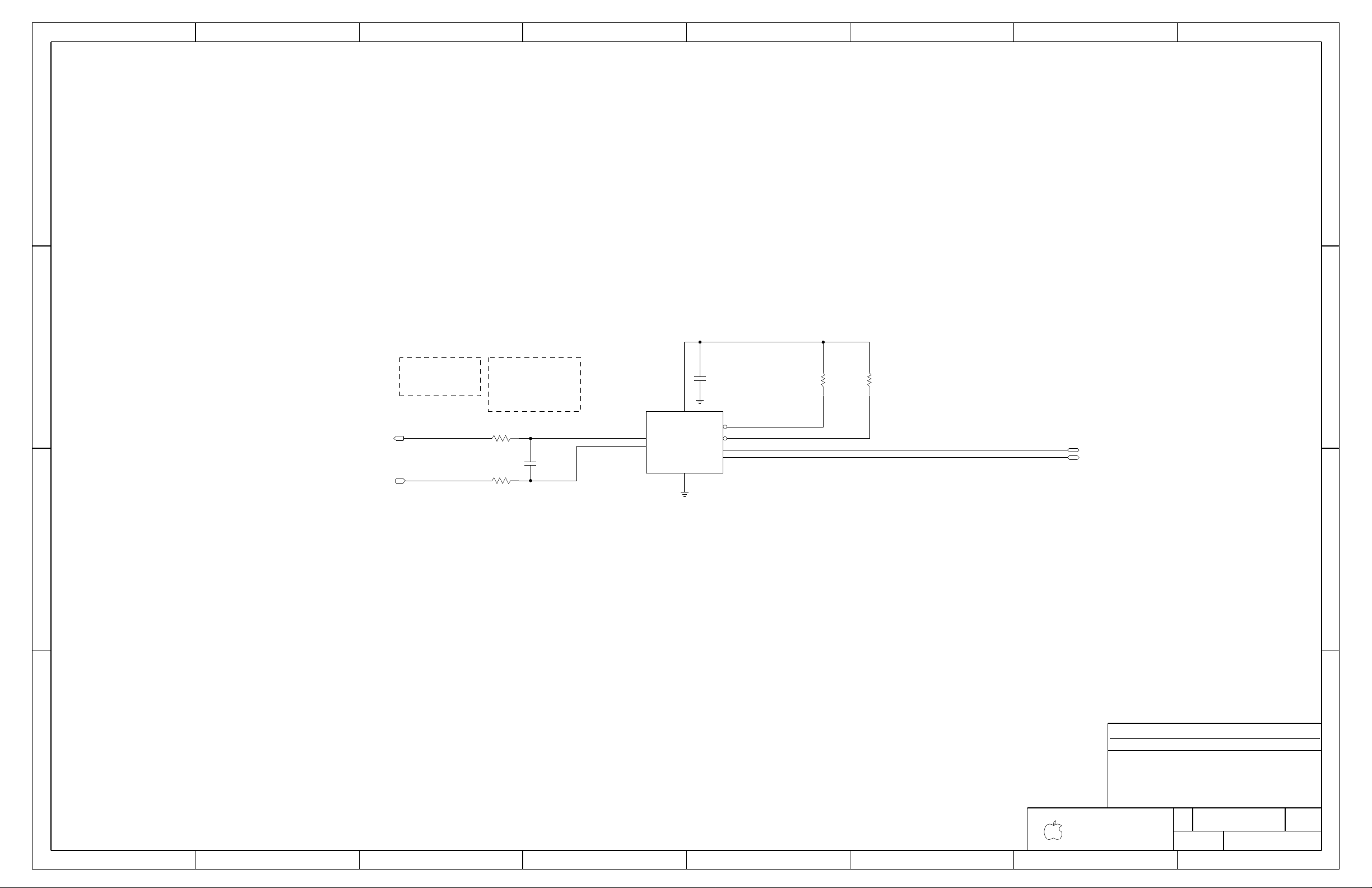

System Block Diagram

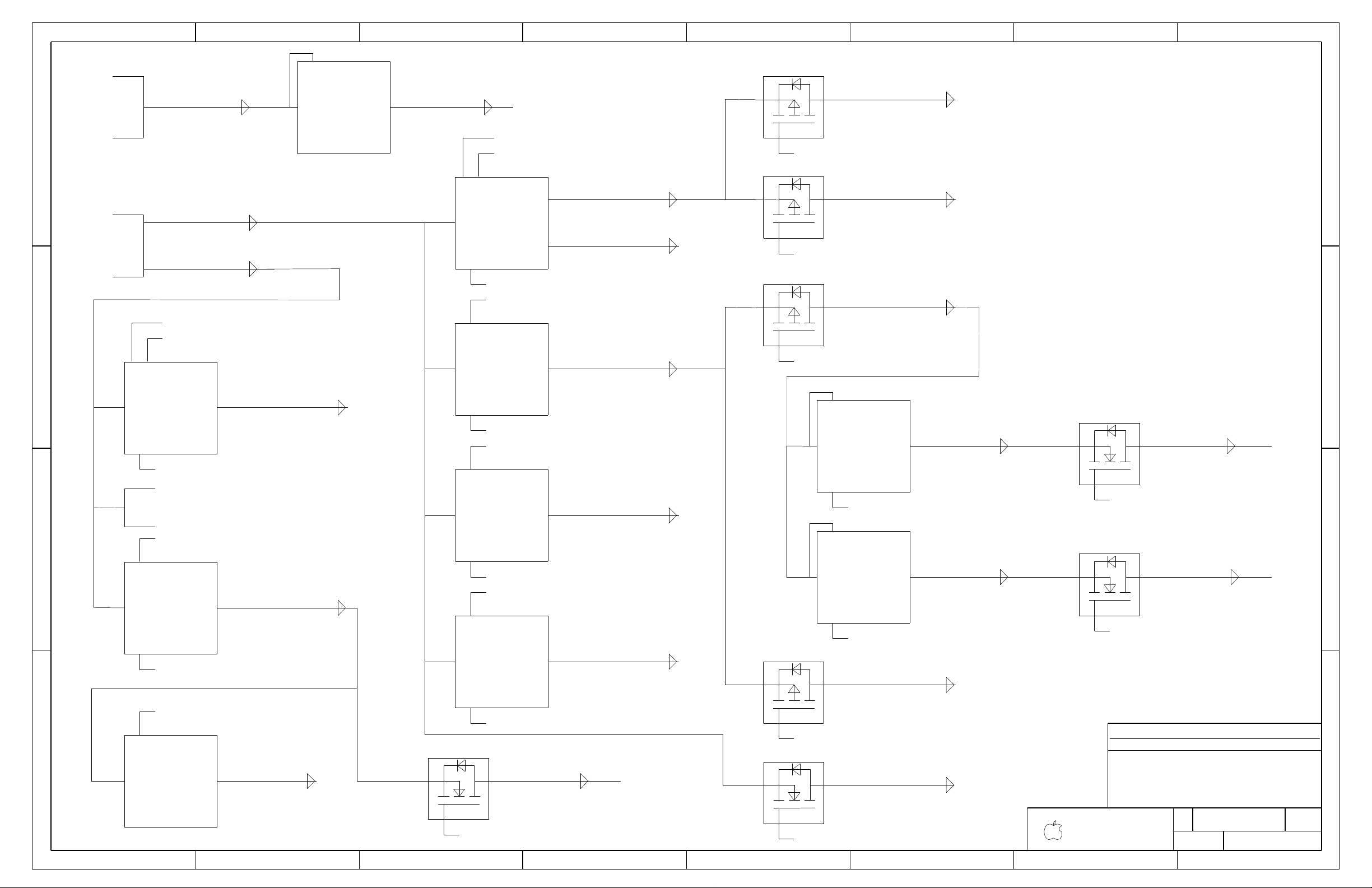

Page 3

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

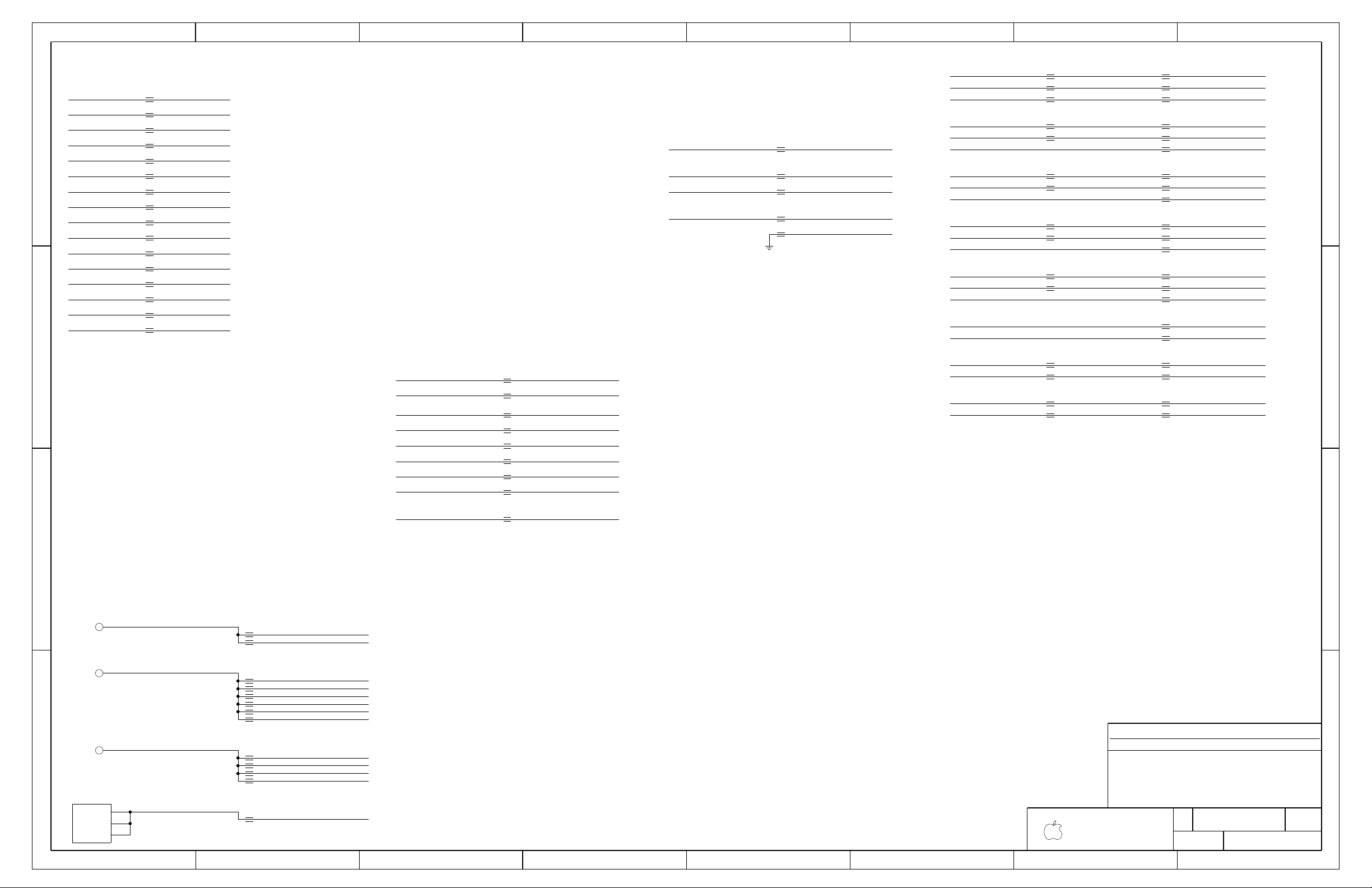

PM_SLP_S4_L

Connector

PPBUS_G3H_A

12.6V - 9V

LIO Power

Connector

LIO Flex

J8200

J5500

PPDCIN_G3H

18.5V - 9V

PPBUS_G3H_B

12.6V - 9V

ENABLE

3.425

G3Hot

(LT3470)

PP3V42_G3H

3.425V

U8000

5.0V

1.8V

PP1V8_S0

Q8325

PM_SLP_S3_LS5V_L

PM_SLP_S3_LS5V_L

1.2V

PP1V2_S0

Q8330

Q8300

PPBUS_S5_FWPORT

12.6V - 9V

Q4565

FWPWR_EN

0.9V

PP0V9_S0

(BD3533FVM)

S0

0.9V (Vtt)

U3100

PM_SLP_S3_L

PGOOD

(ISL6269)

ENABLE

S3

U7800

1.8V

NC

1.8V

PP1V8_S3

Inverter

Connector

J5500

ENABLE

ENABLE

Q8320

Q8315

Q8310

Q8305

PM_SLP_S3_LS5V_L

PM_SLP_S3_LS5V

PM_SLP_S4_LS5V

PM_SLP_S3_LS5V

PM_SLP_S4_LS5V

PM_SLP_S3_L

IMVP_PWRGD_IN/ALL_SYS_PWRGD

S0

(ISL6269)

RSMRST_PWRGD

IMVP_VR_ON

IMVP_PWRGD_IN

ENABLES

U7500

CPU VCore

(ISL6262)

S0

"IMVP6"

VR_PWRGOOD_DELAY

PGOOD

SMC_PM_G2_ENABLE

PM_SLP_S3_L

1.5V

5V

U7600

ENABLES

PGOOD

S5/S0

(LTC3728)

NC

SMC_PM_G2_ENABLE

PP5V_S5

5.0V

PP1V5_S0

PP5V_S3

5.0V

PP5V_S0

PP3V3_S3

3.3V

U7700

ENABLE

PGOOD

S3

2.5V

(LTC3411)

NC

PP2V5_S3

2.5V

PP2V5_S0

2.5V

PP1V2_S3

1.2V

U7750

ENABLE

1.2V

PGOOD

S3

(LTC3412)

NC

3.3V

ENABLE

GPU VCore

PGOOD

(ISL6269)

S0

PPVCORE_S0_GPU

1.2V - 1.0V

U7950

1.05V

PGOOD

PP1V05_S0

1.05V

PPVCORE_S0_CPU

?V

U7900

ENABLE

3.3V

S5

(ISL6269)

PGOOD

PP3V3_S5

1.5V

3.3V

NC

PP3V3_S0

U8500

PM_SLP_S3_L

5V/1.5V

SYNC_DATE=N/A

SYNC_MASTER=N/A

3

103

03

051-6941

Power Block Diagram

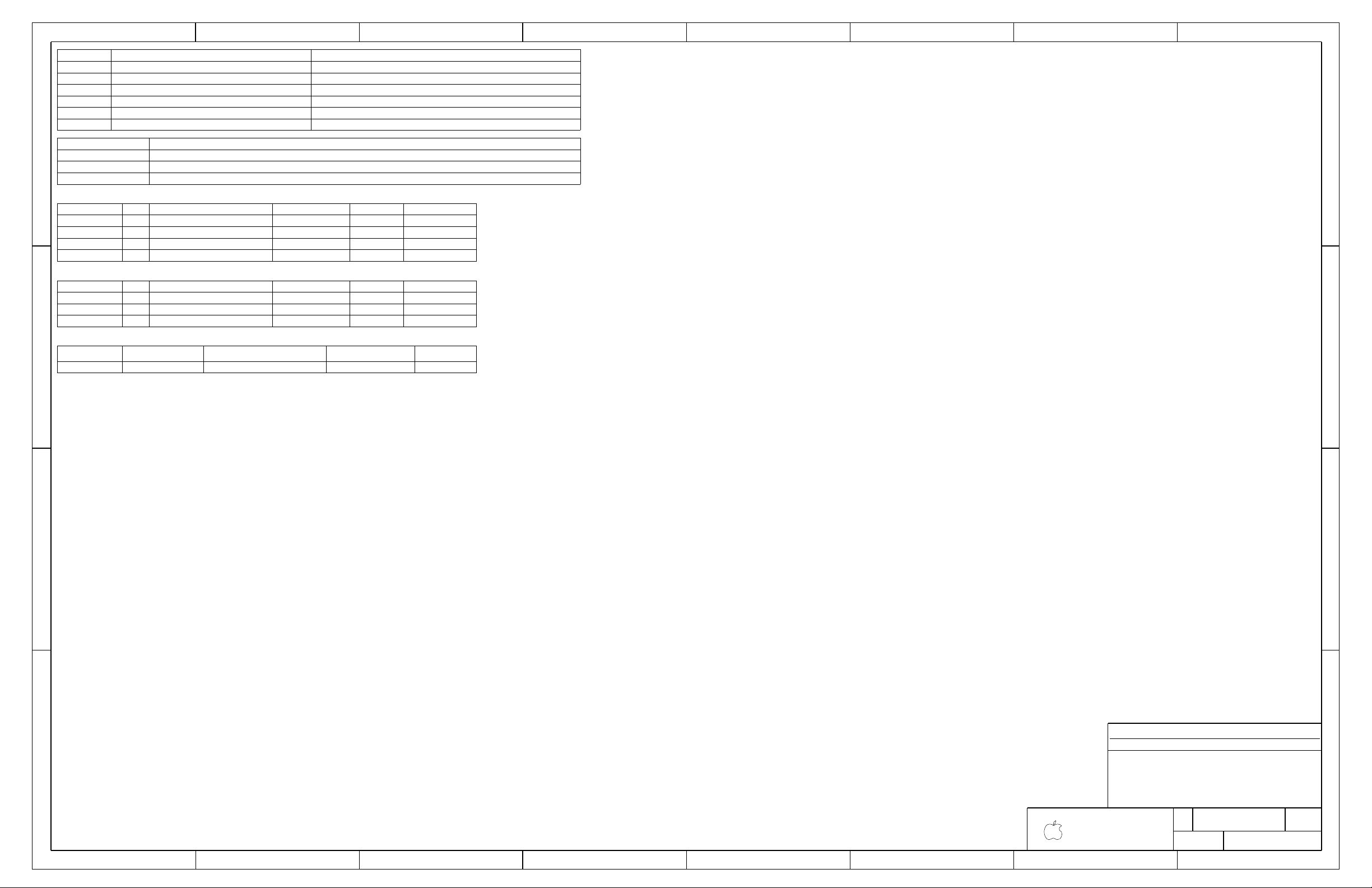

Page 4

PART NUMBER

ALTERNATE FOR

PART NUMBER

REFERENCE DESIGNATOR(S)

BOM OPTION

DESCRIPTION

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

TABLE_BOMGROUP_ITEM

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

BOM OPTIONS

BOM NAME

BOM NUMBER

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

Phantom BOM #’s

Alternate Parts

Module Parts

128S0074998-1175

470uF,2.5V,7mOhm

C0935,C0950,C0952,C0953,C0954,C1900

IC,SGRAM,GDDR3,16MX32,700MHZ,136 FBGA

VRAM_256CRITICAL

U8900,U8950,U9000,U9050

4

333S0350

IC,EEPROM,SERIAL IIC,8KBIT,SO8

U4102

LEMENU

1

CRITICAL341S1797

075-0140

1

LeMENU PTS,MULLET,M1

BOM4 075-0140

PROJ PTS,MULLET,M1

1

BOM3 075-0139075-0139

051-6941

BOM Configuration

03

103

4

SYNC_MASTER=N/A

SYNC_DATE=N/A

333S0354

IC,SGRAM,GDDR3,8MX32,700MHZ,136 FBGA4U8900,U8950,U9000,U9050

CRITICAL VRAM_128

M1_COMMON1

CAMERA_S3,CPUCORE_2PIN,GPU_BB_CTL,GPUTHM_A_GPU,INVERTER_BUF,KBDLED_HAS,LCD_CTL_GPU

075-0140

LEMENU_PTS,MULLET,M1

LEMENU

075-0139

PROJ_PTS,MULLET,M1

ALTERNATE,COMMON,M1_COMMON1,M1_COMMON2,M1_DEBUG

256,MULLET,M1

VRAM_256,GPU_MEM_256M

075-0138

VRAM_128

128,MULLET,M1

075-0137

1

128,MULLET,M1

075-0137 075-0137BOM1

PCBA,MULLET_256,M1

630-7254

075-0138,075-0139,075-0140

PCBA,MULLET_128,M1

630-7207

075-0137,075-0139,075-0140

DEVELOPMENT,ITP,LPCPLUS

M1_DEBUG

1

256,MULLET,M1

BOM2 075-0138075-0138

M1_COMMON2

MEMVREF_S3,MEMVTT_EN_PU,PLTRST_GATE_STUFF,PROTO_ONLY,USB_C_OC_PU,USB_D_OC_PU

Page 5

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

NO_TEST

CPU FSB NO_TESTs

Other Func Test Points

Power Supply NO_TESTs

NO_TEST

Left I/O Power Connector

Battery Digital Connector

Left I/O Data Connector

LPC+ Debug Connector

FUNC_TEST

FUNC_TEST

FUNC_TEST

FUNC_TEST

FUNC_TEST

Functional Test Points

Request for at least 10 GND test points

FUNC_TEST

Fan Connectors

for Functional Test points.

are not on the proper side

since these test points

FUNC_TEST property removed

051-6941

03

103

5

SYNC_MASTER=N/A

SYNC_DATE=N/A

Functional / ICT Test

=PP5V_S0_FAN_LT

TRUE

=USB2_MINI_N

SV_SET_UP

TRUE

PCIE_CLK100M_EXCARD_P

TRUE

TRUE

=PCIE_MINI_R2D_N

=SMBUS_LIO_SB_SCL

TRUE

FSB_DINV_L<3..0>

TRUE

TRUE

FSB_DRDY_L

TRUE

FSB_DSTBP_L<3..0>

TRUE

FSB_HITM_L

TRUE

FSB_LOCK_L

FSB_REQ_L<4..0>

TRUE

TRUE

ACZ_BITCLK

SMC_TMS

TRUE

LPC_AD<0>

TRUE

LPC_FRAME_L

TRUE

PM_CLKRUN_L

TRUE

BOOT_LPC_SPI_L

TRUE

DEBUG_RST_L

TRUE

TRUE

=PP1V5_S0_LIO

=PP5V_S0_LPCPLUS

TRUE

FAN_RT_TACH

FAN_RT_PWM

TRUE

ACZ_SDATAIN<0>

TRUE

ACZ_SDATAOUT

TRUE

ACZ_RST_L

TRUE

EXCARD_OC_L

LPC_AD<1>

TRUE

SMC_TX_L

TRUE

FWH_INIT_L

TRUE

PCI_CLK_PORT80_LPC

TRUE

LPC_AD<3>

TRUE

INT_SERIRQ

TRUE

PM_SUS_STAT_L

TRUE

SMC_TDI

TRUE

SMC_RST_L

TRUE

SMC_NMI

TRUE

SMC_RX_L

TRUE

TRUE

=PP1V05_S0_REG

TRUE

GND_AUDIO

TRUE

GND_AUDIO_PWR

TRUE

=PP3V42_G3H_LIO

TRUE

=PPDCIN_G3H_LIO

=PP5V_S3_LIO

TRUE

PP5V_S0_AUDIO

TRUE

TRUE

PP5V_S0_AUDIO_PWR

SMC_TRST_L

TRUE

FAN_LT_TACH

FAN_LT_PWM

=PP3V3_S5_LPCPLUS

TRUE

SMC_BC_ACOK

TRUE

SMC_BATT_CHG_EN

TRUE

SMC_MD1

TRUE

TRUE

SMC_TDO

SMC_BATT_ISET

TRUE

SMC_SYS_ISET

TRUE

LIO_BATT_ISENSE

TRUE

TRUE

LTUSB_OC_L

TRUE

LIO_DCIN_ISENSE

LIO_P3V3S3_EN

TRUE

SYS_ONEWIRE

TRUE

SMC_BATT_TRICKLE_EN_L

TRUE

MINI_CLKREQ_L

TRUE

EXCARD_CLKREQ_L

TRUE

SMC_EXCARD_CP

TRUE

LIO_PLT_RESET_L

TRUE

SMC_EXCARD_PWR_EN

TRUE

ACZ_SYNC

TRUE

=USB2_LT_P

TRUE

=USB2_LT_N

TRUE

=USB2_EXCARD_P

TRUE

=USB2_EXCARD_N

TRUE

=PCIE_EXCARD_R2D_N

TRUE

TRUE

=PCIE_EXCARD_R2D_P

TRUE

=PCIE_EXCARD_D2R_P

=USB2_MINI_P

TRUE

=PCIE_MINI_D2R_N

TRUE

PCIE_CLK100M_MINI_P

TRUE

=PCIE_MINI_D2R_P

TRUE

PCIE_CLK100M_MINI_N

TRUE

=SMBUS_LIO_SMC_SCL

TRUE

=SMBUS_LIO_SMC_SDA

TRUE

=SMBUS_LIO_SB_SDA

TRUE

PCIE_WAKE_L

TRUE

GND

TRUE

=PPBUSB_G3H_LIO_CONN

TRUE

LIO_P3V3S0_EN_L

TRUE

SMC_PS_ON

TRUE

=SMBUS_BATT_SDA

TRUE

SMC_BS_ALRT_L

TRUE

=SMBUS_BATT_SCL

TRUE

GND_BATT

TRUE

=PCIE_EXCARD_D2R_N

TRUE

=PPBUSA_G3H_LIO_CONN

TRUE

=PCIE_MINI_R2D_P

TRUE

PCIE_CLK100M_EXCARD_N

TRUE

SMC_TCK

TRUE

LPC_AD<2>

TRUE

P1V5S0_RUNSS

TRUE

P1V2S3_RUNSS

TRUE

P1V8S3_FSET

TRUE

P1V8S3_COMP

TRUE

P1V2S3_RT

TRUE

P3V3S5_COMP

TRUE

P3V3S5_FSET

TRUE

P2V5S3_SHDNRT

TRUE

TRUE

P5VS5_RUNSS

GPUBBP_ADJ

TRUE

IMVP6_RBIAS

TRUE

IMVP6_COMP

TRUE

TRUE

FSB_A_L<31..3>

TRUE

GPUVCORE_COMP

P1V05S0_FSET

TRUE

TRUE

FSB_DSTBN_L<3..0>

TRUE

FSB_HIT_L

P1V05S0_COMP

TRUE

P2V5S3_MODE

TRUE

TRUE

GPUVCORE_FSET

P3V42G3H_FB

TRUE

TRUE

FSB_BREQ0_L

FSB_D_L<63..0>

TRUE

FSB_DBSY_L

TRUE

FSB_ADSTB_L<1..0>

TRUE

FSB_ADS_L

TRUE

TRUE

FSB_BNR_L

55

55

55

48

55

55

55

55

47

55

76

76

76

76

76

76

76

48

48

48

46

48 76

76

76

47

48

48

48

48

48

48

48

48

48

62

47

47

48

47

47

47

76

44

46

63

48

48

76

76

76

76

76

76

76

76

76

62

44

48

44

45

44

12

12

12

12

12

12

44

47

46

46

39

47

48

62

62

44

44

44

44

46

47

47

48

46

46

46

47

47

48

47

60

62

62

62

48

62

46

46

48

47

46

46

50

44

50

64

46

46

44

44

46

44

46

44

44

44

44

44

45

45

45

44

45

44

45

44

44

44

44

37

63

64

44

63

47

63

45

63

45

44

47

46

64

64

64

64

12

12

12

12

12

12

12

12

12

53

6

23

34

44

27

7

7

7

7

7

7

21

46

21

21

23

22

26

44

48

53

53

21

21

21

6

21

46

21

34

21

23

23

46

46

46

46

50

44

44

44

44

44

44

44

46

53

53

48

44

44

46

46

44

44

44

6

44

44

44

44

34

34

44

26

44

21

6

6

6

6

44

44

44

6

44

34

44

34

27

27

27

23

62

44

40

27

46

27

63

44

62

44

34

46

21

57

58

59

59

58

60

60

58

57

66

56

56

7

66

60

7

7

60

58

66

61

7

7

7

7

7

7

Page 6

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

Chassis connection to be made at the mounting hole southwest of the USB connector

Chassis connection to be made at the mounting hole northwest of the DVI connector

Chassis connection to be made at the mounting hole east of the LVDS connector

NOTE: NB_CFG<13..12> require test access

USB Port "A" (Debug Port) = Right USB 2.0 Port

USB Port "B" = PCI-E Mini Card

USB Port "H" = Trackpad (Geyser)

USB Port "E" = ExpressCard

USB Port "D" = Camera

USB Port "C" = Left USB 2.0 Port

USB Port "F" = Unused

USB Port "G" = Bluetooth (M13P)

HOLE-VIA-P5RP25

1

ZT0600

HOLE-VIA-P5RP25

1

ZT0601

HOLE-VIA-P5RP25

1

ZT0602

OG-503040

SHLD-SM-LF

3

2

1

SH0600

Signal Aliases

051-6941

03

103

6

SYNC_MASTER=N/A

SYNC_DATE=N/A

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_FWPWR_PWRON

=USB_TRACKPAD_P

MAKE_BASE=TRUE

USB_TRACKPAD_P

=USB_TRACKPAD_N

USB_TRACKPAD_N

MAKE_BASE=TRUE

USB_H_P

USB_H_N

=USB_BT_N

USB_BT_N

MAKE_BASE=TRUE

=USB_BT_P

MAKE_BASE=TRUE

USB_BT_P

=USB2_EXCARD_N

MAKE_BASE=TRUE

USB2_EXCARD_N

=USB2_EXCARD_P

MAKE_BASE=TRUE

USB2_EXCARD_P

=USB2_CAMERA_N

MAKE_BASE=TRUE

USB2_CAMERA_N

=USB2_CAMERA_P

MAKE_BASE=TRUE

USB2_CAMERA_P

USB_G_P

USB_G_N

TP_USBP_F

MAKE_BASE=TRUE

USB_F_P

TP_USBN_F

MAKE_BASE=TRUE

USB_F_N

USB_E_N

EXCARD_OC_L

MAKE_BASE=TRUE

USB_E_OC_L

USB_E_P

UNUSED_USB_D_OC_L

MAKE_BASE=TRUE

USB_D_OC_L

USB_D_N

USB_D_P

=USB2_LT_N

MAKE_BASE=TRUE

USB2_LT_N

=USB2_LT_P

MAKE_BASE=TRUE

USB2_LT_P

=USB2_MINI_N

MAKE_BASE=TRUE

USB2_MINI_N

=USB2_MINI_P

MAKE_BASE=TRUE

USB2_MINI_P

=RTUSB_OC_L

MAKE_BASE=TRUE

RTUSB_OC_L

USB_C_N

LTUSB_OC_L

MAKE_BASE=TRUE

USB_C_OC_L

USB_C_P

UNUSED_USB_B_OC_L

MAKE_BASE=TRUE

USB_B_OC_L

USB_B_N

USB_B_P

USB_A_OC_L

USB_A_N

USB_A_P

=USB2_RT_N

=FWPWR_PWRON

FW_PC0

NB_CFG<11..10>

NB_CFG<6>

ENET_CTRL25

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_ENET_CTRL25

MAKE_BASE=TRUE

TP_NB_CFG<13..12>

=USB2_RT_P

USB2_RT_P

MAKE_BASE=TRUE

USB2_RT_N

MAKE_BASE=TRUE

=GND_CHASSIS_DVI2

=GND_CHASSIS_FW_PORT1

=GND_CHASSIS_FW_EMI

=GND_CHASSIS_LCD2

=GND_CHASSIS_LCD1

MIN_NECK_WIDTH=0.25 mm

MIN_LINE_WIDTH=0.5 mm

VOLTAGE=0V

MAKE_BASE=TRUE

GND_CHASSIS_INVERTER

=GND_CHASSIS_RTUSB

MAKE_BASE=TRUE

TP_NB_CFG<15..14>

MAKE_BASE=TRUE

TP_NB_CFG<11..10>

MAKE_BASE=TRUE

TP_NB_CFG<6>

MAKE_BASE=TRUE

TP_NB_CFG<17>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_MEM_A_A<15..14>

NB_CFG<15..14>

MEM_A_A<15..14>

MEM_B_A<15..14>

NB_CFG<4..3>

=GND_CHASSIS_INVERTER

MAKE_BASE=TRUE

TP_NB_CFG<8>

MAKE_BASE=TRUE

TP_NB_CFG<4..3>

=GND_CHASSIS_ENET

MIN_LINE_WIDTH=0.5 mm

VOLTAGE=0V

MAKE_BASE=TRUE

GND_CHASSIS_DVI_TOP

MIN_NECK_WIDTH=0.25 mm

=GND_CHASSIS_DVI3

=GND_CHASSIS_LCD4

=GND_CHASSIS_LCD3

MIN_NECK_WIDTH=0.25 mm

MIN_LINE_WIDTH=0.5 mm

VOLTAGE=0V

MAKE_BASE=TRUE

GND_CHASSIS_LVDS

NC_CPU_A32_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_A33_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_A34_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_A35_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_A37_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_A36_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_A38_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_A39_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_APM0_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_EXTBREF

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_APM1_L

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_HFPLL

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_SPARE0

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_SPARE2

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_SPARE1

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_CPU_SPARE4

MAKE_BASE=TRUE

NO_TEST=TRUE

TP_CPU_A32_L

TP_CPU_A33_L

TP_CPU_A34_L

TP_CPU_A35_L

TP_CPU_A37_L

TP_CPU_A36_L

TP_CPU_A38_L

TP_CPU_A39_L

TP_CPU_APM1_L

TP_CPU_EXTBREF

TP_CPU_HFPLL

TP_CPU_SPARE0

TP_CPU_SPARE2

TP_CPU_SPARE1

TP_CPU_SPARE4

NB_CFG<13..12>

NB_CFG<17>

NB_CFG<8>

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_MEM_B_A<15..14>

SUS_CLK_SB

MAKE_BASE=TRUE

TP_SB_SUS_CLK

ENET_CTRL12

NO_TEST=TRUE

MAKE_BASE=TRUE

NC_ENET_CTRL12

TP_CPU_APM0_L

=GND_CHASSIS_DVI1

=GND_CHASSIS_DVI4

GND_CHASSIS_DVI_BOT

MAKE_BASE=TRUE

VOLTAGE=0V

MIN_LINE_WIDTH=0.5 mm

MIN_NECK_WIDTH=0.25 mm

47

44

44

44

44

44

44

44

44

42

42

22

22

42

42

5

5

42

42

22

22

22

22

22

5

22

22

22

22

22

5

5

5

5

43

22

5

22

22

22

22

22

22

22

22

43

40

39

14

14

37

43

75

41

41

74

74

43

14

28

29

14

74

38

75

74

74

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

14

14

14

23

37

7

75

75

Page 7

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IN

IN

IN

IN

IN

IN

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

OUT

OUT

OUT

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

IN

IN

IN

IN

IN

IN

IN

IN

OUT

D0*

D1*

D2*

D3*

D4*

D5*

D6*

D7*

D8*

D9*

D10*

D11*

D12*

D13*

D14*

D15*

DSTBN0*

DSTBP0*

DINV0*

D17*

D16*

D18*

D19*

D20*

D22*

D21*

D23*

D25*

D24*

D28*

D27*

D26*

D29*

D30*

D31*

DSTBP1*

DINV1*

GTLREF

TEST1

TEST2

BSEL1

BSEL0

DSTBN1*

BSEL2

D32*

D33*

D34*

D35*

D36*

D37*

D38*

D39*

D40*

D41*

D42*

D43*

D44*

D46*

D45*

DSTBP2*

D47*

DSTBN2*

DINV2*

D48*

D49*

D50*

D51*

D53*

D52*

D54*

D55*

D56*

D57*

D58*

D59*

D60*

D61*

D62*

D63*

DINV3*

DSTBN3*

DSTBP3*

COMP0

COMP1

COMP3

COMP2

DPWR*

DPSLP*

DPRSTP*

PWRGOOD

SLP*

PSI*

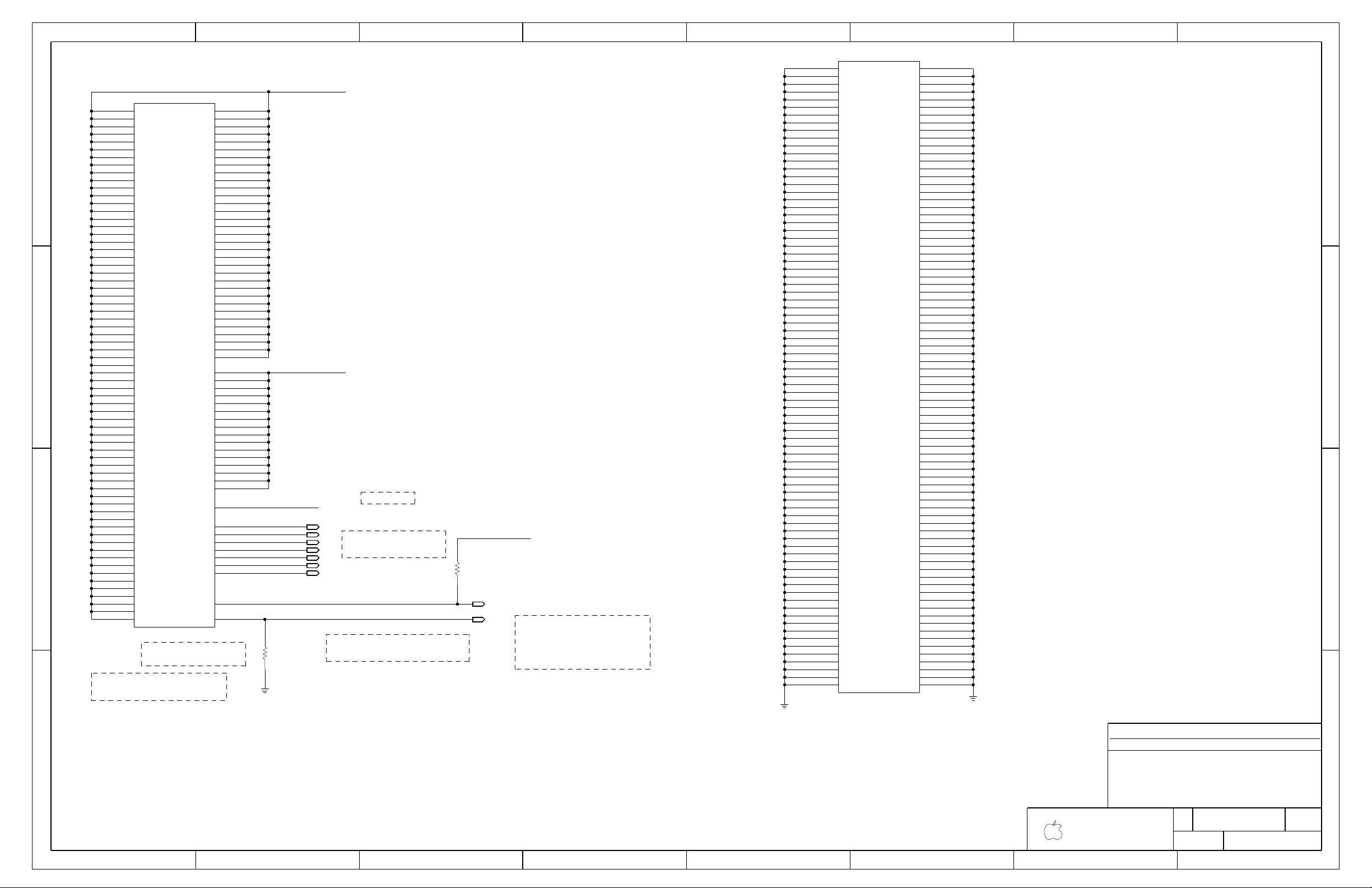

DATA GRP3

DATA GRP1

DATA GRP2

DATA GRP0

MISC

(2 OF 4)

A7*

RSVD14

RSVD15

BCLK1

BCLK0

RSVD20

RSVD17

RSVD18

RSVD19

RSVD16

RSVD13

RSVD12

THERMTRIP*

THERMDC

THERMDA

PROCHOT*

DBR*

TRST*

TMS

TDO

TDI

TCK

PREQ*

PRDY*

BPM3*

BPM1*

BPM2*

BPM0*

HITM*

HIT*

TRDY*

RS2*

RS1*

RS0*

RESET*

LOCK*

INIT*

IERR*

BR0*

DBSY*

DRDY*

DEFER*

BPRI*

BNR*

ADS*

RSVD11

RSVD6

RSVD7

RSVD8

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD9

RSVD10

SMI*

LINT0

LINT1

STPCLK*

IGNNE*

FERR*

A20M*

ADSTB1*

A30*

A31*

A27*

A28*

A29*

A26*

A25*

A24*

A22*

A23*

A21*

A20*

A19*

A18*

A17*

REQ4*

REQ3*

REQ1*

REQ0*

REQ2*

ADSTB0*

A14*

A15*

A16*

A13*

A12*

A11*

A10*

A9*

A8*

A6*

A5*

A4*

A3*

(1 OF 4)

THERM

HCLK

RESERVED

ADDR GROUP1 ADDR GROUP0

CONTROL

XDP/ITP SIGNALS

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

0.1" AWAY

ROUTE TO TP VIA AND

SPARE[7-0],HFPLL:

STUB)

WITHOUT T-ING (NO

PM_THRMTRIP#

SHOULD CONNECT TO

CPU IS HOT

AND CPU VR TO INFORM

CPU_PROCHOT_L TO SMC

COMP1,3 CONNECT WITH ZO=55OHM, MAKE

LAYOUT NOTE:

COMP0,2 CONNECT WITH ZO=27.4OHM, MAKE

TRACE LENGTH SHORTER THAN 0.5".

TRACE LENGTH SHORTER THAN 0.5".

ICH7-M AND GMCH

LAYOUT NOTE: 0.5" MAX LENGTH

PLACE TESTPOINT ON

FSB_IERR_L WITH A GND

PLACE GND VIA W/IN 1000 MILS

TCK PULL DOWN THROUGH 54.9 OHM(FOLLOW UP XDP DESIGN REFERENCE)

SO THE TDI PULL UP THROUGH 54.9 OHM,TMS PULL UP THROUGH 54.9 OHM

WE THROUGH THE ITP700FLEX CONNECTOR CONNECT TO PDB XDP BUFFER BOARD--ECM*50

CHANGE THE PULLS RESISTOR VALUE PER NAPA PLATFORM DG REV 0.9

1/16W

402

MF-LF

54.9

1%

2

1

R0702

MF-LF

402

5%

1/16W

68

2

1

R0704

1/16W

1%

402

MF-LF

1K

2

1

R0705

1/16W

1%

402

MF-LF

2.0K

2

1

R0706

54.9

402

1%

21

R0719

27.4

21

R0718

54.9

402

1%

21

R0717

402

27.4

21

R0716

0

402

NOSTUFF

21

R0730

LEMENU

CPU

YONAH

BGA

D25

C26

D7

D6

AE6

AD26

AE24

Y25

N25

G22

AD23

W24

M24

H23

D24

B5

E5

AC20

V23

M26

J26

G24

K24

E23

AF26

AF22

AF25

AE25

E25

AD21

AE21

AD24

AF23

AE22

AD20

AC25

AB21

AA21

AB22

G25

AC23

AC22

AA24

AC26

Y22

Y26

AA26

Y23

W22

AB25

F23

U22

U25

U23

W25

V26

V24

AB24

AA23

N24

T25

H22

L26

R24

T24

P23

P22

P25

M23

L23

L22

L25

E26

R23

P26

K25

N22

H25

K22

F26

H26

J23

J24

F24

E22

V1

U1

U26

R26

C21

B23

B22

U0700

LEMENU

YONAH

CPU

BGA

AB6

G2

AB5

C7

A25

A24

AB3

AA6

AC5

D5

A3

B2

V3

T2

N5

M4

AA3

AB2

C24

AA4

C23

D22

AF1

C1

D3

F6

D2

T22

B25

C3

AA1

G3

F4

F3

B1

L5

J3

K2

H2

K3

D21

AC1

AC2

H4

B4

C6

B3

C4

D20

E4

G6

A5

F21

H5

E1

C20

F1

G5

AC4

AD1

AD3

AD4

E2

A21

A22

V4

L2

H1

J1

N2

M1

K5

M3

L4

Y1

W2

J4

Y4

W5

W3

T3

T5

R4

U2

Y5

U4

A6

W6

R3

U5

Y2

R1

P1

P4

L1

P2

P5

N3

U0700

NOSTUFF

1K

MF-LF

402

5%

1/16W

2

1

R0707

MF-LF

402

5%

1/16W

51

2

1

R0712

NOSTUFF

54.9

1%

1/16W

MF-LF

402

2

1

R0703

54.9

402

1%

21

R0720

1%

402

54.9

21

R0721

54.9

402

1%

21

R0722

SYNC_DATE=07/26/2005

103

051-6941

03

7

SYNC_MASTER=M42

CPU 1 OF 2-FSB

=PP1V05_S0_CPU

=PP1V05_S0_CPU

CPU_COMP<2>

XDP_BPM_L<5>

=PP1V05_S0_CPU

CPU_PROCHOT_L

XDP_TCK

XDP_TDI

XDP_BPM_L<4>

FSB_RS_L<2>

FSB_TRDY_L

FSB_HIT_L

CPU_BSEL<1>

FSB_D_L<53>

FSB_D_L<55>

FSB_D_L<54>

FSB_D_L<51>

FSB_DSTBP_L<1>

FSB_D_L<30>

CPU_BSEL<0>

CPU_GTLREF

TP_CPU_SPARE4

TP_CPU_EXTBREF

TP_CPU_APM1_L

TP_CPU_APM0_L

TP_CPU_A36_L

TP_CPU_A35_L

TP_CPU_A34_L

TP_CPU_A33_L

TP_CPU_A32_L

TP_CPU_A39_L

TP_CPU_A38_L

TP_CPU_A37_L

CPU_NMI

CPU_SMI_L

CPU_INTR

CPU_STPCLK_L

CPU_FERR_L

CPU_IGNNE_L

CPU_A20M_L

FSB_A_L<31>

FSB_ADSTB_L<1>

FSB_A_L<30>

FSB_A_L<29>

FSB_A_L<28>

FSB_A_L<26>

FSB_A_L<27>

FSB_A_L<25>

FSB_A_L<24>

FSB_A_L<23>

FSB_A_L<22>

FSB_A_L<21>

FSB_A_L<20>

FSB_A_L<19>

FSB_A_L<18>

FSB_A_L<17>

FSB_DPWR_L

CPU_COMP<3>

FSB_D_L<61>

XDP_TMS

XDP_DBRESET_L

TP_CPU_SPARE0

PM_THRMTRIP_L

CPU_THERMD_N

CPU_THERMD_P

XDP_BPM_L<0>

FSB_HITM_L

XDP_TRST_L

XDP_BPM_L<1>

FSB_IERR_L

CPU_INIT_L

XDP_BPM_L<2>

FSB_CLK_CPU_N

TP_CPU_SPARE1

TP_CPU_SPARE2

TP_CPU_SPARE7

TP_CPU_SPARE5

TP_CPU_SPARE6

TP_CPU_SPARE3

FSB_ADS_L

FSB_BNR_L

FSB_DEFER_L

FSB_BPRI_L

FSB_DBSY_L

FSB_LOCK_L

FSB_BREQ0_L

FSB_CPURST_L

FSB_RS_L<1>

XDP_BPM_L<3>

XDP_TDO

FSB_CLK_CPU_P

FSB_D_L<15>

FSB_D_L<14>

FSB_D_L<13>

FSB_D_L<12>

FSB_D_L<11>

FSB_D_L<10>

FSB_D_L<9>

FSB_D_L<8>

FSB_D_L<7>

FSB_D_L<6>

FSB_D_L<5>

FSB_D_L<4>

FSB_D_L<3>

FSB_D_L<2>

FSB_D_L<1>

FSB_D_L<0>

FSB_D_L<31>

FSB_D_L<29>

FSB_D_L<28>

FSB_D_L<27>

FSB_D_L<26>

FSB_D_L<25>

FSB_D_L<24>

FSB_D_L<23>

FSB_D_L<22>

FSB_D_L<21>

FSB_D_L<20>

FSB_D_L<19>

FSB_D_L<18>

FSB_D_L<17>

FSB_D_L<16>

CPU_PSI_L

FSB_SLPCPU_L

CPU_DPSLP_L

CPU_DPRSTP_L

FSB_DINV_L<3>

FSB_DSTBP_L<3>

FSB_DSTBN_L<3>

FSB_D_L<63>

FSB_D_L<62>

FSB_D_L<60>

FSB_D_L<59>

FSB_D_L<58>

FSB_D_L<50>

FSB_D_L<48>

FSB_DSTBN_L<2>

FSB_D_L<46>

FSB_D_L<45>

FSB_D_L<44>

FSB_D_L<43>

FSB_D_L<42>

FSB_A_L<7>

FSB_REQ_L<4>

FSB_REQ_L<3>

FSB_REQ_L<1>

FSB_REQ_L<0>

FSB_REQ_L<2>

FSB_ADSTB_L<0>

FSB_A_L<14>

FSB_A_L<15>

FSB_A_L<16>

FSB_A_L<13>

FSB_A_L<12>

FSB_A_L<11>

FSB_A_L<10>

FSB_A_L<9>

FSB_A_L<8>

FSB_A_L<6>

FSB_A_L<5>

FSB_A_L<4>

FSB_A_L<3>

=PP1V05_S0_CPU

FSB_DSTBN_L<0>

FSB_DSTBP_L<0>

FSB_DINV_L<0>

FSB_DINV_L<1>

FSB_DSTBN_L<1>

FSB_D_L<32>

FSB_D_L<33>

FSB_D_L<34>

FSB_D_L<35>

FSB_D_L<36>

FSB_D_L<37>

FSB_D_L<38>

FSB_D_L<39>

FSB_D_L<40>

FSB_D_L<41>

FSB_DSTBP_L<2>

FSB_D_L<47>

FSB_D_L<49>

FSB_D_L<56>

FSB_D_L<57>

FSB_DINV_L<2>

FSB_D_L<52>

CPU_COMP<1>

CPU_COMP<0>

CPU_PWRGD

FSB_DRDY_L

FSB_RS_L<0>

TP_CPU_HFPLL

CPU_BSEL<2>

CPU_TEST2

CPU_TEST1

XDP_TMS

XDP_TDI

XDP_TCK

62

62

62

62

11

11

11

76

11

9

9

9

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

47

76

76

76

76

76

76

47

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

9

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

8

8

76

8

11

11

76

76

76

12

12

12

12

12

12

12

76

76

76

76

76

76

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

76

12

11

26

21

76

12

76

76

76

12

12

76

76

12

12

12

12

76

76

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

76

56

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

8

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

76

12

76

11

11

11

7

7

76

11

7

47

7

7

11

12

12

5

34

5

5

5

5

5

5

34

76

6

6

6

6

6

6

6

6

6

6

6

6

21

21

21

21

21

21

21

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

12

76

5

7

11

6

14

10

10

11

5

11

11

76

21

11

34

6

6

5

5

12

12

5

5

5

11

12

11

11

34

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

56

12

21

21

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

7

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

76

76

21

5

12

6

34

7

7

7

Page 8

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

VCC_67

VCC_64

VCC_66

VCC_65

VCC_63

VCC_62

VCC_61

VCC_59

VCC_60

VCC_58

VCC_57

VCC_56

VCC_54

VCC_55

VCC_53

VCC_51

VCC_52

VCC_49

VCC_50

VCC_48

VCC_47

VCC_46

VCC_44

VCC_45

VCC_43

VCC_41

VCC_42

VCC_40

VCC_39

VCC_38

VCC_36

VCC_37

VCC_33

VCC_35

VCC_34

VCC_31

VCC_32

VCC_29

VCC_30

VCC_28

VCC_26

VCC_27

VCC_23

VCC_25

VCC_24

VCC_22

VCC_21

VCC_20

VCC_18

VCC_19

VCC_17

VCC_16

VCC_15

VCC_13

VCC_14

VCC_12

VCC_10

VCC_11

VCC_8

VCC_9

VCC_7

VCC_6

VCC_5

VCC_3

VCC_4

VCC_2

VCC_1 VCC_68

VCC_69

VCC_71

VCC_70

VCC_72

VCC_74

VCC_76

VCC_75

VCC_78

VCC_77

VCC_79

VCC_81

VCC_80

VCC_84

VCC_82

VCC_83

VCC_86

VCC_85

VCC_87

VCC_89

VCC_88

VCC_90

VCC_91

VCC_92

VCC_94

VCC_93

VCC_95

VCC_96

VCC_97

VCC_99

VCC_98

VCC_100

VCCP_1

VCCP_2

VCCP_3

VCCP_4

VCCP_5

VCCP_6

VCCP_7

VCCP_9

VCCP_8

VCCP_11

VCCP_10

VCCP_12

VCCP_13

VCCP_14

VCCP_16

VCCP_15

VCCA

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VSSSENSE

VCCSENSE

VCC_73

(3 OF 4)

VSS_82

VSS_83

VSS_84

VSS_85

VSS_87

VSS_86

VSS_88

VSS_89

VSS_90

VSS_92

VSS_91

VSS_93

VSS_94

VSS_95

VSS_97

VSS_96

VSS_100

VSS_98

VSS_99

VSS_102

VSS_101

VSS_105

VSS_103

VSS_104

VSS_106

VSS_107

VSS_110

VSS_109

VSS_108

VSS_111

VSS_112

VSS_115

VSS_114

VSS_113

VSS_116

VSS_117

VSS_118

VSS_120

VSS_119

VSS_123

VSS_121

VSS_122

VSS_124

VSS_125

VSS_128

VSS_126

VSS_127

VSS_129

VSS_130

VSS_133

VSS_131

VSS_132

VSS_134

VSS_135

VSS_138

VSS_136

VSS_137

VSS_139

VSS_140

VSS_141

VSS_143

VSS_142

VSS_146

VSS_144

VSS_145

VSS_147

VSS_148

VSS_151

VSS_150

VSS_149

VSS_152

VSS_153

VSS_156

VSS_155

VSS_154

VSS_157

VSS_158

VSS_159

VSS_161

VSS_160

VSS_162

VSS_1

VSS_2

VSS_3

VSS_5

VSS_4

VSS_6

VSS_7

VSS_8

VSS_10

VSS_9

VSS_11

VSS_12

VSS_15

VSS_13

VSS_14

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_23

VSS_22

VSS_21

VSS_24

VSS_25

VSS_28

VSS_27

VSS_26

VSS_29

VSS_30

VSS_33

VSS_32

VSS_31

VSS_34

VSS_35

VSS_38

VSS_37

VSS_36

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_46

VSS_44

VSS_45

VSS_47

VSS_48

VSS_51

VSS_49

VSS_50

VSS_52

VSS_53

VSS_56

VSS_54

VSS_55

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_63

VSS_62

VSS_64

VSS_65

VSS_66

VSS_69

VSS_68

VSS_67

VSS_70

VSS_71

VSS_74

VSS_73

VSS_72

VSS_75

VSS_76

VSS_79

VSS_78

VSS_77

VSS_80

VSS_81

(4 OF 4)

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

VCCA=1.5 ONLY

LAYOUT NOTE: CONNECT R0803

PULL-DOWN

IF NO USE, NEED PULL-UP OR

VID FOR CPU POWER SUPPLY

TRANSMISSION LINE

RESISTORS TERMINATE THE 55 OHM

LAYOUT NOTE:

(CPU CORE POWER)

(CPU IO POWER 1.05V)

(CPU INTERNAL PLL POWER 1.5V)

STUB.

LAYOUT NOTE:

VCCSENSE AND VSSSENSE LINES

SHOULD BE OF EQUAL LENGTH

LOCATION WHERE THE TWO 54.9 OHM

BETWEEN VCCSENSE AND VSSSENSE AT THE

TO CONNECT A DIFFERENCTIAL PROBE

PROVIDE A TEST POINT (WITH NO STUB)

LAYOUT NOTE:

TO TP_VSSSENSE WITH NO

CPU_VCCSENSE_P/CPU_VCCSENSE_P USE

ZO=27.4 OHM DIFFERNTIAL TRACE ROUTING.

76

9

76

9

76

9

76

9

76

9

76

9

1/16W

1%

402

MF-LF

100

2

1

R0803

76

9

76 56

76 56

100

MF-LF

402

1%

1/16W

2

1

R0802

LEMENU

YONAH

CPU

BGA

AE7

AE2

AF2

AE3

AF4

AE5

AF5

AD6

AF7

N21

M21

K21

J21

M6

K6

J6

G21

W21

V21

T6

T21

R6

R21

N6

V6

B26

AF18

AF17

AF15

AF14

AF12

AF10

AF9

AE20

AE18

AE17

A20

AE15

AE13

AE12

AE10

AE9

AD18

AD17

AD15

AD14

AD12

A18

AD10

AD9

AD7

AC18

AC17

AC15

AC13

AC12

AC9

AC7

A17

AB7

AB20

AB18

AB17

AB15

AB14

AB12

AB10

AC10

AB9

A15

AA20

AA18

AA17

AA15

AA13

AA12

AA10

AA9

AA7

F20

A13

F18

F17

F15

F14

F12

F10

F9

F7

E20

E18

A12

E17

E15

E13

E12

E10

E9

E7

D18

D17

D15

A10

D14

D12

D10

D9

C18

C17

C15

C13

C12

C10

A9

C9

B20

B18

B17

B15

B14

B12

B10

B9

AF20

B7

A7

U0700

LEMENU

YONAH

CPU

BGA

V22

V5

V2

U24

U21

U6

U3

T26

T23

T4B6

T1

R25

R22

R5

R2

P24

P21

P6

P3

N26

A26

N23

N4

N1

M25

M22

M5

M2

L24

L21

L6

A23

L3

K26

K23

K4

K1

J25

J22

J5

J2

H24

A19

H21

H6

H3

G26

G23

G1

G4

F25

F22

F2

A16

F19

F16

F13

F11

F8

F5

E24

E21

E19

E16

A14

E14

E11

E8

E6

E3

D26

D23

D19

D16

D13

A11

D11

D8

D4

D1

C25

C22

C2

C19

C16

C14

A8

C11

C8

C5

AF24

AF21

AF19

B24

AF16

AF13

AF11

AF8

AF6

AF3

AE26

AE23

AE19

AE16

B21

AE14

AE11

AE8

AE4

AE1

AD25

AD22

AD19

AD16

AD13

B19

AD11

AD8

AD5

AD2

AC24

AC21

AC19

AC16

AC14

AC11

B16

AC8

AC6

AC3

AB26

AB23

AB19

AB16

AB13

AB11

AB8

B13

AB4

AB1

AA25

AA22

AA19

AA16

AA14

AA11

AA8

AA5

B11

AA2

Y24

Y21

Y6

Y3

W26

W23

W4

W1

V25

B8

A4

U0700

CPU 2 OF 2-PWR/GND

SYNC_MASTER=M42

051-6941

03

8

103

SYNC_DATE=07/26/2005

CPU_VID<6>

CPU_VCCSENSE_P

CPU_VCCSENSE_N

=PPVCORE_S0_CPU

CPU_VID<5>

CPU_VID<4>

CPU_VID<3>

CPU_VID<2>

CPU_VID<1>

CPU_VID<0>

=PPVCORE_S0_CPU

=PP1V05_S0_CPU

=PP1V5_S0_CPU

62

62

62

50

50

11

9

9

9

8

8

7

Page 9

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

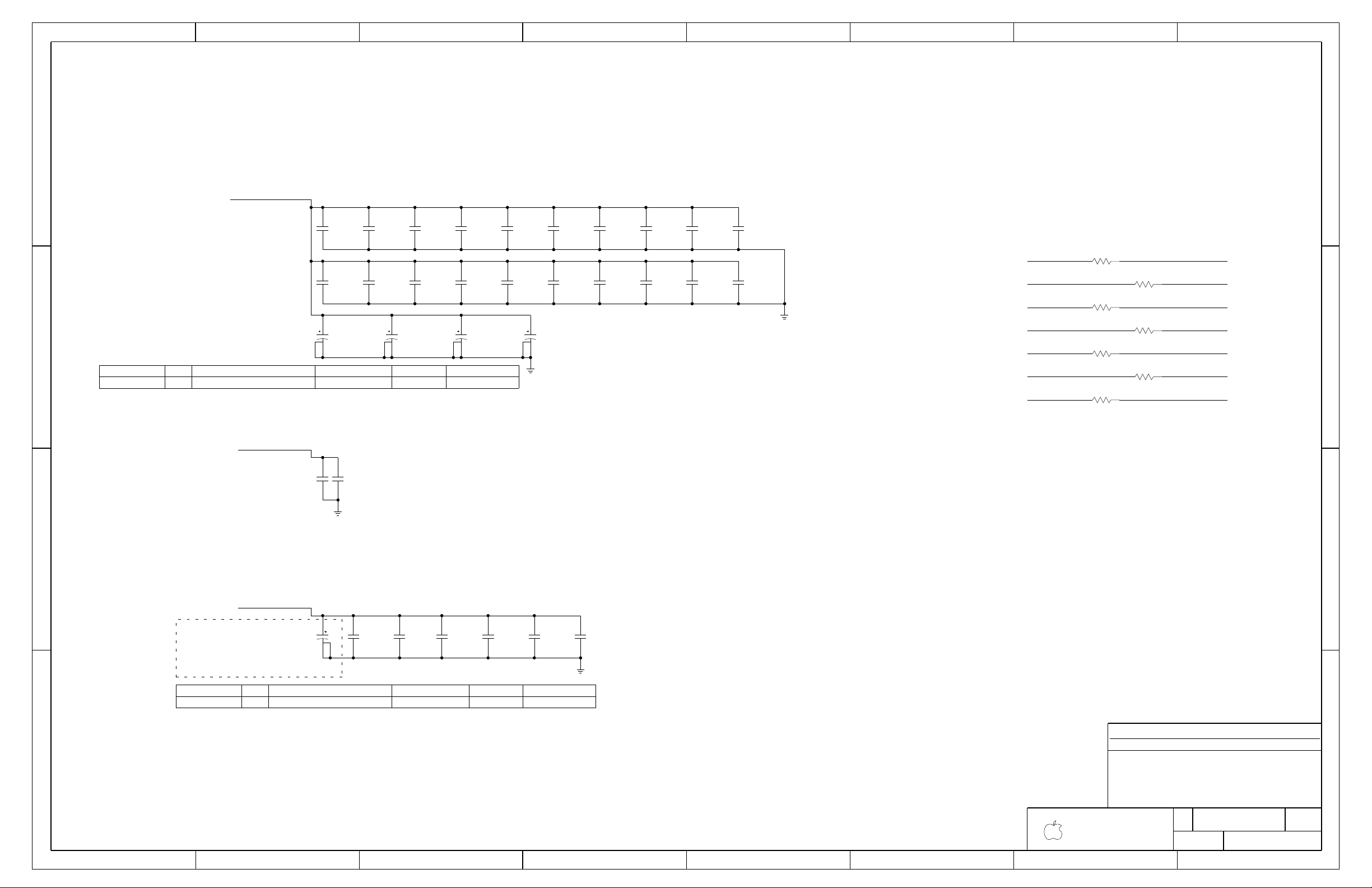

Need to make sure we can do dual-footprint for 128S0068 & 128S0074!!!

NOTE: This cap is shared

between CPU and NB

Need to make sure we can do dual-footprint for 128S0068 & 128S0074!!!

CPU VCORE HF AND BULK DECOUPLING

VCCP (CPU I/O) Decoupling

VCCA (CPU AVdd) Decoupling

Will probably be removed before production

1x 470uF, 6x 0.1uF 0402

4x 470uF. 20x 22uF 0805

Resistors to allow for override of CPU VID

CPU VCORE VID Connections

1x 10uF, 1x 0.01uF

22uF

805

X5R

20%

6.3V

2

1

C0906

805

22uF

X5R

20%

6.3V

2

1

C0904

805

22uF

X5R

20%

6.3V

2

1

C0916

805

22uF

X5R

20%

6.3V

2

1

C0914

805

22uF

X5R

20%

6.3V

2

1

C0908

805

22uF

X5R

20%

6.3V

2

1

C0903

805

22uF

X5R

20%

6.3V

2

1

C0907

805

22uF

X5R

20%

6.3V

2

1

C0902

805

22uF

X5R

20%

6.3V

2

1

C0901

805

22uF

X5R

20%

6.3V

2

1

C0913

805

22uF

X5R

20%

6.3V

2

1

C0912

805

22uF

X5R

20%

6.3V

2

1

C0911

805

22uF

X5R

20%

6.3V

2

1

C0919

805

22uF

X5R

20%

6.3V

2

1

C0900

805

22uF

X5R

20%

6.3V

2

1

C0910

10V

20%

402

CERM

0.1UF

2

1

C0936

CPUCORE_3PIN

20%

2.5V

TANT

D2T

470uF

32

1

C0935

805

22uF

X5R

20%

6.3V

2

1

C0905

805

22uF

X5R

20%

6.3V

2

1

C0909

805

22uF

X5R

20%

6.3V

2

1

C0915

805

22uF

X5R

20%

6.3V

2

1

C0917

10V

20%

402

CERM

0.1UF

2

1

C0937

10V

20%

402

CERM

0.1UF

2

1

C0938

10V

20%

402

CERM

0.1UF

2

1

C0939

10V

20%

402

CERM

0.1UF

2

1

C0940

10V

20%

402

CERM

0.1UF

2

1

C0941

805

6.3V

20%

X5R

22uF

2

1

C0918

CPUCORE_3PIN

470uF

20%

2.5V

TANT

D2T

3 2

1

C0950

470uF

D2T

TANT

2.5V

20%

CPUCORE_3PIN

3 2

1

C0952

2.5V

470uF

CPUCORE_3PIN

D2T

TANT

20%

3 2

1

C0953

D2T

TANT

2.5V

20%

470uF

CPUCORE_3PIN

3 2

1

C0954

20%

402

CERM

0.01UF

16V

2

1

C0981

603

6.3V

20%

10uF

X5R

2

1

C0980

402

MF-LF

1/16W

5%

0

21

R0996

402

MF-LF

1/16W

5%

0

21

R0995

0

5%

1/16W

MF-LF

402

21

R0993

MF-LF

0

5%

1/16W

402

21

R0994

0

5%

1/16W

MF-LF

402

21

R0991

0

5%

1/16W

MF-LF

402

21

R0992

0

5%

1/16W

MF-LF

402

21

R0990

C0950,C0952,C0953,C0954

CAP,TANT,POLY,470UF,20%,2.5V,7MOHM,D2E

4128S0074 CRITICAL

CPUCORE_2PIN

103

9

03

SYNC_MASTER=(MASTER)

SYNC_DATE=(MASTER)

051-6941

CPU Decoupling & VID

C0935

1

CAP,TANT,POLY,470UF,20%,2.5V,7MOHM,D2E

128S0074 CRITICAL

CPUCORE_2PIN

IMVP6_VID<1>

=PP1V05_S0_CPU

=PP1V5_S0_CPU

CPU_VID<6>

IMVP6_VID<4>

CPU_VID<4>

IMVP6_VID<2>

CPU_VID<2>

IMVP6_VID<0>

CPU_VID<0>

IMVP6_VID<5>

CPU_VID<5>

IMVP6_VID<3>

CPU_VID<3>

CPU_VID<1>

=PPVCORE_S0_CPU

IMVP6_VID<6>

62 11

62

8

62

76

76

76

76

76

76

76

50

56

7

8

8

56

8

56

8

56

8

56

8

56

8

8

8

56

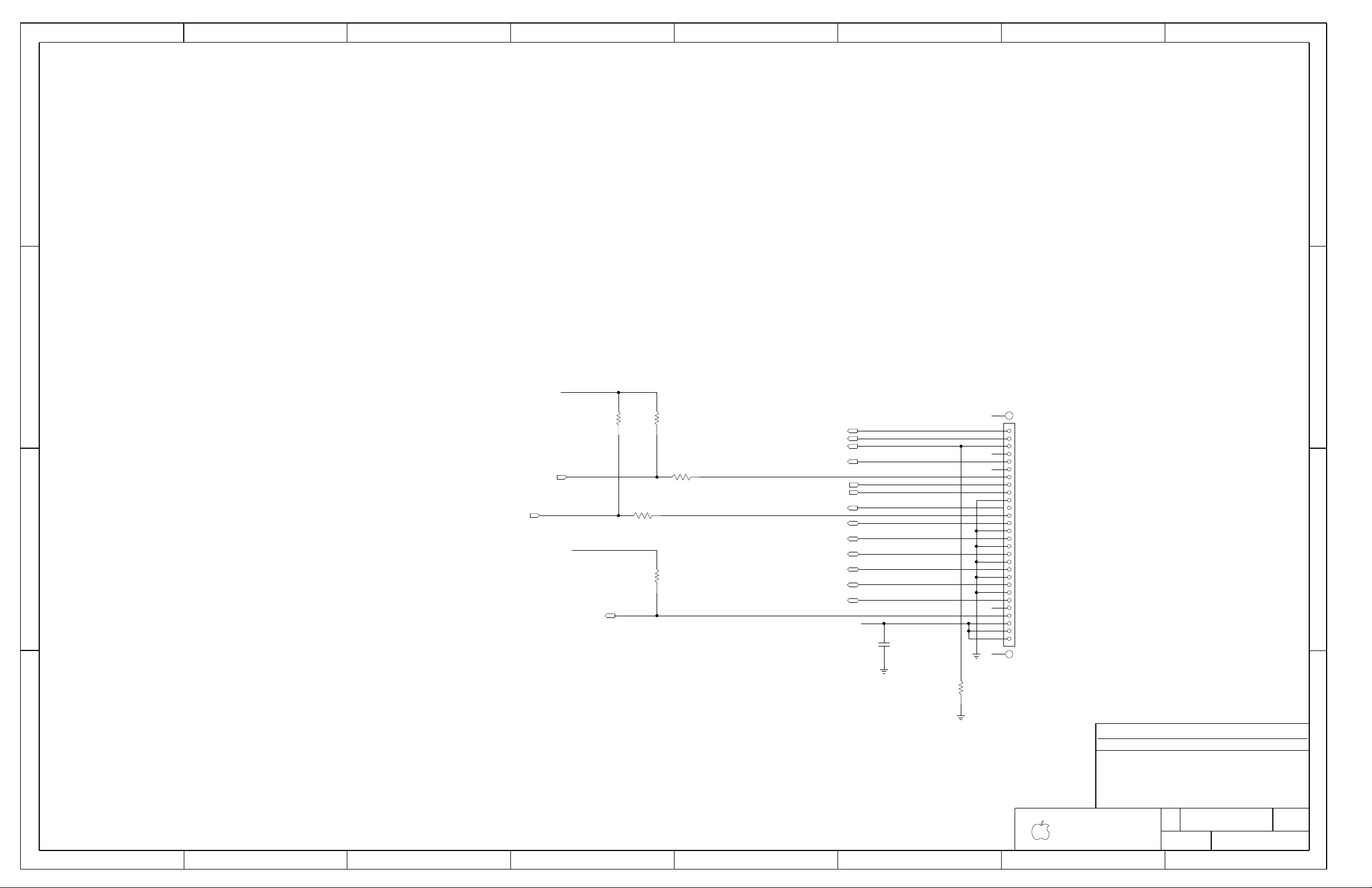

Page 10

D+

D-

ALERT*/

THM*

SCLK

SDATA

VDD

GND

THM2*

IO

IO

IN

OUT

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

PLACE U1001 NEAR THE MCH

;

CPU ZONE THERMAL SENSOR

PLACEHOLDER ADT7461A

CPU_THERMD_N ON SAME

LAYOUT NOTE:

ROUTE CPU_THERMD_P AND

FOR CPU_THERMD_P AND

CPU_THERMD_N

10 MIL SPACING

10 MIL TRACE

(TO CPU INTERNAL THERMAL DIODE)

LAYER.

LAYOUT NOTE:

ADD GND GUARD TRACE

MSOP

ADT7461

1

4

7

8

5

3

2

6

U1001

499

1/16W

402

1%

MF-LF

21

R1001

50V

20%

402

CERM

0.001UF

NOSTUFF

2

1

C1001

X5R

0.1UF

16V

10%

402

2

1

C1002

499

1%

MF-LF

402

1/16W

21

R1002

1/16W

5%

402

10K

MF-LF

2

1

R1005

10K

1/16W

402

MF-LF

5%

2

1

R1006

051-6941

03

10

103

SYNC_MASTER=M42

SYNC_DATE=08/04/2005

CPU MISC1-TEMP SENSOR

SMB_THRM_CLK

SMB_THRM_DATA

=PP3V3_S0_THRM_SNR

CPU_THERMD_N

CPU_THERMD_P

THRM_CPU_DX_P

THRM_ALERT_L

THRM_ALERT

THRM_CPU_DX_N

27

27

62

7

7

49

Page 11

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IO

IO

IO

IO

IO

IO

OUT

IN

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

ITP TCK SIGNAL LAYOUT NOTE:

CONNECTOR’S FBO PIN.

TCK PIN AND THEN FORK BACK FROM CPU TCK PIN AND ROUTE BACK TO ITP700FLEX

ROUTE THE TCK SIGNAL FROM ITP700FLEX CONNECTOR’S TCK PIN TO CPU’S

518S0320

(TCK)

(FBO)

CPU ITP700FLEX DEBUG SUPPORT

(DEBUG PORT ACTIVE)

(DBR#)

(DBA#)

NC

NC

NC

INDICATE THAT ITP IS USING TAP I/F, NC IN 945GM CHIPSET SYSTEM.

TO ICH7M SYS_RST*, AND WITH SYSTEM RESET LOGIC

(AND WITH RESET BUTTON)

(DEBUG PORT RESET)

(FROM CK410M HOST 133/167MHZ)

MF-LF

22.6

1%

1/16W

402

ITP

21

R1100

ITP

402

1%

22.6

1/16W

MF-LF

21

R1102

54.9

1/16W

1%

402

MF-LF

ITP

2

1

R1103

402

X5R

16V

10%

0.1UF

2

1

C1100

1/16W

240

402

MF-LF

5%

2

1

R1104

F-RT-SM

52435-2872

ITP

9

8

7

6

5

4

30

3

29

28

27

26

25

24

23

22

21

20

2

19

18

17

16

15

14

13

12

11

10

1

J1101

1/16W

402

54.9

1%

MF-LF

2

1

R1101

680

402

5%

1/16W

MF-LF

2

1

R1106

CPU ITP700FLEX DEBUG

SYNC_DATE=07/26/2005

051-6941

03

11 103

SYNC_MASTER=M42

CPU_XDP_CLK_N

XDP_TRST_L

XDP_TMS

ITP_TDO

XDP_BPM_L<5>

XDP_BPM_L<4>

XDP_BPM_L<2>

=PP1V05_S0_CPU

=PP3V3_S5_SB_PM

XDP_TDO

XDP_TDI

XDP_TCK

CPU_XDP_CLK_P

XDP_TCK

XDP_BPM_L<3>

XDP_BPM_L<1>

XDP_BPM_L<0>

FSB_CPURST_L ITPRESET_L

=PP1V05_S0_CPU

XDP_DBRESET_L

62

62

11

76

11

9

62

47

9

8

26

76

12

8

26

7

7

7

23

7

7

34

7

76

7

7

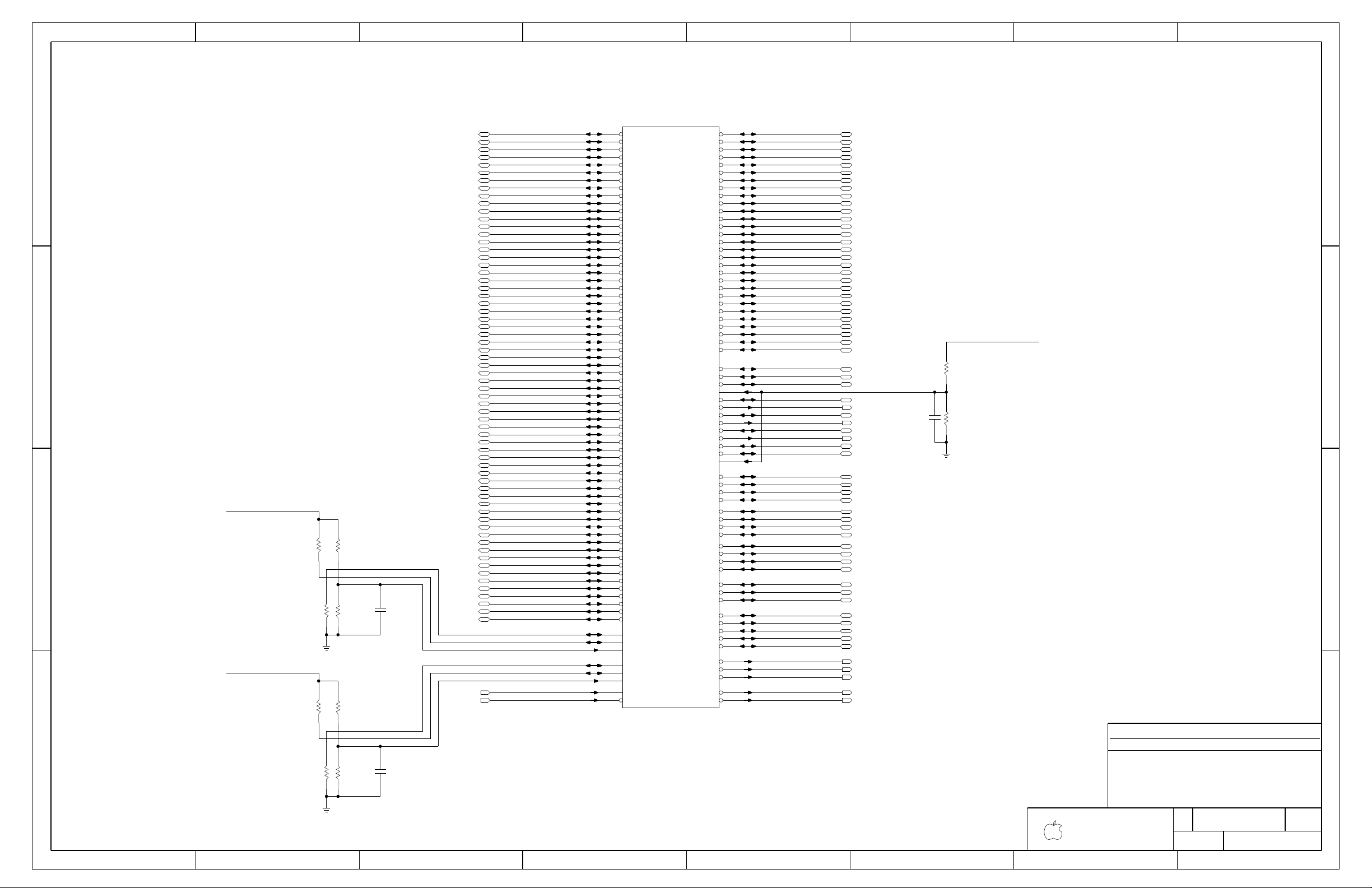

Page 12

IO

IO

IO

OUT

OUT

OUT

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

OUT

IO

OUT

OUT

OUT

OUT

IO

IO

IO

IO

IO

IN

IO

IN

IO

IO

HD4*

HD6*

HD16*

HTRDY*

HSLPCPU*

HRS1*

HRS0*

HHITM*

HLOCK*

HHIT*

HDSTBP2*

HDTSBP3*

HDSTBP1*

HDSTBP0*

HDSTBN3*

HDSTBN1*

HDSTBN2*

HDSTBN0*

HDINV2*

HDINV3*

HDINV1*

HDINV0*

HDVREF

HDRDY*

HDPWR*

HDEFER*

HDBSY*

HCPURST*

HBREQ0*

HBPRI*

HBNR*

HAVREF

HCLKIN*

HCLKIN

HYSWING

HYRCOMP

HYSCOMP

HXSWING

HXSCOMP

HXRCOMP

HA13*

HADS*

HADSTB0*

HD3*

HD2*

HD1*

HD0*

HD63*

HD62*

HD61*

HD60*

HD59*

HD58*

HD57*

HD56*

HD55*

HD54*

HD53*

HD52*

HD51*

HD50*

HD49*

HD48*

HD47*

HD46*

HD45*

HD44*

HD43*

HD42*

HD41*

HD40*

HD39*

HD38*

HD37*

HD36*

HD35*

HD34*

HD33*

HD32*

HD31*

HD29*

HD28*

HD27*

HD26*

HD25*

HD24*

HD23*

HD22*

HD21*

HD20*

HD19*

HD18*

HD17*

HD15*

HD10*

HD11*

HD12*

HD13*

HD14*

HD5*

HD7*

HD8*

HD9*

HA30*

HA29*

HA28*

HA27*

HA26*

HA25*

HA24*

HA23*

HA31*

HA20*

HA19*

HA18*

HA16*

HA15*

HA14*

HA21*

HA22*

HA17*

HA9*

HA8*

HA7*

HA6*

HA5*

HA4*

HA3*

HA10*

HA11*

HA12*

HADSTB1*

HREQ0*

HREQ1*

HREQ2*

HREQ3*

HD30*

HREQ4*

HRS2*

(1 OF 10)

HOST

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

402

X5R

16V

10%

0.1uF

2

1

C1211

200

1%

1/16W

MF-LF

402

2

1

R1211

100

1%

1/16W

MF-LF

402

2

1

R1210

54.9

1%

1/16W

MF-LF

402

2

1

R1220

402

MF-LF

1/16W

1%

24.9

2

1

R1221

221

1%

1/16W

MF-LF

402

2

1

R1225

1%

1/16W

MF-LF

402

100

2

1

R1226

0.1uF

402

X5R

16V

10%

2

1

C1226

402

X5R

16V

10%

0.1uF

2

1

C1236

221

1%

1/16W

MF-LF

402

2

1

R1235

54.9

1%

1/16W

MF-LF

402

2

1

R1230

1%

1/16W

MF-LF

402

100

2

1

R1236

402

MF-LF

1/16W

1%

24.9

2

1

R1231

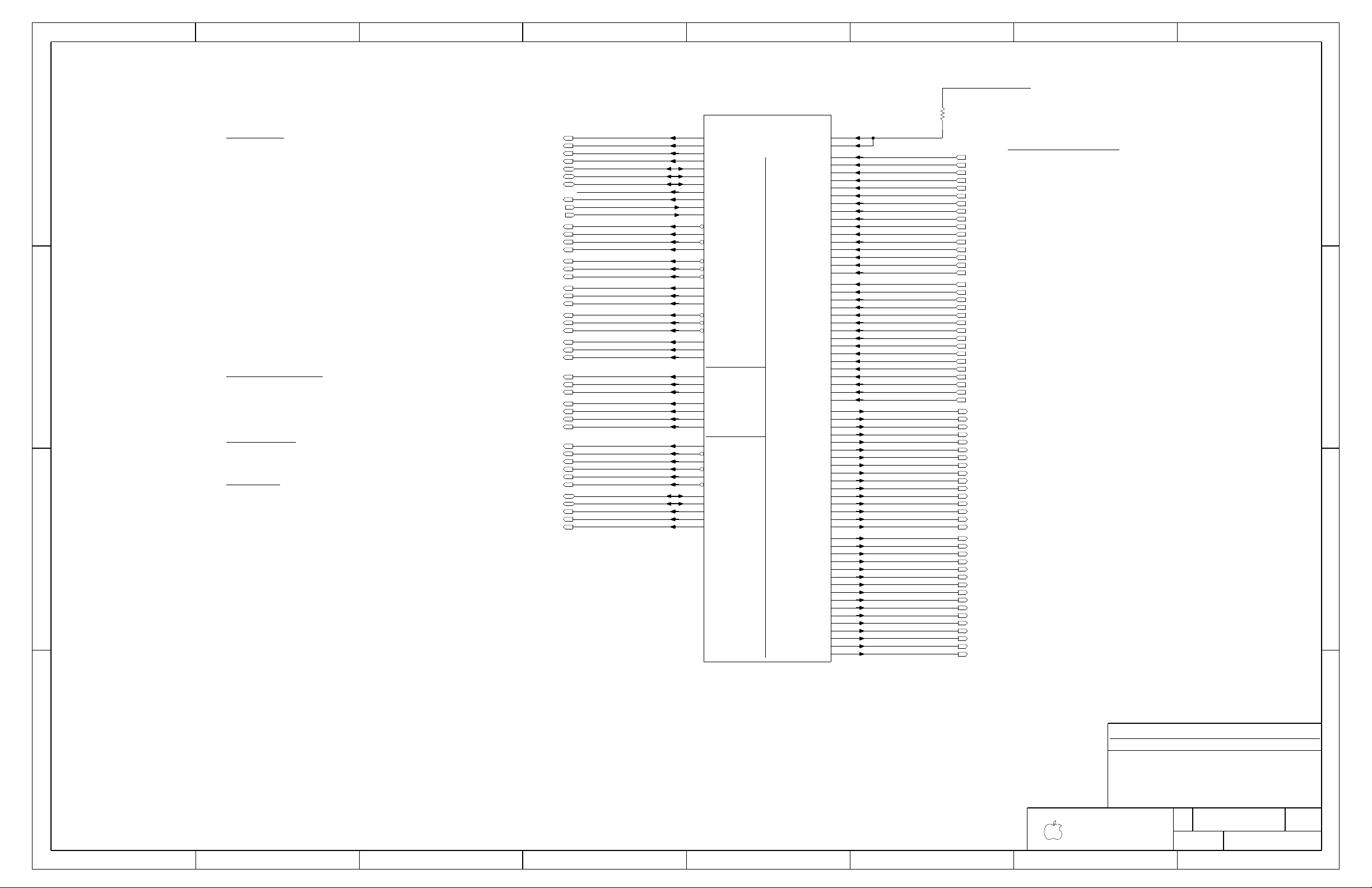

BGA

LEMENU

NB

945GM

W1

U1

Y1

E4

E2

E1

E7

E3

D6

E6

B4

A8

F8

B8

G8

D8

B3

D4

D3

K13

AC5

AA5

T6

K3

AC4

Y5

T7

K4

H8

J9

AB10

U3

W8

J7

C3

A7

K1

K9

G2

AC8

AD4

AD10

AB5

G1

AC6

AD7

AC1

AD9

AD1

AC2

AB3

AC11

AB11

AC9

K2

AB4

AA1

Y8

AA10

AA6

AA2

AA7

AA4

W2

AB8

H3

Y10

W5

Y7

Y3

W3

W4

AA9

AB7

T5

W6

J6

T9

U5

W7

T4

T8

T1

W9

T11

U11

U9

H1

U7

T3

W11

T10

G4

K11

J3

H4

J8

K7

J1

F1

B7

AG1

AG2

C7

F6

C6

J13

C13

B9

E8

F9

G12

F11

G11

E11

C9

D14

C14

H9

A14

C12

B14

B12

F12

G13

E13

A13

A12

C11

A11

D12

F14

J15

H13

J14

D9

G14

J12

H11

U1200

SYNC_MASTER=(MASTER)

SYNC_DATE=(MASTER)

NB CPU Interface

03

12

103

051-6941

NB_FSB_XRCOMP

=PP1V05_S0_FSB_NB

=PP1V05_S0_FSB_NB

=PP1V05_S0_FSB_NB

FSB_RS_L<2>

FSB_REQ_L<4>

FSB_D_L<30>

FSB_REQ_L<3>

FSB_REQ_L<2>

FSB_REQ_L<1>

FSB_REQ_L<0>

FSB_ADSTB_L<1>

FSB_A_L<12>

FSB_A_L<11>

FSB_A_L<10>

FSB_A_L<3>

FSB_A_L<4>

FSB_A_L<5>

FSB_A_L<6>

FSB_A_L<7>

FSB_A_L<8>

FSB_A_L<9>

FSB_A_L<17>

FSB_A_L<22>

FSB_A_L<21>

FSB_A_L<14>

FSB_A_L<15>

FSB_A_L<16>

FSB_A_L<18>

FSB_A_L<19>

FSB_A_L<20>

FSB_A_L<31>

FSB_A_L<23>

FSB_A_L<24>

FSB_A_L<25>

FSB_A_L<26>

FSB_A_L<27>

FSB_A_L<28>

FSB_A_L<29>

FSB_A_L<30>

FSB_D_L<14>

FSB_D_L<13>

FSB_D_L<12>

FSB_D_L<11>

FSB_D_L<15>

FSB_D_L<18>

FSB_D_L<19>

FSB_D_L<20>

FSB_D_L<21>

FSB_D_L<22>

FSB_D_L<23>

FSB_D_L<24>

FSB_D_L<25>

FSB_D_L<26>

FSB_D_L<27>

FSB_D_L<28>

FSB_D_L<29>

FSB_D_L<31>

FSB_D_L<32>

FSB_D_L<33>

FSB_D_L<34>

FSB_D_L<35>

FSB_D_L<36>

FSB_D_L<37>

FSB_D_L<38>

FSB_D_L<39>

FSB_D_L<40>

FSB_D_L<41>

FSB_D_L<42>

FSB_D_L<43>

FSB_D_L<44>

FSB_D_L<45>

FSB_D_L<46>

FSB_D_L<47>

FSB_D_L<48>

FSB_D_L<49>

FSB_D_L<50>

FSB_D_L<51>

FSB_D_L<52>

FSB_D_L<53>

FSB_D_L<54>

FSB_D_L<55>

FSB_D_L<56>

FSB_D_L<57>

FSB_D_L<58>

FSB_D_L<59>

FSB_D_L<60>

FSB_D_L<61>

FSB_D_L<62>

FSB_D_L<63>

FSB_ADSTB_L<0>

FSB_ADS_L

FSB_A_L<13>

NB_FSB_XSCOMP

NB_FSB_XSWING

NB_FSB_YSCOMP

NB_FSB_YRCOMP

NB_FSB_YSWING

FSB_CLK_NB_P

FSB_CLK_NB_N

FSB_BNR_L

FSB_BPRI_L

FSB_BREQ0_L

FSB_CPURST_L

FSB_DBSY_L

FSB_DEFER_L

FSB_DPWR_L

FSB_DRDY_L

FSB_DINV_L<3>

FSB_DSTBN_L<1>

FSB_DSTBP_L<0>

FSB_HIT_L

FSB_LOCK_L

FSB_HITM_L

FSB_RS_L<0>

FSB_RS_L<1>

FSB_SLPCPU_L

FSB_TRDY_L

FSB_D_L<16>

FSB_D_L<0>

FSB_D_L<3>

FSB_D_L<7>

FSB_D_L<8>

FSB_D_L<9>

FSB_D_L<10>

FSB_D_L<6>

FSB_D_L<5>

FSB_D_L<4>

FSB_D_L<2>

FSB_D_L<1>

NB_FSB_VREF

FSB_DINV_L<2>

FSB_DINV_L<1>

FSB_DSTBN_L<0>

FSB_DINV_L<0>

FSB_DSTBP_L<3>

FSB_DSTBP_L<2>

FSB_DSTBP_L<1>

FSB_DSTBN_L<3>

FSB_DSTBN_L<2>

FSB_D_L<17>

62

62

62

34

34

34

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76

76