LC2MOS

Quad 8-Bit D/A Converter

AD7226

FEATURES

Four 8-Bit DACs with Output Amplifiers

Skinny 20-Lead DIP, SOIC, SSOP, and PLCC Packages

Microprocessor-Compatible

TTL/CMOS-Compatible

No User Trims

Extended Temperature Range Operation

Single Supply Operation Possible

APPLICATIONS

Process Control

Automatic Test Equipment

Automatic Calibration of Large System Parameters,

e.g., Gain/Offset

GENERAL DESCRIPTION

The AD7226 contains four 8-bit voltage-output digital-toanalog converters, with output buffer amplifiers and interface

logic on a single monolithic chip. No external trims are required

to achieve full specified performance for the part.

Separate on-chip latches are provided for each of the four D/A

converters. Data is transferred into one of these data latches

through a common 8-bit TTL/CMOS (5 V) compatible input

port. Control inputs A0 and A1 determine which DAC is

loaded when WR goes low. The control logic is speed-compatible with most 8-bit microprocessors.

Each D/A converter includes an output buffer amplifier capable

of driving up to 5 mA of output current. The amplifiers’ offsets

are laser-trimmed during manufacture, thereby eliminating any

requirement for offset nulling.

Specified performance is guaranteed for input reference voltages

from 2 V to 12.5 V with dual supplies. The part is also specified

for single supply operation at a reference of 10 V.

The AD7226 is fabricated in an all ion-implanted high speed

Linear Compatible CMOS (LC

2

MOS) process, which has been

specifically developed to allow high speed digital logic circuits

and precision analog circuits to be integrated on the same chip.

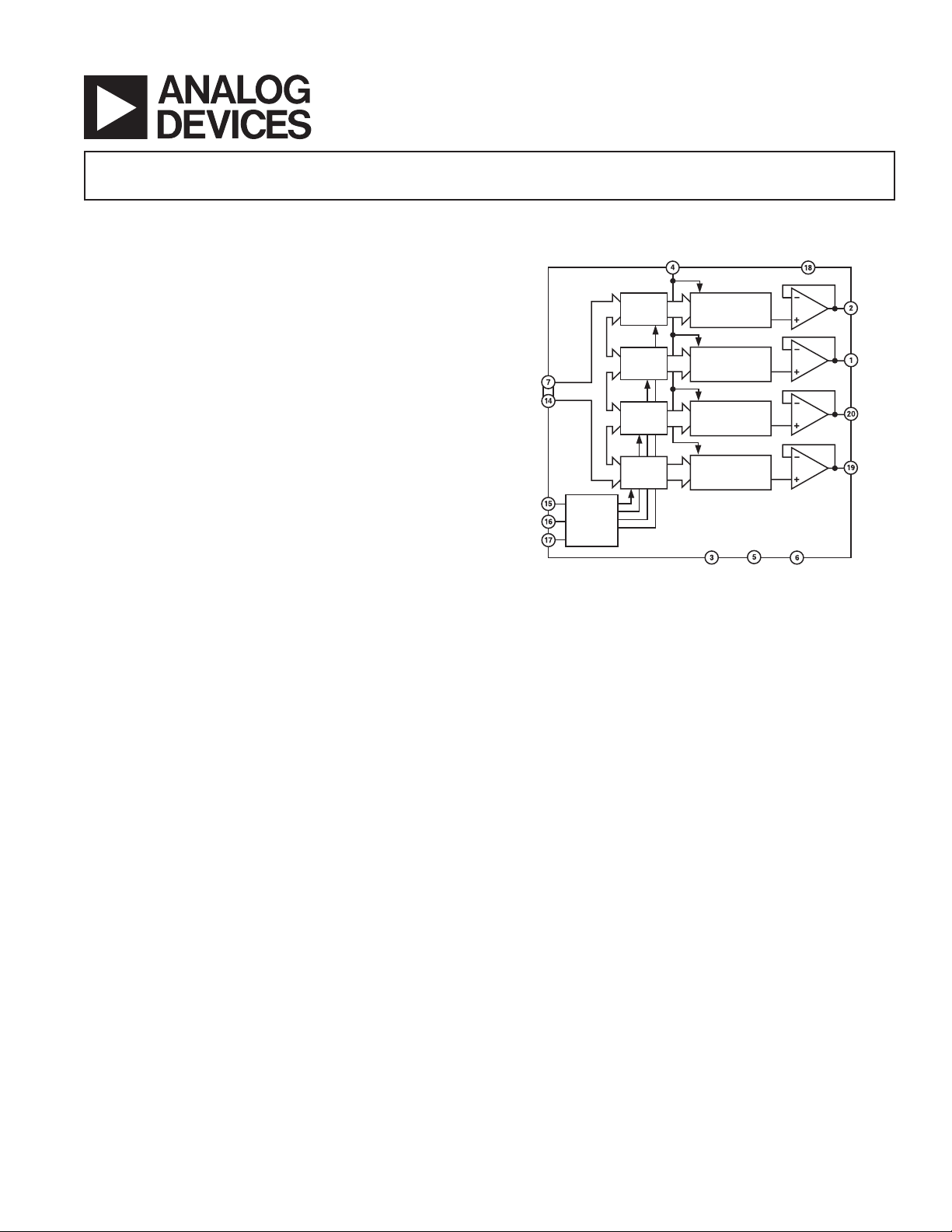

FUNCTIONAL BLOCK DIAGRAM

MSB

DATA

(8-BIT)

LSB

WR

V

REF

LATCH A

D

A

LATCH B

T

A

B

LATCH C

U

S

LATCH D

CONTROL

A1

A0

LOGIC

V

SS

DAC A

DAC B

DAC C

DAC D

AGND AGND

AD7226

V

DD

A

B

C

D

V

OUT

V

OUT

V

OUT

V

OUT

PRODUCT HIGHLIGHTS

1. DAC-to-DAC Matching

Since all four DACs are fabricated on the same chip at the

same time, precise matching and tracking between the DACs

is inherent.

2. Single-Supply Operation

The voltage mode configuration of the DACs allows the

AD7226 to be operated from a single power supply rail.

3. Microprocessor Compatibility

The AD7226 has a common 8-bit data bus with individual

DAC latches, providing a versatile control architecture for

simple interface to microprocessors. All latch enable signals

are level triggered.

4. Small Size

Combining four DACs and four op amps plus interface logic

into a 20-pin package allows a dramatic reduction in board

space requirements and offers increased reliability in systems

using multiple converters. Its pinout is aimed at optimizing

board layout with all the analog inputs and outputs at one

end of the package and all the digital inputs at the other.

A

B

C

D

REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

(VDD = 11.4 V to 16.5 V, VSS = –5 V 10%, AGND = DGND = 0 V; V

AD7226–SPECIFICATIONS

unless otherwise noted. All Specifications T

MIN

to T

unless otherwise noted.)

MAX

DUAL SUPPLY

Parameter K, B Versions

STATIC PERFORMANCE

Resolution 8 Bits

Total Unadjusted Error ± 1LSB maxV

Relative Accuracy ± 0.5 LSB max

Differential Nonlinearity ± 1LSB max Guaranteed Monotonic

Full-Scale Error ± 0.5 LSB max

Full-Scale Temperature Coefficient ± 20 ppm/∞C typ V

Zero Code Error ± 20 mV max

Zero Code Error Temperature Coefficient ± 50 mV/∞C typ

REFERENCE INPUT

Voltage Range 2 to (VDD – 4) V min to V max

Input Resistance 2 kW min

Input Capacitance

3

50 pF min Occurs when each DAC is loaded with all 0s.

200 pF max Occurs when each DAC is loaded with all 1s.

DIGITAL INPUTS

Input High Voltage, V

Input Low Voltage, V

INL

INH

2.4 V min

0.8 V max

Input Leakage Current ± 1 mA max V

Input Capacitance 8 pF max

Input Coding Binary

DYNAMIC PERFORMANCE

Voltage Output Slew Rate

Voltage Output Settling Time

4

4

2.5 V/ms min

4 ms max V

Digital Crosstalk 10 nV secs typ

Minimum Load Resistance 2 kW min V

POWER SUPPLIES

VDD Range 11.4/16.5 V min/V max For Specified Performance

I

DD

I

SS

SWITCHING CHARACTERISTICS

Address to Write Setup Time, t

Address to Write Hold Time, t

Data Valid to Write Setup Time, t

Data Valid to Write Hold Time, t

Write Pulsewidth, t

NOTES

1

Maximum possible reference voltage.

2

Temperature ranges are as follows:

3

Guaranteed by design. Not production tested.

4

Sample Tested at 25∞C to ensure compliance.

5

Switching Characteristics apply for single and dual supply operation.

Specifications subject to change without notice.

K Version: –40∞C to +85∞C

B Version: –40∞C to +85∞C

WR

AS

AH

DS

DH

13 mA max Outputs Unloaded; VIN = V

11 mA max Outputs Unloaded; VIN = V

4, 5

0ns min

0ns min

50 ns min

0ns min

50 ns min

2

Unit Conditions/Comments

= 15 V ± 5%, V

DD

= 14 V to 16.5 V, V

DD

= 0 V or V

IN

= 10 V; Settling Time to ± 1/2 LSB

REF

= 10 V

OUT

DD

= +2 V to (V

REF

= 10 V

REF

REF

– 4 V)1,

DD

= +10 V

or V

INL

or V

INL

INH

INH

REV. C–2–

AD7226

(VDD = 15 V 5%, VSS = AGND = DGND = O V; V

SINGLE SUPPLY

All specifications T

MIN

to T

unless otherwise noted.)

MAX

Parameter K, B Versions

2

= 10 V1 unless otherwise noted.

REF

Unit Conditions/Comments

STATIC PERFORMANCE

Resolution 8 Bits

Total Unadjusted Error ± 2LSB max

Differential Nonlinearity ± 1LSB max Guaranteed Monotonic

REFERENCE INPUT

Input Resistance 2 kW min

Input Capacitance

3

50 pF min Occurs when each DAC is loaded with all 0s.

200 pF max Occurs when each DAC is loaded with all 1s.

DIGITAL INPUTS

Input High Voltage, V

Input Low Voltage, V

INH

INL

Input Leakage Current ± 1 mA max V

2.4 V min

0.8 V max

= 0 V or V

IN

DD

Input Capacitance 8 pF max

Input Coding Binary

DYNAMIC PERFORMANCE

Voltage Output Slew Rate

Voltage Output Settling Time

4

4

2V/ms min

4 ms max Settling Time to ± 1/2 LSB

Digital Crosstalk 10 nV secs typ

Minimum Load Resistance 2 kW min V

= +10 V

OUT

POWER SUPPLIES

VDD Range 14.25/15.75 V min/V max For Specified Performance

I

DD

NOTES

1

Maximum possible reference voltage.

2

Temperature ranges are as follows:

K Version: –40∞C to +85∞C

B Version: –40∞C to +85∞C

3

Guaranteed by design. Not production tested.

4

Sample Tested at 25∞C to ensure compliance.

Specifications subject to change without notice.

13 mA max Outputs Unloaded; VIN = V

ABSOLUTE MAXIMUM RATINGS

1

VDD to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +17 V

to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +17 V

V

DD

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –7 V, V

V

SS

VSS to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –7 V, V

VDD to VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +24 V

ORDERING GUIDE

1

Total

Temperature Unadjusted Package

Model Range Error Option

AD7226KN –40∞C to +85∞C ± 1 LSB N-20

AD7226KP –40∞C to +85∞C ± 1 LSB P-20A

AD7226KR –40∞C to +85∞C ± 1 LSB RW-20

AD7226BQ –40∞C to +85∞C ± 1 LSB Q-20

AD7226BRS –40∞C to +85∞C ± 1 LSB RS-20

NOTES

1

Dual-Supply Operation

2

N = Plastic DIP; P = Plastic Leaded Chip Carrier; Q = CERDIP; RW = SOIC;

RS = SSOP

AGND to DGND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, V

Digital Input Voltage to DGND . . . . . . . –0.3 V, VDD + 0.3 V

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, V

V

REF

V

2

to AGND2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . VSS, V

OUT

Power Dissipation (Any Package) to 75∞C . . . . . . . . . . 500 mW

Derates above 75∞C by . . . . . . . . . . . . . . . . . . . . . 2.0 mW/∞C

Operating Temperature

Commercial (K Version) . . . . . . . . . . . . . . . –40∞C to +85∞C

Industrial (B Version) . . . . . . . . . . . . . . . . . –40∞C to +85∞C

Storage Temperature . . . . . . . . . . . . . . . . . . . –65∞C to +150∞C

Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . . . 300∞C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only, functional operation of the

device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Outputs may be shorted to AGND provided that the power dissipation of the

package is not exceeded. Typically short circuit current to AGND is 50 mA.

INL

or V

INH

DD

DD

DD

DD

DD

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD7226 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

REV. C

–3–

AD7226

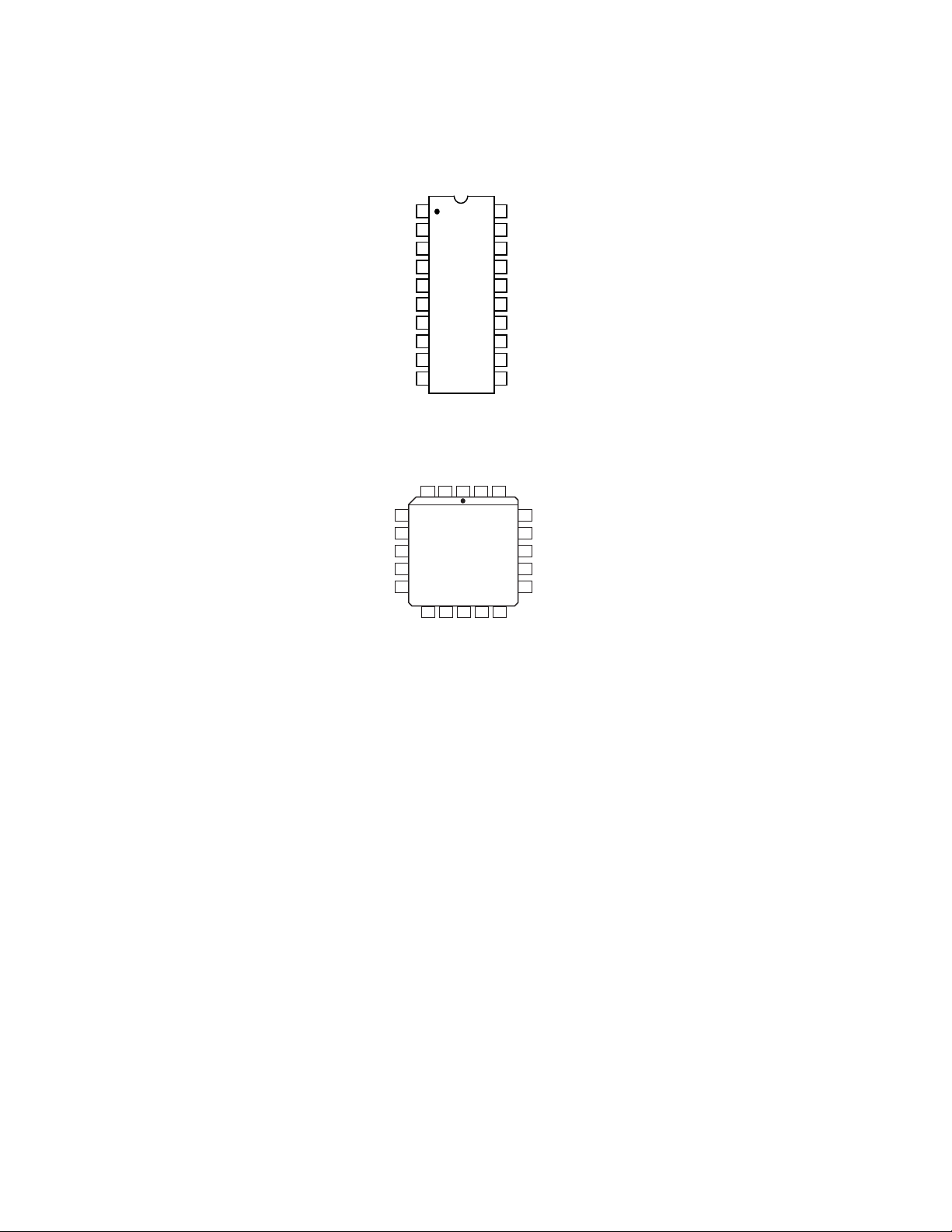

PIN CONFIGURATIONS

DIP and SOIC/SSOP

V

BV

1

OUT

V

A

2

OUT

V

3

SS

4

V

REF

5

AGND

DGND

DB7 (MSB)

DB6

DB5

DB4

AD7226

TOP VIEW

6

(Not to Scale)

7

8

9

10

PLCC

B

A

SSVOUT

OUT

V

V

3 2 1 20 19

REF

AGND

DGND

DB8

4

5

6

(Not to Scale)

7

8

9 10 11 12 13

DB5

AD7226

TOP VIEW

DB4

DB3

V

DB7 (MSB)

C

V

OUT

DB2

20

V

19

V

18

A0

17

A1

16

15

WR

14

DB0(LSB)

13

DB1

12

DB2

11

DB3

D

OUT

V

DB1

OUT

OUT

DD

18

17

16

15

14

C

D

V

DD

A0

A1

WR

DB0(LSB)

TERMINOLOGY

TOTAL UNADJUSTED ERROR

This is a comprehensive specification that includes full-scale

error, relative accuracy and zero code error. Maximum output

voltage is V

256. The LSB size will vary over the V

code error will, relative to the LSB size, increase as V

– 1 LSB (ideal), where 1 LSB (ideal) is V

REF

range. Hence the zero

REF

REF

/

REF

decreases.

Accordingly, the total unadjusted error, which includes the zero

code error, will also vary in terms of LSB’s over the V

REF

range.

As a result, total unadjusted error is specified for a fixed reference voltage of 10 V.

RELATIVE ACCURACY

Relative Accuracy or endpoint nonlinearity, is a measure of the

maximum deviation from a straight line passing through the

endpoints of the DAC transfer function. It is measured after

allowing for zero and full-scale error and is normally expressed

in LSB’s or as a percentage of full-scale reading.

DIFFERENTIAL NONLINEARITY

Differential Nonlinearity is the difference between the measured

change and the ideal 1 LSB change between any two adjacent

codes. A specified differential nonlinearity of ± 1 LSB max over

the operating temperature range ensures monotonicity.

DIGITAL CROSSTALK

The glitch impulse transferred to the output of one converter

due to a change in the digital input code to another of the converters. It is specified in nV secs and is measured at V

REF

= 0 V.

FULL SCALE ERROR

Full-Scale Error is defined as:

Measured Value – Zero Code Error – Ideal Value

REV. C–4–

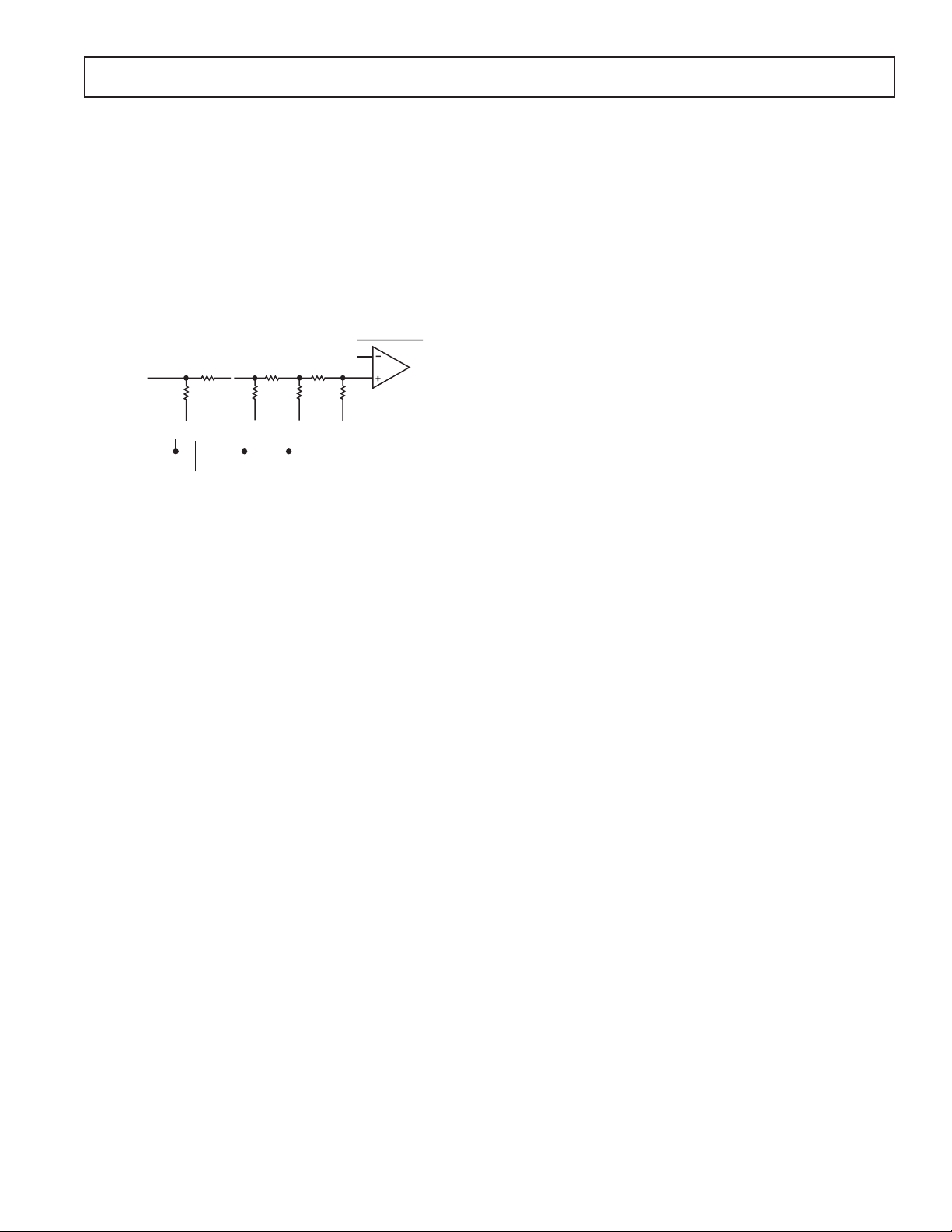

CIRCUIT INFORMATION D/A SECTION

The AD7226 contains four identical, 8-bit, voltage mode digital-toanalog converters. The output voltages from the converters have the

same polarity as the reference voltage allowing single supply operation. A novel DAC switch pair arrangement on the AD7226 allows a

reference voltage range from 2 V to 12.5 V.

Each DAC consists of a highly stable, thin-film, R-2R ladder

and eight high speed NMOS, single-pole, double-throw

switches. The simplified circuit diagram for one channel is

shown in Figure 1. Note that V

are common to all four DACs.

(Pin 4) and AGND (Pin 5)

REF

AD7226

REV. C

–5–

Loading...

Loading...