Analog Devices AD6624A Datasheet

Four-Channel, 100 MSPS Digital

a

FEATURES

100 MSPS Wideband Inputs (14 Linear Bits Plus 3 RSSI)

Dual High-Speed Data Input Ports

Four Independent Digital Receivers in Single Package

Digital Resampling for Noninteger Decimation Rates

Programmable Decimating FIR Filters

Programmable Attenuator Control for Clip Prevention

and External Gain Ranging via Level Indicator

Flexible Control for Multicarrier and Phased Array

3.3 V I/O, 2.5 V CMOS Core

User-Configurable Built-In Self-Test (BIST) Capability

JTAG Boundary Scan

APPLICATIONS

Multicarrier, Multimode Digital Receivers GSM, IS136,

EDGE, PHS, IS95

Micro and Pico Cell Systems

Wireless Local Loop

Smart Antenna Systems

Software Radios

In-Building Wireless Telephony

PRODUCT DESCRIPTION

The AD6624A is a four-channel (quad) digital receive signal

processor (RSP) with four cascaded signal-processing elements:

a frequency translator, two fixed-coefficient decimating filters,

and a programmable-coefficient decimating filter.

Receive Signal Processor (RSP)

AD6624A

The AD6624A is part of Analog Devices’ SoftCell® multicarrier

transceiver chipset designed for compatibility with Analog

Devices’ family of high sample rate IF sampling ADCs (AD6640/

AD6644 12- and 14-bit). The SoftCell receiver comprises a

digital receiver capable of digitizing an entire spectrum of

carriers and digitally selecting the carrier of interest for tuning

and channel selection. This architecture eliminates redundant

radios in wireless base station applications.

High dynamic range decimation filters offer a wide range of

decimation rates. The RAM-based architecture allows easy

reconfiguration for multimode applications.

The decimating filters remove unwanted signals and noise from

the channel of interest. When the channel of interest occupies less

bandwidth than the input signal, this rejection of out-of-band

noise is called “processing gain.” By using large decimation

factors, this “processing gain” can improve the SNR of the

ADC by 30 dB or more. In addition, the programmable RAM

coefficient filter allows antialiasing, matched filtering, and

static equalization functions to be combined in a single, costeffective filter.

The AD6624A is compatible with standard ADC converters such

as the AD664x, AD9042, AD943x and the AD922x families of

data converters. The AD6624A is also compatible with the

AD6600 Diversity ADC, providing a cost and size reduction path.

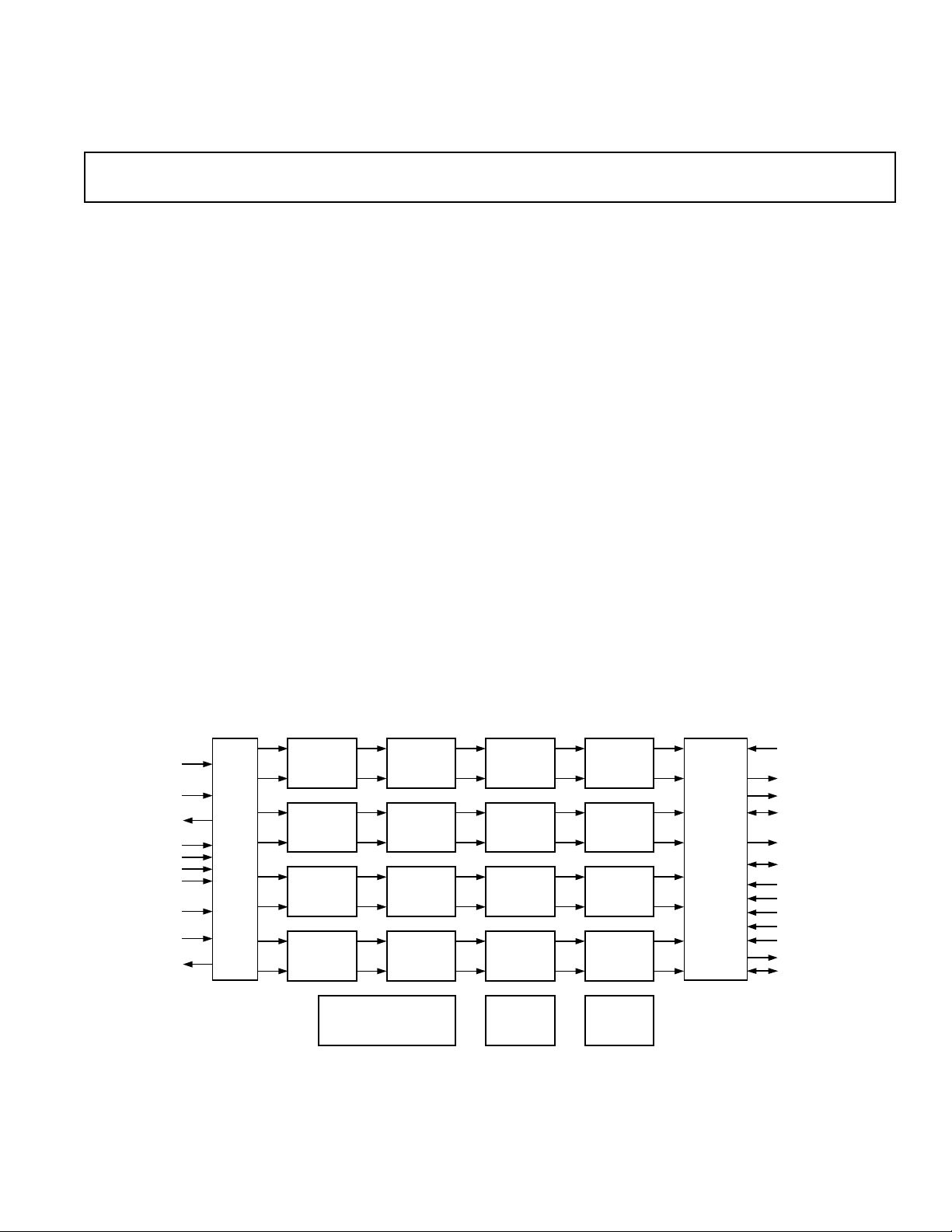

FUNCTIONAL BLOCK DIAGRAM

16 BITS 18 BITS 20 BITS 24 BITS

INA[13:0]

EXPA[2:0]

IENA

LIA-A

LIA-B

SYNCA

SYNCB

SYNCC

SYNCD

INB[13:0]

EXPB[2:0]

IENB

LIB-A

LIB-B

SoftCell is a registered trademark of Analog Devices, Inc.

INPUT

MATRIX

CH A NCO

CH B NCO

CH C NCO

CH D NCO

EXTERNAL SYNC

RESAMPLER

RESAMPLER

RESAMPLER

RESAMPLER

CIRCUITRY

rCIC2

rCIC2

rCIC2

rCIC2

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

CIC5

CIC5

CIC5

CIC5

JTAG

INTERFACE

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

RAM

COEFFICIENT

FILTER

RAM

COEFFICIENT

FILTER

RAM

COEFFICIENT

FILTER

RAM

COEFFICIENT

FILTER

BUILT-IN

SELF-TEST

SERIAL

AND

MICROPORT

SDIN[3:0]

SDO[3:0]

DR[3:0]

SDFS[3:0]

SDFE[3:0]

SCLK[3:0]

MODE

DS(RD)

CS

RW (WR)

DTACK(RDY)

A[2:0]

D[7:0]

AD6624A

TABLE OF CONTENTS

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

FUNCTIONAL BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . 1

SPECIFICATIONS/CHARACTERISTICS . . . . . . . . . . . . . . . . 3

TIMING DIAGRAMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . 9

PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . 11

ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

EXAMPLE FILTER RESPONSE . . . . . . . . . . . . . . . . . . . . . . 14

INPUT DATA PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Input Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Input Enable Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Gain Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Input Data Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Scaling with Fixed-Point ADCs . . . . . . . . . . . . . . . . . . . . . . . 16

Scaling with Floating-Point or Gain-Ranging ADCs . . . . . . . 16

NUMERICALLY CONTROLLED OSCILLATOR . . . . . . . . 17

Frequency Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

NCO Frequency Hold-Off Register . . . . . . . . . . . . . . . . . . . . 17

Phase Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

NCO Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Phase Dither . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Amplitude Dither . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Clear Phase Accumulator on HOP . . . . . . . . . . . . . . . . . . . . . 17

Input Enable Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Mode 00: Blank On IEN Low . . . . . . . . . . . . . . . . . . . . . . . . 17

Mode 01: Clock On IEN High . . . . . . . . . . . . . . . . . . . . . . . 18

Mode 10: Clock on IEN Transition to High . . . . . . . . . . . . . 18

Mode 11: Clock on IEN Transition to Low . . . . . . . . . . . . . . 18

WB Input Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Sync Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

SECOND ORDER rCIC FILTER . . . . . . . . . . . . . . . . . . . . . . 18

rCIC2 Rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Example Calculations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Decimation and Interpolation Registers . . . . . . . . . . . . . . . . . 19

rCIC2 Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

FIFTH ORDER CASCADED INTEGRATOR COMB

FILTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

CIC5 Rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

RAM COEFFICIENT FILTER . . . . . . . . . . . . . . . . . . . . . . . . 20

RCF Decimation Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

RCF Decimation Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

RCF Filter Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

RCF Output Scale Factor and Control Register . . . . . . . . . . 21

USER-CONFIGURABLE BUILT-IN SELF-TEST (BIST) . . 22

RAM BIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

CHANNEL BIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

CHIP SYNCHRONIZATION . . . . . . . . . . . . . . . . . . . . . . . . . 22

Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Hop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

SERIAL OUTPUT DATA PORT . . . . . . . . . . . . . . . . . . . . . . 24

Serial Output Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Compact Serial Data Format . . . . . . . . . . . . . . . . . . . . . . . . . 24

Serial Data Frame (Serial Bus Master) . . . . . . . . . . . . . . . . . . 24

Serial Data Frame (Serial Cascade) . . . . . . . . . . . . . . . . . . . . 25

Configuring the Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Serial Port Data Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Serial Port to DSP Interconnection . . . . . . . . . . . . . . . . . . . . 25

Serial Slave Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Serial Ports Cascaded . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Serial Output Frame Timing (Master and Slave) . . . . . . . . . . 26

Serial Port Timing Specifications . . . . . . . . . . . . . . . . . . . . . . 28

SBM0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

SCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

SDIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

SDO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

SDFS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

SDFE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Serial Word Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

SDFS Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Mapping RCF Data to the BIST Registers . . . . . . . . . . . . . . 30

0x00–0x7F: Coefficient Memory (CMEM) . . . . . . . . . . . . . . 30

0x80: Channel Sleep Register . . . . . . . . . . . . . . . . . . . . . . . . 30

0x81: Soft_SYNC Register . . . . . . . . . . . . . . . . . . . . . . . . . . 30

0x82: Pin_SYNC Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

0x83: Start Hold-Off Counter . . . . . . . . . . . . . . . . . . . . . . . . 30

0x84: NCO Frequency Hold-Off Counter . . . . . . . . . . . . . . 30

0x85: NCO Frequency Register 0 . . . . . . . . . . . . . . . . . . . . . 30

0x86: NCO Frequency Register 1 . . . . . . . . . . . . . . . . . . . . . 30

0x87: NCO Phase Offset Register . . . . . . . . . . . . . . . . . . . . . 30

0x88: NCO Control Register . . . . . . . . . . . . . . . . . . . . . . . . . 30

0x90: rCIC2 Decimation – 1 (M

0x91: rCIC2 Interpolation – 1 (L

–1) . . . . . . . . . . . . . . . . 31

rCIC2

–1) . . . . . . . . . . . . . . . 31

rCIC2

0x92: rCIC2 Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

0x93: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

0x94: CIC5 Decimation – 1 (M

–1) . . . . . . . . . . . . . . . . . 31

CIC5

0x95: CIC5 Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

0x96: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

0xA0: RCF Decimation – 1 (M

0xA1: RCF Decimation Phase (P

0xA2: RCF Number of Taps Minus One (N

0xA3: RCF Coefficient Offset (CO

–1) . . . . . . . . . . . . . . . . . . 31

RCF

) . . . . . . . . . . . . . . . . . . 31

RCF

) . . . . . . . . . . . . . . . . . 31

RCF

-1) . . . . . . . . 31

RCF

0xA4: RCF Control Register . . . . . . . . . . . . . . . . . . . . . . . . . 31

0xA5: BIST Register for I . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

0xA6: BIST Register for Q . . . . . . . . . . . . . . . . . . . . . . . . . . 32

0xA7: BIST Control Register . . . . . . . . . . . . . . . . . . . . . . . . 32

0xA8: RAM BIST Control Register . . . . . . . . . . . . . . . . . . . 32

0xA9: Serial Port Control Register . . . . . . . . . . . . . . . . . . . . 32

MICROPORT CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

External Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Access Control Register (ACR) . . . . . . . . . . . . . . . . . . . . . . . 33

External Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Channel Address Register (CAR) . . . . . . . . . . . . . . . . . . . . . . 34

SOFT_SYNC Control Register . . . . . . . . . . . . . . . . . . . . . . . 34

PIN_SYNC Control Register . . . . . . . . . . . . . . . . . . . . . . . . . 34

SLEEP Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Data Address Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Write Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Read Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Read/Write Chaining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Intel Nonmultiplexed Mode (INM) . . . . . . . . . . . . . . . . . . . . 35

Motorola Nonmultiplexed Mode (MNM) . . . . . . . . . . . . . . . 35

Input Port Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . 35

SERIAL PORT CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

JTAG BOUNDARY SCAN . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

INTERNAL WRITE ACCESS . . . . . . . . . . . . . . . . . . . . . . . . . 37

Write Pseudocode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

INTERNAL READ ACCESS . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Read Pseudocode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

–2–

REV. 0

AD6624A

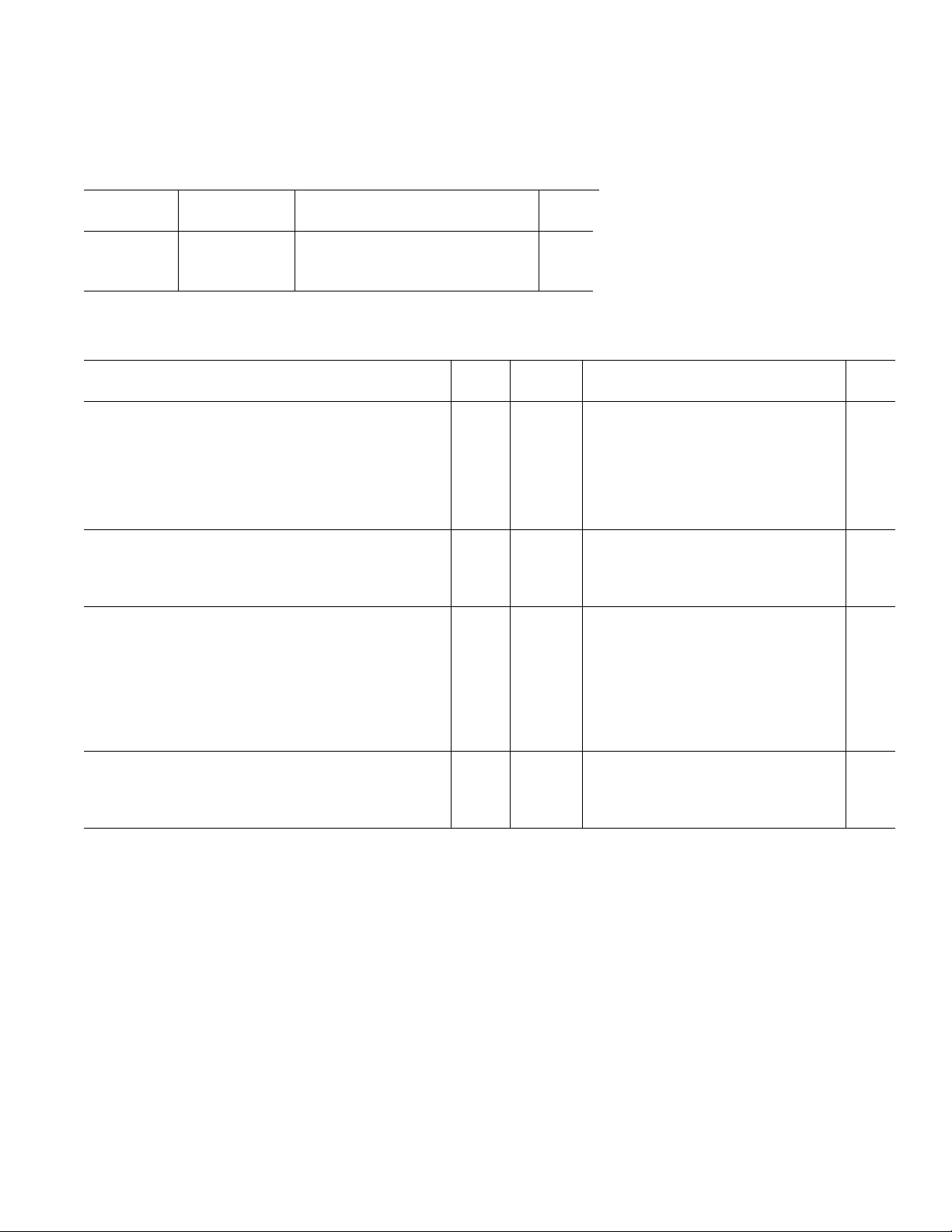

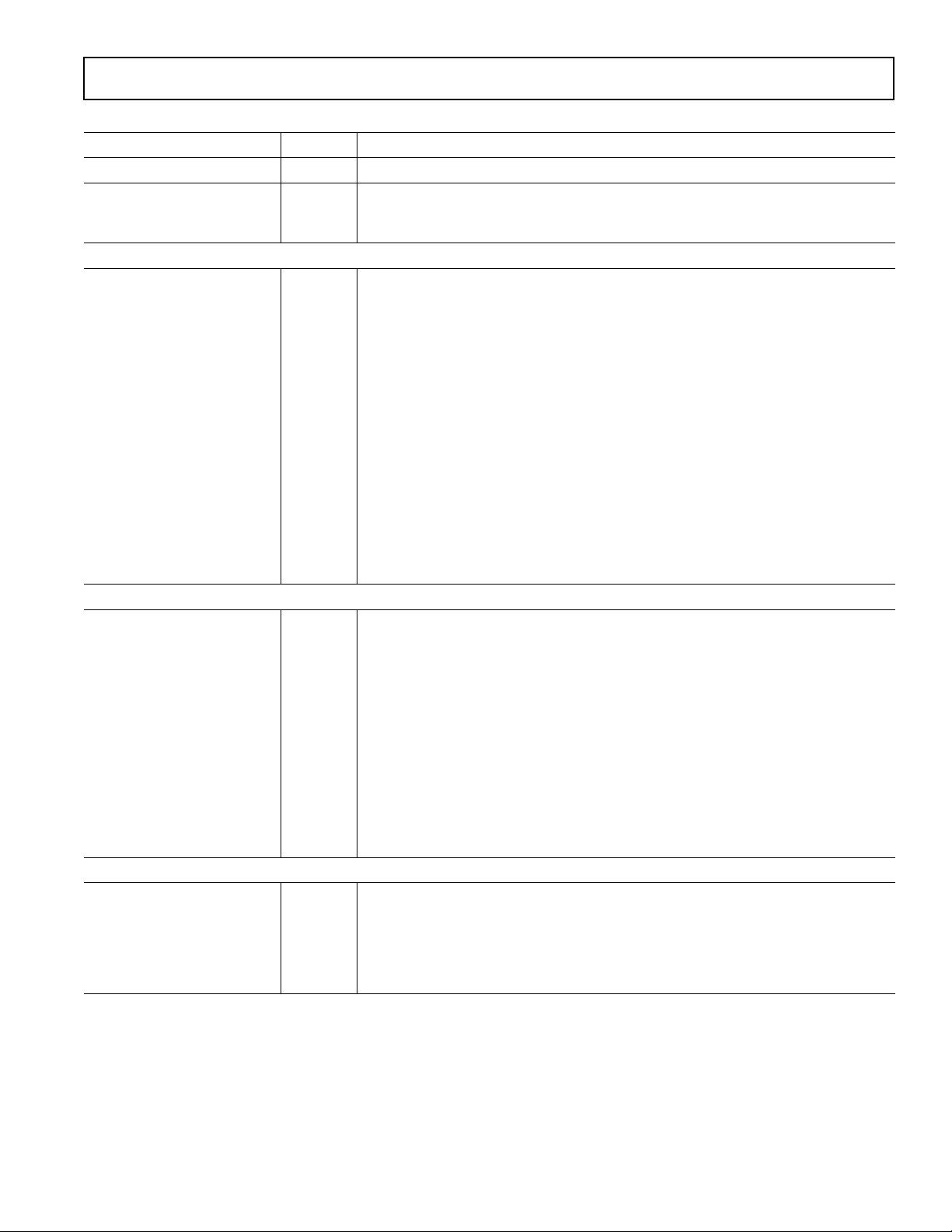

SPECIFICATIONS

(VDD = 2.5 V ⴞ 5%, VDDIO = 3.3 V ⴞ 10%. All specifications TA = T

MIN

to T

, unless otherwise noted.)

MAX

RECOMMENDED OPERATING CONDITIONS

Test AD6624AS

Parameter Level Min Typ Max Unit

VDD IV 2.375 2.5 2.675 V

VDDIO IV 3.0 3.3 3.6 V

T

AMBIENT

IV –40 +25 +70 °C

ELECTRICAL CHARACTERISTICS

Test AD6624AS

Parameter (Conditions) Temp Level Min Typ Max Unit

LOGIC INPUTS

Logic Compatibility Full 3.3 V CMOS

Logic “1” Voltage Full IV 2.0 5.0 V

Logic “0” Voltage Full IV –0.3 +0.8 V

Logic “1” Current Full IV 1 10 µA

Logic “0” Current Full IV 1 10 µA

Input Capacitance 25°CV 4 pF

LOGIC OUTPUTS

Logic Compatibility Full 3.3 V CMOS/TTL

Logic “1” Voltage (I

Logic “0” Voltage (IOL = 0.25 mA) Full IV 0.2 0.4 V

IDD SUPPLY CURRENT

CLK = 100 MHz, (VDD = 2.75 V, VDDIO = 3.6 V) Full IV

I

VDD

I

VDDIO

CLK = GSM Example (65 MSPS, VDD = 2.5 V,

VDDIO = 3.3 V, Dec = 2/10/6 120 Taps 4 Channels) 25°CV

I

VDD

I

VDDIO

POWER DISSIPATION

CLK = 80 MHz TD-SCDMA Full IV 1.1 W

CLK = 65 MHz

Sleep Mode Full IV 287 µW

Specifications subject to change without notice.

(5 V TOLERANT)

= 0.25 mA) Full IV 2.4 VDD – 0.2 V

OH

545 mA

60 mA

250 mA

24 mA

GSM/EDGE Example V 700 mW

REV. 0

–3–

AD6624A

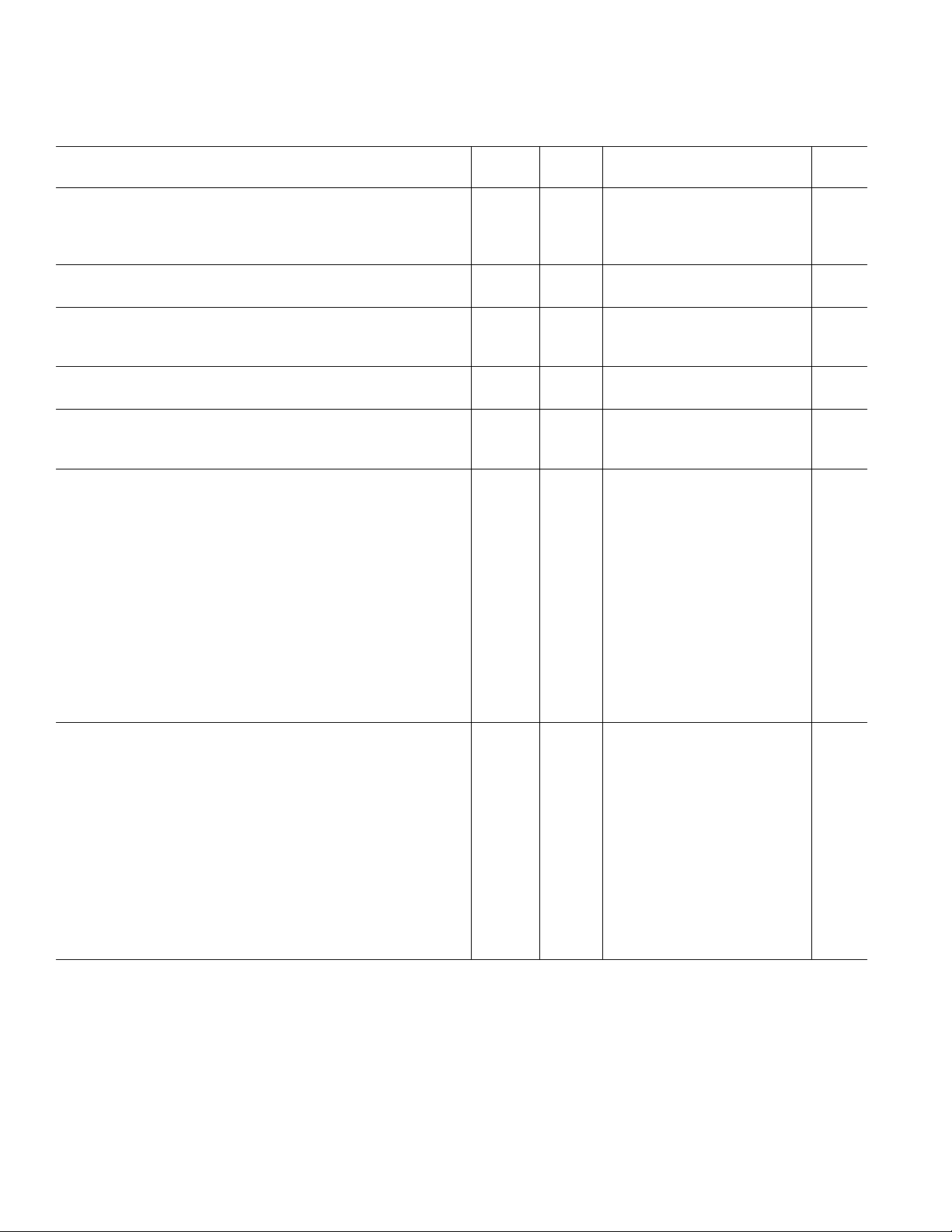

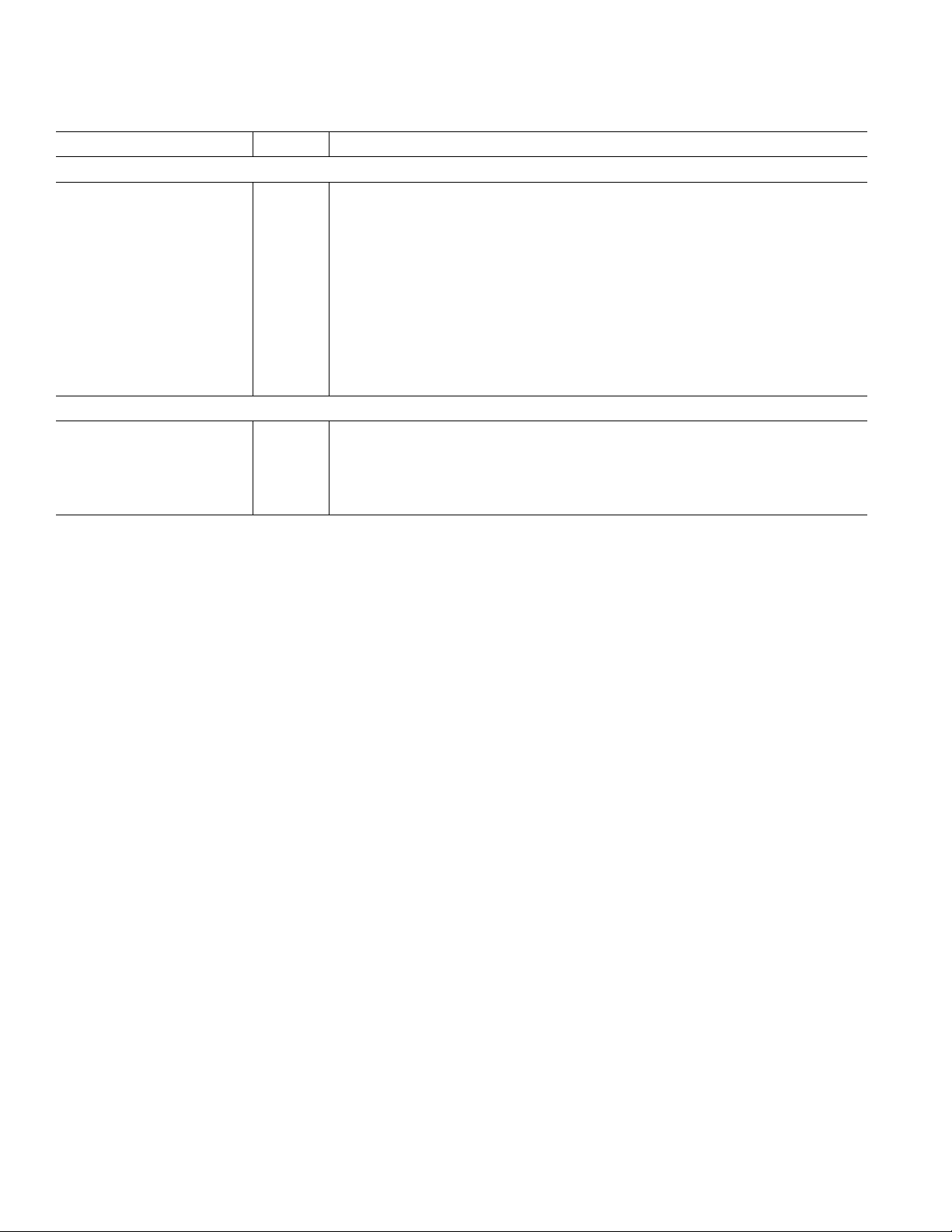

GENERAL TIMING CHARACTERISTICS

1, 2

Test AD6624AS

Parameter (Conditions) Temp Level Min Typ Max Unit

CLK Timing Requirements:

t

CLK

t

CLKL

t

CLKH

CLK Period Full I 10 ns

CLK Width Low Full IV 4.5 0.5 × t

CLK Width High Full IV 4.5 0.5 × t

CLK

CLK

ns

ns

RESET Timing Requirement:

t

RESL

RESET Width Low Full I 30.0 ns

Input Wideband Data Timing Requirements:

t

SI

t

HI

Input to ↑CLK Setup Time Full IV 0.8 ns

Input to ↑CLK Hold Time Full IV 2.0 ns

Level Indicator Output Switching Characteristic:

t

DLI

↑CLK to LI (A–A, B; B–A, B) Output Delay Time Full IV 3.8 12.6 ns

SYNC Timing Requirements:

t

SS

t

HS

Serial Port Timing Requirements (SBM = 1):

Switching Characteristics:

t

DSCLK1

t

DSCLKH

t

DSCLKL

t

DSCLKLL

t

DSDFS

t

DSDFE

t

DSDO

t

DSDR

t

DDR

SYNC (A, B, C, D) to ↑CLK Setup Time Full IV 1.0 ns

SYNC (A, B, C, D) to ↑CLK Hold Time Full IV 2.0 ns

3

↑CLK to ↑SCLK Delay (Divide by 1) Full IV 3.9 13.4 ns

↑CLK to ↑SCLK Delay (For Any Other Divisor) Full IV 4.4 14.0 ns

↑CLK to ↓SCLK Delay (Divide by 2 or Even #) Full IV 3.25 6.7 ns

↓CLK to ↓SCLK Delay (Divide by 3 or Odd #) Full IV 3.8 6.9 ns

↑SCLK to SDFS Delay Full IV 0.2 5.3 ns

↑SCLK to SDFE Delay Full IV –0.4 +4.7 ns

↑SCLK to SDO Delay Full IV –1.0 +4.0 ns

↑SCLK to DR Delay Full IV –0.3 +4.6 ns

↑CLK to DR Delay Full IV 5.4 17.6 ns

Input Characteristics:

t

SSI

t

HSI

Serial Port Timing Requirements (SBM = 0):

Switching Characteristics:

t

SCLK

t

SCLKL

t

SCLKH

t

DSDFE

t

DSDO

t

DSDR

SDI to ↓SCLK Setup Time Full IV 2.4 ns

SDI to ↓SCLK Hold Time Full IV 3.0 ns

3

SCLK Period Full IV 16 ns

SCLK Low Time (When SDIV = 1, Divide by 1) Full IV 5.0 ns

SCLK High Time (When SDIV = 1, Divide by 1) Full IV 5.0 ns

↑SCLK to SDFE Delay Full IV 3.8 15.4 ns

↑SCLK to SDO Delay Full IV 3.7 15.2 ns

↑SCLK to DR Delay Full IV 3.9 15.9 ns

Input Characteristics:

t

SSF

t

HSF

t

SSI

t

HSI

NOTES

1

All Timing Specifications valid over VDD range of 2.375 V to 2.675 V and VDDIO range of 3.0 V to 3.6 V.

2

C

LOAD

3

The timing parameters for SCLK, SDFS, SDFE, SDO, SDI, and DR apply to all four channels (0, 1, 2, and 3). The slave serial port’s (SCLK) operating frequency is

limited to 62.5 MHz.

Specifications subject to change without notice.

SDFS to ↑SCLK Setup Time Full IV 1.9 ns

SDFS to ↑SCLK Hold Time Full IV 0.7 ns

SDI to ↓SCLK Setup Time Full IV 2.4 ns

SDI to ↓SCLK Hold Time Full IV 2.0 ns

= 40 pF on all outputs unless otherwise specified.

–4–

REV. 0

AD6624A

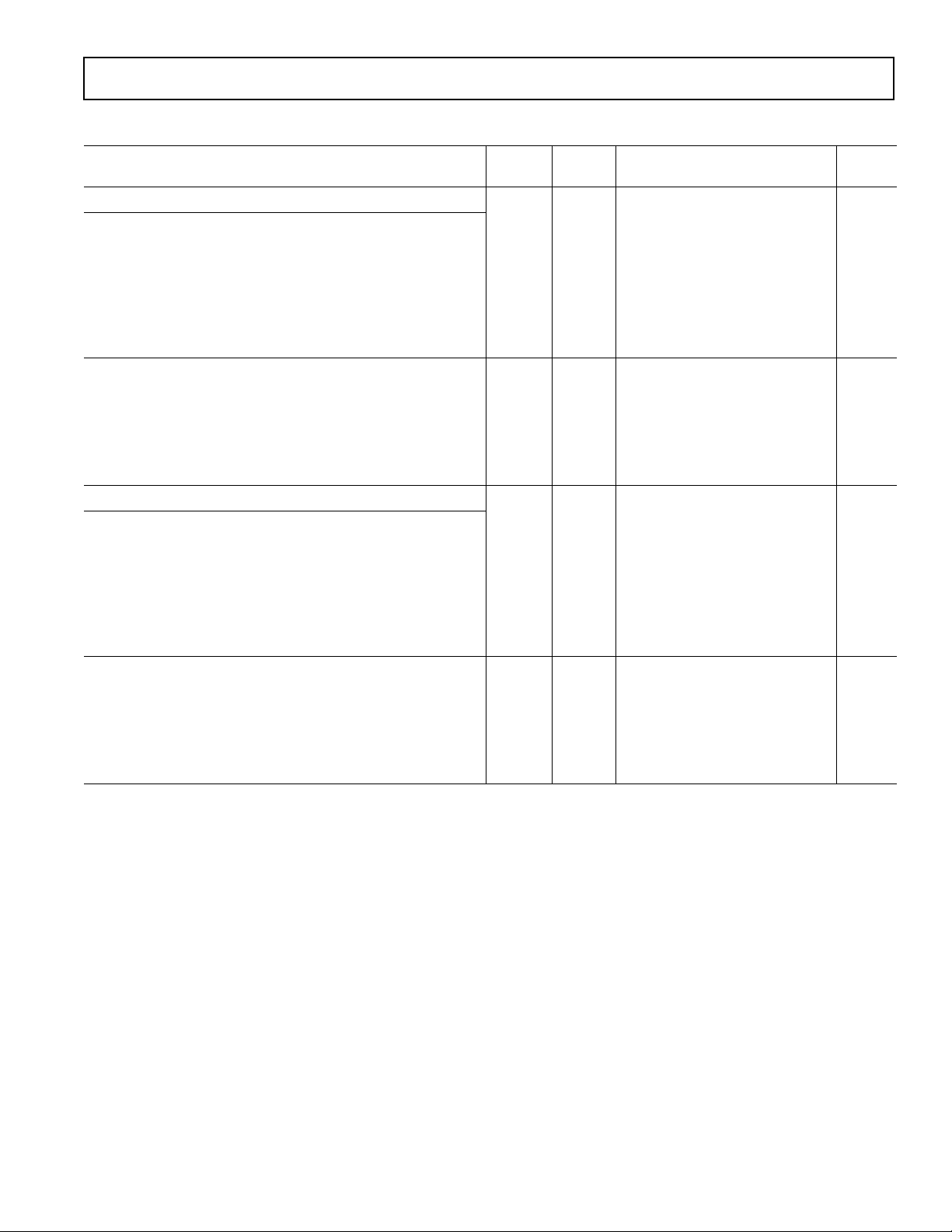

MICROPROCESSOR PORT TIMING CHARACTERISTICS

1, 2

Test AD6624AS

Parameter (Conditions) Temp Level Min Typ Max Unit

MICROPROCESSOR PORT, MODE INM (MODE = 0)

MODE INM Write Timing:

t

SC

t

HC

t

HWR

t

SAM

t

HAM

t

DRDY

t

ACC

Control3 to ↑CLK Setup Time Full IV 5.5 ns

Control3 to ↑CLK Hold Time Full IV 1.0 ns

WR(RW) to RDY(DTACK) Hold Time Full IV 8.0 ns

Address/Data to WR(RW) Setup Time Full IV –0.5 ns

Address/Data to RDY(DTACK) Hold Time Full IV 7.0 ns

WR(RW) to RDY(DTACK) Delay Full IV 4.0 ns

WR(RW) to RDY(DTACK) High Delay Full IV 4 × t

CLK

5 × t

CLK

9 × t

CLK

ns

MODE INM Read Timing:

t

SC

t

HC

t

SAM

t

HAM

t

DRDY

t

ACC

Control3 to ↑CLK Setup Time Full IV 4.0 ns

Control3 to ↑CLK Hold Time Full IV 2.0 ns

Address to RD(DS) Setup Time Full IV 0.0 ns

Address to Data Hold Time Full IV 7.0 ns

RD(DS) to RDY(DTACK) Delay Full IV 4.0 ns

RD(DS) to RDY(DTACK) High Delay Full IV 8 × t

CLK

10 × t

CLK

13 × t

CLK

ns

MICROPROCESSOR PORT, MODE MNM (MODE = 1)

MODE MNM Write Timing:

t

SC

t

HC

t

HDS

t

HRW

t

SAM

t

HAM

t

ACC

Control3 to ↑CLK Setup Time Full IV 5.5 ns

Control3 to ↑CLK Hold Time Full IV 1.0 ns

DS(RD) to DTACK(RDY) Hold Time Full IV 8.0 ns

RW(WR) to DTACK(RDY) Hold Time Full IV 8.0 ns

Address/Data to RW(WR) Setup Time Full IV –0.5 ns

Address/Data to RW(WR) Hold Time Full IV 7.0 ns

RW(WR) to DTACK(RDY) Low Delay Full IV 4 × t

CLK

5 × t

CLK

9 × t

CLK

ns

MODE MNM Read Timing:

t

SC

t

HC

t

SAM

t

HAM

t

ZD

t

ACC

NOTES

1

All Timing Specifications valid over VDD range of 2.375 V to 2.675 V and VDDIO range of 3.0 V to 3.6 V.

2

C

= 40 pF on all outputs unless otherwise specified.

LOAD

3

Specification pertains to control signals: RW, (WR), DS, (RD), CS.

Specifications subject to change without notice.

Control3 to ↑CLK Setup Time Full IV 4.0 ns

Control3 to ↑CLK Hold Time Full IV 2.0 ns

Address to DS(RD) Setup Time Full IV 0.0 ns

Address to Data Hold Time Full IV 7.0 ns

Data Three-State Delay Full IV 7.0 ns

DS(RD) to DTACK(RDY) Low Delay Full IV 8 × t

CLK

10 × t

CLK

13 × t

CLK

ns

REV. 0

–5–

AD6624A

R

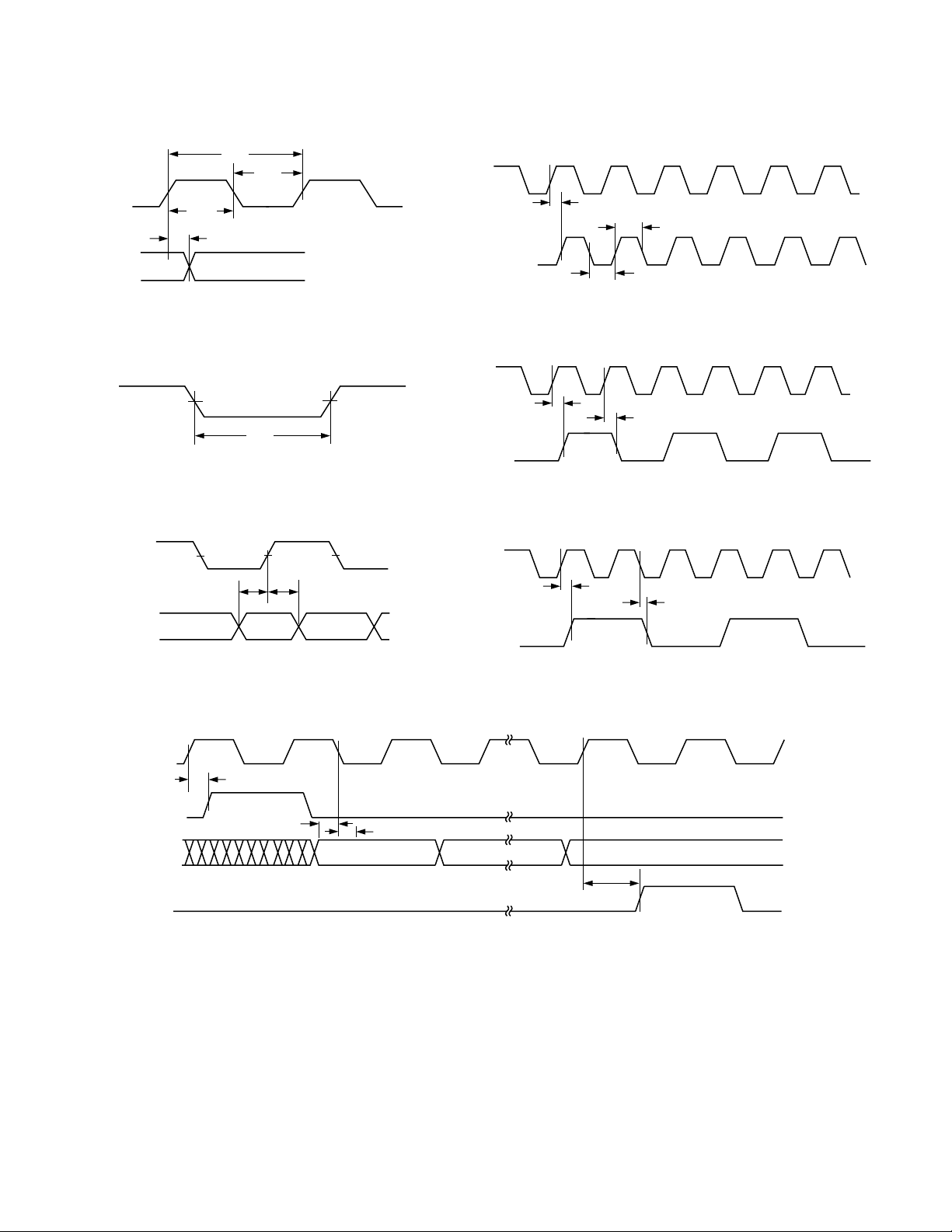

TIMING DIAGRAMS

CLK

t

CLKH

LIA-A

LIA-B

LIB-A

LIB-B

Figure 1. Level Indicator Output Switching

Characteristics

ESET

t

CLK

t

CLKL

t

DLI

CLK

SCLK

t

DSCLKH

t

SCLKL

t

SCLKH

Figure 4. SCLK Switching Characteristics (Divide by 1)

CLK

t

DSCLKH

t

SSF

SCLK

t

SCLKL

Figure 2.

CLK

IN[13:0]

EXP[2:0]

RESET

Timing Requirements

t

SItHI

DATA

Figure 3. Input Data Timing Requirements

SCLK

t

DSDFS

SDFS

SDI

SDFE

t

SSI

t

DATA n

HSI

Figure 7. Serial Port Switching Characteristics

Figure 5. SCLK Switching Characteristic (Divide by 2 or

EVEN Integer)

CLK

t

DSCLKH

SCLK

t

DSCLKLL

Figure 6. SCLK Switching Characteristic (Divide by 3 or

ODD Integer)

t

DSDFE

–6–

REV. 0

AD6624A

CLK

IN[13:0]

EXP[2:0]

IEN

t

SI

t

HI

t

DSDO

SCLK

SDO

SDFE

I

15

I

14

Q

Figure 8. SDO, SDFE Switching Characteristics

CLK

t

DDR

DR

Figure 9. CLK, DR Switching Characteristics

SCLK

t

DSDR

DR

Figure 10. SCLK, DR Switching Characteristics

t

DSDFE

1

Q

0

SCLK

SDFS

t

SSF

t

HSF

Figure 11. SDFS Timing Requirements (SBM = 0)

Figure 12. Input Timing for A and B Channels

CLK

SYNCA

SYNCB

SYNCC

SYNCD

t

SS

t

HS

Figure 13. SYNC Timing Inputs

REV. 0

–7–

AD6624A

[

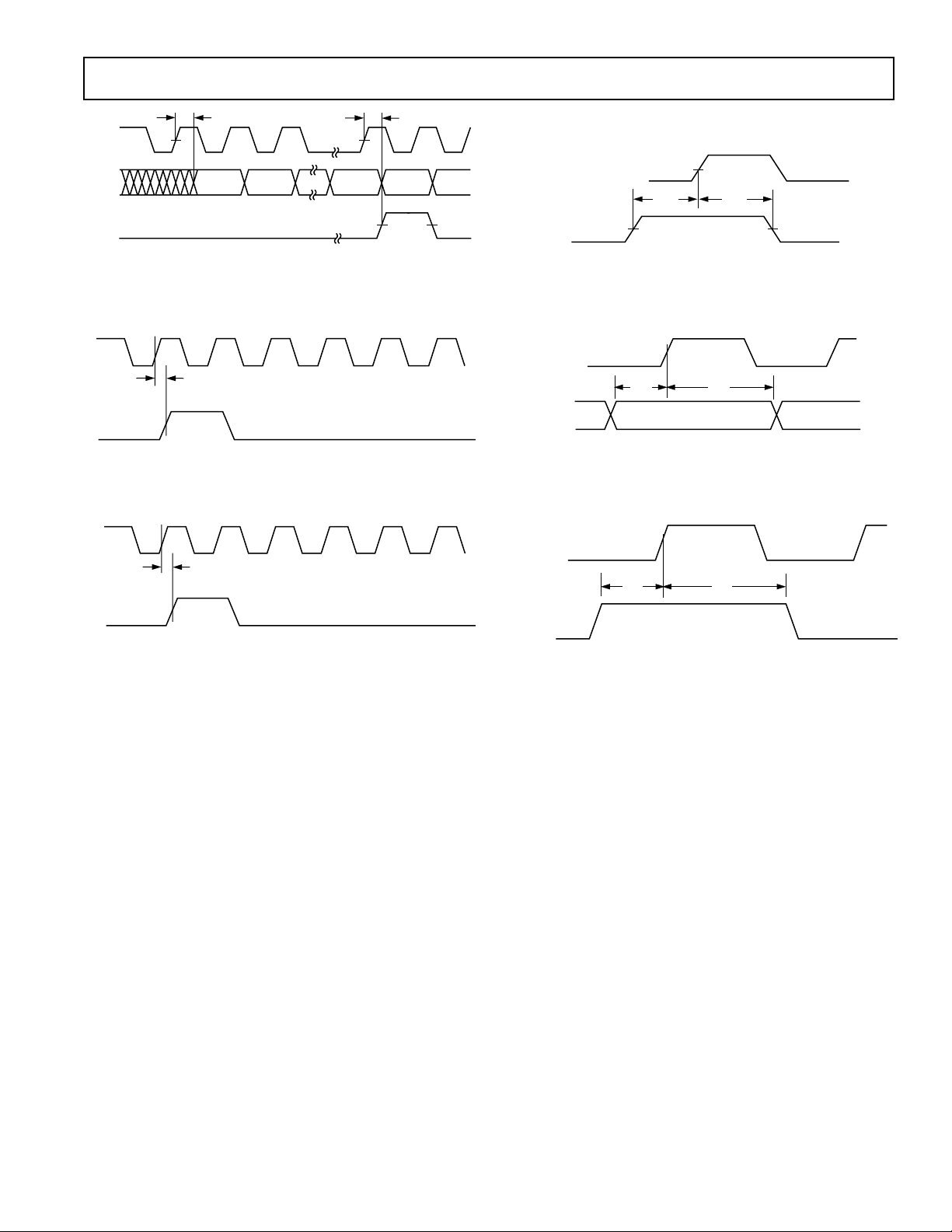

TIMING DIAGRAMS—INM MICROPORT MODE

CLK

RD(DS)

t

WR(RW )

CS

A[2:0]

D[7:0]

RDY

(DTACK)

NOTES

ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS TIME IS

1. t

ACC

MEASURED FROM FE OF WR TO THE RE OF RDY.

REQUIRES A MAXIMUM 9 CLK PERIODS.

2. t

ACC

SC

VALI D DATA

t

DRDY

t

ACC

t

t

HAM

HAM

t

SAM

VALID ADDRESS

t

SAM

t

t

HC

HWR

Figure 14. INM Microport Write Timing Requirements

TIMING DIAGRAMS—MNM MICROPORT MODE

CLK

t

t

SC

t

VALI D DATA

t

ACC

t

t

HDS

HAM

HAM

DS(RD)

RW(WR)

CS

t

SAM

A[2:0]

D[7:0]

DTACK

(RDY)

NOTES

t

1.

ACC

MEASURED FROM FE OF DS TO THE FE OF DTACK.

t

2.

ACC

VALID ADDRESS

t

SAM

ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS TIME IS

REQUIRES A MAXIMUM 9 CLK PERIODS.

HC

t

HRW

t

DDTACK

Figure 16. MNM Microport Write Timing Requirements

CLK

t

HAM

t

HC

t

t

SAM

SC

VALID ADDRESS

t

ZD

t

DRDY

t

ACC

t

DD

VALID DATA

RD (DS)

WR(RW)

CS

A[2:0]

D[7:0]

RDY

(DTACK)

NOTES

t

ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS

1.

ACC

TIME IS MEASURED FROM FE OF WR TO THE RE OF RDY.

t

REQUIRES A MAXIMUM OF 13 CLK PERIODS AND APPLIES TO

2.

ACC

2:0] = 7, 6, 5, 3, 2, 1

A

Figure 15. INM Microport Read Timing Requirements

CLK

t

t

SC

RD(DS)

WR(RW)

CS

t

SAM

t

ZD

A[2:0]

t

D[7:0]

DTACK

(RDY)

NOTES

t

ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS TIME IS

1.

ACC

MEASURED FROM FE OF DS TO THE FE OF DTACK.

t

REQUIRES A MAXIMUM 13 CLK PERIODS.

2.

ACC

ZD

t

ACC

t

t

DD

HDS

HC

VALID ADDRESS

t

HAM

VALID DATA

t

DDTACK

t

ZD

Figure 17. MNM Microport Read Timing Requirements

–8–

REV. 0

AD6624A

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6 V

Input Voltage . . . . . . . . . . . . –0.3 V to +5.3 V (5 V Tolerant)

Output Voltage Swing . . . . . . . . . . –0.3 V to VDDIO + 0.3 V

Load Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200 pF

Junction Temperature Under Bias . . . . . . . . . . . . . . . . 125°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (5 sec) . . . . . . . . . . . . . . . . . . . . . . . 280°C

*Stresses greater than those listed above may cause permanent damage to the

device. These are stress ratings only; functional operation of the device at these or

any other conditions greater than those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

Thermal Characteristics

196-Lead Ball Grid Array:

θ

= 26.3°C/W, No Airflow

JA

= 22°C/W, 200 LFPM Airflow

θ

JA

Thermal measurements made in the horizontal position on

a 4-layer board.

ORDERING GUIDE

Model Temperature Range Package Description Option

AD6624AABC –40°C to +85°C (Ambient) 196-Lead BGA (Ball Grid Array) BC-196

AD6624AS/PCB Evaluation Board with AD6624A and Software

EXPLANATION OF TEST LEVELS

I. 100% Production Tested.

II. 100% Production Tested at 25°C, and Sample Tested at

Specified Temperatures.

III. Sample Tested Only.

IV. Parameter Guaranteed by Design and Analysis.

V. Parameter is Typical Value Only.

VI. 100% Production Tested at 25°C, and Sample Tested at

Temperature Extremes.

Package

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD6624A features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0

–9–

AD6624A

A

B

C

D

E

F

G

H

J

K

L

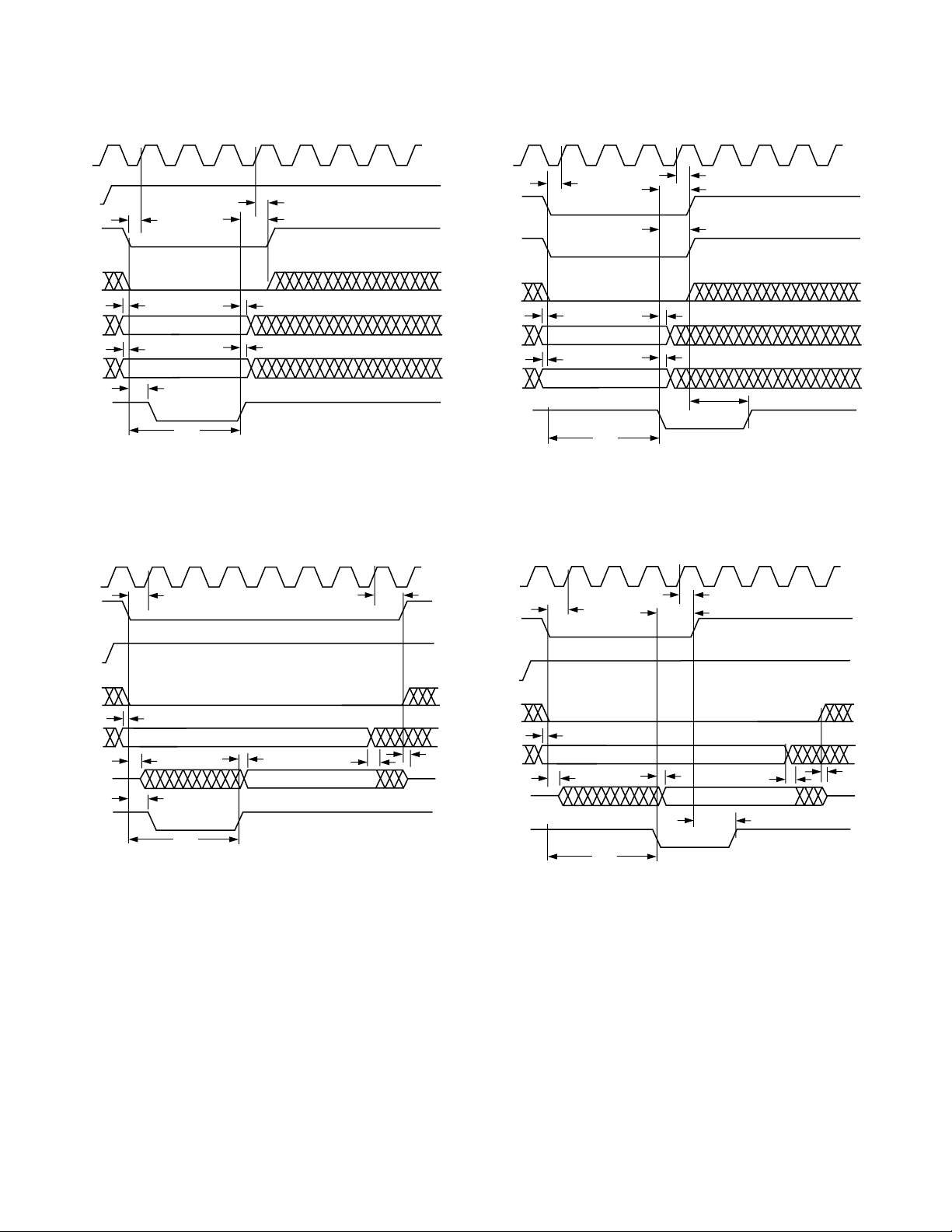

PIN CONFIGURATION

(Top View)

1 2 3 4 5 6 7 8 9 10 11 12 13 14

15mm SQ.

M

N

P

1.0mm.

1234567891011121314

A

NC INB5 INB6 INB12 EXPB1 EXPB0 SDIN3 SDFS3 DR2 SDFS2 NC

B

INB3 INB4 INB7 INB10 INB13 DR3 SDO3 SDFE2 SDO2

C

INB1 INB8 INB9 INB11 EXPB2 SDFE3 SCLK3 SDIN2 SCLK2 SDFE1

D

LIB-B INB2 INB0 SDFS1 DR1 SDIN1

E

CLK IENB LIB-A SDO1

F

EXPA1 EXPA0 EXPA2 SCLK1 DR0 SDIN0

G

INA12 INA13 INA10 SDFE0 SDO0 SCLK0

H

INA11 INA9 INA7 SDFS0 SDIV1 SDIV0

J

INA8 INA6 INA4 SDIV2 SMB0 SDIV3

K

INA5 INA2 INA0 CHIP

L

INA1 INA3 TDI TMS CHIP

M

IENA SYNCD SYNCA D5 D2 DS(RD) A0 MODE TRST TD0

N

P

NC LIA-B SYNCB RESET D6 D3 D0 RW(WR)A1 NC

LIA-A SYNCC D7 D4 D1 DTACK(RDY) A 2 CS TCLK

TOP VIEW

VDDIO VDD VDDIO VDD VDDIO VDD

VDD GND GND GND GND VDDIO

VDDIO GND GND GND GND VDD

VDD GND GND GND GND VDDIO

VDDIO GND GND GND GND VDD

VDD VDDIO VDD VDDIO VDD VDDIO

BALL LEGEND

I/O

GROUND

CORE POWER

RING POWER

NO

ID1 CHIP ID3 CHIP ID0

ID2

NC = NO CONNECT

–10–

REV. 0

PIN FUNCTION DESCRIPTIONS 196-LEAD BGA

Pin No. Type Function

POWER SUPPLY

VDD P 2.5 V Supply

VDDIO P 3.3 V IO Supply

GND G Ground

INPUTS

INA[13:0]

EXPA[2:0]

IENA

INB[13:0]

EXPB[2:0]

IENB

1

1

2

1

1

2

I A Input Data (Mantissa)

I A Input Data (Exponent)

I Input Enable—Input A

I B Input Data (Mantissa)

I B Input Data (Exponent)

I Input Enable—Input B

RESET I Active Low Reset Pin

CLK I Input Clock

SYNCA

SYNCB

SYNCC

SYNCD

SDIN0

SDIN1

SDIN2

SDIN3

CS

CHIP_ID[3:0]

1

1

1

1

1

1

1

1

1

1

I All Sync Pins Go to All Four Output Channels

I All Sync Pins Go to All Four Output Channels

I All Sync Pins Go to All Four Output Channels

I All Sync Pins Go to All Four Output Channels

I Serial Data Input—Channel 0

I Serial Data Input—Channel 1

I Serial Data Input—Channel 2

I Serial Data Input—Channel 3

I Chip Select

I Chip ID Selector

CONTROL

1

SBM0

SCLK0

SCLK1

SCLK2

SCLK3

SDIV[3:0]

SDFS0

SDFS1

SDFS2

SDFS3

1

1

1

1

1

1

1

1

1

I Serial Bus Master—Channel 0 only

I/O Bidirectional Serial Clock—Channel 0

I/O Bidirectional Serial Clock—Channel 1

I/O Bidirectional Serial Clock—Channel 2

I/O Bidirectional Serial Clock—Channel 3

I Serial Clock Divisor—Channel 0

I/O Bidirectional Serial Data Frame Sync—Channel 0

I/O Bidirectional Serial Data Frame Sync—Channel 1

I/O Bidirectional Serial Data Frame Sync—Channel 2

I/O Bidirectional Serial Data Frame SyncvChannel 3

SDFE0 O Serial Data Frame End—Channel 0

SDFE1 O Serial Data Frame End—Channel 1

SDFE2 O Serial Data Frame End—Channel 2

SDFE3 O Serial Data Frame End—Channel 3

MICROPORT CONTROL

D[7:0] I/O/T Bidirectional Microport Data

A[2:0] I Microport Address Bus

DS (RD) I Active Low Data Strobe (Active Low Read)

DTACK (RDY)

2

O/T Active Low Data Acknowledge (Microport Status Bit)

RW (WR) I Read Write (Active Low Write)

MODE I Intel or Motorola Mode Select

AD6624A

REV. 0

–11–

AD6624A

PIN FUNCTION DESCRIPTIONS 196-LEAD BGA (continued)

Pin No. Type Function

OUTPUT

LIA-A O Level Indicator—Input A, Interleaved-Data A

LIA-B O Level Indicator—Input A, Interleaved-Data B

LIB-B O Level Indicator—Input B, Interleaved-Data B

LIB-A O Level Indicator—Input B, Interleaved-Data A

1

SDO0

1

SDO1

1

SDO2

1

SDO3

DR0 O Output Data Ready Indicator—Channel 0

DR1 O Output Data Ready Indicator—Channel 1

DR2 O Output Data Ready Indicator—Channel 3

DR3 O Output Data Ready Indicator—Channel 3

JTAG and BIST

2

TRST

1

TCLK

2

TMS

TDO O/T Test Data Output

2

TDI

NOTES

1

Pins with a pull-down resistor of nominal 70 kΩ.

2

Pins with a pull-up resistors of nominal 70 kΩ.

O/T Serial Data Output—Channel 0

O/T Serial Data Output—Channel 1

O/T Serial Data Output—Channel 2

O/T Serial Data Output—Channel 3

I Test Reset Pin

I Test Clock Input

I Test Mode Input

I Test Data Input

–12–

REV. 0

Loading...

Loading...