4-Channel, 104 MSPS Digital

a

FEATURES

Pin Compatible to the AD6622

18-Bit Parallel Digital IF Output

Real or Interleaved Complex

18-Bit Bidirectional Parallel Digital IF Input/Output

Allows Cascade of Chips for Additional Channels

Clipped or Wrapped Over Range

Two’s Complement or Offset Binary Output

Four Independent Digital Transmitters in Single Package

RAM Coefficient Filter (RCF)

Programmable IF and Modulation for Each Channel

Programmable Interpolating RAM Coefficient Filter

p/4-DQPSK Differential Phase Encoder

3p/8-PSK Linear Encoder

8-PSK Linear Encoder

Programmable GMSK Look-Up Table

Programmable QPSK Look-Up Table

All-Pass Phase Equalizer

Programmable Fine Scaler

Programmable Power Ramp Unit

High Speed CIC Interpolating Filter

Transmit Signal Processor (TSP)

AD6623

Digital Resampling for Noninteger Interpolation Rates

NCO Frequency Translation

Spurious Performance Better than –100 dBc

Separate 3-Wire Serial Data Input for Each Channel

Bidirectional Serial Clocks and Frames

Microprocessor Control

2.5 V CMOS Core, 3.3 V Outputs, 5 V Inputs

JTAG Boundary Scan

APPLICATIONS

Cellular/PCS Base Stations

Micro/Pico Cell Base Stations

Wireless Local Loop Base Stations

Multicarrier, Multimode Digital Transmit

GSM, EDGE, IS136, PHS, IS95, TDS CDMA, UMTS,

CDMA2000

Phased Array Beam Forming Antennas

Software Defined Radio

Tuning Resolution Better than 0.025 Hz

Real or Complex Outputs

SDINA

SDFIA

SDFOA

SCLKA

SDINB

SDFIB

SDFOB

SCLKB

SDINC

SDFIC

SDFOC

SCLKC

SDIND

SDFID

SDFOD

SCLKD

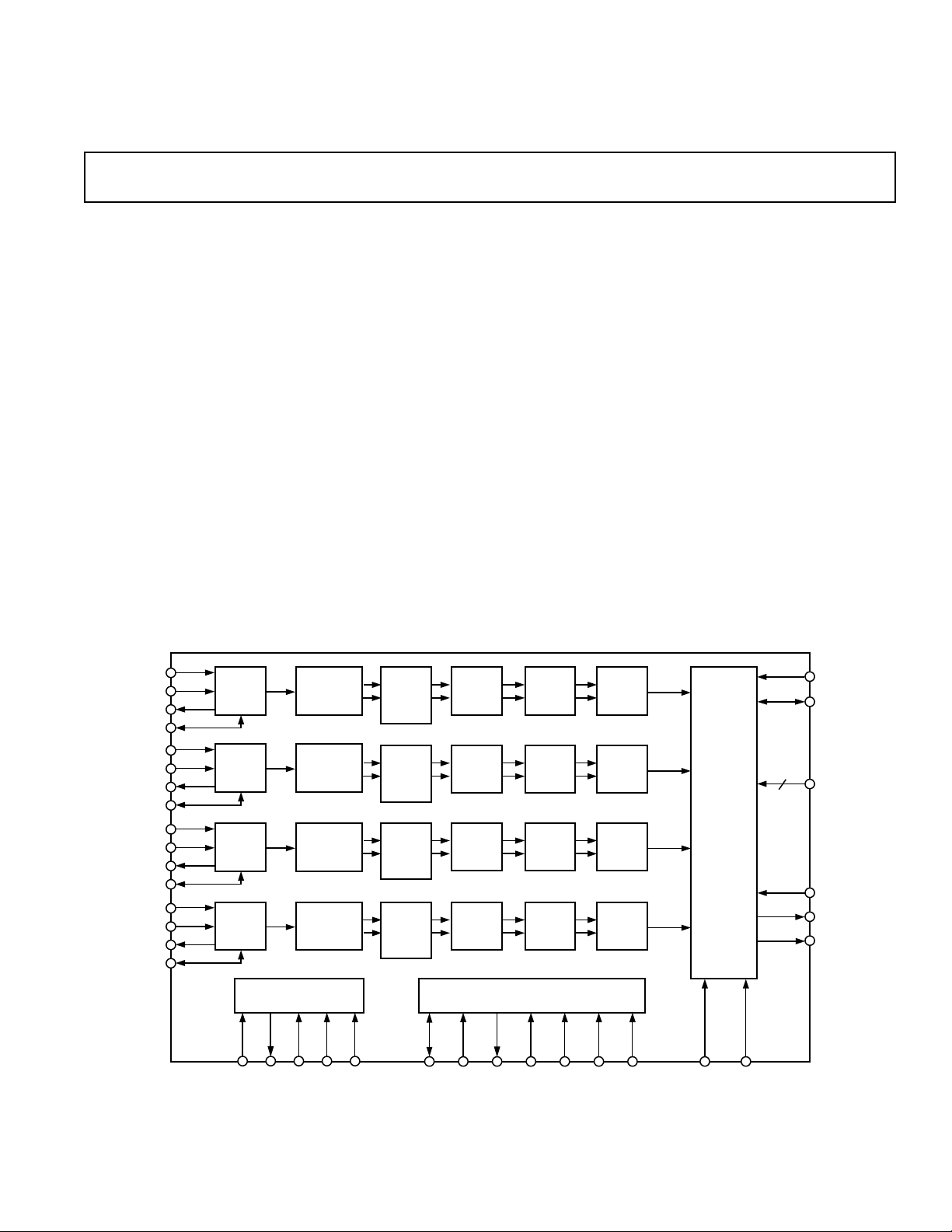

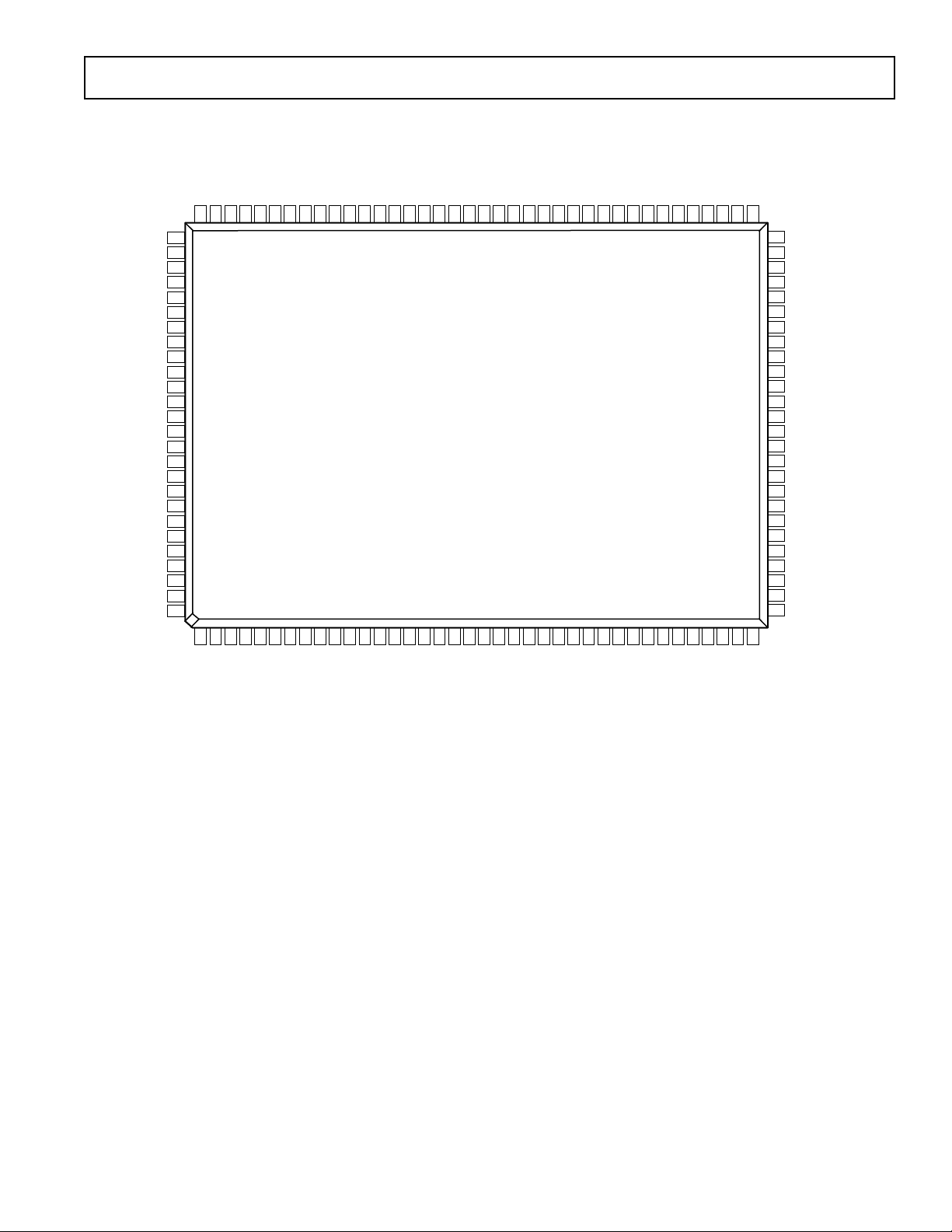

FUNCTIONAL BLOCK DIAGRAM

NCO = NUMERICALLY CONTROLLED

OSCILLATOR/TUNER

SYNC

4

QIN

IN

[17–0]

OEN

QOUT

OUT

[17:0]

DATA

SP

ORT

DATA

SP

ORT

DATA

SP

ORT

DATA

SP

ORT

RAM

COEFFICIENT

FILTER

RAM

COEFFICIENT

FILTER

RAM

COEFFICIENT

FILTER

RAM

COEFFICIENT

FILTER

JTAG

I

Q

I

Q

I

Q

I

Q

SCALER

SCALER

SCALER

SCALER

AND

POWER

RAMP

AND

POWER

RAMP

AND

POWER

RAMP

AND

POWER

RAMP

I

Q

I

Q

I

Q

I

Q

CIC5

FILTER

CIC5

FILTER

CIC5

FILTER

CIC5

FILTER

I

RCIC2

Q

FILTER

I

RCIC2

Q

FILTER

I

RCIC2

Q

FILTER

I

RCIC2

Q

FILTER

MICROPORT

I

Q

I

Q

I

Q

I

Q

NCO

NCO

NCO

NCO

CHAN A

CHAN B

SUMMATION

CHAN C

CHAN D

TDL TMS TCK

TDO

TRST

D[7:0]

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

A[2:0]MODERW

DTACKDS

CS

CLK

RESET

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

AD6623

TABLE OF CONTENTS

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

FUNCTIONAL BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

PRODUCT DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

FUNCTIONAL OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

RECOMMENDED OPERATING CONDITIONS . . . . . . . . . . . . . . . . 4

ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . 4

LOGIC INPUTS (5 V TOLERANT) . . . . . . . . . . . . . . . . . . . . . . . . . 4

LOGIC OUTPUTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

IDD SUPPLY CURRENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

POWER DISSIPATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

GENERAL TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . 5

MICROPROCESSOR PORT TIMING CHARACTERISTICS . . . . . . . . 6

MICROPROCESSOR PORT, MODE INM (MODE = 0) . . . . . . . . . 6

MICROPROCESSOR PORT, MOTOROLA (MODE = 1) . . . . . . . . 6

TIMING DIAGRAMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–9

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . 10

THERMAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

EXPLANATION OF TEST LEVELS . . . . . . . . . . . . . . . . . . . . . . . . . . 10

ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

ESD SENSITIVITY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

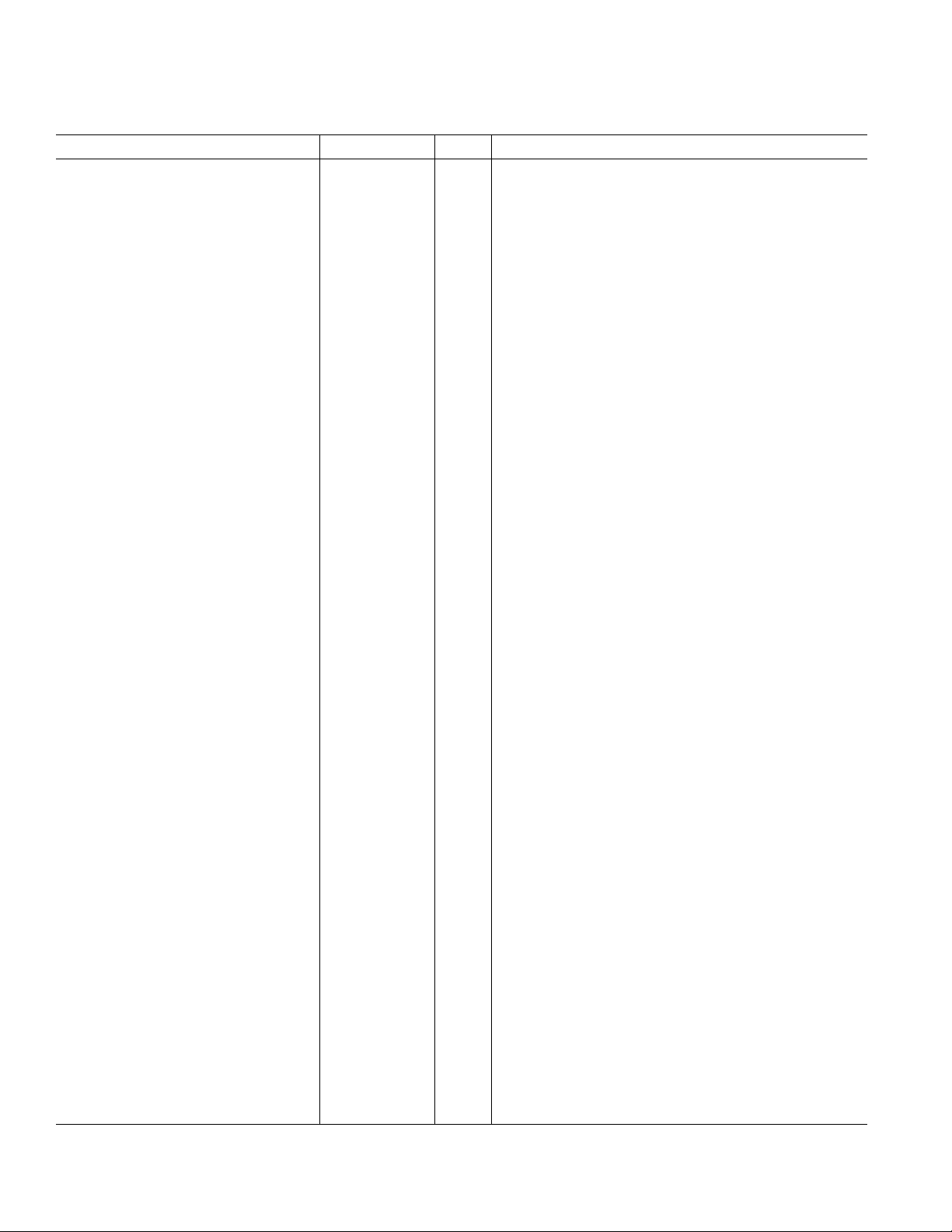

PIN CONFIGURATION – 128-Lead MQFP . . . . . . . . . . . . . . . . . . . . 11

128 PIN FUNCTION DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . 12

PIN CONFIGURATION – 196-Lead BGA . . . . . . . . . . . . . . . . . . . . . . 13

196 PIN FUNCTION DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . 14

POWER SUPPLY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

INPUTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

MICROPORT CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

OUTPUTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

JTAG AND BIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

SERIAL DATA PORT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Serial Master Mode (SCS = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Serial Slave Mode (SCS = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Self-Framing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

External Framing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Serial Port Cascade Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Serial Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

PROGRAMMABLE RAM COEFFICIENT FILTER (RCF) . . . . . . . . . 16

OVERVIEW OF THE RCF BLOCKS . . . . . . . . . . . . . . . . . . . . . . . . 16

INTERPOLATING FIR FILTER . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

RCF CONTROL REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

PSK MODULATOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

/4-DQSPK MODULATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

8-PSK MODULATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3/8-8-PSK MODULATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

MSK Look-Up Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

GMSK Look-Up Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

QPSK Look-Up Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

PHASE EQUALIZER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

SCALE AND RAMP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

FINE SCALING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

RCF POWER RAMPING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

CASCADED INTERGRATOR COMB (CIC)

INTERPOLATING

CIC Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

CIC5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

rCIC2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

NUMERICALLY CONTROLLED

OSCILLATOR/TUNER (NCO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Phase Dither . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Amplitude Dither . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Phase Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

NCO Frequency Update and Phase Offset Update

Hold-Off Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

NCO Control Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

SUMMATION BLOCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

SYNCHRONIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

FILTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

24

Start with No Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Start with Soft Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Start with Pin Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Hop with Soft Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Hop with Pin Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Beam with Soft Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Beam with Pin Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

JTAG INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

SCALING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Multicarrier Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Single Carrier Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

MICROPORT INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

MicroPort Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

EXTERNAL MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Intel Nonmultiplexed Mode (INM) . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Motorola Nonmultiplexed Mode (MNM) . . . . . . . . . . . . . . . . . . . . . 30

External Address 7 Upper Address Register (UAR) . . . . . . . . . . . . . . 30

External Address 6 Lower Address Register (LAR) . . . . . . . . . . . . . . 30

External Address 5 Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

External Address 4 Sleep . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

External Address 3:0 (Data Bytes) . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

INTERNAL CONTROL REGISTERS AND ON-CHIP RAM . . . . . . . . . 31

AD6623 and AD6622 Compatibility

Common Function Registers (not associated

with a particular channel) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Channel Function Registers (0x1XX = Ch. A,

0x2XX = Ch. B, 0x3XX = Ch. C, 0x4XX = Ch. D) . . . . . . . . . . . 31

(0x000) Summation Mode Control . . . . . . . . . . . . . . . . . . . . . . . . . . 33

(0x001) Sync Mode Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

(0x002) BIST Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

(0x003) BIST Result . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Channel Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

(0xn00) Start Update Hold-Off Counter . . . . . . . . . . . . . . . . . . . . . . 34

(0xn01) NCO Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

(0xn02) NCO Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

(0xn03) NCO Frequency Update Hold-Off Counter . . . . . . . . . . . . . 34

(0xn04) NCO Phase Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

(0xn05) NCO Phase Offset Update Hold-Off Counter . . . . . . . . . . . . 34

(0xn06) CIC Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

(0xn07) CIC2 Decimation – 1 (M

(0xn08) CIC2 Interpolation – 1 (L

(0xn09) CIC5 Interpolation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

(0xn0A) Number of RCF Coefficients – 1 . . . . . . . . . . . . . . . . . . . . . 34

(0xn0B) RCF Coefficient Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

(0xn0C) Channel Mode Control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

(0xn0D) Channel Mode Control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

(0xn0E) Fine Scale Factor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

(0xn0F) RCF Time Slot Hold-Off Counter . . . . . . . . . . . . . . . . . . . . 35

(0xn10–0xn11) RCF Phase Equalizer Coefficients . . . . . . . . . . . . . . . 35

(0xn12–0xn15) FIR-PSK Magnitudes . . . . . . . . . . . . . . . . . . . . . . . . 35

(0xn16) Serial Port Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

(0xn17) Power Ramp Length 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

(0xn18) Power Ramp Length 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

(0xn19) Power Ramp Rest Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

(0xn20–0xn1F) Unused . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

(0xn20–0xn3F) Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

(0xn40–0xn17F) Power Ramp Coefficient Memory . . . . . . . . . . . . . . 35

Pseudocode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Write Pseudocode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Read Pseudocode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

USING THE AD6623 TO PROCESS UMTS CARRIERS . . . . . . . . 36

DIGITAL-TO-ANALOG CONVERTER (DAC) SELECTION . . . . . . .

MULTIPLE TSP OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Determining the Number of TSPs to Use . . . . . . . . . . . . . . . . . . . . 36

Programming Mulitple TSPs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Driving Multiple TSP Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . 37

THERMAL MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

PACKAGE OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . 39

– 1) . . . . . . . . . . . . . . . . . . . . . 34

CIC2

– 1) . . . . . . . . . . . . . . . . . . . . 34

CIC2

36

–2–

REV. 0

AD6623

PRODUCT DESCRIPTION

The AD6623 is a 4-channel Transmit Signal Processor (TSP)

that creates high bandwidth data for Transmit Digital-to-Analog

Converters (TxDACs) from baseband data provided by a Digital

Signal Processor (DSP). Modern TxDACs have achieved sufficiently high sampling rates, analog bandwidth, and dynamic range

to create the first Intermediate Frequency (IF) directly.

AD6623 synthesizes multicarrier and multistandard digital signals

to drive these TxDACs. The RAM-based architecture allows easy

reconfiguration for multimode applications. Modulation,

shaping and anti-imaging filters, static equalization, and tuning

functions are combined in a single, cost-effective device. Digital

IF signal processing provides repeatable manufacturing, higher

accuracy, and more flexibility than comparable high dynamic

range analog designs.

The AD6623 has four identical digital TSPs complete with synchro-

circuitry and cascadable wideband channel summation.

nization

AD6623 is pin compatible to AD6622 and can operate in AD6622compatible control register mode.

The AD6623 utilizes a 3.3 V I/O power supply and a 2.5 V core

power supply. All I/O pins are 5 V tolerant. All control registers

and coefficient values are programmed through a generic microprocessor interface. Intel and Motorola microprocessor bus modes

are supported. All inputs and outputs are LVCMOS compatible.

FUNCTIONAL OVERVIEW

Each TSP has five cascaded signal processing elements: a programmable interpolating RAM Coefficient Filter (RCF), a

programmable Scale and Power Ramp, a programmable fifth order

Cascaded Integrator Comb (CIC5) interpolating filter, a flexible

second order Resampling Cascaded Integrator Comb filter (rCIC2),

and a Numerically Controlled Oscillator/Tuner (NCO).

The outputs of the four TSPs are summed and scaled on-chip.

In multicarrier wideband transmitters, a bidirectional bus allows

the Parallel (wideband) IF Input/Output to drive a second

In this operational mode two AD6623 channels

and the other two AD6623 channels drive a second

tiple AD6623s may be combined by driving the INOUT[17:0]

the succeeding with the OUT[17:0] of the preceding chip. The

drive one DAC

DAC.

The

pulse-

DAC.

Mul-

of

INOUT[17:0] can alternatively be masked

allow preceding AD6623’s outputs to be ignored.

Each channel accepts input data from independent serial ports

that may be connected directly to the serial port of Digital Signal

Processor (DSP) chips.

The RCF implements any one of the following functions:

Interpolating Finite Impulse Response (FIR) filter, /4-DQPSK

modulator, 8-PSK modulator, or 3 /8-8-PSK modulator, GMSK

modulator, and QPSK modulator. Each AD6623 channel can

be dynamically switched between the GMSK modulation mode

and the 3 /8-8-PSK modulation mode in order to support the

GSM/EDGE standard. The RCF also implements an Allpass

Phase Equalizer (APE) which meets the requirements of IS-95-A/B

standard (CDMA transmission).

The programmable Scale and Power Ramp block allows power

ramping on a time-slot basis as specified for some air-interface

standards (e.g., GSM, EDGE). A fine scaling unit at the pro-

grammable FIR filter output allows an easy signal amplitude

level adjustment on time slot basis.

The CIC5 provides integer rate interpolation from 1 to 32 and

coarse anti-image filtering. The rCIC2 provides fractional rate

interpolation from 1 to 4096 in steps of 1/512. The wide range

of interpolation factors in each CIC filter stage and a highly

flexible resampler incorporated into rCIC2 makes the AD6623

useful for creating both narrowband and wideband carriers in a

high-speed sample stream.

The high resolution 32-bit NCO allows flexibility in frequency

planning and supports both digital and analog air interface stan-

dards. The high speed NCO tunes the interpolated complex signal

from the rCIC2 to an IF channel. The result may be real or com-

plex.

registers allow intelligent management of the relative phase

independent RF channels. This capability supports the require-

ments for phased array antenna architectures and management

of the wideband peak/power ratio to minimize clipping at the DAC.

The wideband Output Ports can deliver real or complex data.

Complex words are interleaved into real (I) and imaginary (Q)

parts at half the master clock rate.

off by software to

Multicarrier phase synchronization pins and phase

offset

of

REV. 0

–3–

AD6623

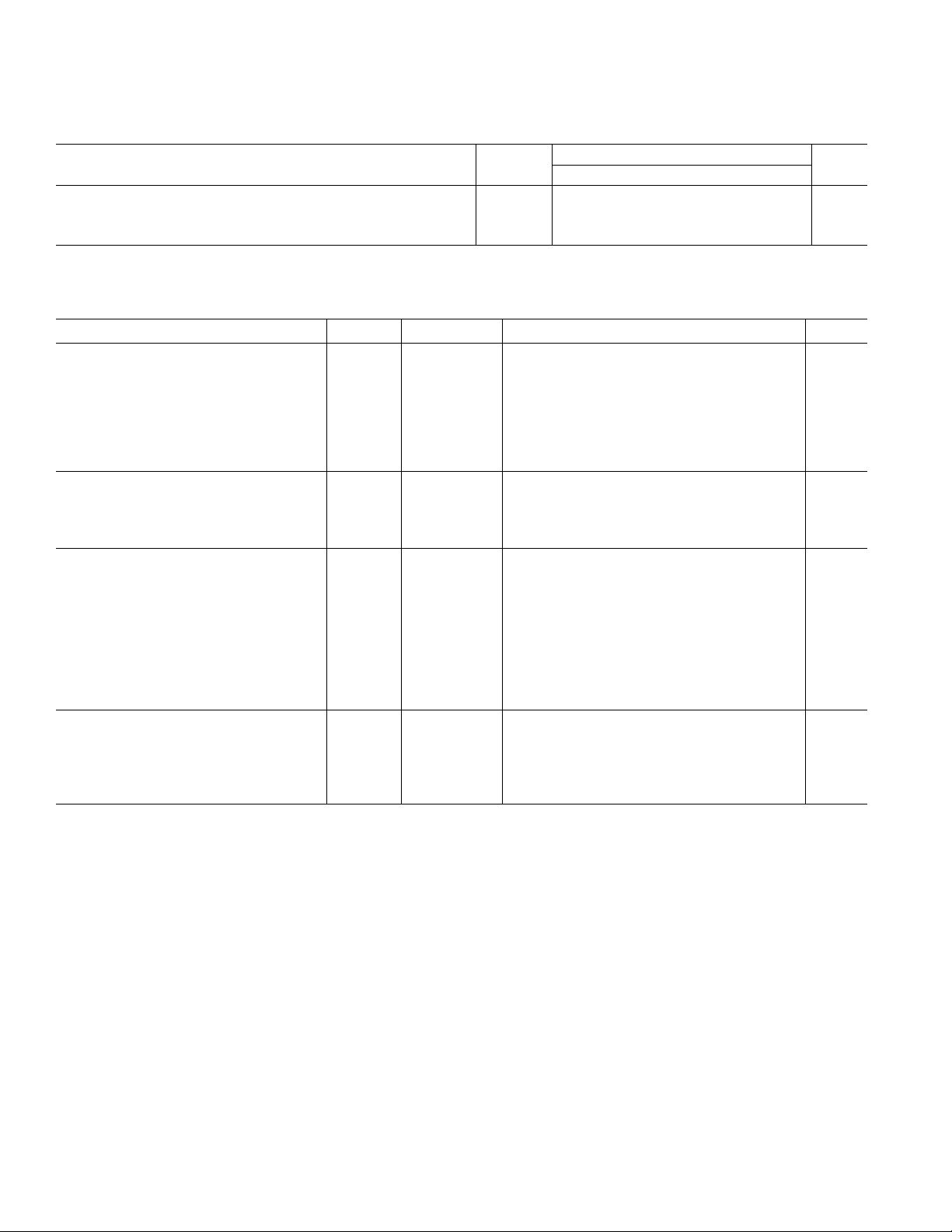

RECOMMENDED OPERATING CONDITIONS

Test AD6623

Parameter Level Min Typ Max Unit

VDD IV 2.25 2.5 2.75 V

VDDIO IV 3.0 3.3 3.6 V

T

AMBIENT

IV –40 +25 +70 °C

ELECTRICAL CHARACTERISTICS

Parameter (Conditions) Temp Test Level Min Typ Max Unit

LOGIC INPUTS (5 V TOLERANT)

Logic Compatibility Full 3.3 V CMOS

Logic “1” Voltage Full IV 2.0 5.0 V

Logic “0” Voltage Full IV –0.3 +0.8 V

Logic “1” Current Full IV 1 10 µA

Logic “0” Current Full IV 0 10 µA

Input Capacitance 25°CV 4 pF

LOGIC OUTPUTS

Logic Compatibility Full 3.3 V CMOS/TTL

Logic “1” Voltage (I

Logic “0” Voltage (IOL = 0.25 mA) Full IV 0.2 0.4 V

IDD SUPPLY CURRENT

CLK = 104 MHz, VDD = 2.75 V* Full IV 422 TBD* mA

CLK = 104 MHz, VDDIO = 3.6 V* Full IV 193 mA

GSM Example: CORE V 232 mA

I/O 56 mA

IS-136 Example: CORE V 207 mA

I/O 55 mA

WBCDMA Example V Tbd mA

Sleep Mode Full IV Tbd TBD mA

POWER DISSIPATION

GSM Example V 740 mW

IS-136 Example V 700 mW

WBCDMA Example V Tbd mW

Sleep Mode Full IV Tbd TBD mW

= 0.25 mA) Full IV 2.0 VDD – 0.2 V

OH

*This specification denotes an absolute maximum supply current for the device. The conditions include all channels active, minimum interpolation in both CIC

stages, and maximum switching of input data. In an actual application the power will be less.

See the Thermal Management section of the data sheet for further details.

–4–

REV. 0

AD6623

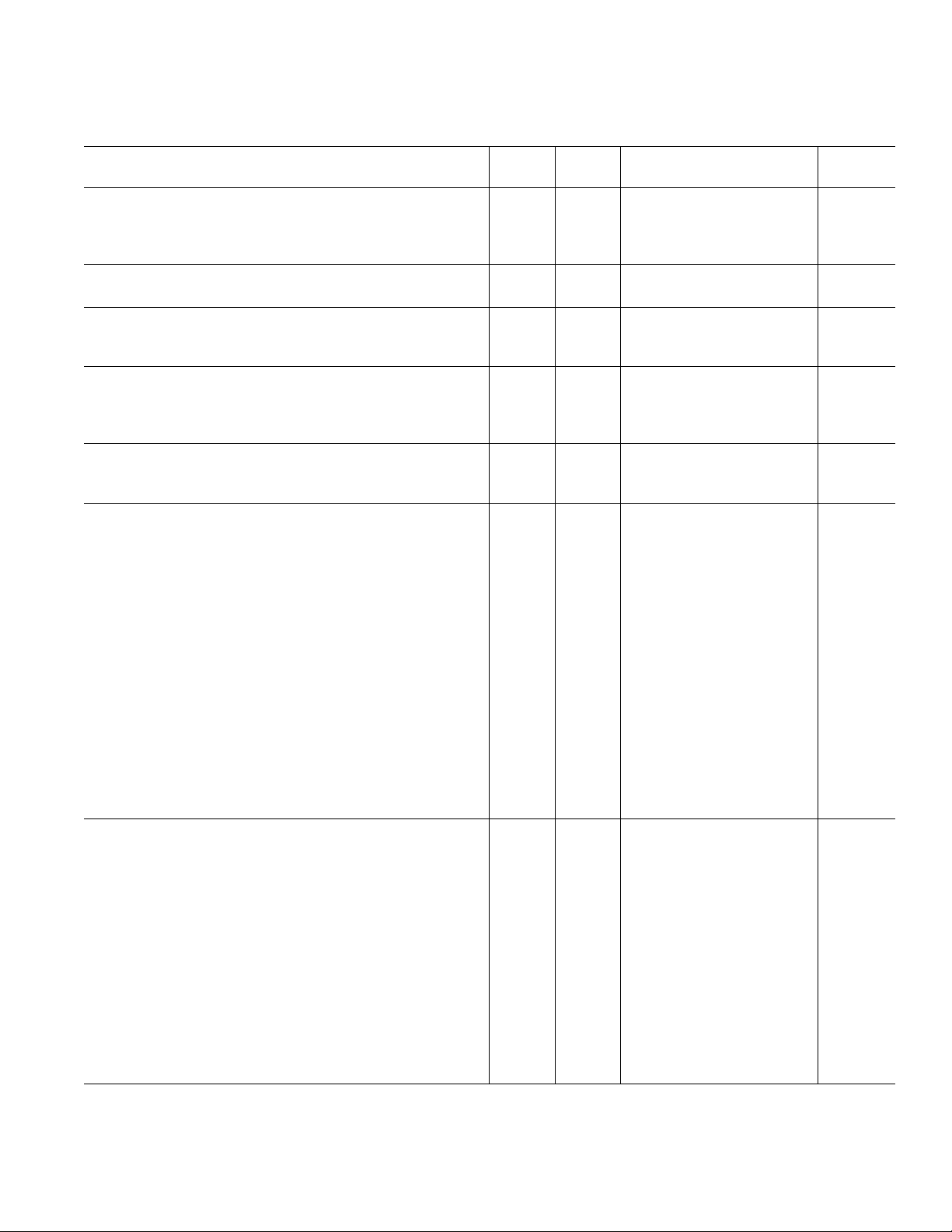

GENERAL TIMING CHARACTERISTICS

1, 2

Test AD6623AS

Parameter (Conditions) Temp Level Min Typ Max Unit

CLK Timing Requirements:

t

CLK

t

CLKL

t

CLKH

CLK Period Full I 9.6 ns

CLK Width Low Full IV 3 ns

CLK Width High Full IV 3 0.5 × t

CLK

ns

RESET Timing Requirement:

t

RESL

RESET Width Low Full I 30.0 ns

Input Data Timing Requirements:

t

SI

t

HI

INOUT[17:0], QIN to ↑CLK Setup Time Full IV 1 ns

INOUT[17:0], QIN to ↑CLK Hold Time Full IV 2 ns

Output Data Timing Characteristics:

t

DO

↑CLK to OUT[17:0], INOUT[17:0],

QOUT Output Delay Time Full IV 2 6 ns

t

DZO

OEN HIGH to OUT[17:0] Active Full IV 3 7.5 ns

SYNC Timing Requirements:

t

SS

t

HS

Master Mode Serial Port Timing Requirements (SCS = 0):

Switching Characteristics

t

DSCLK1

t

DSCLKH

t

DSCLKL

SYNC(0, 1, 2, 3) to ↑CLK Setup Time Full IV 1 ns

SYNC(0, 1, 2, 3) to ↑CLK Hold Time Full IV 2 ns

3

↑CLK to ↑SCLK Delay (divide by 1) Full IV 4 10.5 ns

↑CLK to ↑SCLK Delay (for any other divisor) Full IV 5 13 ns

↑CLK to ↓SCLK Delay

(divide by 2 or even number) Full IV 3.5 9 ns

t

DSCLKLL

↓CLK to ↓SCLK Delay

(divide by 3 or odd number) Full IV 4 10 ns

Channel is Self-Framing

t

SSDI0

t

HSDI0

t

DSFO0A

SDIN to ↑SCLK Setup Time Full IV 1.7 ns

SDIN to ↑SCLK Hold Time Full IV 0 ns

↑SCLK to SDFO Delay Full IV 0.5 3.5 ns

Channel is External-Framing

t

SSFI0

t

HSFI0

t

SSDI0

t

HSDI0

t

DSFO0B

Slave Mode Serial Port Timing Requirements (SCS = 1):

Switching Characteristics

t

SCLK

t

SCLKL

t

SCLKH

SDFI to ↑SCLK Setup Time Full IV 2 ns

SDFI to ↑SCLK Hold Time Full IV 0 ns

SDIN to ↑SCLK Setup Time Full IV 2 ns

SDIN to ↑SCLK Hold Time Full IV 0 ns

↑SCLK to SDFO Delay Full IV 0.5 3 ns

3

SCLK Period Full IV 2 t

CLK

ns

SCLK Low Time Full IV 3.5 ns

SCLK High Time Full IV 3.5 ns

Channel is Self-Framing

t

SSDH

t

HSDH

t

DSFO1

SDIN to ↑SCLK Setup Time Full IV 1 ns

SDIN to ↑SCLK Hold Time Full IV 2.5 ns

↑SCLK to SDFO Delay Full IV 4 10 ns

Channel is External-Framing

t

SSFI1

t

HSFI1

t

SSDI1

t

HSDI1

t

DSFO1

NOTES

1

All Timing Specifications valid over VDD range of 2.375 V to 2.675 V and VDDIO range of 3.0 V to 3.6 V.

2

C

= 40 pF on all outputs (unless otherwise specified).

LOAD

3

The timing parameters for SCLK, SDIN, SDFI, SDFO, and SYNC apply to all four channels (A, B, C, and D).

Specifications subject to change without notice.

SDFI to ↑ SCLK Setup Time Full IV 2 ns

SDFI to ↑SCLK Hold Time Full IV 1 ns

SDIN to ↑SCLK Setup Time Full IV 1 ns

SDIN to ↑SCLK Hold Time Full IV 2.5 ns

↓SCLK to SDFO Delay Full IV 10 ns

REV. 0

–5–

AD6623

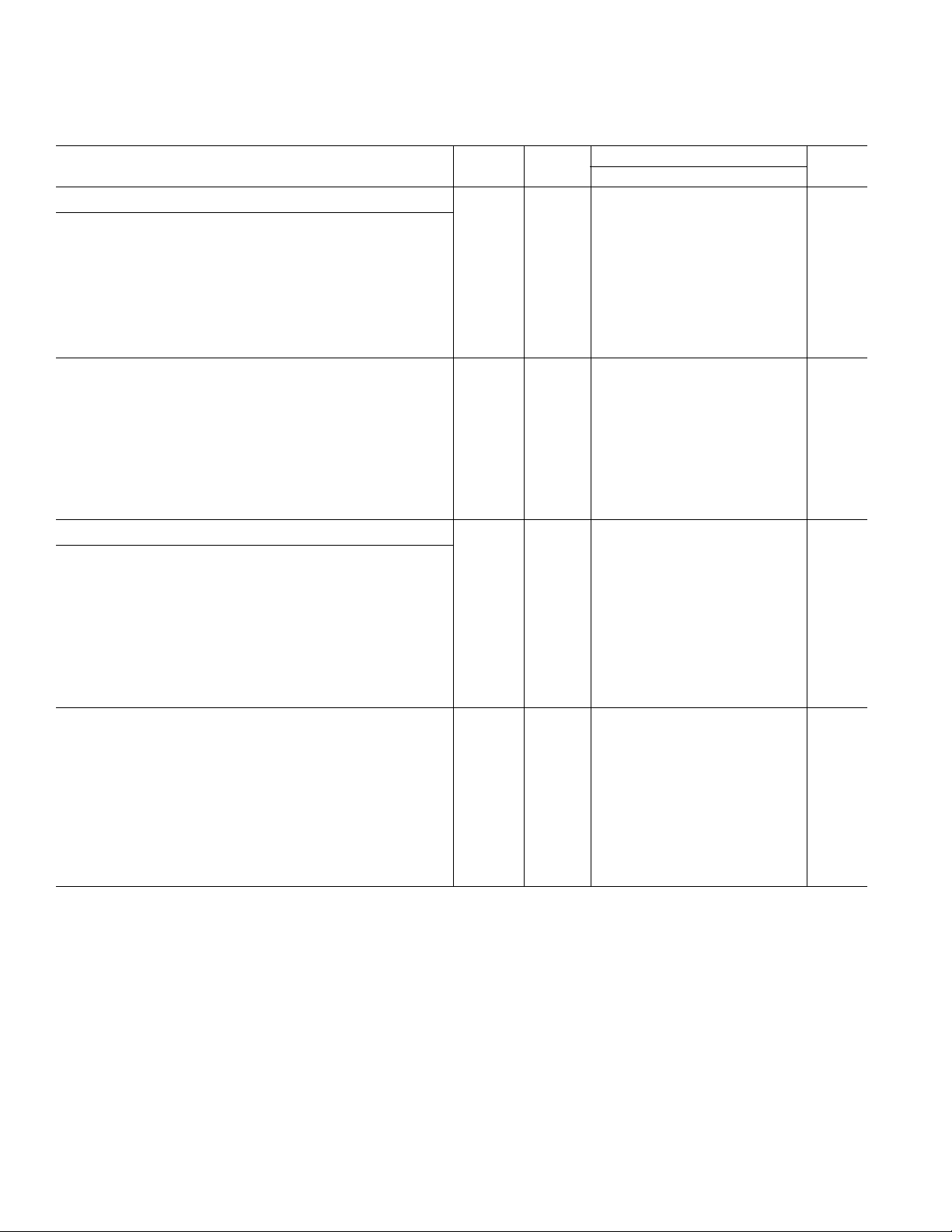

MICROPROCESSOR PORT TIMING CHARACTERISTICS

1, 2

Test AD6623AS

Parameter (Conditions) Temp Level Min Typ Max Unit

MICROPROCESSOR PORT, MODE INM (MODE = 0)

MODE INM Write Timing:

t

SC

t

HC

t

HWR

t

SAM

t

HAM

t

DRDY

t

ACC

Control3 to ↑CLK Setup Time Full IV 4.5 ns

Control3 to ↑CLK Hold Time Full IV 2.0 ns

WR(RW) to RDY(DTACK) Hold Time Full IV 8.0 ns

Address/Data to WR(RW) Setup Time Full IV 3.0 ns

Address/Data to RDY(DTACK) Hold Time Full IV 2.0 ns

WR(RW) to RDY(DTACK) Delay Full IV 4.0 ns

WR(RW) to RDY(DTACK) High Delay Full IV 4 × t

CLK

5 × t

CLK

9 × t

CLK

ns

MODE INM Read Timing:

t

SC

t

HC

t

SAM

t

HAM

t

ZOZ

t

DD

t

DRDY

t

ACC

Control3 to ↑CLK Setup Time Full IV 4.5 ns

Control3 to ↑CLK Hold Time Full IV 2.0 ns

Address to RD(DS) Setup Time Full IV 3.0 ns

Address to Data Hold Time Full IV 2.0 ns

Data Three-State Delay Full IV ns

RDY(DTACK) to Data Delay Full IV ns

RD(DS) to RDY(DTACK) Delay Full IV 4.0 ns

RD(DS) to RDY(DTACK) High Delay Full IV 8 × t

CLK

10 × t

CLK

13 × t

CLK

ns

MICROPROCESSOR PORT, MOTOROLA (MODE = 1)

MODE MNM Write Timing:

t

SC

t

HC

t

HDS

t

HRW

t

SAM

t

HAM

t

DDTACK

t

ACC

Control3 to ↑CLK Setup Time Full IV 4.5 ns

Control3 to ↑CLK Hold Time Full IV 2.0 ns

DS(RD) to DTACK(RDY) Hold Time Full IV 8.0 ns

RW(WR) to DTACK(RDY) Hold Time Full IV 8.0 ns

Address/Data to RW(WR) Setup Time Full IV 3.0 ns

Address/Data to RW(WR) Hold Time Full IV 2.0 ns

DS(RD) to DTACK(RDY) Delay ns

RW(WR) to DTACK(RDY) Low Delay Full IV 4 × t

CLK

5 × t

CLK

9 × t

CLK

ns

MODE MNM Read Timing:

t

SC

t

HC

t

HDS

t

SAM

t

HAM

t

ZD

t

DD

t

DDTACK

t

ACC

NOTES

1

All Timing Specifications valid over VDD range of 2.375 V to 2.675 V and VDDIO range of 3.0 V to 3.6 V.

2

C

= 40 pF on all outputs (unless otherwise specified).

LOAD

3

Specification pertains to control signals: RW, (WR), DS, (RD), CS.

Specifications subject to change without notice.

Control3 to ↑CLK Setup Time Full IV 4.0 ns

Control3 to ↑CLK Hold Time Full IV 2.0 ns

DS(RD) to DTACK(RDY) Hold Time Full IV 8.0 ns

Address to DS(RD) Setup Time Full IV 3.0 ns

Address to Data Hold Time Full IV 2.0 ns

Data Three-State Delay Full IV ns

DTACK(RDY) to Data Delay Full IV ns

DS(RD) to DTACK(RDY) Delay Full IV ns

DS(RD) to DTACK(RDY) Low Delay Full IV 8 × t

CLK

10 × t

CLK

13 × t

CLK

ns

–6–

REV. 0

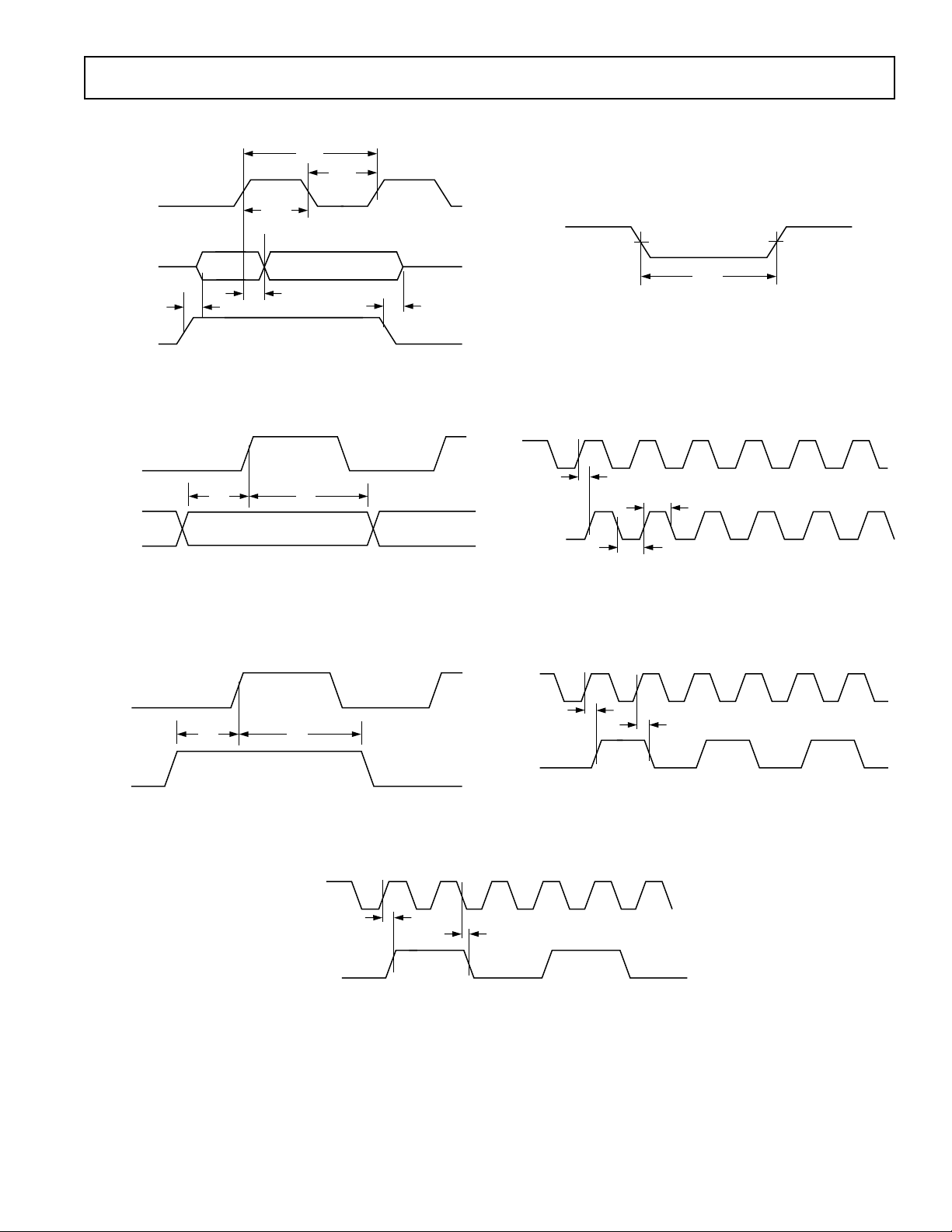

TIMING DIAGRAMS

R

CLK

INOUT[17:0]

OUT[17:0]

QOUT

t

ZO

OEN

AD6623

t

CLK

t

CLKL

t

CLKH

ESET

t

t

DO

t

ZO

RESL

Figure 1. Parallel Output Switching Characteristics

CLK

INOUT[17:0]

QIN

t

SI

t

HI

Figure 2. Wideband Input Timing

CLK

SYNC

t

SS

t

HS

Figure 3. SYNC Timing Inputs

Figure 4.

CLK

SCLK

t

DSCLKH

t

SCLKL

RESET

Timing Requirements

t

SCLKH

Figure 5. SCLK Switching Characteristics (Divide by 1)

CLK

t

DSCLKH

SCLK

t

DSCLKL

Figure 6. SCLK Switching Characteristic (Divide by 2 or

EVEN Integer)

CLK

t

DSCLKH

SCLK

t

DSCLKLL

Figure 7. SCLK Switching Characteristic (Divide by 3 or ODD Integer)

REV. 0

–7–

AD6623

SCLK

SDFO

SDIN

SCLK

SDFO

SDIN

t

DSFO0A

t

SSDI0

DATA n

t

HSDI0

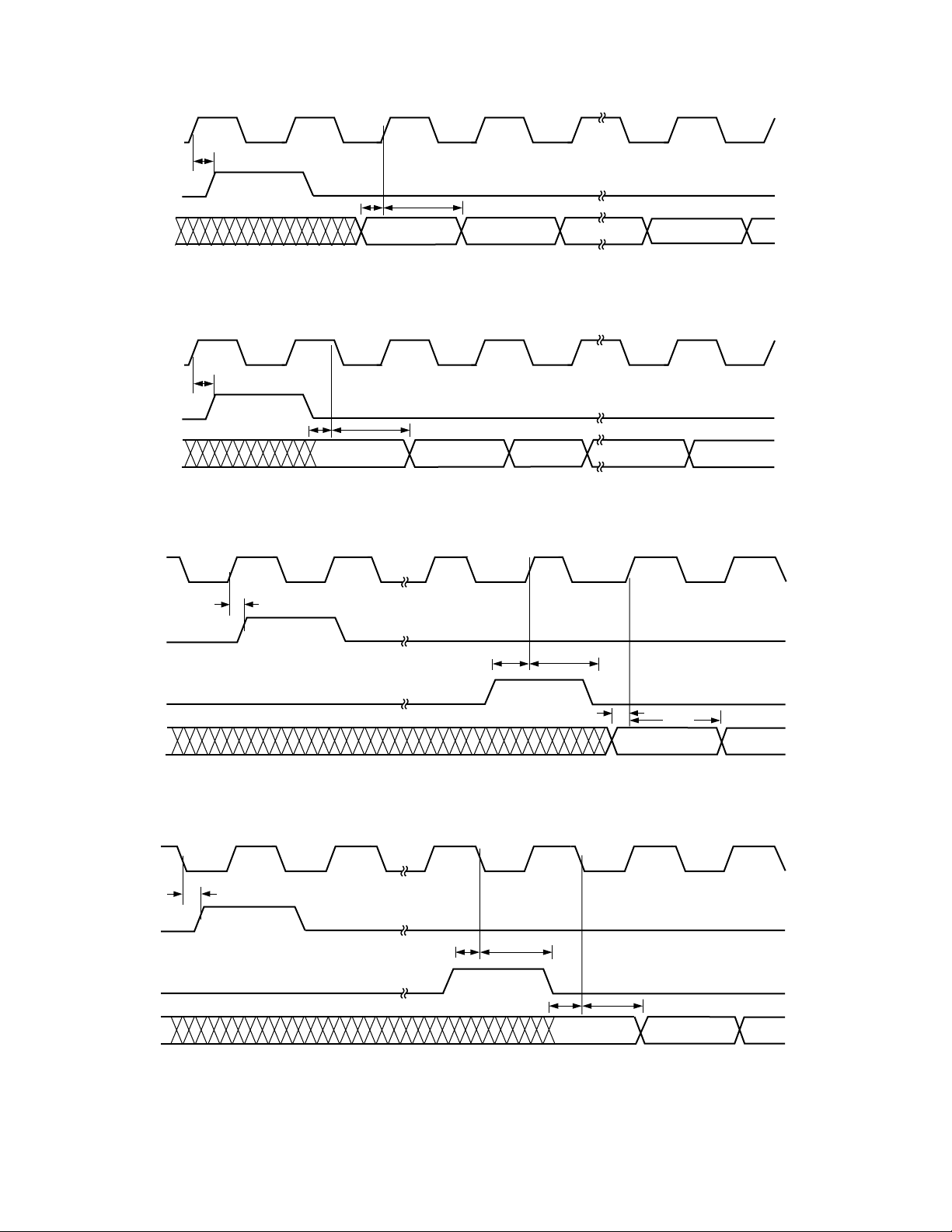

Figure 8. Serial Port Timing, Master Mode (SCS = 0), Channel is Self-Framing

t

DSFO1

t

SSDI1

DATA n

t

HSDI1

Figure 9. Serial Port Timing, Slave Mode (SCS = 1), Channel is Self-Framing

SCLK

SDFO

SDFI

SDIN

SCLK

SDFO

SDFI

SDIN

nCLKs

t

DSFO0B

t

SSDI0

t

HSFI0

t

DATA n

HSDI0

t

SSFI0

Figure 10. Serial Port Timing, Master Mode (SCS = 0), Channel is External-Framing

nCLKs

t

DSFO1

t

SSDI1

t

HSFI1

DATA n

t

HSDI1

t

SSFI1

Figure 11. Serial Port Timing, Slave Mode (SCS = 1), Channel is External-Framing

–8–

REV. 0

AD6623

[

CLK

DS (RD)

RW (WR)

A[2:0]

D[7:0]

DTACK

(RDY)

t

SC

t

SAM

t

ZD

VALID DATA

VALID ADDRESS

t

ACC

t

HC

CS

t

ZD

t

HAM

t

DD

t

DDTACK

t

HDS

NOTES

1.

t

ACC

ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS TIME IS

MEASURED FROM FE OF DS TO THE FE OF DTACK.

2.

t

ACC

REQUIRES A MAXIMUM 13 CLK PERIODS.

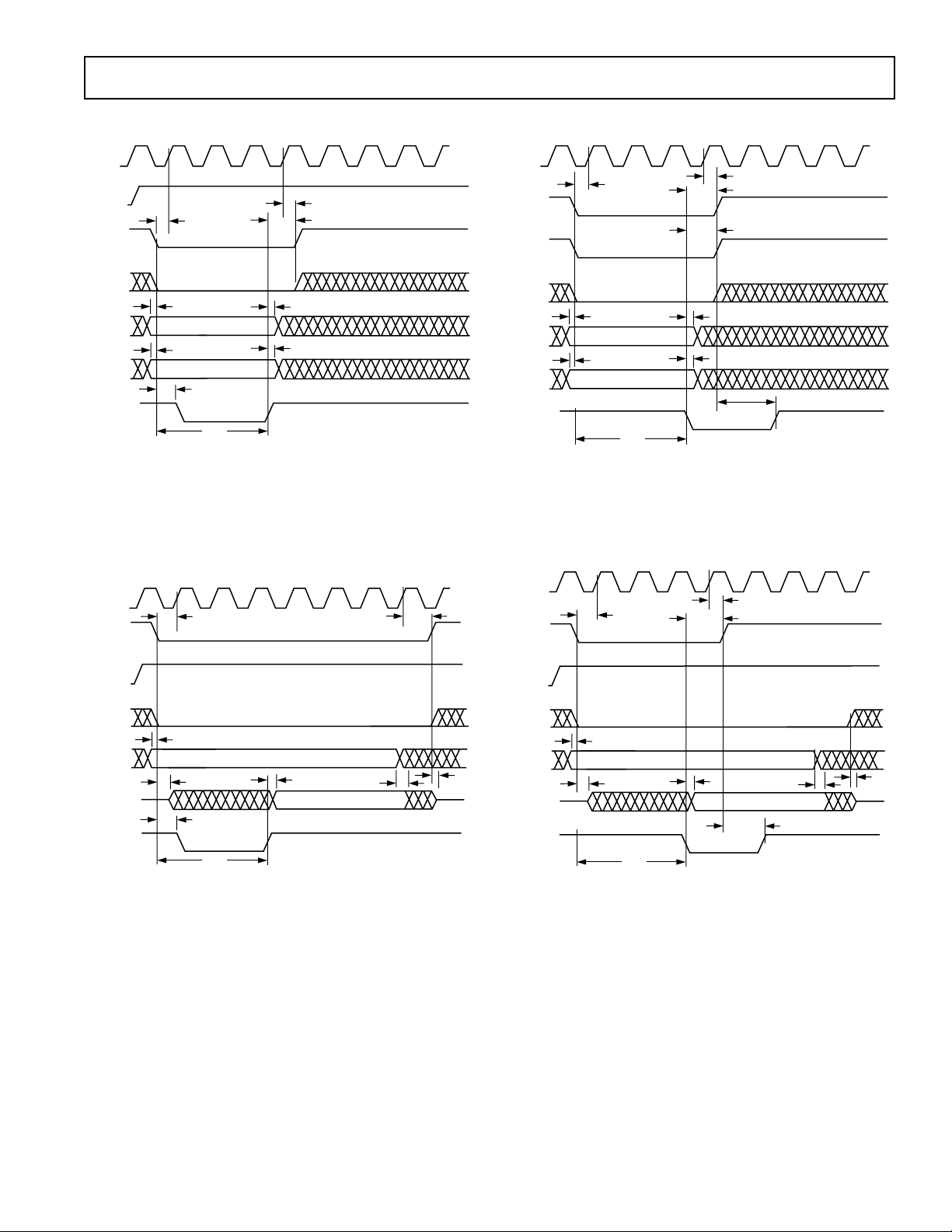

TIMING DIAGRAMS—INM MICROPORT MODE

CLK

RD (DS)

t

WR (RW)

CS

A[2:0]

D[7:0]

RDY

(DTACK)

NOTES

t

ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS TIME IS

1.

ACC

MEASURED FROM FE OF WR TO THE RE OF RDY.

t

REQUIRES A MAXIMUM 9 CLK PERIODS.

2.

ACC

SC

VA LI D DATA

t

DRDY

t

ACC

t

t

HAM

HAM

t

SAM

VALID ADDRESS

t

SAM

t

t

HC

HWR

Figure 12. INM Microport Write Timing Requirements

TIMING DIAGRAMS—MNM MICROPORT MODE

CLK

t

t

SC

t

VA LI D DATA

t

ACC

t

t

HDS

HAM

HAM

DS (RD)

RW (WR)

CS

t

SAM

A[2:0]

D[7:0]

DTACK

(RDY)

NOTES

1.

t

ACC

MEASURED FROM FE OF DS TO THE FE OF DTACK.

2.

t

ACC

VALID ADDRESS

t

SAM

ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS TIME IS

REQUIRES A MAXIMUM 9 CLK PERIODS.

HC

t

HRW

t

DDTACK

Figure 14. MNM Microport Write Timing Requirements

CLK

t

t

SAM

SC

t

ZD

t

DRDY

t

ACC

RD (DS)

WR (RW)

CS

A[2:0]

D[7:0]

RDY

(DTACK)

NOTES

t

ACCESS TIME DEPENDS ON THE ADDRESS ACCESSED. ACCESS

1.

ACC

TIME IS MEASURED FROM FE OF WR TO THE RE OF RDY.

t

REQUIRES A MAXIMUM OF 13 CLK PERIODS AND APPLIES TO

2.

ACC

2:0] = 7, 6, 5, 3, 2, 1

A

Figure 13. INM Microport Read Timing Requirements

REV. 0

VALID ADDRESS

t

DD

VALID DATA

t

HAM

t

HC

t

ZD

Figure 15. Motorola Microport Read Timing Requirements

–9–

AD6623

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6 V

Input Voltage . . . . . . . . . . . . . . –0.3 V to +5 V (5 V Tolerant)

Output Voltage Swing . . . . . . . . . . –0.3 V to VDDIO + 0.3 V

Load Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200 pF

THERMAL CHARACTERISTICS

128-Lead MQFP:

= 33°C/W, no airflow

JA

= 27°C/W, 200 lfpm airflow

JA

= 24°C/W, 400 lfpm airflow

JA

Junction Temperature Under Bias . . . . . . . . . . . . . . . . . 125°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (5 sec) . . . . . . . . . . . . . . . . . . . . . . . 280°C

*Stresses greater than those listed above may cause permanent damage to the

device. These are stress ratings only; functional operation of the devices at these

or any other conditions greater than those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect device reliability.

196-Lead BGA:

= 26.3°C/W, no airflow

JA

= 22°C/W, 200 lfpm airflow

JA

Thermal measurements made in the horizontal position on a

2-layer board.

EXPLANATION OF TEST LEVELS

I. 100% Production Tested

II. 100% Production Tested at 25°C, and Sample Tested at

Specified Temperatures

III. Sample Tested Only

IV. Parameter Guaranteed by Design and Analysis

V. Parameter is Typical Value Only

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD6623AS –40°C to +70°C (Ambient) 128-Lead MQFP (Metric Quad Flatpack) S-128A

AD6623ABC –40°C to +85°C (Ambient) 196-Lead BGA (Ball Grid Array) BC-196

AD6623S/PCB MQFP Evaluation Board with AD6623 and Software

AD6623BC/PCB BGA Evaluation Board with AD6623 and Software

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD6623 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–10–

REV. 0

GND

VDD

SDFIA

TMS

TDO

TDI

SCLKA

VDDIO

SDFOA

SDINA

SCLKB

SDFOB

SDFIB

GND

SDFIC

SDINB

SCLKC

SDFOC

SDINC

VDDIO

SCLKD

SDFOD

SDIND

SDFID

VDD

GND

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

GND

102

1

GND

TCK

101

2

OEN

TRST

100

3

GND

GND

99

4

GND

GND

98

5

GND

INOUT0

GND

97

769

OUT0

OUT1

GND

95

8

OUT2

INOUT1

INOUT2

93

94

10

GND

OUT3

INOUT3

INOUT4

92

12

11

OUT4

OUT5

PIN CONFIGURATION

128-Lead MQFP

VDDIO

INOUT5

INOUT6

INOUT7

INOUT8

GND

GND

GND

INOUT9

90918889879686

83

82

84

AD6623

TOP VIEW

(Not to Scale)

16

15

13

OUT6

14

VDDIO

OUT7

OUT8

1817201922

GND

OUT9

OUT10

GND

21

GND

INOUT11

INOUT12

VDDIO

INOUT10

78

81

79

80

24232625282730

OUT11

OUT12

OUT13

OUT14

INOUT13

INOUT14

INOUT15

INOUT16

SYNC3

GND

INOUT17

QIN

SYNC2

76

7785757374717269706768

343336

31

32

D7

GND

GND

VDDIO

OUT15

29

OUT16

OUT17

GND

QOUT

GND

CLK

353837

GND

GND

VDD

66

D6

GND

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

GND

AD6623

GND

SYNC1

SYNC0

RESET

CS

VDD

A0

A1

A2

MODE

GND

GND

GND

RW(WR)

DTACK(RDY)

DS(RD)

D0

VDD

D1

D2

D3

D4

GND

VDDIO

D5

GND

REV. 0

–11–

AD6623

128 PIN FUNCTION DESCRIPTIONS

Pin Number Mnemonic Type Description

1, 3–5, 9, 19–21, 31, 32, 34–36, 38, 39,

42, 52–54, 64–65, 68, 72, 83–85, 95, 96,

98, 99, 102, 103, 116, 128 GND P Ground Connection

2 OEN

29, 28, 27, 25, 24, 23, 22, 18, 17, 16, 15,

13, 12, 11, 10, 8, 7, 6 OUT[17:0] O/T Parallel Output Data

47, 59, 66, 104, 127 VDD P 2.5 V Supply

14, 26, 41, 78, 90, 110, 122 VDDIO P 3.3 V Supply

30 QOUT O/T When HIGH indicates Q Output Data

33, 37, 40, 43, 44, 45, 46, 48 D[7:0] I/O/T Bidirectional Microport Data

49 DS (RD) I INM Mode: Read Signal, MNM Mode: Data Strobe Signal

50 DTACK

51 RW (WR) I Active HIGH Read, Active Low Write

55 MODE I

56, 57, 58 A[2:0] I Microport Address Bus

60 CS I Chip Select, Active low enable for µP Access

61 RESET

62 SYNC0

63 SYNC1

67 CLK

69 SYNC2

70 QIN

71, 74–77, 79–82, 86–89, 91–94, 97 INOUT[17:0]1I/O Wideband Input/Output Data (Allows Cascade of Multiple

73 SYNC3

100 TRST

101 TCK

105 SDFIA I Serial Data Frame Input—Channel A

106 TMS

107 TDO O Test Data Output

108 TDI

109 SCLKA I/O Bidirectional Serial Clock—Channel A

111 SDFOA O Serial Data Frame Sync Output—Channel A

112 SDINA

113 SCLKB I/O Bidirectional Serial Clock—Channel B

114 SDFOB O Serial Data Frame Sync Output—Channel B

115 SDFIB I Serial Data Frame Input —Channel B

117 SDFIC I Serial Data Frame Input—Channel C

118 SDINB

119 SCLKC I/O Bidirectional Serial Clock—Channel C

120 SDFOC O Serial Data Frame Sync Output—Channel C

121 SDINC

123 SCLKD I/O Bidirectional Serial Clock—Channel D

124 SDFOD O Serial Data Frame Sync Outpu—Channel D

125 SDIND

126 SDFID I Serial Data Frame Input—Channel D

NOTES

1

Pins with a Pull-Down resistor of nominal 70 kΩ.

2

Pins with a Pull-Up resistor of nominal 70 kΩ.

1

(RDY) O

2

1

1

1

1

1

1

2

1

2

1

1

1

1

1

I Active High Output Enable Pin

(Complex Output Mode)

Acknowledgment of a Completed Transaction (Signals when

µP Port Is Ready for an Access) Open Drain, Must Be

Pulled Up Externally

Sets Microport Mode: MODE = 1, MNM Mode; MODE = 0,

INM Mode

I Active Low Reset Pin

I SYNC Signal for Synchronizing Multiple AD6623s

I SYNC Signal for Synchronizing Multiple AD6623s

I Input Clock

I SYNC Signal for Synchronizing Multiple AD6623s

I

When HIGH indicates Q input data (Complex Input Mode)

AD6623 Chips In a System)

I SYNC Signal for Synchronizing Multiple AD6623s

I Test Reset Pin

I Test Clock Input

I Test Mode Select

I Test Data Input

I Serial Data Input—Channel A

I Serial Data Input—Channel B

I Serial Data Input—Channel C

I Serial Data Input—Channel D

–12–

REV. 0

Loading...

Loading...