Low Cost Monolithic

a

FEATURES

Low Cost

Single or Dual Supply, 5 V to 36 V, 65 V to 618 V

Full-Scale Frequency Up to 500 kHz

Minimum Number of External Components Needed

Versatile Input Amplifier

Positive or Negative Voltage Modes

Negative Current Mode

High Input Impedance, Low Drift

Low Power: 2.0 mA Quiescent Current

Low Offset: 1 mV

PRODUCT DESCRIPTION

The AD654 is a monolithic V/F converter consisting of an input

amplifier, a precision oscillator system, and a high current output stage. A single RC network is all that is required to set up

any full scale (FS) frequency up to 500 kHz and any FS input

voltage up to ±30 V. Linearity error is only 0.03% for a 250 kHz

FS, and operation is guaranteed over an 80 dB dynamic range.

The overall temperature coefficient (excluding the effects of external components) is typically

ates from a single supply of 5 V to 36 V and consumes only

2.0 mA quiescent current.

The low drift (4 µV/°C typ) input amplifier allows operation

directly from small signals such as thermocouples or strain

gauges while offering a high (250 MΩ) input resistance. Unlike

most V/F converters, the AD654 provides a square-wave output,

and can drive up to 12 TTL loads, optocouplers, long cables, or

similar loads.

±50 ppm/°C. The AD654 oper-

Voltage-to-Frequency Converter

AD654

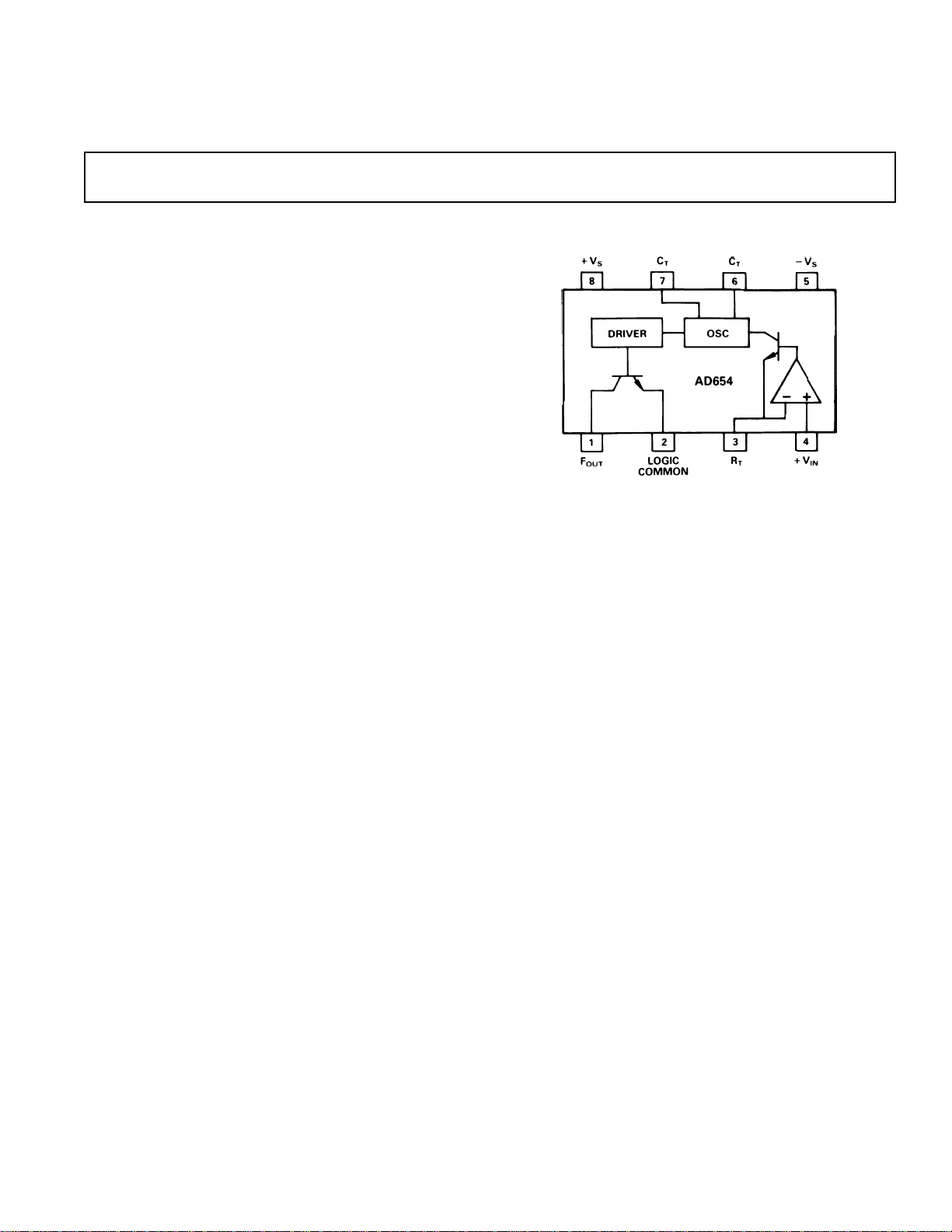

FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHTS

1. Packaged in both an 8-pin mini-DIP and an 8-pin SOIC

package, the AD654 is a complete V/F converter requiring

only an RC timing network to set the desired full-scale frequency and a selectable pullup resistor for the open-collector

output stage. Any full scale input voltage range from 100 mV

to 10 volts (or greater, depending on +V

dated by proper selection of the timing resistor. The fullscale frequency is then set by the timing capacitor from the

simple relationship, f = V/10 RC.

2. A minimum number of low cost external components are

necessary. A single RC network is all that is required to set

up any full scale frequency up to 500 kHz and any full-scale

input voltage up to ±30 V.

3. Plastic packaging allows low cost implementation of the standard VFC applications: A/D conversion, isolated signal

transmission, F/V conversion, phase-locked loops, and tuning switched-capacitor filters.

4. Power supply requirements are minimal; only 2.0 mA of quiescent current is drawn from the single positive supply from

4.5 volts to 36 volts. In this mode, positive inputs can vary

from 0 volts (ground) to (+V

easily be connected for below ground operation.

5. The versatile open-collector output stage can sink more than

10 mA with a saturation voltage less than 0.4 volts. The

Logic Common terminal can be connected to any level between ground (or –V

easy direct interface to any logic family with either positive or

negative logic levels.

) and 4 volts below +VS. This allows

S

–4) volts. Negative inputs can

S

) can be accommo-

S

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

(TA = +258C and VS (total) = 5 V to 16.5 V, unless otherwise noted.

AD654–SPECIFICATIONS

All testing done@ VS = +5 V.)

AD654JN/JR

Model Min Typ Max Units

CURRENT-TO-FREQUENCY CONVERTER

Frequency Range 0 500 kHz

Nonlinearity

f

MAX

f

MAX

1

= 250 kHz 0.06 0.1 %

= 500 kHz 0.20 0.4 %

Full-Scale Calibration Error

C = 390 pF, I

vs. Supply (f

V

= +4.75 V to +5.25 V 0.20 0.40 %/V

S

V

= +5.25 V to +16.5 V 0.05 0.10 %/V

S

= 1.000 mA –10 10 %

IN

≤ 250 kHz)

MAX

vs. Temp (0°C to +70°C) 50 ppm/°C

ANALOG INPUT AMPLIFIER

(Voltage-to-Current Converter)

Voltage Input Range

Single Supply 0 (+V

Dual Supply –V

S

– 4) V

S

(+VS – 4) V

Input Bias Current

(Either Input) 30 50 nA

Input Offset Current 5 nA

Input Resistance (Noninverting) 250 MΩ

Input Offset Voltage 0.5 1.0 mV

vs. Supply

V

= +4.75 V to +5.25 V 0.1 0.25 mV/V

S

V

= +5.25 V to +16.5 V 0.03 0.1 mV/V

S

vs. Temp (0°C to +70°C) 4 µV/°C

OUTPUT INTERFACE (Open Collector Output)

(Symmetrical Square Wave)

Output Sink Current in Logic “0”

V

= 0.4 V max, +25°C 10 20 mA

OUT

V

= 0.4 V max, 0°C to +70°C 5 10 mA

OUT

2

Output Leakage Current in Logic “1” 10 100 nA

0°C to +70°C 50 500 nA

Logic Common Level Range –V

Rise/Fall Times (C

I

= 1 mA 0.2 µs

IN

I

= 1 µA1µs

IN

= 0.01 µF)

T

S

(+VS – 4) V

POWER SUPPLY

Voltage, Rated Performance 4.5 16.5 V

Voltage, Operating Range

Single Supply 4.5 36 V

Dual Supply ±5 ± 18 V

Quiescent Current

V

(Total) = 5 V 1.5 2.5 mA

S

VS (Total) = 30 V 2.0 3.0 mA

TEMPERATURE RANGE

Operating Range –40 +85 °C

PACKAGE OPTIONS

3

SOIC (R-8) AD654JR

Plastic DIP (N-8) AD654JN

NOTES

1

At f

= 250 kHz; RT = 1 kΩ, CT = 390 pF, IIN = 0 mA–1 mA.

MAX

1

At f

= 500 kHz; RT = 1 kΩ, CT = 200 pF, IIN = 0 mA–1 mA.

MAX

2

The sink current is the amount of current that can flow into Pin 1 of the AD654 while maintaining a maximum voltage of 0.4 V between Pin 1 and Logic Common.

3

N = Plastic DIP; R = SOIC.

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min

and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

Specifications subject to change without notice

–2–

REV. A

AD654

ABSOLUTE MAXIMUM RATING

Total Supply Voltage +VS to –VS . . . . . . . . . . . . . . . . . . . 36 V

Maximum Input Voltage

(Pins 3, 4) to –V

. . . . . . . . . . . . . . . . . . . . .–300 mV to +V

S

S

Maximum Output Current

Instantaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

Sustained . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 mA

Logic Common to –V

. . . . . . . . . . . . . . . –500 mV to (+VS –4)

S

Storage Temperature Range . . . . . . . . . . . . . –65°C to +150°C

CIRCUIT OPERATION

The AD654’s block diagram appears in Figure 1. A versatile

operational amplifier serves as the input stage; its purpose is to

convert and scale the input voltage signal to a drive current in

the NPN follower. Optimum performance is achieved when, at

the full-scale input voltage, a 1 mA drive current is delivered to

the current-to-frequency converter (an astable multivibrator).

The drive current provides both the bias levels and the charging

current to the externally connected timing capacitor. This

“adaptive” bias scheme allows the oscillator to provide low nonlinearity over the entire current input range of 100 nA to 2 mA.

The square wave oscillator output goes to the output driver

which provides a floating base drive to the NPN power transistor. This floating drive allows the logic interface to be referenced to a level other than –V

.

S

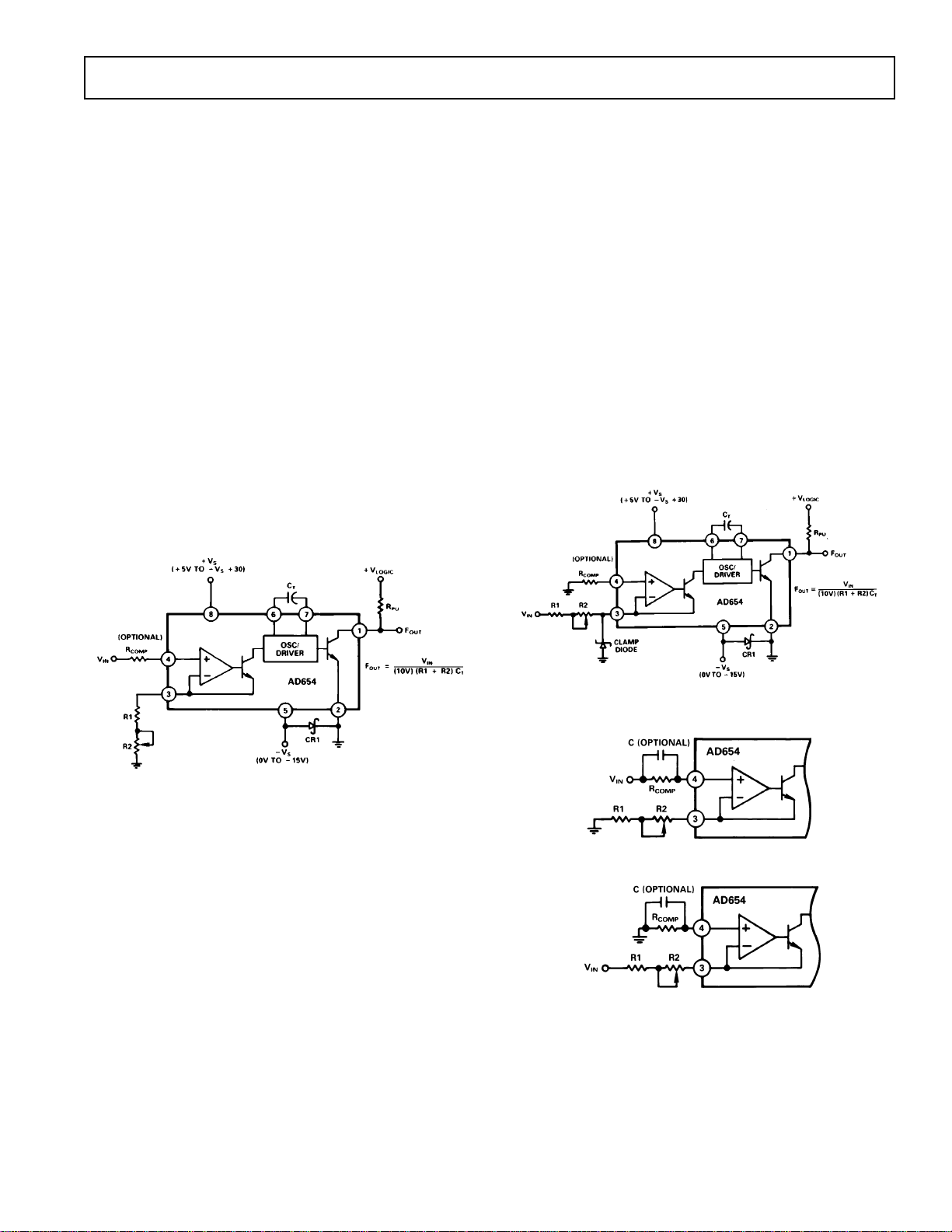

for a component having a small tempco. Polystyrene, polypropylene, or Teflon* capacitors are preferred for tempco and dielectric absorption; other types will degrade linearity. The capacitor

should be wired very close to the AD654. In Figure 1, Schottky

diode CR1 (MBD101) prevents logic common from dropping

more than 500 mV below –V

required if –V

V/F CONNECTIONS FOR NEGATIVE INPUT VOLTAGE

OR CURRENT

is equal to logic common.

S

. This diode is not

S

The AD654 can accommodate a wide range of negative input

voltages with proper selection of the scaling resistor, as indicated

in Figure 2. This connection, unlike the buffered positive connection, is not high impedance because the signal source must

supply the 1 mA FS drive current. However, large negative voltages beyond the supply can be handled easily by modifying the

scaling resistors appropriately. If the input is a true current

source, R1 and R2 are not used. Again, diode CR1 prevents

latch-up by insuring Logic Common does not drop more than

500 mV below –V

AD654 input from “below –V

. The clamp diode (MBD101) protects the

S

” inputs.

S

Figure 1. Standard V-F Connection for Positive Input

Voltages

V/F CONNECTION FOR POSITIVE INPUT VOLTAGES

In the connection scheme of Figure 1, the input amplifier presents a very high (250 MΩ) impedance to the input voltage,

which is converted into the proper drive current by the scaling

resistors at Pin 3. Resistors R1 and R2 are selected to provide a

1 mA full-scale current with enough trim range to accommodate

the AD654’s 10% FS error and the components’ tolerances.

Full-scale currents other than 1 mA can be chosen, but linearity

will be reduced; 2 mA is the maximum allowable drive. The

AD654’s positive input voltage range spans from –V

(ground in

S

sink supply operation) to four volts below the positive supply.

Power supply rejection degrades as the input exceeds (+V

3.75 V) and at (+V

– 3.5 V) the output frequency goes to zero.

S

–

S

As indicated by the scaling relationship in Figure 1, a 0.01 µF

timing capacitor will give a 10 kHz full-scale frequency, and 0.001

µF will give 100 kHz with a 1 mA drive current. Good V/F linearity

requires the use of a capacitor with low dielectric absorption

(DA), while the most stable operation over temperature calls

*Teflon is a trademark of E.I. Du Pont de Nemours & Co.

Figure 2. V-F Connections for Negative Input Voltages or

Current

Figure 3a. Bias Current Compensation—Positive Inputs

Figure 3b. Bias Current Compensation—Negative Inputs

If the AD654’s 1 mV offset voltage must be trimmed, the trim

must be performed external to the device. Figure 3c shows an

optional connection for positive inputs in which R

R

add a variable resistance in series with RT. A variable

OFF2

source of ±0.6 V applied to R

then adjusts the offset ±1 mV.

OFF1

Similarly, a ±0.6 V variable source is applied to R

OFF1

OFF

and

in Fig-

ure 3d to trim offset for negative inputs. The ±0.6 V bipolar

source could simply be an AD589 reference connected as shown

in Figure 3e.

REV. A

–3–

Loading...

Loading...