Analog Devices AD5259 Datasheet

V

V

V

A

Nonvolatile, I2C-Compatible

FEATURES

Nonvolatile memory maintains wiper settings

256-position

Compact MSOP-10 (3 mm × 4.9 mm) package

2

C®-compatible interface

I

pin provides increased interface flexibility

V

LOGIC

End-to-end resistance 5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ

Resistance tolerance stored in EEPROM (0.1% accuracy)

Power-on EEPROM refresh time < 1ms

Software write protect command

Three-state Address Decode Pins AD0 and AD1 allow

9 packages per bus

100-year typical data retention at 55°C

Wide operating temperature −40°C

3 V to 5 V single supply

APPLICATIONS

LCD panel V

LCD panel brightness and contrast control

Mechanical potentiometer replacement in new designs

Programmable power supplies

RF amplifier biasing

Automotive electronics adjustment

Gain control and offset adjustment

Fiber to the home systems

Electronics level settings

adjustment

COM

to +85°C

256-Position, Digital Potentiometer

AD5259

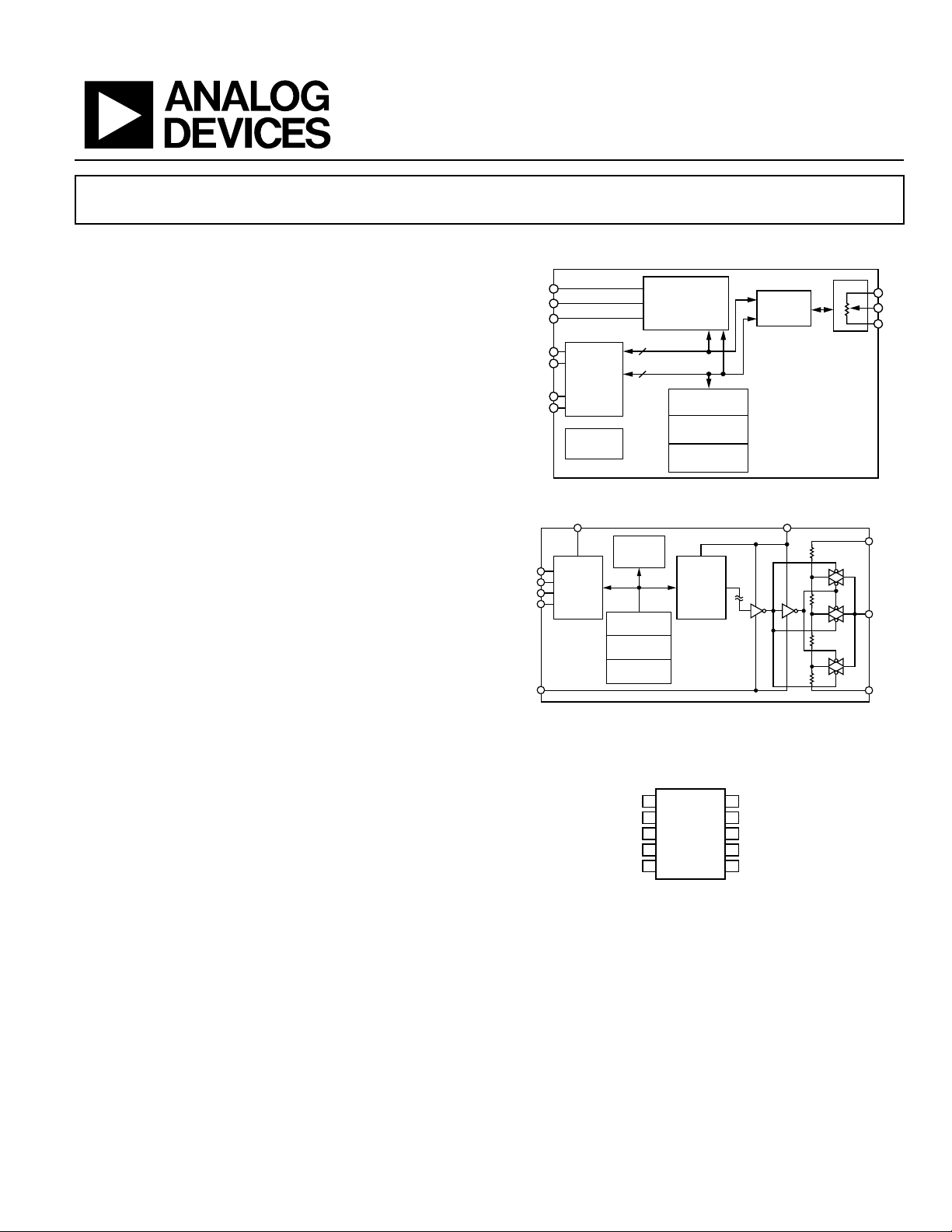

FUNCTIONAL BLOCK DIAGRAMS

RDAC

A

W

B

05026-001

A

W

B

05026-003

SCL

SDA

AD0

AD1

GND

V

LOGIC

GND

SCL

SDA

AD0

AD1

DD

RDAC

EEPROM

DATA

8

I2C

SERIAL

INTERFACE

POWER-

ON RESET

8

CONTROL

COMMAND

DECODE LOGIC

ADDRESS

DECODE LOGIC

CONTROL LOGIC

Figure 1. Block Diagram

LOGIC

EEPROM

RDAC

I2C

SERIAL

INTERFACE

COMMAND

DECODE LOGIC

ADDRESS

DECODE LOGIC

CONTROL

LOGIC

REGISTER

AND

LEVEL

SHIFTER

Figure 2. Block Diagram Showing Level Shifters

RDAC

REGISTER

AD5259

DD

GENERAL DESCRIPTION

The AD5259 provides a compact, nonvolatile 3 mm × 4.9 mm

packaged solution for 256-position adjustment applications.

These devices perform the same electronic adjustment function

1

as mechanical potentiometers

or variable resistors, but with

enhanced resolution and solid-state reliability.

2

The wiper settings are controllable through an I

C-compatible

digital interface that is also used to read back the wiper register

and EEPROM content. Resistor tolerance is also stored within

EEPROM providing an end-to-end tolerance accuracy of 0.1%.

There is also a software write protection function that ensures

data cannot be written to the EEPROM register.

A separate V

pin delivers increased interface flexibility. For

LOGIC

users who need multiple parts on one bus, Address Bit AD0 and

Address Bit AD1 allow up to nine devices on the same bus.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

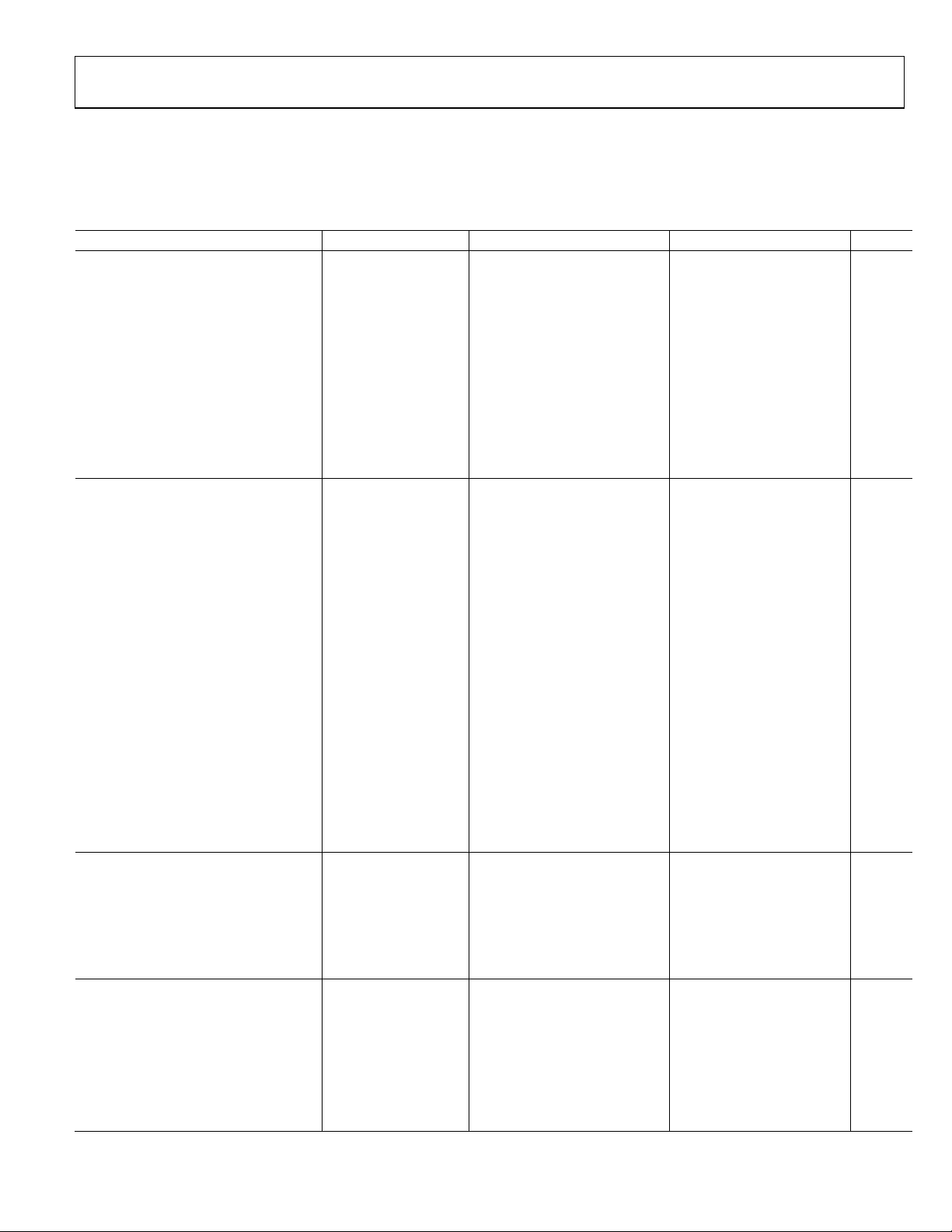

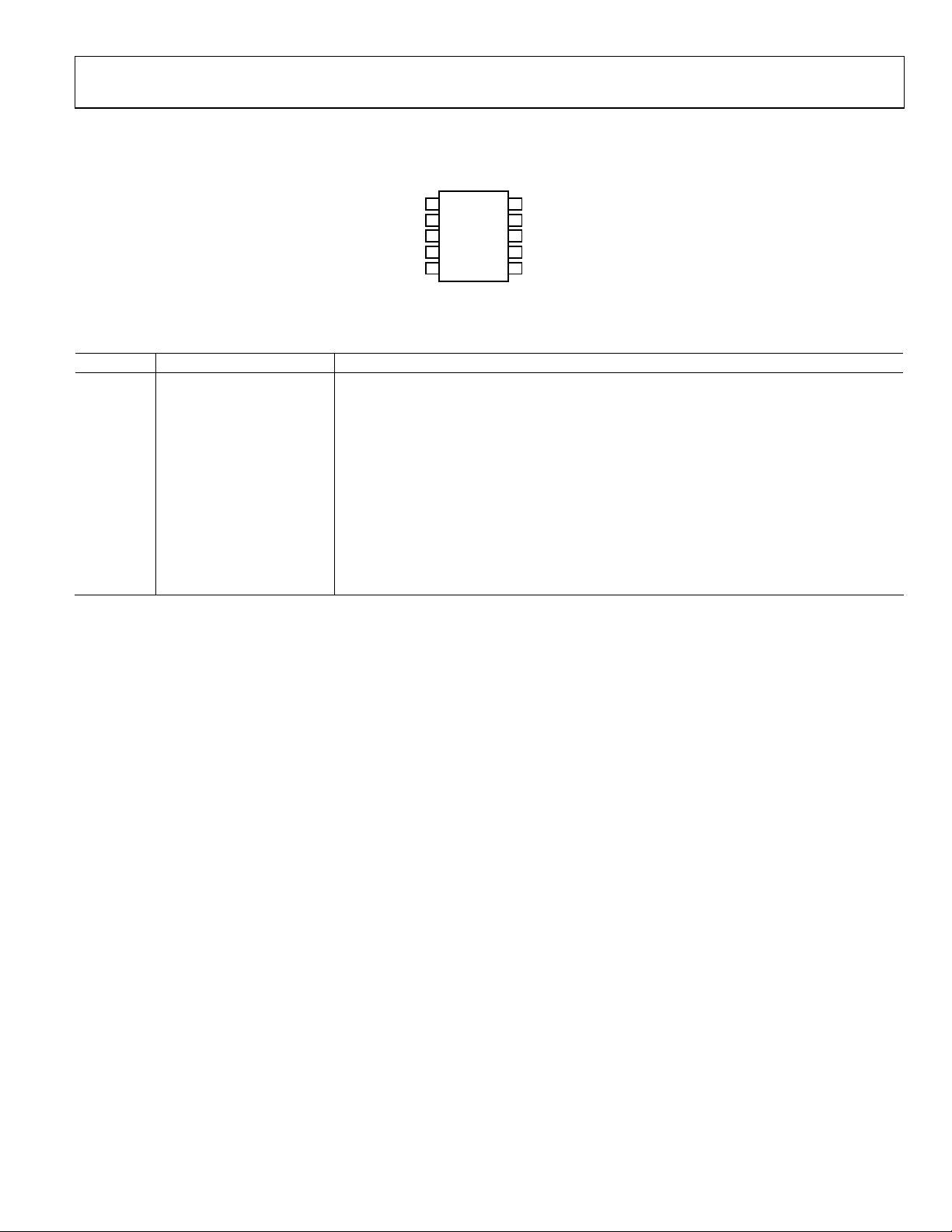

CONNECTION DIAGRAM

AD0

AD1

SD

SCL

W

1

2

3

4

5

AD5259

TOP VIEW

(Not to Scale)

Figure 3. Pinout

10

A

9

B

8

V

DD

GND

7

6

V

LOGIC

05026-002

1

The terms digital potentiometer, VR (variable resistor), and RDAC are used

interchangeably.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

www.analog.com

AD5259

TABLE OF CONTENTS

Specifications..................................................................................... 3

Writ e M o des ................................................................................ 17

Electrical Characteristics............................................................. 3

Timing Characteristics ................................................................ 5

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Descriptions............................. 7

Typical Performance Characteristics............................................. 8

Test C ir c uit s ..................................................................................... 13

Theory of Operation ...................................................................... 14

Programming the Variable Resistor......................................... 14

Programming the Potentiometer Divider............................... 14

2

I

C Interface..................................................................................... 15

2

I

C Byte Formats............................................................................. 16

Generic Interface........................................................................ 16

REVISION HISTORY

Read Modes................................................................................. 17

Store/Restore Modes .................................................................. 17

Tole ran c e Re adb ack M o de s ...................................................... 18

ESD Protection of Digital Pins and Resistor Terminals........ 19

Power-Up Sequence ................................................................... 19

Layout and Power Supply Bypassing ....................................... 19

Multiple Devices on One Bus ................................................... 19

Evaluation Board ........................................................................ 19

Display Applications ...................................................................... 20

Circuitry ...................................................................................... 20

Outline Dimensions ....................................................................... 21

Ordering Guide .......................................................................... 21

2/05 — Revision 0: Initial Version

Rev. 0 | Page 2 of 24

AD5259

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

VDD = V

Table 1.

Parameter Symbol Conditions Min Typ

DC CHARACTERISTICS: RHEOSTAT MODE

Resistor Differential Nonlinearity R-DNL RWB, V

Resistor Integral Nonlinearity R-INL RWB, V

Nominal Resistor Tolerance ∆R

Resistance Temperature Coefficient (∆RAB x 106)/(RAB x ∆T) Code = 0x00/0x80 500/15 ppm/°C

Total Wiper Resistance R

DC CHARACTERISTICS:

POTENTIOMETER DIVIDER MODE

Differential Nonlinearity DNL LSB

Integral Nonlinearity INL LSB

Full-Scale Error V

Zero-Scale Error V

Voltage Divider Temperature

Coefficient

RESISTOR TERMINALS

Voltage Range V

Capacitance A, B C

Capacitance W C

Common-Mode Leakage I

DIGITAL INPUTS AND OUTPUTS

Input Logic High V

Input Logic Low V

Leakage Current I

Input Capacitance C

= 5 V ± 10%, or 3 V ± 10%; VA = VDD; VB = 0 V; −40°C < TA < +85°C; unless otherwise noted.

LOGIC

1

Max Unit

= no connect

A

LSB

5 kΩ –1 ±0.2 +1

10 kΩ −1 ±0.1 +1

50 kΩ/100 kΩ −0.5 ±0.1 +0.5

= no connect

A

LSB

5 kΩ –4 ±0.3 +4

10 kΩ −2 ±0.2 +2

50 kΩ/100 kΩ −1 ±0.4 +1

AB

WB

TA = 25°C, VDD = 5.5 V –30 +30 %

Code = 0x00 75 350 Ω

5 kΩ –1 ±0.2 +1

10 kΩ −0.5 ±0.1 +0.5

50 kΩ/100 kΩ −0.5 ±0.2 +0.5

5 kΩ –1 ±0.2 +1

10 kΩ −0.5 ±0.1 +0.5

50 kΩ/100 kΩ −0.5 ±0.1 +0.5

WFSE

Code = 0xFF LSB

5 kΩ −7 −3 0

10 kΩ −4 −1.5 0

50 kΩ/100 kΩ −1 −0.4 0

WZSE

Code = 0x00 LSB

5 kΩ 0 4 2.5

10 kΩ 0 3 1

50 kΩ/100 kΩ 0 0.5 0.2

x 106)/(VW x T) Code = 0x00/0x80 60/5 ppm/°C

(V

W

A, B, W

A, B

GND V

f = 1 MHz, measured to GND,

45 pF

DD

Code = 0x80

W

f = 1 MHz, measured to GND,

60 pF

Code = 0x80

CM

IH

IL

IL

VA = VB = VDD/2 10 nA

0.7 × VL V

+ 0.5 V

L

−0.5 0.3 × VLV

µA

SDA, AD0, AD1 VIN = 0 V or 5 V 0.01 ±1

SCL – Logic High VIN = 0 V −2.5 −1.3 +1

SCL – Logic Low VIN = 5 V 0.01 ±1

IL

5 pF

V

Rev. 0 | Page 3 of 24

AD5259

Parameter Symbol Conditions Min Typ

1

Max Unit

POWER SUPPLIES

Power Supply Range V

Positive Supply Current I

Logic Supply V

Logic Supply Current I

Programming Mode Current (EEPROM) I

Power Dissipation P

DD

DD

LOGIC

LOGIC

LOGIC(PROG)

DISS

2.7 5.5 V

0.1 2 µA

2.7 5.5 V

VIH = 5 V or VIL = 0 V 3 6 µA

VIH = 5 V or VIL = 0 V 35 mA

VIH = 5 V or VIL = 0 V, VDD = 5 V 15 40 µW

Power Supply Rejection Ratio PSRR VDD = +5 V ± 10%, Code = 0x80 ±0.005 ±0.06 %/%

DYNAMIC CHARACTERISTICS

Bandwidth −3 dB BW Code = 0x80

R

R

R

R

Total Harmonic Distortion THD

W

= 5 kΩ 2000 kHz

AB

= 10 kΩ 800 kHz

AB

= 50 kΩ 160 kHz

AB

= 100 kΩ 80 kHz

AB

RAB = 10 kΩ, VA = 1 V rms, VB = 0,

0.1 %

f = 1 kHz

VW Settling Time t

S

RAB = 10 kΩ, VAB = 5 V,

500 ns

±1 LSB error band

Resistor Noise Voltage Density e

1

Typical values represent average readings at 25°C and V = 5 V.

N_WB

DD

RWB = 5 kΩ, f = 1 kHz 9 nV/√Hz

Rev. 0 | Page 4 of 24

AD5259

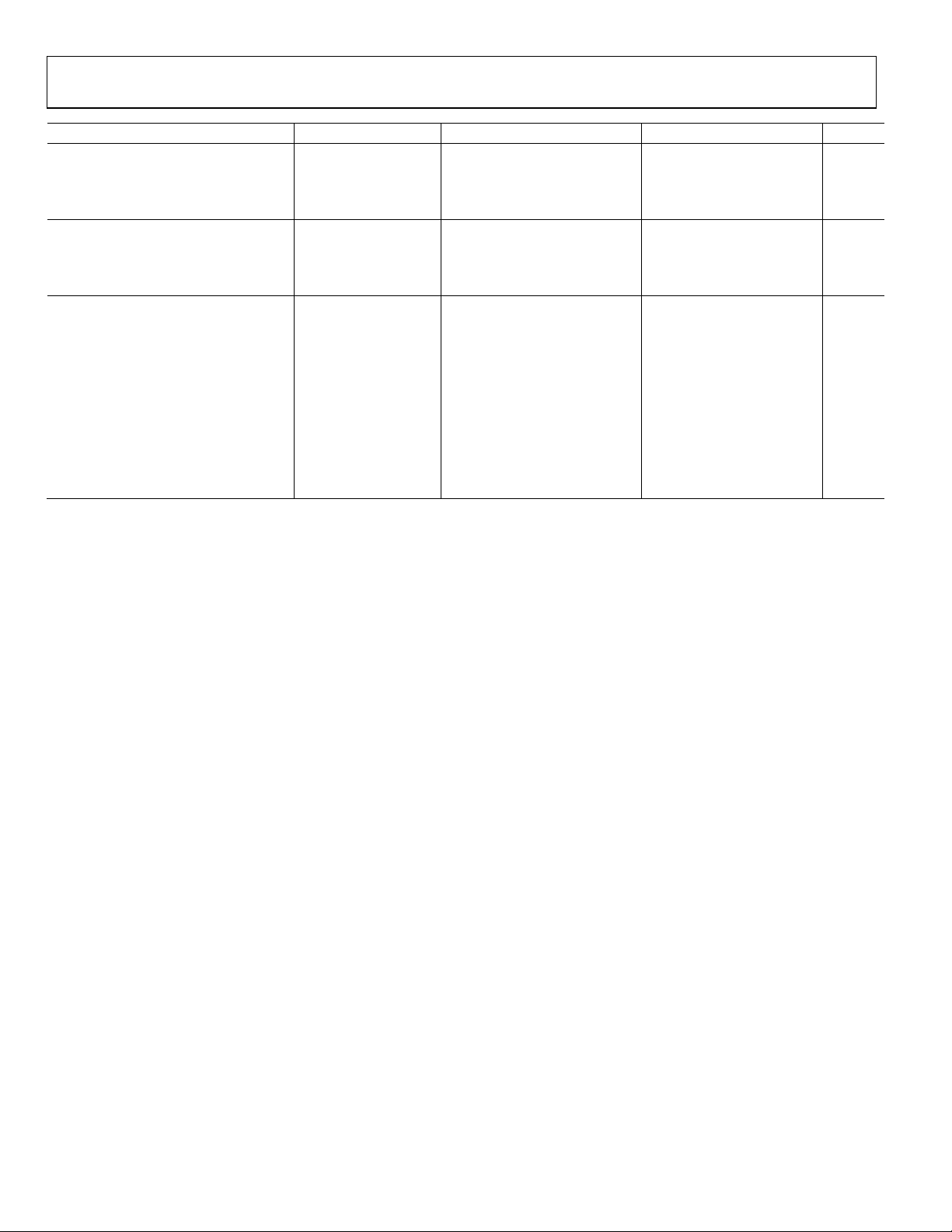

TIMING CHARACTERISTICS

VDD = V

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

I2C INTERFACE TIMING CHARACTERISTICS

SCL Clock Frequency f

t

BUF

t

HD;STA

t

LOW

t

HIGH

t

SU;STA

Condition

t

HD;DAT

t

SU;DAT

tF Fall Time of Both SDA and SCL Signals t

tR Rise Time of Both SDA and SCL Signals t

t

SU;STO

EEPROM Data Storing Time t

EEPROM Data Restoring Time at Power On

EEPROM Data Restoring Time upon Restore

Command

EEPROM Data Rewritable Time

FLASH/EE MEMORY RELIABILITY

Endurance

Data Retention

1

During power-up, the output is momentarily preset to midscale before restoring EEPROM content.

2

Delay time after power-on PRESET prior to writing new EEPROM data.

3

Endurance is qualified to 100,000 cycles per JEDEC Std. 22 method A117, and is measured at –40°C, +25°C, and +85°C; typical endurance at +25°C is 700,000 cycles.

4

Retention lifetime equivalent at junction temperature (TJ) = 55°C per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6eV derates

with junction temperature.

= 5 V ± 10%, or 3 V ± 10%; VA = VDD; VB = 0 V; −40°C < TA < +85°C; unless otherwise noted.

LOGIC

0 400 kHz

1.3 µs

After this period, the first clock pulse is

Bus Free Time between STOP and START t

Hold Time (Repeated START) t

SCL

1

2

generated.

Low Period of SCL Clock t

High Period of SCL Clock t

Setup Time for Repeated START

Data Hold Time t

Data Setup Time t

Setup Time for STOP Condition t

1

1

2

3

4

3

4

t

5

6

7

8

9

10

EEMEM_STORE

t

EEMEM_RESTORE1

t

EEMEM_RESTORE2VDD

t

EEMEM_REWRITE

100 700 kCycles

100 Years

1.3 µs

0.6 µs

0.6 µs

0 0.9 µs

100 ns

300 ns

300 ns

0.6 µs

26 ms

VDD rise time dependent. Measure without

decoupling capacitors at V

DD

= 5 V. 300 µs

540 µs

0.6 µs

300 µs

and GND.

t

SCL

SDA

t

8

t

t

3

2

t

9

t

8

t

1

PS P

Figure 4. I

t

9

t

t

4

2

C Interface Timing Diagram

5

6

t

7

t

10

05026-004

Rev. 0 | Page 5 of 24

AD5259

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 3.

Parameter Value

VDD to GND

VA, VB, VW to GND

I

MAX

Pulsed

1

−0.3 V to +7 V

GND − 0.3 V, V

±20 mA

+ 0.3 V

DD

Continuous ±5 mA

Digital Inputs and Output Voltage to GND 0 V to 7 V

Operating Temperature Range

Maximum Junction Temperature (T

Storage Temperature

−40°C to +85°C

) 150°C

JMAX

−65°C to +150°C

Lead Temperature (Soldering, 10 sec) 300°C

Thermal Resistance2

: MSOP–10

θ

JA

1

Maximum terminal current is bounded by the maximum current handling of

the switches, maximum power dissipation of the package, and maximum

applied voltage across any two of the A, B, and W terminals at a given

resistance.

2

Package power dissipation = (T

– TA)/θJA.

JMAX

200°C/W

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 6 of 24

AD5259

A

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

10

A

B

9

V

8

DD

GND

7

V

6

LOGIC

05026-008

AD0

AD1

SD

SCL

1

W

2

3

4

5

AD5259

TOP VIEW

(Not to Scale)

Figure 5. Pin Configuration

Table 4. AD5259 Pin Function Descriptions

Pin Mnemonic Description

1 W W Terminal, GND ≤ VW ≤ VDD.

2 ADO

Programmable Three-State Address Bit 0 for Multiple Package Decoding. State is registered on

power-up.

3 AD1

Programmable Three-State Address Bit 1 for Multiple Package Decoding. State is registered on

power-up.

4 SDA Serial Data Input/Output.

5 SCL Serial Clock Input. Positive edge triggered.

6 V

LOGIC

Logic Power Supply.

7 GND Digital Ground.

8 V

DD

Positive Power Supply.

9 B B Terminal, GND ≤ VB ≤ VDD.

10 A A Terminal, GND ≤ VA ≤ VDD.

Rev. 0 | Page 7 of 24

AD5259

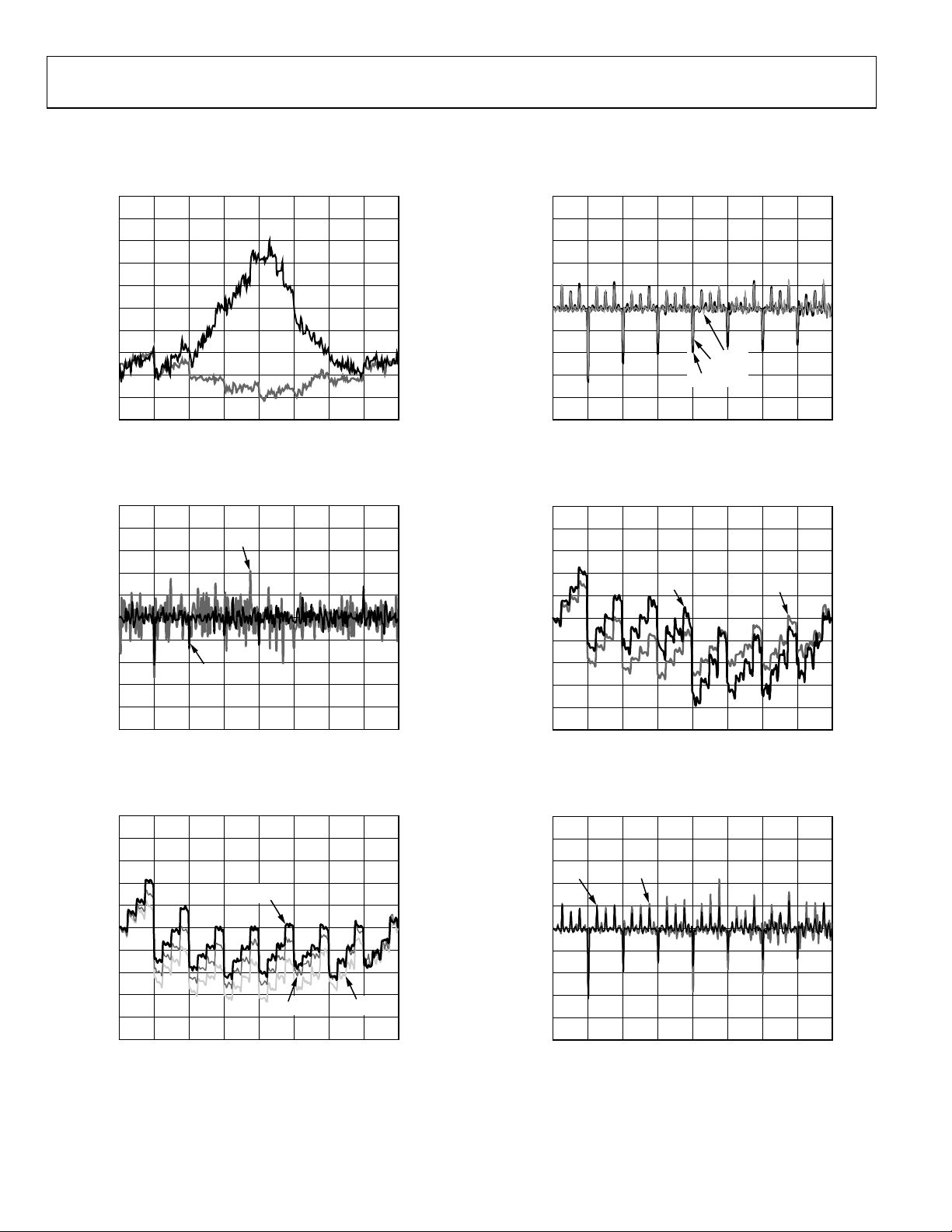

TYPICAL PERFORMANCE CHARACTERISTICS

VDD = V

RHEOSTAT MODE INL (LSB)

= 5.5 V, RAB = 10 kΩ, TA = +25°C; unless otherwise noted.

LOGIC

1.5

1.3

1.1

0.9

0.7

0.5

0.3

0.1

–0.1

–0.3

–0.5

0 256224192160128966432

2.7V

5.5V

CODE (Decimal)

Figure 6. R-INL vs. Code vs. Supply Voltage

05026-015

POTENTIOMETER MODE DNL (LSB)

0.25

0.20

0.15

0.10

0.05

–0.05

–0.10

–0.15

–0.20

–0.25

0

0 256224192160128966432

CODE (Decimal)

Figure 9. DNL vs. Code vs. Temperature

+25°C

+85°C

–40°C

05026-012

RHEOSTAT MODE DNL (LSB)

POTENTIOMETER MODE INL (LSB)

0.5

0.4

0.3

0.5

0.1

–0.1

–0.2

–0.3

–0.4

–0.5

0

0 256224192160128966432

2.7V

5.5V

CODE (Decimal)

Figure 7. R-DNL vs. Code vs. Supply Voltages

0.25

0.20

0.15

0.10

0.05

–0.05

–0.10

–0.15

–0.20

–0.25

0

0 256224192160128966432

T

A

CODE (Decimal)

Figure 8. INL vs. Code vs. Temperature

= +85°C

T

= +25°C

A

TA = –40°C

05026-017

05026-010

POTENTIOMETER MODE INL (LSB)

POTENTIOMETER MODE DNL (LSB)

0.25

0.20

0.15

0.10

0.05

–0.05

–0.10

–0.15

–0.20

–0.25

0

0 256224192160128966432

2.7V

CODE (Decimal)

Figure 10. INL vs. Supply Voltages

0.25

0.20

0.15

0.10

0.05

–0.05

–0.10

–0.15

–0.20

–0.25

2.7V

0

0 256224192160128966432

5.5V

CODE (Decimal)

Figure 11. DNL vs. Code vs. Supply Voltages

5.5V

05026-011

05026-013

Rev. 0 | Page 8 of 24

Loading...

Loading...