Page 1

-- DISCONTINUED PRODUCT --

LogiCORE™ IP

1-Gigabit Ethernet

MAC v8.5

User Guide

UG144 April 24, 2009

R

Page 2

-- DISCONTINUED PRODUCT --

R

Xilinx is providing this product documentation, hereinafter “Information,” to you “AS IS” with no warranty of any kind, express or implied.

Xilinx makes no representation that the Information, or any particular implementation thereof, is free from any claims of infringement. You

are responsible for obtaining any rights you may require for any implementation based on the Information. All specifications are subject to

change without notice. XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF

THE INFORMATION OR ANY IMPLEMENTATION BASED THEREON, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR

REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF INFRINGEMENT AND ANY IMPLIED WARRANTIES

OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Except as stated herein, none of the Information may be copied,

reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited

to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx.

© 2004-2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx

in the United States and other countries. The PowerPC name and logo are registered trademarks of IBM Corp. and used under license. All

other trademarks are the property of their respective owners.

www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 3

-- DISCONTINUED PRODUCT --

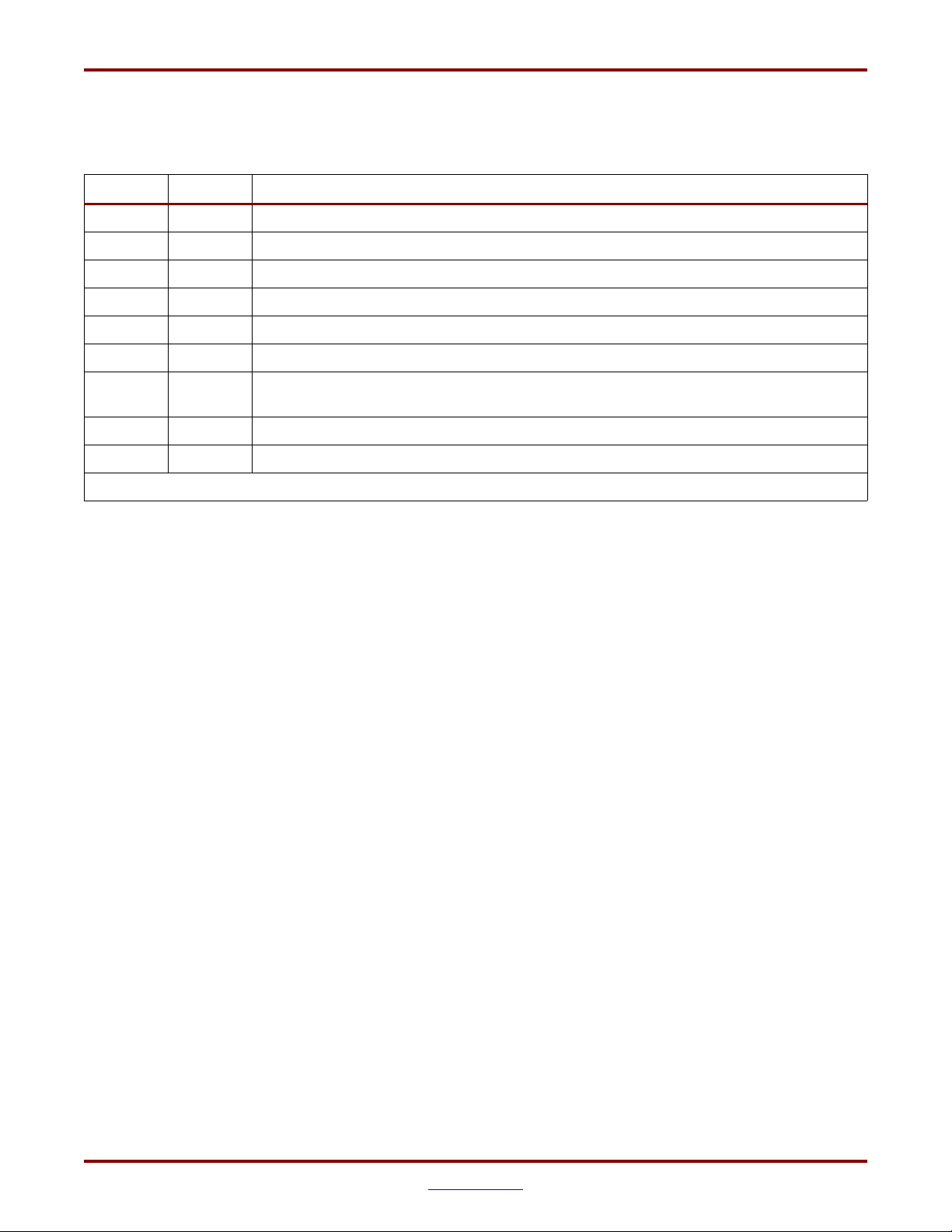

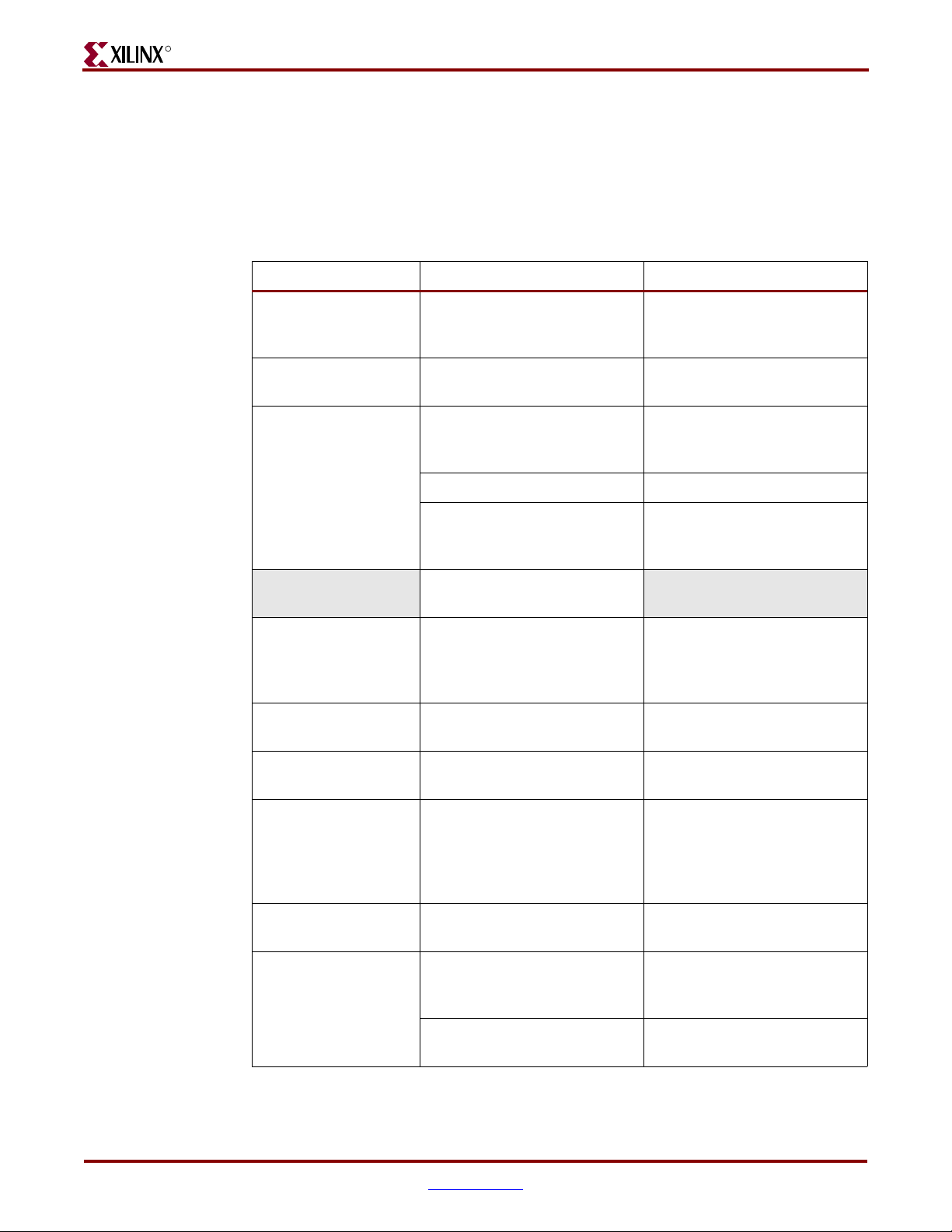

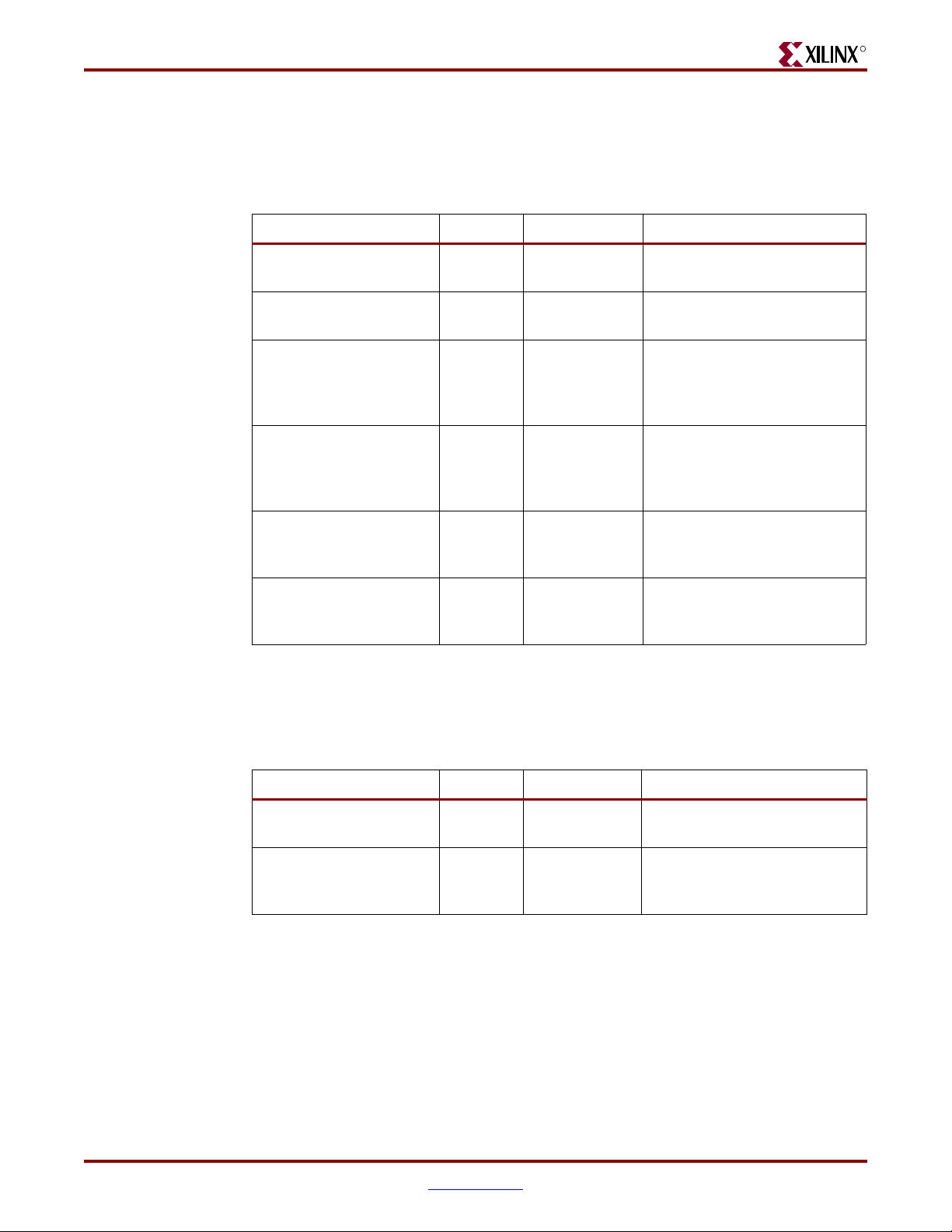

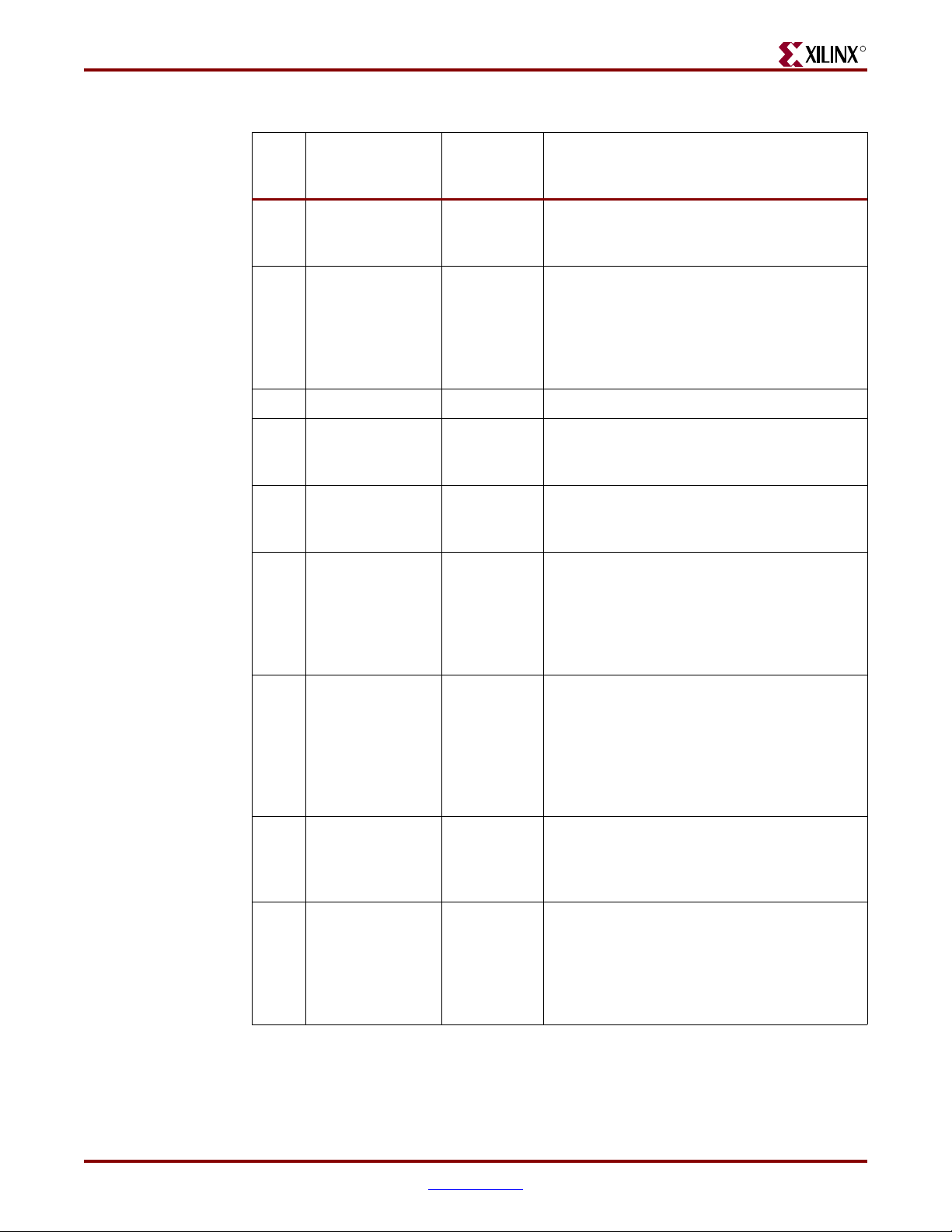

Revision History

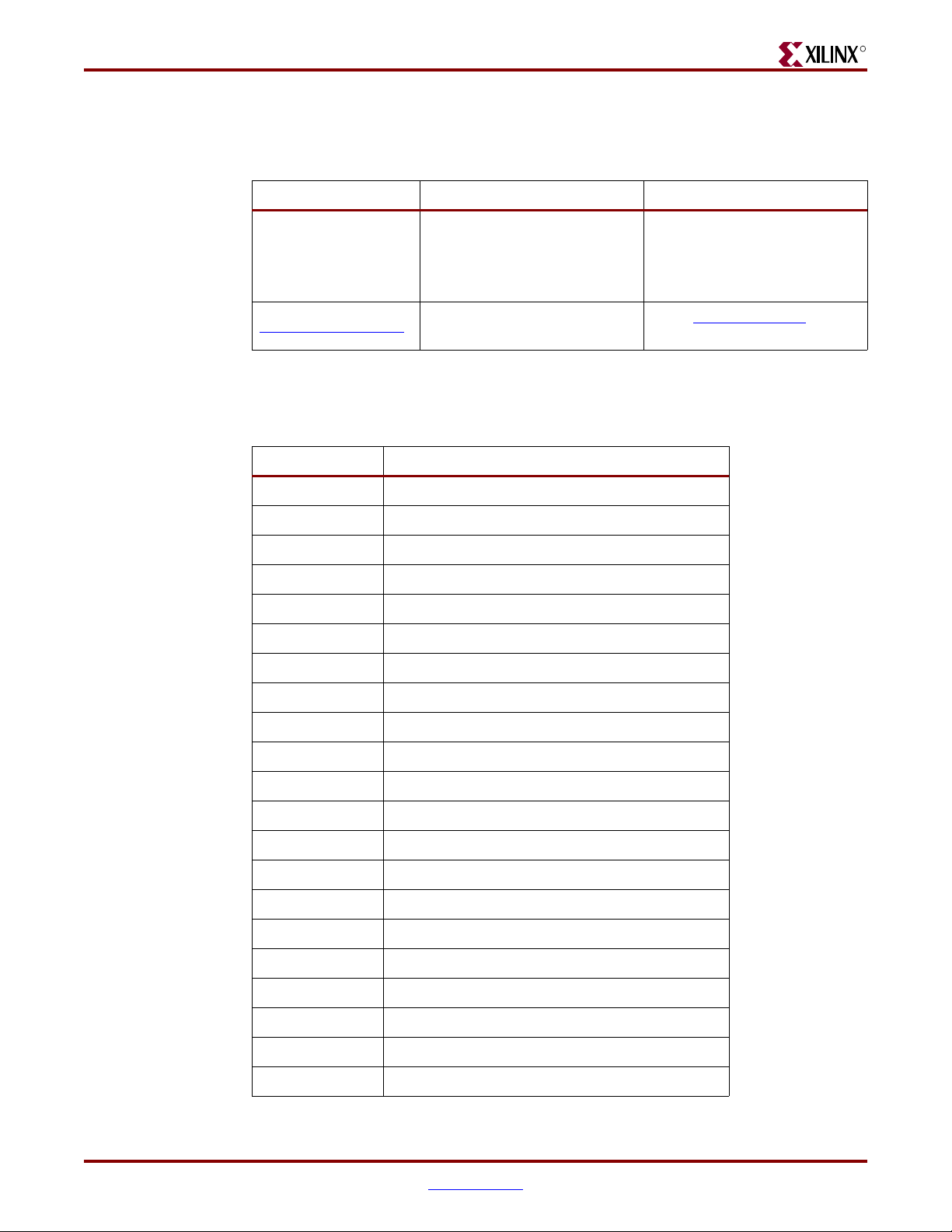

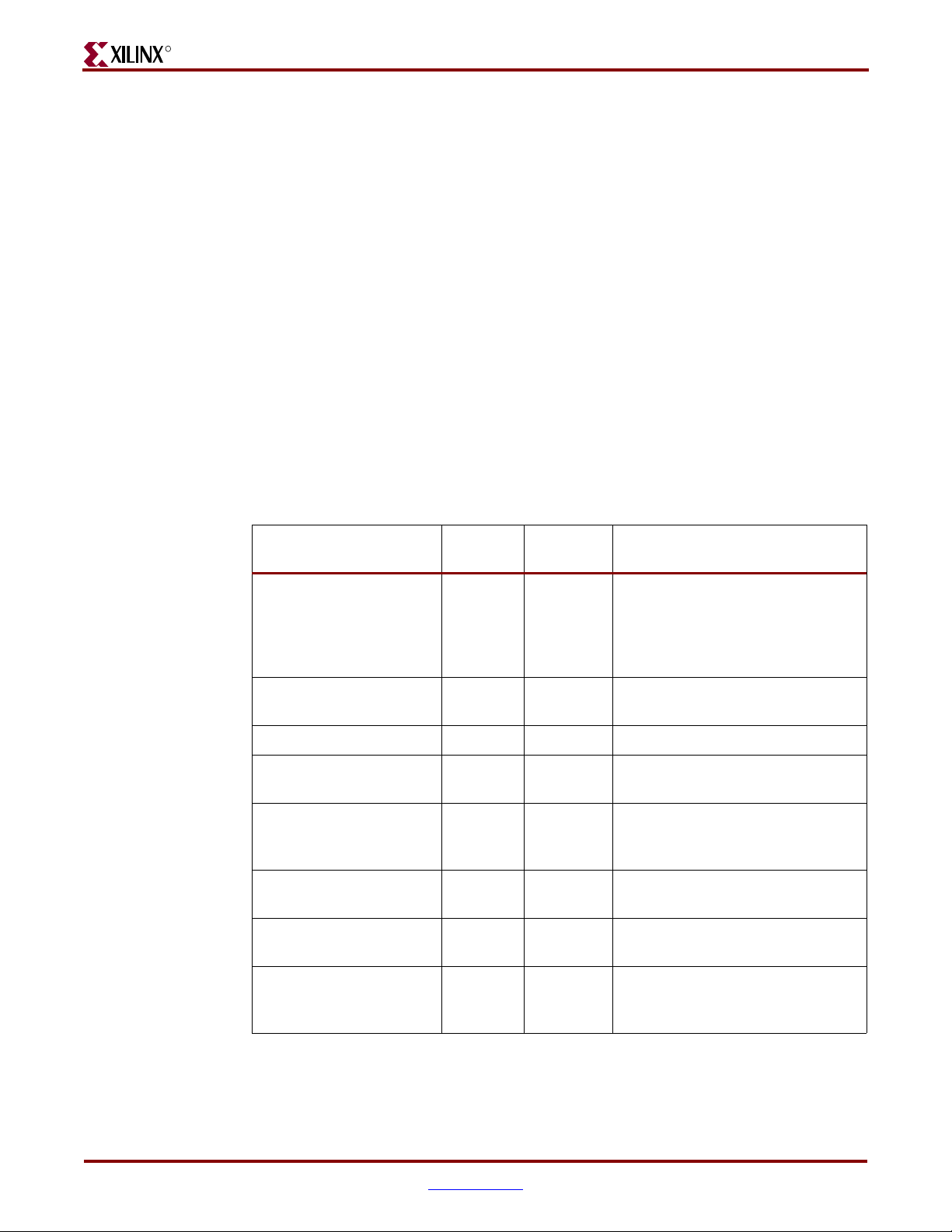

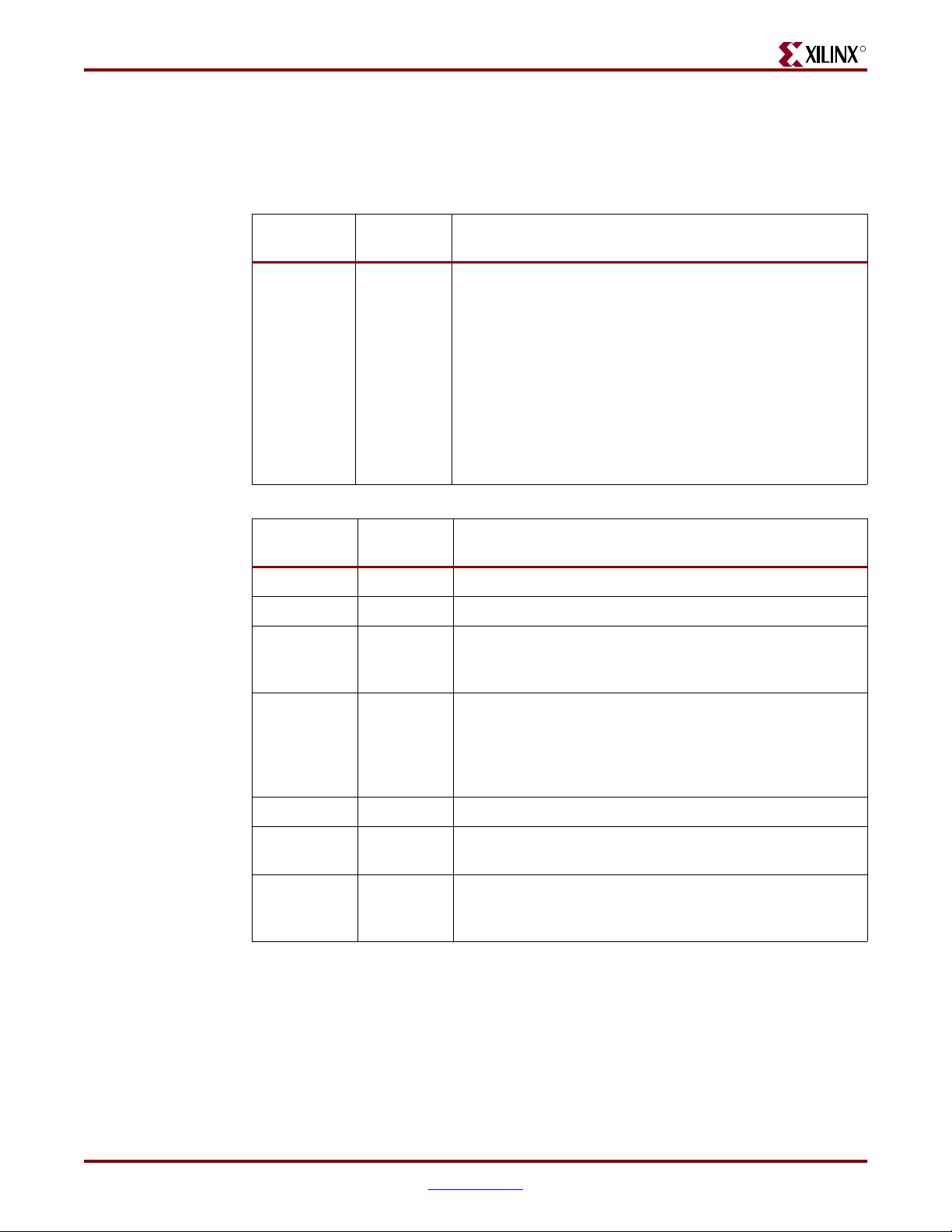

The following table shows the revision history for this document.

Date Version Revision

09/30/04 1.0 Initial Xilinx release.

04/28/05 2.0 Updated to 1-Gigabit Ethernet MAC version 6.0, Xilinx tools v7.1i SP1.

01/18/06 3.0 Updated to 1-Gigabit Ethernet MAC version 7.0, Xilinx tools v8.1i.

07/13/06 4.0 Updated to 1-Gigabit Ethernet MAC version 8.0, Xilinx tools v8.2i.

09/21/06 4.1 Updated to 1-Gigabit Ethernet MAC version 8.1, added support for Spartan®-3A platform.

02/15/07 4.2 Updated to 1-Gigabit Ethernet MAC version 8.2, Xilinx tools v9.1i.

08/08/07 5.0 Advanced core version to 8.3, updated various tool versions and trademarks for the

IP1 I Jade Minor release.

03/24/08 6.0 Updated core version to 8.4; Xilinx tools 10.1.

04/24/09 7.0 Updated core version to 8.5; Xilinx tools 11.1.

The product was discontinued as of August 31, 2009.

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com

UG144 April 24, 2009

Page 4

-- DISCONTINUED PRODUCT --

www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 5

-- DISCONTINUED PRODUCT --

Table of Contents

Schedule of Figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Schedule of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Typographical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Online Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

List of Acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Chapter 1: Introduction

About the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Recommended Design Experience. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Additional Core Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Related Xilinx Ethernet Products and Services . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Technical Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Feedback. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

GEMAC Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Chapter 2: Core Architecture

System Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Core Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Core Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

GMAC Core with Optional Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

GMAC Core Without Management Interface and With Address Filter . . . . . . . . . . . 24

GEMAC Core Without Management Interface and Without Address Filter . . . . . . . 25

Client Side Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Physical Side Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Chapter 3: Generating the Core

Graphical User Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Component Name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Management Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Address Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Number of Address Table Entries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Physical Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Parameter Values in the XCO File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Output Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com

UG144 April 24, 2009

Page 6

-- DISCONTINUED PRODUCT --

R

Chapter 4: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Design Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Know the Degree of Difficulty . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Keep it Registered . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Recognize Timing Critical Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Use Supported Design Flows . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Make Only Allowed Modifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Chapter 5: Using the Client Side Data Path

Receiving Inbound Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Normal Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

rx_good_frame, rx_bad_frame timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Frame Reception with Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Client-Supplied FCS Passing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

VLAN Tagged Frames. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Maximum Permitted Frame Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Length/Type Field Error Checks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Address Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Receiver Statistics Vector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Transmitting Outbound Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Normal Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Padding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Client-Supplied FCS Passing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Client Underrun . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

VLAN Tagged Frames. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Maximum Permitted Frame Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Inter-Frame Gap Adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Transmitter Statistics Vector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Chapter 6: Using Flow Control

Overview of Flow Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Flow Control Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Flow Control Basics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Pause Control Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Flow Control Operation of the GEMAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Transmitting a PAUSE Control Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Receiving a Pause Control Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

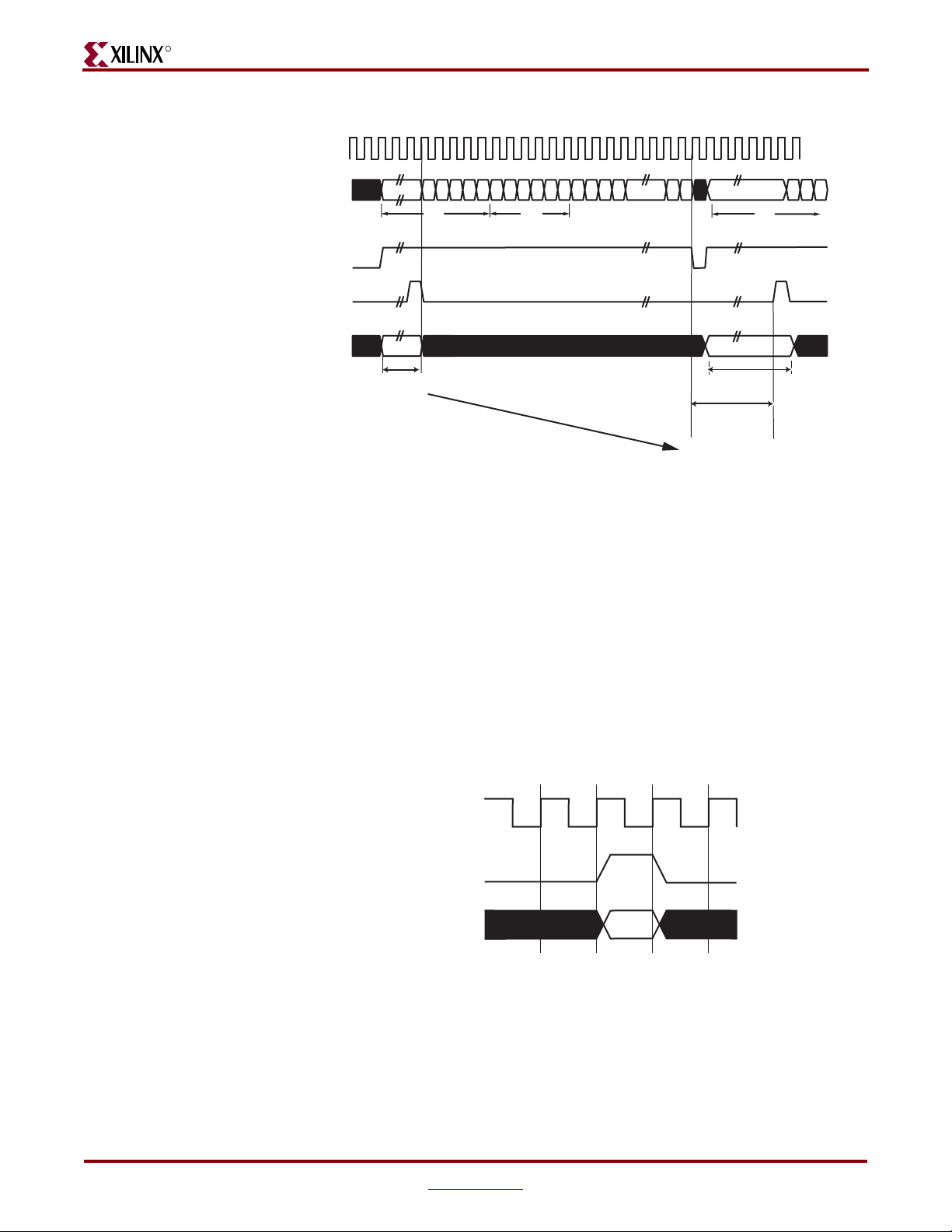

Flow Control Implementation Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Chapter 7: Using the Physical Side Interface

Implementing External GMII. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

GMII Transmitter Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

GMII Receiver Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Implementing External RGMII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

RGMII Transmitter Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

RGMII Receiver Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

RGMII Inband Status Decoding Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Using the MDIO interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 7

-- DISCONTINUED PRODUCT --

Connecting the MDIO to an Internally Integrated PHY . . . . . . . . . . . . . . . . . . . . . . . . 76

Connecting the MDIO to an External PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Chapter 8: Configuration and Status

Using the Optional Management Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Host Clock Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

MDIO Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Access without the Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Chapter 9: Constraining the Core

Required Constraints. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Device, Package, and Speedgrade Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

I/O Location Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Placement Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Timing Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Constraints when Implementing an External GMII . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Understanding Timing Reports for GMII Setup/Hold Timing . . . . . . . . . . . . . . . . . . 99

Constraints when Implementing an External RGMII . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Understanding Timing Reports for RGMII Setup/Hold timing . . . . . . . . . . . . . . . . 105

R

Chapter 10: Clocking and Resetting

Clocking the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

With Internal GMII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

With External GMII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

With RGMII. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Multiple Cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

With External GMII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

With RGMII. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Reset Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Chapter 11: Interfacing to Other Cores

Ethernet 1000Base-X PCS/PMA or SGMII Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Integration to Provide 1000BASE-X PCS with TBI . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Integration to Provide 1000BASE-X PCS and PMA using a RocketIO Transceiver . 115

Integration to Provide SGMII Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Ethernet Statistics Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Connecting the Ethernet Statistics Core to Provide Statistics Gathering. . . . . . . . . . 119

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com

UG144 April 24, 2009

Page 8

-- DISCONTINUED PRODUCT --

R

Chapter 12: Implementing Your Design

Pre-implementation Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Using the Simulation Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Synthesis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

XST—VHDL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

XST—Verilog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Generating the Xilinx Netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Mapping the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Placing-and-Routing the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Static Timing Analysis. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Generating a Bitstream . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Post-Implementation Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Generating a Simulation Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Using the Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Other Implementation Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Appendix A: Using the Client-Side FIFO

Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Transmit FIFO. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Receive FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Overview of LocalLink Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Functional Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Clock Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Receive FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Transmit FIFO. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Expanding Maximum Frame Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

User Interface Data Width Conversion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Appendix B: Core Verification, Compliance, and Interoperability

Verification by Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Hardware Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

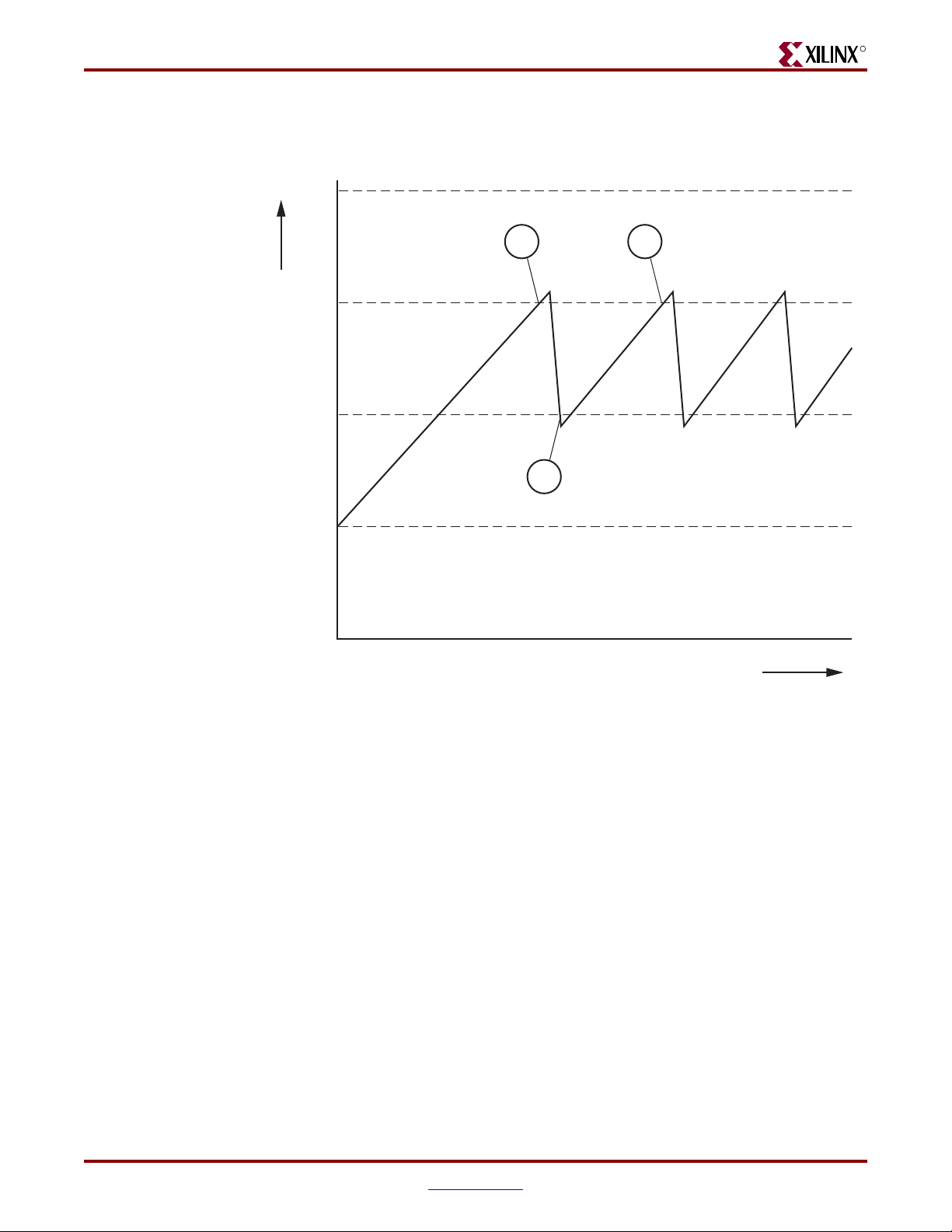

Appendix C: Calculating DCM Phase-Shifting

DCM Phase-Shifting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Finding the Ideal Phase-Shift. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Appendix D: Core Latency

Transmit Path Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Receive Path Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 9

-- DISCONTINUED PRODUCT --

Schedule of Figures

Chapter 1: Introduction

Chapter 2: Core Architecture

Figure 2-1: Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 2-2: Component Pinout for MAC with Optional Management Interface . . . . . . 23

Figure 2-3: Component Pinout for MAC without Optional Management Interface

and with Optional Address Filter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 2-4: Component Pinout for MAC without Optional Management Interface or

Optional Address Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Chapter 3: Generating the Core

Figure 3-1: 1-Gigabit Ethernet MAC Main Screen. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Chapter 4: Designing with the Core

Figure 4-1: 1-Gigabit Ethernet MAC Core Example Design . . . . . . . . . . . . . . . . . . . . . . . . 36

Chapter 5: Using the Client Side Data Path

Figure 5-1: Normal Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 5-2: Frame Reception with Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 5-3: Frame Reception with In-Band FCS Field. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 5-4: Reception of a VLAN Tagged Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 5-5: Receiver Statistics Vector Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 5-6: Normal Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 5-7: Frame Transmission with Client-supplied FCS. . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 5-8: Frame Transmission with Underrun . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 5-9: Transmission of a VLAN Tagged Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 5-10: Inter-Frame Gap Adjustment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 5-11: Transmitter Statistic Vector Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Chapter 6: Using Flow Control

Figure 6-1: Requirement for Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

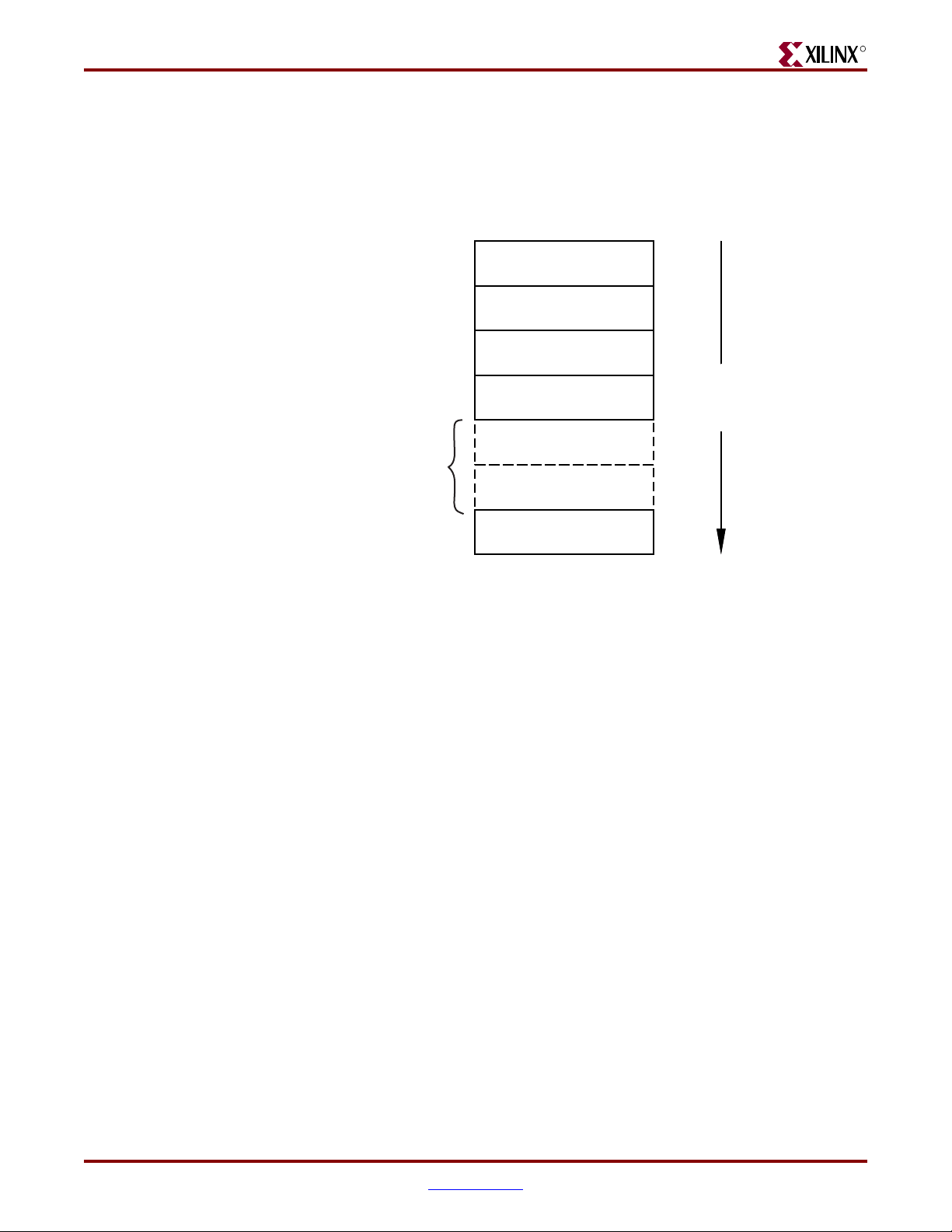

Figure 6-2: MAC Control Frame Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 6-3: Pause Request Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 6-4: Flow Control Implementation Triggered from FIFO Occupancy. . . . . . . . . . 59

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 9

UG144 April 24, 2009

Page 10

-- DISCONTINUED PRODUCT --

R

Chapter 7: Using the Physical Side Interface

Figure 7-1: External GMII Transmitter Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 7-2: External GMII Receiver Logic for Spartan-3, Spartan-3E, and

Spartan-3A Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Figure 7-3: External GMII Receiver Logic for Virtex-5 Devices . . . . . . . . . . . . . . . . . . . . . 65

Figure 7-4: External RGMII Transmitter Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 7-5: External RGMII Transmitter Logic in Virtex-4 Devices. . . . . . . . . . . . . . . . . . 68

Figure 7-6: External RGMII Transmitter Logic in Virtex-5 Devices. . . . . . . . . . . . . . . . . . 69

Figure 7-7: External RGMII Receiver Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 7-8: External RGMII Receiver Logic for Virtex-4 Devices. . . . . . . . . . . . . . . . . . . . 73

Figure 7-9: External RGMII Receiver Logic for Virtex-5 Devices. . . . . . . . . . . . . . . . . . . . 74

Figure 7-10: RGMII Inband Status Decoding Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 7-11: Creating an External MDIO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Chapter 8: Configuration and Status

Figure 8-1: Configuration Register Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 8-2: Configuration Register Read Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 8-3: Address Table Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 8-4: Address Table Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 8-5: Typical MDIO-managed System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 8-6: MDIO Write Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 8-7: MDIO Read Transaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Figure 8-8: MDIO Access through Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . 89

Chapter 9: Constraining the Core

Figure 9-1: Input GMII Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 9-2: Timing Report Setup/Hold Illustration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Figure 9-3: Input RGMII Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure 9-4: Timing Report Setup/Hold Illustration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Chapter 10: Clocking and Resetting

Figure 10-1: Clock Management Logic with External GMII . . . . . . . . . . . . . . . . . . . . . . . 109

Figure 10-2: Clock Management with External RGMII . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Figure 10-3: Clock Management Logic with External GMII (Multiple Cores). . . . . . . . 111

Figure 10-4: Clock Management Logic with External RGMII (Multiple Cores) . . . . . . 112

Figure 10-5: Reset Circuit for a Single Clock/reset Domain. . . . . . . . . . . . . . . . . . . . . . . . 112

10 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 11

-- DISCONTINUED PRODUCT --

Chapter 11: Interfacing to Other Cores

Figure 11-1: 1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS with TBI 114

Figure 11-2: 1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS and PMA

using a RocketIO Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Figure 11-3: 1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS and PMA

using a RocketIO transceiver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Figure 11-4: 1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS and PMA

using the RocketIO transceiver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Figure 11-5: Interfacing the Ethernet Statistics to the 1-Gigabit Ethernet MAC . . . . . . 120

Chapter 12: Implementing Your Design

Appendix A: Using the Client-Side FIFO

Figure A-1: Typical 10 Mbps/100 Mbps/ 1 Gbps Ethernet FIFO Implementation. . . . . 127

Figure A-2: Frame Transfer across LocalLink Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Figure A-3: Frame Transfer with Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

R

Appendix B: Core Verification, Compliance, and Interoperability

Appendix C: Calculating DCM Phase-Shifting

Appendix D: Core Latency

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 11

UG144 April 24, 2009

Page 12

-- DISCONTINUED PRODUCT --

R

12 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 13

-- DISCONTINUED PRODUCT --

Schedule of Tables

Chapter 1: Introduction

Chapter 2: Core Architecture

Table 2-1: Transmitter Client Interface Signal Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 2-2: Receive Client Interface Signal Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 2-3: Flow Control Interface Signal Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 2-4: Optional Management Interface Signal Pinout. . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 2-5: Optional MAC Unicast Address Signal Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 2-6: Optional Configuration Vector Signal Pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 2-7: Reset Signal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 2-8: GMII Interface Signal Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 2-9: MDIO Interface Signal Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Chapter 3: Generating the Core

Table 3-1: XCO File Values and Default Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Chapter 4: Designing with the Core

Table 4-1: Degree of Difficulty for Various Implementations . . . . . . . . . . . . . . . . . . . . . . 38

Chapter 5: Using the Client Side Data Path

Table 5-1: Abbreviations Used in Timing Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 5-2: Bit Definition for the Receiver Statistics Vector . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 5-3: Rx Statistics conversion to previous core GEMAC core versions. . . . . . . . . . . 46

Table 5-4: Bit Definition for the Transmitter Statistics Vector . . . . . . . . . . . . . . . . . . . . . . 51

Table 5-5: Tx Statistics conversion to previous core GEMAC core versions. . . . . . . . . . . 52

Chapter 6: Using Flow Control

Chapter 7: Using the Physical Side Interface

Chapter 8: Configuration and Status

Table 8-1: Management Interface Transaction Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 8-2: Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 8-3: Receiver Configuration Word 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 8-4: Receiver Configuration Word 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 8-5: Transmitter Configuration Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 8-6: Flow Control Configuration Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 8-7: Management Configuration Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 13

UG144 April 24, 2009

Page 14

-- DISCONTINUED PRODUCT --

R

Table 8-8: Unicast Address Word 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 8-9: Unicast Address Word 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 8-10: Address Table Configuration Word 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 8-11: Address Table Configuration Word 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 8-12: Address Filter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 8-13: Configuration Vector Bit Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Chapter 9: Constraining the Core

Table 9-1: Input GMII Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 9-2: Input RGMII Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Chapter 10: Clocking and Resetting

Chapter 11: Interfacing to Other Cores

Table 11-1: Management Interface Transaction Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Chapter 12: Implementing Your Design

Appendix A: Using the Client-Side FIFO

Table A-1: Transmit FIFO Client Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table A-2: Transmit FIFO LocalLink Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table A-3: Receive FIFO Client Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Table A-4: Receive FIFO LocalLink Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Appendix B: Core Verification, Compliance, and Interoperability

Appendix C: Calculating DCM Phase-Shifting

Appendix D: Core Latency

14 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 15

-- DISCONTINUED PRODUCT --

R

About This Guide

The LogiCORE™ IP 1-Gigabit Ethernet MAC User Guide provides information about

generating the core, customizing and simulating the core utilizing the provided example

design, and running the design files through implementation using the Xilinx tools.

Guide Contents

This guide contains the following chapters:

• Preface, “About this Guide” introduces the organization and purpose of the guide

and the conventions used in this document.

• Chapter 1, “Introduction” describes the core and related information, including

recommended design experience, additional resources, technical support, and

submitting feedback to Xilinx.

• Chapter 2, “Core Architecture” provides an overview of the core and discusses the

Physical/Client signal interfaces.

• Chapter 3, “Generating the Core” describes the graphical user interface options used

to generate the core.

• Chapter 4, “Designing with the Core” through Chapter 8, “Configuration and Status”

describe design parameters, including how to initialize the core, generate and

consume core packets, and how to operate the Management Interface.

• Chapter 9, “Constraining the Core” describes the constraints associated with the core.

• Chapter 10, “Clocking and Resetting” discusses special design considerations

associated with clock management logic, including the Gigabit Media Independent

Interface (GMII) and Reduced Gigabit Media Independent Interface (RGMII) options.

• Chapter 11, “Interfacing to Other Cores” describes how to interface the 1-Gigabit

Ethernet MAC core to the Ethernet 1000BASE-X PCS/PMA or SGMII core and the

Ethernet Statistics core.

• Chapter 12, “Implementing Your Design” provides instructions for how to set up

synthesis, simulation, and implementation environments and how to generate a

bitstream through the design flow.

• Appendix A, “Using the Client-Side FIFO” describes the FIFO provided in the

example design that accompanies the GEMAC core.

• Appendix B, “Core Verification, Compliance, and Interoperability” describes how the

core was verified and certified for compliance.

• Appendix C, “Calculating DCM Phase-Shifting” provides information about how to

calculate the system timing requirements when using DCMs with the core.

• Appendix D, “Core Latency” describes the latency of the core.

Preface

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 15

UG144 April 24, 2009

Page 16

-- DISCONTINUED PRODUCT --

R

Conventions

Typographical

Preface: About This Guide

This document uses the following conventions. An example illustrates each convention.

The following typographical conventions are used in this document:

Convention Meaning or Use Example

Messages, prompts, and

Courier font

Courier bold

Italic font

program files that the system

displays

Literal commands you enter in

a syntactical statement

Variables in a syntax

statement for which you must

supply values

References to other manuals See the User Guide for details.

speed grade: - 100

ngdbuild design_name

See the Development System

Reference Guide for more

information.

Emphasis in text

Dark Shading

Square brackets [ ]

Braces { }

Vertical bar |

Vertical ellipsis

.

.

.

Horizontal ellipsis . . . Omitted repetitive material

Notations

Items that are not supported

or reserved

An optional entry or

parameter. However, in bus

specifications, such as

bus[7:0], they are required.

A list of items from which you

must choose one or more

Separates items in a list of

choices

Repetitive material that has

been omitted

The prefix ‘0x’ or the suffix ‘h’

indicate hexadecimal notation

An ‘_n’ means the signal is

active low

If a wire is drawn so that it

overlaps the pin of a symbol,

the two nets are not connected.

This feature is not supported

ngdbuild [option_name]

design_name

lowpwr ={on|off}

lowpwr ={on|off}

IOB #1: Name = QOUT’

IOB #2: Name = CLKIN’

.

.

.

allow block block_name

loc1 loc2 ... locn;

A read of address

0x00112975 returned

45524943h.

usr_teof_n is active low.

16 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 17

Conventions

Online Document

-- DISCONTINUED PRODUCT --

R

The following linking conventions are used in this document:

Convention Meaning or Use Example

Blue text

Blue, underlined text

List of Acronyms

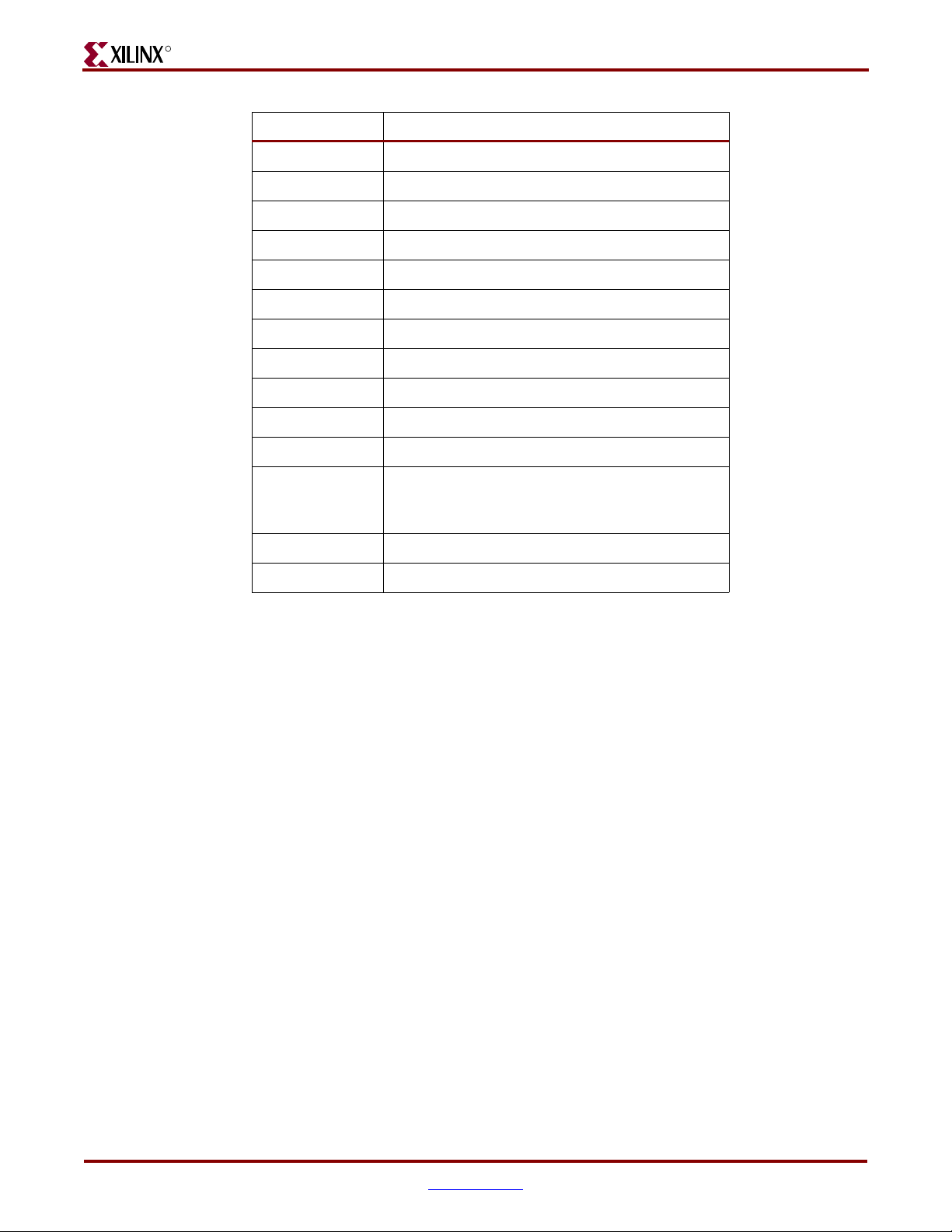

The following table describes acronyms used in this manual.

Acronym Spelled Out

CLB Configurable Logic Block

DCM Digital Clock Manager

DDR Double Data Rate

FCS Frame Check Sequence

FPGA Field Programmable Gate Array.

GBIC Gigabit Interface Converter

Gbps Gigabit per second

Cross-reference link to a

location in the current

document

Hyperlink to a website (URL)

See the section “Additional

Resources” for details.

See “Title Formats” in

Chapter 1 for details.

Go to w

latest speed files.

ww.xilinx.com for the

GEMAC Gigabit Ethernet Media Access Controller

GMII Gigabit Media Independent Interface

HDL Hardware Description Language

IO Input/Output

IOB Input/Output Block

IP Intellectual Property

ISE® Integrated Software Environment

LSW Least Significant Word

MAC Media Access Controller

MDIO Management Data Input/Output

MHz Mega Hertz

MMD MDIO Managed Device

ms milliseconds

MSW Most Significant Word

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 17

UG144 April 24, 2009

Page 18

-- DISCONTINUED PRODUCT --

R

Preface: About This Guide

Acronym Spelled Out

NCD Native Circuit Description

NGC Native Generic Circuit

NGD Native Generic Database

ns nanoseconds

PCB Printed Circuit Board

PCS Physical Coding Sublayer

PHY physical-side interface

PMA Physical Medium Attachment

PMD Physical Medium Dependent

RGMII Reduced Gigabit Media Independent Interface

SGMII Serial Gigabit Media Independent Interface

VHDL VHSIC Hardware Description Language

(VHSIC an acronym for Very High-Speed

Integrated Circuits).

VCS Verilog Compiled Simulator

VLAN Virtual LAN (Local Area Network)

18 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 19

R

Introduction

The 1-Gigabit Ethernet MAC (GEMAC) core is a fully verified solution that supports

Verilog-HDL and VHDL. In addition, the example design provided with the core is

provided in both Verilog and VHDL.

This chapter introduces the GEMAC core and provides other related information,

including recommended design experience, additional resources, technical support, and

ways to submit feedback to Xilinx.

-- DISCONTINUED PRODUCT --

Chapter 1

About the Core

The GEMAC core is a Xilinx CORE Generator™ IP core, included in the latest IP Update on

the Xilinx IP Center. For detailed information about the core, see the GEMAC product

page. For information about licensing options, see Chapter 2, “Licensing the Core,” in the

1-Gigabit Ethernet MAC Getting Started Guide.

Recommended Design Experience

Although the GEMAC core is a fully verified solution, the challenge associated with

implementing a complete design varies, depending on the configuration and functionality

of the application. For best results, previous experience building high performance,

pipelined FPGA designs using Xilinx implementation software and user constraint files

(UCFs) is recommended.

Contact your local Xilinx representative for a closer review and estimation for your specific

requirements.

Additional Core Resources

For detailed information and updates about the GEMAC core, see the following

documents, located on the GEMAC product page

• 1-Gigabit Ethernet MAC Data Sheet

• 1-Gigabit Ethernet MAC Getting Started Guide

.

After generating the core, the 1-Gigabit Ethernet MAC Release Notes are available from the

document directory.

Related Xilinx Ethernet Products and Services

See the Ethernet Products and Services page.

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 19

UG144 April 24, 2009

Page 20

R

Specifications

• IEEE 802.3 2005

• Reduced Gigabit Media Independent Interface (RGMII) version 2.0

Technical Support

For technical support, see support.xilinx.com/. Questions are routed to a team of engineers

with expertise using the GEMAC core.

Xilinx will provide technical support for use of this product as described in the 1-Gigabit

Ethernet MAC User Guide and the 1-Gigabit Ethernet MAC Getting Started Guide. Xilinx

cannot guarantee timing, functionality, or support of this product for designs that do not

follow these guidelines.

Feedback

Xilinx welcomes comments and suggestions about the GEMAC core and the

documentation supplied with the core.

-- DISCONTINUED PRODUCT --

Chapter 1: Introduction

GEMAC Core

For comments or suggestions about the GEMAC core, please submit a WebCase from

s

upport.xilinx.com/. Be sure to include the following information:

• Product name

• Core version number

• Explanation of your comments

Document

For comments or suggestions about this document, please submit a WebCase from

s

upport.xilinx.com/. Be sure to include the following information:

• Document title

• Document number

• Page number(s) to which your comments refer

• Explanation of your comments

20 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 21

-- DISCONTINUED PRODUCT --

R

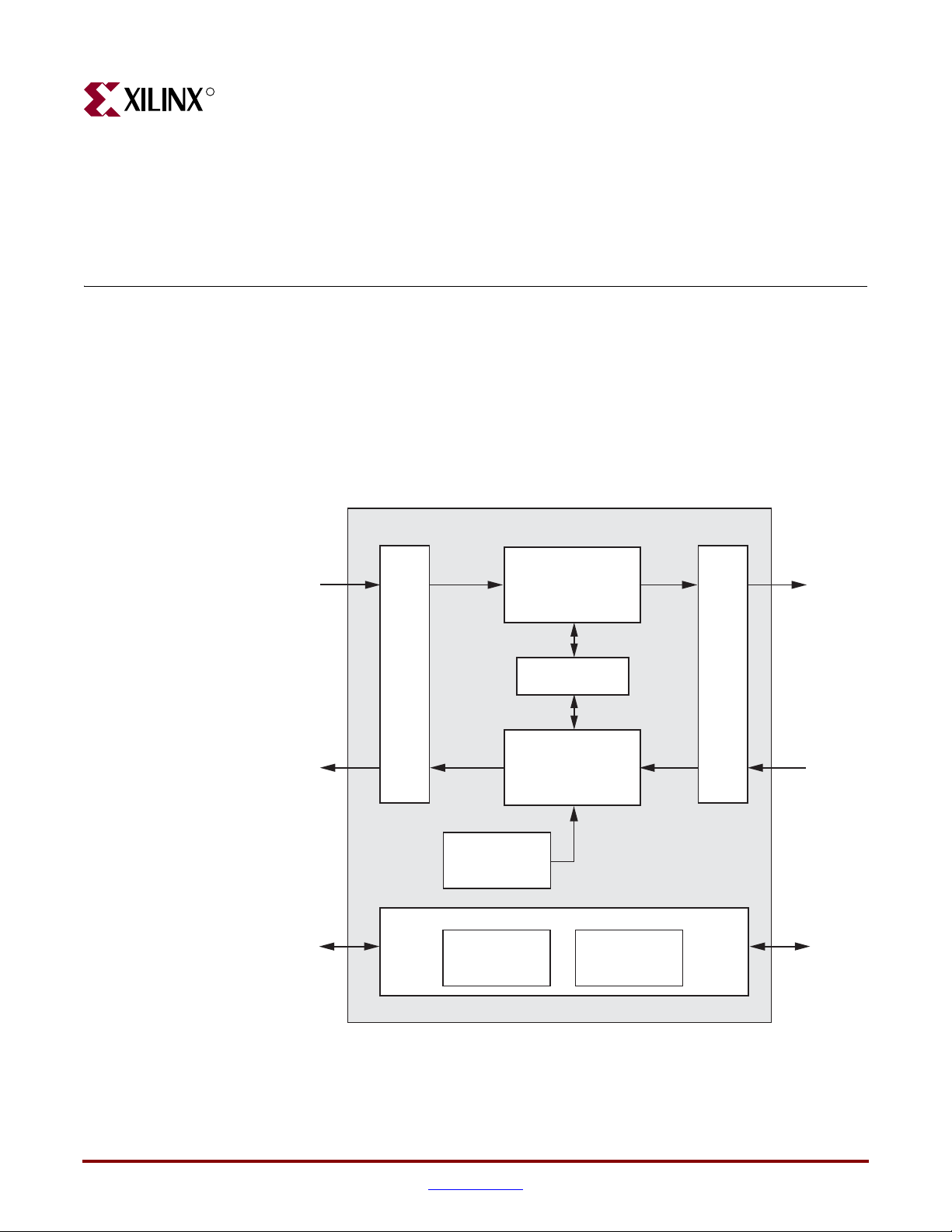

Core Architecture

This chapter describes the GEMAC core architecture, including the major functional blocks

and all interfaces.

System Overview

Figure 2-1 illustrates a block diagram of the GEMAC core with all the major functional

blocks and interfaces. Descriptions of the functional blocks and interfaces are provided in

the sections that follow.

Chapter 2

Client

Tr ansmitter

Interface

Client

Receiver

Interface

Client

Management

Interface

Gigabit Ethernet MAC Core

Client Interface

Optional

Address

Filter

Configuration MDIO

Tr ansmit Engine

Flow Control

Receive Engine

Optional Management

GMII Block

To Physical

Sublayers

Figure 2-1: Block Diagram

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 21

UG144 April 24, 2009

Page 22

R

Core Components

Transmit Engine

The Transmit Engine accepts Ethernet frame data from the Client Transmitter Interface,

adds the preamble field to the start of the frame, adds padding bytes (if required) to ensure

that the frame meets the minimum frame length requirements, and adds the frame check

sequence (when configured to do so). The transmitter also ensures that the inter-frame

spacing between successive frames is at least the minimum specified. The frame is then

converted into a format that is compatible with the GMII and sent to the GMII Block.

Receive Engine

The Receive Engine accepts Ethernet frame data from the GMII Block, removes the

preamble field at the start of the frame, removes padding bytes and Frame Check Sequence

(if required, and when configured to do so). The receiver also performs error detection on

the received frame using information such as the frame check sequence field, received

GMII error codes, and legal frame size boundaries.

-- DISCONTINUED PRODUCT --

Chapter 2: Core Architecture

Flow Control

The Flow Control block is designed to clause 31 of the IEEE 802.3-2005 standard. The MAC

may be configured to send pause frames and to act upon their reception. These two

behaviors can be configured independently.

Address Filter

The Address Filter checks the address of incoming frames into the receiver. If the Address

Filter is enabled, the device will not pass frames that do not contain one of a set of known

addresses to the client.

Management Interface

The optional processor-independent Management Interface has standard address, data,

and control signals. It may be used as is, or you can apply a logical shim to interface to

common bus architectures. See Chapter 8, “Configuration and Status.”

This interface is used to access the following blocks.

• Configuration Register After power up or reset, the client may reconfigure the core

parameters from their defaults. Configuration changes can be written at any time.

• MDIO Interface The Management Interface is also used to access the MDIO interface

of the GEMAC core; this interface is typically connected to the MDIO port of a

physical layer device (PHY) to access its configuration and status registers. The MDIO

format is defined in IEEE802.3 clause 22.

GMII Block

This implements GMII style signaling for the physical interface of the core and is typically

attached to a physical layer device (PHY), either off-chip or internally integrated.

22 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 23

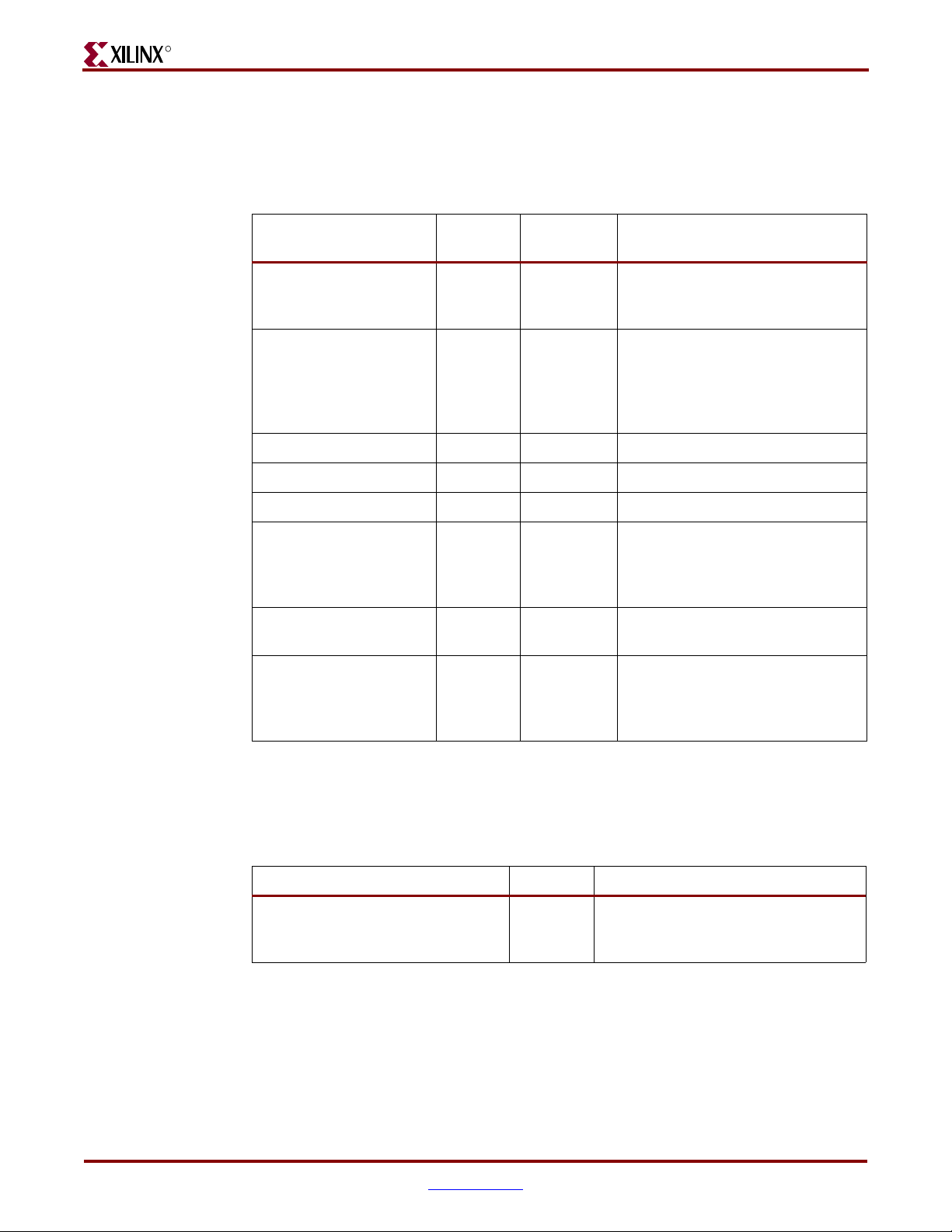

Core Interfaces

Core Interfaces

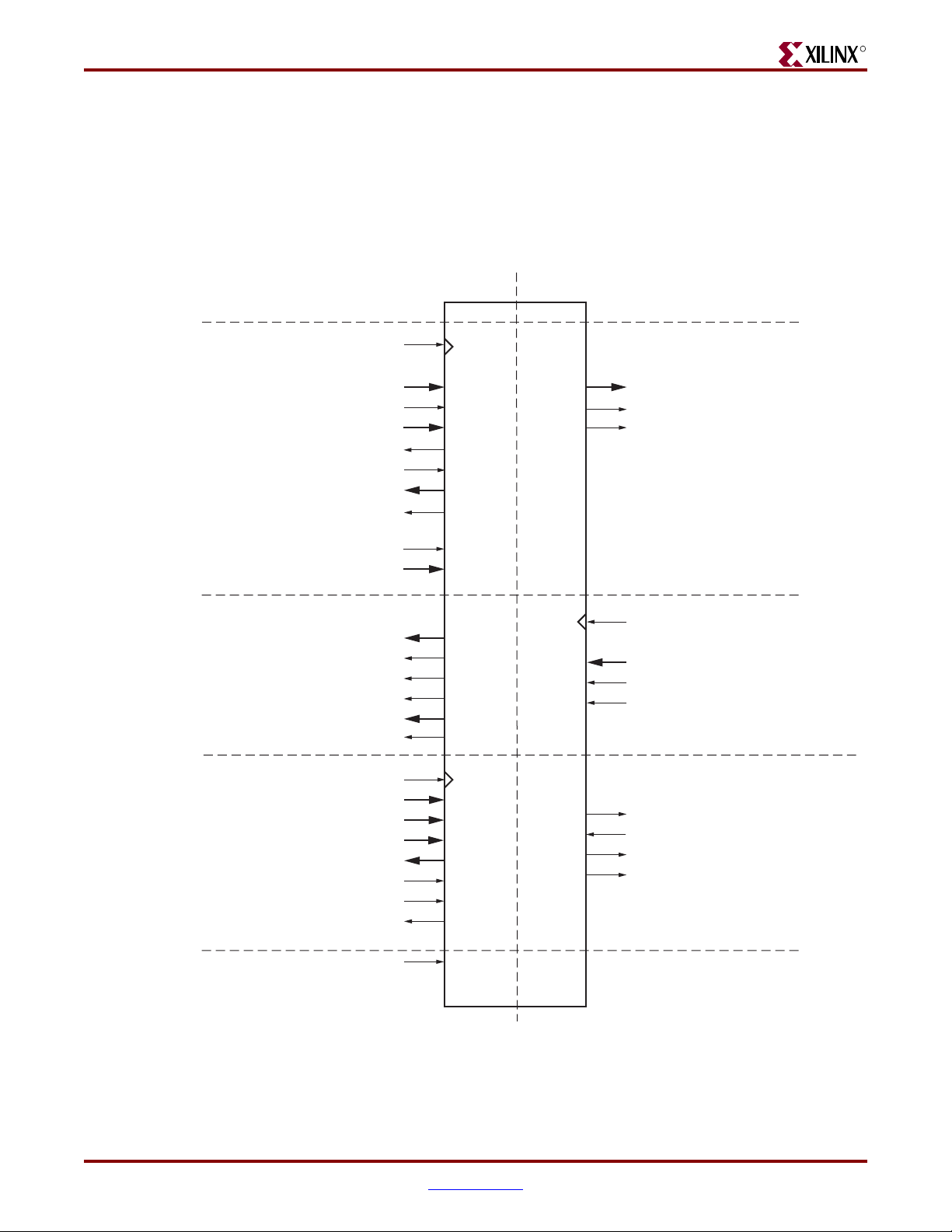

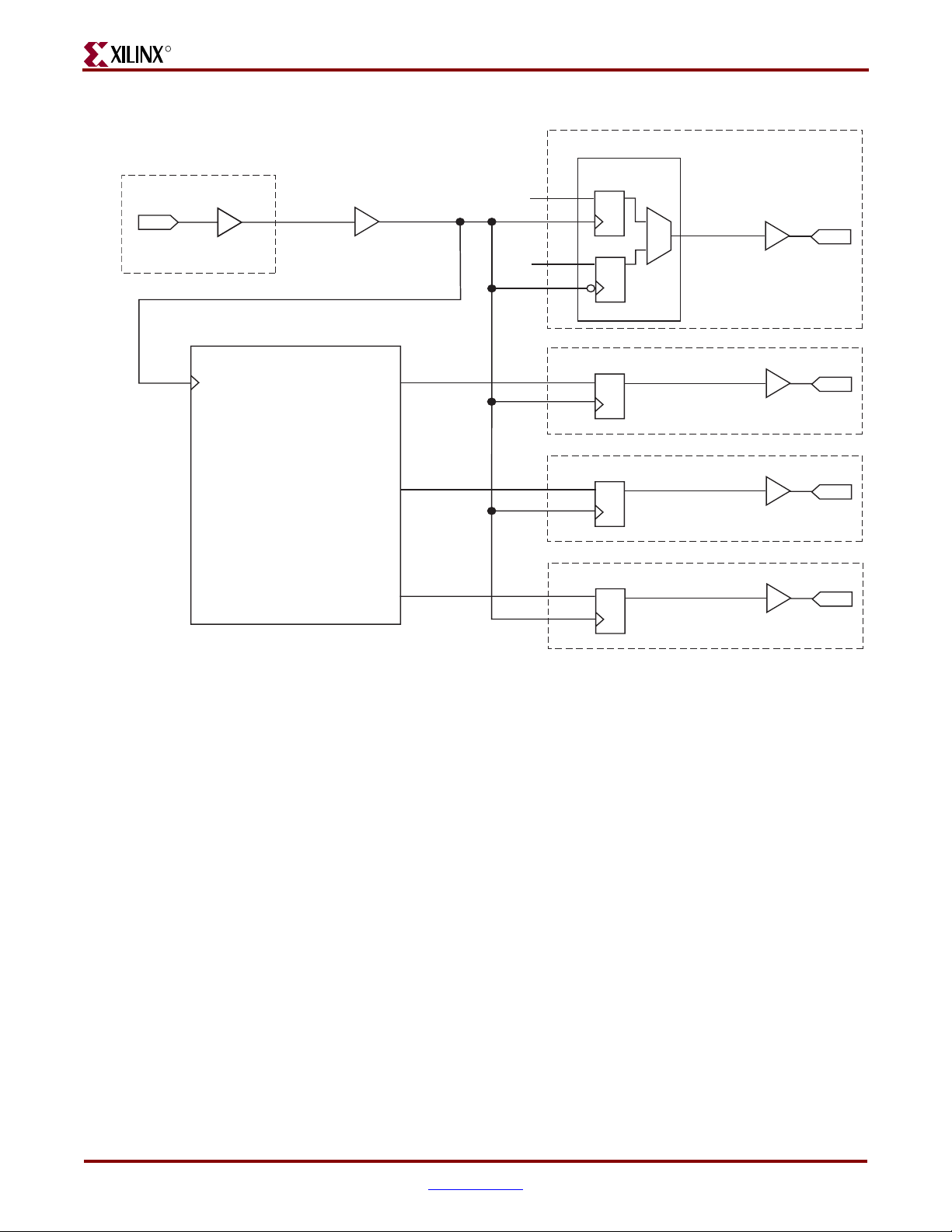

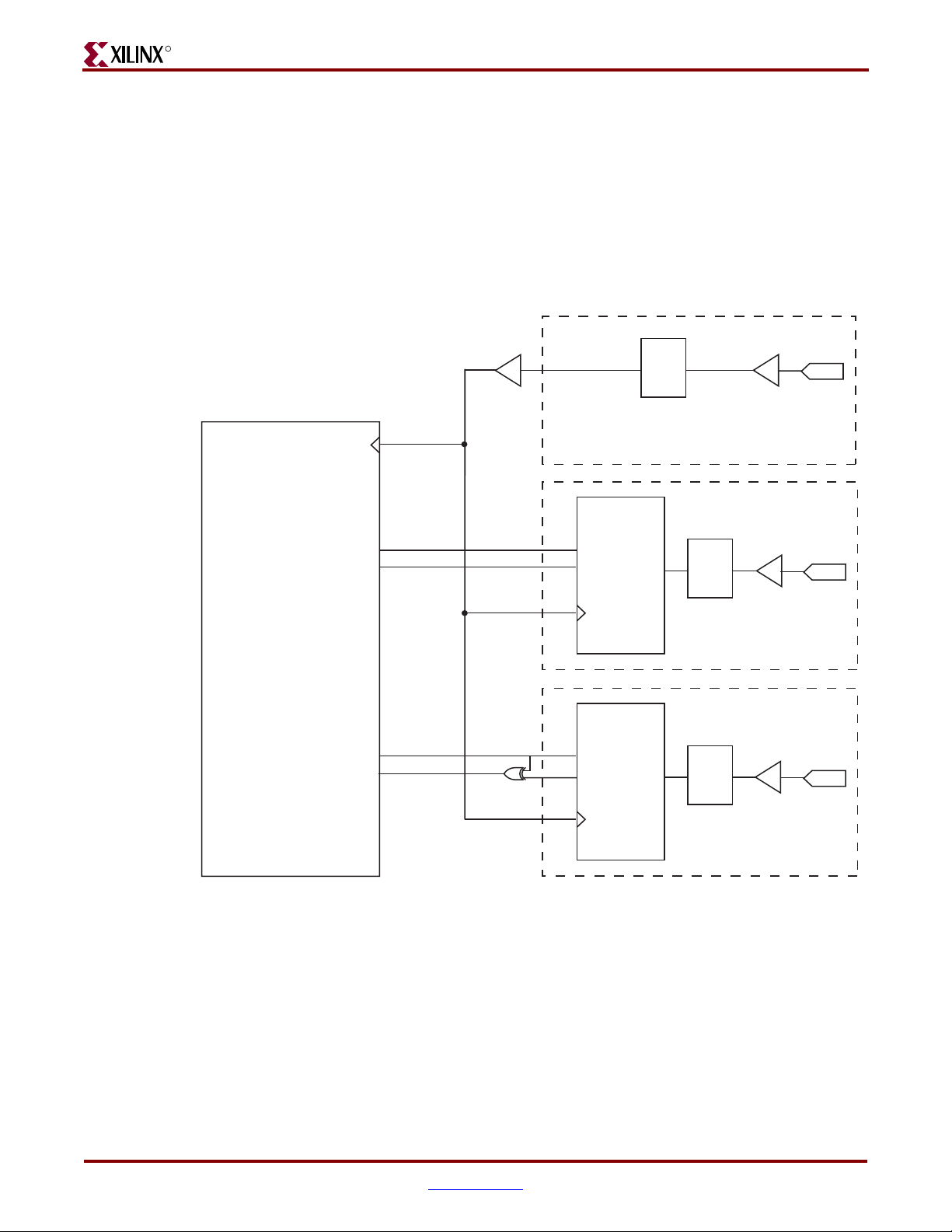

GMAC Core with Optional Management Interface

Figure 2-2 shows the pinout for the GEMAC core using the optional Management

Interface. The interface is unchanged, regardless of whether the optional Address Filter is

included.

Client Side Interface Physical Side Interface (GMII)

-- DISCONTINUED PRODUCT --

R

gtx_clk domain

tx_ifg_delay[7:0]

tx_statistics_vector[31:0]

tx_statistics_valid

pause_val[15:0]

gmii_rx_clk domain

rx_statistics_vector[27:0]

rx_statistics_valid

host_clk domain

host_opcode[1:0]

host_wr_data[31:0]

host_rd_data[31:0]

gtx_clk

tx_data[7:0]

tx_data_valid

tx_ack

tx_underrun

pause_req

rx_data[7:0]

rx_data_valid

rx_good_frame

rx_bad_frame

host_clk

host_addr[9:0]

host_miim_sel

host_req

host_miim_rdy

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

gmii_rx_clk

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

mdc

mdio_in

mdio_out

mdio_tri

reset

Figure 2-2: Component Pinout for MAC with Optional Management Interface

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 23

UG144 April 24, 2009

Page 24

-- DISCONTINUED PRODUCT --

R

Chapter 2: Core Architecture

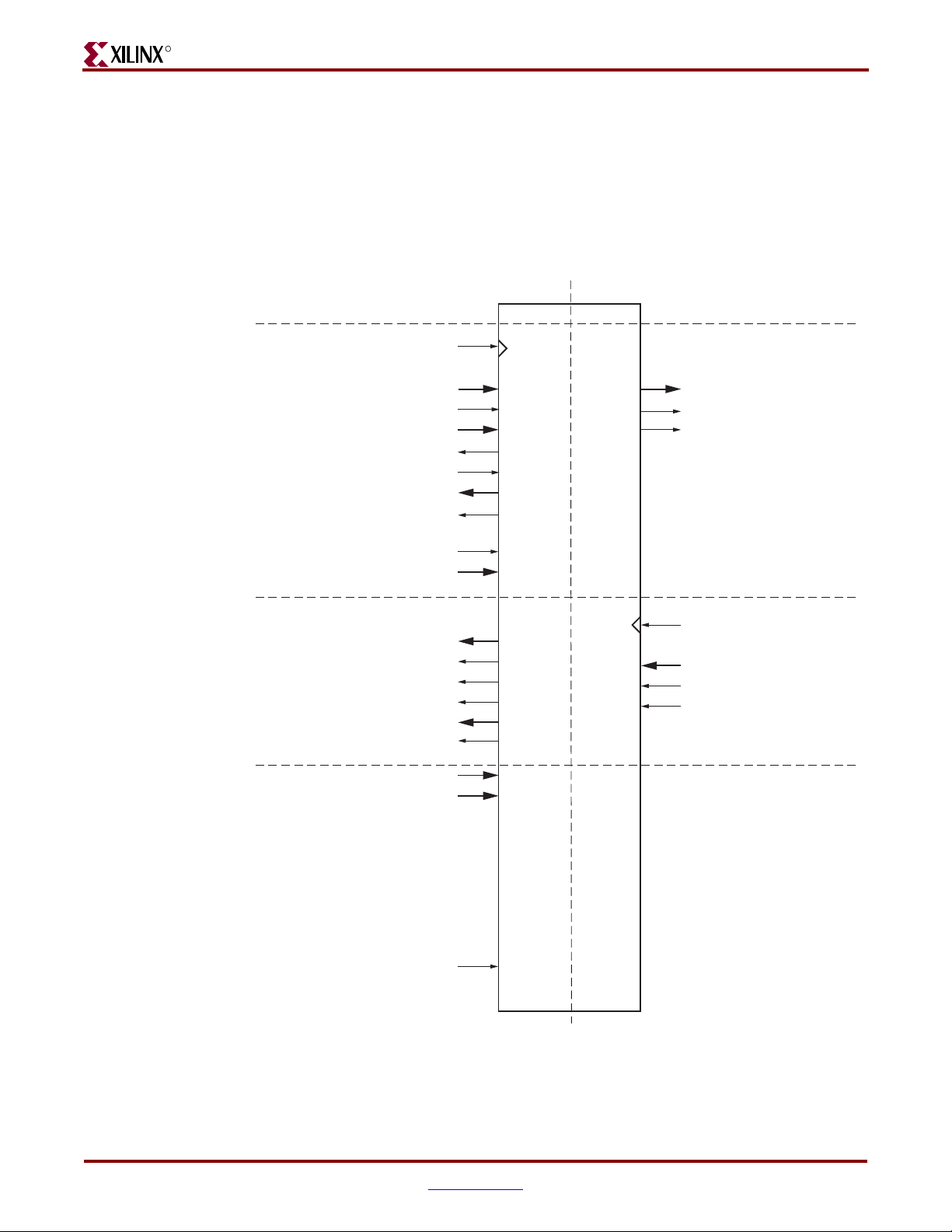

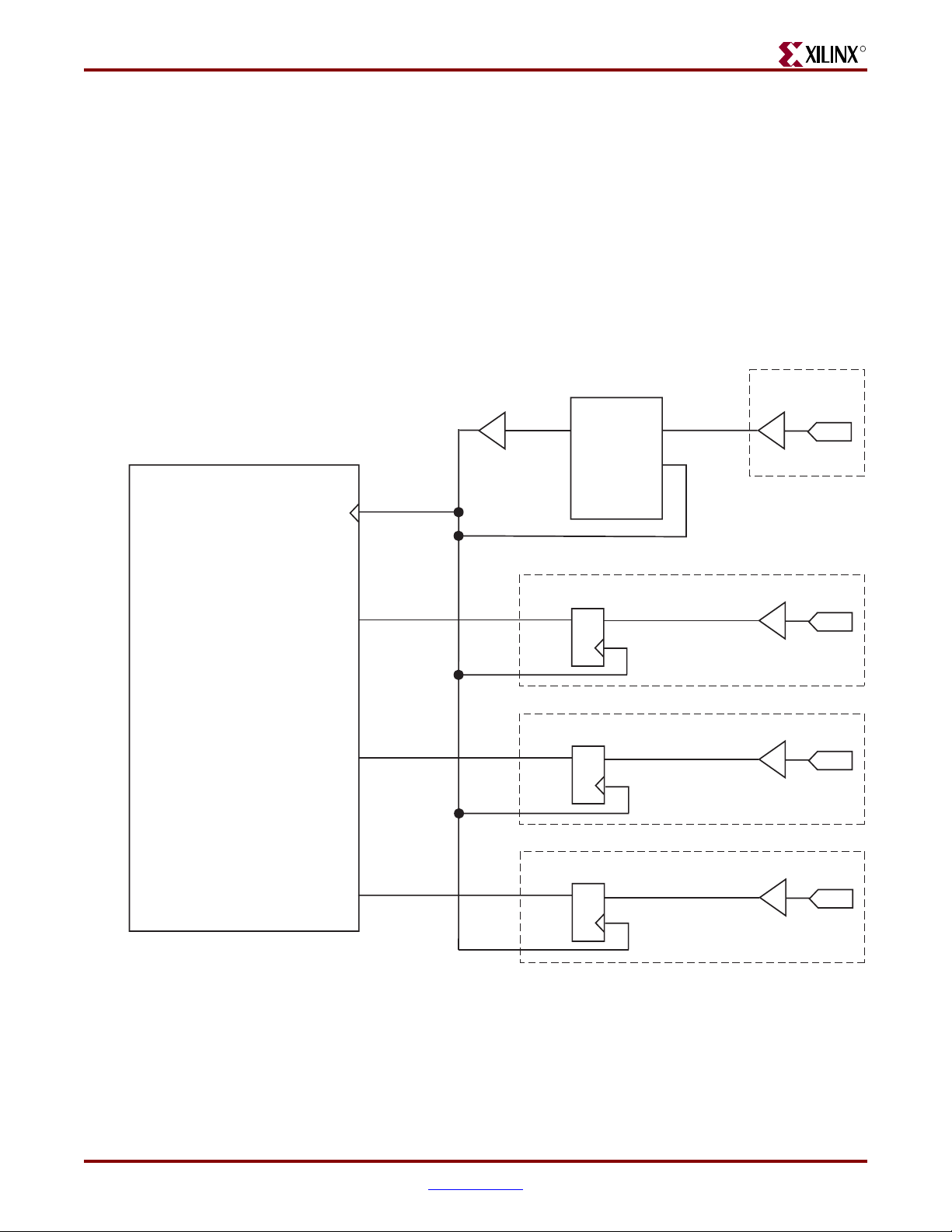

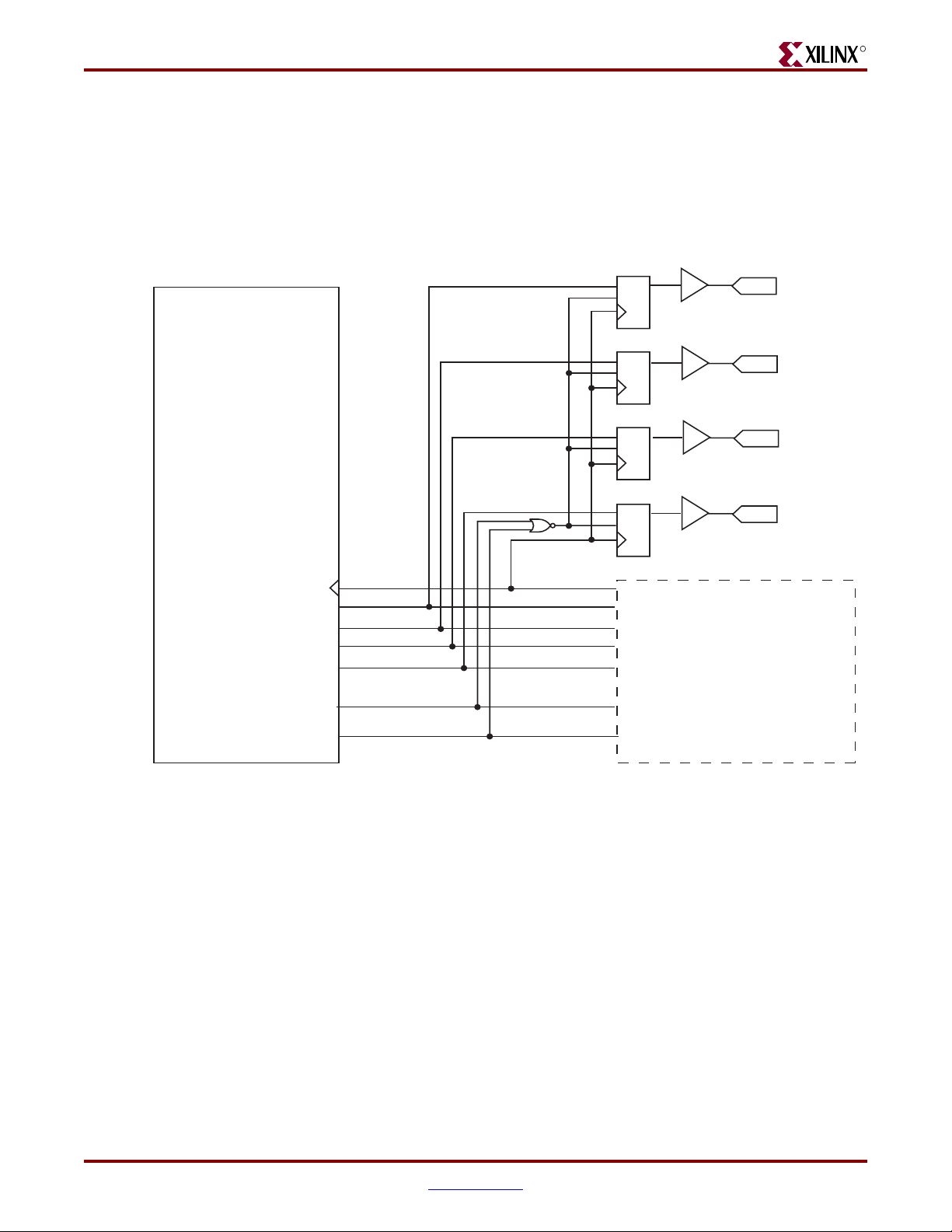

GMAC Core Without Management Interface and With Address Filter

Figure 2-3 shows the pinout for the GEMAC core when the optional Management Interface

is omitted and the optional Address Filter is included in the core.

The configuration_vector[67:0] input provides the method for configuration of

the core, and mac_unicast_address[47:0] input provides the method of setting the

unicast address used by the Address Filter.

Client Side Interface Physical Side Interface (GMII)

gtx_clk domain

tx_data[7:0]

tx_data_valid

tx_ifg_delay[7:0]

tx_underrun

tx_statistics_vector[31:0]

tx_statistics_valid

pause_req

pause_val[15:0]

gmii_rx_clk domain

rx_data[7:0]

rx_data_valid

rx_good_frame

rx_bad_frame

rx_statistics_vector[27:0]

rx_statistics_valid

mac_unicast_address[47:0]

configuration_vector[67:0]

gtx_clk

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

tx_ack

gmii_rx_clk

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

reset

Figure 2-3: Component Pinout for MAC without Optional Management Interface

and with Optional Address Filter

24 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 25

Core Interfaces

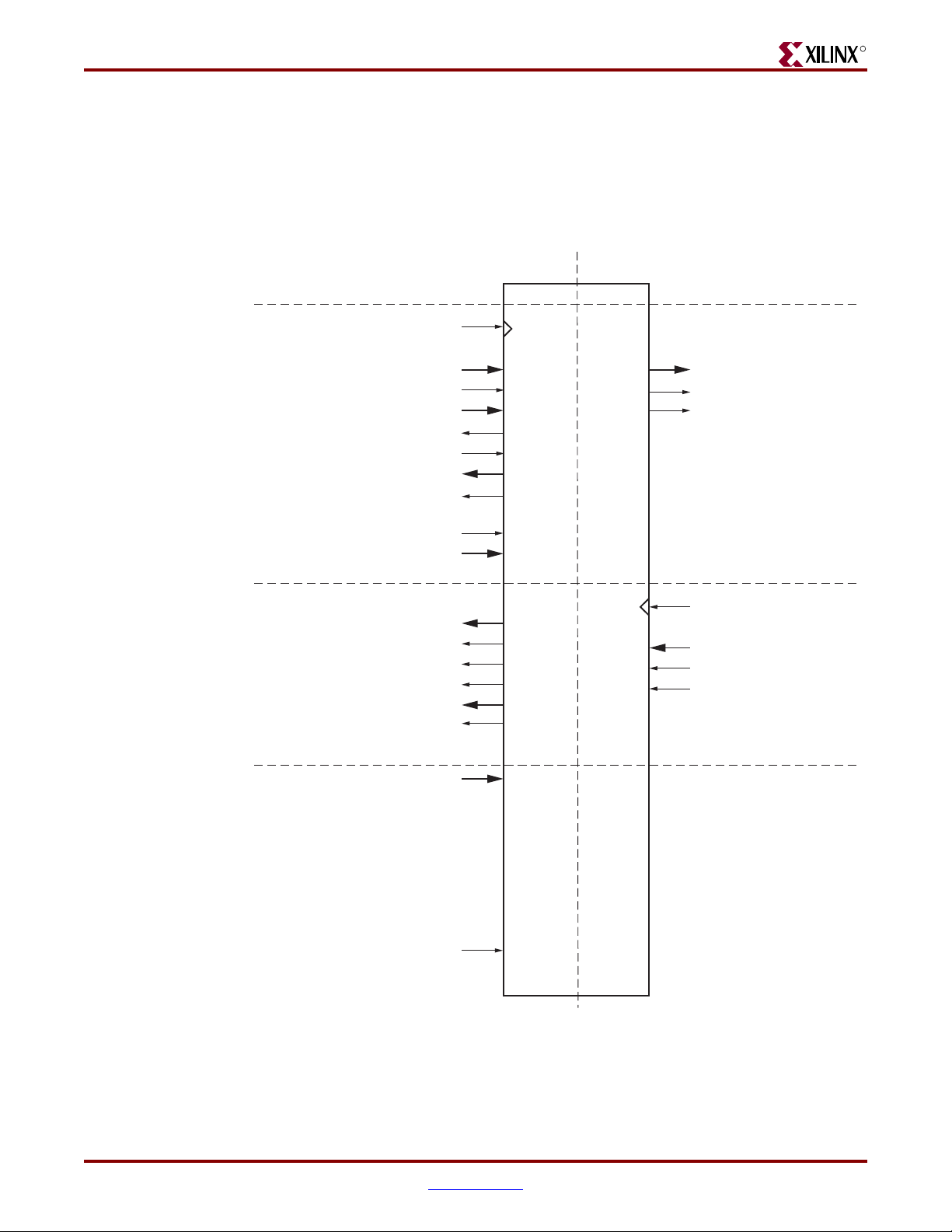

GEMAC Core Without Management Interface and Without Address Filter

-- DISCONTINUED PRODUCT --

R

Figure 2-4 shows the pinout for the GEMAC core when the optional Management Interface

is omitted and the optional Address Filter is omitted.

The configuration_vector[67:0] input provides the method for configuration of

the core.

Client Side Interface Physical Side Interface (GMII)

gtx_clk domain

tx_ifg_delay[7:0]

tx_statistics_vector[31:0]

tx_statistics_valid

pause_val[15:0]

gmii_rx_clk domain

rx_data_valid

rx_good_frame

rx_bad_frame

rx_statistics_vector[27:0]

rx_statistics_valid

gtx_clk

tx_data[7:0]

tx_data_valid

tx_ack

tx_underrun

pause_req

rx_data[7:0]

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

gmii_rx_clk

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

configuration_vector[67:0]

reset

Figure 2-4: Component Pinout for MAC without Optional Management Interface or Optional Address Filter

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 25

UG144 April 24, 2009

Page 26

R

All ports of the core are internal connections in FPGA fabric. An HDL example design is

delivered with the core that will add IBUFs, OBUFs, and IOB flip-flops to the external

signals of the Gigabit Media Independent Interface (GMII) or Reduced Gigabit Media

Independent Interface (RGMII).

All clock management logic is placed in this example design, which allows for more

flexibility in implementation (for example, in designs using multiple cores). This example

design is provided in both VHDL and Verilog. For more information about example

designs, see the 1-Gigabit Ethernet MAC Getting Started Guide.

Client Side Interface

Transmitter Interface

Tab le 2- 1 describes the client-side transmitter signals of the GEMAC core. These signals are

used to transmit data from the client logic into the core. See “Transmitting Outbound

Frames,” on page 47.

The Transmitter Interface is designed to be connected to internal device logic only.

Attempting to add external ports to this interface will result in a breakdown of the

handshaking protocol used by this interface.

-- DISCONTINUED PRODUCT --

Chapter 2: Core Architecture

Table 2-1: Transmitter Client Interface Signal Pins

Signal Direction

Clock

Domain

Description

gtx_clk Input n/a Clock signal provided to the core at

125 MHz. Tolerance must be

within IEEE 802.3-2005

specification. This clock signal is

used by all of the transmitter logic.

tx_data[7:0] Input gtx_clk Frame data to be transmitted is

supplied on this port.

tx_data_valid Input gtx_clk Control signal for tx_data port.

tx_ifg_delay[7:0] Input gtx_clk Control signal for configurable

Inter Frame Gap adjustment.

tx_ack Output gtx_clk Handshaking signal asserted when

the current data on tx_data has

been accepted.

tx_underrun Input gtx_clk Asserted by clien t to fo rce GEMA C

core to corrupt the current frame.

tx_statistics_vector[31:0] Output gtx_clk Provides statistical information

about the last frame transmitted.

tx_statistics_valid Output gtx_clk Asserted at end of frame

transmission, indicating that the

tx_statistics_vector is valid.

26 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 27

Core Interfaces

-- DISCONTINUED PRODUCT --

R

Receiver Interface

Tab le 2- 2 describes the client-side receiver signals of the GEMAC core. These signals are

used by to transfer data to the client. See “Receiving Inbound Frames,” on page 39.

Table 2-2: Receive Client Interface Signal Pins

Signal Direction Clock Domain Description

rx_data[7:0] Output gmii_rx_clk Frame data received is

supplied on this port.

rx_data_valid Output gmii_rx_clk Control signal for the rx_data

port.

rx_good_frame Output gmii_rx_clk Asserted at end of frame

reception to indicate that the

frame should be processed by

the MAC client.

rx_bad_frame Output gmii_rx_clk Asserted at end of frame

reception to indicate that the

frame should be discarded by

the MAC client.

rx_statistics_vector[27:0] Output gmii_rx_clk Provides statistical

information about the last

frame received.

rx_statistics_valid Output gmii_rx_clk Asserted at end of frame

reception, indicating that the

rx_statistics_vector is valid.

Flow Control Interface

Tab le 2- 3 describes the signals used by the client to request a flow control action from the

transmit engine. See “Using Flow Control,” on page 53.

Table 2-3: Flow Control Interface Signal Pinout

Signal Direction Clock Domain Description

pause_req Input gtx_clk Pause request. sends a pause

frame down the link.

pause_val[15:0] Input gtx_clk Pause value; inserted into the

parameter field of the

transmitted pause frame.

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 27

UG144 April 24, 2009

Page 28

-- DISCONTINUED PRODUCT --

R

Management Interface (Optional)

Tab le 2- 4 describes the optional signals used by the client to access the management

features of the GEMAC core. See “Using the Optional Management Interface,” on page 77.

Table 2-4: Optional Management Interface Signal Pinout

Chapter 2: Core Architecture

Signal Direction

Clock

Domain

Description

host_clk Input n/a Clock for the Management

Interface; must be 10 MHz or

above.

host_opcode[1:0] Input host_clk Defines operation to be performed

over MDIO interface. Bit 1 is also

used as a read/write control

signal for configuration register

access.

host_addr[9:0] Input host_clk Address of register to be accessed.

host_wr_data[31:0] Input host_clk Data to write to register .

host_rd_data[31:0] Output host_clk Data read from register.

host_miim_sel Input host_clk When asserted, the MDIO

interface is accessed. When not

asserted, the configuration

registers are accessed.

host_req Input host_clk Used to signal a transaction on the

MDIO interface.

host_miim_rdy Output host_clk When high, the MDIO interface

has completed any pending

transaction and is ready for a new

transaction.

MAC Unicast Address (Optional)

Tab le 2- 5 describes the alternative method of access to the unicast address registers when

the optional Management Interface is not present.

Table 2-5: Optional MAC Unicast Address Signal Pinout

Signal Direction Description

mac_unicast_address[47:0] Input Used to assess the MAC unicast

address registers when the

Management Interface is not used

Note: All bits are registered on input but may be treated as asynchronous inputs.

28 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 29

Core Interfaces

-- DISCONTINUED PRODUCT --

R

Configuration Vector (Optional)

Tab le 2- 6 describes the alternative to the optional Management Interface signals. The

Configuration Vector uses direct inputs to the core to replace the functionality of the MAC

configuration bits. See “Access without the Management Interface,” on page 90.

Table 2-6: Optional Configuration Vector Signal Pinout

Signal Direction Description

configuration_vector[67:0] Input Used to replace the functionality of

the MAC Configuration Registers

when the Management Interface is

not used

Note: All bits are registered on input but may be treated as asynchronous inputs.

Asynchronous Reset

Tab le 2- 7 describes the asynchronous reset signal for the entire core.

Table 2-7: Reset Signal

Signal Direction Clock Domain Description

reset Input n/a Asynchronous reset for entire core

Physical Side Interface

GMII

Tab le 2- 8 describes the GMII-style interface signals of the core. See Chapter 7, “Using the

Physical Side Interface.”

Table 2-8: GMII Interface Signal Pinout

Signal Direction Clock Domain Description

gmii_txd[7:0] Output gtx_clk Transmit data from MAC

gmii_tx_en Output gtx_clk Transmit control signal from MAC

gmii_tx_er Output gtx_clk Transmit control signal from MAC

gmii_rx_clk Input n/a Receive clock from external PHY (125

gmii_rxd[7:0] Input gmii_rx_clk Received data to MAC

gmii_rx_dv Input gmii_rx_clk Received control signal to MAC

MHz)

gmii_rx_er Input gmii_rx_clk Received control signal to MAC

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 29

UG144 April 24, 2009

Page 30

R

MDIO Interface

-- DISCONTINUED PRODUCT --

Chapter 2: Core Architecture

Tab le 2- 9 describes the MDIO Interface signals. See “Using the MDIO interface,” on page

76.

Table 2-9: MDIO Interface Signal Pinout

Signal Direction

Clock

Domain

Description

mdc Output host_clk Management Clock: programmable

frequency derived from host_clk.

mdio_in

1

Input host_clk Input data signal for communication with

PHY configuration and status. Tie high if

unused.

mdio_out

1

Output host_clk Output data signal for communication

with PHY configuration and status.

mdio_tri

1

Output host_clk Tristate control for MDIO signals; 0 signals

that the value on mdio_out should be

asserted onto the MDIO bus.

1. mdio_in, mdio_out and mdio_tri can be connected to a Tri-state buffer to create a bi-directional mdio

signal suitable for connection to an external PHY.

30 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 31

-- DISCONTINUED PRODUCT --

R

Generating the Core

The GEMAC core is generated through the Xilinx CORE Generator™ using a graphical

user interface (GUI). This chapter describes the GUI options used to generate and

customize the core.

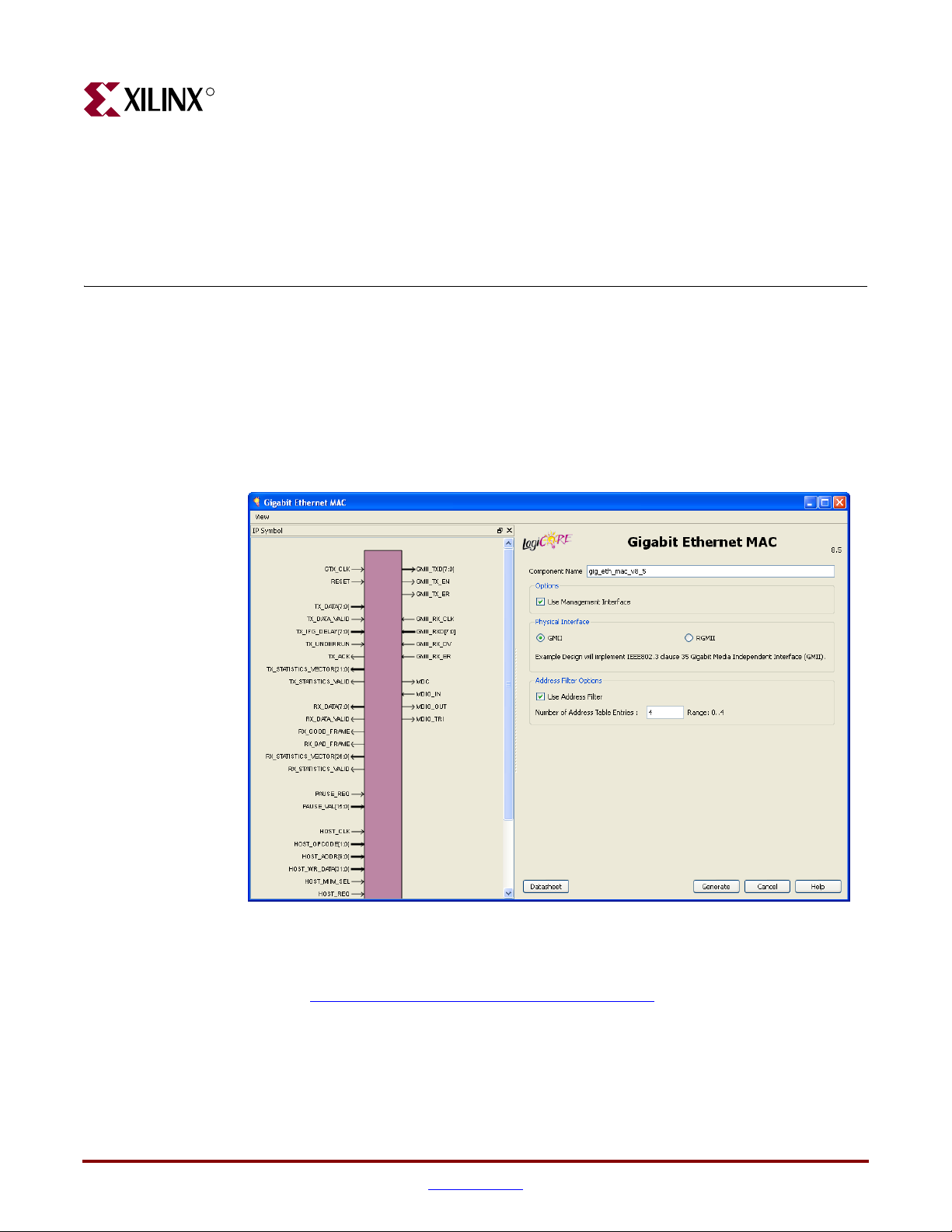

Graphical User Interface

Figure 3-1 shows the main GEMAC core user GUI screen.

Chapter 3

Figure 3-1: 1-Gigabit Ethernet MAC Main Screen

For general help starting and using CORE Generator on your system, see the

documentation supplied with the Xilinx ISE® software, including the CORE Generator

Guide at www.xilinx.com/support/software_manuals.htm

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 31

UG144 April 24, 2009

.

Page 32

-- DISCONTINUED PRODUCT --

R

Component Name

The component name is used as the base name of the output files generated for the core.

Names must begin with a letter and must be composed from the following characters:

a through z, 0 through 9 and “_”.

Management Interface

Select this option to include the optional Management Interface (see “Using the Optional

Management Interface,” on page 77). If this option is not selected, the core is generated

with a replacement configuration vector (see “Access without the Management Interface,”

on page 90). The default is to use the Management Interface.

Address Filter

Select this option to include the optional Address Filter. This prevents the reception of

frames that are not addressed to this MAC (see “Address Filter,” on page 44). The default

is to use the Address Filter.

Chapter 3: Generating the Core

Number of Address Table Entries

The Address Filter can be instantiated with an address table that holds up to 4 additional

valid addresses. You may select an integer between 0 and 4 to define the number of

addresses that are present in the table.

This option is only available when the Management Interface and Address Filter have been

selected. The default is to use 4 address table entries.

Physical Interface

Depending on the target Xilinx FPGA architecture, it may be possible to select from two

different physical interface choices for the core:

• GMII. See Chapter 7, “Implementing External GMII”

• RGMII. See Chapter 7, “Implementing External RGMII”

The choice of physical interface determines the content of the example design delivered

with the core. The external GMII or RGMII is added in the HDL top-level design file. There

is no change in the core netlist for this option. The default is the GMII physical interface.

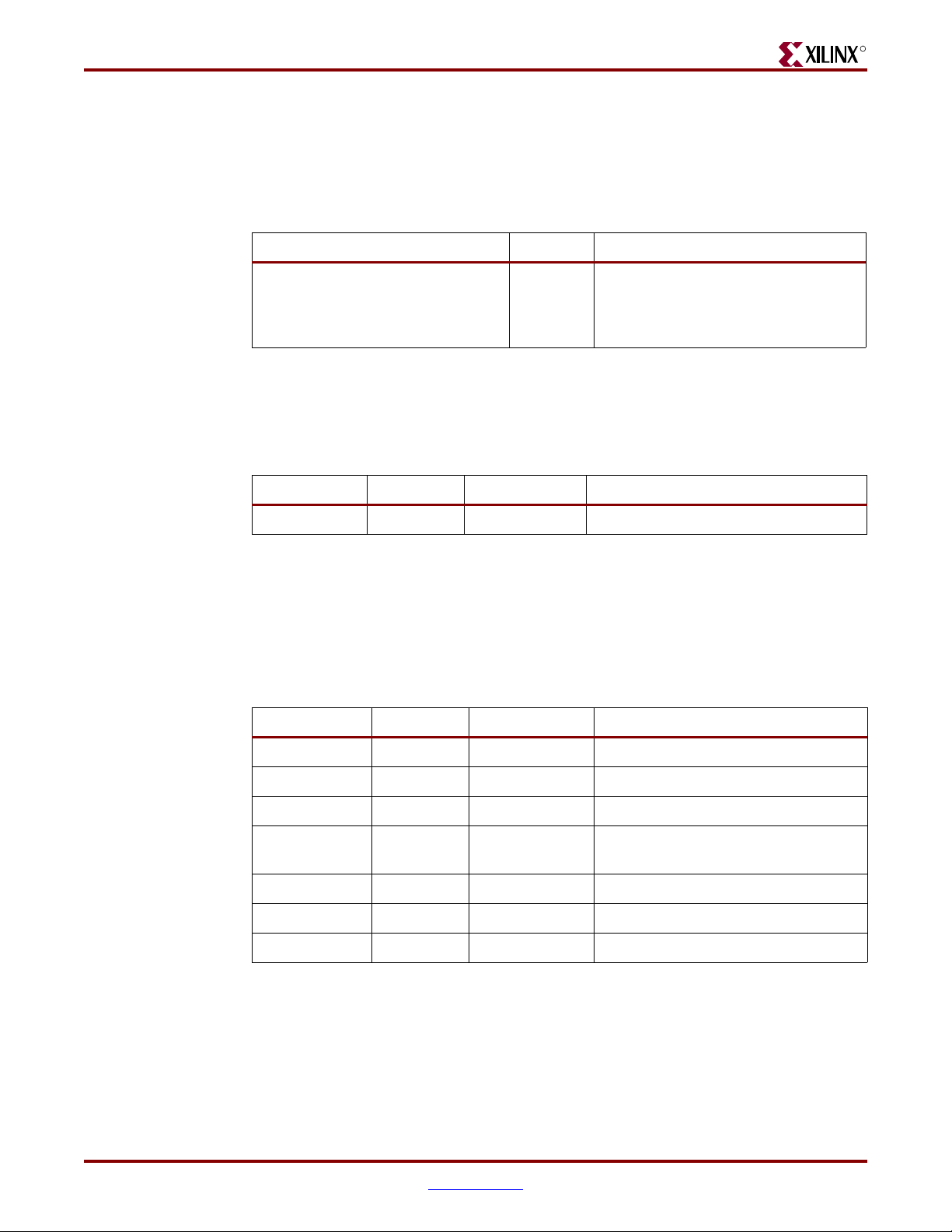

Parameter Values in the XCO File

XCO file parameter names and their values are identical to the names and values shown in

the GUI, except that underscore characters (_) are used instead of spaces. The text in an

XCO file is not case-sensitive.

Tab le 3- 1 defines the XCO file parameters and values and summarizes the GUI defaults.

The following is an example of the CSET parameters in an XCO file.

CSET component_name = abc123

CSET physical_interface = gmii

CSET management_interface = true

CSET address_filter = true

CSET no_of_address_table_entries = 4

32 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 33

Output Generation

-- DISCONTINUED PRODUCT --

R

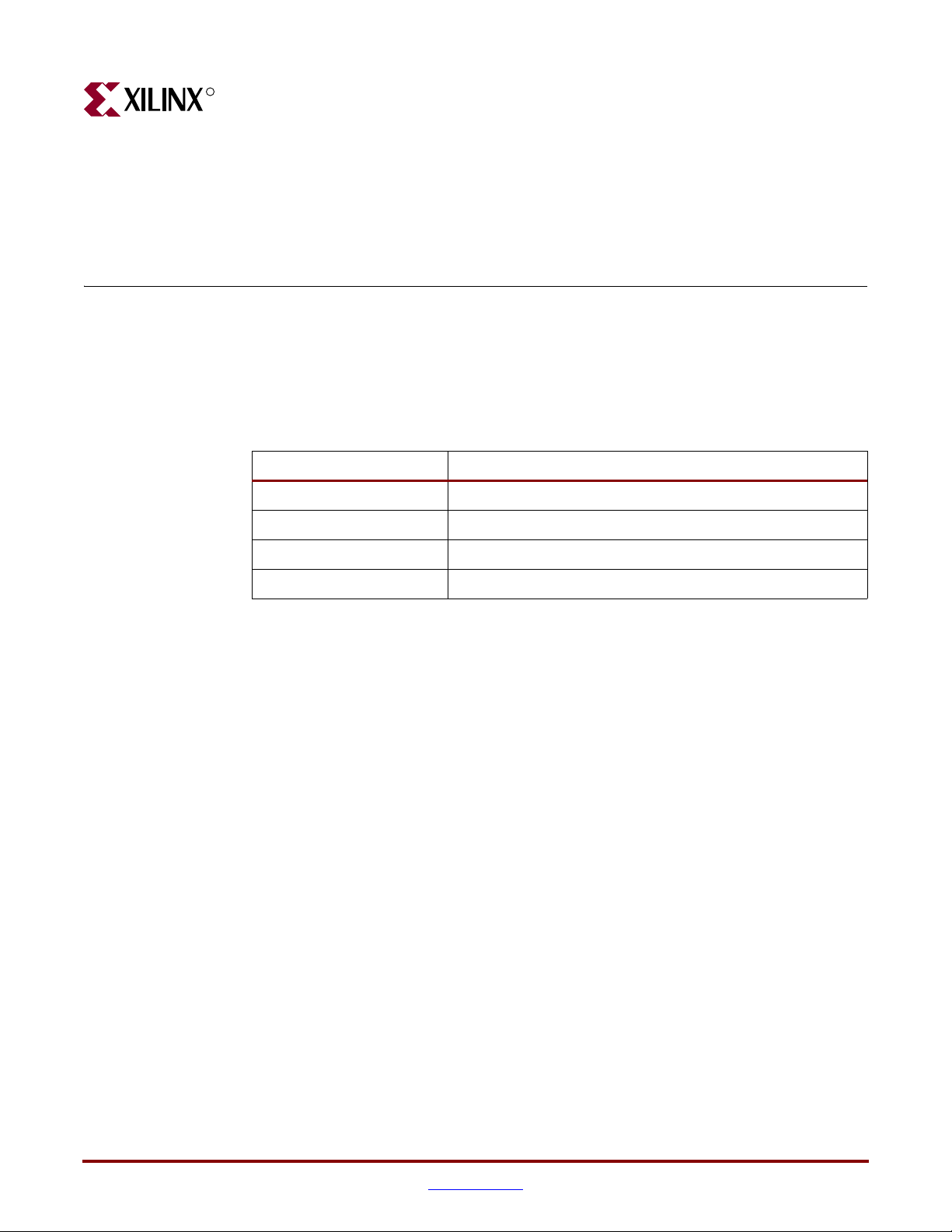

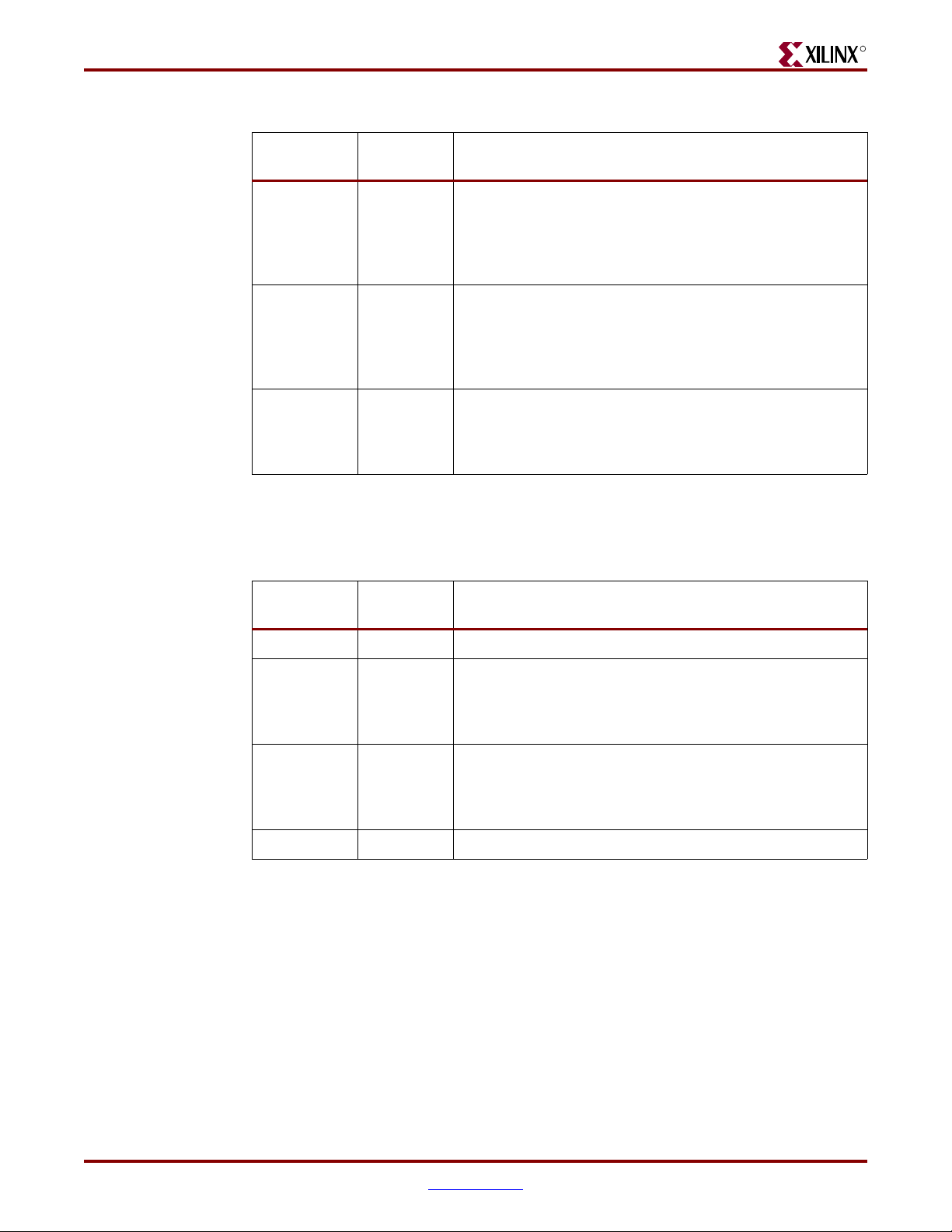

Table 3-1: XCO File Values and Default Values

Parameter XCO File Values Default GUI Setting

component_name ASCII text starting with a letter and

physical_interface One of the following keywords: gmii,

management_interface One of the following keywords: true,

address_filter One of the following keywords: true,

no_of_address_table_

entries

Output Generation

The output files generated from the CORE Generator tool are placed in the CORE

Generator project directory. The list of output files includes the following items.

• Netlist file for the core

• Supporting CORE Generator files

• Release notes and documentation

• Subdirectories containing an HDL example design

• Scripts to run the core through the back-end tools and to simulate the core using either

Mentor Graphics ModelSim, Cadence IUS or Synopsys VCS simulators.

gig_eth_mac_v8_5

based upon the following character

set: a..z, 0..9 and _

gmii

rgmii

true

false

true

false

Integer in the range 0 - 4 4

See the 1-Gigabit Ethernet MAC Getting Started Guide for more information about the CORE

Generator output files and for details on the HDL example design.

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 33

UG144 April 24, 2009

Page 34

-- DISCONTINUED PRODUCT --

R

Chapter 3: Generating the Core

34 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 35

-- DISCONTINUED PRODUCT --

R

Designing with the Core

This chapter provides general guidelines for creating designs using the GEMAC core. To

work with the example design included with the GEMAC core, see the 1-Gigabit Ethernet

MAC Getting Started Guide.

General Design Guidelines

This section describes the steps required to turn a GEMAC core into a fully functioning

design integrated with user-application logic. Not all implementations require all the

design steps described in this chapter. The following sections discuss the design steps

required for various implementations. For best results, carefully follow the logic design

guidelines.

Chapter 4

Design Steps

Generate the core from the Xilinx CORE Generator™. See Chapter 3, “Generating the

Core.”

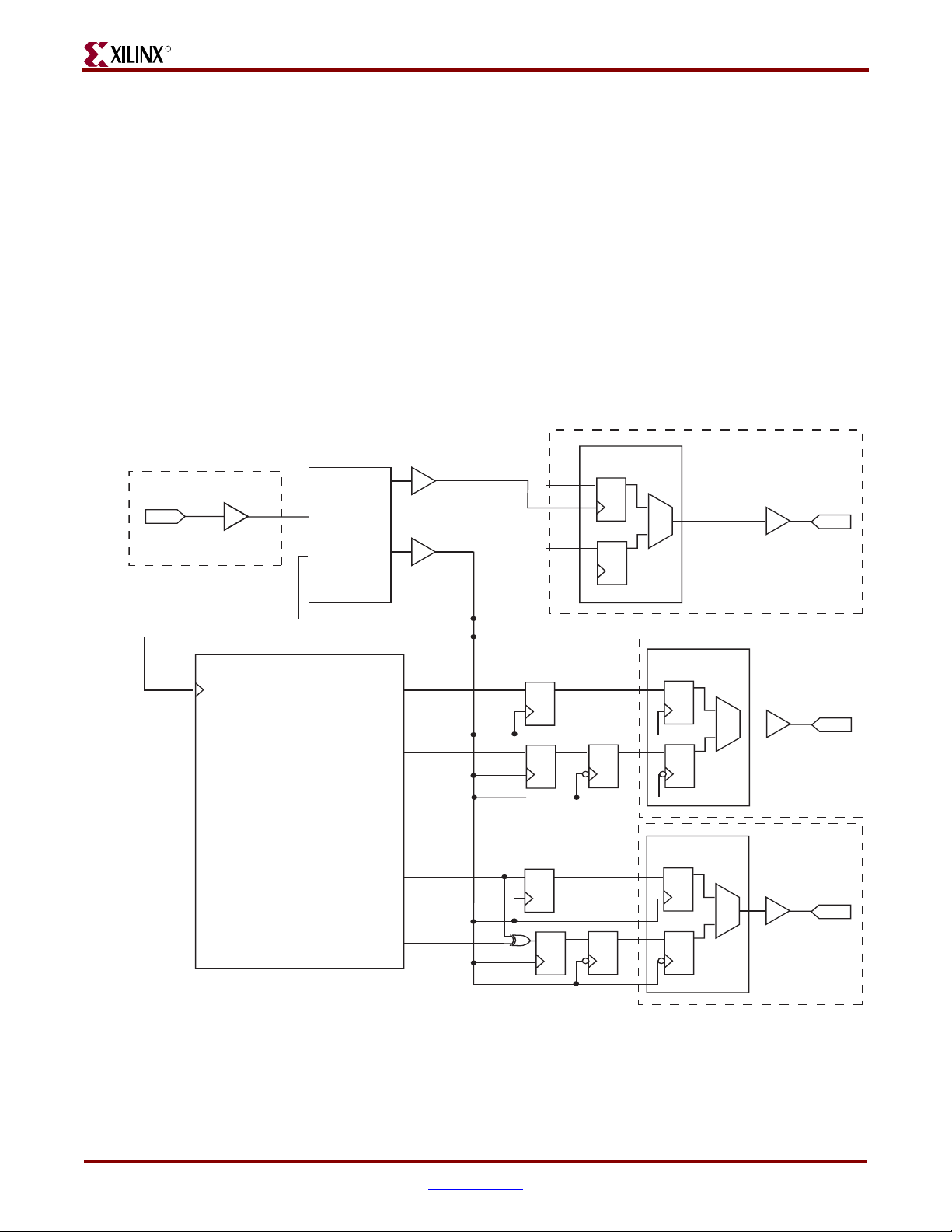

Using the Example Design as a Starting Point

The GEMAC core is delivered through the CORE Generator with an HDL example design

built around the core, allowing the functionality of the core to be demonstrated using

either a simulation package or in hardware, if placed on a suitable board. Figure 4-1 is a

block diagram of the example design. For more information about the example design, see

the 1-Gigabit Ethernet MAC Getting Started Guide.

The example design illustrates how to:

• Instantiate the core from HDL.

• Source and use the client-side interface ports of the core from application logic.

• Connect the physical-side interface of the core (GMII or RGMII) to device IOBs

• Derive the clock management logic, as described in Chapter 10, “Clocking and

creating an external interface. (See Chapter 7, “Using the Physical Side Interface.”)

Resetting.”

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 35

UG144 April 24, 2009

Page 36

-- DISCONTINUED PRODUCT --

R

Chapter 4: Designing with the Core

<component_name>_example_design

<component_name>_locallink

Clock/

Reset

Circuitry

10 Mbps, 100 Mbps

1 Gbps Ethernet FIFO

Tx Client

FIFO

Address

Swap

Module

LocalLink Interface

Rx Client

FIFO

<component_name>_block

1-Gigabit Ethernet

MAC Core

Client

Interface

Management

Interface

Statistics Vectors

Interface

Physical

Interface

GMII/ RGMII

Management

Figure 4-1: 1-Gigabit Ethernet MAC Core Example Design

Using the example design as a starting point, you can do the following:

Interface

Logic,

IOBs and

Clock

• Edit the HDL top level of the example design file to:

♦ Change the clocking scheme.

♦ Add/remove IOBs as required.

♦ Replace the client loopback logic with your specific application logic.

♦ Adapt the 10 Mbps, 100 Mbps, 1 Gbps Ethernet FIFO to suit your specific

application (see “Using the Client-Side FIFO”).

• Synthesize the entire design.

The Xilinx Synthesis Tool (XST) script and Project file in the /implement directory

may be adapted to include any HDL files you may want to add.

• Run the implement script in the /implement directory to create a top-level netlist for

the design. The script may also run the Xilinx tools map, par, and bitgen, creating a

bitstream that can be downloaded to a Xilinx device. SimPrim-based simulation

models for the entire design are also produced by the implement scripts.

• Simulate the entire design using the demonstration test bench provided as a template

in the /simulation directory.

• Download the bitstream to a target device.

36 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 37

General Design Guidelines

Implementing the 1-Gigabit Ethernet MAC in Your Application

The example design can be studied as an example of how to do the following:

• Instantiate the core from HDL.

• Source and use the client-side interface ports of the core from application logic.

• Connect the physical-side interface of the core (GMII or RGMII) to device IOBs to

• Derive the clock management logic.

After working with the example design, you can write your own HDL application, using

single or multiple instances of the GEMAC core. Client-side interfaces and operation of the

core are detailed later in this chapter. For more information, see:

• Clock Management Logic in Chapter 10, “Clocking and Resetting.”

• Using the GEMAC core in conjunction with the Ethernet 1000BASE-X PCS/PMA or

• Using the GEMAC core in conjunction with the Ethernet Statistics core in Chapter 11,

• 10 Mbps, 100 Mbps, 1 Gbps Ethernet FIFO in Appendix A, “Using the Client-Side

-- DISCONTINUED PRODUCT --

R

create an external interface.

SGMII core in Chapter 11, “Interfacing to Other Cores.”

“Interfacing to Other Cores”

FIFO.”

You can synthesize the entire design using any synthesis tool. The GEMAC core is presynthesized and is delivered as an NGC netlist (which appears as a black box to synthesis

tools).

Run the Xilinx tools map, par, and bitgen to create a bitstream that can be downloaded to

a Xilinx device. Care must be taken to constrain the design correctly, and the UCF

produced by the CORE Generator should be used as the basis for the your own UCF. See

Chapter 9, “Constraining the Core,”.

You can simulate the entire design and download the bitstream to the target device.

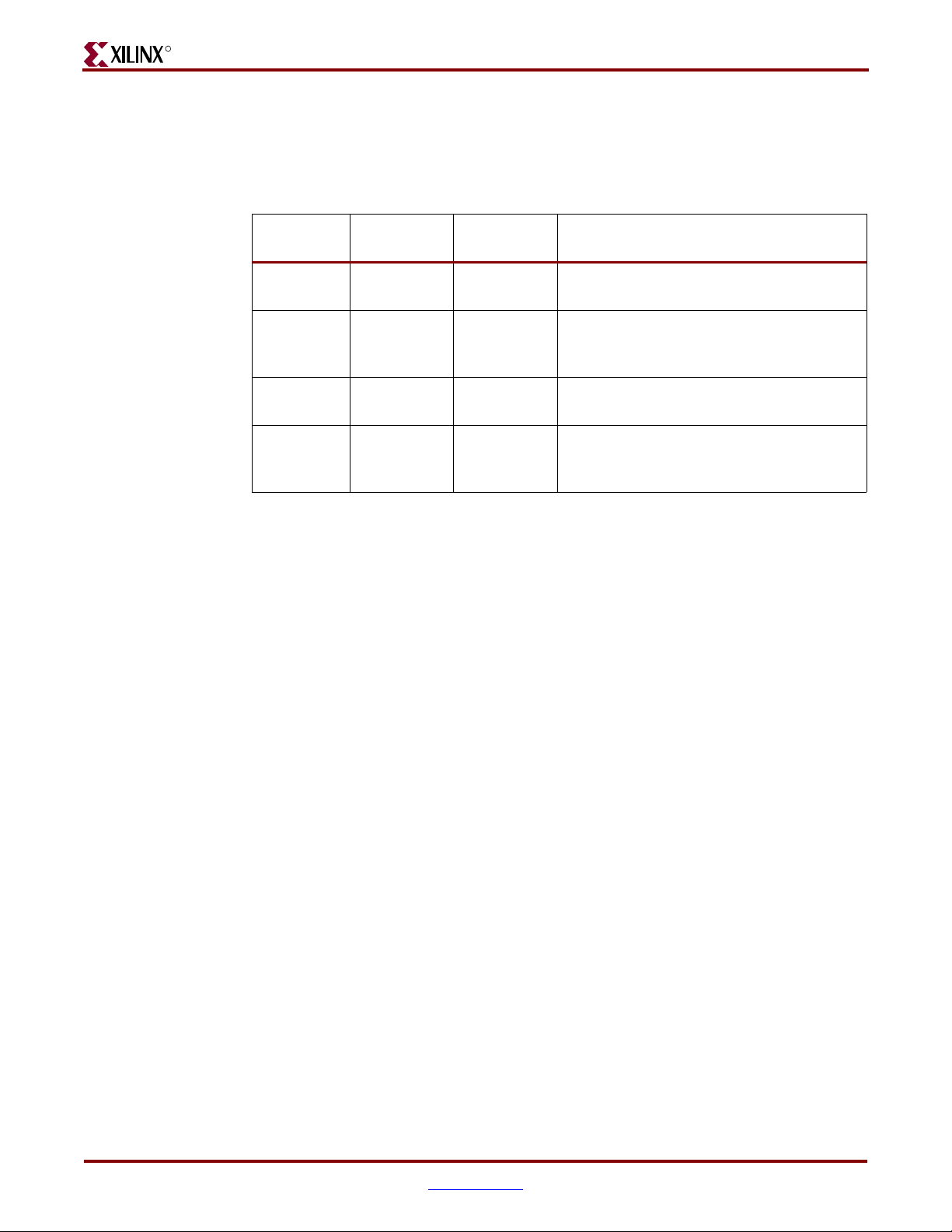

Know the Degree of Difficulty

A 1-Gigabit Ethernet MAC implementation is challenging to implement in any technology,

and all applications require careful attention to system performance requirements.

Pipelining, logic mapping, placement constraints, and logic duplication are all methods

that help boost system performance.

See Tab le 4-1 to determine the relative level of difficulty associated with the Spartan® and

Virtex® device families. These designs relate to meeting the core required system clock

frequency of 125 MHz.

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 37

UG144 April 24, 2009

Page 38

R

See also Appendix C, “Calculating DCM Phase-Shifting” to meet Spartan-3, Spartan-3E

and Spartan-3A device setup and hold requirements for external GMII.

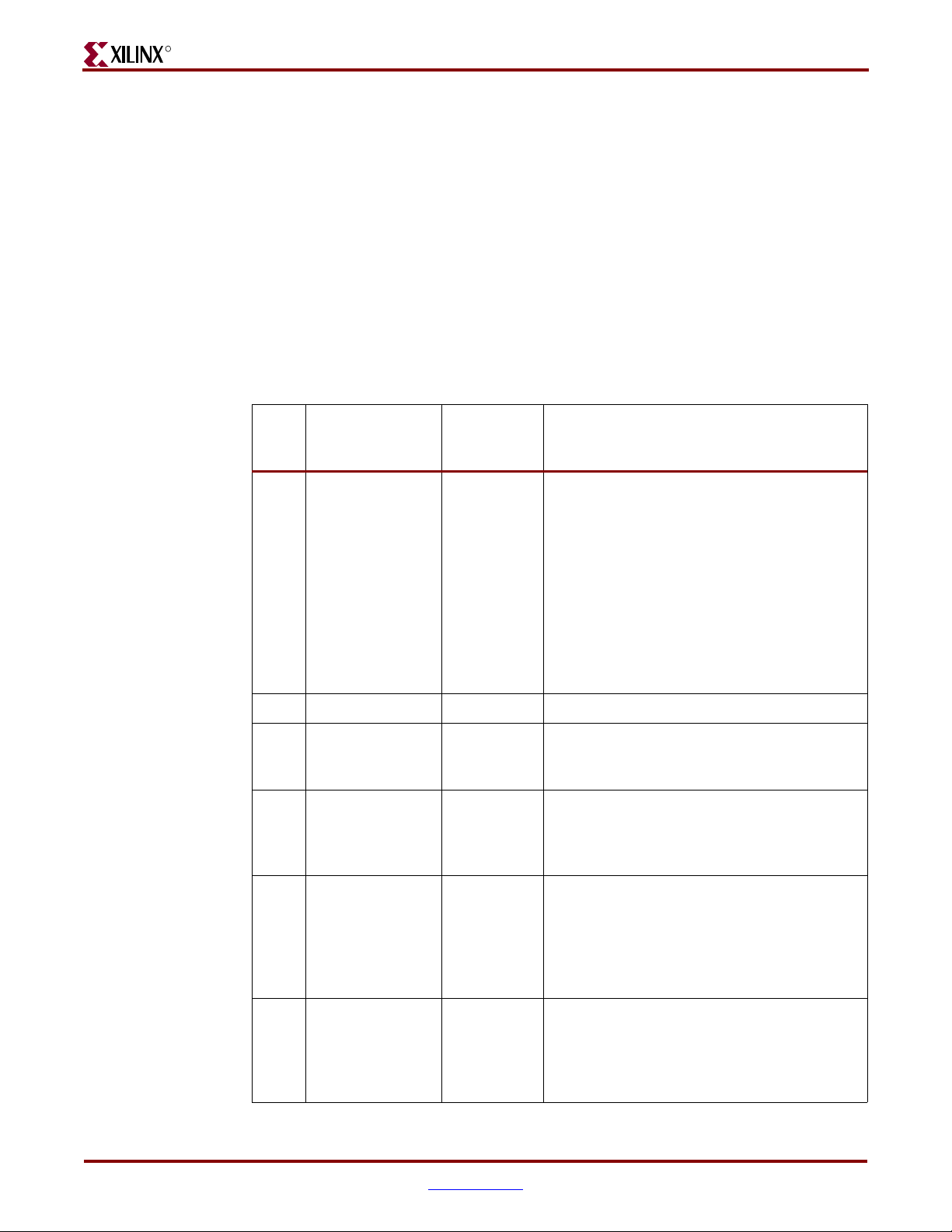

Table 4-1: Degree of Difficulty for Various Implementations

Spartan-3A/3AN/3A DSP platforms Difficult

Spartan-3E platform Difficult

Spartan-3 device Difficult

Virtex-4 device Easy

Virtex-5 device Easy

Keep it Registered

To simplify timing and increase system performance in an FPGA design, keep all inputs

and outputs registered between the user application and the core. This means that all

inputs and outputs from the user application should come from, or connect to, a flip-flop.

While registering signals may not be possible for all paths, it simplifies timing analysis and

makes it easier for the Xilinx tools to place-and-route the design.

-- DISCONTINUED PRODUCT --

Chapter 4: Designing with the Core

Device Family Difficulty

Recognize Timing Critical Signals

The UCF provided with the example design identifies the critical signals and timing

constraints that should be applied. See Chapter 9, “Constraining the Core”

Use Supported Design Flows

The core is pre-synthesized and delivered as an NGC netlist. The example implementation

scripts provided use XST 11.1 as the synthesis tool for the HDL example design. Other

synthesis tools may be used for the user application logic. The core is always unknown to

the synthesis tool and should appear as a black box. For post synthesis, only ISE® 11.1 tools

are supported.

Make Only Allowed Modifications

The GEMAC core should not be modified by you. Any modifications may have adverse

effects on system timing and protocol compliance. Supported user configurations of the

GEMAC core can only be made by selecting the options in the CORE Generator when the

core is generated. See Chapter 3, “Generating the Core.”

38 www.xilinx.com 1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Page 39

-- DISCONTINUED PRODUCT --

R

Using the Client Side Data Path

This chapter provides general guidelines for creating designs using the GEMAC core,

including a detailed description of each client-side data flow interface of the core.

Definitions of the abbreviations used throughout the remainder of this chapter are defined

in Tab le 5- 1.

Table 5-1: Abbreviations Used in Timing Diagrams

Abbreviation Definition

DA Destination address; 6 bytes

Chapter 5

SA Source address; 6 bytes

L/T Length/type field; 2 bytes

FCS Frame check sequence; 4 bytes

Receiving Inbound Frames

Received Ethernet frames are presented to the client logic on the Receiver subset of the

Client-Side Interface. For port definition, see “Receiver Interface,” on page 27.

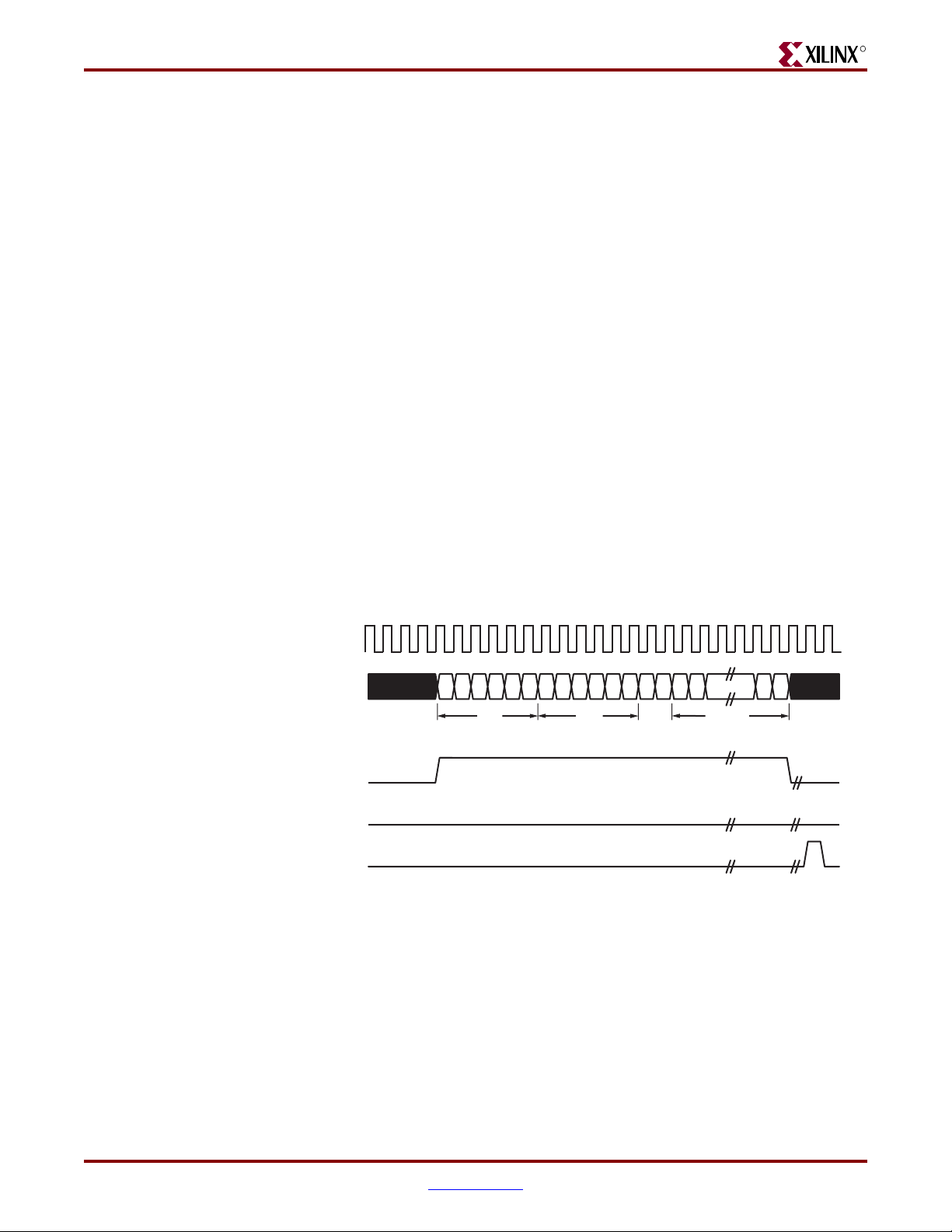

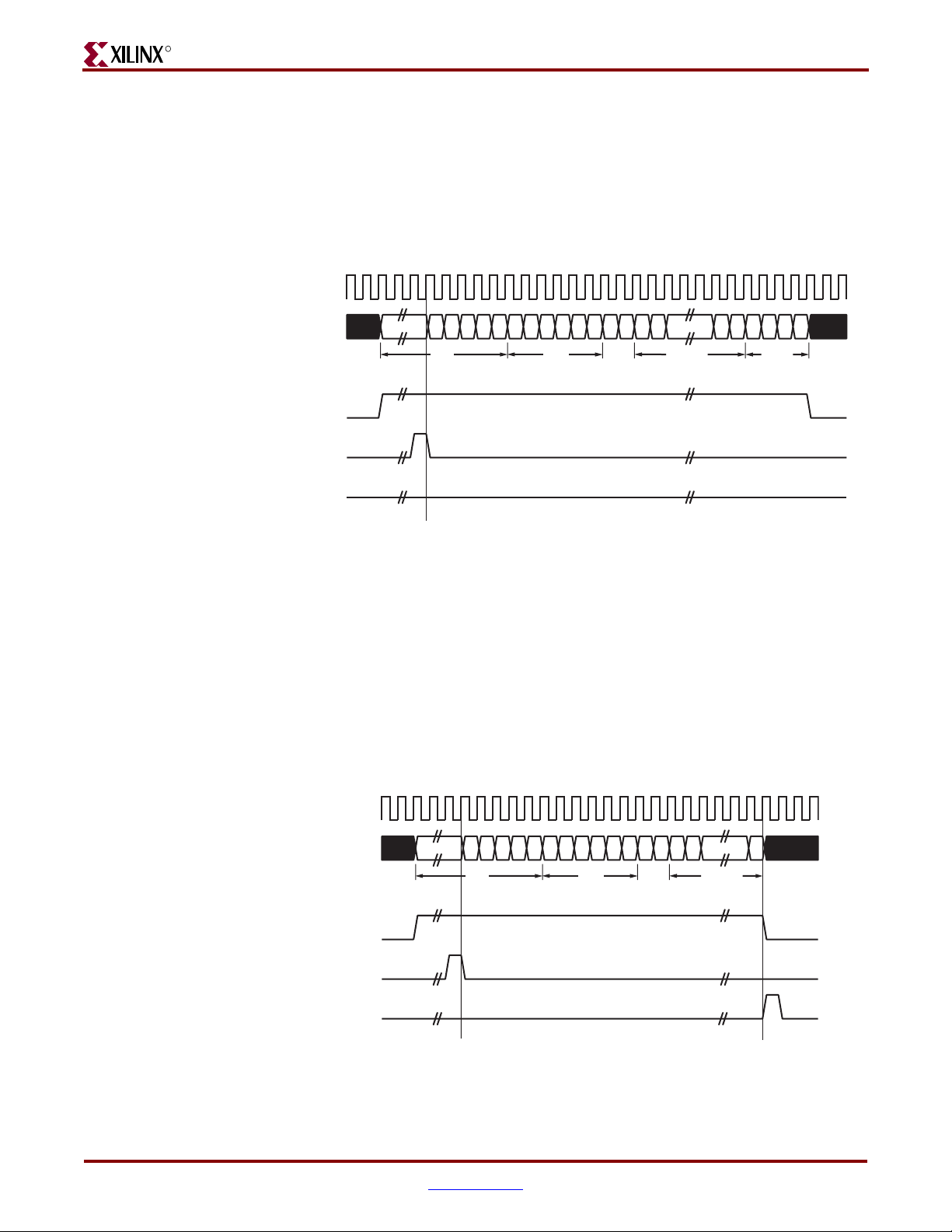

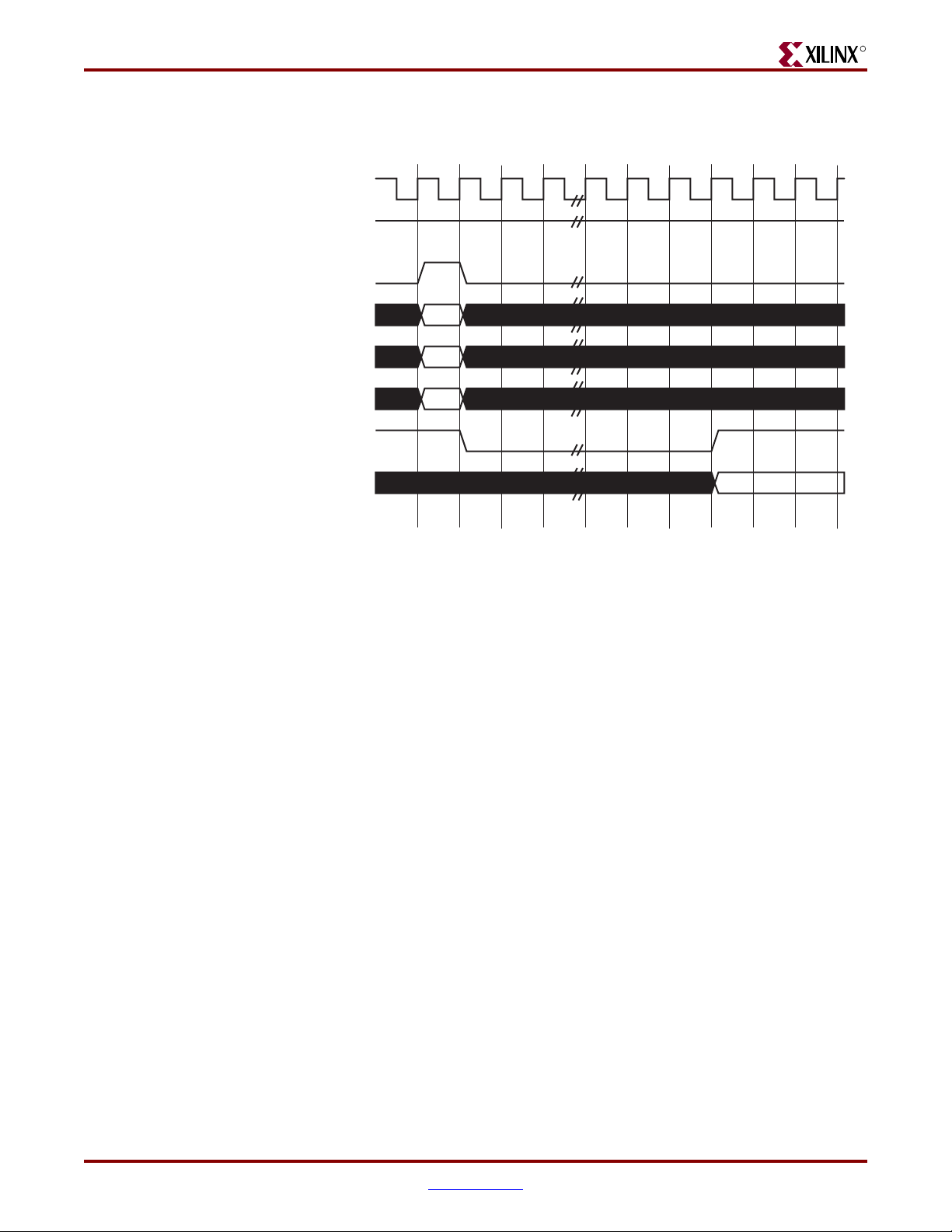

Normal Frame Reception

Figure 5-1 illustrates the timing of a normal inbound frame transfer. The client must be

prepared to accept data at any time; there is no buffering within the MAC to allow for

latency in the receive client. Once frame reception begins, data is transferred on

consecutive clock cycles to the receive client until the frame is complete. The MAC asserts

the rx_good_frame signal to indicate that the frame was successfully received and that

the frame should be analyzed by the client.

1-Gigabit Ethernet MAC v8.5 User Guide www.xilinx.com 39

UG144 April 24, 2009

Page 40

-- DISCONTINUED PRODUCT --

R

gmii_rx_clk

rx_data[7:0]

DA SA DATAL/T

rx_data_valid

rx_good_frame

rx_bad_frame

Chapter 5: Using the Client Side Data Path

Figure 5-1: Normal Frame Reception

Frame parameters (destination address, source address, length/type and optionally FCS)

are supplied on the data bus according to the timing diagram.

If the length/type field in the frame has a length interpretation, indicating that the

inbound frame has been padded to meet the Ethernet minimum frame size, the padding is

not passed to the client in the data payload. The exception to this is where FCS passing is

enabled. See “Client-Supplied FCS Passing.”

When Client-Supplied FCS passing is disabled, rx_data_valid is equal to zero between