Page 1

TEAC

FD-55AV/

GV

MINI FLEXIBLE DISK DRIVE

MAINTENANCE

MANUAL

REV.

A

Page 2

MINI

TEAC

FD-5SAV~GV

=~XI3LE

DISK

DRl~JE

H.~INTI:N;'_~G

P.Jl..NU;lL

- i -

Page 3

TABLE

OF

CONTENTS

SECTION 3

3-1

CONSTRUCTION

3-1-1

3-1-2

3-2

3-2-1

General

Mechanical

CIRCUIT

Read

3-2-1-1

3- 2-1- 2

3-2-1-3

3-2-1-4

3-2-1-5

3-2-2

Control

3-2-2-1

3-2-2-2

3-2-2-3

THEORY

OF

Block

DESCRIPTIONS

Write

Mode

selector

Re

a d c

ireuit.

Writecircui

Low

voltage

Function

Circui

Strap

LED

and

circui

head

Write/erase

Title

OPERATION

AND

FUNCTION

Diagram

Section

Circuit

(for

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

t

.....•...........................................

sensor

and

operating

t

t

load

control

read

control

circuit

write

waveform

circuit

circuit)

of

read

......•......................

write

LSI

_

terminals

..

Page

300

301

301

302

307

307

309

311

315

317

318

326

328

329

333

3-2-2-4

3-2-2-5

3-2-2-6

3-2-2-7

3-2-2-8

3-2-2-9

3-2-3

3-3

3-3-1

3-3-2

Mc>tor

Ready

Stepping

Track

Other

Interface

Servo

Circuit

FUNCTION OF

Function

Function

on

gate

detector

motor

counter

terminals

driver

TEST

of

Test

of

Variable

...........................................•.....

control

and

POINTS

circuit

function

AND VARIABLE

of

control

RESISTORS

Points

Resistors

LSI

335

336

339

343

344

346

347

3~8

349

354

-

ii

-

Page 4

Title

Page

SECTION 4

4

-1

4-1-1

4-1~2

4-1-3

4-2

4-2-1

4-2-2

4-2-3

4-2-4

4-2-4-1

4-2-4-2

4-2-4-3

4-2-4-4

4-2-4-5

4-2-4-6

MAINTENANCE

GENERAL.............

Periodic

Check

Maintenance

and

Adjustment

Maintenance

........................•.........................

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...4001

.'

Jigs

and

Tools

PRECAUTIONS...............................................

Torque

Handling

Head

Initial

Applied

Cable

Setting

Cable

connection

Setting

Setting

Level

disk

Alignment

of

Connectors

Treatment

of

of

disk

to

Screws

of

SKA-G

and

the

maximum

step

rate

calibration

calibration

Humiditysetting

and

and

setting

track

and

Locking

SKA

of

number

settling

Paint

power

time

supply

.~

•.....................

voltage

4000

4001

4002

4003

. . . . . ...4007

4007

4008

4013

4015

4015

4018

4018

4021

4023

4026

4

-2 -4

4-2-4-8

4-2-5

4-3

4-3-1

4-3-2

4-4

4-4-1

4-4-2

4-4-3

4-4-3-1

4-4-3-2

4-4

-4

4-4-5

4-4-6

4-4-7

- 7

Setting

Setting

Others

PREVENTIVE

Cleaning

Direct

CHECK

AND

Adjustment

Check

Check

and

and

[)()uble

Single

Check

of

Check

Check

of

Check

0 f

SKA

of

FDD

MAINTENANCE

of

Magnetic

Cleaning

ADJUSTMENT

of

Adjustment

Adjustment

sided

sided

CSS

Ass'

of

File

Disk

of

Erase

gain

Set

straps

<Single

Arm

and

Head

sided}

Position

of

Holder

of

Arm

SKA

by

Lifter

special

Cleaning

Position

key

Disk

....•....................

Y -.f054

Protect

Rotation

Gate

Sensor

Delay

............•.......................

Speed

4026

4027

4029

4032

4032

4034

4036

4036

4038

4041

4041

4051

4058

4061

4063

4-4-8

Check

of

Head

Touch

4066

-

iii

-

Page 5

Title

Page

4-4-9

4-4-10

4-4-11

4-4-12

4-4-13

4-4-14

4-4-15

4-5

4-5-1

4-5-1-1

4-5-1-2

4-5-2

4-5-3

4-5-4

4-5-5

4-5-6

Check

MAINTENANCE

Replacement

Replacement

Replacement

Replacement

Replacement

Replacement

and

Check

Check

Check

Check

Check

Check

of

of

and

and

and

and

Replacement

Replacement

Adjustment

Read

Level

Resolution

Adjustment

Adjustment

Adjustment

Adjustment

PARTS

REPLACEMENT

of

Head

of

of

of

Stepping

of

DD

of

Collet

of

Head

of

Track

Carriage

v-type

L-type

motor

Load

of

Asymmetry

of

of

of

of

carriage

carriage

MQtor

Ass'y

Ass'y

00

Sensor

Track

Track

Track

Index

Ass'y

Solenoid

Alignment

00

Sensor

00

Stopper

Burst

Ass

<Spindle

Ass'y

Timing

........................•.....

'y

motor},

........•......................

.........................

........................

.......................

.....................

4072

4077

4080

4084

4093

4100

4105

4110

4110

4110

4117

4121

4124

4126

4127

4129

4-5-7

4-5-8

4-5-9

4-5-10

4-5-11

4-5-12

Replacement

Replacement

Replacement

Replacement

Replacement

Replacement

of

of

of

of

of

of

PCBA

PCBA

Front

Front

CSS

Head

MFD

Front

Bezel

Lever

Ass'y

Pad

Control

OPT

Ass'y

(Single

#H

Ass'y

#H

sided)

.........•................

4130

4132

4133

4134

4135

4136

-

iv

-

Page 6

SECTION 3

THEORY

OF

OPERATION

-

300

-

Page 7

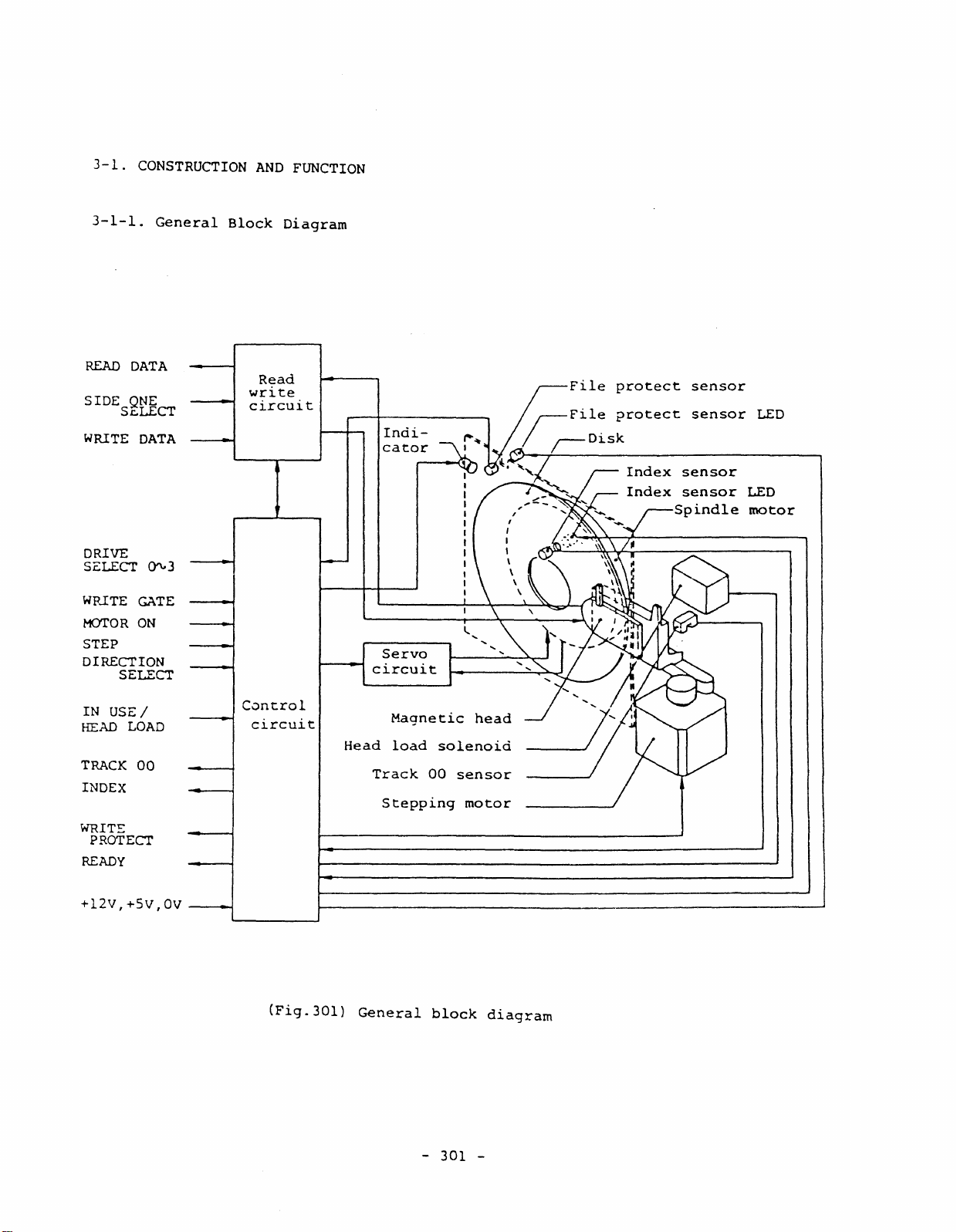

3-1.

CONSTRUCTION

AND

FUNCTION

3-1-1.

READ

DATA

SIDE

QNE

SeLECT

WRITE

DATA

DRIVE

Sc.:LECT

WRITE

MOTOR

STEP

()'\..3

GATE

ON

DIRECTION

SELECT

General

Block

write

circuit

Read

Diagram

Indi-

cator

Servo

circuit

File

protect

Index

Index

sensor

sensor

sensor

sensor

Spindle

LED

LED

motor

IN

USc.:

HEAD

TRACK

/

LOAD

00

INDEX

WRITE

PROTECT

READY

+12V,+SV,OV

Cunt.rol

circuit

(Fig.30l)

Head

General

Magnetic

load

Track

Stepping

solenoid

00

sensor

block

head

motor

diagram

-

301

-

Page 8

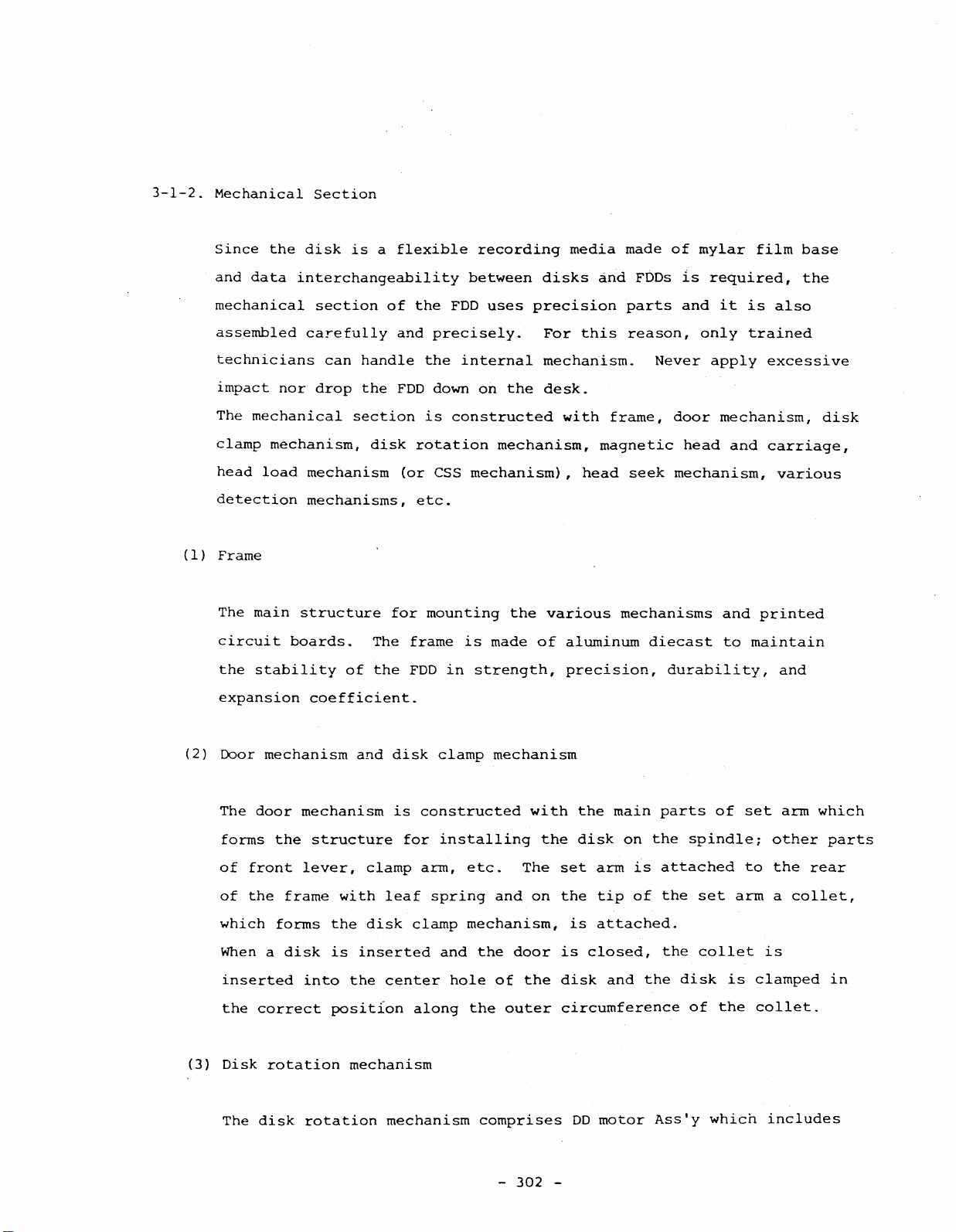

3-1-2.

Mechanical

Section

(1)

Since

and

the

data

mechanical

assembled

technicians

impact

The

mechanical

clamp

head

mechanism,

load

detection

Frame

The

main

circuit

the

stability

expansion

disk

is

interchangeability

section

carefully

can

handle

nor

drop

the

section

mechanism

mechanisms,

structure

boards.

of

coefficient.

a

disk

The

the

flexible

of

the

and

FDD

rotation

(or

etc.

for

frame

FDD

between

FDD

precisely.

the

internal

down

is

constructed

CSS

mechanism),

mounting

is

in

recording

uses

on

the

mechanism,

the

made

strength,

media

disks

precision

For

this

mechanism.

desk.

with

head

various

of

aluminum

precision,

made

and

FDDs

parts

reason,

frame,

magnetic

seek

mechanisms

of

is

and

Never

door

head

mechanism,

diecast

durability,

mylar

required,

it

only

apply

mechanism,

and

and

to

film

is

also

trained

excessive

carriage,

various

printed

maintain

and

base

the

disk

(2)

(3)

Door

The

door

forms

of

front

of

the

which

When a

inserted

the

Disk

The

mechanism

mechanism

the

structure

lever,

frame

forms

disk

into

correct

rotation

disk

rotation

and

clamp

with

the

disk

is

inserted

the

position

mechanism

disk

clamp

is

constructed

for

installing

arm,

leaf

spring

clamp

and

center

along

mechanism

mechanism

etc.

and

mechanism,

the

hole

of

the

comprises

outer

-

with

The

door

the

302

the

the

disk

set

on

the

is

is

disk

circumference

DO

-

main

on

arm

tip

attached.

closed,

and

motor

is

of

the

parts

the

attached

the

the

disk

Ass'y

of

spindle;

set

collet

is

of

the

which

set

arm

which

other

to

the

rear

armacollet,

is

clamped

collet.

includes

parts

in

Page 9

spindle.

The

DO

long

The

rotation

and

is

motor

life

maintained

of

is

an

30,000

speed

outor-rotor

hours

is

300rpm

at

a

stable

or

type

more

for

A

condition

DC

in

continuous

~

F

brushless

models

against

rotation.

or

load

motor

360rpm

which

for

variations

has

G

the

model

and

environmental

internal

The

center

and

position.

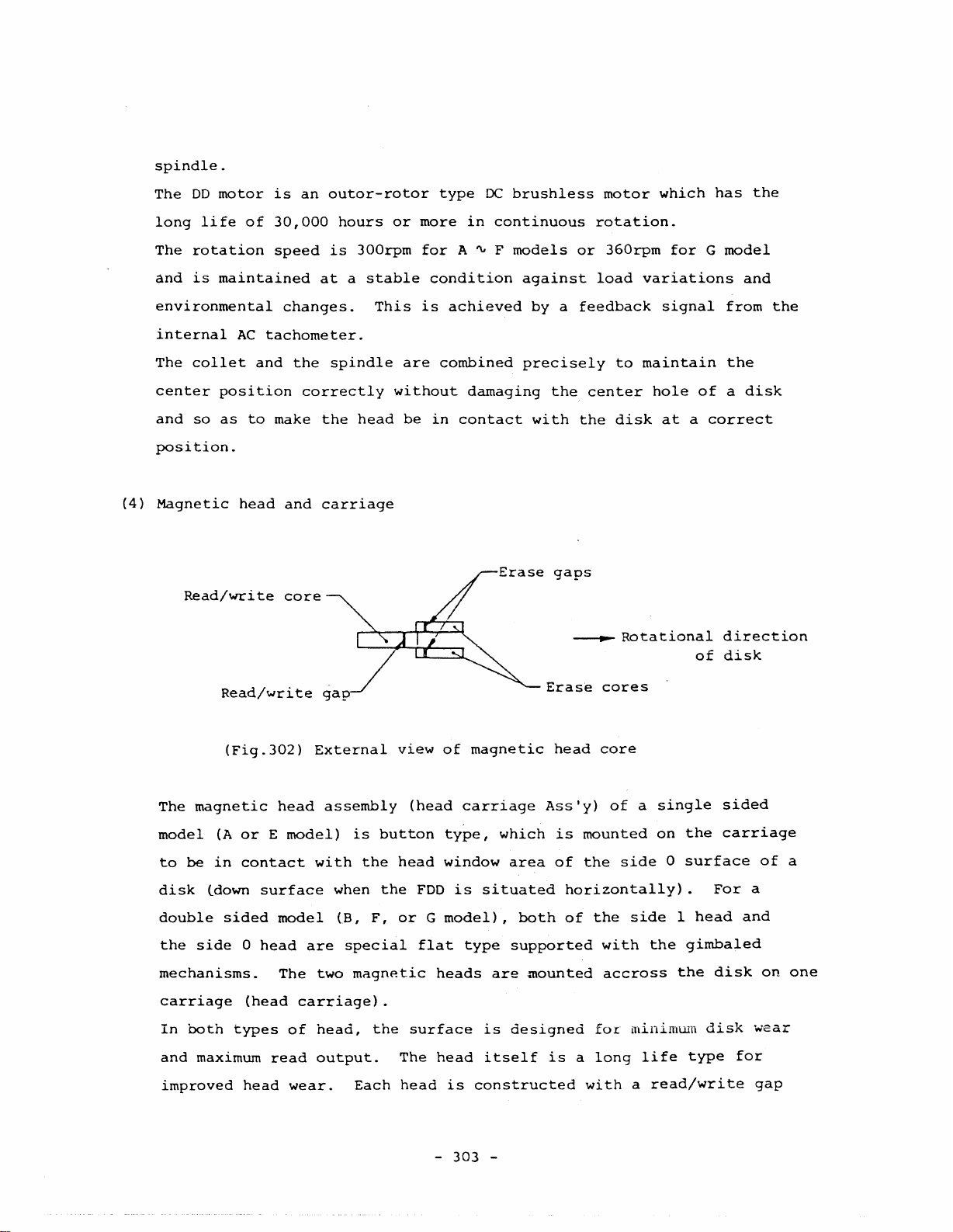

(4)

Magnetic

collet

position

so

as

Read/wri

(Fig.302)

AC

tachometer.

and

to

head

te

changes.

the

correctly

make

and

core

spindle

the

head

carriage

External

This

is

are

without

be

in

view

achieved

combined

damaging

contact

of

magnetic

by

a

precisely

the

with

gaps

Erase

head

feedback

center

the

___

cores

core

to

disk

Rota

signal

maintain

hole

at

tional

of

a

of

from

the

a

correct

direction

disk

the

disk

The

magnetic

model

to

disk

double

the

be

(A

in

(down

sided

side

mechanisms.

carriage

In

both

and

maximum

improved

or

contact

surface

0

head

(head

types

head

head

E

model)

model

The

of

read

wear.

assembly

with

when

(B,

are

special

two

carriage).

head,

output.

is

button

the

head

the

F,

or

magnp.tic

the

The

Each

head

(head

type,

window

FDD

G

model),

flat

heads

surface

head

-

carriage

is

type

is

constructed

303

which

area

situated

both

supported

are

is

designed

itself

-

Ass'y)

is

of

horizontally).

of

mounted

is

of

mounted

the

the

with

accross

for

a

long

with

a

single

on

side

side

the

iltinimWii

life

a

read/write

the

0

surface

1

head

gimbaled

the

type

sided

carriage

For

disk

disk

for

a

and

wear

of

on

gap

a

one

Page 10

used

for

data

reading

and

data

writing

and

two

erase

gaps

to

erase

the

(5)

recorded

The

magnetic

and

is

Head

The

head

the

CSS

solenoid.

The

head

disk

This

If

the

attached

the

side

track

specially

load

mechanism

load

mechanism

load

when

only

mechanism

head

to

1

surface

edge

ehad

assembled

mechanism

mechanism

required

is

loading

the

pad

immediately

and

the

or

CSS

is

is

used

functions

so

constructed

is

executed

arm

of

of

a

disk.

carriage

with

mechanism

used

for

double

as

to

with

the

carriage

after

high

for

reduce

for

form

precision.

models

sided

to

make

head

a

the

the

disk

load

single

is

recordinCJ

core

with

head

CSS

model

the

head

and

solenoid,

sided

depressed

(tunnel

section

load

without

in

magnetic

model,

lightly

of

contact

arm

erase).

the

solenoid

head

with

head

lifter,

the

head

against

FDD

and

load

a

wear.

etc.

pad

For

a

double

the

carriage

appropriate

The

side

and

the

between

In

the

disk

as

and

head

necessary.

The

CSS

to

protect

front

head

lever

being

insertion

pressure.

0

surfaces

depression

the

heads

CSS

model,

far

as

leves,

mechanism

the

is

caught

and

sided

is

depressed

the

it

contact

closed

ejection,

model,

of

of

and

the

disk

is

is

constructed

and

the

against

the

head

the

side

the

disk.

magnetic

is

installed.

required

of

side

without

damaged

head

side

the

and

1

head

heads

to

make

with

0

and

disk.

by

the

protector

1

the

head

side

disk

produces

are

In

the

a CSS

side

For

head

is

attached

1

surface

are

always

order

disk

ASs'y

1

heads

the

window

also

set

the

in

to

rotate

purpose

edge

equipped

to

the

of

to

stable

contact

elongate

which

directly

os

during

upper

a

disk

the

contact

with

only

is

designed

when

protecting

to

the

same

the

when

disk

arm

with

a

disk

the

CSS

of

an

height

it

the

is

mechanism

to

lift

up

the

disk

jacket.

-

304

The

head

-

protector

is

also

used

Page 11

(6)

in

Head

The

models

seek

head

with

mechanism

seek

mechanism

head

load

solenoid.

consists

mainly

of

stepping

motor

with

a

capstan

(pooly),

connected

and

is

The

stepping

(1.8°)

the

stepping

type

4-phase

seek

operation

motor

the

heat

The

parallelism

line

of

Also

the

taken

mutually

slided

in

is

a

into

steel

driven

radiation

thermal

offset

belt

to

the

capstan

along

motor

96tpi

models

motor

stepping

and

in

and

disk,

and

expansion

consideration

with

(band),

the

guide

rotates

for

rotates

motor

precision

a

unique

and

to

the

distance

shafts

the

and

of

the

shafts.

2

steps

one

3.60for

is

of

manner

obtain

and

of

the

in

the

expansion

guide

stepping

(3.6°)

track

adopted

the

which

a

highly

between

capstan

frame,

process

of

shafts.

space.

one

head

the

motor

in

48tpi

In

steps.

to

improve

positioning.

brought

precise

the

shafts

themselves

steel

of

design

disk.

The

head

through

models

some

For

speed

a

positioning.

are

belt,

so

the

48tpi

all

This

success

and

precisely

carriage,

that

carriage

steel

and

models,

models,

of

the

special

in

the

center

they

is

belt

I

step

hybrid

head

reducing

machined.

etc.

are

are

(7)

Detection

(a)

File

This

detect

When a

for

to

disk

The

on

mechanisms

protect

mechanism

the

disk

detection

the

read/write

is

protected

LED

the

PCBA

is

detection

is

existence

with

is

mounted

front

mechanism

constructed

of

the

notch

disturbed,

and

erase

from

on

the

OPT

#H.

the

an

with

write

covered

no

write

heads

erroneous

PCBA

DD

-

305

an

enable

is

or

and

input

motor

-

LED

andaphoto-transistor

notch

installed

erase

the

servo

of

current

recorded

of

a

and

and

write

the

disk

the

light

will

information

command.

the

photo-transistor

jacket.

pass

be

supplied

on

to

the

Page 12

(b)

Track

This

00

detection

mechanism

mechanism

is

constructed

with

a

photo-interrupter

for

detecting

the'outermost

00

stopper

Inside

tracks

erroneous

command

If

impact

stopper

at

item

the

a

will

head

during

to

next

5-2-1

stopper.

screwed

When

moves

the

small

step-in

toward

head

track

which

from

step

be

moves

transportation),

protect

power

and

And

if

parts

commands

inward

window

are

out

ignored

on.

Table

L-type

edge

position

attached

the

command

out

from

the

If

505),

functions

are

with

of

track

by

head

V-type

carriage

input

an

the

(track

to

00

on

is

input

the

internal

the

track

the

from

carriage

the

frame

as

frOIn

appropriate

disk.

00)

the

the

from

head

moving

(refer

a

track

In

rear

00

edge

the

order

of

side

disk

the

circuit

by

carriage

out

is

to

00

innermost

space

the

head

of

are

track

some

of

the

used

functions

Table

stopper.

left

to

recalibrate

the

used.

00

of

the

reason

strikes

(refer

504)

and

with

head

Even

position,

FDD.

(such

returnable

to

like

is

track,

against

carriage.

if

the

Note

a

track

used,

the

the

a

track

an

as

track

range

head

the

12

a

track

00

of

00

(c)

from

required

to

the

Index

LED

and

at

the

The

LED

motor)

hole

this

position

to

input

maximum

detection

photo-transistor

index

is

mounted

and

the

will

be

(returning

the

track

number.

mechanism

window

area

on

photo-transistor

detected

step-out

for

of

the

PCBA

along

operation

commands

detecting

the

disk

DD

on

the

rotation

motor

the

to

with

the

jacket.

servo

PCBA

of

the

several

index

front

the

track

(in

hole

the

OPT

disk.

00),

it

additional

are

located

rotor

#H.

of

The

is

steps

spindle

index

-

306

-

Page 13

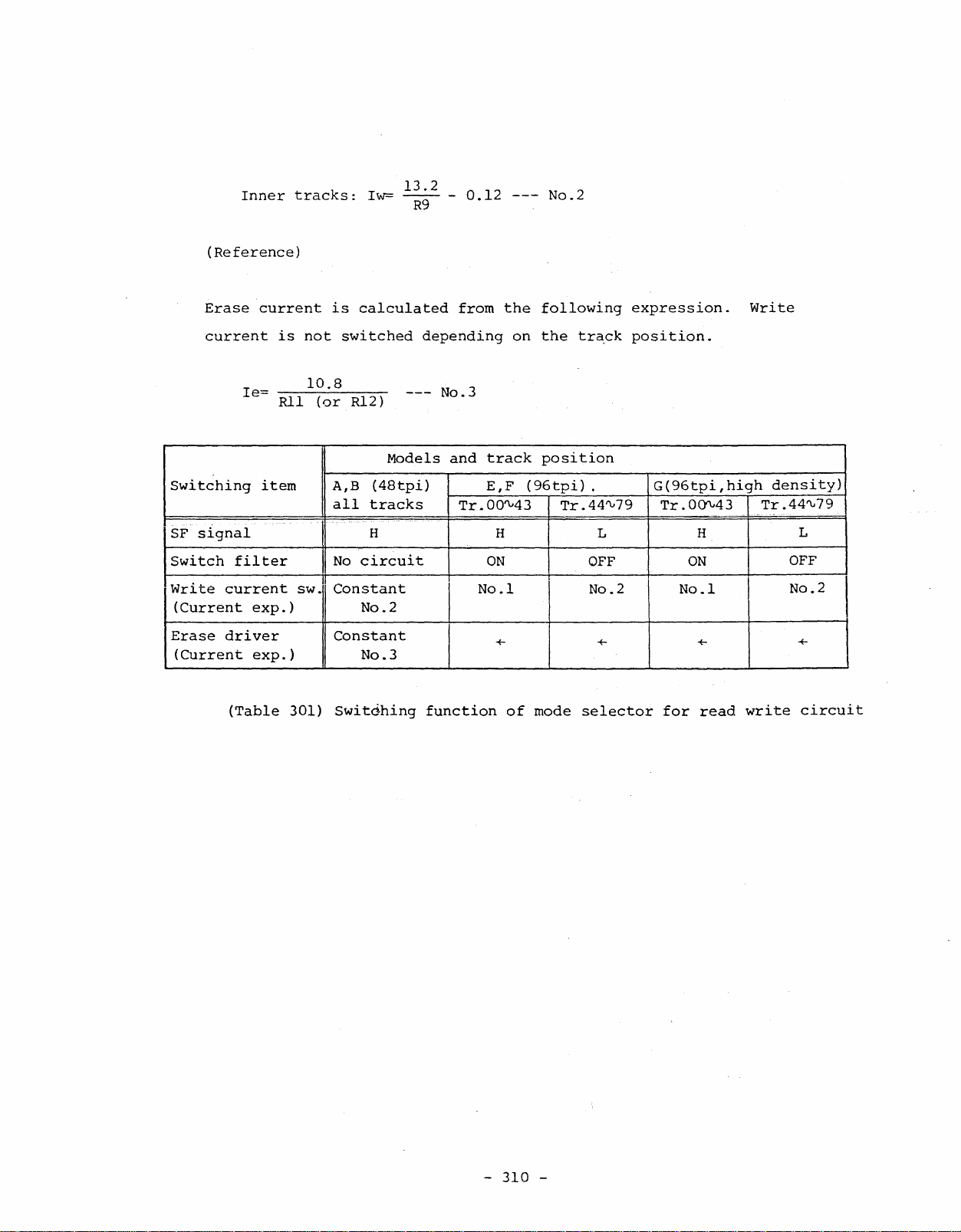

3-2.

CIRCUIT DESCRIPTIONS

The

electronics

read

write

circuit,

of

the

control

FDD

is

constructed

circuit,

and

with

servo

three

circuit.

sections

Read

which

write

are

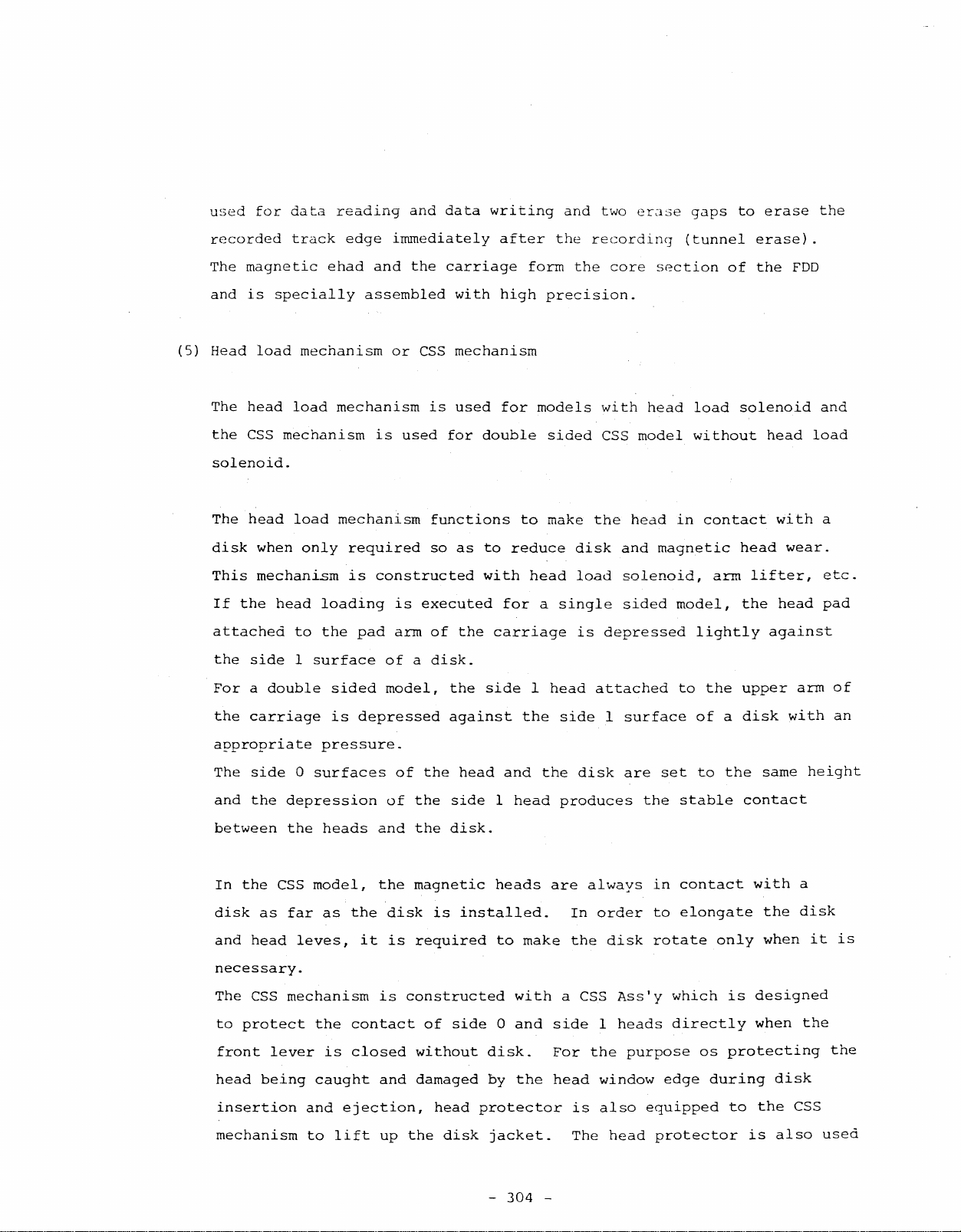

3-2-1.

circuit

servo

Read

The

write

write

Fig.303

and

circuit

write

read

circuit,

LSI

control

Circuit

write

(bipolar

shows

is

on

circuit

low

the

circuit

the

voltage

LSI,

block

PCBA

is

U5).

diagram.

are

mounted

DD

motor

constructed

sensor.

on

servo.

with

They

the

are

PCBA

mode

mostly

MFD

selector,

packed

control

read

in

#H,

circuit,

a

read

and

-

307

-

Page 14

w

a

CD

LOW

(Fig.303)

SIOEO

HEAD

~

'r----v--

t

'---.-'-----~

~---4~~

~~

--...r-

~

SI

ol-E

1----~:r-t---+-.--H--~:::=.!.--I~.19

HEAD

Block

read

RE

ADWRI H

ERASE

COMMON(CENTER

1,/9-12

2

~-I"'n-=--_

_ 8 L.::.:::.

,...

10 R"'11 r-:-=-

.....

J-=-..:;..--4---.

,..

9

"'lr

Crl3

..;

diagram

write

r.nll

COIL

r--

of

circuit

lAP)

R'iOO

__

-:.R~W...:..1..:..0

R"'01 -IT!f---+ MATRIX V

1r----~...:..:..-..l{I[

oY~~

HJ,.

.....~

~"

~--++---=C~OM~O~r--'

L

R12

_+----'\NvA\r-if-+-_~E:..!:::D~1

WT

'liT

COM

EVCC

GA

JN SELEClOR I

S4/55

I

'-----.·r-Cll---

~

rw

~;J

~

_

--fIool..ff3f---+

r-:-=- r

-L1l.

18

l..!.£..

1 r;-;::::-

~

ill

--1m

~

[It

HER

HE

AO

SW

ITCH

COMI.ION

DR

I Veil r J I

I 1

t,

ASE

DRJVEIl

....C)-----cn-J

~

~.~ ~ ~

r10l

nh

~

f--tl.

f--tl.

'---

I

WR

leu

SOURCE

TP4

A5V'"

A

/..).

'8~ '7~

PRE.

AMP

I

WRJTE

DRIVER

llE

R

RENT

PASS Fl:LTER

L4. L5. RA1L C1B.C29

I

TPS

...

C17

C20

:;

>0

:;

."

."

'6~

,h

I

~CT

0 JFFERE

=:E.

l~

/I

'iR J

TE

LOW

LV

'.

DV

EVCC

GG

t , t t t IfR0

~~4U~D6@~~~~;D~~@~~~~~

Rl1

---J.\IV'I..--+-t-

....

'--------.t

~\1SY),lMETRY

ft

~

ADJUSTOR

OV~EGND

1,/1-22

I

I

WRI1E

Re.

6

WRITE

DATA

...,

0

-.l

o

R9.Q1

-:

n n

VI

~

CURRENT

5WJTCH

~,

« n «

tn

I 0 I

VI

0

WG

_..--J

EG-....

....

I:;)

-------'

SWITCH

C30.C31.07.

I

OJ.FFERENTIATOR

R~2.

C32.

0 0 0

:;; :;; :;;

~.~ r9~

L3.

·0

"?1

'2~

J,

~

I

VE

NH

AT

OR

.'

VOLTAGE

sol

I ITIME

I

CONlR

lOG IC

c:

,..,

C)

~

SENSOR

LV

S1 tiil

~

I'-J"r

I

0L : 1

TPc I' IDRI

"'1"32

0_

SIDE

SELECT

r-

~l.J)

,-,

I-"

< LJ

III

I'

I

OUTPUT

I

1,/1

6

ONE

READ

DATA

FILTER 1

oa.

U1

I~-l-RA-C-K---SW---IT-C-H-.-SF-----------

I

C35

r0lLol

JL.:.F~

0

rn-~~.C

~E

ETECTOR

DOMAIN

I F I L

TER

~£r

DR

:llCI

----

VER

~-----

-30

~

~

'I-

~

AK

/ ..:uo....J

t'acP

~

~

~

~

tEJ

~

~

~14-=-:;;"'--+-

~

JVER

ill

DRIVE

SELECT

-..

:h

C25

~TPe

DIFO

......

I--...J

CJ

......

:....:...._--S-y-6---4Ib-

A

DVGG

lDeR

RDCR

DGND

LVGG

CD

OINV

os

.....

r---r----'--,.-I-..-'-...---..---,

:»-

'0

G>

=

lJ'J

:x

»

"

."

V)

G>

=

:x

qp

I r

......

.-

0

0

"'0

,..,

'<

z :x

"-

:10

0

-<

0

0

:=

"'0

,..,

Cj)

:x

z

"-

:10

0

-<

0

.....-

I

I

1

T

C24

-:

l'ME

C21. C22.

"tJ

::

n 0

CD

G>

,..

,

,.,.,

."

:=

n

(j')

CD

:x

."

.....

I

»

-0

V)

TRACK

SWI

TP7

---.

CONSTAllT

RAg

'0

0

c::

-l

"'0

c::

-l

n

0

z:

-l

:lC

0

,...

J

TCU

Page 15

3-2-1-1.

Mode

Mode

selector

selector

is

constructed

with

the

switch

filter

and

write

current

(1)

switch,

Table

the

301

track

control

Switch

Switch

eliminating

outer

tracks.

transistors,

level.

increase

is

the

low

pass

which

shows

switch

circuit.

filter

filter

Then

the

On-state

filter

are

is

the

When

Q7

the

capacity

used

the

switching

signal

used

influence

the

and

Q8

switch

of

the

is

set

only

(SF

only

SF

(includes

filter

of

the

switch

to

in

of

signal

low.

for

condition

signal

G

saddle

capacitors,

low

filter,

96tpi

in

model

is

resistors

pass

models.

of

the

and

waveform

HIGH

filter

and

the

read

write

schematic

in

optional

(refer

level,

diagram)

to

the

int~rnally)

C30

and

C3l

capacitor,

the

cut-off

F

model

Fig.304)

output

becomes

are

C29.

frequency

circuit

from

for

at

of

the

LOW

activated

This

of

by

the

the

NPN

to

state

the

(2)

Write

Write

making

than

(write

of

IF)

Write

in

the

can

be

resistors

Outer

current

current

the

in

inner

2F

and

current

read

calculated

write

after

sholder

write

R9,

tracks:

switch

switch

current

tracks

IF

is

supplied

R8,

LSI,

from

and

Iw=

is

used

in

outer

(track

write

44

and

characteristics.

to

US.

The

the

following

Ql

(ON

13.2

~

+

only

to

measure

the

write

supplied

at

outer

12.7

~

in

E,

tracks

track

the

expression

-

O.

F,

(track

79)

residual

driver

value

tracks)

12

---

and

to

G

00

improve

by

from

combining

.

1

No.

models

to

frequency

write

this

and

track

the

current

used

43)

over-write

components

current

the

for

higher

source

source

external

-

309

-

Page 16

Inner

(Reference)

tracks:

Iw=

13.2

---R9

-

0.12

---

No.2

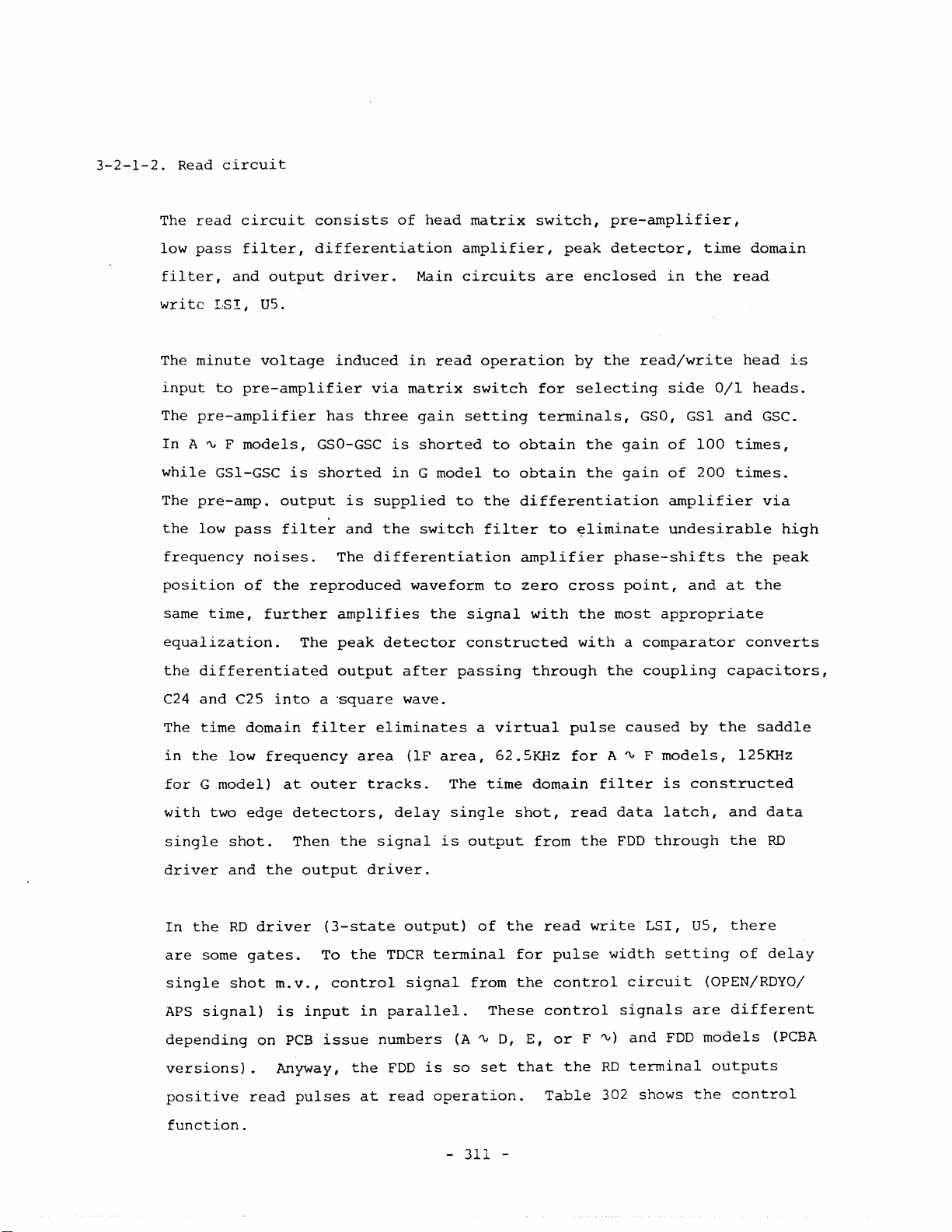

Erase

current

Switching

SF

signal

Switch

Write

current

(Current

Erase

driver

(Current

(Table

Ie=

filter

exp.)

exp.)

current

is

Rll

item

......

.

sw.

301)

not

10.8

(or

is

I

calculated

switched

R12)

---

Models

(48tpi)

A,B

all

tracks

.....

H H L H

No

circuit

Constant

from

depending

No.3

and

Tr.00'V43

No.1

the

track

E,F

ON

on

(96tpi)

following

the

tr~ck

position

.

Tr.44'V79

OFF

No.2

No.2

Constant

+

+

No.3

Switdhing

function

of

mode

selector

expression.

position.

G(96tpi,high

Tr.0Q'V43

ON

No.1

+

for

read

Write

density)

Tr.44'\.,79

OFF

write

L

No.2

+

circuit

-

310

-

Page 17

3-2-1-2.

The

low

Read

read

pass

circuit

circuit

filter,

consists

of

differentiation

head

matrix

amplifier,

switch,

peak

pre-amplifier,

detector,

time

domain

filter,

write

The

input

The

In

while

The

the

LSI,

minute

to

pre-amplifier

A~F

GSl-GSC

pre-amp.

low

frequency

position

same

time,

equalization.

the

differentiated

C24

and

The

time

and

output

US.

voltage

pre-amplifier

models,

is

output

pass

filter

noises.

of

the

further

C25

into

domain

driver.

induced

has

GSO-GSC

shorted

is

\

and

The

reproduced

amplifies

The

peak

output

a

~quare

filter

Main

in

read

via

matrix

three

is

in

gain

shorted

G

model

supplied

the

switch

differentiation

waveform

the

detector

after

wave.

eliminates

circuits

operation

switch

setting

to

to

to

the

filter

to

signal

constructed

passing

a

virtual

are

enclosed

by

for

selecting

terminals,

obtain

obtain

the

the

differentiation

to

~liminate

amplifier

zero

cross

with

the

with

through

pulse

the

read/write

GSa,

gain

gain

phase-shifts

point,

most

a

comparator

the

coupling

caused

in

the

side

0/1

GSI

of

100

of

200

amplifier

undesirable

and

appropriate

by

the

read

head

heads.

and

GSC.

times,

times.

via

the

peak

at

the

converts

capacitors,

saddle

i·s

high

in

the

for

G

with

two

single

driver

In

the

are

some

single

APS

signal)

depending

versions).

positive

function.

low

model)

edge

shot.

and

RD

gates.

shot

read

frequency

at

detectors,

Then

the

driver

m.v.,

is

on

PCB

Anyway,

pulses

outer

output

(3-state

To

control

input

issue

the

area

the

in

the

at

tracks.

delay

signal

driver.

TDCR

parallel.

numbers

FDD

read

(IF

output)

terminal

signal

is

operation.

area,

The

single

is

(A

so

-

time

output

of

from

These

~

set

311

62.5KHz

domain

shot,

from

the

for

the

0,

E,

that

-

for

read

read

pulse

control

control

or

the

Table

the

write

F

A~F

filter

data

FDD

width

signals

~)

RD

302

models,

is

latch,

through

LSI,

setting

circuit

and

PDD

terminal

shows

125KHz

constructed

and

the

US,

there

of

(OPEN/ROYO/

are

different

models

outputs

the

control

data

RD

delay

(PCBA

Page 18

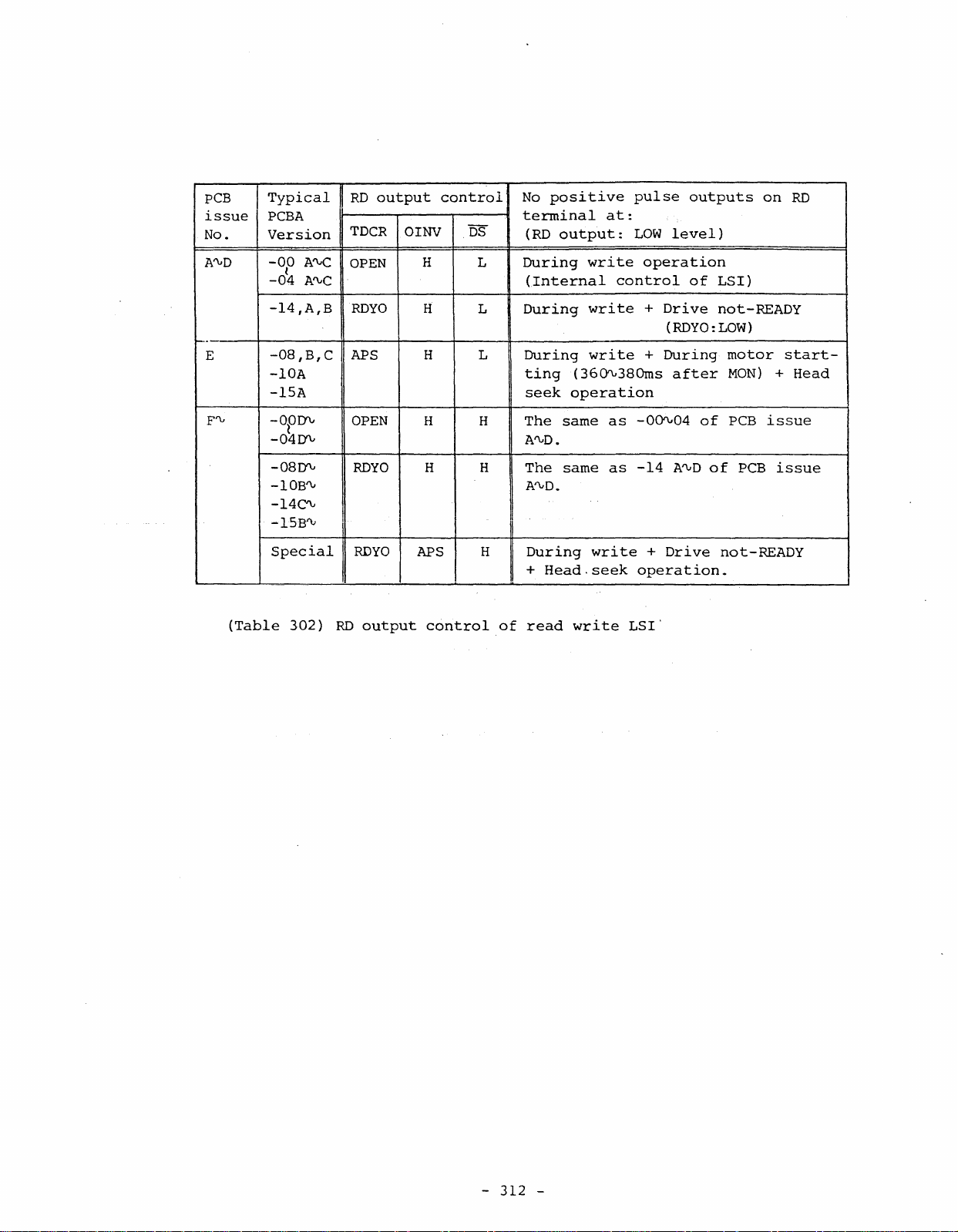

PCB

issue

No.

Typical

PCBA

Version

RD

output

TDCR

orNV

control

DS

No

positive

terminal

(RD

output:

at:

pulse

LOW

outputs

level)

on

RD

A"'D

_.

E

F'V

(Table

-00

A"-'C

(

-04

A"-'C

-14,A,B

-08,B,C

-lOA

-lSA

-OOD'\.

~

-040'\.

-080'\.

-lOB"-'

-14C'V

-ISH""

Special

302)

OPEN

RD

RDYO

APS

OPEN

RDYO

RDYO

output

H

H

H L

H

H

APS

control

During

L

(Internal

L

During

During

ting

seek

H

The

A"-'D.

H

The

A"-'D.

H

During

+

of

read

write

write

write

(36O'V380ms

operation

same

same

write

Head,

seek

write

control

-0Qt\..04

as

as

-14

operation.

LSI'

operation

of

Drive

+

(RDYO:LOW)

During

+

after

A"-'D

+

Drive

LSI)

not-READY

motor

MON)

of

PCB

PCB

of

not-READY

start-

+ Head

issue

issue

- 312 -

Page 19

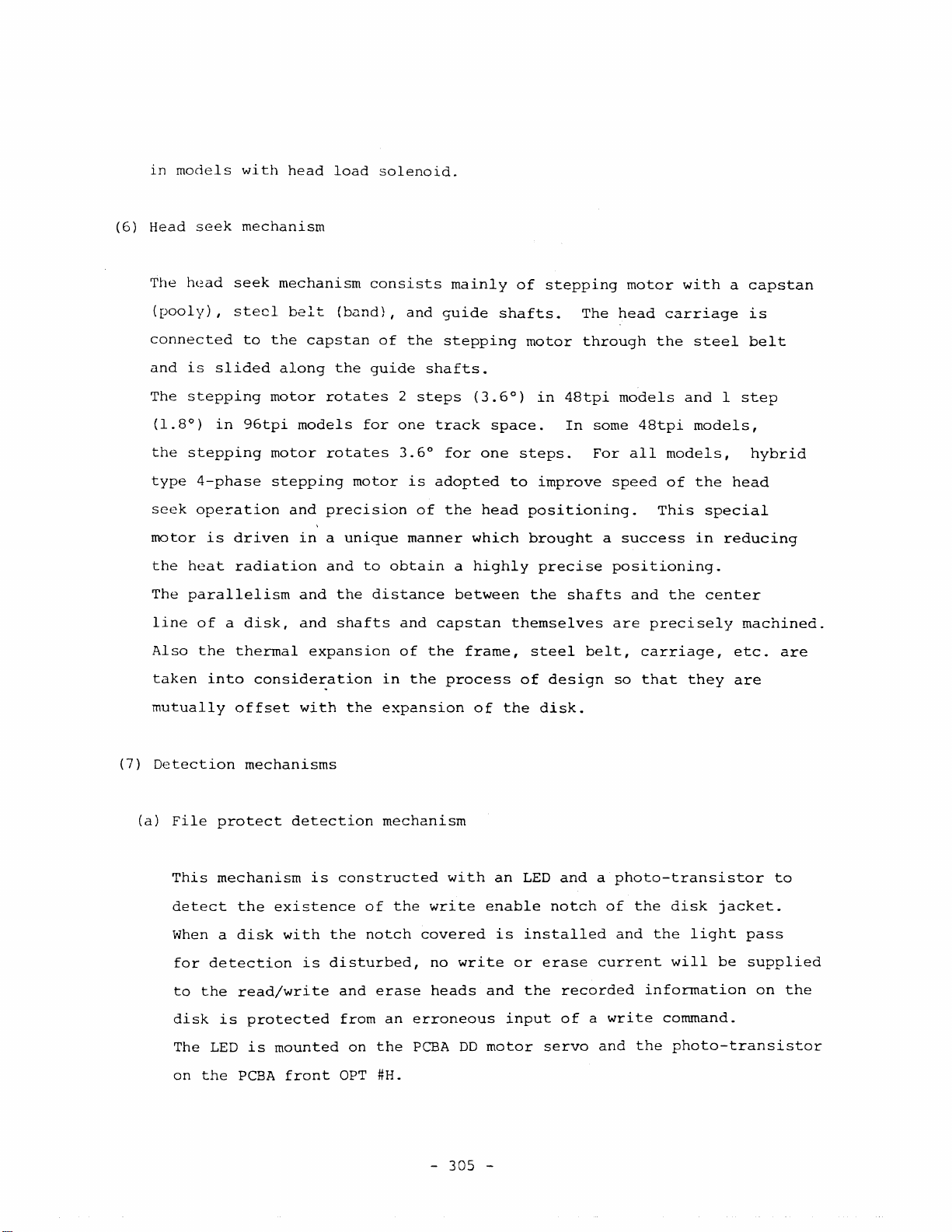

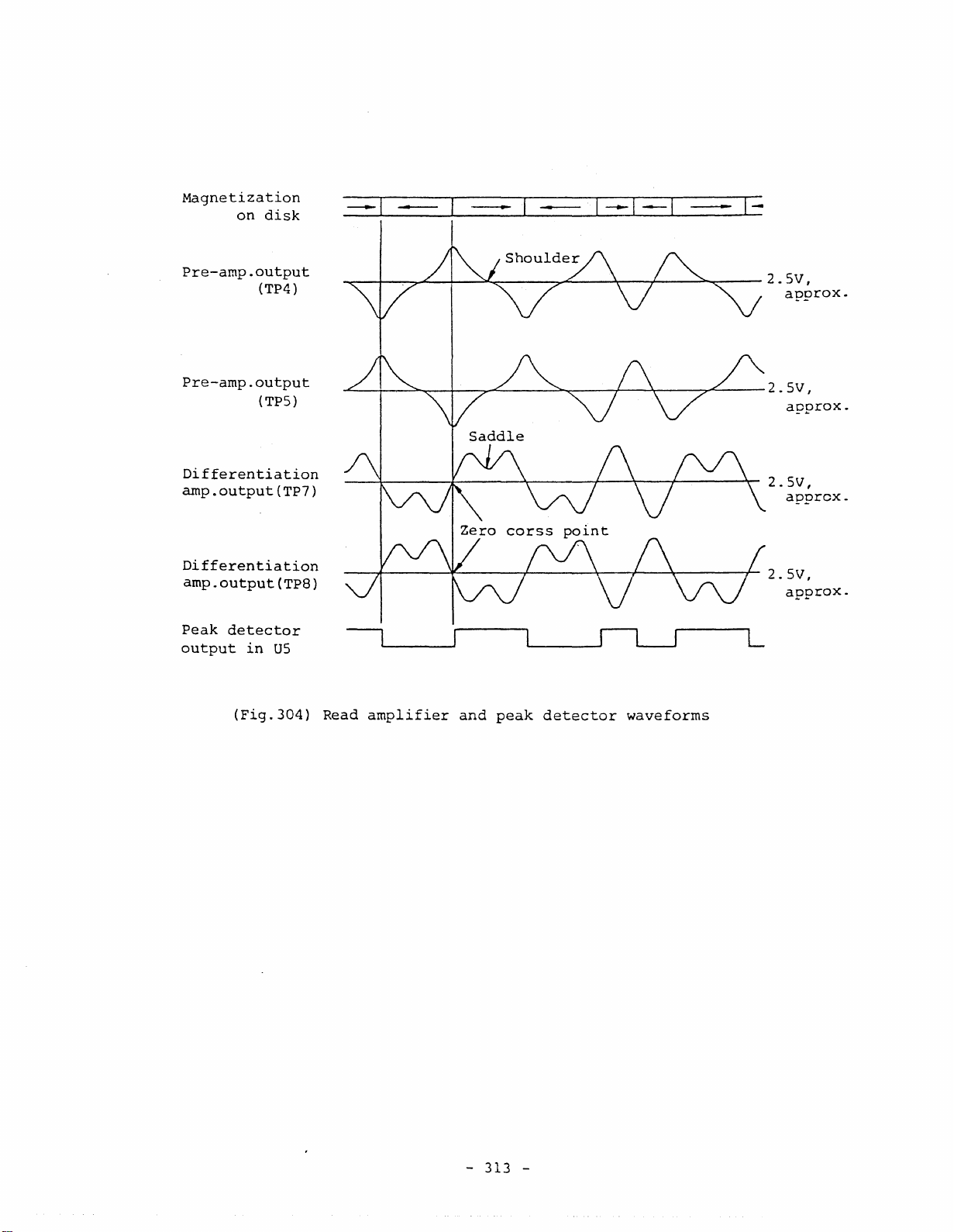

Magnetization

on

disk

Pre-amp.output

(TP4)

Pre-amp.output

(TP5)

Differentiation

amp.output(TP7)

Differentiation

amp.

Peak

output

output

detector

in

(TP8)

us

(Fig.304)

----l-~~-+--~:__----::;~---J't"-__t'---..;::".""r;::::.__-

2.

5V,

approx.

..L...--l-..:::::,.........--+--~::::..-----=::~---;f---'l~---::T'<::..---

2. 5V ,

approx.

2.5V,

approx.

--..l:..-----¥:----I---~r-----)'--_4:___--_t_

2.

5

V,

approx.

I~-

Read

amplifier

and

peak

detector

waveforms

L

- 313 -

Page 20

Peak

output

Edge

output

detector

in

detector

in

US

uS

#1

Virtual

pulse

(drop~in)

Delay

Q

output

Read

output

Edge

output

RD

output

READ

s.s.

in

data

latch

in

detector

in

DATA

(Fig.30S)

US

uS

#2

uS

(US-33)

(Jl-30)

I

T

I

-H--A"'F

U U

Time

domain

filter

n

models:

and

Ills,

read

n

U

approx.

gate

LJLJl

G

model:

,

LnJIJ

waveforms

fL

O.S\.ls,approx.

LJ

- 314 -

Page 21

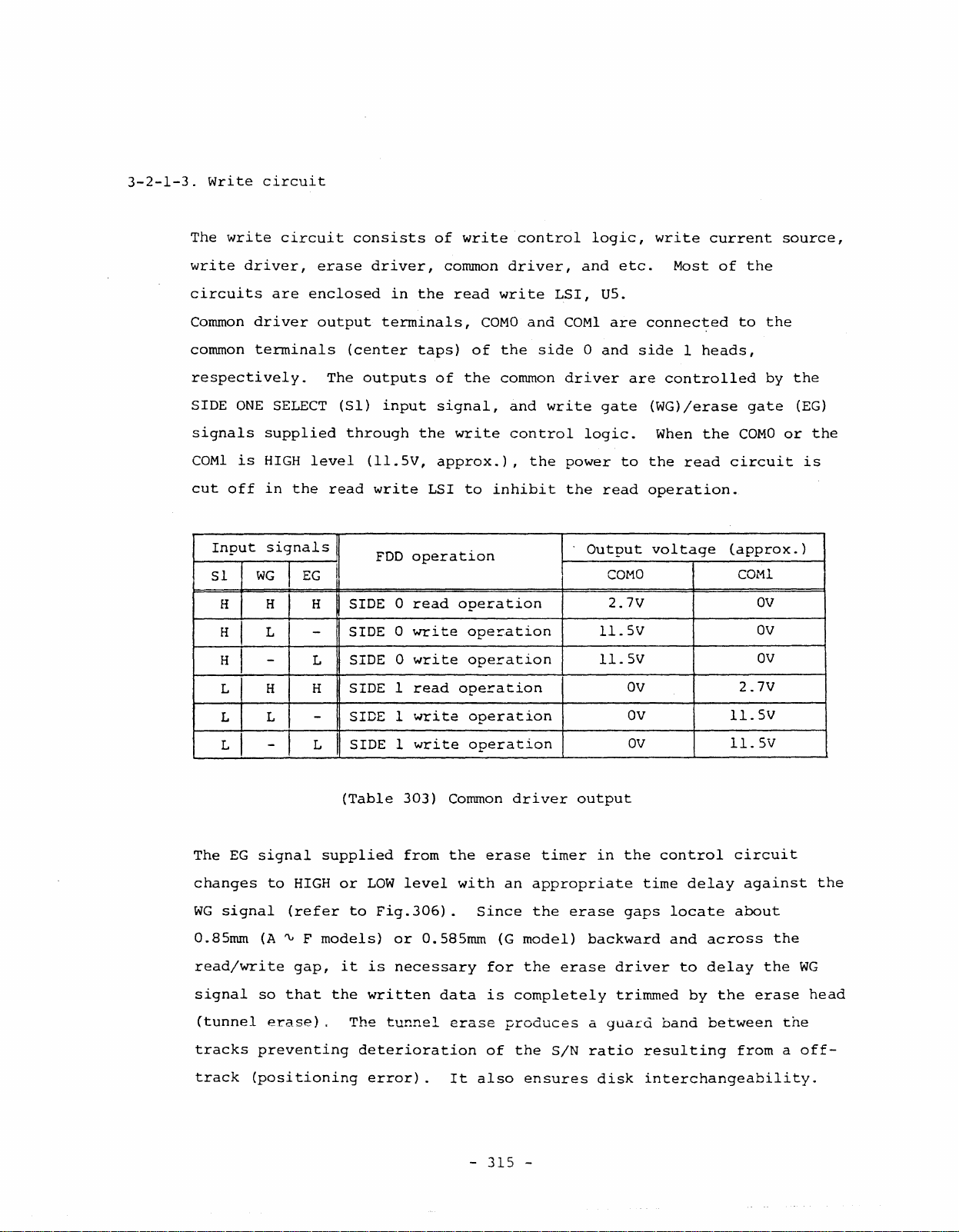

3-2-1-3.

The

Write

write

circuit

circuit

consists

of

write

control

logic,

write

current

source,

write

circuits

Common

common

respectively.

SIDE

signals

COMl

cut

driver,

driver

terminals

ONE

is

off

Input

WG

Sl

H

H

I

H - L

L H

are

enclosed

SELECT

supplied

HIGH

in

the

signals

EG

H H

L

erase

output

The

level

read

-

H

(center

(Sl)

through

I

I

SIDE

SIDE

SIDE

SIDE

driver,

in

terminals,

outputs

input

(ll.sV,

write

FDD

0

0

0

1

common

the

read

taps)

of

signal,

the

write

approx.),

LSI

operation

read

operation

write

write

read

operation

driver,

write

COMO

of

the

the

common

to

inhibit

operation

operation

and

side

and

control

the

LSI,

COMl

driver

write

power

the

and

US.

are

0

and

gate

logic.

read

Output

COMO

2.7V

11.sV

11.SV

etc.

side

are

to

OV

connected

the

operation.

Most

1

heads,

controlled

(WG)/erase

When

voltage

the

read

of

the

to

gate

COMO

circuit

(approx.

COMl

2.7V

OV

OV

OV

the

by

or

the

(EG)

the

is

)

L

L

I

The

EG

changes

WG

signal

O.8srnm

read/write

signal

(tunnel

tracks

track

L

-

signal

to

-

L

HIGH

(refer

(A~F

gap,

so

that

erase).

preventing

(positioning

SIDE

SIDE

I

(Table

supplied

or

to

models)

it

the

The

deterioration

1

1

303)

from

LOW

level

Fig.306).

or

is

necessary

written

tunnel

error).

write

write

Common

the

O.s8srnm

data

erase

It

operation

operation

erase

with

Since

for

is

of

also

driver

timer

an

appropriate

the

(G

model)

the

completely

produces

the

ensures

erase

SiN

output

in

erase

backward

a

ratio

disk

OV

OV

the

control

time

gaps

locate

and

driver

trimmed

guard

band

resulting

interchangeability.

delay

to

by

11.SV

11.sV

circuit

against

about

across

delay

the

between

from

the

the

erase

the

a

the

WG

head

off-

-

315

-

Page 22

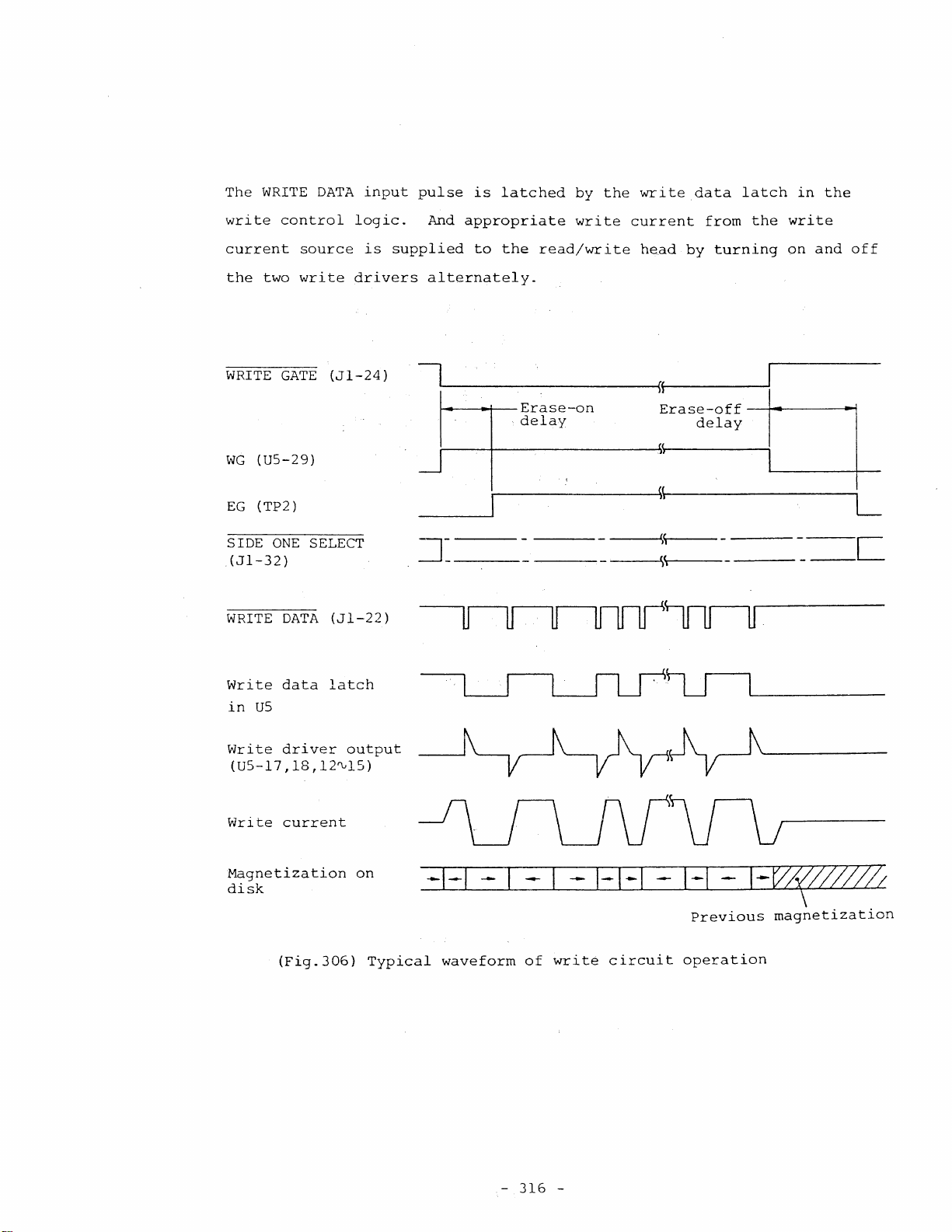

The

WRITE

DATA

input

pulse

is

latched

by

the

write

data

latch

in

the

write

current

the

WRITE

WG

(US-29)

EG

(TP2)

SIDE

,(Jl-J2)

WRITE

two

ONE

control

source

write

GATE

SELECT

DATA

logic.

drivers

(Jl-24)

(Jl-22)

is

And

supplied

alternately.

-

appropriate

to

the

Erase-on

delay

write

read/write

current

head

Erase-off

((

,

..

~\

(,~

by

delay

from

turning

the

___

write

on

and

off

L

L

Write

in

Write

(US-17,18,12tV1S)

Write

Magnetization

disk

uS

(Fig.J06)

data

driver

current

latch

output

on

Typical

waveform

of

write

circuit

Previous

operation

magnetization

-

J16

-

Page 23

3-2-1-4.

The

Low

voltage

low

voltage

sensor

sensor

is

equipped

to

protect

the

FDD

from

erroneous

operation

unstable

sensors

LVSO

monitors

of

the

it

supplies

write

driver,

protect

unstable

LVSl

is

circuit

of

3.SV

connected

the

LVS

LSI,

U3)

due

state

of

LVSO

read

the

state

equipped

in

item

through

to

signal

are

to

of

and

the

write

signals

erase

disk

of

3-2-2.

4.4V.

the

is

reset~

the

the

LVSl

+5V

LSI.

driver,

from

the

to

LVGG

LOW

internal

power

are

and

If

to

inhibit

an

erroneous

power

generate

As

The

terminal

level,

circuit

voltage

equipped

+12V

voltage

the

voltage

the

and

voltage.

LVS

well

monitored

all

write

signal

as

(pin

the

construction

such

as

in

supplied

is

operation

control

write

to

LVSO,

voltage

37)

of

control

at

the

lower

or

erroneous

be

it

the

power

read

of

logic

supplied

is

activated

by

read

circuits

write

to

than

the

the

of

the

on

the

3.SV

common

in

erase

LVSl

write

FDD

or

off.

LSI,

internal

through

driver,

the

LSI,

to

the

in

is

LSI.

(mainly

during

US.

during

control

the

only

control

Two

circuit

4.4V,

which

range

+5v

While

+sv

LVS

power

(US-32)

Power

(Fig.307)

on

Typical

3.S'\.4.4V

waveform

-

317

Power

of

low

voltage

-

off

-++--

sensor

3 .

5'\.4

. 4V

Page 24

3-2-1-5.

Function

and

operating

waveform

of

read

write

LSI

terminals

Following

operation

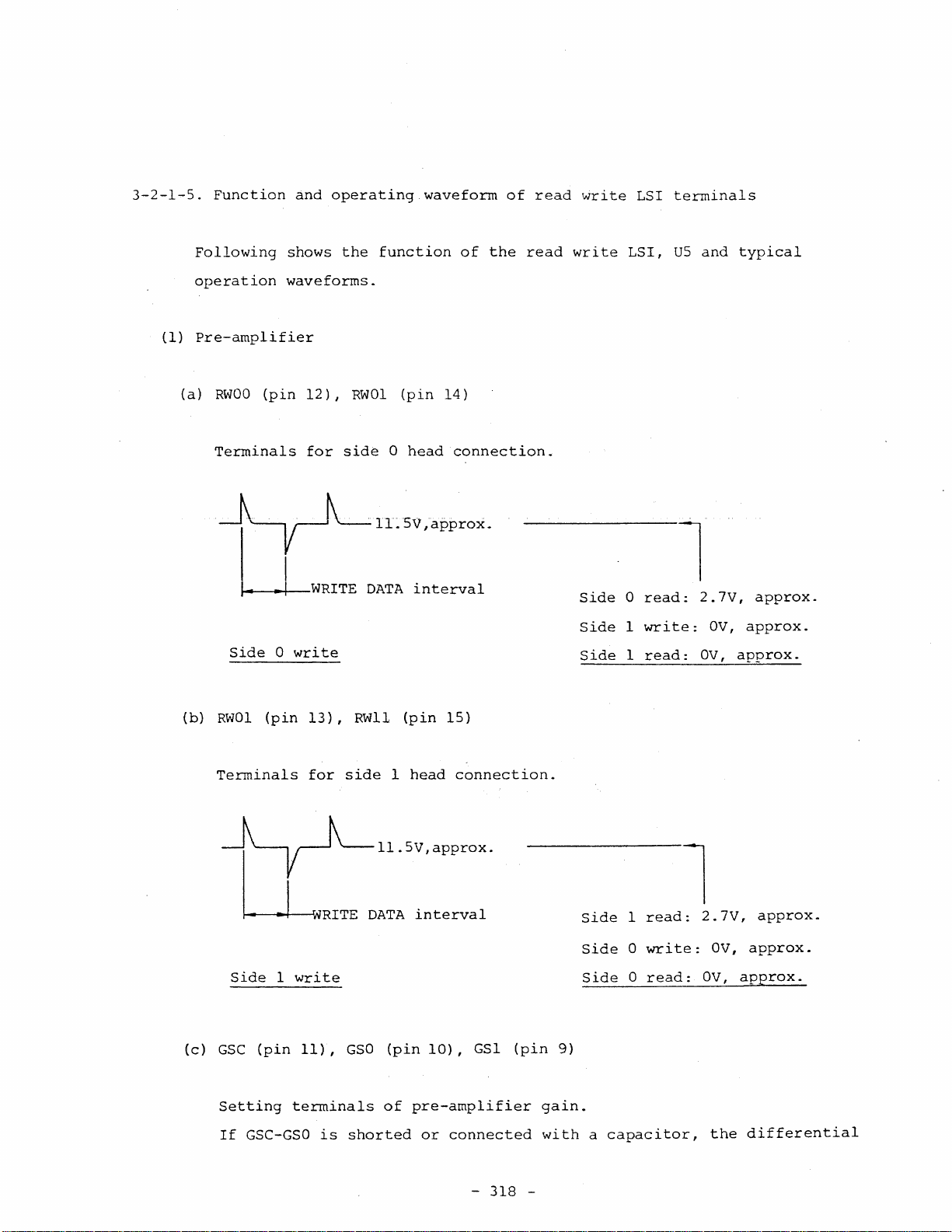

(1)

Pre-amplifier

(a)

RWOO

Terminals

(pin

shows

waveforms.

12),

for

the

RWOl

side

function

(pin

0

head

of

the

read

14)

connection~

write

LSI,

US

and

~IL5v,approx.

I.

Side

-I

0

I

write

WRITE

DATA

interval

Side

Side

Side

0

1

1

read:

write:

read:

l

2.7V,

OV,

OV,

typical

approx.

approx.

approx.

(b)

(c)

RWOl

Terminals

(pin

Ll

Side

GSC

(pin

Setting

If

GSC-GSO

13),

for

1

write

II),

terminals

RITE

is

RWll

side

1

11.sV,approx.

DATA

GSO

(pin

of

shorted

(pin

15)

head

connection.

interval

10),

pre-amplifier

or

connected

GSl

(pin

9)

gain.

with

Side

Side

Side

a

capacitor,

1

0

0

read:

write:

read:

l

2.7V,

OV,

OV,

the

approx.

approx.

approx.

differential

-

318

-

Page 25

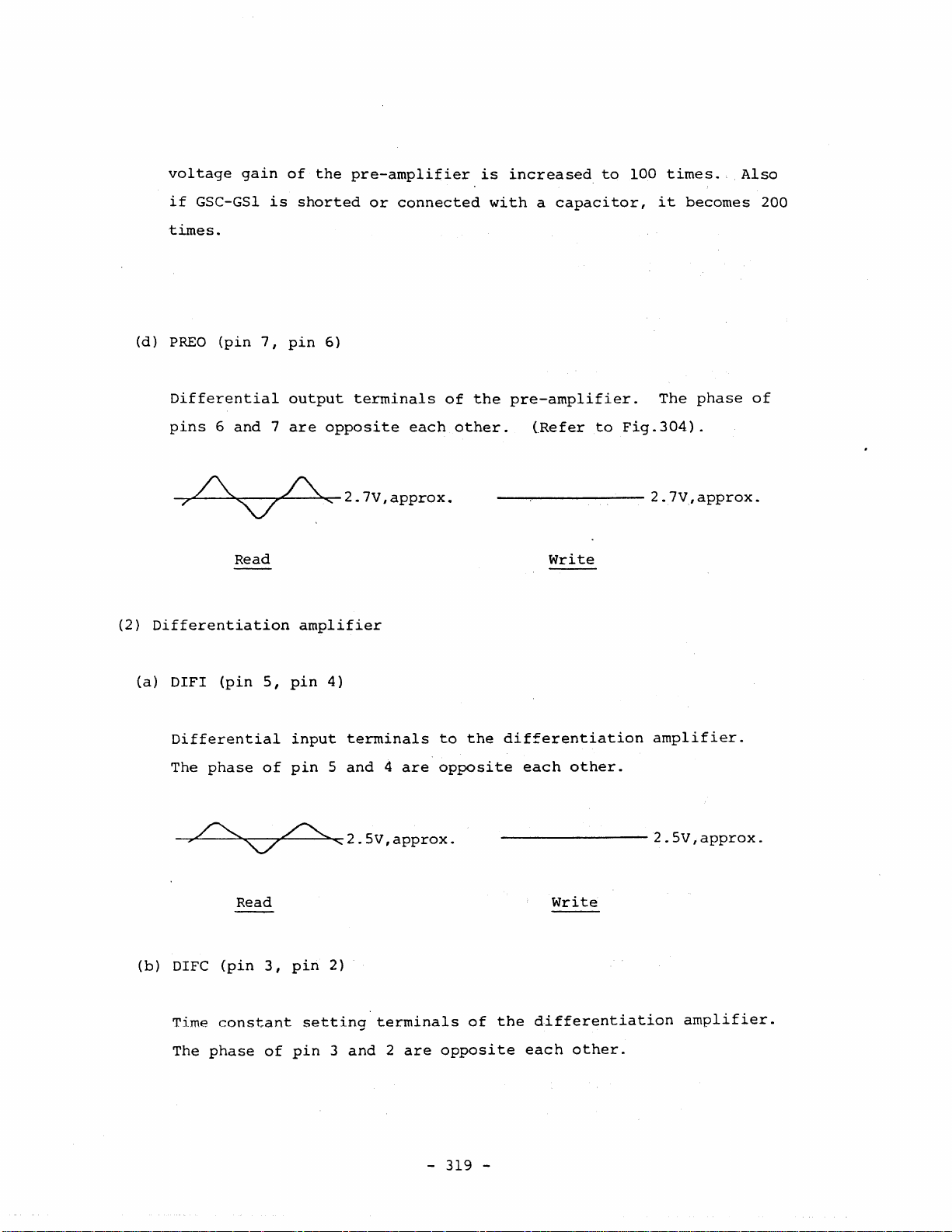

(d)

voltage

if

GSC-GSI

times.

PREO

(pin

gain

7,

is

of

the

shorted

pin

pre-amplifier

or

6)

connected

is

with

increased

a

capacitor,

to

100

times.

it

becomes

Also

200

Differential

pins

-7....,.,L-~

(2)

Differentiation

(a)

DIFI

Differential

The

6

and7are

A

......

V----...e--~'-

Read

(pin

5,

phase

/"-.... •

» "'-7'

of

output

opposite

/\.

amplifier

pin

4)

input

pin5and

~

.....

terminals

2.

7V

,

appro

terminals

4

2.

SV,

approx.

each

are

of

the

other.

x •

to

the

opposite

pre-amplifier.

(Refer

---,-------

Write

differentiation

each

other.

---------

to

The

Fig.

304)

2.7V,approx.

amplifier.

2.Sv,approx.

phase

.

of

(b)

DIFC

Time

The

Read

(pin

constant

phase

3,

of

pin

setting

pin

2)

3

and2are

terminals

-

of

opposite

319

-

Write

the

differentiation

each

amplifier.

other.

Page 26

A A

---O/,.L----.oo...:V,.--r----..:>o.,',.-- 1 . 1

v,

a

pprox

.

---------

1.

lV,

approx,

(c)

(d)

Read

DIFO

Differential

The

CI

Differential

phase

(pin

phase

Read

(pin

of

43,

of

pin

1,

pin

output

pin

pin

input

43

44)

terminals

1

and

2.7V,approx.

42)

terminal

and

42

44

are

are

of

opposite

of

the

opposite

the

write

differentiation

each

write

comparator

each

other.

other.

(peak

amplifier.

2.7V,approx.

detector).

The

(3)

fV\

-j+---\W--+---\-\-

Time

domain

(a)

TDCR

Pulse

models

While

Read

(pin

width

use

this

fV\

filter

40)

setting

this

terminal

2 • 5

terminal

terminal

is

V,

approx.

forced

for

----------2.5V,approx.

write

of

the

delay

the

inhibit

to

be

LOW

-

320

-

single

gate

level,

of

the

shot

the

RD

delay

m.v.

pulse

single

Some

output.

shot

Page 27

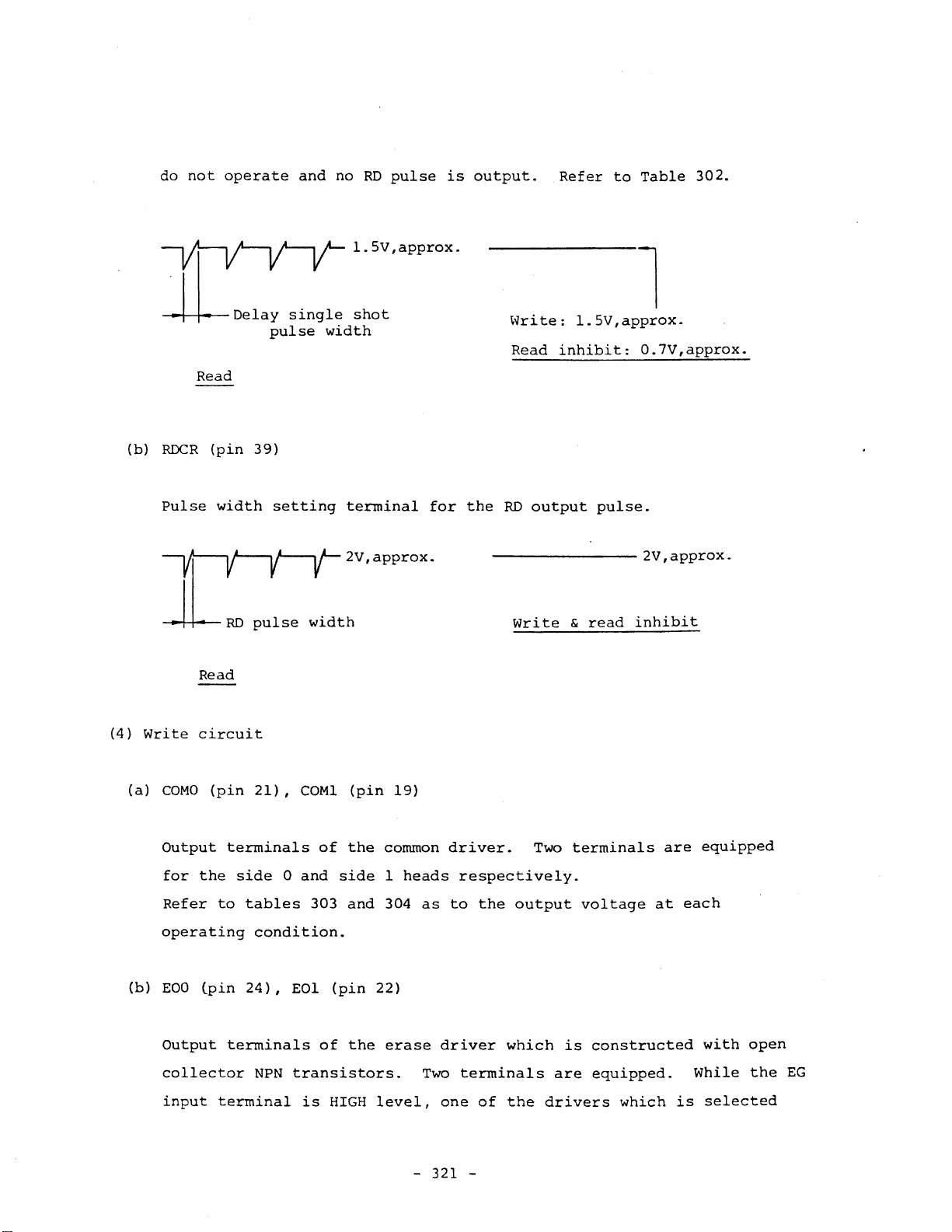

do

not

operate

and

no

RD

pulse

1.5V,approx.

is

output.

Refer

to

Table

302.

(4)

~

(b)

RDCR

Pulse

r-RD

Write

Read

(pin

width

Read

circuit

Delay

39)

pulse

single

pulse

setting

width

width

shot

terminal

2V,approx.

for

the

Write:

Read

RD

--------

write

inhibit:

output

l

1.5V,approx.

pulse.

&

read

inhibit

0.7V,approx.

2V,approx.

(a)

(b)

COMO

Output

for

Refer

operating

EOO

Output

collector

(pin

the

(pin

input

21),

terminals

side

to

tables

condition.

24),

terminals

NPN

terminal

COMl

of

0

and

303

EOl

(pin

of

transistors.

is

HIGH

(pin

the

side

and

the

19)

cornmon

1

heads

304

22)

erase

level,

-

as

Two

321

driver.

respectively.

to

the

driver

terminals

one

of

-

Two

output

which

the

terminals

is

are

drivers

voltage

constructed

equipped.

which

at

are

equipped

each

While

is

with

selected

open

the

EG

Page 28

by

the

CS

input

terminal

turns

on

(becomes

LOW).

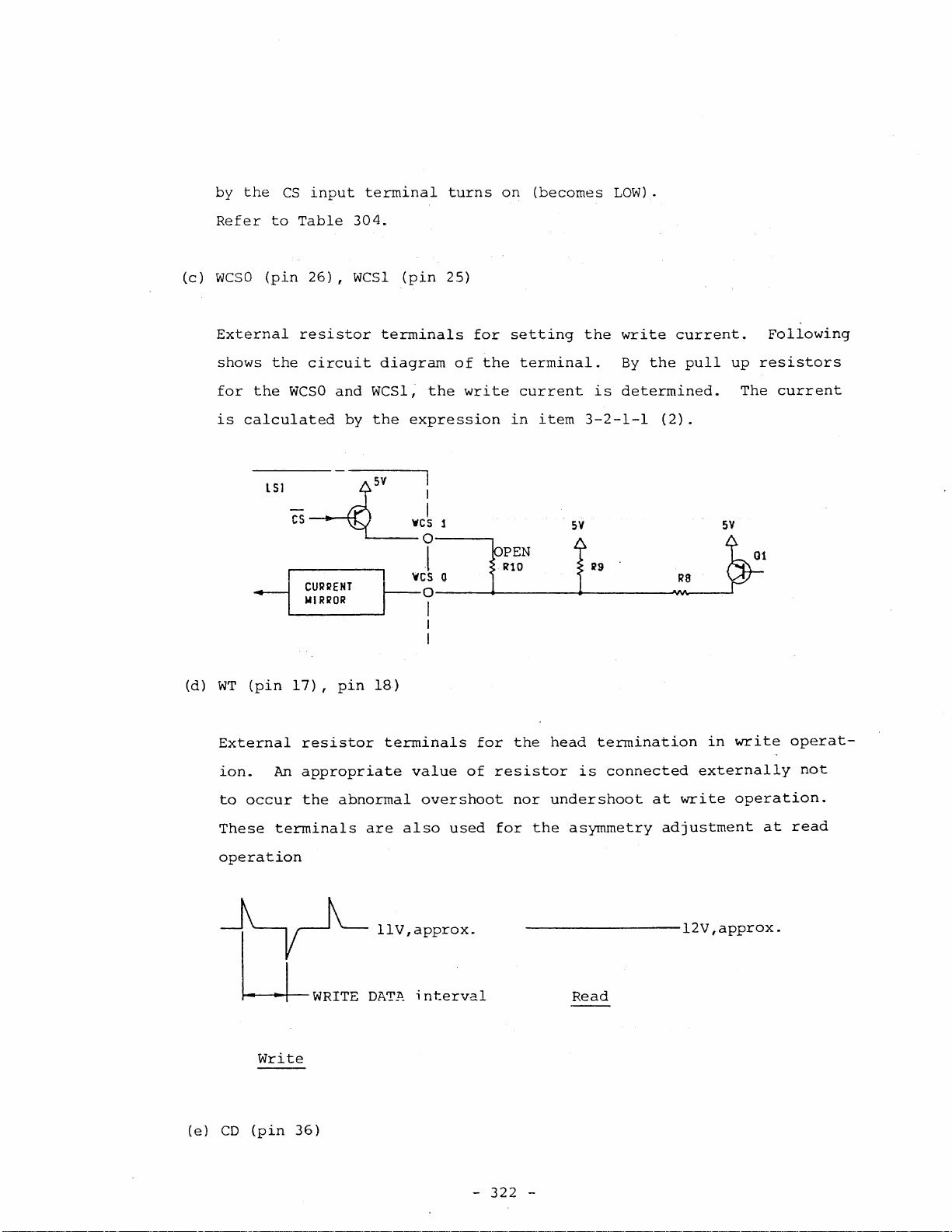

(c)

Refer

WCSO

External

shows

for

the

is

calculated

to

(pin

the

Table

26),

resistor

circuit

WCSO

and

by

304.

WCSI

WCSl,

the

(pin

terminals

diagram

the

expression

25)

of

for

the

write

setting

terminal.

current

in

item

the

write

By

is

determined.

3-2-1-1

the

(2).

current.

pull

up

The

Following

resistors

current

(d)

(e)

WT

(pin

17),

pin

18)

External

ion.

to

occur

These

operation

UWRITE

CD

(pin

An

terminals

Write

resistor

appropriate

the

abnormal

36)

terminals

are

llV,approx.

DATA

value

overshoot

also

interval

used

for

of

the

resistor

nor

for

the

---------12V

head

tennination

is

connected

undershoot

asymmetry

Read

externally

at

write

adjustment

in

write

operation.

,approx.

at

operat-

not

read

-

322

-

Page 29

In

order

to

protect

the

head

from

undersirable

magnetization,

this

(f)

terminal

at

a

determined

completion

WG

CD

CS

(pin

Control

Table

i)

304).

ON/OFF

is

used

to

set

the

direction

of

a

write

operation

H

~

1 $

27)

---

input

control

Schmitt

terminal

of

TTL

having

write

delay

for

input

current

time

1

through

(WG

I_L_

JL

following

setting

turns

to

keep

S~s,

off).

1.5V.approx.

Delay

two

the

approx.,

time

functions.

terminal

write

WCSl.

after

current

the

(Refer

flow

to

(5)

(g)

(h)

ii)

WD

WRITE

WG

Control

from

Others

Selection

(pin

28)

DATA

~vri

te

(pin

29),

input

the

of

---

input

control

erase

Schmitt

terminal

EG

(pin

terminals

circuit

driver

30)

TTL

---

for

in

input

from

write

the

output

the

Schmitt

FDD.

terminals

host

---------

TTL

permit

controller.

Read

input

(WG)

Refer

to

EOO

and

Tables

and

erase

E01.

SV,approx.

permit

304

and

(EG)

305.

-

323

-

Page 30

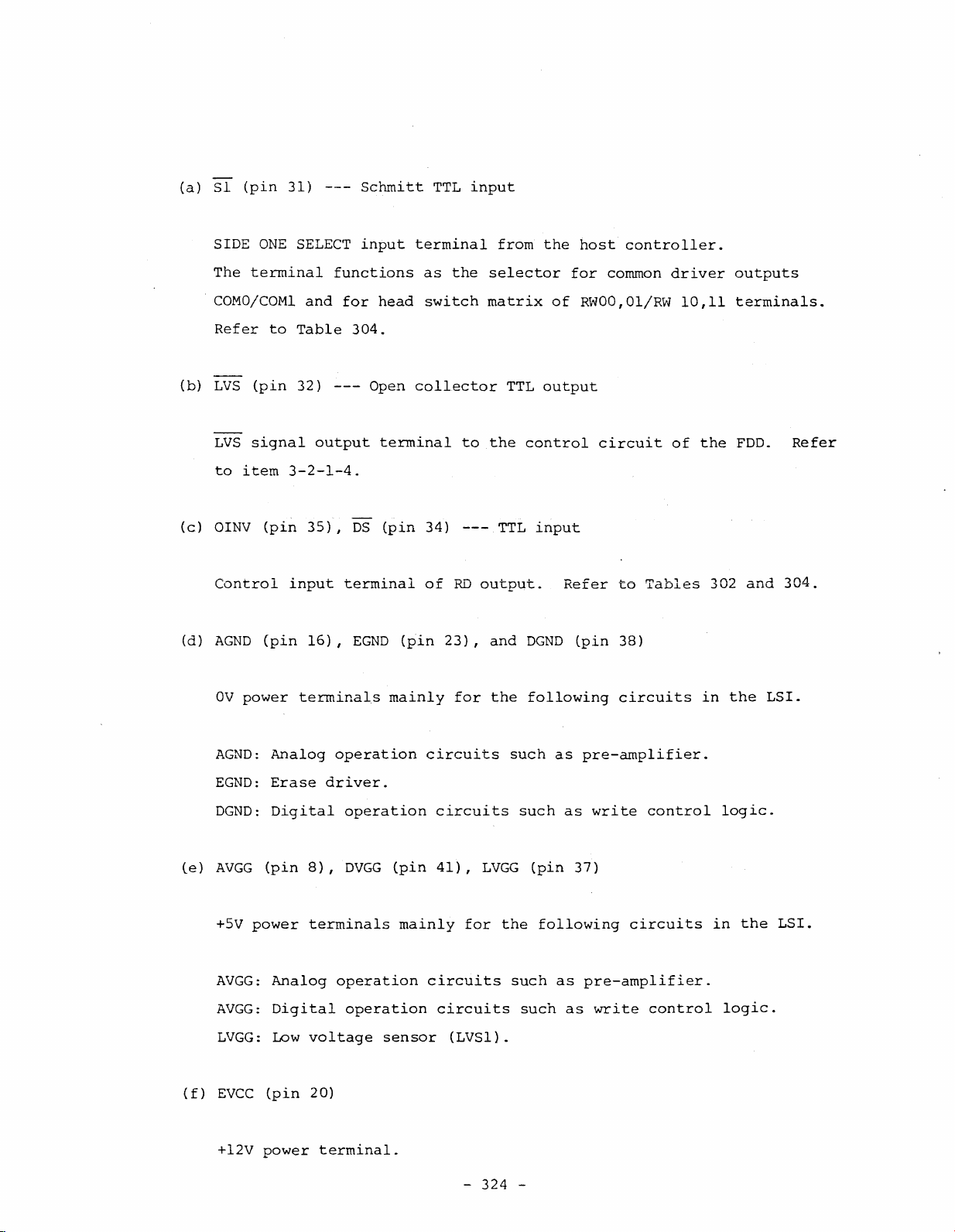

(a)

Sl

SIDE

The

(pin

ONE

terminal

31)

SELECT

---

Schmitt

input

functions

TTL

terminal

as

the

input

selector

from

the

for

host

controller.

common

driver

outputs

COMO/COMl

Refer

(b)

LVS

LVS

to

(e)

OINV

Control

(d)

AGND

OV

to

(pin

signal

item

(pin

(pin

power

and

Table

32)

output

3-2-1-4.

35),

input

16),

terminals

for

304.

---

DS

terminal

EGND

head

Open

terminal

(pin

mainly

switch

collector

34)

of

(pin

RD

23),

for

to

---

matrix

TTL

the

TTL

output.

and

the

of

output

control

input

Refer

DGND

following

RWOO,Ol/RW

circuit

to

Tables

(pin

38)

circuits

10,11

of

the

302

in

terminals.

FDD.

and

the

LSI.

Refer

(e)

(f)

AGND:

EGND:

DGND:

AVGG

+5v

AVGG:

AVGG:

LVGG:

EVCC

+12V

Analog

Erase

Digital

(pin

power

Analog

Digital

Low

(pin

power

operation

driver.

operation

8),

DVGG

terminals

operation

operation

voltage

20)

terminal.

(pin

mainly

sensor

circuits

circuits

41),

circuits

circuits

(LVSl).

for

-

LVGG

the

324

such

such

(pin

such

such

-

as

pre-amplifier.

as

37)

following

as

pre-amplifier.

as

write

write

control

circuits

control

logic.

in

logic.

the

LSI.

Page 31

R

e

a·

d

WG

L L

L L

L

L L

EG

L

Inputs

-

Sl

H

L

-

H

- -

CS

-

-

-

-

OS

Outputs

OINV

L

L

H

-

--

LVS

COMO

L H

L H

L H

H H R

EOO

COMl

R

0

0

R Z Z

0 Z Z

EOl

Z Z N 0

Z Z

Write

I

RD

current

N

Z 0

!

P

0

0

L L

W

r

/

E

r

a

e

LV

L:

H

i

t

e

s

Logic

L H

L H

H H

H

L

L H

H H

H

L H

L H H L -

H H H

H

L

L H L

H H

-

- -

level

L

H H

H

L

L

L

L

L L

(LOW)

0

-

H

-

-

- -

H

H

H -

H

L

L -

L - -

L

- - H

-

-

-

-

-

-

-

H H

-

-

-

-

-

I

-

-

-

-

-

R:

0

H

Hi

H

Hi

Hi

H

H

L

COM

0

0

0

Hi

Hi

Hi

0

0

0

voltage,

Hi

Hi

Hi

Hi

Hi

Hi

H

H

H F

H

H

H

H 0

R

0 z

0

0

0

0 Z

0 z

0

2.7V,

Z Z

0

0

Z Z

0 Z

0

Z

Z

Z

Z

Z

z

Z

Z

Z 0

Z

0

0

Z F

0

0

Z Z

approx.

P

F

WCS

F

F

F

F

WCS

WCS

F 0

WCS

WCS

F 0

F

WCS

WCS

F

WCS

F

0

0

0

0

0

0+1

0+1

0+1

0

0+1

0

H:

z:

Hi:

Logic

High

COM

level

impedance

voltage,

(Table

1 (HIGH)

(OPEN)

ll.5V,

304)

approx.

Read

write

-

P:

N:

F:

LV:

LSI

325

positive

Negative

FALSE (No

Low

voltage

control

-

pulse

pulse

pulse

table

output)

Page 32

3-2-2.

Control

The

control

Circuit

circuit

consists

of

strap

circuit,

LED&head

load

control

circuit,

stepping

interface

Almost

LSI,

U3.

(less

the

input

Fig.308

write/erase

motor

driver,

all

Since

than

terminal.

shows

control

the

circuits

the

±l~A)

the

control

circuit,

circuit,

etc.

except

LSI

is

a

CMOS

andaprotective

block

diagram.

track

for

motor

counter,

drivers

type,

register

input

on

are

is

gate,

disk

enclosed

current

serially

ready

change

is

inserted

detector,

circuit,

in

the

very

control

small

in

-

326

-

Page 33

W

10

~.J

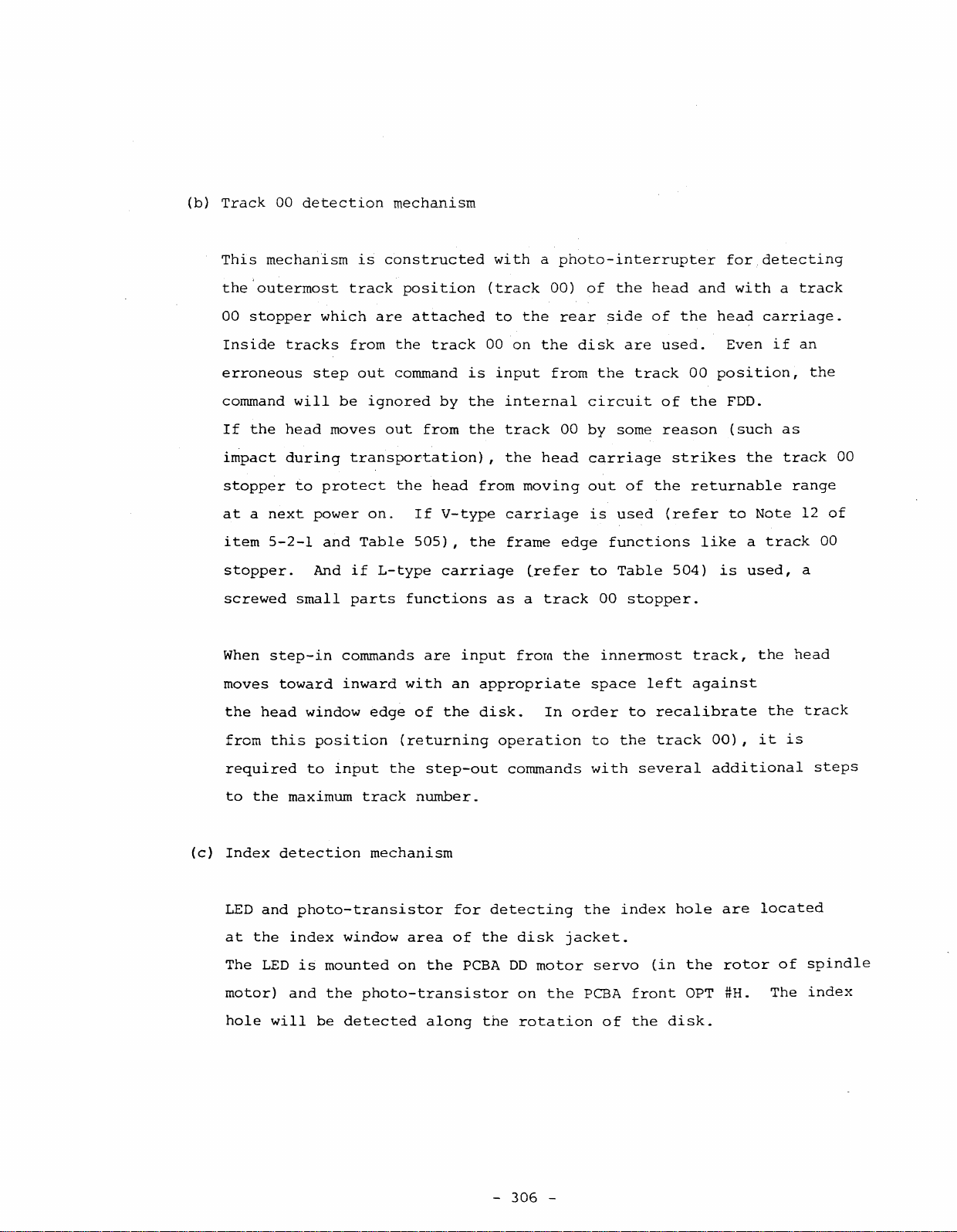

(Fig.308)

STEP

WRllE

MOTOR

INDElC

TRACK

WRllE

PROTECT

READYI

DISK

GAlE

ON

00

CHANGE

Block

of

diagram

control

STRAPS

RY.

Xl

circuit

/r-----------:.~-~:.......::...:....;,:...::...:...:.....:-------__.\.

TO/FRO~

ROYO

l.40N1

l.40NO

READ

VRITE

APS

CIRCUIT

VG

EGLVS

SF

DSEl

~

I

ISTP

ill

DeDO

IDXO

TOO

WPO

RDYO

CLOCK

~--+-J

LSI

U3

I 1

CLOCK

GENERATOR

---.

I

~.

LEW

I

ov+

FRONT

INDEX

SENSOR

LED

STEPP

MOTOR

I

NG

L :

A.S

H E'G

MODEL(4BtDI)_

MODEl(96tcl)

~

L :

A'F

H G

MODELC300rorn)

MODEl(360rorn)

L..-.._--=":...:'_-.=,3

..

~C

FOR

0n

SPINDLE

MOTO~

Page 34

3-2-2-1.

In

Strap

order

circuit

to

select

the

various

function

by

users,

various

strap

posts

as

Some

wires

to

.to

the

are

the

models

instead

version

available.

details

have

of

table

not

the

of

Refer

strap

strap

strap

in

the

to

the

function.

posts.

posts,

schematic

Specification

These

and

models

~~e

diagraml.

function

items

have

soldered

is

1-11

fixed.

and

jumping

(Refer

1-12

-

328

-

Page 35

3-2-2-2.

The

LED

circuits

and

head

load

consists

control

of

circuit

LED/Head

load

gate,

overdrive

timer

1,

LED

driver,

(1) LED/Head

To

the

and

IN

According

signal)

to

the

(a)

DLED

A

signal

While

Strap

Ul

OFF

OFF

ON

solenoid

load

LED/Head

USE

(IU}/HEAD

to

the

and

U2

LED

driver

signal

to

this

signal

setting

U2

OFF

ON

OFF

gate

(US2

turn

driver,

load

selected

and

on

U3

USI

L

L

H

gate

LOAD

signal),

the

the

is

LOW

input

US2

and

in

(IHL)

function

solenoid

front

level,

L

H

L

overdrive

the

control

signals

these

bezel

the

LED

on

(No

~elation

-

(L)

IU

-

(L)

IU

(L)

IU

circuit

LSI,

are

designated

input

driver

signals

indicator

LED

condition

--

+

OSEL

--

+

OSEL

input.

as

turns

to

1.

U3,

by

OLEO

HL

(L)

(L)

DRIVE

the

are

and

(LED).

on.

(OLEO

strap

SELECT

straps

gated

HLC

LOW)

& IHL

Ul (USI

to

output

signals.

input)

(DSEL)

(b)

ON

HLC

signal

A

signal

solenoid.

ON

RDYO:

(Table

to

U3,

activate

While

H

Ready

305)

this

H

detector

LED

the

signal

IU

turn-on

solenoid

is

-

(L)

output

LOW

329

+

DSEL

signal.

condition

for

the

level,

-

(L) x

models

the

ROY

a

HIGH

with

solenoid

(H)

in

ready.

head

is

load

activated.

Page 36

Strap

Ul

setting

U2

BL

USl

U3

input

US2

--

IHL

Solenoid

(No

relation

on

condition

to

IU

(HLS HIGH)

strap

&

IU

input)

(2)

OFF OFF OFF

OFF OFF

OFF

ON

OFF

ON

ON

OFF

ON

OFF

ON

ON

ON

ON

Note:

LED

driver

ON

OFF L

ON

OFF

ON

OFF B

ON

PRDY=

Pre-ready:

RDYO

(Table

L

L L

L

H L

H

H

(see

Internal

one

306)

L

L/H

H

H

L/H

L

LIB

H

H

LIB

Table

rotation

Solenoid

L DSEL

DSEL

PRDY

L

--

IHL

The

L

The

L

The

The

305)

signal

of

drive

(L)

(L)

---

(L)

same

same

same

same

+

Pre-ready

of

LSI.

the

condition

x

disk

x

PRDY

x

IHL

No.3

PRDY

as

as

as

as

No.1

No.2

No.1

No.2

It

(one

---

(L)

x

No.4

---

becomes

INDEX

No.1

PRDY

---

TRUE

pulse)

No.2

before

DLED

driver

collector

(3)

Solenoid

The

lKQ

construction

(4)

Overdrive

The

LSI.

For

output

signal

HLC

is

HLC

The

the

IC,

U7.

output).

driver

signal

supplied

timer

signal

overdrive

initial

(open

from

of

drain)

the

U7

from

to

U7.

1

is

also

26msec

control

is

constructed

Refer

the

the

driver

supplied

timer

of

LOW

to

control

is

the

level.

LSI,

U3

with

Fig.309.

LSI,

IC,

U7.

to

the

constructed

solenoid

is

inverted

NPN

U3

with

Refer

overdrive

activation,

transistor

with

and

a

pull

to

Fig.309

timer

a

retriggerable

is

up

it

input

array

resistor

as

to

in

the

maintains

to

(open

the

control

counter.

of

the

the

HOD

-

330

-

Page 37

vee

-1

.....

1-...-0

CQA

IN

STB

- - --M-- -

STa

IN

IN

IN

1N

IN

JN

GNO

(Fig.309)

+---

1

3

4

5

6

Construction

20K

......-.......

of

-~-

OUT

driver

.......

1

2

3

4

5

6

--n

IC,

OUT

GHO

U7

(5)

Overdrive

The

overdrive

level.

the

After

+5v

In

some

emitter-collector

the

circuit

HOD

signal

circuit

+l2V

drawing-in

the

overdrive

power

through

models,

solenoid.

is

power

action

1

input

1

and

is

period,

the

overdrive

of

Q5.

to

it

applied

of

the

diode

the

PNP

makes

to

solenoid

the

CRl

function

In

such

-

transistor

Q5

turn

the

solenoid

to

save

is

a

model,

331

-

on

solenoid

securely.

maintains

the

not

Q5

while

at

power.

equipped

+l2V

which

the

that

is

signal

time

its

with

always

constructs

to

situation

shorting

supplied

is

LOW

execute

the

with

the

to

Page 38

HLC

input

HOD

output

Applied

to

solenoid

voltage

coil

(Fig.310)

l

--_,-llv,approx.

J

I I

~overdrive

approx.

Overdrive

1~---------------12V'

I

,

~----OV

period

timing

of

head

load

solenoid

approx.

4V,approx.

- 332 -

Page 39

3-2-2-3.

Write/erase

The

circuit

control

consists

circuit

of

write/erase

gate

and

erase

timer.

Most

of

the

(1)

(a)

(b)

parts

of

Write/erase

The

gate

If

it

can

LSI

and

The

WG

are

different

Control

WG=

DSEL(L) x IWG(L) x

Control

--

WG=

DSEL(L} x IWG(L) x

the

judges

be,

erase

signal

LSI

LSI:

circuit

gate

whether

the

timer.

becomes

depending

No.:

2206-00

--

are

circuit

2206-00

enclosed

new

supplies

TRUE

on

FPT(L)

LHS060B

FPT(L)

data

in

the

each

LHS060

in

the

can

be

written

the

WG

followin~

LSI

No.

or

LHS060A

x

MON

delay

control

signal

condition.

1 x SEEK

on

LSI,

for

an

U3.

installed

the

read

The

disk.

write

conditions

(2)

Notes

Erase

WG:

Write

operation

DSEL: DRIVE SELECT

IWG: WRITE

FPT:

File

The

enable

is

MaN

delay

GATE