Page 1

HCD-SR4W

Amplifier section

Stereo mode (rated) 65 W + 65 W (4 ohms at

1 kHz, DIN)

Surround mode Front:

114

W +

114

W

(reference) (with SS-TS21)

music power output Center*:

114

W

(with SS-CT33)

Surround*:

114

W +

114

W

(with SA-TS22W,

Subwoofer*:

115

W × 2

(with SS-WS12)

*Depending on the sound field settings and the source

,

there may be no sound output.

Inputs VIDEO/TV/SAT:

Sensitivity: 250 mV/

450 mV/450 mV

Impedance: 50 kilohms

Output SURROUND BACK

Voltage: 2V

Impedance: 1 kilohms

Phones Accepts low-and high-

impedance headphones.

Super Audio CD/DVD system

Laser Semiconductor laser

(Super Audio CD/DVD: λ

= 650 nm)

(CD: λ = 780 nm)

Emission duration:

continuous

Signal format system PAL/NTSC

Frequency response (at 2 CH STEREO mode)

DVD (PCM): 2 Hz to 22

kHz (±1.0 dB)

CD: 2 Hz to 20 kHz (±1.0

dB)

Harmonic distortion Less than 0.03 %

Tuner section

System PLL quartz-locked digital

synthesizer system

FM tuner section

Tuning range 87.5 – 108.0 MHz (50 kHz

step)

Antenna (aerial) FM wire antenna (aerial)

Antenna (aerial) terminals

75 ohms, unbalanced

Intermediate frequency 10.7 MHz

AM tuner section

Tuning range

European, Russian models:

531 – 1,602 kHz (with the

interval set at 9 kHz)

531 – 1,602 kHz (with the

interval set at 9 kHz)

531 – 1,602 kHz (with the

interval set at 9 kHz)

530 – 1,710 kHz (with the

interval set at 10 kHz )

Antenna (aerial) AM loop antenna (aerial)

Intermediate frequency 450 kHz

Middle Easten models:

Other models:

European, Russian models:

Video section

Outputs

Video: 1 Vp-p 75 ohms

V

S video:

Y: 1 Vp-p 75 ohms

C:0.286 Vp-p 75 ohms

COMPONENT:

Y: 1 Vp-p 75 ohms

P

B/CB

, PR/CR: 0.7 Vp-p

75 ohms

ideo: Vp-p 75 ohmsOther models:

General

Power requirements

European models: 230 V AC, 50/60 Hz

Other models: 220 – 240 V AC,

50/60 Hz

Power consumption 90 W

0.3 W (at the Power

Saving mode)

Dimensions (approx.) 430 × 60 × 385 mm

incl. projecting

parts

Mass (approx.) 4.7 kg

Design and specifications are subject to change

without notice.

/h/d) (w

SS-TS21)

SERVICE MANUAL

Ver 1.0 2004.07

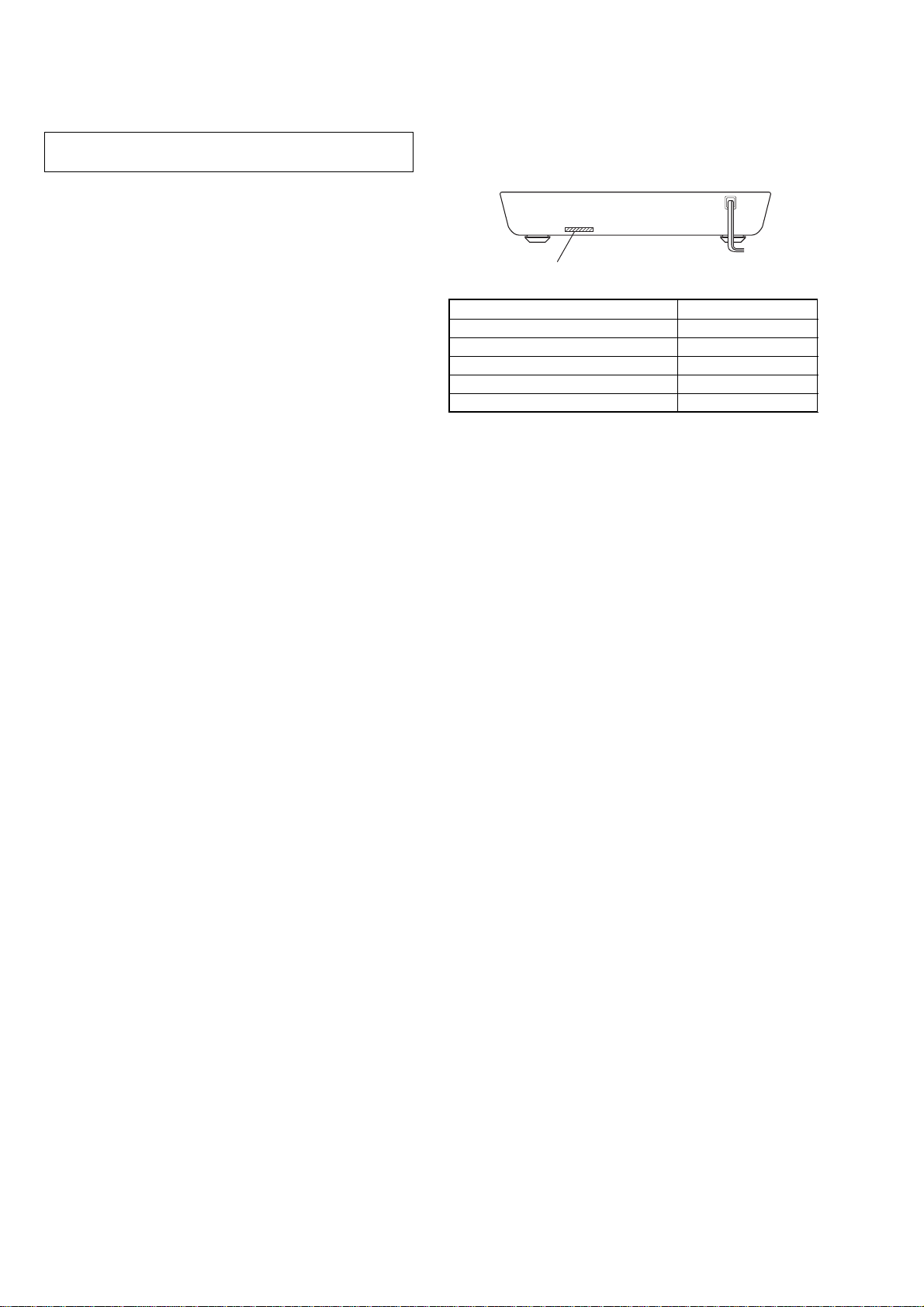

HCD-SR4W is the amplifier, DVD/

SACD and tuner section in DAV-SR4W.

SPECIFICATIONS

AEP Model

UK Model

E Model

Australian Model

Chinese Model

Model Name Using Similar Mechanism HCD-SR1

Mechanism T ype CDM80A-DVBU24

Optical Pick-up Name DBU-1

9-879-095-01

2004G1678-1

© 2004.07

Sony Corporation

Audio Group

Published by Sony Engineering Corporation

SACD/DVD RECEIVER

Page 2

HCD-SR4W

Laser component in this product is capable of emitting radiation

exceeding the limit for Class 1.

This appliance is classified as

a CLASS 1 LASER product.

The CLASS 1 LASER

PRODUCT MARKING is

located on the rear exterior.

CAUTION

Use of controls or adjustments or performance of procedures

other than those specified herein may result in hazardous radiation

exposure.

Notes on chip component replacement

• Never reuse a disconnected chip component.

• Notice that the minus side of a tantalum capacitor may be

damaged by heat.

Flexible Circuit Board Repairing

• Keep the temperature of the soldering iron around 270 °C

during repairing.

• Do not touch the soldering iron on the same conductor of the

circuit board (within 3 times).

• Be careful not to apply force on the conductor when soldering

or unsoldering.

UNLEADED SOLDER

Boards requiring use of unleaded solder are printed with the leadfree mark (LF) indicating the solder contains no lead.

(Caution: Some printed circuit boards may not come printed with

the lead free mark due to their particular size)

: LEAD FREE MARK

Unleaded solder has the following characteristics.

• Unleaded solder melts at a temperature about 40 °C higher

than ordinary solder.

Ordinary soldering irons can be used but the iron tip has to be

applied to the solder joint for a slightly longer time.

Soldering irons using a temperature regulator should be set to

about 350 °C.

Caution: The printed pattern (copper foil) may peel away if

the heated tip is applied for too long, so be careful!

• Strong viscosity

Unleaded solder is more viscou-s (sticky, less prone to flow)

than ordinary solder so use caution not to let solder bridges

occur such as on IC pins, etc.

• Usable with ordinary solder

It is best to use only unleaded solder but unleaded solder may

also be added to ordinary solder.

SAFETY-RELATED COMPONENT WARNING!!

COMPONENTS IDENTIFIED BY MARK 0 OR DOTTED LINE

WITH MARK 0 ON THE SCHEMATIC DIAGRAMS AND IN

THE PARTS LIST ARE CRITICAL TO SAFE OPERATION.

REPLACE THESE COMPONENTS WITH SONY PARTS WHOSE

PART NUMBERS APPEAR AS SHOWN IN THIS MANUAL OR

IN SUPPLEMENTS PUBLISHED BY SONY.

2

Page 3

TABLE OF CONTENTS

HCD-SR4W

1. SERVICING NOTE ................................................... 4

2. GENERAL ................................................................... 5

3. DISASSEMBLY

3-1. Disassembly Flow ........................................................... 8

3-2. Side Panel (R)(L), Front Panel Section ........................... 9

3-3. Fl Board........................................................................... 9

3-4. Mechanism Deck (CDM80A-DVBU24)......................... 10

3-5. AMP Board...................................................................... 10

3-6. Switching Regulator ........................................................ 11

3-7. Tuner Unit, IO Board ...................................................... 11

3-8. DMB08 Board ................................................................. 12

3-9. Chassis (Top) ................................................................... 12

3-10. Lever (Loading R/L)........................................................ 13

3-11. Disc Stop Lever, Disc Sensor Lever ................................ 14

3-12. DRIVER Board ............................................................... 14

3-13. RF Board ......................................................................... 15

3-14. Optical Pick-up (DBU-1) ................................................ 15

3-15. Base Unit ......................................................................... 16

3-16. Lever (BU Lock) ............................................................. 16

3-17. Close Lever...................................................................... 17

3-18. Dir Lever, Gear (IDL-B).................................................. 17

3-19. Gear (IDL-C).................................................................... 18

4. TEST MODE ............................................................... 19

5. ELECTRICAL ADJUSTMENT ............................. 27

6. DIAGRAMS

6-1. Block Diagram – RF/SERVO Section – .......................... 30

6-2. Block Diagram – AUDIO (DSP) Section – ..................... 31

6-3. Block Diagram – AUDIO (OUT) Section – .................... 32

6-4. Block Diagram – VIDEO Section – ................................ 33

6-5. Block Diagram – DIAT TRANSMIT Section – .............. 34

6-6. Block Diagram – POWER Section –............................... 35

6-7. Printed Wiring Board – RF Board – ................................ 36

6-8. Schematic Diagram – RF Board –................................... 37

6-9. Printed Wiring Board – DRIVER Board – ...................... 38

6-10. Schematic Diagram – DRIVER Board –......................... 38

6-11. Printed Wiring Board – DMB08 Board (Side A) – ......... 39

6-12. Printed Wiring Board – DMB08 Board (Side B) – ......... 40

6-13. Schematic Diagram – DMB08 Board (1/10) –................ 41

6-14. Schematic Diagram – DMB08 Board (2/10) –................ 42

6-15. Schematic Diagram – DMB08 Board (3/10) –................ 43

6-16. Schematic Diagram – DMB08 Board (4/10) –................ 44

6-17. Schematic Diagram – DMB08 Board (5/10) –................ 45

6-18. Schematic Diagram – DMB08 Board (6/10) –................ 46

6-19. Schematic Diagram – DMB08 Board (7/10) –................ 47

6-20. Schematic Diagram – DMB08 Board (8/10) –................ 48

6-21. Schematic Diagram – DMB08 Board (9/10) –................ 49

6-22. Schematic Diagram – DMB08 Board (10/10) –.............. 50

6-23. Printed Wiring Board – AMP Board (Side A) – .............. 51

6-24. Printed Wiring Board – AMP Board (Side B) – .............. 52

6-25. Schematic Diagram – AMP Board (1/4) – ...................... 53

6-26. Schematic Diagram – AMP Board (2/4) – ...................... 54

6-27. Schematic Diagram – AMP Board (3/4) – ...................... 55

6-28. Schematic Diagram – AMP Board (4/4) – ...................... 56

6-29. Printed Wiring Board – IO Section – .............................. 57

6-30. Schematic Diagram – IO Section (1/2) – ........................ 58

6-31. Schematic Diagram – IO Section (2/2) – ........................ 59

6-32. Printed Wiring Board – DDCON Board –....................... 60

6-33. Schematic Diagram – DDCON Board – ......................... 61

6-34. Printed Wiring Board – DIAT TRANSMIT Board – ...... 62

6-35. Schematic Diagram – DIAT TRANSMIT Board – ........ 63

6-36. Printed Wiring Board – SPEAKER OUT Section –........ 64

6-37. Schematic Diagram – SPEAKER OUT Section – .......... 65

6-38. Printed Wiring Board – FL Board – ................................ 66

6-39. Schematic Diagram – FL Board – ................................... 67

6-40. Printed Wiring Board

– POWER/FRONT PANEL Section –............................. 68

6-41. Schematic Diagram

– POWER/FRONT PANEL Section –............................. 69

7. EXPLODED VIEWS

7-1. Case Section ................................................................... 103

7-2. Front Panel Section ........................................................ 104

7-3. Chassis Section............................................................... 105

7-4. Mechanism Deck Section-1 (CDM80A-DVBU24) ....... 106

7-5. Mechanism Deck Section-2 (CDM80A-DVBU24) ....... 107

7-6. Mechanism Deck Section-3 (CDM80A-DVBU24) ....... 108

7-7. Base Unit Section ........................................................... 109

8. ELECTRICAL PARTS LIST ................................. 110

3

Page 4

HCD-SR4W

SECTION 1

SERVICING NOTE

NOTES ON HANDLING THE OPTICAL PICK-UP

BLOCK OR BASE UNIT

The laser diode in the optical pick-up block may suffer electrostatic

break-down because of the potential difference generated by the

charged electrostatic load, etc. on clothing and the human body.

During repair, pay attention to electrostatic break-down and also

use the procedure in the printed matter which is included in the

repair parts.

The flexible board is easily damaged and should be handled with

care.

NOTES ON LASER DIODE EMISSION CHECK

The laser beam on this model is concentrated so as to be focused on

the disc reflective surface by the objective lens in the optical pickup block. Therefore, when checking the laser diode emission,

observe from more than 30 cm away from the objective lens.

MODEL IDENTIFICATION

— BACK PANEL —

Part No.

Model Name Part No.

EA 2-109-513-0[]

HK, SP, TW, KR, CH 2-109-513-1[]

AEP, UK 4-253-896-7[]

RU 4-253-896-8[]

MX, AUS, E41 4-253-896-9[]

• Abbrevia tion

AUS : Australian model

CH : Chinese model

E41 : 230 V AC area in E model

EA : Saudi Arabia model

HK : Hong Kong model

KR : Korean model

MX : Mexican model

RU : Russian model

SP : Singapore model

TW : Taiwan model

4

Page 5

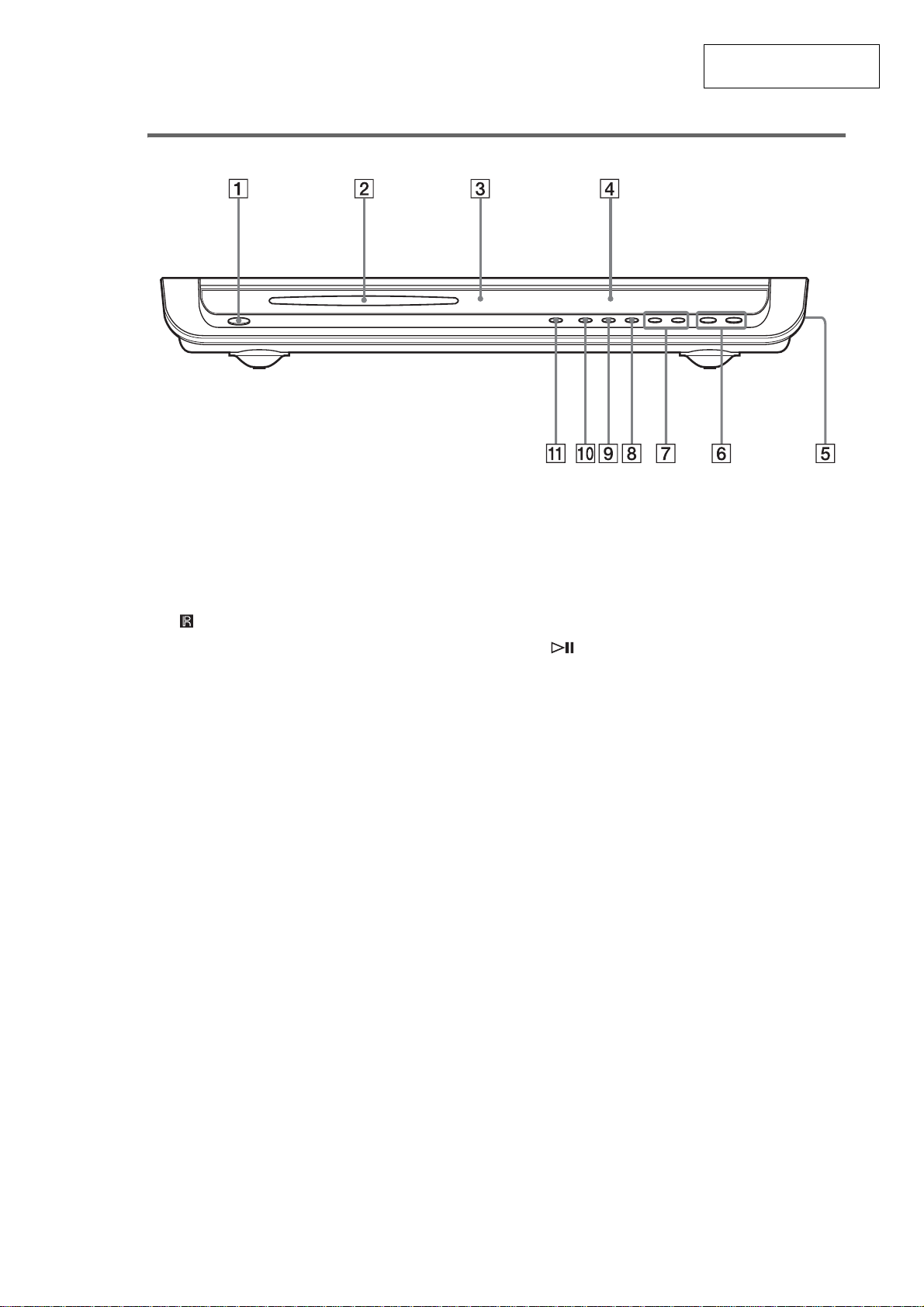

Front Panel

SECTION 2

GENERAL

HCD-SR4W

This section is extracted

from instruction manual.

A [/1 (power) switch/STANDBY indicator F VOLUME +/–

B Disc slot

C (remote sensor)

D Front panel display

E PHONES (on the side of the system)

jack

G ./>

H x (stop)

I (play/pause)

J FUNCTION

K

Z

(eject)

5

Page 6

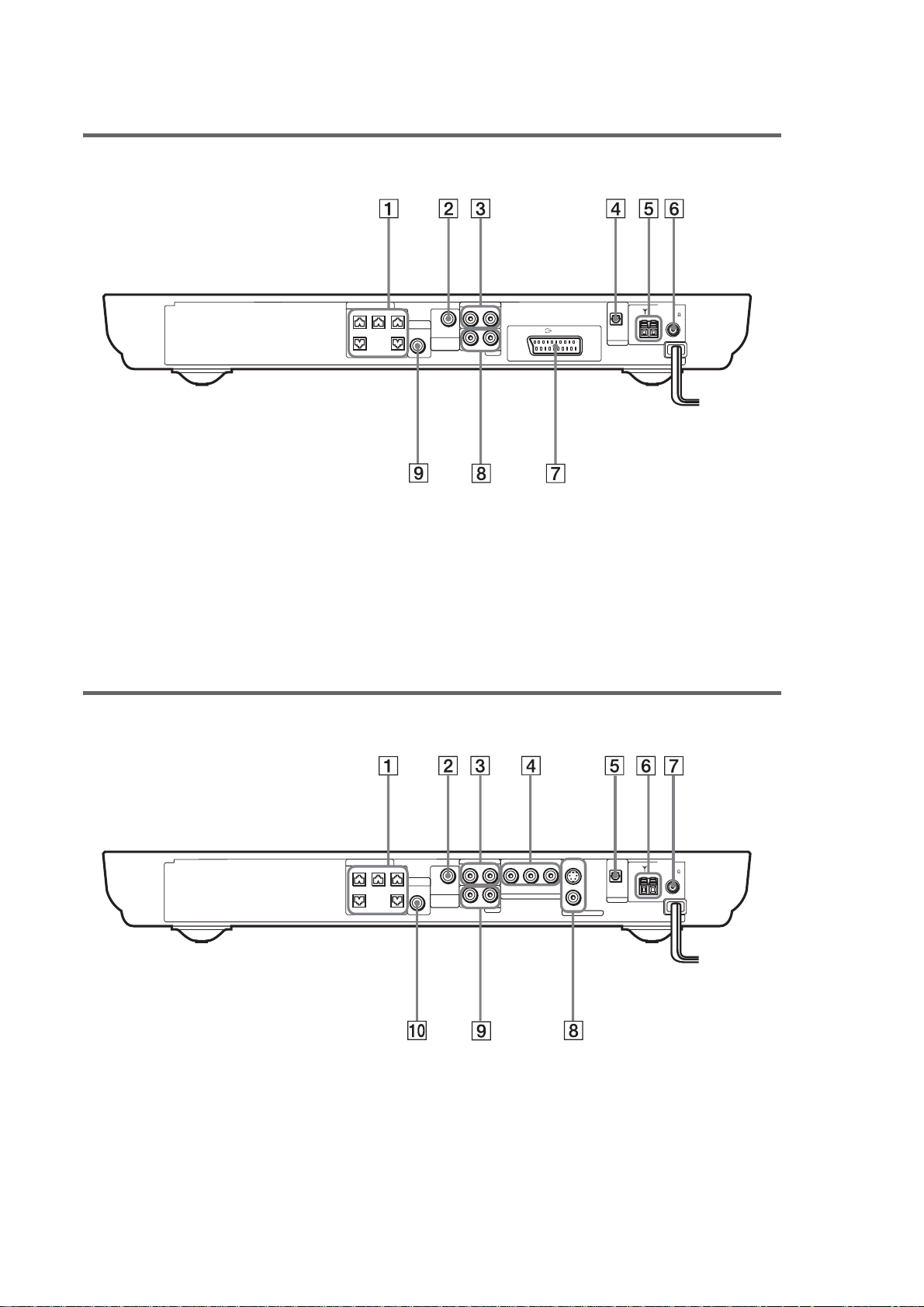

HCD-SR4W

Rear Panel

(European, Russian models)

SPEAKER

A SPEAKER jacks (14)

B SURROUND BACK jack (16)

C VIDEO AUDIO IN (L/R) jacks (21)

D SAT OPTICAL DIGITAL IN jack (22)

E AM terminals (19)

Rear Panel

(Other models)

VIDEO

AUDIO IN

CENTER FRONT LFRONT R

DIR-T1

WOOFERWOOFER

RL

SURROUND

RL

BACK

AUDIO IN

EURO AV OUTPUT(TO TV)

SAT

OPTICAL

DIGITAL IN

SAT

AM

FM 75

COAXIAL

F FM 75 Ω COAXIAL jack (19)

G EURO AV OUTPUT (TO TV) jacks (21)

H SAT AUDIO IN (L/R) jacks (21)

I DIR-T1 jack (14)

A SP EAKER jacks (14)

B SURROUND BACK jack (16)

C VIDEO AUDIO IN (L/R) jacks (21)

D COMPONENT VIDEO OUT jacks (21)

E SA T OPTICA L DIGITAL IN jack (22)

F AM terminals (19)

6

SPEAKER

CENTER FRONT LFRONT R

VIDEO

YP

AUDIO IN

DIR-T1

WOOFERWOOFER

RL

SURROUND

RL

BACK

AUDIO IN

B/CBPR/CR

COMPOMEMT VIDEO OUT

SAT

S VIDEO

(DVD ONLY)

VIDEO

MONITOR OUT

OPTICAL

DIGITAL IN

SAT

AM

FM 75

COAXIAL

G FM 75 Ω COAXIAL jack (19)

H MONITOR OUT (VIDEO/S VIDEO) jacks

(21)

I SAT AUDIO IN (L/R) jacks (21)

J DIR-T1 jack (14)

Page 7

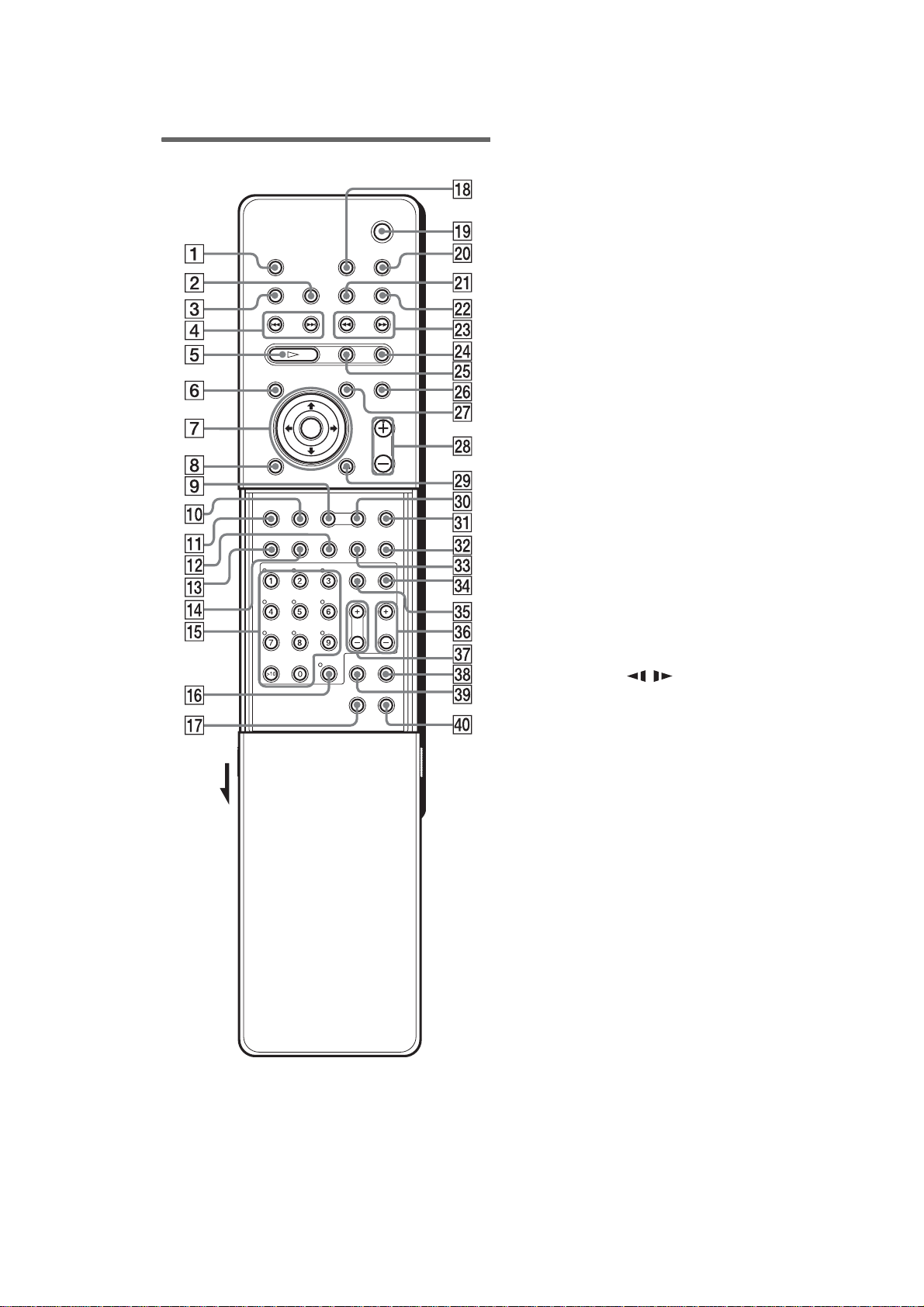

Remote

Open the cover.

Note

This remote control glows in the dark. However,

before glowing, the remote must be exposed to light for

awhile.

HCD-SR4W

AZ (eject)

B DISPLAY

C SLEEP

D ./>, PRESET –/+

E H (play)

F DVD TOP MENU/ALBUM–

G C/X/x/c/ENTER

H DVD DISPLAY

I AUTO FORMAT DIRECT

J DSGX

K DVD SETUP

L SUBTITLE

M AUDIO

N ANGLE

O Number buttons

P ENTER

Q TUNER MENU

R TV [/1 (on/standby)

S "/1 (standby)

T SONY TV DIRECT

U TUNER/BAND

V FUNCTION

W m/M// SLOW, TUNING –/+

X x (stop)

Y X (pause)

Z MUTING

wj DVD MENU/ALBUM+

wk VOL +/–

wl O RETURN

e; MODE

ea NIGHT MODE

es PLAY MODE

ed REPEAT

ef TV

eg TV/VIDEO

eh TV CH +/–

ej TV VOL +/–

ek AMP MENU

el CLEAR

r; FM MODE

7

Page 8

HCD-SR4W

SECTION 3

DISASSEMBLY

•This is can be assemble according to the following sequence.

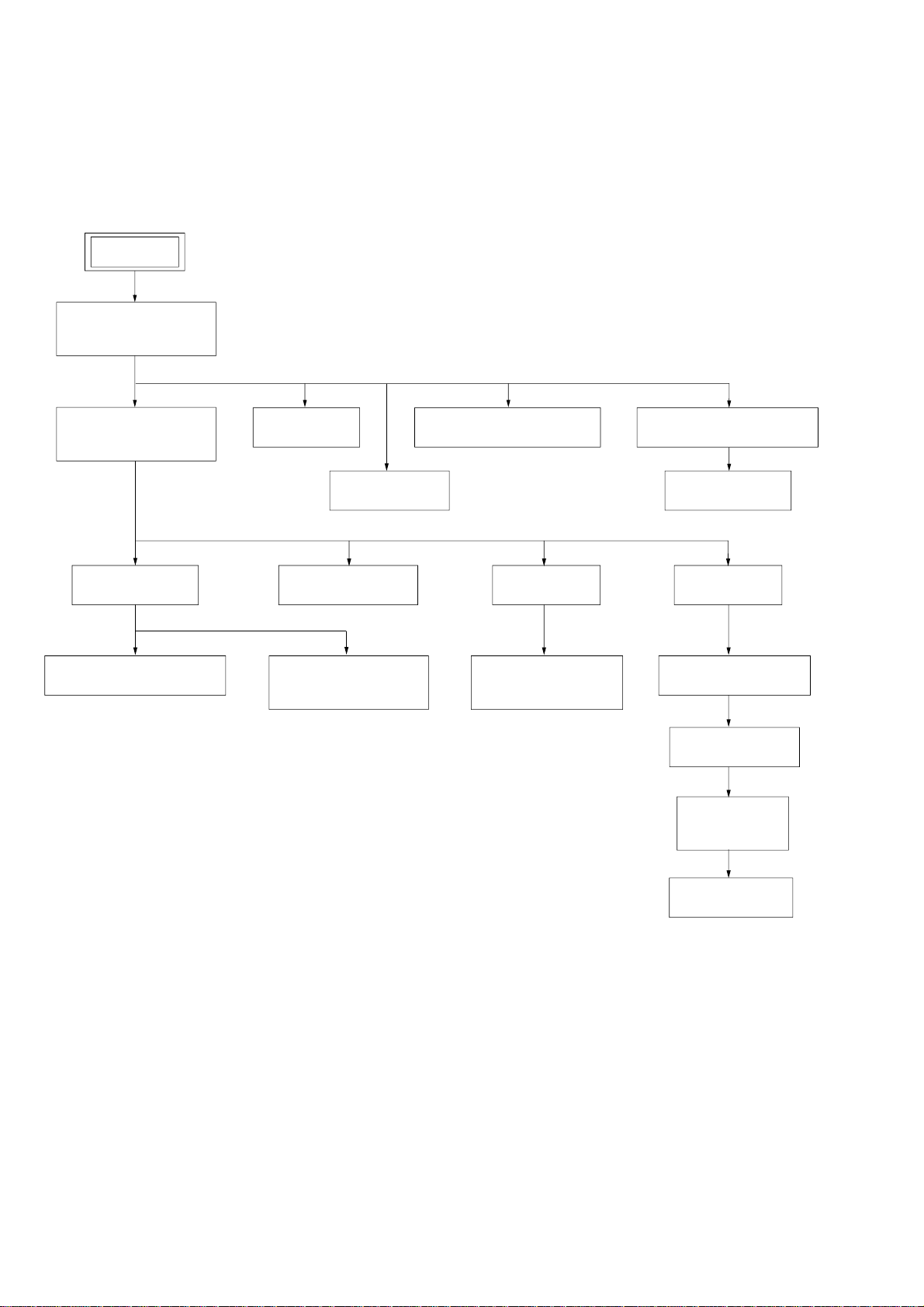

3-1. DISASSEMBLY FLOW

SET

3-2.

SIDE PANEL (R)(L),

FRONT PANEL SECTION

(Page 9)

MECHANISM DECK

3-4.

(CDM80A-DVBU24)

(Page 10)

3-9

. CHASSIS (TOP)

(Page 12)

. LEVER (LOADING R/L)

3-10

(Page 13)

3-

3. FL BOARD

(Page 9)

. AMP BOARD

3-5

(Page 10)

. DRIVER BOARD

3-12

(Page 14)

3-11

. DISC STOP LEVER,

DISC SENSOR LEVER

(Page 14)

SWITCHING REGULATOR

3-6.

(Page 11)

. RF BOARD

3-13

(Page 15)

3-14

. OPTICAL PICK-UP

(DBU-1)

(Page 15)

3-7

. TUNER UNIT, IO BOARD

(Page 11)

. DMB08 BOARD

3-8

(Page 12)

. BASE UNIT

3-15

(Page 16)

3-16

. LEVER (BU LOCK)

(Page 16)

. CLOSE LEVER

3-17

(Page 17)

. DIR LEVER,

3-18

GEAR (IDL-B)

(Page 17)

. GEAR (IDL-C)

3-19

(Page 18)

8

Page 9

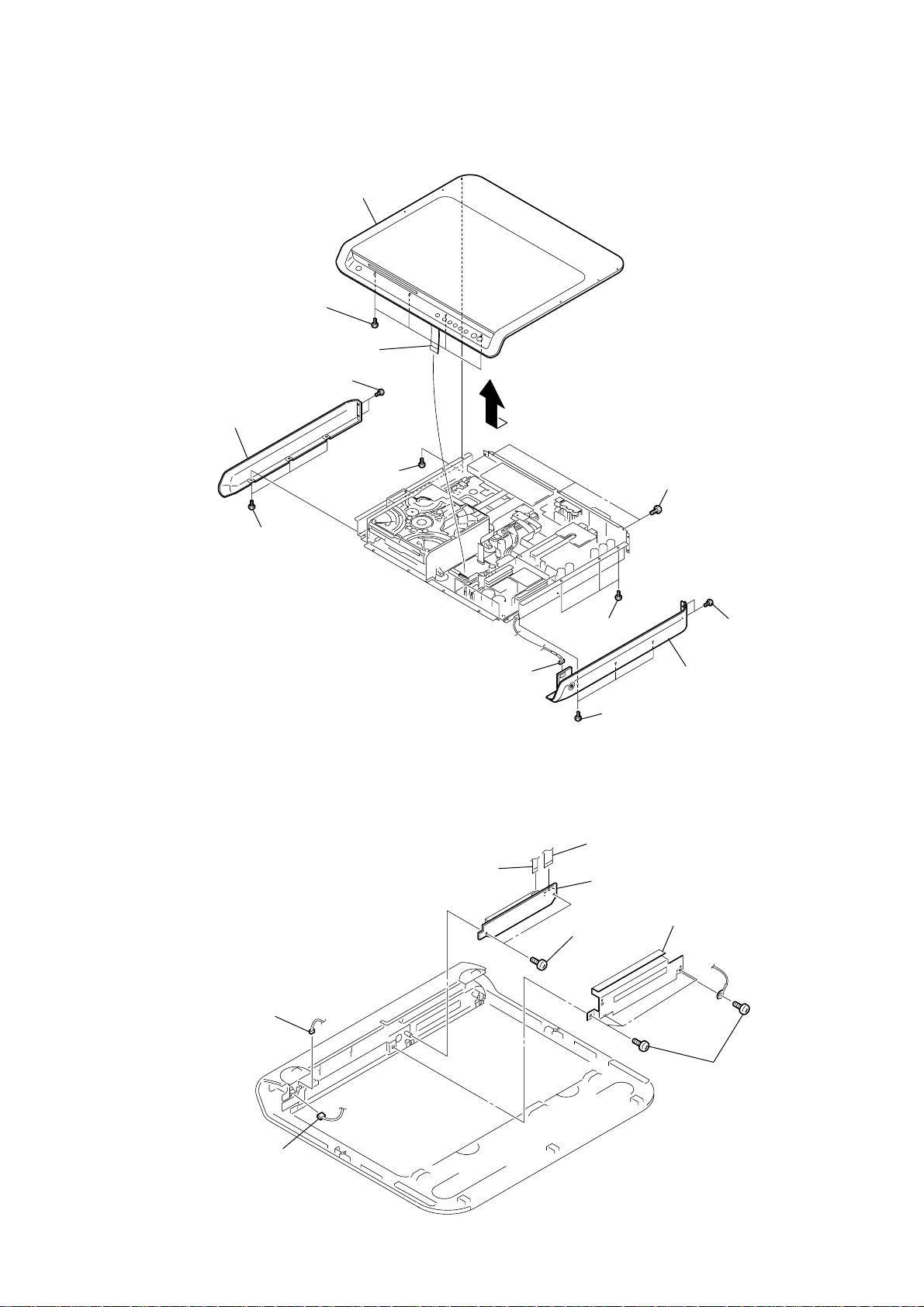

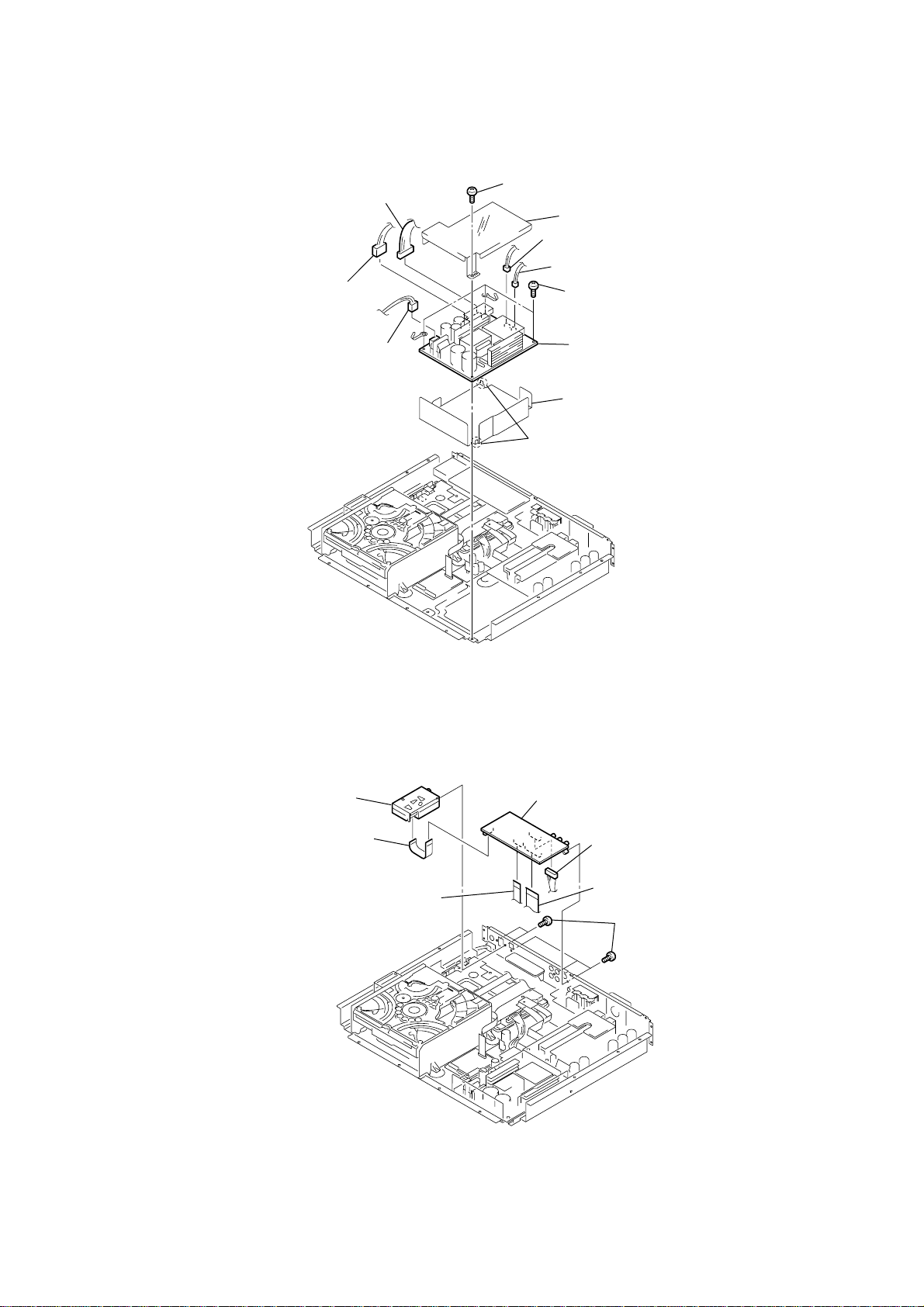

3-2. SIDE PANEL (R)(L), FRONT PANEL SECTION

s

s

qd

front panel section

qa

four screws

(+BV3)

qs

wire (flat type)

(17 core) (CN801)

5

two screws

(+BV3)

7

side panel (L)

q;

three screws

(+BV3)

9

three screws

(+BV3)

HCD-SR4W

3-3. FL BOARD

6

three screws

(+BV3)

3

7

wire (flat type)

(7 core) (CN812)

connector

(5p) (CN811)

8

three screws

(+BV3)

5

2

three screws

(+BV3)

6

wire (flat type)

(17 core) (CN803)

8

FL board

two screws

(+BV3)

4

side panel (R)

2

cover

1

two screw

(+BV3)

3

connector

(2p)

4

connector

(3p)

1

four screw

(+BV3)

9

Page 10

HCD-SR4W

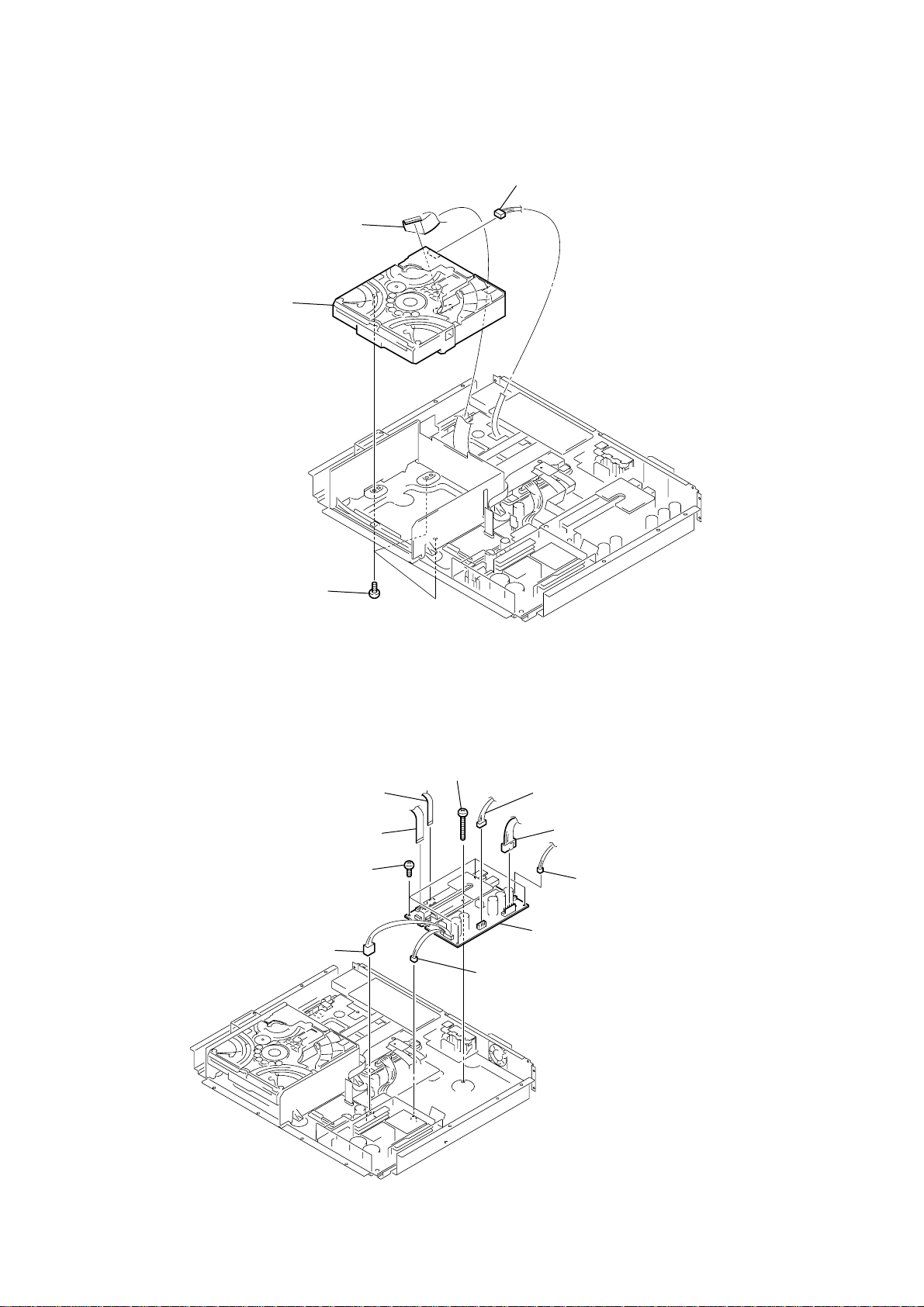

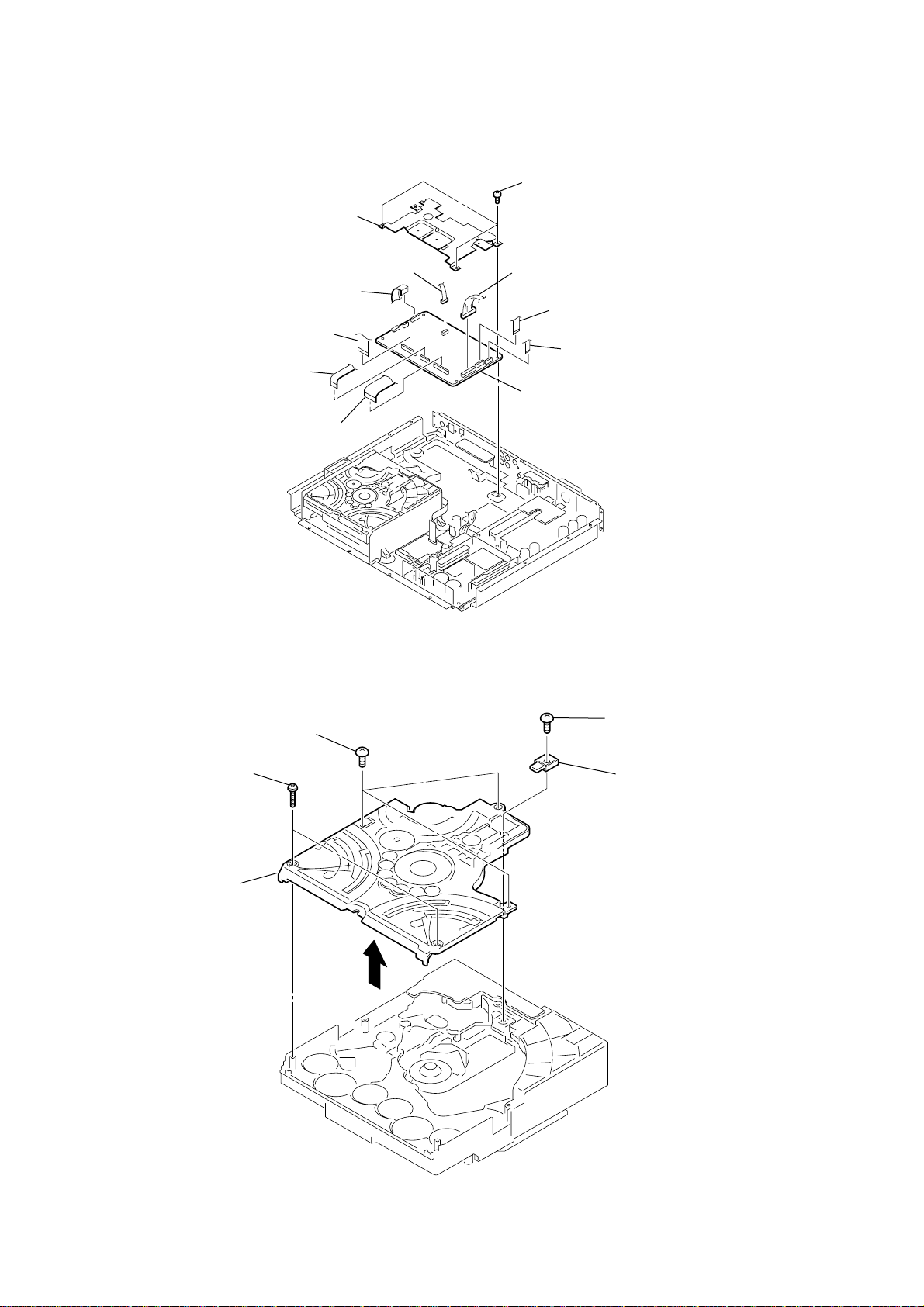

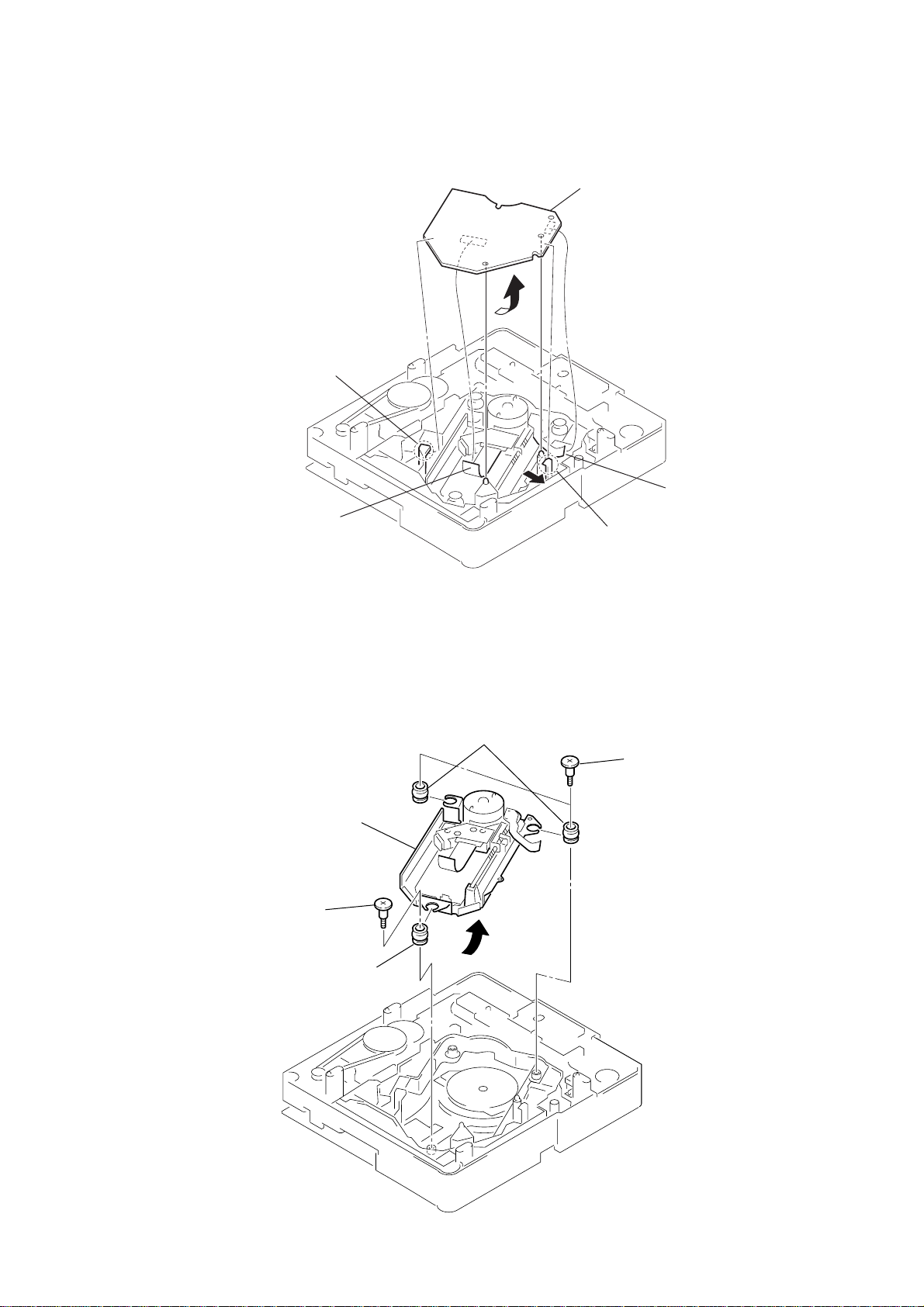

3-4. MECHANISM DECK (CDM80A-DVBU24)

3

wire (flat type)

(29 core)

4

mechanism deck

(CDM80A-DVBU24)

2

connector

(7p) (CN701)

3-5. AMP BOARD

1

three screws

(+BV3)

2

1

3

connector

(4p) (CN4)

wire (flat type)

(9 core) (CN302)

wire (flat type)

(17 core) (CN301)

6

four screws

(+BV3)

5

screw

(+BVTP 3

×

16)

4

connector

(2p) (CN7)

9

connector

(5p) (CN306)

8

connector

(6p) (CN313)

q;

AMP board

7

connector

(2p) (CN300)

10

Page 11

3-6. SWITCHING REGULATOR

6

7

connector

(4p) (CN4)

connector

(12p) (CN8)

8

connector

(2p) (CN3)

1

screw

(+BV3)

2

power sheet (top)

5

connector (2p) (CN7)

4

connector (2p) (CN5)

3

three screws

(+BV3)

qa

switching regulator

q;

power sheet

9

Remove the two solderings.

HCD-SR4W

3-7. TUNER UNIT, IO BOARD

3

tuner unit

2

wire (flat type)

(11 core)

4

wire (flat type)

(15 core) (CN201)

7

IO board

6

connector

(10p) (CN205)

5

wire (flat type)

(29 core) (CN601)

1

five screws

(+BV3)

11

Page 12

HCD-SR4W

)

)

3-8. DMB08 BOARD

5

q;

wire (flat type)

(17 core) (CN005)

9

wire (flat type)

(29 core) (CN401)

3

wire (flat type)

(15 core) (CN003)

2

wire (flat type)

(29 core) (CN002)

bracket (DMB)

1

connector

(7p) (CN007)

4

four screws

(+BV3)

6

connector

(13p) (CN008)

7

qa

DMB08 board

wire (flat type)

(17 core) (CN004)

8

wire (flat type)

(9 core) (CN001

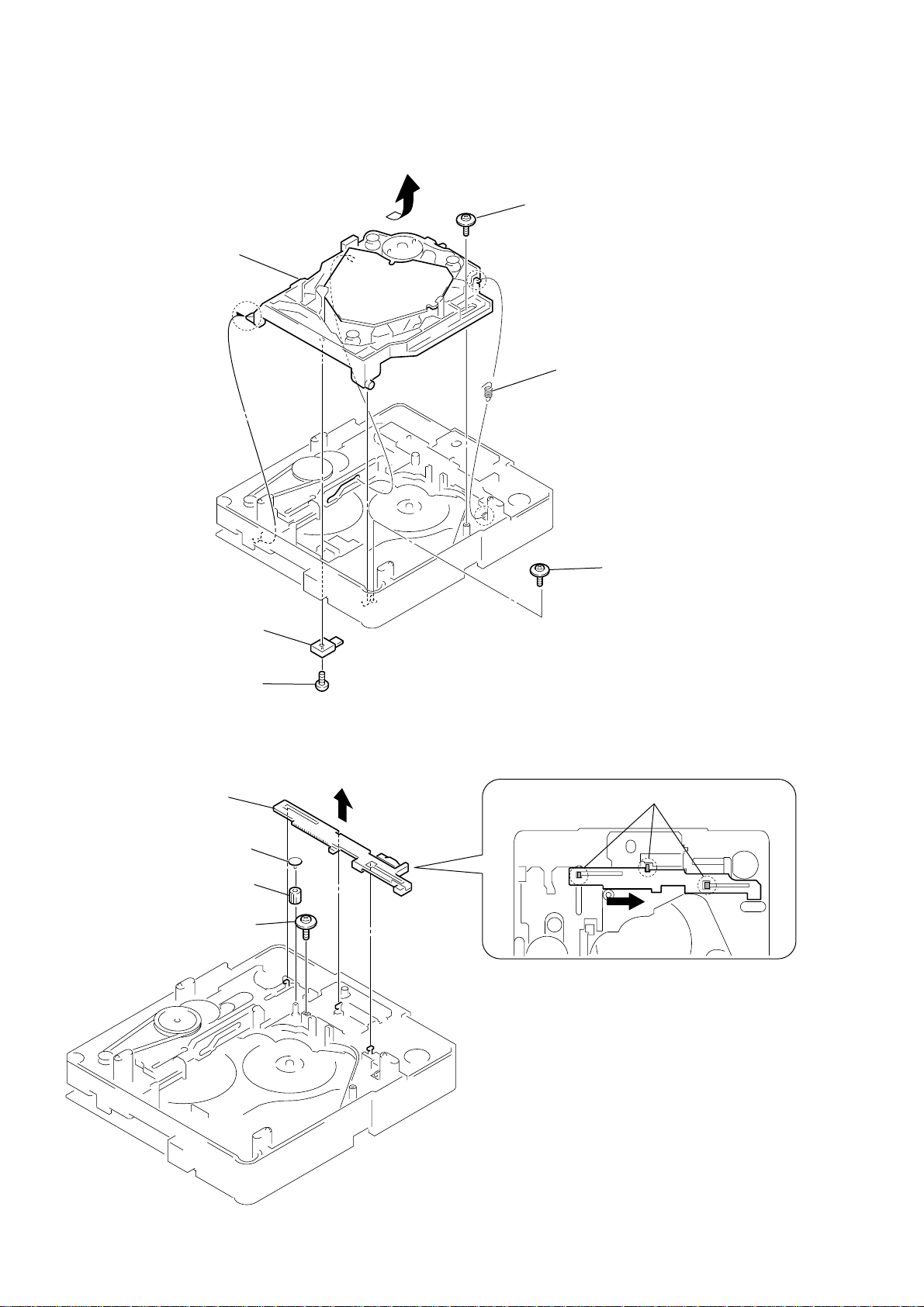

3-9. CHASSIS (TOP)

3

two screws

(+P 2

5

chassis (top)

4

three screws

(+BVTP 2.6

×

10)

1

×

8)

screw

(+BVTP 2.6

2

lever (CL UP2

×

8)

12

Page 13

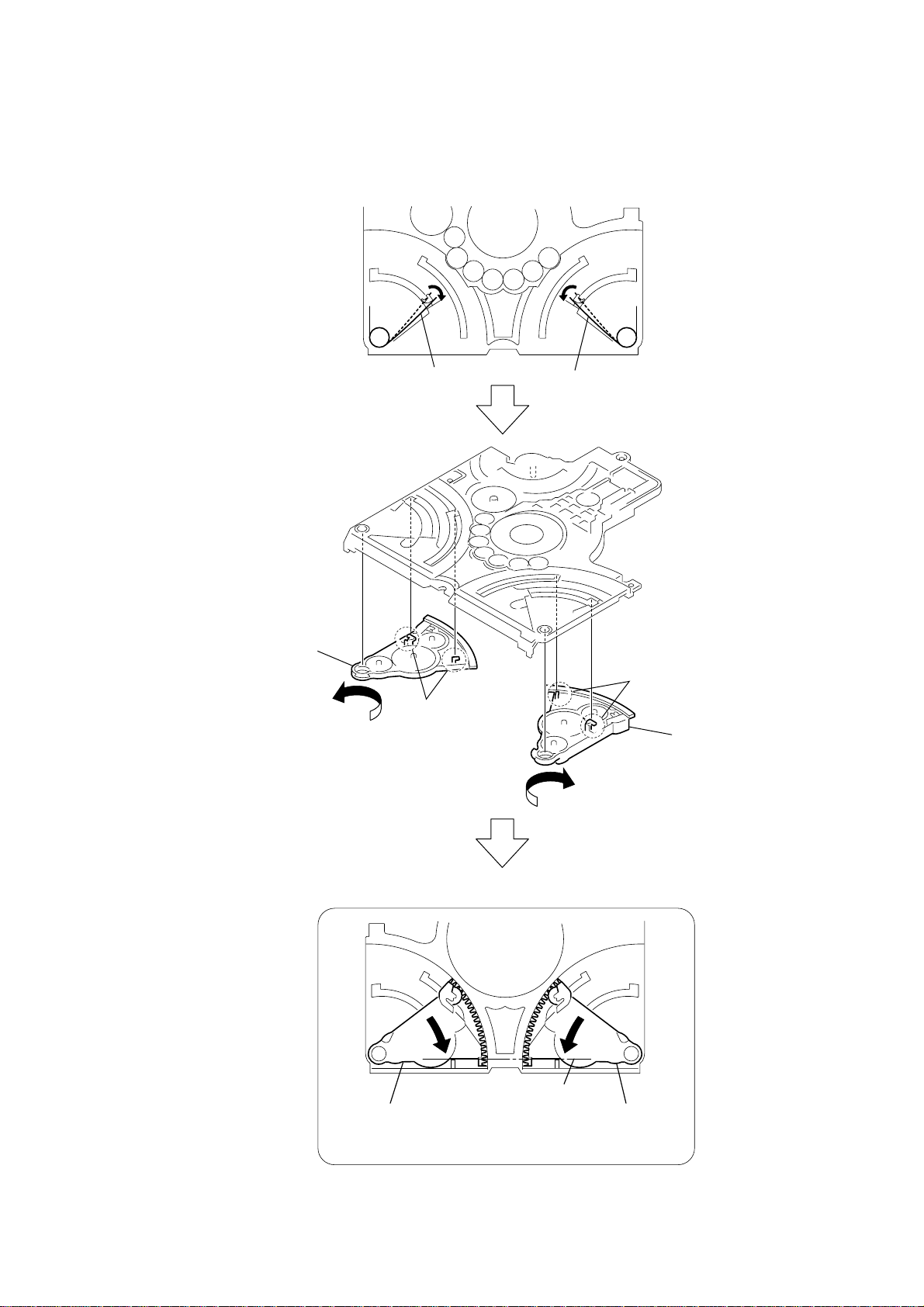

3-10. LEVER (LOADING R/L)

HCD-SR4W

5

lever (loading R)

1

spr-T (loading L) spr-T (loading R)

4

two hooks

1

2

two hooks

3

lever (loading L)

PRECAUTION DURING LEVER (LOADING R / L) INSTALLATION

Align the horizontal position.

lever (loading L)

Install the

both levers so that they move symmetrically.

lever (loading R)

13

Page 14

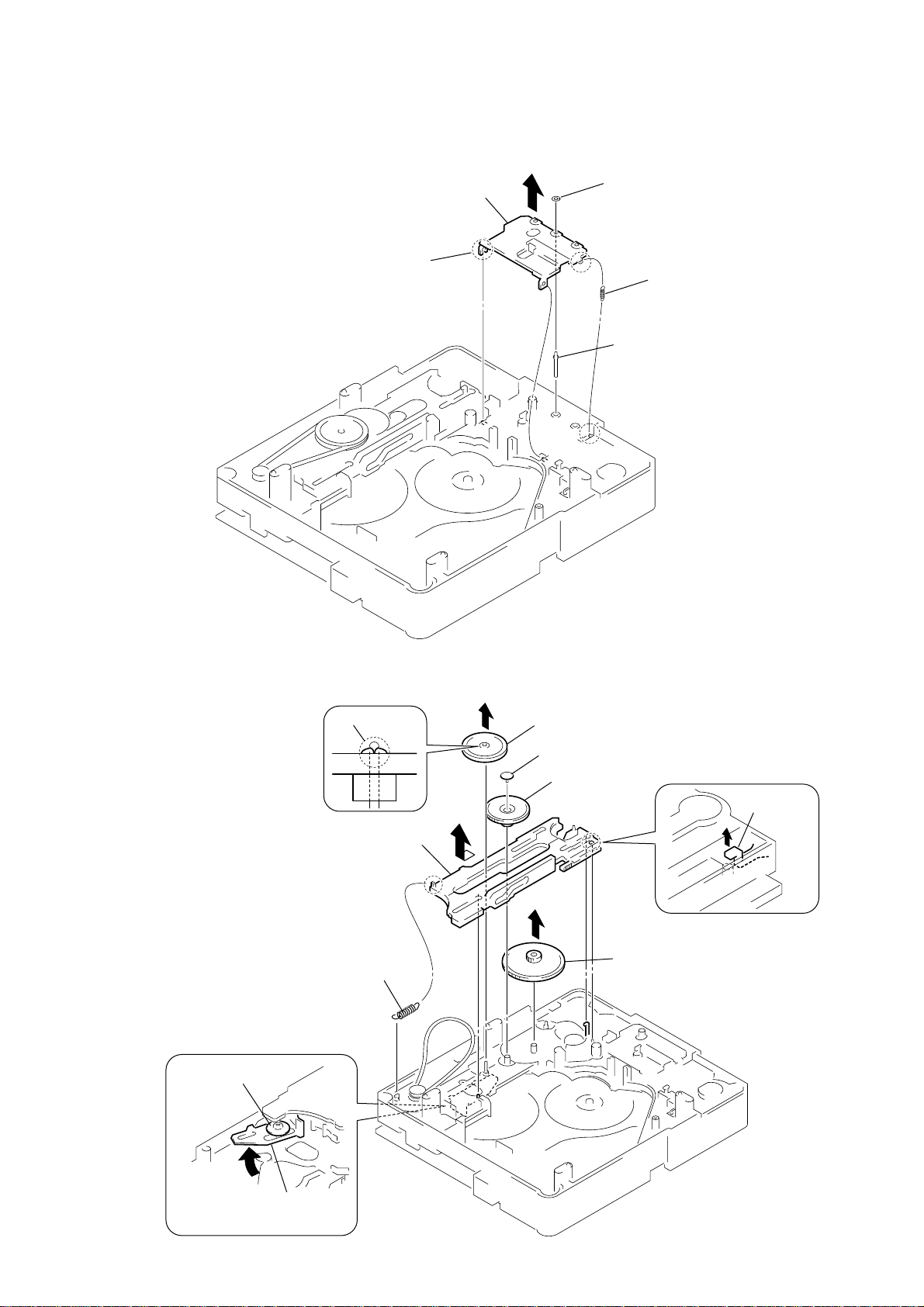

HCD-SR4W

)

3-11. DISC STOP LEVER, DISC SENSOR LEVER

1

gear (cap)

2

gear (IDL L)

PRECAUTION DURING DISC STOP LEVER INSTALLATION

5

two hooks

6

disc stop lever

3-12. DRIVER BOARD

3

Remove soldering

from the two points.

3

two claws

4

disc sensor lever

hole

hole

Install the disc stop lever so that the both holes

are aligned.

2

three screws

(+BVTP 2.6

5

DRIVER board

chassis (top)

disc stop lever

×

8

14

4

motor (pully) assy

1

belt (MOT)

Page 15

3-13. RF BOARD

)

2

claw

5

RF board

HCD-SR4W

4

wire (flat type)

(CN001)

3-14. OPTICAL PICK-UP (DBU-1)

5

optical pick-up

(DBU-1)

2

step screw (M)

3

two insulators

3

wire (flat type)

(CN003)

1

claw

1

two step screws (M

4

insulator

15

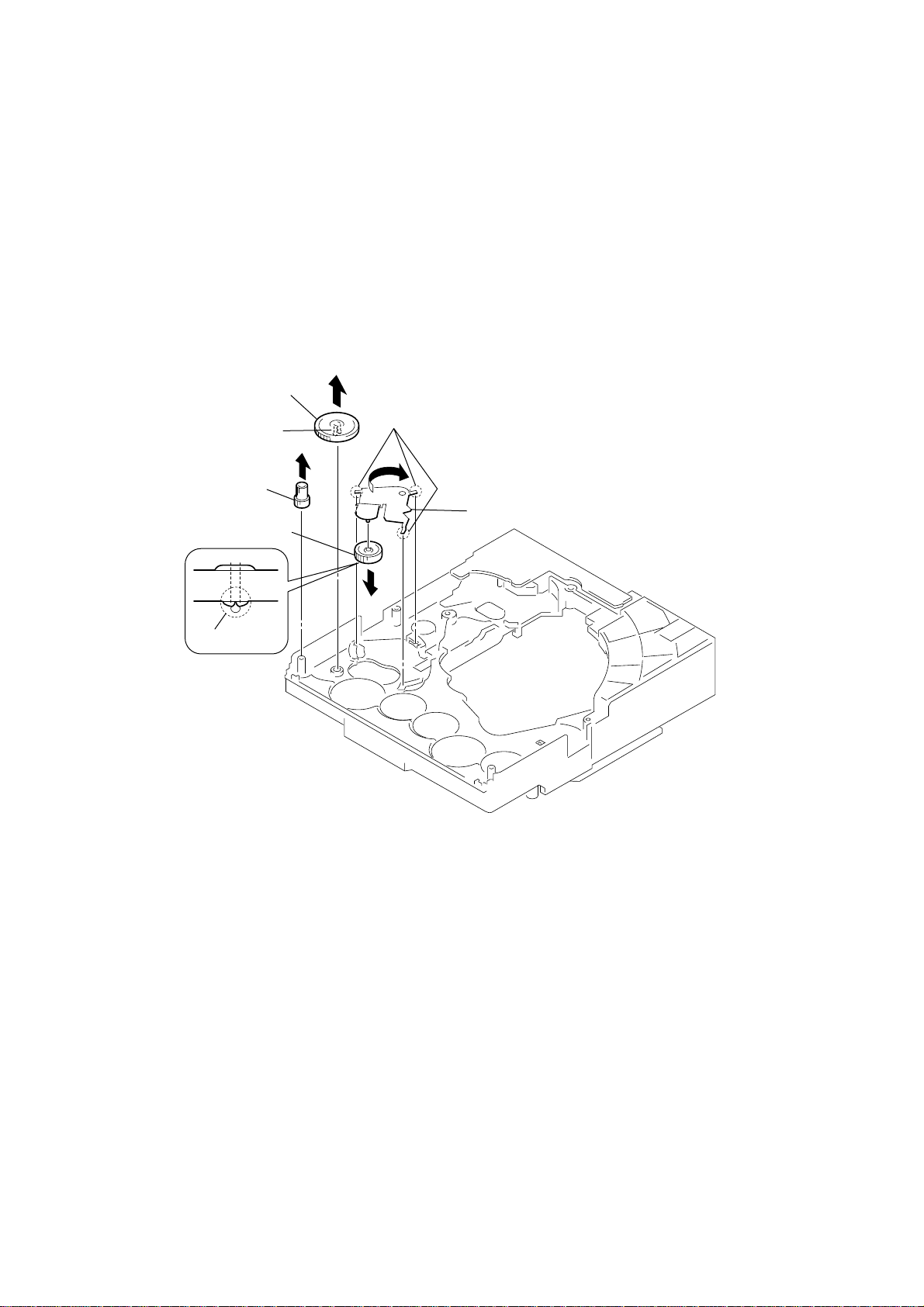

Page 16

HCD-SR4W

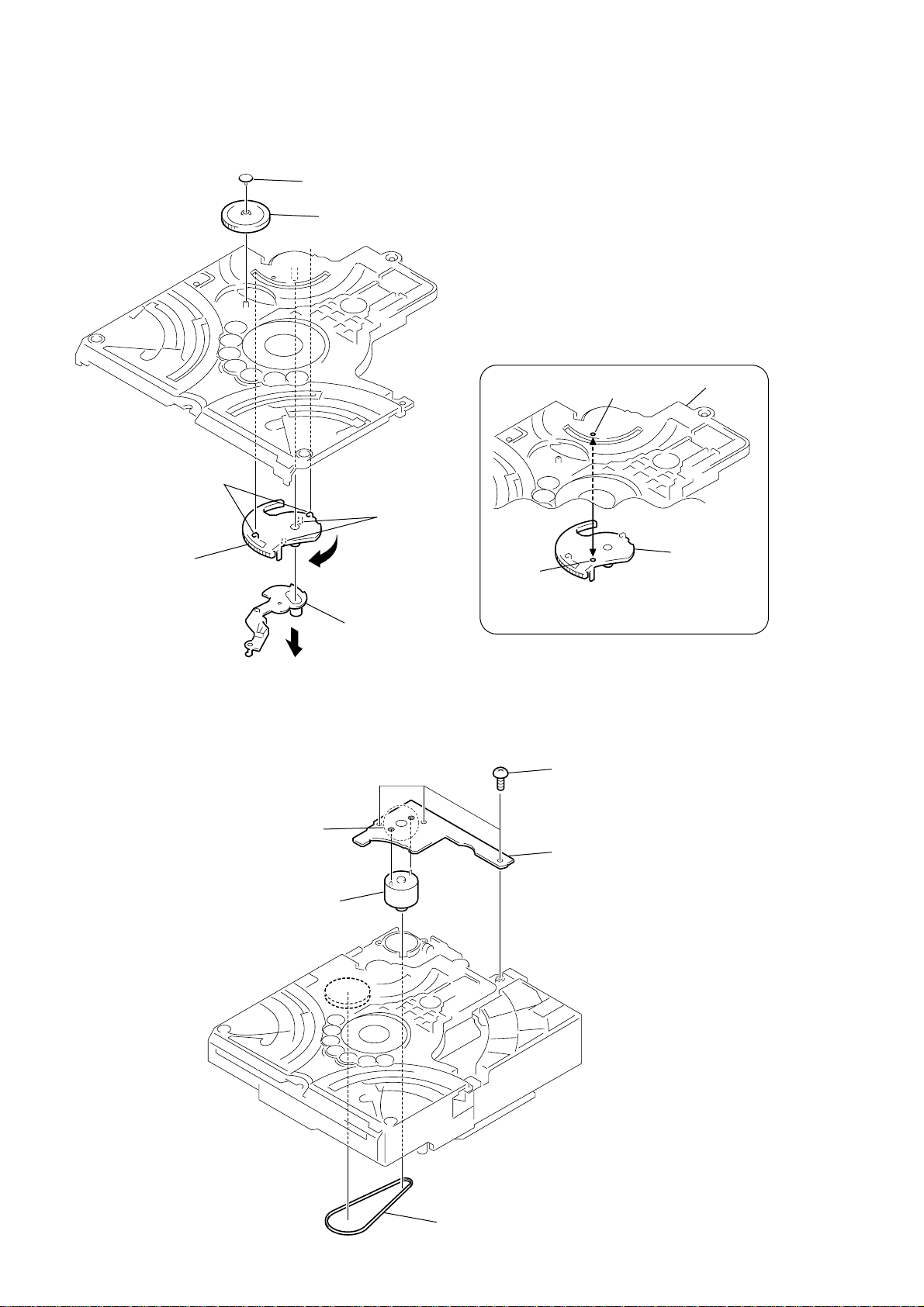

3-15. BASE UNIT

6

base unit

4

floating screw

(+PTPWHM 2.6)

3

holder down spring

2

lever (CL UP2)

1

screw

(+BVTP 2.6

3-16. LEVER (BU LOCK)

6

lever (BU lock)

1

gear (cap)

2

gear (BU lock)

3

floating screw

(+PTPWHM 2.6)

5

floating screw

(+PTPWHM 2.6)

×

8)

5

three hooks

4

16

Page 17

3-17. CLOSE LEVER

3

5

claw

close lever

1

washer (3-1-0.4)

2

4

shaft disc stop

HCD-SR4W

close lever spring

3-18. DIR LEVER, GEAR (IDL-B)

1

6

Loosen the screw.

2

claw

9

DIR lever

DIR spring

3

gear puley

4

gear (cap)

5

gear (IDL-A)

q;

gear (IDL-B)

8

stopper

7

Hold the release lever

and change the direction.

17

Page 18

HCD-SR4W

3-19. GEAR (IDL-C)

3

gear (IDL-D)

2

two claws

4

three hooks

1

gear (IDL-F)

7

6

gear (IDL-C)

claw

5

gear loading lever

18

Page 19

SECTION 4

TEST MODE

HCD-SR4W

[Version Display Mode]

*The software version is displayed.

Procedure:

1. Press three buttons of [VOLUME -], [VOLUME +] and A simultaneously for two seconds.

2. The message “VERSION” is displayed. The version display

mode is activated.

3. Press the > button. “IF ***” is displayed.

4. Each time the > button is pressed, the display changes in

the order of DVD, AREA, VERSION and IF.

5. To exit from this mode, press the ?/1 button.

[Key T est Mode]

* Button check

Procedure:

1. Press three buttons of [VOLUME -], [VOLUME +] and [FUNCTION] simultaneously.

2. The message “KEY NUM 0” is displayed and “0” blinks.

3. Each time a button is pressed, “KEY NUM 0” value increases.

However, once a button is pressed, it is no longer taken into

account.

4. When all buttons are pressed, “KEY NUM 9” appears and the

number blinking is stopped.

5. To exit from this mode, disconnect the power cord.

[Display T est Mode]

Procedure:

1. Press three buttons of [VOLUME -], . and A simulta-

neously.

2. All segments are turned on.

TITLE TRK CHAP SLEEP NTSC TUNED ST MONO NIGHT

CD MULTIPBC

ALBM

1

SB

DSGX

kHz D

a

MHz PL II

a

DTS-ES NEO:6

ALL1DISC S PGM

ALBM SHUF REP

MP3 JPEG

-

SA

3. When the > button is pressed, the display will light up as

follows.

ALL1DISC S PGM

ALBM SHUF REP

MP3 JPEG

-

CD MULTIPBC

SA

ALBM TITLE TRK CHAP SLEEP NTSC TUNED ST MONO NIGHT

1

DSGX

SB

kHz D

a

MHz PL II

a

DTS-ES NEO:6

4. Press the > button and confirm the display.

[Cold Reset]

* The cold reset clears all data including preset data stored in

the RAM to initial conditions. Execute this mode when

returning the set to the customers.

Procedure:

1. Press the ?/1 button to turn the power on.

2. Press three buttons of . , HX and A simultaneously.

3. When this button is operated, display as “COLD RESET” for

a while and all of the settings are reset.

[Disc Slot Lock]

The disc slot lock function for the antitheft of an demonstration

disc in the store is equipped.

Setting Procedure:

1. Turn the set on.

2. Press two buttons of x and A simultaneously for five sec-

onds.

3. The message “LOCKED” is displayed and the slot is locked.

Releasing Procedure:

1. Press two buttons of x and A simultaneously for five sec-

onds again.

2. The message “UNLOCKED” is displayed and the slot is

unlocked.

Note : When “LOCKED” is displayed, the slot lock is not released by

turning power on/off with the ?/1 button.

[Repeat Limit Release Mode]

Procedure:

1. Press three buttons of A , > and [VOLUME+] simulta-

neously.

2. Repeat limit is released.

DEC

EX

[CDM Ship Mode]

*This mode moves the optical pick-up to the position durable

to vibration. Use this mode when returning the set to the

customer after repair.

Procedure:

1. Turn the set on.

DEC

EX

2. Set the function to DVD.

3. Press three buttons of > , . and A simultaneously.

4. The message “MECHA LOCK” is displayed.

5. The CDM ship mode is set.

5. Press the > button, all segments are turned off.

6. Every pressing of the > button turns on each segments in

the same order.

7. To exit from this mode, press the ?/1 button.

19

Page 20

HCD-SR4W

[GENERAL DESCRIPTION]

The T est Mode allows you to make dia gnosis and adjustment easily

using the remote commander and monitor TV. The instructions,

diagnostic results, etc. are given on the on-screen display (OSD).

[TEST DISC LIST]

Use the following test disc on test mode.

TDV-520CSO (DVD-SL) : PART No. J-2501-236-A

LUV-P01 (CD) : PART No. 4-999-032-01

TDV-540C (DVD-DL) : PART No. J-2501-235-A

Note: Do not use exiting test disc for DVD.

[STARTING TEST MODE]

1. Press the @/1 button to turn the power on, and set the function

to DVD.

2. Press three buttons of A , x and [VOLUME+] simultaneously

to enter the test mode.

3. It displays “SERVICE IN” on the fluorescent indicator tube,

and displays the Test Mode Menu on the monitor screen as

follows. (At the bottom of the menu screen, the model name

and revision number are displayed)

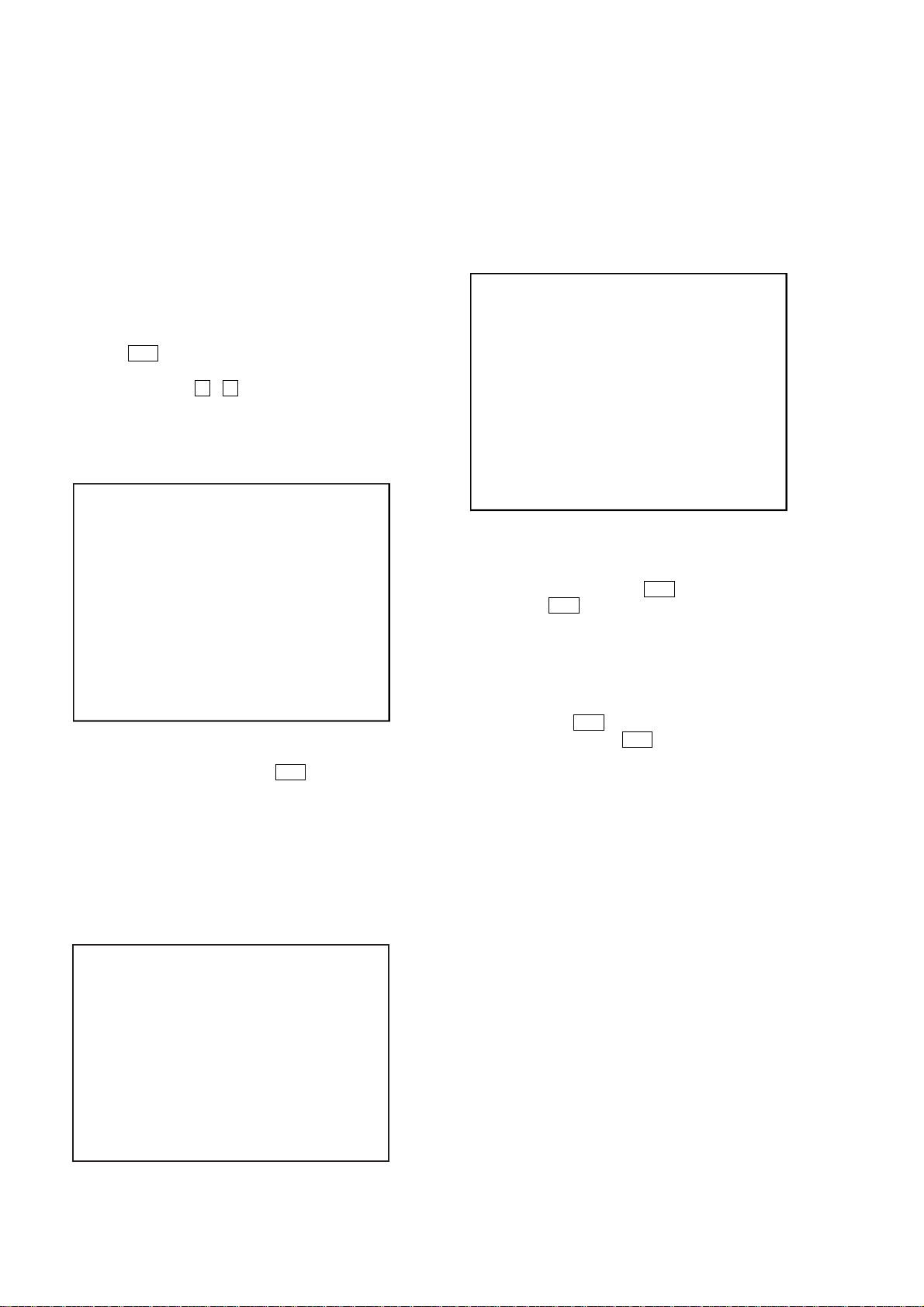

Test Mode Menu

0. Syscon Diagnosis

1. Drive Auto Adjustment

2. Drive Manual Operation

3. Mecha Aging

4. Emergency History

5. Mecha Error History

6. Version Information

7. Video Level Adjustment

Exit: POWER Key

Model :DAV-xxx xx

Revision :x.xx

4. To execute each function, select the desired menu and press

its number on the remote commander (RM-SP320).

5. To release from test mode, press the @/1 button and turn the

power off.

[OPERATING TEST MODE]

0. SYSCON DIAGNOSIS

The same contents as board detail check by serial interface can be

checked from the remote commander operation.

On the Test Mode Menu screen, press [0] key on the remote

commander, and the following Check Menu will be displayed.

### Syscon Diagnosis ###

Check Menu

0. Quit

1. All

2. Version

3. EEPROM

4. GPIO

5. SD Bus

6. Video

0-0. Quit

Quit the Syscon Diagnosis and return to the Test Mode Menu.

0-1. All (All items continuous check)

This menu checks all diagnostic items continuously. Normally, all

items are checked successively one after another automatically

unless an error is found, but at a certain item that requires judgment

through a visual check to the result, the following screen is displayed

for the key entry.

• Example display

### Syscon Diagnosis ###

Diag All Check

No.2 Version

2-2. Version

ROM Revision = x.xx

Press NEXT Key to Continue

Press PREV Key to Repeat

For the ROM Check, the check sum calculated by the Syscon is

output, and therefore you must compare it with the specified value

for confirmation.

Following the message, press the > button to go to the next

item, or press the . button to repeat the same operation again.

To quit the diagnosis and return to Check Menu screen, press the

[RETURN] key on the remote commander to display Check Menu.

• Error occurred

If an error occurred, the diagnosis is suspended and error is displayed.

Press the [RETURN] key on the remote commander to quit the

diagnosis, or press the . button to repeat the same check where

an error occurred, or press the > button to continue the check

from the item next to faulty item.

General Description of Checking Method

Selecting 2 and subsequent items calls the submenu screen of each

item. And selecting 2 and subsequent items executes respective

menus and outputs the results.

For the contents of each submenu, see “Check Items List” as below .

Check Items List:

0-2. Version

0-2-1. All

0-2-2. Revision

0-2-3. ROM Check Sum

0-2-4. Model Type

0-2-5. Region

0-3. EEPROM Check

0-3-1. Sampling Check

0-3-2. Detail Check

0-4. GP I/O Check

0-5. SD Bus Check

0-6. Video Check

0-2. Version

0-2-2. Revision

The revision number of ROM (IC205) that the program

for the DVD system processor (IC206) is stored.

0-2-3. ROM Check Sum

Check sum is calculated. (4 digits hexadecimal number)

20

Page 21

HCD-SR4W

0-2-4. Model Type

Model name is displayed. (DAV-SR4W)

0-2-5. Region

Model destination code is displayed. (2 digits number)

0-3. EEPROM Check

0-3-1. Sampling Check

EEPROM check at every 64 words.

It compares read data with write data of each address.

When there are discrepancies between two data, it displays

error.

0-3-2. Detail Check

EEPROM check at every 1 word.

It compares read data with write data of each address.

When there are discrepancies between two data, it displays

error.

0-4. GP I/O Check

Pull up/down setting check of the DVD system processor (IC206)

pin 150, 151 and 154 (for clock setting port).

0-5. SD Bus Check

SD bus data check between DVD decoder (IC701) and D-RAM

(IC706).

0-6. Video Check

Output the color bars for video level adjustment.

1. DRIVE AUTO ADJUSTMENT

On the Test Mode Menu screen, press the [1] key on the remote

commander, and the Adjustment Menu will be displayed.

## Drive Auto Adjustment ##

Adjustment Menu

0. ALL

1. DVD-SL

2. CD

3. DVD-DL

1-1. DVD-SL (single layer)

Press the [1] key on the remote commander and insert a D VD single

layer disc following the message. Then the adjustment will be made

through the steps below, then adjusted values will be written to the

EEPROM.

DVD Single Layer Disc Adjustment Steps:

1. Sled tilt reset

2. Disc check memory SL

3. Wait 300 msec

4. Set disc type SL

5. LD on

6. Spindle start

7. Wait 1 sec

8. Focus servo on 0

9. Auto track offset adjust

10. CLVA on

11. Wait 500 msec

12. Tracking on

13. Wait 1 sec

14. Sled on

15. Check CLV on

16. Auto LFO adjust

17. Auto focus offset adjust

18. Auto tilt position adjust

19. Auto focus gain adjust

20. Auto focus offset adjust

21. EQ boost adjust

22. Auto loop filter offset adjust

23. Auto track gain adjust

Search Check

24. 32 track jump forward

25. 32 track jump reverse

26. 500 track jump forward

27. 500 track jump reverse

28. All servo stop

29. EEP copy loop filter offset

1-2. CD

Press the [2] key on the remote commander and insert a CD disc

following the message. Then the adjustment will be made through

the steps below , then adjusted values will be written to the EEPR OM.

Exit: RETURN

Normally, [0] is selected to adjust D VD (single layer), CD and DVD

(dual layer) in this order. But, individual items can be adjusted for

the case where adjustment is suspended due to an error. In this mode,

the adjustment can be made easily through the operation following

the message displayed on the screen.

The disc used for adjustment must be the one specified for

adjustment.

1-0. ALL

Press the [0] key on the remote commander, and the servo set data

in EEPROM will be initialized. Then, 1. DVD-SL disc, 2. CD disc

and 3. DVD-DL disc are adjusted in this order.

Each time one disc was adjusted, it is ejected. Replace it with the

specified disc following the message. Y ou can finish the adjustment

by pressing the [RETURN] button on the remote commander.

Note: During adjustment of each disc, the measurement for disc type

judgment is made. As automatic adjustment does not judge the disc

type unlike conventional models, take care not to insert wrong type

discs. Also, do not give a shock during adjustment.

CD Adjustment Steps

1. Sled tilt rest

2. Disc check memory CD

3. Wait 500 msec

4. Set disc type CD

5. LD on

6. Spindle start

7. Wait 500 msec

8. Focus servo on 0

9. Auto track offset adjust

10. CLVA on

11. Wait 500 msec

12. Tracking on

13. (TC display start)

14. Wait 1 sec

15. Jitter display start

16. Sled ON

17. Check CLV on

18. Auto loop filter offset adjust

19. Auto focus offset adjust

20. Auto focus gain adjust

21. Auto focus offset adjust

22. EQ boost adjust

23. Auto LFO Adjust

21

Page 22

HCD-SR4W

24. Auto track gain adjust

Search Check

25. 32Tj forward

26. 32Tj reverse

27. 500Tj forward

28. 500Tj reverse

29. All servo stop

1-3. DVD-DL (dual layer)

Press the [3] key on the remote commander and insert a DVD dual

layer disc following the message. Then the adjustment will be made

through the steps below, then adjusted values will be written to the

EEPROM.

DVD Dual Layer Disc Adjustment Steps:

1. Sled tilt reset

2. Disc check memory DL

3. Wait 500 msec

4. Set disc type DL

5. LD on

6. Spindle start

7. Wait 1 sec

Layer 1 Adjust

8. Focus servo on 0

9. Auto track offset adjust

10. CLVA on

11. Wait 500 msec

12. Tracking on

13. Wait 500 msec

14. Sled on

15. Check CLV lock

16. Auto loop filter offset adjust, Auto focus adjust

17. Auto focus gain adjust

18. Auto focus offset adjust

19. EQ boost adjust

20. Auto loop filter offset adjust

21. Auto Track Gain Adjust

Search Check

22. 32 track jump forward

23. 32 track jump reverse

24. 500 track jump forward

25. 500 track jump reverse

Layer 0 Adjust

26. Focus jump (L1 t L0)

27. Auto track offset adjust L0

28. CLVA on

29. Wait 500 msec

30. Tracking on

31. Wait 500 msec

32. Sled on

33. Check CLV lock

34. Auto focus filter offset adjust

35. Auto Focus Adjust

36. Auto focus gain adjust

37. Auto focus offset adjust

38. EQ boost adjust

39. Auto Loop Filter Offset

40. Auto track gain adjust

Search Check

41. 32 track jump forward

42. 32 track jump reverse

43. 500 track jump forward

44. 500 track jump reverse

Layer Jump Check

45. Layer jump (L0 t L1)

46. Layer jump (L1 t L0)

47. All servo stop

2. DRIVE MANUAL OPERATION

Note: This mode is used for design, and not used in service fundamentally.

On the Test Mode Menu screen, press the [2] key on the remote

commander, and the Operation Menu will be displayed. For the

manual operation, each servo on/off control and adjustment can be

executed manually.

## Drive Manual Operation ##

Operation Menu

1. Disc Type

2. Servo Control

3. Track/Layer Jump

4. Non EEPROM Write Adjust

5. EEPROM Write Adjust

6. Memory Check

7. Disc Check Memory

8. Error Rate Display

9. SACD Water Mark

Exit: RETURN

In using the manual operation menu, take care of the following

points. These commands do not provide protection, thus requiring

correct operation. The sector address or time code field is displayed

when a disc is loaded.

Note:

1. Set correctly the disc type to be used on the Disc

Type screen.

2. In case of an alarm, immediately press the x button

to stop the servo oper ation, and press the +/1 but ton to turn the power off.

Basic operation:

(controllable from front panel or remote commander)

@/1 :Power OFF (release the Test Mode)

x : Servo stop

Z : Stop and eject

[RETURN] : Return to Operation Menu or T est Mode Menu

. , > :Transition between sub modes of menu

[1] to [9], [0] : Selection of menu items

Cursor o/

: Increase/Decrease in manually adjusted value

O

22

Page 23

HCD-SR4W

Servo Control

1.LD off R.Sled FWD

2.Focus off L.Sled REV

3.SPDL off U.Sled Reset

4.CLVA off D.Sled Limit

5.Trk. off

6.Sled off

7.Fcs.Srch off

0.All Servo Off

Exit: RETURN

2-1. Disc Type

Disc Type

Disc Type Select

1. Disc Type Auto Check

2. Set Disc Type DVD

3. Set Disc Type CD

4. Set Disc Type Hybrid

Exit: RETURN

2-1-1. Disc Type Auto Check

1) Press the [1] key on the remote commander to display the Disc

Type Auto Check screen.

2) Insert a disc and press the [ENTER] key on the remote com-

mander.

3) It judges the type of inserted disc automatically and displays

the disc type and so on as below.

Disc Type Auto Check

2-1-3. Disc Type CD

It sets up so that it may judge as a disc type of specification of the

disc with which the set was inserted.

[1]: CD disc (normal speed, 12 cm)

[2]: CD disc (double speed, 12 cm)

[3]: CD disc (normal speed, 8 cm)

[4]: CD disc (double speed, 8 cm)

[5]: CD-RW disc (normal speed, 12 cm)

[6]: CD-RW disc (double speed, 12 cm)

[7]: CD-RW disc (normal speed, 8 cm)

[8]: CD-RW disc (double speed, 8 cm)

2-1-4. Disc Type Hybrid

It sets up so that it may judge as a disc type of specification of the

disc with which the set was inserted.

[1]: SACD Hybrid disc (SACD layer, 12 cm)

[2]: SACD Hybrid disc (CD layer, normal speed, 12 cm)

[3]: SACD Hybrid disc (CD layer, double speed, 12 cm)

[4]: SACD Hybrid disc (SACD layer, 8 cm)

[5]: SACD Hybrid disc (CD layer, normal speed, 8 cm)

[6]: SACD Hybrid disc (CD layer, double speed, 8 cm)

2-2. Servo Control

Note: Be sure to perform the disc type setup befor eperforming this item.

Disc Type xx

Layer xx

Mirr Time xx

Mirr Count xx

FZC Count xx

PI Reference xx

PI Peak xx

ENTER.Execute

Disc Type : CD, DVD or Hybrid (SACD)

Layer : SINGLE, DUAL or HYBRID

Mirr Time : Mirror time of between disc surface and record

surface when disc type judgment. (hexadecimal

number)

Mirr Count : The number of times which mirror counts between

disc surface and record surface when disc type

judging. (hexadecimal number)

FZC Count : The number of times which focus zero cross points

of each layer when lens down. (hexadecimal

number)

PI Reference : The average of PI reference voltage. (hexadecimal

number)

PI Peak : PI peak level voltage. It performs only when disc

type judgment is successful. (hexadecimal number)

2-1-2. Disc Type DVD

It sets up so that it may judge as a disc type of specification of the

disc with which the set was inserted.

[1]: DVD single layer disc (12 cm)

[2]: DVD dual layer disc (0 layer, 12 cm)

[3]: DVD dual layer disc (1 layer, 12 cm)

[4]: DVD-RW disc (12 cm)

[5]: DVD single layer disc (8 cm)

[6]: DVD dual layer disc (0 layer, 8 cm)

[7]: DVD dual layer disc (1 layer, 8 cm)

Exit: RETURN

On this screen, the servo on/off control necessary for replay is

executed. Normally, turn on each servo from 1 sequentially and

when CLVA is turned on, the usual trace mode becomes active. In

the trace mode, DVD sector address or CD time code is displayed.

This is not displayed where the spindle is not locked.

The spindle could run overriding the control if the spindle system is

faulty or RF is not present. In such a case, do not operate CLVA.

[1] LD : Turn on/off the laser.

[2] Focus : Search the focus and turn on the focus.

[3] SPDL : Turn on/off the spindle.

[4] CLVA : Turn on/off normal servo of spindle servo.

[5] Trk. : Turn on/off the tracking servo.

[6] Sled : Turn on/off the sled servo.

[7] FCS. Srch : Turn on/off the focus search.

[8] FCS. OppL : Turn on/of f the focus search to another layer

of designated layer in Disc Type setting.

(dual layer disc only)

[0] : All servo off.

p Sled FWD (right cursor) : Move the sled forward.

P Sled REV (left cursor) : Move the sled reverse.

O Sled FWD (up cursor) : Reset the sled.

o Sled REV (down cursor) : Limit in the sled.

23

Page 24

HCD-SR4W

2-3. Track/Layer Jump

Track/Layer Jump

1. 1Tj FWD R.Lj L0>L1

2. 1Tj REV L.Lj L1>L0

3.500Tj Fine FWD U.Fj L0>L1

4.500Tj Fine REV D.Fj L1>L0

5.10kTj Dirc FWD

6.10kTj Dirc REV

7.20kTj Dirc FWD

8.20kTj Dirc REV

0. All Servo Off

Exit: RETURN

On this screen, track jump, etc. can be performed. Only for the DVD

dual layer disc, the focus jump and layer jump are displayed in the

right field

[1] 1Tj FWD : 1 track jump forward.

[2] 1Tj REV : 1 track jump reverse.

[3] 500Tj FWD : 500 track jump (fine search)forward.

[4] 500Tj REV : 500 track jump (fine search) reverse.

[5] 10kTj FWD : 10k track jump (direct search) forward.

[6] 10kTj REV : 10k track jump (direct search) reverse.

[7] 20kTj FWD : 20k track jump (direct search) forward.

[8] 20kTj REV : 20k track jump (direct search) reverse.

[0] : All servo off.

2-4. Non EEPROM Write Adjust

2-5. EEPROM Write Adjust

EEPROM Write Adjust

1. Focus Offset

2. Focus Gain

3. Trk. Offset Coarse

4. ——————

5. Trk. Gain

6. EQ Boost

0.All Servo Off

Exit: RETURN

On this screen, each item can be adjusted automatically. Select the

desired number [1] to [0] from the remote commander, and selected

item is adjusted automatically.

[1] Focus Offset : Adjusts focus offset.

[2] Focus Gain : Adjusts focus gain.

[3] TRK. Offset : Adjusts tracking offset of the RF amp

(IC001) side.

[5] TRK. Gain : Adjusts track gain.

[6] EQ Boost : Adjusts amount of boost of equalizer.

[0] : All servo off.

2-6. Memory Check

Display images are shown as follows, and all two screens are able

to switch by the O key (UP) or o key (DW).

Non EEPROM Write Adjust

1. Focus Offset

2. Focus Gain

3. Trk. Offset Coarse

4. Trk. Offset Fine

5. Trk. Gain

6. EQ Boost

0.All Servo Off

Exit: RETURN

On this screen, each item can be adjusted manually. Select the desired

number [1] to [0] from the remote commander, and current setting

for the selected item will be displayed, then increase or decrease

numeric value with the O key or o key. This value is stored in the

EEPROM. If CLV has been applied, the jitter is displayed for

reference for the adjustment.

[1] Focus Offset : Adjusts focus offset.

[2] Focus Gain : Adjusts focus gain.

[3] TRK. Offset : Adjusts tracking offset of the RF amp

(IC001) side.

[4] TRK. Offset : Adjusts tracking offset of the DSP

(IC401) side.

[5] TRK. Gain : Adjusts track gain.

[6] EQ Boost : Adjusts amount of boost of equalizer.

[0] : All servo off.

24

EEPROM Data 1/2 CD SL L0 L1

Focus Gain xx xx xx xx

Trk. Gain xx xx xx xx

Focus Offset xx xx xx xx

Trk. Offset xx xx xx xx

EQ. Boost xx xx xx xx

PI Level xx xx -- -Fcs. Balance -- xx -- -Jitter xx xx xx xx

Mirror Time xx xx xx -FE Level -- xx -- -Traverse Lv1. -- xx -- -Next:DW Default:CLR Exit:RET

EEPROM Data 2/2 CDRW DVDRW

Focus Gain xx xx

Trk. Gain xx xx

Focus Offset xx xx

Trk. Offset xx xx

EQ. Boost xx xx

Prev:UP Default:CLR Exit:RET

On this screen, current servo adjusted data stored in the EEPROM

are displayed. The adjusted data are initialized by pressing the

[CLEAR] key, but be careful that they are not recoverable after

initialization.

Before clearing the adjusted data, make a note of the set data. This

screen will also appear if [0]-All is selected in the Drive Auto

Adjustment. In this case, default setting cannot be made.

Page 25

HCD-SR4W

### EMG. History ###

Laser Hours CD xxxxhxxm

DVD xxxxhxxm

a. bb xx xx xx xx xx xx xx

xx xx xx xx xx xx xx xx

a. bb xx xx xx xx xx xx xx

xx xx xx xx xx xx xx xx

Select:1-9 Scroll:UP/DOWN

(1.Latest EMG.) Exit: RETURN

2-7. Disc Check Memory

Disc Check Memory

1. SL Disc check

2. CD Disc check

3. DL Disc check

On this screen, measure the mirror time of chucked disc, and write

to the EEPROM.

2-8. Error Rate Display

Error Rate Display

UC CR Address

PI1 Err Now xx xxxx xxxxxxxx

Max xx xxxx xxxxxxxx

Avg xx xxxx

PI2 Err Now xx xxxx xxxxxxxx

Max xx xxxx xxxxxxxx

Avg xx xxxx

PO Err Now xx xxxx xxxxxxxx

Max xx xxxx xxxxxxxx

Avg xx xxxx

Start: ENTER Exit: RETURN

On this screen, measure and display the error rate.

UC : Incorrect value

CR : Correct value

2-9. SACD Water Mark Check

SACD Water Mark Check

PSP AMP

PSN

Start: ENTER Exit: RETURN

On this screen, measure the PSP AMP v alue and PSN value of SACD

water mark.

3. EMERGENCY HISTORY

On the Test Mode Menu screen, selecting [4] displays the

information such as servo emergency history.

The history information from last 1 up to 10 can be scrolled with

the O key or o key. Also, specific information can be displayed

by directly entering that number with ten keys.

Exit: RETURN

xxxxhxxm : The laser on total hours. Data below minutes

are omitted.

a. : Error number.

bb : Error code.

xx : Not used.

• Clearing History Information

Clearing laser hours:

Press the [DVD DISPLAY] and [CLEAR] keys in this order.

Then both CD and DVD data are cleared.

Clearing emergency history:

Press the [DVD TOP MENU] and [CLEAR] keys in this order.

Initializing set up data:

Press [DVD MENU] and [CLEAR] keys in this order.

The data have been initialized when “EEPROM Initialize

Finished.”. messa ge is displayed. The EMG. History screen

will be restored soon.

• Code list of Emergency History

10: Communication to RF AMP (IC001) failed.

11: Each servo for focus, tracking, and spindle is unlocked.

12: Check sum error of EEPROM (IC203).

14: Communication to servo DSP (IC401) failed, or servo DSP

(IC401) is faulty.

15: Communication to DVD decoder (IC701) failed, or DVD

decoder (IC701) is faulty.

16: Communication to DSD decoder (IC801) failed, or DSD

decoder (IC801) is faulty.

20: Initialization of sled servo failed. It is not placed in the initial

position.

23: Sled servo operation error.

24: Made a request to move the sled servo to wrong position.

30: Tracking balance adjustment error.

31: Tracking gain adjustment error.

33: Focus bias adjustment error.

34: Focus gain adjustment error.

35: Equalizer adjustment error.

40: Focus servo does not operate.

41: With a DVD dual layer disc, focus jump failed.

50: CLV (spindle) servo does not operate.

51: Spindle does not stop.

60: Made a request to seek nonexistent address.

61: Seek error of retry more than regulated times.

70: Control data could not be read.

80: Disc reading failed.

25

Page 26

HCD-SR4W

4. MECHA ERROR HISTORY

On the Test Mode Menu screen, selecting [5] displays the

information of mechanism deck error history.

The history information from last 1 up to 8 can be scrolled with the

O key or o key. Also, specific information can be displayed by

directly entering that number with ten keys.

### Mecha Error History ###

1. aa bb cc dd xx xx xx xx

2. aa bb cc dd xx xx xx xx

3. aa bb cc dd xx xx xx xx

4. aa bb cc dd xx xx xx xx

5. aa bb cc dd xx xx xx xx

6. aa bb cc dd xx xx xx xx

7. aa bb cc dd xx xx xx xx

8. aa bb cc dd xx xx xx xx

Scroll:UP/DOWN

(1.Latest Err.) Exit: RETURN

aa : The error in the midst of initializing the mechanism deck.

bb : The error in the midst of loading operation.

cc : The error in the midst of up/down the stocker.

dd : The error in the midst of switching the mechanism deck

mode.

xx : Not used.

• Error code (bb)

00 : Initializing the mechanism deck.

10 : Retry over of eject and loading.

30 : Open operation in no disc status.

60 : Retry over of eject and loading.

70 : Disc is chucking position.

81 : Retry failed of disc movement from chucking position to

stocker.

83 : Retry pr eparation failed of disc movement from chucking

position to stocker.

90 : Disc is stored in the stocker.

A1 : Retry failed of disc movement from stocker to chucking

position.

A3 : Retry preparation failed of disc movement from stocker to

chucking position.

B0 : Just before the release operation.

B1 : Retry failed of the release operation.

• Error code (cc)

10 : Under a stop.

22 : Retry preparation failed.

23 : Retry failed.

• Error code (dd)

10 : Under a stop.

22 : Retry preparation failed.

23 : Retry failed.

• Error code (aa)

FF : Complete the initializing. (normal operation)

11 : Stocker movement (to chucking position) failing in the midst

of initializing the mechanism deck.

12 : Stocker movement (to chucking position) failing in the midst

of initializing the mechanism deck.

1x : Initializing the mechanism deck.

2x : Initializing the mechanism deck.

3x : Initializing the mechanism deck.

41 : Disc eject failing in the midst of initializing the mechanism

deck.

4x : Initializing the mechanism deck.

50 : Disc eject failing in the midst of initializing the mechanism

deck.

5x : Initializing the mechanism deck.

A2 : Disc eject failing in the midst of initializing the mechanism

deck.

Ax : Initializing the mechanism deck.

D3 : Disc eject failing in the midst of initializing the mechanism

deck.

Dx : Initializing the mechanism deck.

Ex : Initializing the mechanism deck.

5. VERSION INFORMATION

On the Test Mode Menu screen, selecting [6] displays the ROM

version and region code.

The parenthesized hexadecimal number in version field is checksum

value of ROM.

## Version Information ##

IF con. Ver.x. xx

SYScon. Ver.x. xx (xxxx)

Model DAV-xxx

Region

Config xxxxxxxx

Front End Ver.x.xx

IF con. : The version of system controller (IC901).

SYScon. : The version of DVD system processor (IC206).

Front End : The version of mechanism controller (IC301).

6. VIDEO LEVEL ADJUSTMENT

On the T est Mode Menu screen, selecting [7] displays color bars for

video level adjustment. During display of color bars, OSD disappears

but the menu screen will be restored if pressing the [RETURN] key.

0x

Exit: RETURN

26

Page 27

SECTION 5

p

ELECTRICAL ADJUSTMENT

HCD-SR4W

[TEST DISC LIST]

Use the following test disc on test mode.

TDV-520CSO (DVD-SL) : PART No. J-2501-236-A

LUV-P01 (CD) : PART No. 4-999-032-01

TDV-540C (DVD-DL) : PART No. J-2501-235-A

Note: Do not use exiting test disc for DVD.

AUTO SERVO ADJUSTMENT

After parts related to the servo circuit (RF amplifier (IC001), DSP

(IC401), motor driver (IC501), EEPR OM (IC302) so on) and optical

pick-up (DBU-1) are replaced, re-adjusting the servo circuit is

necessary. Select “ALL” at “1. DRIVE AUTO ADJUSTMENT”

(Refer to page 25 in TEST MODE) and adjust DVD-SL (single

layer), CD and DVD-DL (dual layer).

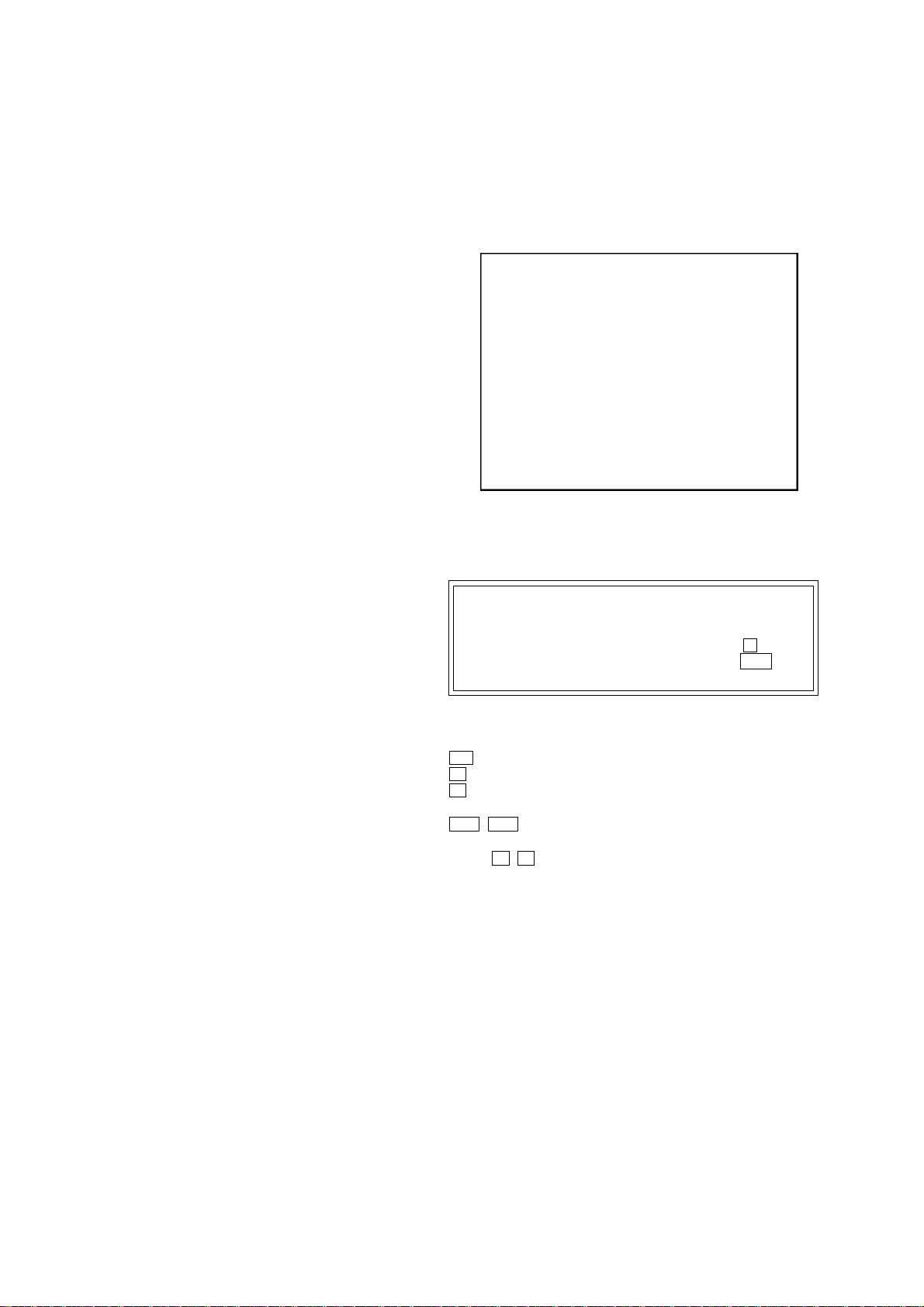

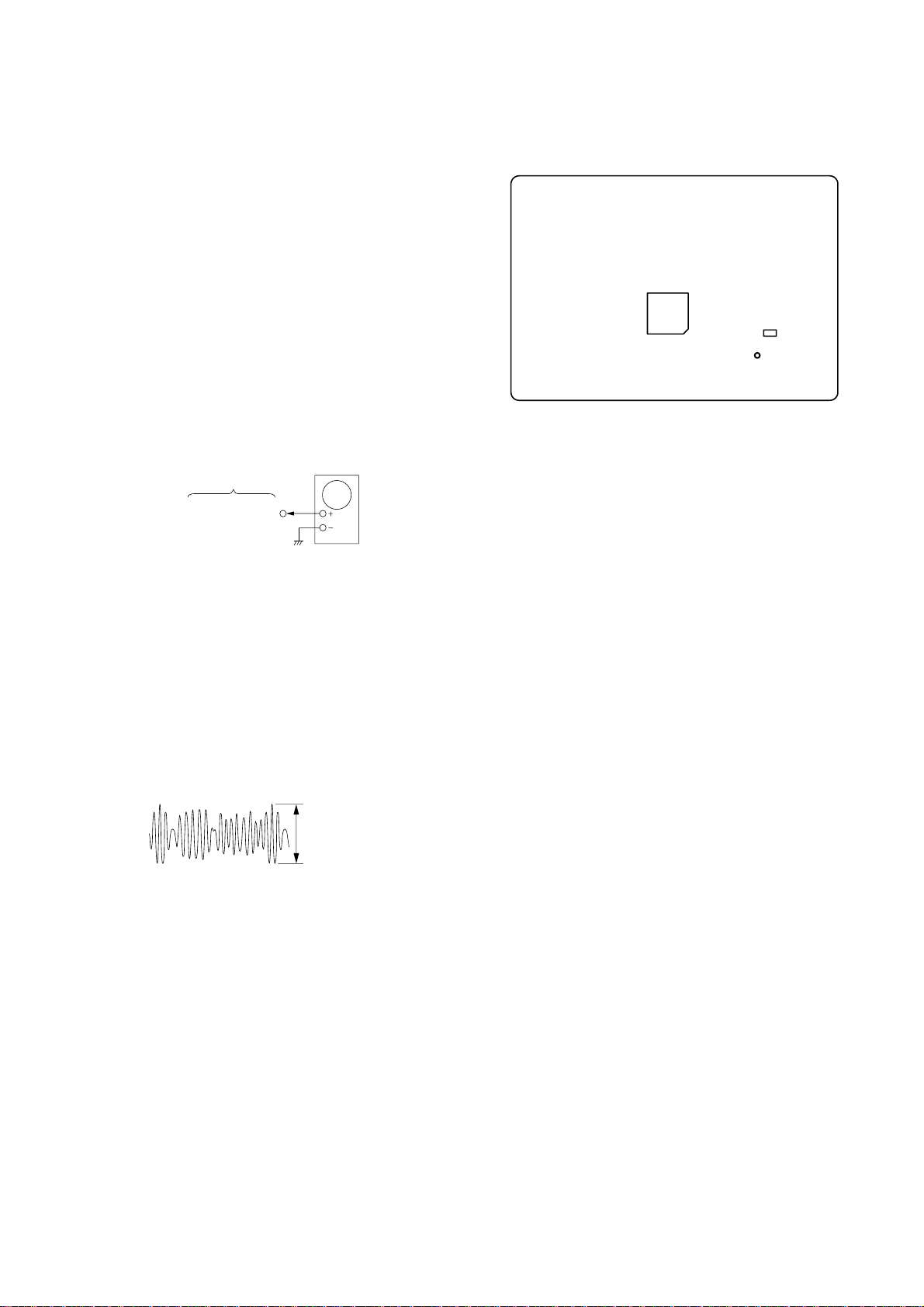

DIAT SIGNAL RF LEVEL ADJUSTMENT

This adjustment is performed in order to adjust the transmission

distance of RF signal for DIAT communication.

Connection:

DIA T TRANSMIT

board

TP815

(RF AMP OUT)

Procedure:

1. Connect the oscilloscope to TP815 (RF AMP OUT) and GND

on the DIAT TRANSMIT board.

2. Connect DIR-T1 to DIR-T1 jack (J301).

3. Adjust RV801 on the DIAT TRANSMIT board so that the

center of waveform becomes 1.0 Vp-p.

4. Confirm trigger is locked.

5. Adjust RV801 on the DIAT TRANSMIT board so that the

center of waveform becomes 2.2 to 2.4 Vp-p.

oscilloscope

Adjustment Location:

– DIAT TRANSMIT Board (SIDE A) –

IC804

(RF AMP OUT)

IC805

TP815

RF Signal Reference Waveform

VOLT/DIV : 500 mV

TIME/DIV : 500 ns

level : 2.2 to 2.4 Vp-

27

Page 28

HCD-SR4W

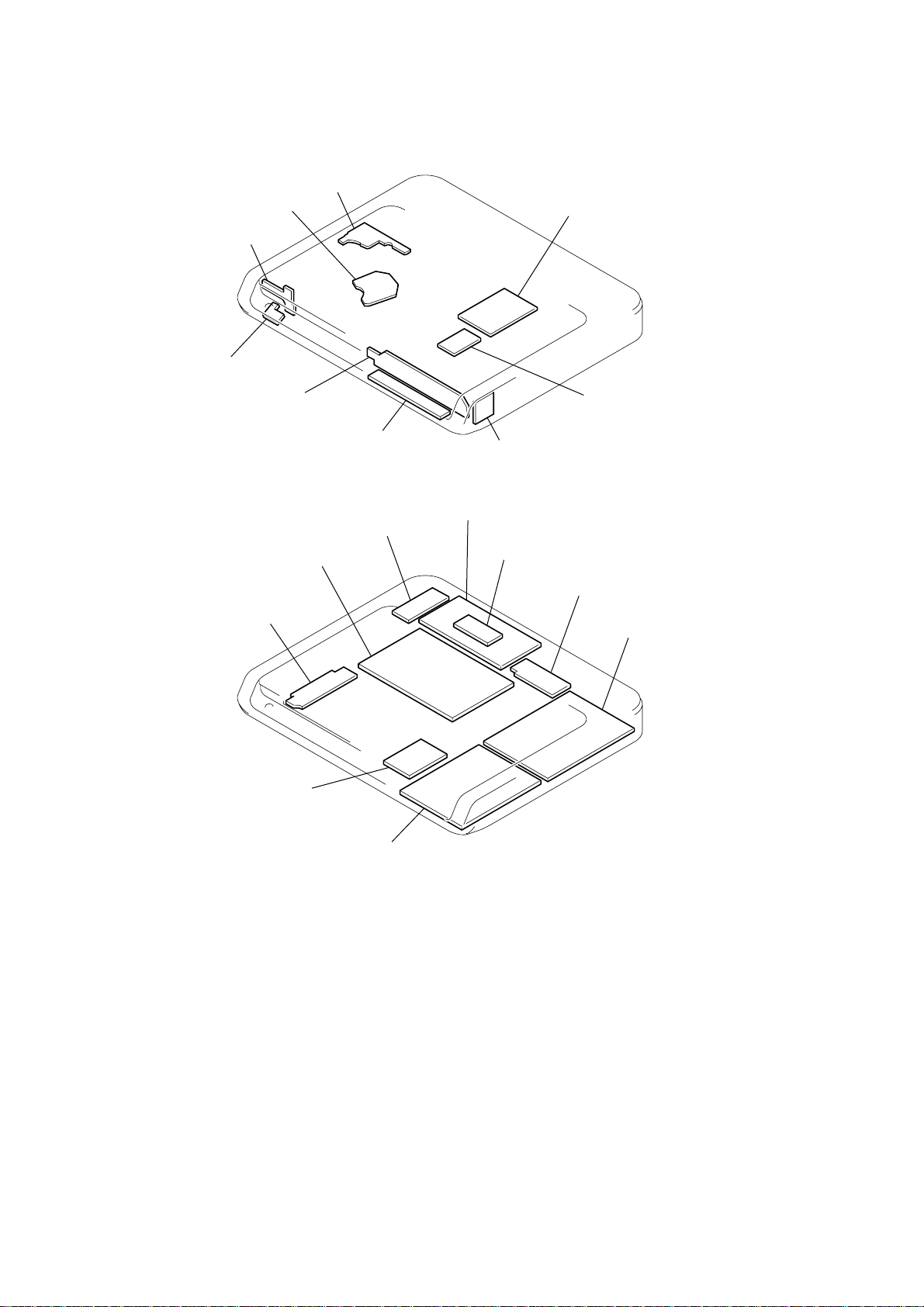

• Circuit Boards Location

SONY LAMP board

PW KEY board

RF board

SECTION 6

DIAGRAMS

DRIVER board

DIA T TRANSMIT board

FL board

DMB08 board

LF board

DDCON board

CONTROL KEY board

TUNER UNIT

SWITCHING REGLATOR

DIAT PW board

HP board

IO board

SCART board

(only for AEP, UK and Russian models)

DIAT SPK board

AMP board

28

Page 29

HCD-SR4W

d

d

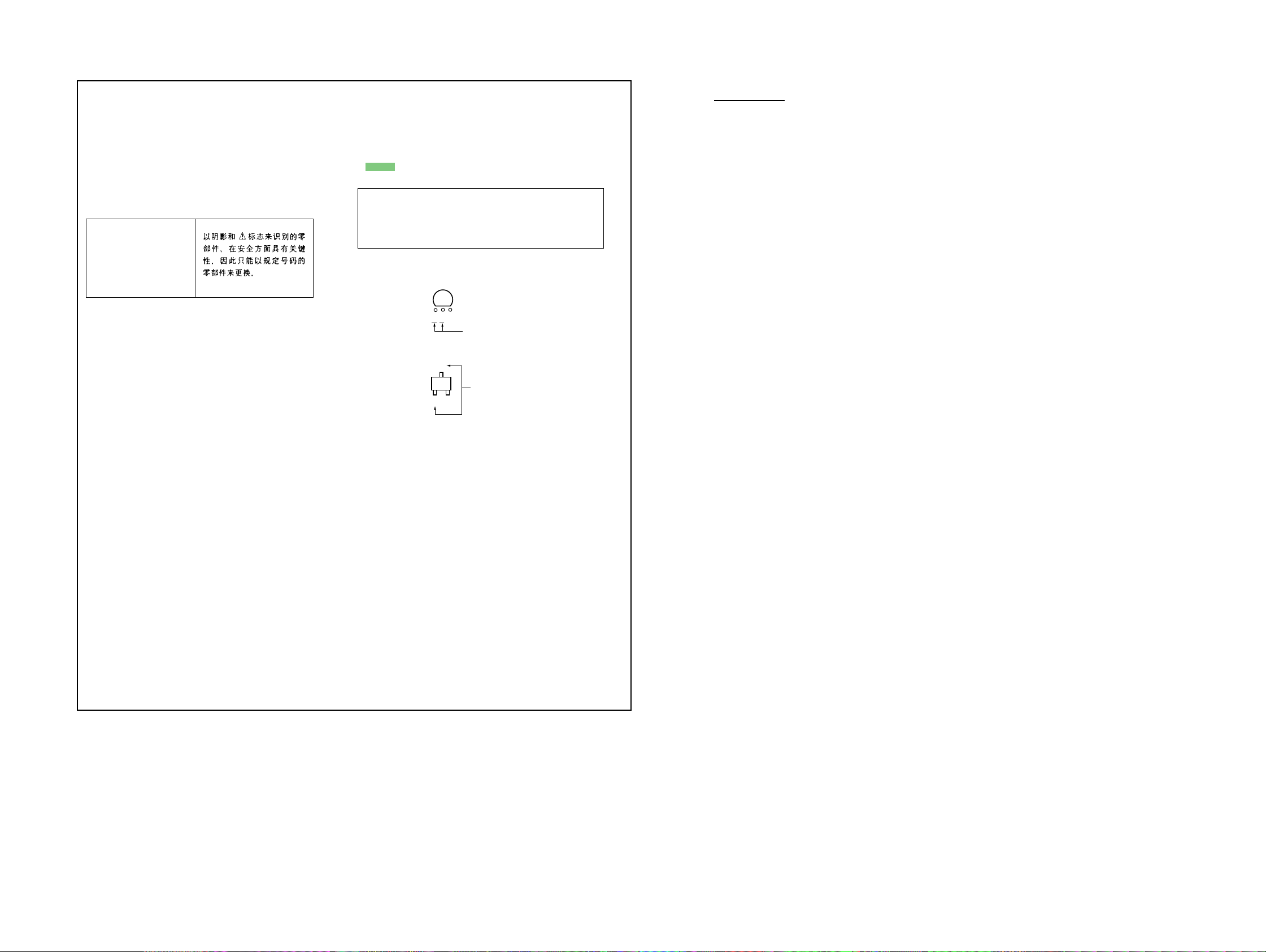

THIS NOTE IS COMMON FOR PRINTED WIRING BOARDS AND SCHEMATIC DIAGRAMS.

(In addition to this, the necessary note is printed in each block.)

For Schematic Diagrams.

Note:

• All capacitors are in µF unless otherwise noted. (p: pF)

50 WV or less are not indicated except f or electrolytics and

tantalums.

• All resistors are in Ω and 1/

specified.

• f : internal component.

• C : panel designation.

Note:

The components identified by mark 0 or dotted line with mark 0 are

critical for safety.

Replace only with part

number specified.

• A : B+ Line.

• B : B– Line.

• H : adjustment for repair.

•Voltages and wavef orms are dc with respect to ground under no-signal (detuned) conditions.

•Voltages and wavefor ms are dc with respect to ground in

service mode.

•Voltages are taken with a VOM (Input impedance 10 MΩ).

Voltage variations may be noted due to normal production

tolerances.

•Waveforms are taken with a oscilloscope.

Voltage variations may be noted due to normal production

tolerances.

no mark : DVD STOP

• Circled numbers refer to waveforms.

• Signal path.

F : AUDIO

J : CD PLAY

c : DVD PLAY

d : TUNER

L : VIDEO

i : OPTICAL DIGITAL IN

a : CHROMA

E : Y

r : COMPONENT VIDEO

e : AUX IN

I : SACD PLAY

q : R, G, B

•Abbreviation

AUS: Australian model

CH : Chinese model

E41 : 230 V AC area in E model

HK : Hong Kong model

KR : Korean model

MX : Mexican model

RU : Russian model

SP : Singapore model

TW : Taiwan model

4

W or less unless otherwise

For Printed Wiring Boards.

Note:

• X : parts extracted from the component side.

• a : Through hole.

• : Pattern from the side which enables seeing.

(The other layers' patterns are not indicated.)

Caution:

Pattern face side: Parts on the pattern face side seen from

(Side A) the pattern face are indicated.

Parts face side: Parts on the parts face side seen from

(Side B) the parts face are indicated.

• Indication of transistor

CEB

These are omitte

C

Q

These are omitte

EB

MEMO

HCD-SR4W

2929

Page 30

HCD-SR4W

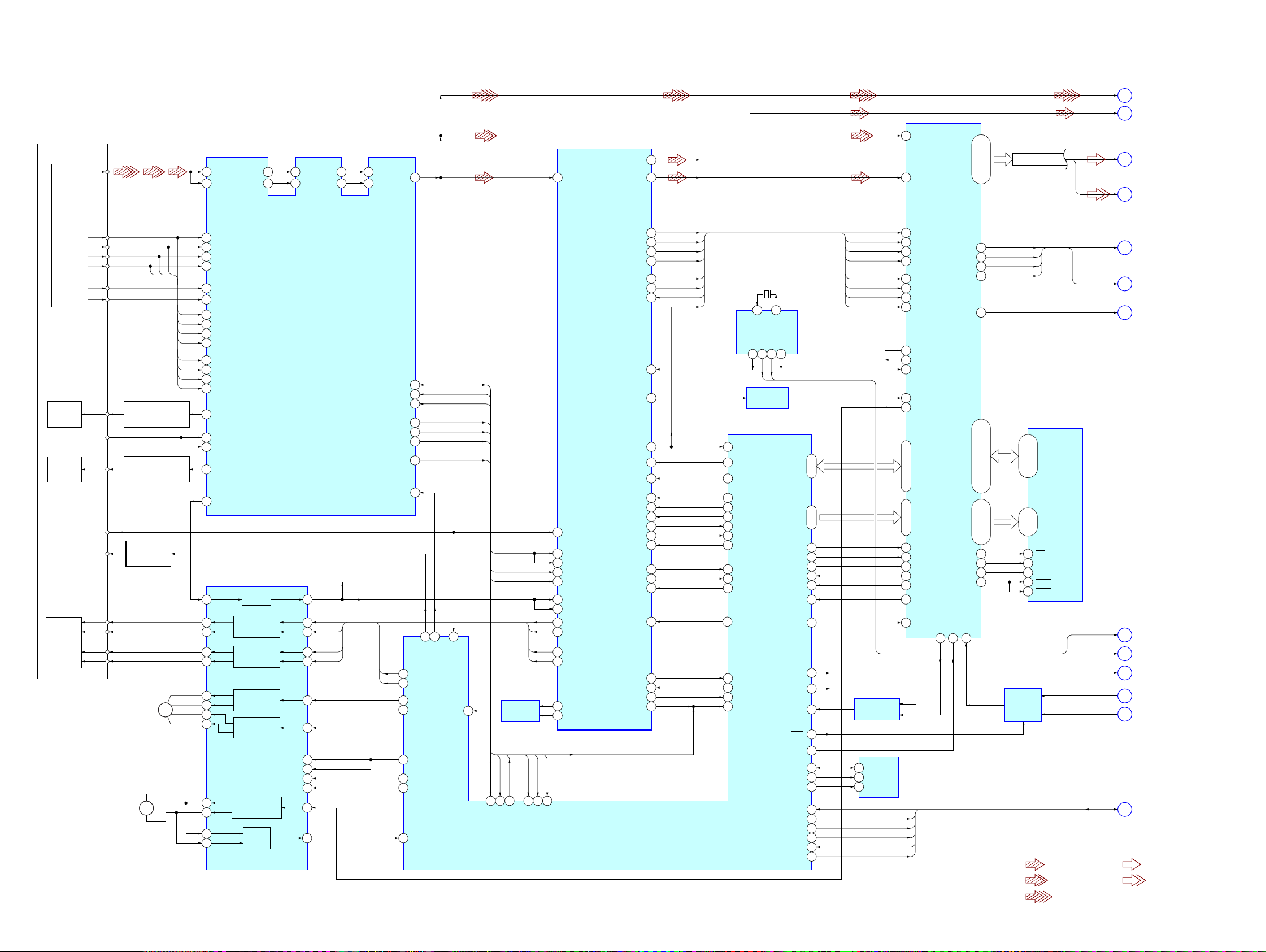

6-1. BLOCK DIAGRAM — RF/SERVO SECTION —

OPTICAL PICK-UP

BLOCK

DETECTOR

LASER

CD LD

DIODE

(FOR CD)

LASER

DVD LD

DIODE

(FOR DVD)

INLIM

FCS+

FCS–

2AXIS

DEVICE

FOCUS/

COIL

TRK+

TRK–

TRACKING

RF

A

B

C

D

F

E

PD

SW

AUTOMATIC POWER

CONTROL (FOR CD)

AUTOMATIC POWER

CONTROL (FOR DVD)

LASER DIODE

(SPINDLE)

Q301

SELECT

(SLED)

MM

D

Q002

Q001

CBA

MM

1

63

3

4

5

6

18

17

B

12

A

11

D

10

C

9

B

16

A

15

D

14

C

13

22

24

23

21

36

FOCUS/TRACKING COIL DRIVER,

SPINDLE, SLED MOTOR DRIVER

36 48

37 1

34 3

35 4

32

31

30

29

27

28

47

46

RFSIN

A2

B2

C2

D2

CD E

CD F

A

B

C

D

CD A

CD B

CD C

CD D

CDLD

CDPD

DVDPD

DVDLD

V125

ATON

IC501

BUFFER

FOCUS COIL

DRIVE

TRACKING COIL

DRIVE

SLED MOTOR

DRIVE

SLED MOTOR

DRIVE

SPINDLE MOTOR

DRIVE

BUFFER

ATOP

DVDRFP

FNP

62

61

AIP

59

FNN

AIN

60

IC001

CD/DVD/SACD RF AMP,

FOCUS/TRACKING ERROR AMP

4042

FF

FR

TF

TR

7

10

19

MUTE12

20

MUTE34

21

MUTE5

22

TSD-M

13

45

535254

AVC

(1.65V)

WARFI

CDDOUT

117

RFIN

64

DOUT

DIP

55

DIN

RFAC

SDATA

SCLK

SDEN

MIRR

LDON

FF

FR

57

47

46

48

39

TE

40

FE

42MNTR

27

26

7

FCS_JMP_1

8

FCS_JMP_2

44

SLED_B

43

SLED_A

60

MUTE_2D

63

SP_ON

73

TSD-M

62

FG

28

76 31

LDON

LDSEL

SLED

DATA_RF

CLK_RF

SDEN

MIRR

INLIM

61

TE

FE

PI

TE

FE

PI

CLK_RF

DATA_RF

82

83

SDCLK RF

SDATA RF

IC402 (1/2)

AMP

SDEN

2

65

SDEN

50

RFAC

IC401

DIGITAL SIGNAL PROCESSOR,

DIGITAL SERVO PROCESSOR

SSTP

26

41

TE

40

SE

FE

39

43

RFDC

VC

38

CE

42

FF

33

FFDR

FR

34

FRDR

TF

31

TFDR

TR

32

TRDR

SFDR

29

SRDR

30

MIRR

PI

FE

TE

67PI66

FE

TE

IC301 (1/2)

MECHANISM

CONTROLLER

PCMD

BCLK

LRCK

C2PO

WDCK

WFCK

SBSO

EXCK

XTAI

MDP

SCOR

XTSL

MD2

DATA

CLOK

XLAT

SENS

SQSO

SQCK

LOCK

GFS

MUTE

XRST

COUT

SCLK

FOK

MIRR

66

BCLK

67

LRCK

65

C2PO

14

GSCOR

17

WFCK

10

SBSO

79

EXCK

80

SCOR

IC303

CLOCK

GENERATOR

10 3

71

26

10

3

49

50

27

9

52

54

75

71

59

98

30

72

74

29

IC703 (2/2)

SCOR

CDSP2

DOCTRL/

ISBTEST

DATA_CD

CLOK_CD

LAT_CD

SENS_CD

SQSO

SQCK

LOCK_CD

GFS_CD

MUTE_CD

XDRST

COUT_CD

SCLK_CD

FOK_CD

MIRR

25

15

69

63

4

6

5

7

76

77

24

13

3

2

19

8

22

20

7 8

XTI

SO2

MO1

13 9

27M

BUFFER

SDOUT_DSD

X302

27MHz

XTO

SO3

SO1

768FS

XRD

XWR

XCS_DVD

INIT0_DVD

INIT1_DVD

GFS_DVD

XRST_DVD

XRST_DSD

JIT OFFSET

SACD/DVD

EEP_RDY

EEP_SI

EEP_CLK

EEP_CS

SDIN_DSD

SCK_DSD

XMSLAT

READY_DSD

MUTE_DSD

JIT

14-21

D0 – D7

89-96

A0 – A7

85

84

12

22

23

58

25

4

45

64

77

6

5

100

99

47

46

24

51

48

53

BCLK

LRCK

C2PO

GSCOR

WFCK

SBSO

EXCK

SCOR

IC703 (1/2)

COMPARATOR

5

SDA

6

SCL

7

WP

MSDATO

MSDATI

MSCK

XMSLAT

SHRRDY

SHRMUT

160

MDAT

158

BCK

163

LRCK

155

C2PO

146

GSCOR

151

WFCK

148

SBIN

147

EXCK

150

SCOR

DVD DECODER

167

XTA1

169

XTA2

170

XTAL

137

MDIN2

135

SPO

D0 – D7

172-176, 1, 2, 4

A0 – A7

5, 7, 9-14

17

XRD

18

XWR

19

XCS

20

XINT0

21

XINT1

107

GFS

164

XRST

IC302

EEPROM

IC701

AEP0

109

HDB0 – HDB7

XHWR

XDRQ

HDB8

XHRD

MNT2

MDB0 – MDB9,

MDBA – MDBF

MA0 – MA9

XMWE

XMOE

XRAS

XCAS

XHAC

MNT1

53

92

44, 41, 39, 35,

48

46

26

49

93

66-69, 71, 73-75, 96, 97,

79, 80, 82-87,

76

94

78

95

AV DATA BUS

32, 30, 27, 24

XDCK

XSAK

SDEF

XSHD

2-5, 7-10,

41-44, 46-49

99, 101, 102, 104-106

89, 91

27-32

21-24,

17

WE

33

OE

18

RAS

34

UCAS

35

LCAS

IC814

SACD/DVD

SELECT

XMSLAT, SHRRDY, SHRMUT

• SIGNAL PATH

I/O0 – I/O15A0 – A9

IC706

16Mbit

D-RAM

MSDATO, MSDATI, MSCK,

: CD

SD0 – SD7

(for AUDIO SYSTEM)

SD0 – SD7

(for VIDEO SYSTEM)

XDCK, XSAK, SDEF, XSHD

(for AUDIO SYSTEM)

XDCK, XSAK, SDEF

(for VIDEO SYSTEM)

768FS

27M

XRST_DSD

XSRQ

XSRQ-ZIVA

: DVD

WCK

A

B

C

D

E

F

G

H

I

J

K

L

M

AUDIO(DSP)

SECTION

AUDIO(DSP)

SECTION

AUDIO(DSP)

SECTION

VIDEO

SECTION

AUDIO(DSP)

SECTION

VIDEO

SECTION

AUDIO(DSP)

SECTION

AUDIO(DSP)

SECTION

VIDEO

SECTION

AUDIO(DSP)

SECTION

AUDIO(DSP)

SECTION

VIDEO

SECTION

AUDIO(DSP)

SECTION

: AUDIO

: VIDEO

: SACD

HCD-SR4W

3030

Page 31

6-2. BLOCK DIAGRAM — AUDIO (DSP) SECTION —

HCD-SR4W

HCD-SR4W

RF/SERVO

SECTION

RF/SERVO

SECTION

RF/SERVO

SECTION

RF/SERVO

SECTION

RF/SERVO

SECTION

RF/SERVO

SECTION

RF/SERVO

SECTION

RF/SERVO

SECTION

VIDEO

SECTION

RF/SERVO

SECTION

VIDEO

SECTION

VIDEO

SECTION

VIDEO

SECTION

AUDIO (OUT)

SECTION

WARFI

A

WCK

G

SD0 - SD7

C

SDEF, XSHD,

XDCK, XSAK

E

768FS

H

MSDATO, MSDATI, MSCK,

XMSLAT, SHRRDY, SHRMUT

M

XRST_DSD

J

XSRQ

K

TDOSA, TDISA,

TCK, TMS, TRST

N

CDDOUT

B

SPDIF

O

L, R

X

COAXIAL

FM

75 ohm

AM

AV1, AV3,

RGB SEL, DVD SEL

P

RSTAD

S

R

SAT

J601

VIDEO

D5V

AV DATA BUS

R-CH

AUDIO IN

AUDIO IN

FM/AM TUNER PACK

FM ANT

L-CH

GND

R-CH

AM ANT

GND

TUNED

FM-DET

DI

DO

CK

CE

IC402 (2/2)

REFERENCE VOLTAGE

GENERATOR

XDCK

XSAK

SDEF

XSHD

L

R

L

R

R-CH

TUDI

TUDO

TUCLK

TCE

TUN

DET AMP

LEVEL SHIFT

LEVEL SHIFT

OPTICAL

DIGITAL IN

R-CH

R-CH

Q103

IC812

IC813

MSDATO

MSDATI

MSCK

XMSLAT

SHRRDY

SHRMUT

TDOSA

TDISA

TCK

TMS

TRST

OPTICAL RECEIVER

AEP, UK, RU

Q101

AMP

4

X101

4.332MHz

127

126

123

169 - 176

166

167

168

165

11

6

4

3

2

7

10

9

164

29

27

26

30

31

IC603

IC602

AUDIO INPUT

SELECTOR

4

Y3

2

Y2

1

Y0

5

Y1

Q604 Q605

AV0

RDATA

MUX

RCLK

XI XO

13

14

WAVRB

WARFI

WCK

SD0 - SD7

SDCK

XSAK

SDEF

XSHD

MCKI

DSD DECODER

MSDATO

MSDATI

MSCK

XMSLAT

MSREADY

SMUTE

XRST

XSRQ

TDO

TDI

TCK

TMS

TRST

Y

AB

10

9

AV2

2

16

RDS DECODER

IC801

12.288MHz

3

AEP, UK, RU

RDSD

RDSC

IC101

X600

DSAL

DSAR

DSAC

DSALFE

DSALS

DSARS

BCKAO

EXCKO1

XWE

XRAS

XCAS

DCKE

DCLK

3

LOW-PASS

64

66

69

71

74

76

60

13

134-131

139-136,

DQ0 - DQ7A0 - A11

162-159, 157-154,

152, 151, 149, 148

143

145

144

142

141

5

4

3

22

21

20

IC603

FILTER

R-CH

DIN2

DIN1

DIN0

XIN

XOUT

XMCK

1

9, 11, 12

DQ0 - DQ7

2, 3, 5, 6, 8,

IC808

16Mbit

SD-RAM

20, 19

A0 - A11

21-24, 27-32,

15

WE

17

RAS

16

CAS

34

CKE

35

CLK

IC606

DIGITAL AUDIO

INTERFACE

XSTATE

XMODE

IC609

A/D CONVERTER

1

LIN

5

RIN

15

DATA

CKOUT

BCK

LRCK

ERROR

AUDIO

DOUT

BCK

LRCK

SCK

PDWN

7

RSTDSP

12

DSP-BST

DSP-RST

D1 - D3, SCK,

BCKO, LRCKO

DIGDI, DIGCLK

SOFTMUTE

AUDIO (OUT)

Q

SECTION

AUDIO (OUT)

T

SECTION

AUDIO (OUT)

R

SECTION

R-ch is omitted due to same as L-ch.

SIGNAL PATH

: AUDIO

: CD

: SACD

: AUX IN

: OPTICAL

39

DSIFL

40

DSIFR

41

DSICT

42

DSISW

43

DSISL

44

DSISR

38

DSBCK

27

MCK

IC612

DIGITAL AUDIO

EXIFLR

EXIMCK

EXIBCK

EXILRCK

EXID1

PLOCK

DIGDI

DIGCLK

CSDIR

XST

RSTDIR

EXID1

BCKI

LRCKI

DO

EXIFLR

EXIMCK

EXIBCK

EXILRCK

TUDI

TUDO

TUCLK

TCE

TUN

RDSD

RDSC

AV0

AV1

AV2

RGB SEL

DVD SEL

AV3

33

AD-RST

52

TUN-DI

54

TUN-DO

55

TUN-CLK

53

TUN-CE

51

TUNED

88

RDS_DATA

94

RDS_CLK

95

AV-SEL0

96

AV-SEL1

48

VIDEO-MUTE

73

RGB SEL

70

DVD SEL

98

AV-SEL3

65

89

DF-RST

DVD-POWER

16

13

14

15

36

DI

35

DO

38

CL

37

CE

17

48

34

24

12

11

10

AEP, UK ,RU

35

EXIFLR

29

EXIMCK

31

EXIBCK

32

EXILRCK

34

EXICSW

47

INIT

2

SELTES

SELEXT

4

Q908 - 910

ENABLE

SWITCH

97

PROCESSOR

DF-SW

DIGDI

7

DIG-DI

25

POCSW

MCKOUT

DO

DIRDO

POFLR

POSLR

PBCK

PLRCK

CSDIR

DIGCLK

8

20

DIG-CLK

23

22

21

17

19

20

RSTDIR

24

DIR-CE

DIR-XMODE

BCKI

LRCKI

X601

13.9MHz

DIGDI

DIGCLK

XST

PLOCK

IC900

LEVEL SHIFT

22

18

6

DSP-DO

DIR-XST

DIR-ZERO

IC901 (1/3)

SYSTEM CONTROLLER

15

17

DSP-HACN

DSP-GP9

18

SDI1

30

SDI2

114

SDI3

22

KFSIO

17

BCKI1

15

LRCKI1

SIGNAL PROCESSOR

29

BCKI2

28

LRCKI2

MCLK1

9

12

MCLK2

33

HDIN

34

HCLK

35

HDOUT

32

HACN

68

GP9

19

DIR-ERR

IC607

DIGITAL AUDIO

EXLOCK

59

23

GP8

69

DIR-AD

SDO4

SDO1

SDO2

SDO3

SCKOUT

BCKO

LRCKO

GP10

CS0

WE0

HCS

BST

XRST

Q903

D903

D0 - D15A0 - A15

PM

26

23

24

25

14

20

19

67

108, 107, 105-102, 99

112, 110, 109,97-92,

44

45

113

36

56

2

SUR BACK

98, 80-77, 75-72

82, 85-83, 66-64

RSTDSP

D1

D2

D3

SCK

BCKO

LRCKO

D0 - D15

7-10, 13-16,

29-32, 35-38

S-RAM

A0 - A15

5-1, 44-42,

27-24, 21-18

6

CS

17

WE

PM

HCS

BST

PM

13

IC604

HCS

14

DSP-PM

BST

16

DSP-CS

DIGITAL IN

: TUNER

3131

Page 32

HCD-SR4W

6-3. BLOCK DIAGRAM — AUDIO (OUT) SECTION —

DIGDI, DIGCLK

T

RSTAD

S

J602

MUTE DRIVE

FL DRIVER

5 - 39

S1 - S35

40 - 51

G1 - G12

AUDIO(DSP)

SECTION

D1 - D3, SCK,

BCKO, LRCKO

Q

AUDIO(DSP)

SECTION

AUDIO(DSP)

SECTION

SURROUND

BACK

FL801

FLUORESCENT

INDICATOR TUBE

Q607,608

IC803

SUR BACK

SCK

BCKO

LRCKO

DAT

CLK

CS

RST

VFL

P1

63

62

61

60

56

1

DIGDI

DIGCLK

LED DRIVE

Q900

SWITCH

VFL

Q810

D/A CONVERTER

3

SDTI

1

MCLK

2

BICK

4

LRCK

8

CDTI

7

CCLK

1

IC606

(2/2)

IC608

60

57

61

56

AOUTL+

AOUTL-

PDN

3

2

FL-DATA

FL-CLK

FL-CS

FL-MUTE

12

11

CSN

65

IC605

CONVERTER

2

VOUT

IC901 (2/3)

SYSTEM CONTROLLER

DATA

CLK

VIN

SBR-OUT

SB-OUT

1

4

5

SB-MUTE

SB-SCK

SB-DATA

HPSW

HP-MUTE

DAC-LAT

OVERFLOW1

IC108

STREAM PROCESSOR

45

HPOUTL1

43

HPOUTL2

41

HPOUTR1

39

HPOUTR2

DAC-LAT

IC606

(1/2)

5

7

6

47

50

49

64

46

32

85

HP-SW

HP-MUTE

DAC-LAT

2

IC904(2/3)

BUFFER

D1

SCK

BCKO

LRCKO

SCDT

SHIFT

LATCH1

INIT

NSPMUTE

SOFTMUTE

6

31

36

30

29

21

22

23

27

18

19

24

DATA

XFSIIN

BCK

LRCK

SCDT

SCSHIFT

SCLATCH

INIT

NSPMUTE

SOFTMUTE

OVF FLAGR

OUTL1

OUTL2

OUTR1

OUTR2

XFS0OUT

FSOI

XFSOIN

11

9

6

4

14

38

48

IC305

OSC

X450

49.152MHz

IC301

HEADPHONE

AMP

HP-MUTE

POWER DRIVER

2

PWMBP

17

PWMAP

4

RESET

POWER DRIVER

2

PWMBP

17

PWMAP

4

RESET

Q902

MUTING

CONTROL

IC101

OUTB

OUTA

8 13

IC102

OUTB

OUTA

8

DIAGA

DIAGA

13

Q801-804

MUTING

29

LPF

30

25

LPF

26

SD

29

30

25

26

SD

LPF

LPF

Q101, 102

OVER LOAD

DETECT

Q103, 104

OVER LOAD

DETECT

HP-SW

TB301

SPEAKER

J800

PHONES

(+)

FRONT

L

(ñ)

(+)

FRONT

R

(ñ)

CSOD

XRST

DIAT TRANSMIT

SECTION

AUDIO(DSP)

Y

VIDEO

SECTION

VIDEO

SECTION

SECTION

XLAT

SDATA

SCDT

D2(SL/SR)

BCKO

LRCKO

R-ch is omitted due to same as L-ch.

SIGNAL PATH

: AUDIO

ZIVARESET

V

I2CDATA, I2CCLK

W

R

S800, 801, 807-809,

S815 - 818

SCDT

SHIFT

D2

BCKO

LRCKO

Q913

DISC INSERT

DETECT

IC801

REMOTE CONTROL

RECEIVER

SONY

KEY2

IC903

KEY INPUT

DETECT

Q906, 907

SIRCS DETECT

INVERTER

IC7004

I2CDATA

I2CCLK

D821D819

D802

66

STBY LED

82 - 84

KEY0 - KEY2

38

81

78

93

92

91

100

99

4

3

5

SEN2

LSEN

WAKE

SIRCS

POWER SW

XRST

XLAT