SGS Thomson Microelectronics ST72P589BW5, ST72T589BW5, ST72589BW5, ST72589BW, ST72389BW4 Datasheet

...

Rev. 2.7

June 2003 1/158

ST72589BW,

ST72389BW

8-BIT MCU WITH NESTED INTERRUPTS, DOT MATRIX LCD,

ADC, TIMERS, PWM-BRM, SPI, SCI, I²C, CAN INTERFACES

DATASHEET

■ 16K ROM or 24 Kbytes EPROM/OTP/

FASTROM

■ Master Reset and Power-on Reset

■ Low consumption resonator main oscillator

■ 4 Power saving modes

■ Nested interrupt controller

■ NMI dedicated non maskable interrupt pin

■ 31 multifunctional bidirectional I/O lines with:

– external interrupt capability (5 vectors)

– 21 alternate function lines

■ LCD driver with 60 segment outputs and 8

backplane outputs able to drive up to 60x8 (480)

or 60x4 (240) LCD displays

■ Real time base, Beep and Clock-out capabilities

■ Software watchdog reset

■ Two 16-bit timers with:

– 2 input captures

– 2 output compares

– external clock input on one timer

– PWM and Pulse generator modes

■ 10-bit PWM (DAC) with 4 dedicated output pins

■ SPI synchronous serial interface

■ SCI asynchronous serial interface

■ I2C multi master / slave interface

■ CAN interface

■ 8-bit ADC with 5 dedicated input pins

■ 8-bit Data Manipulation

■ 63 Basic Instructions

■ 17 main Addressing Modes

■ 8 x 8 Unsigned Multiply Instruction

■ True Bit Manipulation

■ Full hardware/software development package

Device Summary

PQFP128

14 x 20

Features ST72589BW5 ST72389BW4

Program memory - bytes 24K OTP/FASTROM 16K ROM

RAM (stack) - byte s 1024 (256) 512 (256)

Std. Peripherals

LCD 60x8 , Watchdog,

16-bit Timers, PWM-BRM,

SPI, SCI, I2C, CAN, ADC

LCD 60x 8, Watchdog,

16-bi t Ti mers,

SPI, SCI, ADC

Operat ing Supply 4.5V to 5.5V

CPU Frequency 4 to 8 MHz (with 8 to 16 MHz os cillato r)

Temper ature Range -40°C to +8 5°C

Packages PQFP128

Development device ST72E589BW5

1

Table of Cont ents

158

2/158

2

1 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.3 REGISTER & MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.4 MEMORIES AND PROGRAMMING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2 CENTRAL PROCESSING UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.2 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.3 CPU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3 SUPPLY, RESET AND CLOCK MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1 RESET MANAGER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.2 LOW CONSUMPTION OSCILLATOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.3 MAIN CLOCK CONTROLLER (MCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4 INTERRUPTS & POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.1 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.2 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.2 FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.3 I/O PORT IMPLEMENTATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6 MISCELLANEOUS REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.1 I/O PORT INTERRUPT SENSITIVITY DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.2 I/O PORT ALTERNATE FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.3 MISCELLANEOUS REGISTERS DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

7 ON-CHIP PERIPHERALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7.1 LCD DRIVER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7.2 WATCHDOG TIMER (WDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.3 16-BIT TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

7.4 PWM/BRM GENERATOR (DAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

7.5 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

7.6 SERIAL COMMUNICATIONS INTERFACE (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

7.7 I2C BUS INTERFACE (I2C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.8 CONTROLLER AREA NETWORK (CAN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.9 8-BIT A/D CONVERTER (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

8 INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

8.1 CPU ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

8.2 INSTRUCTION GROUPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

9 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

9.1 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

9.2 RECOMMENDED OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

9.3 TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

9.4 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table of Cont ents

3/158

3

9.5 I/O PORTS CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

9.6 SUPPLY, RESET AND CLOCK CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . 143

9.7 MEMORY AND PERIPHERAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

10 PACKAGE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

10.1PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

11 DEVICE CONFIGURATION AND ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . 154

11.1ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE . . . . . . . . . . . . 154

11.2ST7 APPLICATION NOTES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

12 SUMMARY OF CHANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

ST72589BW, ST72389BW

4/158

1 GENERAL DESCRIPTION

1.1 INTRODUCTION

The ST72589W and ST72389W Microcontroller

Units are members of the ST7 famil y of Microc ontrollers dedicated to high-end applications with

LCD driver capabilit y.

These devices are bas ed on an industry-standard

8-bit core and feature an enhanced instruction set.

Under software control, these microcontrollers

may be placed in either WAIT, SLOW, ACTIVE-

HALT or HALT mo des, thus reducing power consumption.

The enhanced instruction set and addressing

modes afford real programming po tential. In addition to standard 8-bit data management, these microcontrollers feature true bit manipulation, 8x8

unsigned multiplication and indirect addressing

modes.

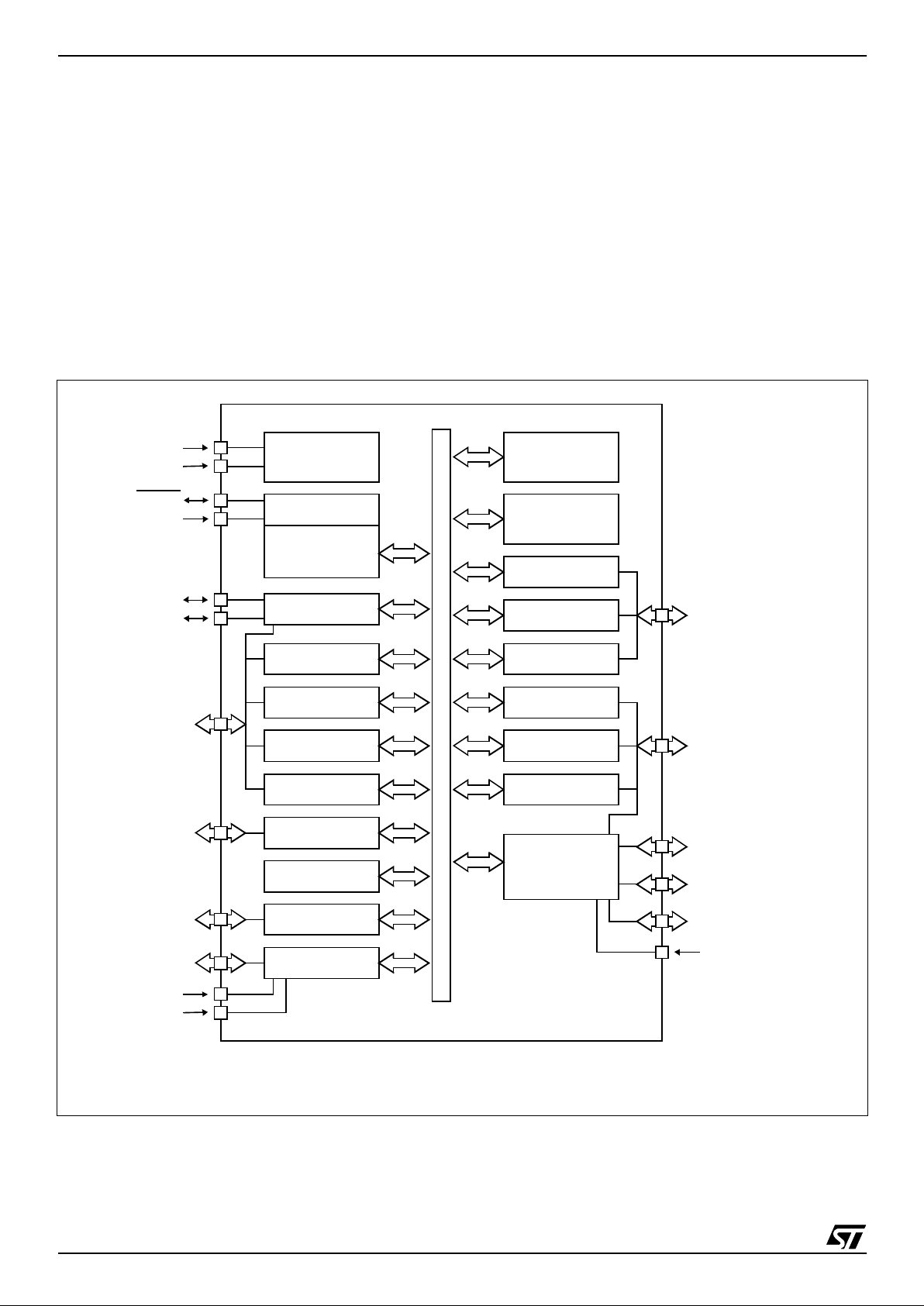

Figure 1. Device Block Diagram

8-BIT CO RE

ALU

ADDRESS AND DATA BUS

OSC2

OSC1

RESET

MAIN OSC

CONTROL

EPROM

24K

V

DD

NMI

PORT C

PC0 -> PC7

(8-bit)

SCI

BEEP

TIMER A

RAM

512 or 1K

POWER

SUPPLY

V

SS

WATCHDOG

PWM-BRM*

8-bit ADC

PWM0 -> PWM3

(4-bit)

AIN0 -> AIN4

(5-channel)

V

DDA

V

SSA

PORT B

PB0 - > PB6

(7-bit)

TIMER B

CAN*

PORT D

PD0 -> PD7

(8-bit)

SPI

I2C*

LCD DRI V ER

+

LCD RAM (60x8)

S1 -> S60

(60-segment)

COM1 -> COM8

(60-common)

GLCD

VLCD,VLCD3/4,

VLCD1/2, VLCD1/4

PORT A

PA0 - > PA7

(8-bi t)

*availab l e on ST7258 9 version on l y

4

ST72589BW, ST72389BW

5/158

1.2 PIN DESCRIPTION

Figure 2. 128-Pin PQFP Package Pinout

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

S49

S50

S51

S52

S53

S54

S55

S56

S57

S58

S59

S60

S45

S46

S47

S48

S40

S39

S38

S37

S36

S35

S34

S33

S32

S31

S30

S29

S44

S43

S42

S41

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

V

LCD

V

DD_A

AIN0

AIN1

AIN2

AIN3

AIN4

V

SS_A

PWM0*

PWM1*

PWM2*

PWM3*

G

LCD

V

LCD1/4

V

LCD1/2

V

LCD3/4

33

34

35

36

37

38

RESET

VPP

V

DD_1

OSC1

OSC2

V

SS_1

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

EI5

EI5

S14

S13

S12

S11

S10

S9

S8

S7

S6

S5

S4

S3

S18

S17

S16

S15

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

COM6

COM5

COM4

COM3

COM2

COM1

V

DD_3

VSS

V

SS

V

SS_3

PD7

PD6

S2

S1

COM8

COM7

70

69

68

67

66

65

PD5 / SDAI*

PD4 / SCLI*

PD3 / SS

PD2 / SCK

PD1 / MOSI

PD0 / MISO

112

111

110

109

108

107

106

105

104

103

S28

S27

S26

S25

S24

S23

S22

S21

S20

S19

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

ICAP2_A / PC3

ICAP1_A / PC2

RDI / PC1

TDO / PC0

V

SS_2

V

DD_2

CAN_ RX */ PB6

CAN_ RX* / PB5

PB4

ICAP2_B / PB3

ICAP1_B / PB2

OCMP2_B / PB1

MCO / BEEP / PC7

CLK_A / PC6

OCMP2_A / PC5

OCMP1_A / PC4

48

47

46

45

44

43

42

41

40

39

OCMP1_B / PB0

NMI

PA7

PA6

PA5

PA4

PA3

PA2

PA1

PA0

EI4EI3EI2EI1

5

ST72589BW, ST72389BW

6/158

PIN DESCRIPTION (Cont’d)

Legend / Abbreviations:

Type: I = input, O = output, S = supply, CK = Clock

Output level: LCD = V

LCD

, V

LCD3/4

, V

LCD1/2

, V

LCD1/4

, or G

LCD

level.

Input level: C = CMOS 0.3V

DD

/0.7V

DD

Port configuration capabilities:

– Input: float = floating, wpu = weak pull-up, int = interrupt, ana = analog

– Output: OD = open drain, T = true open drain, PP = push-pull

Note: Reset configuration of each pin is bold.

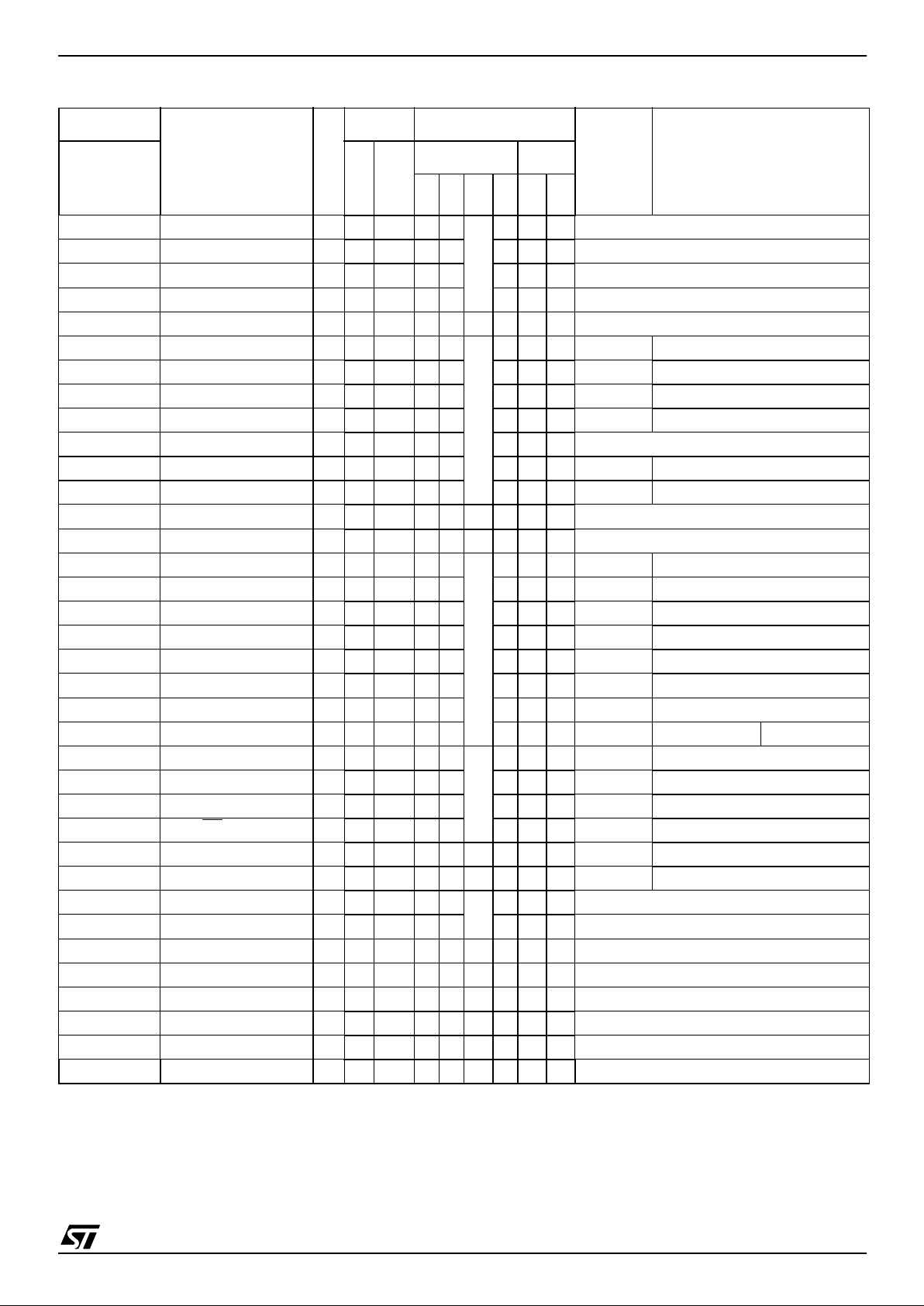

Table 1. Device Pin Description

Pin n°

Pin Name

Type

Level Port

Main func

tion

(after

reset)

Alternate function

PQFP128

Input

Output

Input Output

float

wpu

int

ana

OD

PP

1 ... 16 S45 ... S60 O LCD LCD Segment Analog Outputs

17 G

LCD

S LCD Ground Reference Volta ge

18 V

LCD1/4

S

LCD Supply Reference Voltage

19 V

LCD1/2

S

20 V

LCD3/4

S

21 V

LCD

S

22 V

DDA

S Analog Power Supply Voltage

23 A IN0 I X ADC Analog Input 0

24 A IN1 I X ADC Analog Input 1

25 A IN2 I X ADC Analog Input 2

26 A IN3 I X ADC Analog Input 3

27 A IN4 I X ADC Analog Input 4

28 V

SSA

S Analog Ground Voltage

29 PWM0* or NC O Pulse Width Modulator output 0*

30 PWM1*or NC O Pulse Width Modulator output 1*

31 PWM2* or NC O Pulse Width Modulator output 2*

32 PWM3* or NC O Pulse Width Modulator output 3*

33 RESET

I/O Top priority non maskable interrupt.

34 V

PP

I

Must be tied low in user mode. In the programming mode when available, this pin

acts as the programming voltage input

V

PP

.

35 V

DD_1

S Digital Main Supply Voltage

36 OSC1 CK These pins connect a parallel-resonant

crystal or an external source to the on-chip

main oscillator.

37 OSC2 CK

38 V

SS_1

S Digital Ground Voltage

39 PA0 I/O C X

EI1

X X Port A0

40 PA1 I/O C X X X Port A1

41 PA2 I/O C X X X Port A2

42 PA3 I/O C X X X Port A3

6

ST72589BW, ST72389BW

7/158

* available on ST72589 version only.

** available on ST72589 version only. Port D4 and D5 in open-drain output only for ST72589.

43 PA4 I/O C X

EI2

X X Port A4

44 PA5 I/O C X X X Port A5

45 PA6 I/O C X X X Port A6

46 PA7 I/O C X X X Port A7

47 NMI I No maskable interrupt input pin (floating)

48 PB0/OCMP1_B I/O C X

EI3

X X Port B0 Timer B Output Compare 1

49 PB1/OCMP2_B I/O C X X X Port B1 Timer B Output Compare 2

50 PB2/ICAP1_B I/O C X X X Port B2 Timer B Input Capture 1

51 PB3/ICAP2_B I/O C X X X Port B3 Timer B Input Capture 2

52 PB4 I/O C X X X Port B4

53 PB5/CANTX* I/O C X X X Port B5 CAN Transmit Data Output*

54 PB6/CANRX* I/O C X X X Port B6 CAN Receive Data Input*

55 V

DD_2

S Digital Main Supply Voltage

56 V

SS_2

S Digital Ground Voltage

57 PC0/TDO I/O C X

EI4

X X Port C0 SCI Transmit Data Out

58 PC1/RDI I/O C X X X Port C1 SCI Receive Data In

59 PC2/ICAP1_A I/O C X X X Port B2 Timer A Input Capture 1

60 PC3/ICAP2_A I/O C X X X Port B3 Timer A Input Capture 2

61 PC4/OCMP1_A I/O C X X X Port B0 Timer A Output Compare 1

62 PC5/OCMP2_A I/O C X X X Port B1 Timer A Output Compare 2

63 PC6/EXTCLK_A I/O C X X X Port C6 Timer A External Clock

64 PC7/MCO/BEEP I/O C X X X Port C7 Main clock-out Beep signal

65 PD0/MISO I/O C X

EI5

X X Port D0 SPI Master In / Slave Out Data

66 PD1/MOSI I/O C X X X Port D1 SPI Master Out / Slave In Data

67 PD2/SCK I/O C X X X Port D2 SPI Serial Clock

68 PD3/SS

I/O C X X X Port D3 SPI Slave Select (active low)

69 PD4/SCLI* I/O C X X X Port D4 I2C Clock**

70 PD5/SDAI* I/O C X X X Port D5 I2C Data**

71 PD6 I/O C X

EI5

X X Port D6

72 PD7 I/O C X X X Port D7

73 V

SS_3

S Digital Ground Voltage

74 V

SS

S Ground Voltage

75 V

SS

S Ground Voltage

76 V

DD_3

S Digital Main Supply Voltage

77 to 84 COM1 to COM8 O C LCD LCD Common (backplane) analog output

85 to 128 S1 to S44 O LCD LCD Segment Analog Outputs

Pin n°

Pin Name

Type

Level Port

Main func

tion

(after

reset)

Alternate function

PQFP128

Input

Output

Input Output

float

wpu

int

ana

OD

PP

ST72589BW, ST72389BW

8/158

1.3 REGISTER & MEMORY MAP

As shown in the Figure 3, the MCU i s capable of

addressing 64K bytes of memories and I/O registers.

The available memory locations consist of 128

bytes of register location, up to 1Kbyte of RAM, 60

bytes of LCD RAM and up to 24Kbytes of user program memory. The RAM space includes up to 256

bytes for the stack from 0100h to 01FFh.

The highest address bytes contain the user re set

and interrupt vectors.

Figure 3. Me m ory M a p

Table 2. Interrupt Vector Map

* available on ST72589 version only.

0000h

512 Bytes RAM

Program Memory

Interrupt & Reset Vectors

HW Registers

047Fh

0080h

Short Addressing

RAM (zero page)

Stack Area

256 Bytes

16-bit Addressing

RAM

007Fh

0480h

9FFFh

Reserved

0100h

01FFh

027Fh

0080h

(see Table 3)

A000h

FFDFh

FFE0h

FFFFh

(see Table 1)

LCD RAM

(60 Bytes)

04BBh

04BCh

0200h

00FFh

1024 Bytes RAM

or 047F h

24 KBytes

Program Memory

16 KBytes

BFFFh

C000h

Vector Address Description Remarks

FFE0-FFE1h

FFE2-FFE3h

FFE4-FFE5h

FFE6-FFE7h

FFE8-FFE9h

FFEA-FFEBh

FFEC-FFEDh

FFEE-FFEFh

FFF0-FFF1h

FFF2-FFF3h

FFF4-FFF5h

FFF6-FFF7h

FFF8-FFF9h

FFFA-FFFBh

FFFC-FFFDh

FFFE-FFFFh

I2C interrupt vector*

SCI interrupt vector

TIMER B interrupt vector

TIMER A interrupt vector

SPI interrupt vector

CAN interrupt vector*

Not used

MCC interrupt vector

External interrupt vector (EI5: port D)

External interrupt vector (EI4: port C)

External interrupt vector (EI3: port B)

External interrupt vector (EI2: port A7..4)

External interrupt vector (EI1: port A3..0)

Non maskable external interrupt vector (NMI)

TRAP (software) interrupt vector

RESET vector

Internal Interrupt

External Interrupt

CPU Interrupt

ST72589BW, ST72389BW

9/158

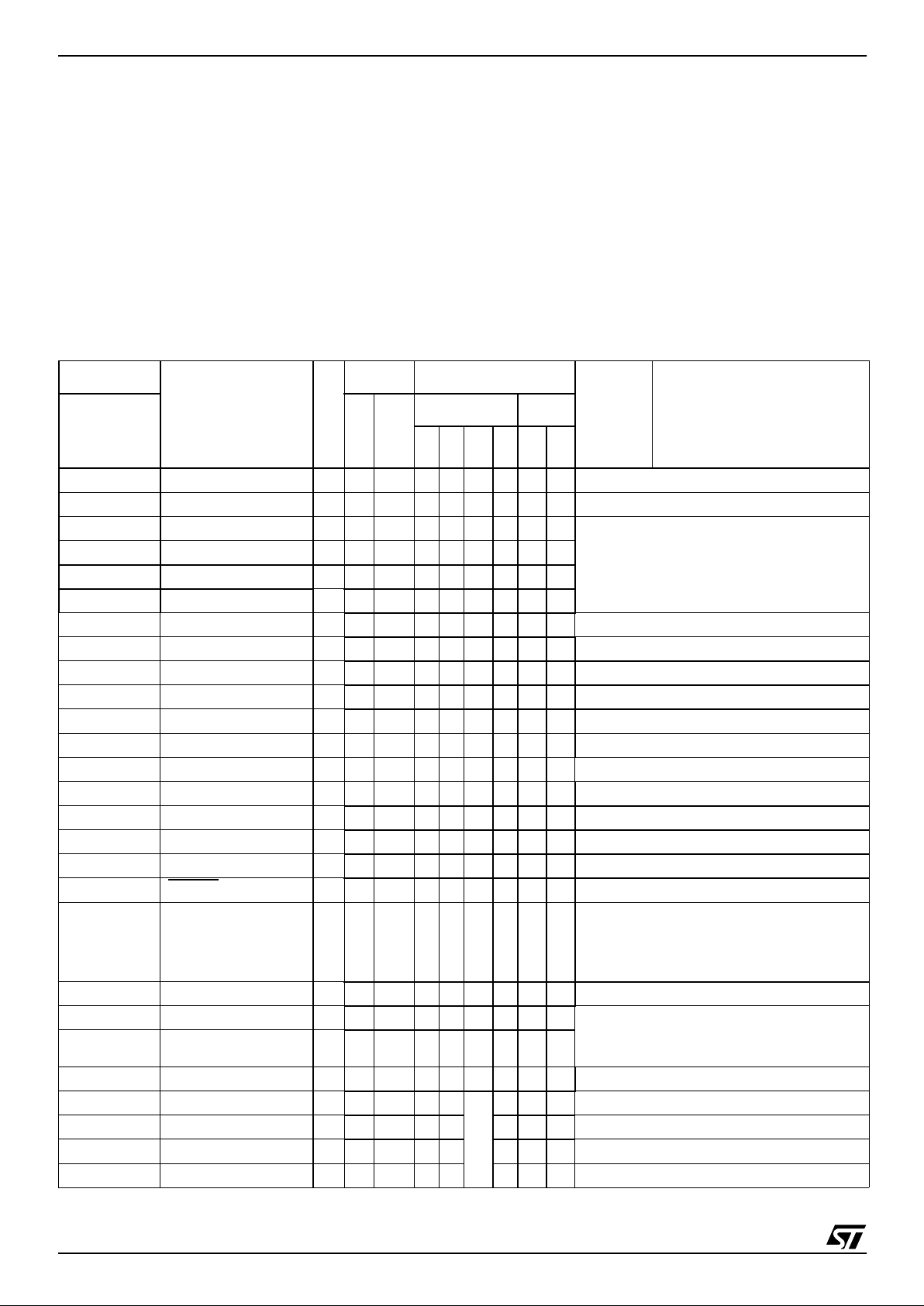

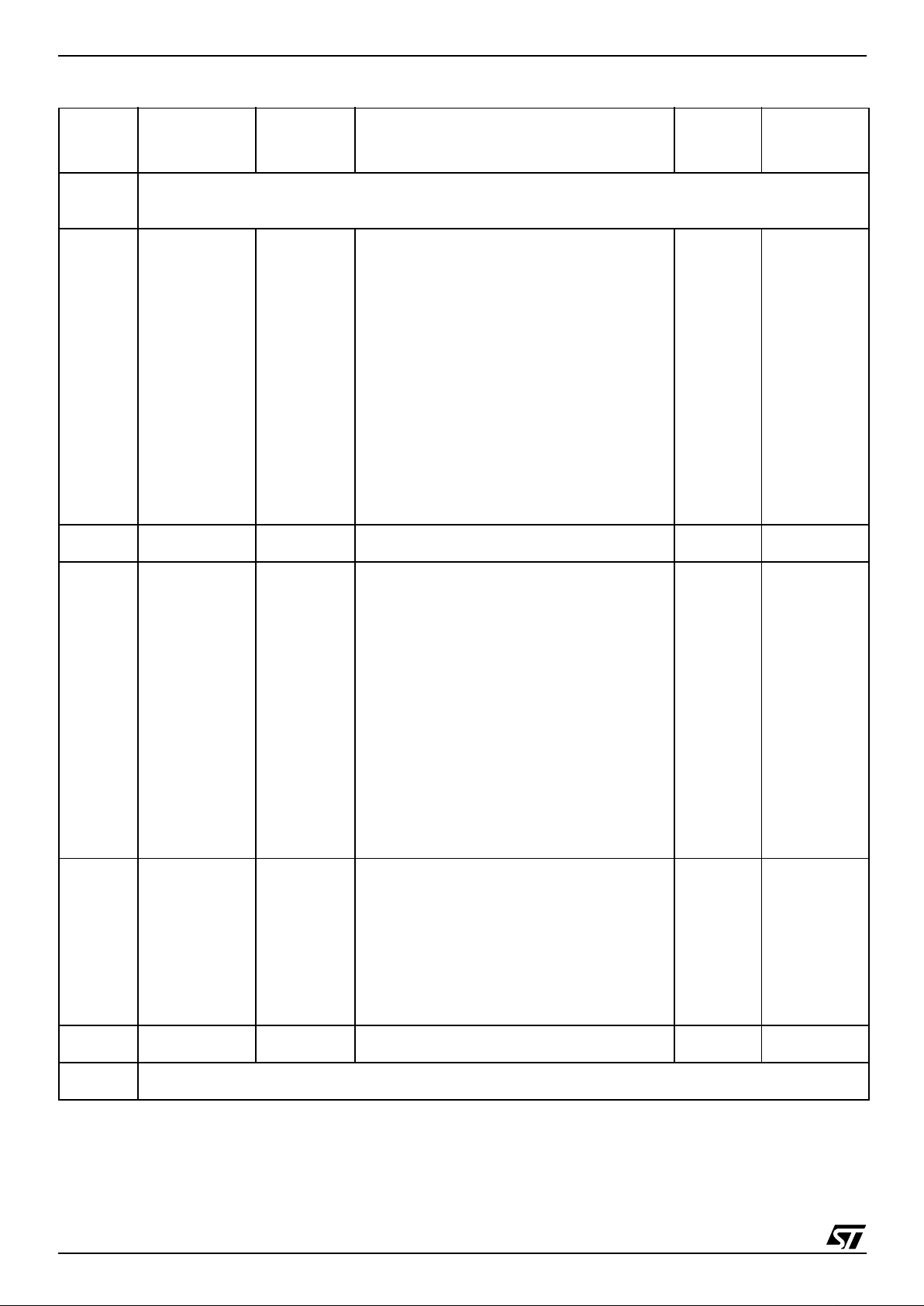

Table 3. Hardware Register M ap

Address B lock

Register

Label

Register Name

Reset

Status

Remarks

0000h

0001h

0002h

Port A

PADR

PADDR

PAOR

Port A Data Register

Port A Data Direction Register

Port A Option Register

00h

00h

00h

R/W

R/W

R/W

0003h Reserved Area (1 Byte)

0004h

0005h

0006h

Port B

PBDR

PBDDR

PBOR

Port B Data Register

Port B Data Direction Register

Port B Option Register

00h

00h

00h

R/W

R/W

R/W.

0007h Reserved Area (1 Byte)

0008h

0009h

000Ah

Port C

PCDR

PCDDR

PCOR

Port C Data Register

Port C Data Direction Register

Port C Option Register

00h

00h

00h

R/W

R/W

R/W

000Bh Reserved Area (1 Byte)

000Ch

000Dh

000Eh

Port D

PDDR

PDDDR

PDOR

Port D Data Register

Port D Data Direction Register

Port D Option Register

00h

00h

00h

R/W

R/W

R/W

000Fh

to

001Bh

Reserved Area (13 Bytes)

001Ch

001Dh

001Eh

001Fh

ITC

ISPR0

ISPR1

ISPR2

ISPR3

Interrupt Software Priority Register 0

Interrupt Software Priority Register 1

Interrupt Software Priority Register 2

Interrupt Software Priority Register 3

FFh

FFh

FFh

FFh

R/W

R/W

R/W

R/W

0020h MISCR1 Miscellaneous Register 1 00h R/W

0021h

0022h

0023h

SPI

SPIDR

SPICR

SPISR

SPI Data I/O Register

SPI Control Register

SPI Status Register

xxh

0xh

00h

R/W

R/W

Read Only

0024h WATCHDOG WDGCR Watchdog Control Register 7Fh R/W

0025h Reserved Area (1 Byte)

0026h MCC MCCSR Main Clock Control / Status Register 00h R/W

0027h Reserved Area (1 Byte)

0028h

0029h

002Ah

002Bh

002Ch

002Dh

002Eh

I

2

C*

I2CCR

I2CSR1

I2CSR2

I2CCCR

I2COAR1

I2COAR2

I2CDR

I

2

C Control Register

I

2

C Status Register 1

I

2

C Status Register 2

I

2

C Clock Control Register

I

2

C Own Address Register 1

I

2

C Own Address Register 2

I

2

C Data Register

00h

00h

00h

00h

00h

00h

00h

R/W

Read Only

Read Only

R/W

R/W

R/W

R/W

ST72589BW, ST72389BW

10/158

002Fh

0030h

Reserved Area (2 Bytes)

0031h

0032h

0033h

0034h

0035h

0036h

0037h

0038h

0039h

003Ah

003Bh

003Ch

003Dh

003Eh

003Fh

TIMER A

TACR2

TACR1

TASR

TAIC1HR

TAIC1LR

TAOC1HR

TAOC1LR

TACHR

TACLR

TAACHR

TAACLR

TAIC2HR

TAIC2LR

TAOC2HR

TAOC2LR

Timer A Control Register 2

Timer A Control Register 1

Timer A Status Register

Timer A Input Capture 1 High Register

Timer A Input Capture 1 Low Register

Timer A Output Compare 1 High Register

Timer A Output Compare 1 Low Register

Timer A Counter High Register

Timer A Counter Low Register

Timer A Alternate Counter High Register

Timer A Alternate Counter Low Register

Timer A Input Capture 2 High Register

Timer A Input Capture 2 Low Register

Timer A Output Compare 2 High Register

Timer A Output Compare 2 Low Register

00h

00h

xxh

xxh

xxh

80h

00h

FFh

FCh

FFh

FCh

xxh

xxh

80h

00h

R/W

R/W

Read Only

Read Only

Read Only

R/W

R/W

Read Only

Read Only

Read Only

Read Only

Read Only

Read Only

R/W

R/W

0040h MISCR2 Miscellaneous Register 2 00h R/W

0041h

0042h

0043h

0044h

0045h

0046h

0047h

0048h

0049h

004Ah

004Bh

004Ch

004Dh

004Eh

004Fh

TIMER B

TBCR2

TBCR1

TBSR

TBIC1HR

TBIC1LR

TBOC1HR

TBOC1LR

TBCHR

TBCLR

TBACHR

TBACLR

TBIC2HR

TBIC2LR

TBOC2HR

TBOC2LR

Timer B Control Register 2

Timer B Control Register 1

Timer B Status Register

Timer B Input Capture 1 High Register

Timer B Input Capture 1 Low Register

Timer B Output Compare 1 High Register

Timer B Output Compare 1 Low Register

Timer B Counter High Register

Timer B Counter Low Register

Timer B Alternate Counter High Register

Timer B Alternate Counter Low Register

Timer B Input Capture 2 High Register

Timer B Input Capture 2 Low Register

Timer B Output Compare 2 High Register

Timer B Output Compare 2 Low Register

00h

00h

xxh

xxh

xxh

80h

00h

FFh

FCh

FFh

FCh

xxh

xxh

80h

00h

R/W

R/W

Read Only

Read Only

Read Only

R/W

R/W

Read Only

Read Only

Read Only

Read Only

Read Only

Read Only

R/W

R/W

0050h

0051h

0052h

0053h

0054h

0055h

0056h

0057h

SCI

SCISR

SCIDR

SCIBRR

SCICR1

SCICR2

SCIERPR

SCIETPR

SCI Status Register

SCI Data Register

SCI Baud Rate Register

SCI Control Register 1

SCI Control Register 2

SCI Extended Receive Prescaler Register

Reserved area

SCI Extended Transmit Prescaler Register

C0h

xxh

00xx xxxx

xxh

00h

00h

---

00h

Read Only

R/W

R/W

R/W

R/W

R/W

R/W

0058h LCD LCDCR LCD Control Register 00h R/W

0059h Reserved Area (1 Byte)

Address B lock

Register

Label

Register Name

Reset

Status

Remarks

ST72589BW, ST72389BW

11/158

* Note: available on ST72589 version only.

005Ah

005Bh

005Ch

005Dh

005Eh

005Fh

0060h

to

006Fh

CAN*

CANISR

CANICR

CANCSR

CANBRPR

CANBTR

CANPSR

CAN Interrupt Status Register

CAN Interrupt Control Register

CAN Control / Status Register

CAN Baud Rate Prescaler Register

CAN Bit Timing Register

CAN Page Selection Register

First address

to

Last address of CAN page X

00h

00h

00h

00h

23h

00h

--

R/W

R/W

R/W

R/W

R/W

R/W

See CAN

Description

0070h

0071h

ADC

ADCDR

ADCCSR

Data Register

Control/Status Register

xxh

00h

Read Only

R/W

0072h

0073h

Reserved Area (2 Bytes)

0074h

0075h

0076h

0077h

0078h

0079h

PWMBRM*

PWM0

BRM10

PWM1

PWM2

BRM32

PWM3

10-bit PWM / BRM Registers

00h

00h

00h

00h

00h

00h

R/W

R/W

R/W

R/W

R/W

R/W

Address Block

Register

Label

Register Name

Reset

Status

Remarks

ST72589BW, ST72389BW

12/158

1.4 MEMORIES AND PROGRAMMING MODES

1.4.1 EPROM Program Memory

The program memory of the OTP and EPROM devices can be programmed with EPROM programming tools available from STMicroelectronics

EPROM Erasure

EPROM devices are erased by exposure to high

intensity UV light admitted through the transparent

window. This exposure discharges the floating

gate to its initial state through induced photo current.

It is recommended that the EPROM devices be

kept out of direct sunlight, since the UV content of

sunlight can be su fficient to cause functional failure. Extended exposure to room level fluorescent

lighting may also cause erasure.

An opaque coating (paint, tape, label, etc...)

should be placed over the package window if the

product is to be operated under these lighting conditions. Covering the window also reduces I

DD

in

power-saving modes du e to photo-diode leakage

currents.

ST72589BW, ST72389BW

13/158

2 CENTRAL PROCE SSING UNIT

2.1 INTRODUCTION

This CPU has a full 8-bit architecture and contains

six internal registers allowing efficient 8-bit data

manipulation.

2.2 MAIN FEATURES

■ Enable executing 63 basic instructions

■ Fast 8-bit by 8-bit multiply

■ 17 main addressing modes (with indirect

addressing mode)

■ Two 8-bit index registers

■ 16-bit stack pointer

■ Low power HALT and WAIT modes

■ Priority maskable hardware interrupts

■ Non-maskable software/hardware interrupts

2.3 CPU REGISTERS

The 6 CPU registers shown in Figure 4 are not

present in the memory mapping and are accessed

by spec ifi c ins t ru c tio n s .

Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the res ults of the

arithmetic and logic calculations and to manipulate

data.

Index Registers (X and Y)

These 8-bit registers are used to create effective

addresses or as tempo rary storage areas f or data

manipulation. (The Cross -Assembler generates a

precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

Program Counter (PC)

The program counter is a 16-bit register containing

the address of the next instruction to be executed

by the CPU. It is made of two 8-bit registers PCL

(Program Counter Low which is the LSB) and PCH

(Program Counter High which is the MSB).

Figure 4. CPU Registers

ACCUMULATOR

X INDEX REGISTER

Y INDEX REGISTER

STACK POINTER

CONDITION CODE REGISTER

PROGRAM COUNTER

70

1C1I1HI0NZ

RESET VALUE = RESET VECTOR @ FFFEh-FFFFh

70

70

70

0

7

15 8

PCH

PCL

15

8

70

RESET VALUE = STACK HIGHER ADDRESS

RESET VALUE =

1X11X1XX

RESET VALUE = XXh

RESET VALUE = XXh

RESET VALUE = XXh

X = Undefined Value

ST72589BW, ST72389BW

14/158

CENTRAL PROC ESSING UNIT (Cont’d)

Condition Code Register (CC)

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code regist er contains the i nterrupt masks and four flags representative of the

result of the instruction just executed. This register

can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

Arithmetic Management Bits

Bit 4 = H

Half carry

.

This bit is set by hardware when a carry occurs between bits 3 and 4 of t he ALU during an ADD or

ADC instructions. It is reset by hardware during

the same instructio n s.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutine s .

Bit 2 = N

Negative

.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic,

logical or data manipulation. I t’s a copy of the result 7

th

bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(i.e. the most significant bit is a logic 1).

This bit is accesse d by the JRMI and JRPL instructions.

Bit 1 = Z

Zero

.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical

or data manipulation is zero.

0: The result of the last operation is different from

zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test

instructions.

Bit 0 = C

Carry/borrow.

This bit is set and cleared b y hardware and software. It indicates an overflow or an un derflow has

occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions

and tested by the JRC and JRNC instructions. It i s

also affected by the “bit test and branch”, shift and

rotate instructions.

Interrupt Managem ent B i ts

Bit 5,3 = I1, I0

Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

These two bits are set/cleared by hardware when

entering in interrupt. The loaded value is given by

the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/

cleared by software with the RIM, SIM, IRET,

HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more

details.

70

11I1HI0NZ

C

Interrupt Software Priorit y I1 I0

Level 0 (main) 1 0

Level 1 0 1

Level 2 0 0

Level 3 (= interrupt disable) 1 1

ST72589BW, ST72389BW

15/158

CENTRAL PROC ESSING UNIT (Cont’d)

Stack Poi nter (SP)

Read/Write

Reset Value: 01 FFh

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack.

It is then decremented after data has been pushed

onto the stack and incremented before data is

popped from the stack (see Figure 5).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hard ware. Following a n

MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack

higher address.

The least significant byte of the Stack Pointer

(called S) can be directly accessed by a LD instruction.

Note: When the lower limit is exceeded, the Stack

Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously

stored information is then o verwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to sav e the return address during a subroutine call and the CPU context during

an interrupt. The user may also directly manipulate

the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored

at the first location po inted t o by t he SP. Th en t he

other registers are stored in the next locations as

shown in Figure 5.

– When an interrupt is received, the SP is decre-

mented and the context is pushed on the stack.

– On return from interrupt, the SP is incremented

and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locat ion s i n the stack ar ea.

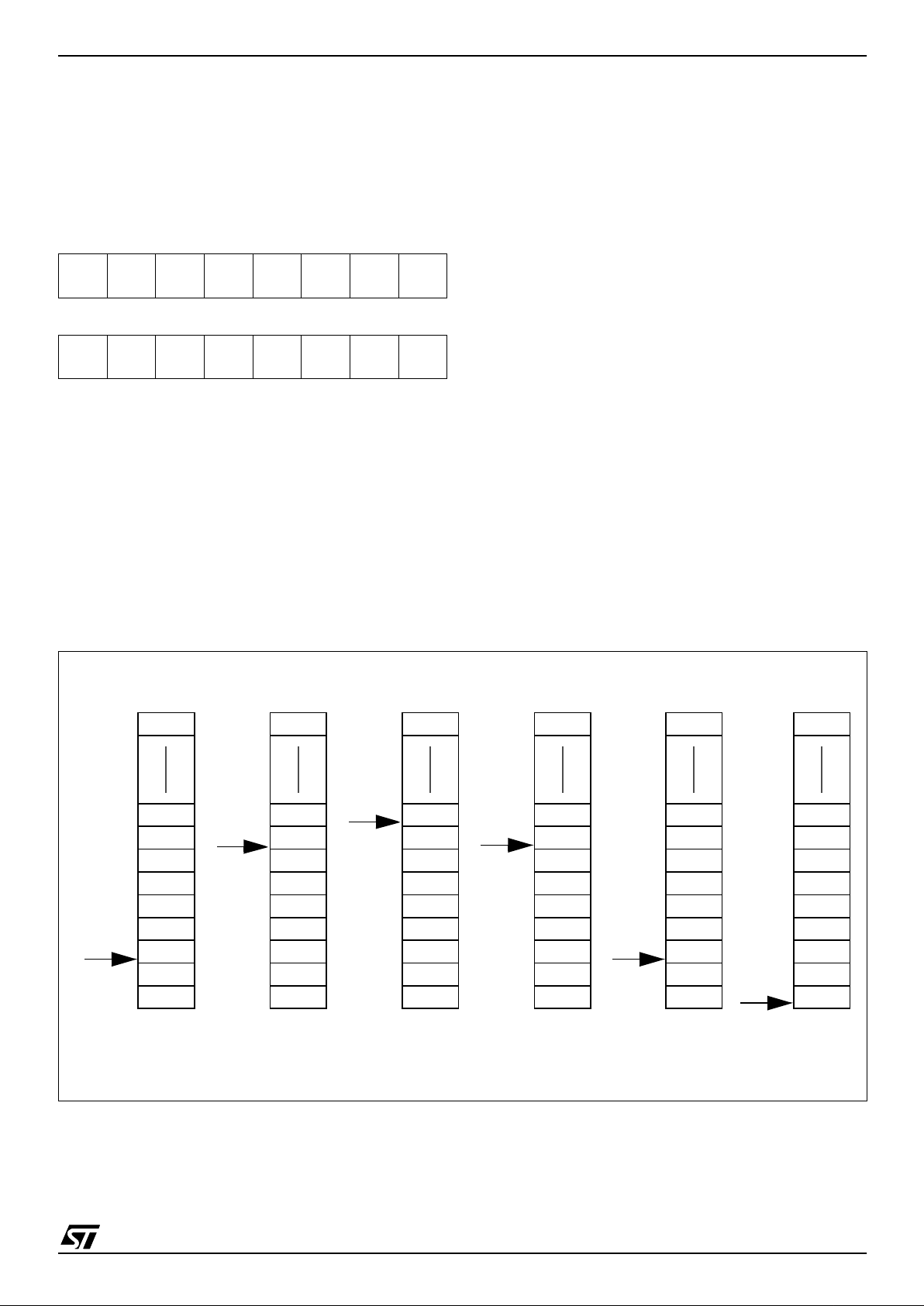

Figure 5. Stack Manipulation Example

15 8

00000001

70

SP7 SP6 SP5 SP4 SP3 SP2 SP1

SP0

PCH

PCL

SP

PCH

PCL

SP

PCL

PCH

X

A

CC

PCH

PCL

SP

PCL

PCH

X

A

CC

PCH

PCL

SP

PCL

PCH

X

A

CC

PCH

PCL

SP

SP

Y

CALL

Subroutine

Interrupt

Event

PUSH Y POP Y IRET

RET

or RSP

@ 01FFh

@ 0100h

Stack Higher Address = 01FFh

Stack Lower Address =

0100h

ST72589BW, ST72389BW

16/158

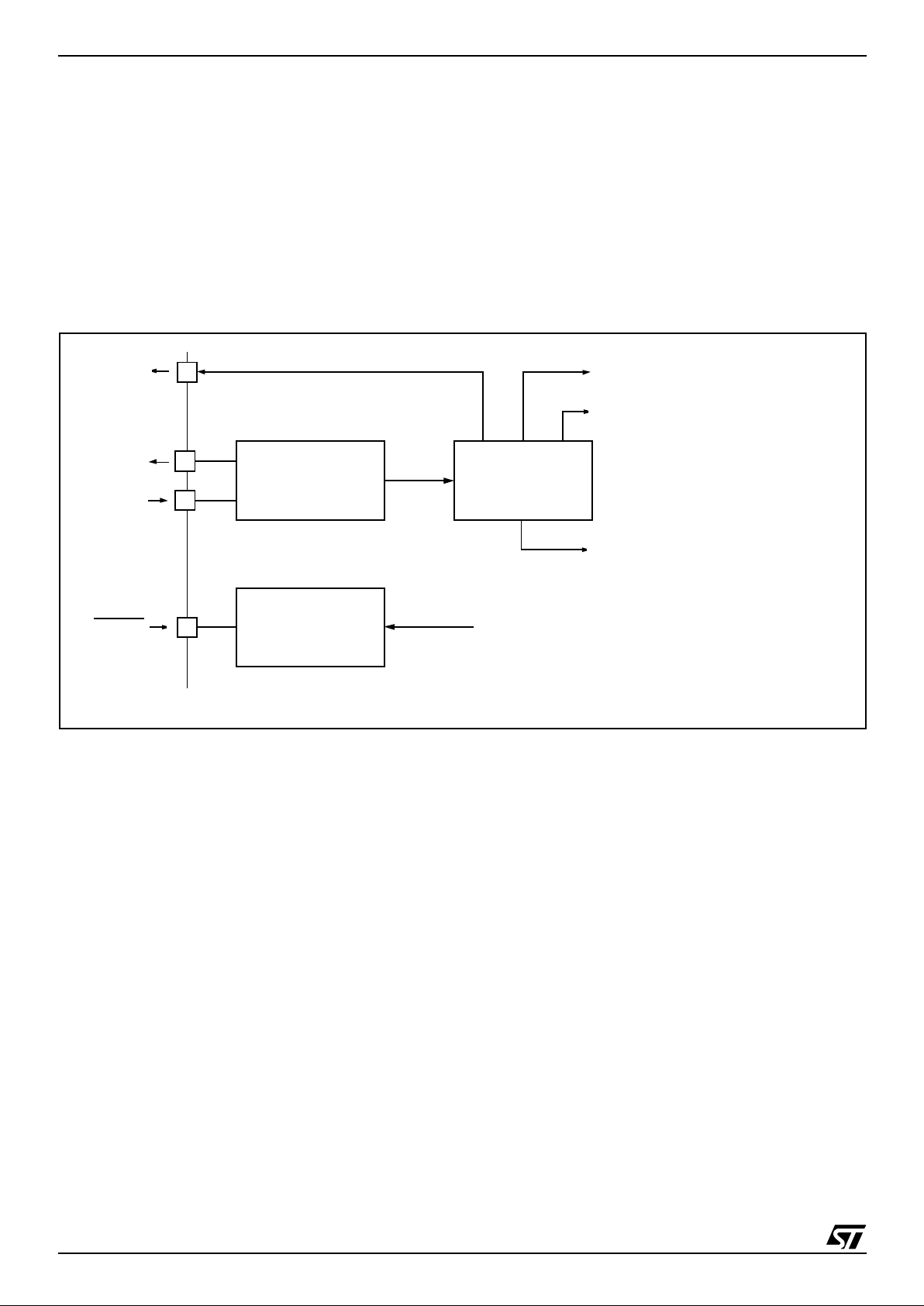

3 SUPPLY, RESET AND CLOCK MANAGE MENT

This chapter describes the following generic f eatures to guaranty the ST7 correct operation. An

overview is shown in Figure 6.

■ RESET Manager

■ Low Consum pti o n C ryst a l Os c illators

■ Main Clock controller (MCC)

Figure 6. Clock and RESET Management Overview

f

OSC

MAIN CLOCK

CONTROLLER

(MCC)

MAIN

OSCILLATOR

f

CPU

FROM

WATCHDOG

PERIPHERAL

MCC INTERRUPT

MCO

OSC1

OSC2

RESET

f

OSC

/2

RESET

ST72589BW, ST72389BW

17/158

3.1 RESET MANAGER

3.1.1 Introd uc tion

There are three sources of Reset:

– RESET

pin (external source)

– Power-On Reset (internal source)

– WATCHDOG (internal source)

The Reset Service Routine vector is located at address FFFEh-FFFFh.

Figure 7. Reset Block Diagram

3.1.2 External Reset

The RESET

pin is both an input and an open-drain

output with integrated R

ON

weak pull-up resistor

(see Figure 7). This pull-up has not a fixed value

but varies in accordance with the input voltage. It

can be pulled low by external circuitry to reset th e

device.

A RESET signal originating from an external

source must have a duration of at least t

PULSE

in

order to be recognized. The RESET sequence associated to this RES ET s ource is shown in Fi gure

8.

When the RESET is generated by a internal

source, during the two first phases of the RESET

sequence, the device RE SET

pin acts as an out-

put that is pulled low.

Figure 8. External RESET Sequences

f

CPU

COUNTE R

RESET

R

ON

V

DD

WATCHDOG R ESET

POR

INTERNAL

RESET

RESET

RUN

INTERNAL RESET

4096 CLOCK CYCLES

FETCH

VECTOR

RUN

RESET PIN

EXTERNALRESET SOURCE

t

PULSE

WATCHDOGRESET

DELAY

ST72589BW, ST72389BW

18/158

RESET MANAGER (Cont’d)

3.1.3 Internal Watchdog RESET

The RESET sequence generated by a internal

Watchdog counter underflow is reduced to 2 phases (see Figure 9).

Figure 9. Wat chdog RES E T Sequence

3.1.4 Reset Operation

The duration of the Reset condition, which is al so

reflected on the output pin, is fixed at 4096 internal

CPU Clock cycles. A Reset signal originating from

an external source must have a duration of at least

1.5 intern al CPU Clock cycles i n order to be recog nised. At the end of the Power-On Reset cycle, the

MCU may be held in the Reset condition by an External Reset signal. The RESET

pin may thus be

used to ensure V

DD

has risen to a point where the

MCU can operate correctly before the User program is run. Following a Reset event, or after exiting Halt mode, a 4096 CPU Clock cycle delay period is initiated in order to allow the oscillator to

stabilise and to ensure that recovery has taken

place from the Reset state.

During the Reset cycle, the device Reset pin acts

as an output that is pulsed low. In its high state, an

internal pull-up resistor is connected to the Reset

pin. This resistor can be pulled low by external circuitry to reset the device.

3.1.5 Power-on Reset

This circuit detects the ramping up of V

DD

, and

generates a pulse that is used to reset the application at V

POR

supply voltage.

Power-On Reset is desig ned exclusively to cope

with power-up conditions, and s houl d not be used

in order to attempt to detect a drop in the power

supply voltage.

Caution: to re-initialize the Power-On Reset, the

power supply voltage must fall below V

TN

, prior to

rise above V

POR

. If this condition is not respected,

on subsequent power-up the Reset pulse may not

be generated. An external Reset pulse may be required to correctly reactivate the circuit.

RESET

RUN

INTERNAL RESET

4096 CLOCK CYCLES

FETCH

VECTOR

RUN

RESET PIN

EXTERNALRESET SOURCE

WATCHDOGRESET

WATCHDOGUNDERFLOW

ST72589BW, ST72389BW

19/158

3.2 LOW CONSUMPTION OSCILLATOR

The oscillator of the ST72589 and ST72389 devices is a Crystal/Ceramic Resonator Oscillator. Its

architecture is based on a constant current to minimize the consumption. It can be used either with

an external resonator or an external source.

This oscillator allows a high accuracy to supply the

clock for the ST7 CPU and its internal peripherals.

Using a Crystal/Ceramic Resonator

The resonator and the load capacitanc es have to

be connected as shown in Figure 10 and have t o

be mounted as c lose as pos sible to the o scillator

pins in order to minimize output distortion and

start-up stabilization time.

Figure 10. Main Crystal/Ceramic Resonator

Using an External Clock Source

In this mode, a square clock signal with ~50% duty

cycle has to drive the OSC1 pin while the OSC2

pin is tied to ground (see F igure 11).

Figure 11. Main External Clock Source

OSC1 OSC2

LOAD

CAPACITANCES

ST7

C

L2

C

L1

OSC1 O SC 2

EXTERNAL

ST7

SOURCE

ST72589BW, ST72389BW

20/158

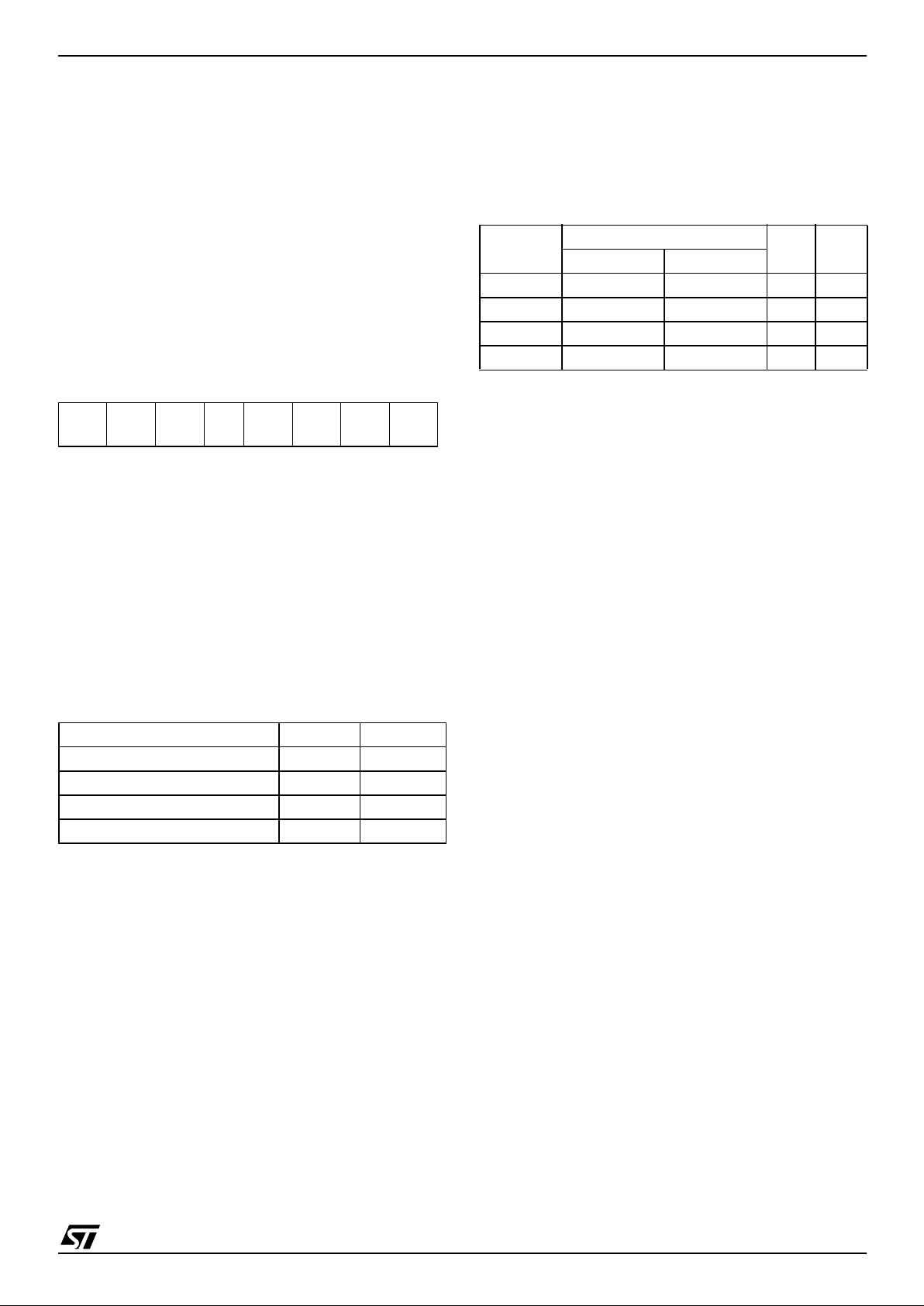

3.3 MAIN CLOCK CONTROLLER (MCC)

The MCC block supplies the clock for the ST7

CPU and its internal peripherals. It allows to m anage the power saving m odes such as the SLOW

and ACTIVE-HALT m odes . The whole functionality is managed by the Main Clock Control/Status

Register (MCCSR) and the M iscellaneous Register 2 (MISCR2).

The MCC block described in Figure 12 consists of:

– a programmable CPU clock prescaler

– a time base counter with inter rupt capabilit y

– a clock-out signal to supply external devices

The prescaler allows to select th e main clock frequency and is controlled with three bits of the

MCCSR: CP1, CP0 and SMS.

The counter allows to generate an interrupt based

on a accurate real time clock. Four different time

bases depending directly on f

OSC

are available.

The whole functionality is controlled by four bits of

the MCCSR register: TB1, TB0, OIE and OIF.

The clock-out capability allows to configure a dedicated I/O port pin as an f

OSC

/2 clock out to drive

external devices. It is controlled by a bit in the

MISCR2 register: MCO.

Figure 12. Main Clock Controller (MCC) Block Diagram

DIV 2, 4, 8, 16

MCC INTERRUPT

DIV 2

-

- -

TB1 TB0 OIE OIF

CPU CLOCK

MISCR2

PROGRAMMABLE

DIVIDER

CAN

TO CPU AND

PERIPHERALS

PERIPHERAL

f

OSC

f

CPU

MCO

PORT

FUNCTION

ALTERNATE

OSC1

OSC2

MAIN

OSCILLATOR

- --MCO-

0CP0CP1SMS

MCCSR

ST72589BW, ST72389BW

21/158

MAIN CLOCK CONTROLLER (Cont’d)

MISCELLANEOUS REGISTER 2 (MISCR2)

See description in MISCELLANEOUS Register

Section.

MAIN CLOCK CONTROL/STATUS REGISTER

(MCCSR)

Read/Write

Reset Value: 0000 0000 (00h)

Bit 0 = SMS

Slow mode select

This bit is set and cleared by software.

0: Normal mode. f

CPU

= f

OSC

/ 2

1: Slow mode. f

CPU

is given by CP1, CP0

See low power consumption mode and MCC

chapters for more details.

Bit 2:1 = CP1-CP0

CPU clock prescaler

These bits select the CPU clock prescaler which is

applied in the different slow modes. Their action is

conditioned by the setting of the SM S bit. These

two bits are set and cleared by software

Bit 4 = R eserved , alway s read as 0.

Bit 3:2 = TB1-TB0

Time base control

These bits select the programmable divider time

base. They are set and cleared by software.

A mod ification of th e time base is tak en into account at the end of the current period (previously

set) to avoid unwanted time shift. This allows to

use this time base as a real time clock.

Bit 1 = OIE

Oscillator interrupt enable

This bit set and cleared by software.

0: Oscillator interrupt disable

1: Oscillator interrupt enable

This interrupt allows to exit from ACTIVE-HALT

mode. When this bit is set, calling the ST7 software HALT instruction accesses the ACTIVEHALT power saving mode.

Bit 0 = OIF

Oscillator interrupt flag

This bit is set by hardware and cleared by software

reading the CSR register. It indicates when set

that the main oscillator has measured the selected

elapsed time (TB1:0).

0: timeout not reached

1: timeout reached

Warning: BRES and BSET instructions must not

be used on the MCCS R register to avoid unwanted clearing of OIF bit.

70

SMS CP1 CP0 0 TB1 TB0 OIE OIF

f

CPU

in SLOW mode CP1 CP0

f

OSC

/ 4 0 0

f

OSC

/ 8 0 1

f

OSC

/ 16 1 0

f

OSC

/ 32 1 1

Counter

Prescaler

Time Base

TB1 TB0

f

OSC

=8MHz f

OSC

=16MHz

32000 4ms 2ms 0 0

64000 8ms 4ms 0 1

160000 20ms 10ms 1 0

400000 50ms 25ms 1 1

ST72589BW, ST72389BW

22/158

MAIN CLOCK CONTROLLER (Cont’d)

Table 4. Main Clock Controller Register Map and Reset Values

Address

(Hex.)

Register

Label

76543210

0026h

MCCSR

Reset Value

SMS

0

CP1

0

CP0

00

TB1

0

TB0

0

OIE

0

OIF

0

ST72589BW, ST72389BW

23/158

4 INTERRUPTS & POWER SAVING MODES

4.1 INTERRUPTS

4.1.1 Introd uc tion

The ST7 enhanced interrupt management provides the following features:

■ Hardware interrupts

■ Software interrupt (TRAP)

■ Nested or concurrent interrupt management

with flexible interrupt priority and level

management:

– Up to 4 software programmable nesting levels

– Up to 16 interrupt vectors fixed by hardware

– 3 non maskable events: NMI, RESET, TRAP

This interrupt management is based on:

– Bit 5 and bit 3 of the CPU CC register (I1:0),

– Interrupt software priority registers (ISPRx),

– Fixed interrupt vector addresses locat ed at the

high addresses of the memory map (FFE0h to

FFFFh) sorted by hardware priority order.

This enhanced interrupt cont roller guarantees full

upward compatibility with the standard (not nested) ST7 interrupt controller.

4.1.2 Interrupt Masking and Processing Flow

The interrupt masking is managed by the I1 and I0

bits of the CC register and the ISPRx registers

which give the interrupt software priority level of

each interrupt vector (see Table 5 ). The processing flow is shown in Figure 13

When an interrupt request has to be serviced:

– Normal processing is suspended at the end of

the current instruction execution.

– The PC, X, A and CC registers are saved onto

the stack.

– I1 and I0 bits of CC register are set according to

the corresponding values in the ISPRx registers

of the serviced interrupt vector.

– The PC is then loaded with the interrupt vector of

the interrupt to service and the first instruction of

the interrupt service routine is fetched (refer to

“Interrupt Mapping” table for vector addresses).

The interrupt service routine should end with the

IRET instruction which c auses the contents of the

saved registers to be recovered from the stack.

Note: As a consequence of the IRET instruction,

the I1 and I0 bits will be restored from the stack

and the program in the previous level will resume.

Table 5. Interrupt Software Priority Levels

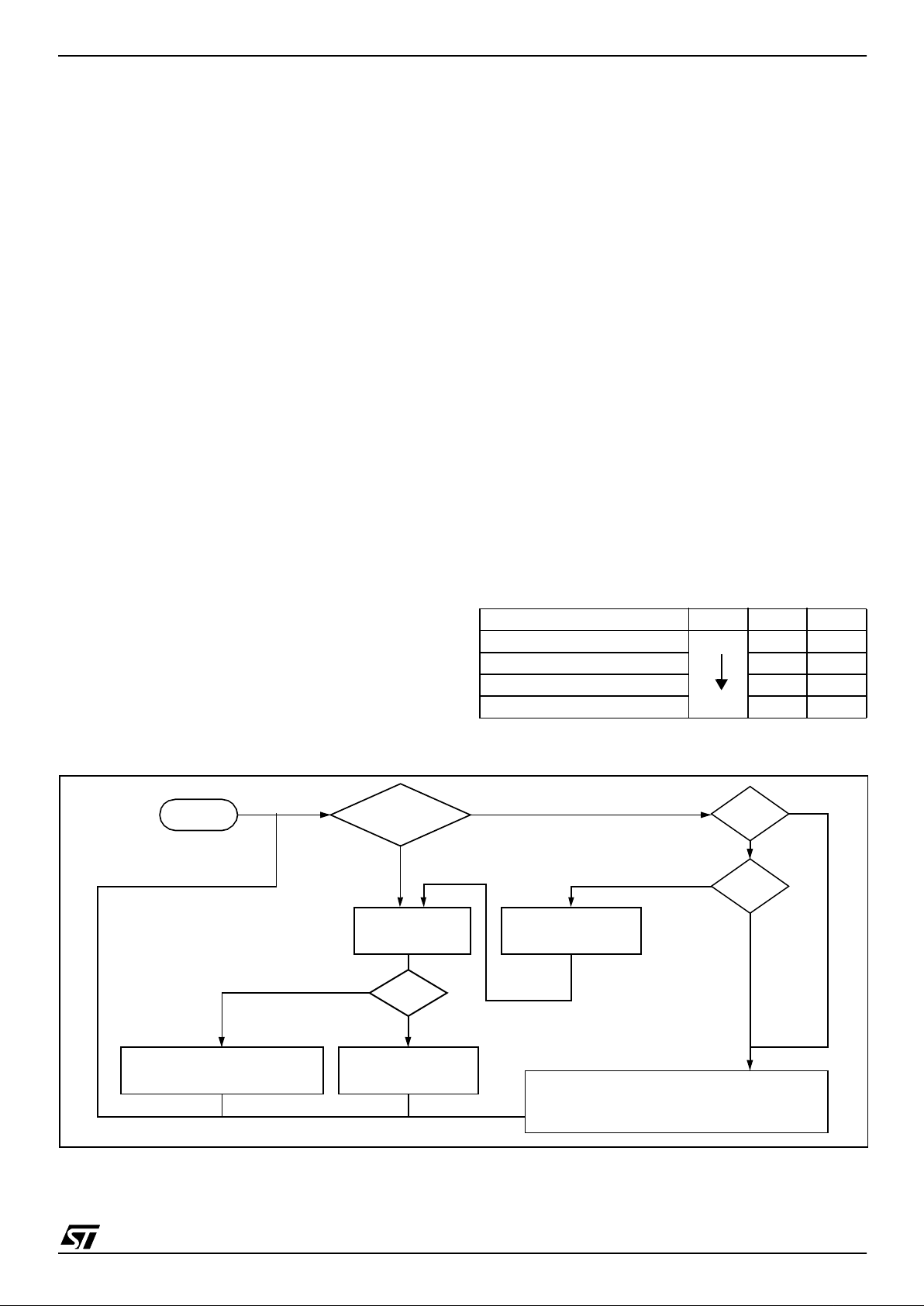

Figure 13. Int errupt Processing Flow c hart

Interrupt software priority Level I1 I0

Level 0 (main)

Low

High

10

Level 1 0 1

Level 2 0 0

Level 3 (= interrupt disable) 1 1

“IRET”

RESTORE PC, X, A, CC

STACK PC, X, A, CC

LOAD I1:0 FROM INTERRUPT SW REG .

FETCH NEX T

RESET

NMI

PENDING

INSTRUCTION

I1:0

FROM STACK

LOAD PC FROM INTERRUPT VECTOR

Y

N

Y

N

Y

N

Interrupt has the same or a

lower software priority

THE INTERRUPT

STAYS PENDING

than c u rrent one

Interrupt has a higher

softwarepriority

than current one

EXECUTE

INSTRUCTION

INTERRUPT

ST72589BW, ST72389BW

24/158

INTERRUPTS (Cont’d)

Servicing Pending In te rrup t s

As several interrupts can b e pen ding at the s ame

time, the interrupt to be taken into account is determined by the following two-step process:

– the highest software priority interrupt is serviced,

– if several interrupts have the same software pri-

ority then the interrupt with the highest hardware

priority is serviced first.

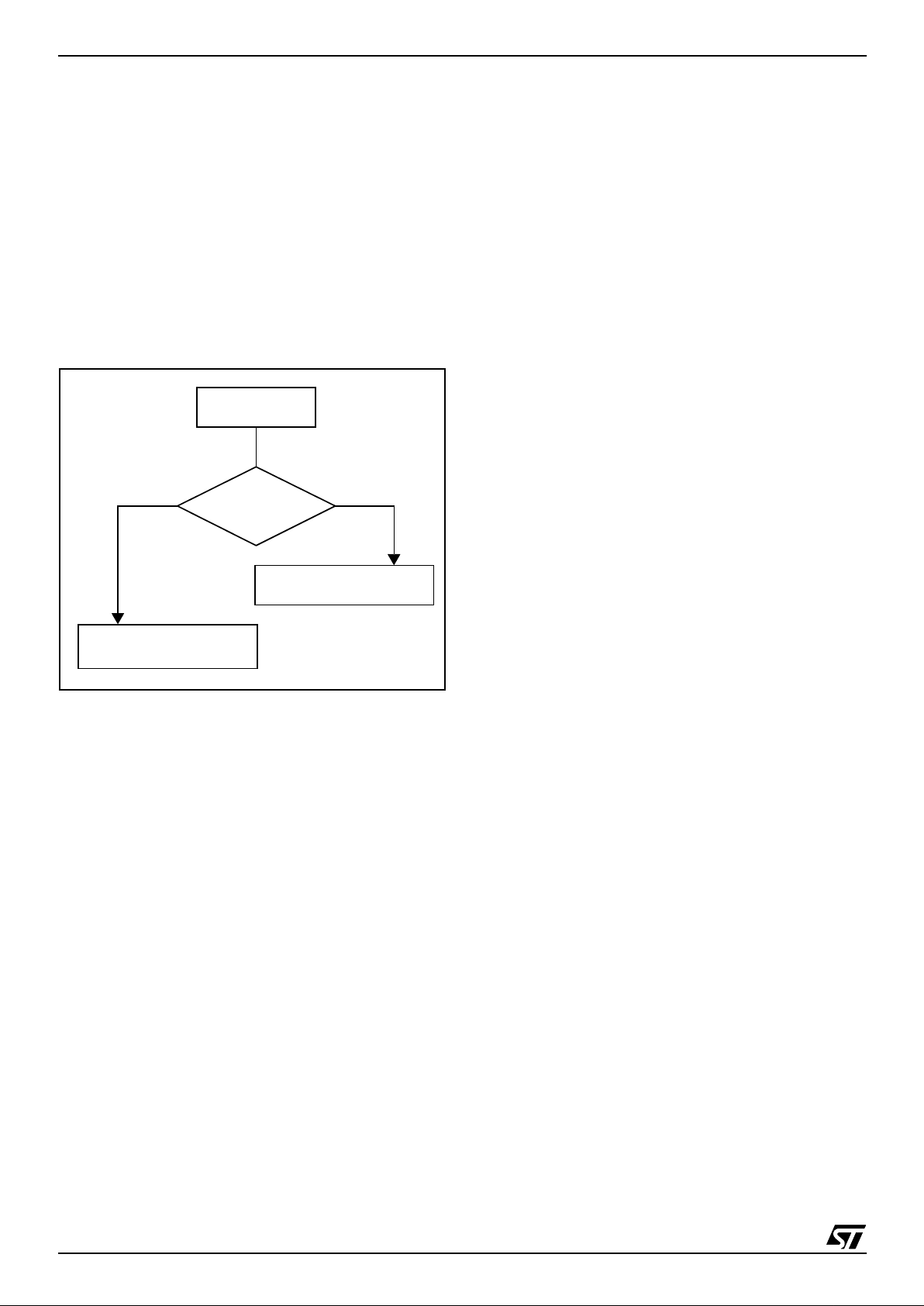

Figure 14 describes this decision process.

Figure 14. Priority Decision Process

When an interrupt request is not serviced immediately, it is latched and then processed when its

software priority combined with the hardware priority becomes the highest one.

Note 1: The hardware priority is exclusive while

the software one i s not. This allows the prev ious

process to succeed with only one interrupt.

Note 2: RESET, TRAP and NMI are non maskable

and they can be considered as havin g the highest

software priority in the decision process.

Different Interrupt Vector Sources

Two interrupt source types are managed by the

ST7 interrupt controller: the non-maskable type

(RESET, NMI, TRAP) and t he maskable type (external or from internal peripherals).

Non-Maskable Sources

These sources are processed regardless of the

state of the I1 and I0 bits of the CC register (see

Figure 13). After stacking the PC, X, A and CC

registers (except for RESET), the corresponding

vector is loaded in the PC register and t he I1 and

I0 bits of the CC are set to disable interrupts (level

3). These sources allow the processor to exit

HALT mode.

■ NM I (Non Maskable Hardware Interrupt)

This hardware interrupt occurs when a specific

edge is detected on the dedicated NMI pin. Its detailed specification is given in the Miscellaneous

register chapter.

■ TRA P (Non Maskable Sof tware Interrupt)

This software interrupt is serviced when the TRAP

instruction is executed. It will be serviced according to the flowchart on Figure 13 as an NMI.

■ RE SET

The RESET source has the highest priority in the

ST7. This means that the first current routine has

the highest software priority (level 3) and the highest hardware priority.

See the RESET chapter for more details.

Maskable Sources

Maskable interrup t vector sourc es can be servi ced

if the corresponding in terrupt is enabled and if its

own interrupt software priority (in ISPRx registers)

is higher than the one currently being serviced (I1

and I0 in CC register). If any of these two co nditions is false, the interrupt is la tched and thus remains pending.

■ External Interrupts

External interrupts allow the processor to exit from

HALT low power mode.

External interrupt sensitivity is software selectable

through the Miscellaneous registers (MISCRx).

External interrupt triggered on edge will be latched

and the interrupt request automatically cleared

upon entering the interrupt service routine.

If several input pins of a group connected to the

same interrupt line are selected simultaneously,

these w ill be log i cally ORed.

■ Peripheral Interrupts

Usually the peripheral interrupts cause the MCU to

exit from HALT mode except thos e mentioned in

the “Interrupt Mapping” table.

A peripheral interrupt occurs when a specific flag

is set in the peripheral status registers and if the

corresponding enable bit is set in the peripheral

control register.

The general sequence for clearing an interrupt is

based on an access to the status register followed

by a read or write to an associated register.

Note: The clearing sequence resets the internal

latch. A pending interrupt (i.e. waiting for being

serviced) will therefore be lost if the clear sequence is executed.

PENDING

SOFTWARE

Different

INTERRUPTS

Same

HIGHEST HARDWARE

PRIORITY SERVICED

PRIORITY

HIGHEST SOFTWARE

PRIORITY SERVICED

ST72589BW, ST72389BW

25/158

INTERRUPTS (Cont’d)

4.1.3 Interrupts and Low Power Modes

All interrupts allow the processor to exit the WAIT

low power mode. On the contrary, only external

and other specified interrupt s allow the processor

to exit the HALT modes (see column “Exit from

HALT” in “Interrupt Mapping” table). When several

pending interrupts are present while exiting HALT

mode, the first one serviced can only be an interrupt with exit from HALT mode capability and i t is

selected through the same decision process

shown in Figure 14

Note: If an interrupt, that is not able to Exit from

HALT mode, is pending with the highest priority

when exiting HALT mode, this interrupt is serviced

after the first one serviced.

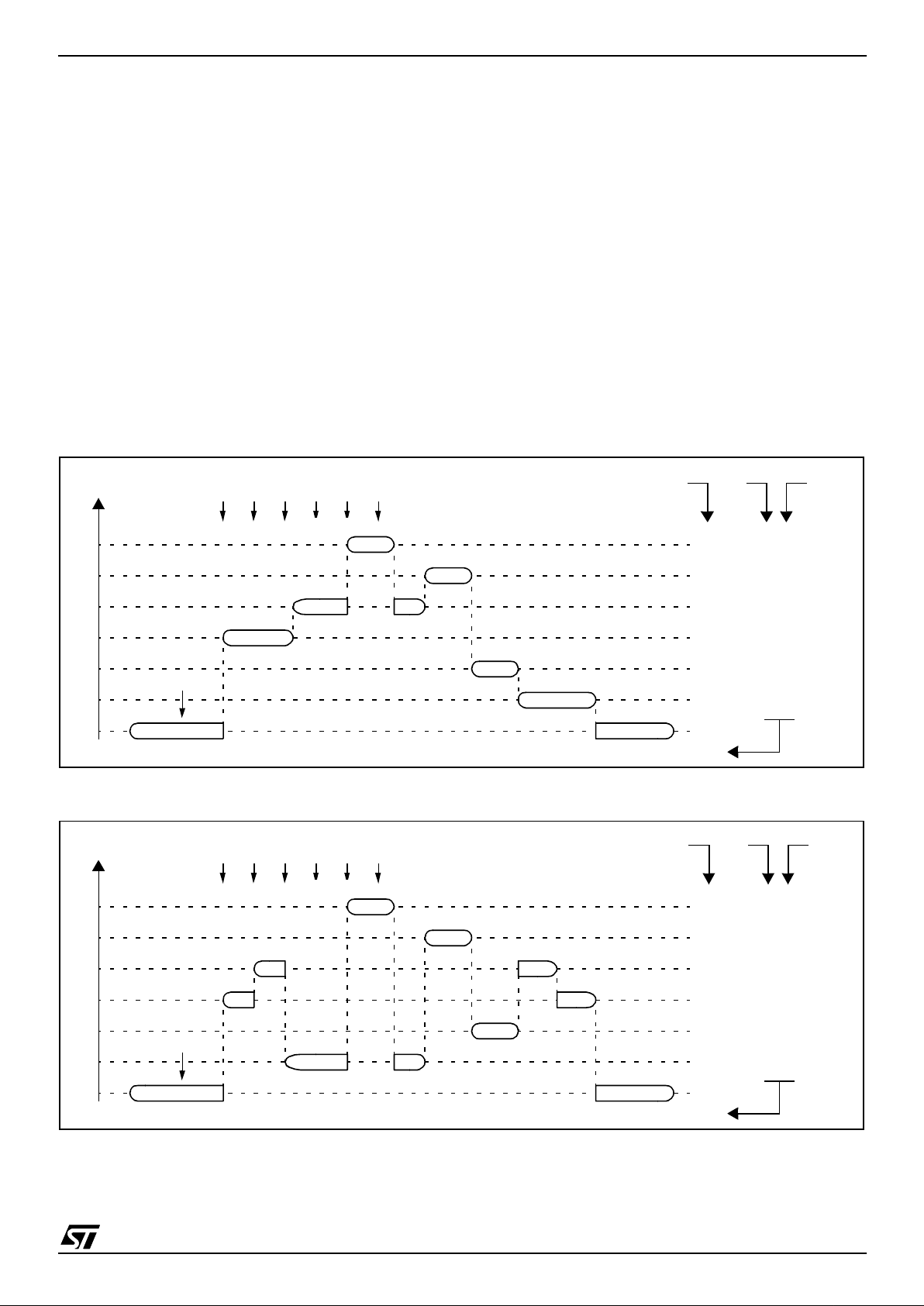

4.1.4 Concurrent and Nested Interrupt

Management

The following Figure 15 and Figure 16 show two

different interrupt management modes. The first is

called concurrent mode and do es not allow an interrupt to be interrupted, unlike the nested mode in

Figure 16 The interrupt hardware priority is given

in this order from the l owes t to the hi ghest: M A IN,

IT4, IT3, IT2, IT1, IT0, NMI. The software priority is

given for each interrupt.

Warning: A stack overflow may occur without notifying the software of the failure.

Figure 15. Con c u rre n t int erru pt m anagemen t

Figure 16. Nested interrupt management

MAIN

IT4

IT2

IT1

NMI

IT1

MAIN

IT0

I1

HARDWARE PRIORITY

SOFTWARE

3

3

3

3

3

3/0

3

11

11

11

11

11

11 / 10

11

RIM

IT2

IT1

IT4

NMI

IT3

IT0

IT3

I0

10

PRIORITY

LEVEL

USED STACK = 10 BYTES

MAIN

IT2

NMI

MAIN

IT0

IT2

IT1

IT4

NMI

IT3

IT0

HARDWARE PRIORITY

3

2

1

3

3

3/0

3

11

00

01

11

11

11

RIM

IT1

IT4

IT4

IT1

IT2

IT3

I1 I0

11 / 10

10

SOFTWARE

PRIORITY

LEVEL

USED STACK = 20 BYTES

ST72589BW, ST72389BW

26/158

INTERRUPTS (Cont’d)

4.1.5 Interrupt Register Description

CPU CC REGISTER INTERRUPT BITS

Read/Write

Reset Value: 111x 1010 (xAh)

Bit 5, 3 = I1, I0

Soft w a re In te r r u p t Priority

These two bits indicate the current interrupt software priority.

These two bits are set/cle ared by hardware whe n

entering in interrupt. The loaded value is given by

the corresponding bits in the interrupt software priority registers (ISPRx).

They can be also s et/cleared by s oft ware wi th the

RIM, SIM, HALT, WFI, IRET and PUSH/POP instructions (see “Interrupt Dedicated Instruction

Set” table).

*Note: NMI, TRAP and RESET events are non

maskable sources and can interrupt a level 3 program.

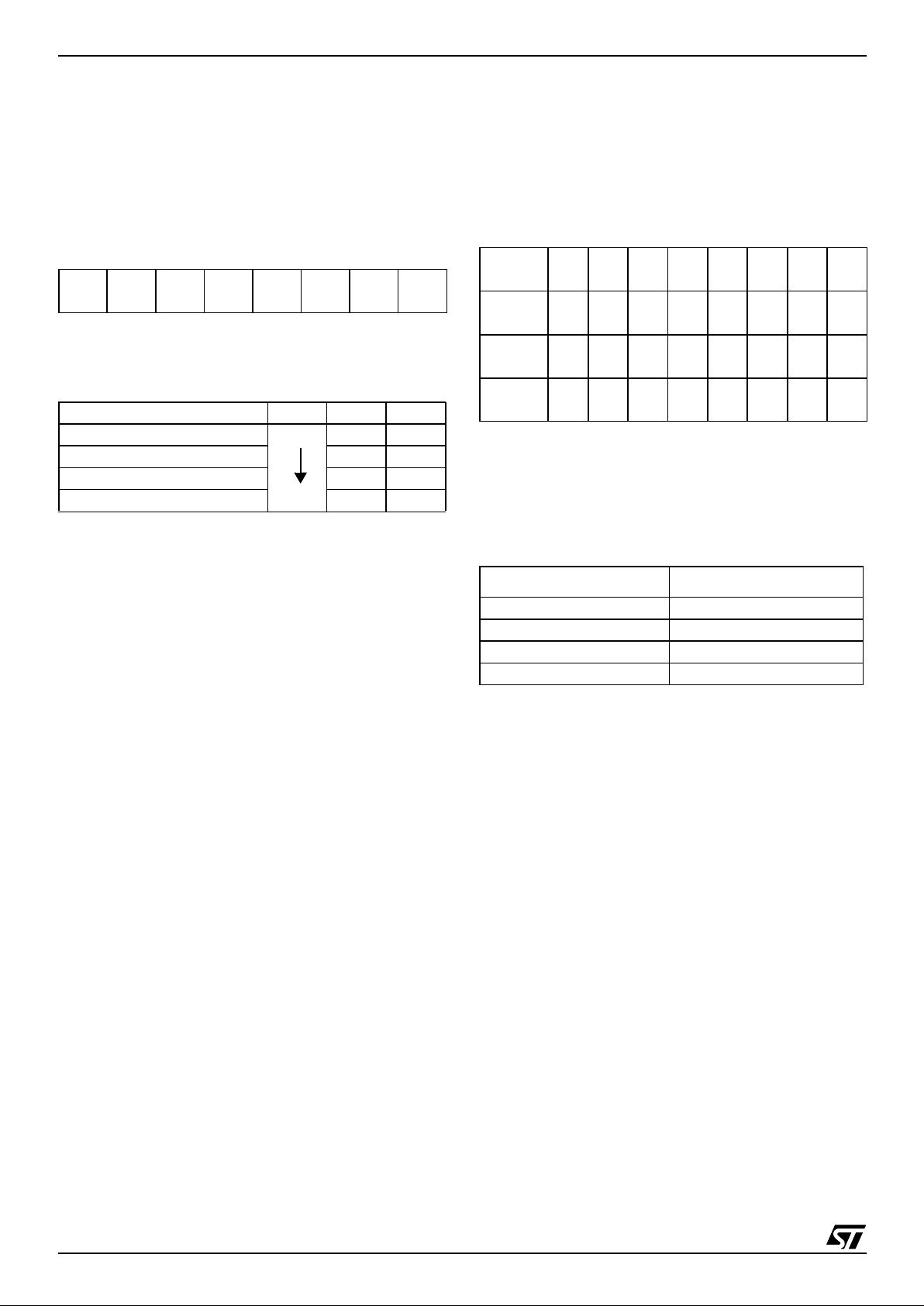

INTERRUPT SOFTWARE PRIORITY REGISTERS (ISPRX)

Read/Write (bit 7:4 of ISPR3 are read only)

Reset Values: 1111 1111 (FFh)

These four registers contain the interrupt software

priority of each interrupt vector.

– Each interrupt vector (except RESET and TRAP)

has corresponding bits in these registers where

its own software priority is stored. This correspondence is shown in the following table.

– Each I1_x and I0_x bit value in the ISPRx regis-

ters has the same meaning as the I1 and I0 bits

in the CC register.

– Level 0 can not be written (I1_x=1, I0_x=0). In

this case, the previously stored value is kept. (example: previous=CFh, write=64h, result=44h)

The RESET, TRAP and NMI vectors have no software priorities. When one is serviced, the I1 and I0

bits of the CC register are both set.

*Note: Bits in the ISPRx registers which correspond to the NMI can be read and written but they

are not significant in the interrupt process management.

Caution: If the I1_x and I0_x bits are modified

while the interrupt x is execu ted the following behaviour has to be considered: If the interrupt x is

still pending (new interrupt or flag not cleared) and

the new software priority is highe r than the previous one, the interrupt x is re-ent ered. Otherwise,

the software priority stays unchanged up to the

next interrupt request (after the IRET of the interrupt x).

70

11I1 H I0 NZC

Interrupt Software Priority Level I1 I0

Level 0 (main) Low

High

10

Level 1 0 1

Level 2 0 0

Level 3 (= interrupt disable*) 1 1

70

ISPR0 I1_3 I0_3 I1_2 I0_2 I1_1 I0_1 I1_0 I0_0

ISPR1 I1_7 I0_7 I1_6 I0_6 I1_5 I0_5 I1_4 I0_4

ISPR2 I1_11 I0_11 I1_10 I0_10 I1_9 I0_9 I1_8 I0_8

ISPR3 1 1 1 1 I1_13 I0_13 I1_12 I0_12

Vector address ISPRx bits

FFFBh-FFFAh I1_0 and I0_0 bits*

FFF9h-FFF8h I1_1 and I0_1 bits

... ...

FFE1h-FFE0h I1_13 and I0_13 bits

ST72589BW, ST72389BW

27/158

INTERRUPTS (Cont’d)

Table 6. Dedicated Interrupt Instruc tion Set

Note: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current

software priority up to the next IRET instruction or one of the previously mentioned instructions.

In order not to lose the cu rrent so ftwar e priorit y level, the RIM, SIM, HA LT, WF I and PO P CC ins tructio ns sho uld nev er

be used in an interrupt routine.

Table 7. I nte rrupt Mapp in g

Instruction New Description Function/Example I1 H I0 N Z C

HALT Entering Halt mode 1 0

IRET Interrupt routine return Pop CC, A, X, PC I1 H I0 N Z C

JRM Jump if I1:0=11 I1:0=11 ?

JRNM Jump if I1:0<>11 I1:0<>11 ?

POP CC Pop CC from the Stack Mem => CC I1 H I0 N Z C

RIM Enable interrupt (level 0 set) Load 10 in I1:0 of CC 1 0

SIM Disable interrupt (level 3 set) Load 11 in I1:0 of CC 1 1

TRAP Software trap Software NMI 1 1

WFI Wait for interrupt 1 0

N°

Source

Block

Description

Register

Label

Priority

Order

Exit

from

HALT

Address

Vector

RESET Reset

N/A

Highest

Priority

Lowest

Priority

yes FFFEh-FFFFh

TRAP Software Interrupt no FFFCh-FFFDh

0 NMI External Non Maskable Interrupt MISCR1 yes FFFAh-FFFBh

1 EI1 External Interrupt Port A3..0

N/A

FFF8h-FFF9h

2 EI2 External Interrupt Port A7..4 FFF6h-FFF7h

3 EI3 External Interrupt Port B6..0 FFF4h-FFF5h

4 EI4 External Interrupt Port C7..0 FFF2h-FFF3h

5 EI5 External Interrupt Port D7..0 FFF0h-FFF1h

6 MCC Main Oscillator Time Base Interrupt MCCSR FFEEh-FFEFh

7 Not used FFECh-FFE Dh

8 CAN* CAN Peripheral Interrupts CANISR FFEAh-FFEBh

9 SPI SPI Peripheral Interrupts SPISR no FFE8h-FFE9h

10 TIMER A TIMER A Peripheral Interrupts TASR FFE6h-FFE7h

11 TIMER B TIMER B Peripheral Interrupts TBSR FFE4h-FFE5h

12 SCIP SCI Peripheral Interrupts SCISR FFE2h-FFE3h

13 I2C* I2C Peripheral Interrupts I2CSRx FFE0h-FFE1h

ST72589BW, ST72389BW

28/158

INTERRUPTS (Cont’d)

Table 8. Nested Interrupts Register Map and Reset Values

Address

(Hex.)

Register

Label

76543210

001Ch

ISPR0

Reset Value

EI3 EI2 EI1 NMI

I1_3

1

I0_3

1

I1_2

1

I0_2

1

I1_1

1

I0_1

111

001Dh

ISPR1

Reset Value

ACC MCC EI5 EI4

I1_7

1

I0_7

1

I1_6

1

I0_6

1

I1_5

1

I0_5

1

I1_4

1

I0_4

1

001Eh

ISPR2

Reset Value

TIMER B TIMER A SPI CAN

I1_11

1

I0_11

1

I1_10

1

I0_10

1

I1_9

1

I0_9

1

I1_8

1

I0_8

1

001Fh

ISPR3

Reset Value1111

I2C SCI

I1_13

1

I0_13

1

I1_12

1

I0_12

1

ST72589BW, ST72389BW

29/158

4.2 POWER SAVI N G MO DES

4.2.1 Introd uc tion

To give a large measure of flexibility to the application in terms of power consumption, four main

power saving modes are implemented in the ST7.

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives

the device (CPU and embedded peripherals) by

means of a master clock which is based on the

main oscilla tor frequ ency divided by 2 (f

CPU

).

From Run mode, the different power saving

modes may be selected by setting the relevant

register bits or by calling the specific ST7 software

instruction whose action depends on the oscillator

status.

Figure 17. Power savi ng mode con sump tio n / transitions

4.2.2 HALT Modes

The HALT modes are the lowest power cons um ption modes of the MCU. They are en tered by executing the ST7 HALT instruction (see Figure 19).

Two different HALT modes can be distinguished:

– HALT : main os c illato r is turned of f,

– ACTIVE- HALT: only main oscillator is running.

The decision to enter either in HALT or AC TIVE-

HALT mode is given by the ma in osc illator enabl e

interrupt flag (OIE bit in CROSS-MCCSR register:

see Table 9).

When entering HALT modes, the I 1 and I 0 bits i n

the CC Register are forced to level 0 (“10”) to enable interrupts.

The MCU can exit HALT or ACTIVE-HALT modes

on reception of either an external interrupt, an in-

terrupt with Exit from Halt Mode capabi lity or a reset (see Table 2). A 4096 CPU clock cycles delay

is performed before the CPU operation resumes

(see Figure 18).

After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up.

Table 9. HALT Modes selection

Figure 18. HALT /ACTIVE-HALT Modes timing overview

POWER CONSUMPTION

WAIT SLOW RUNHALT ACTIVE-HALT

High

Low

SLOW WAIT

MCCSR

OIE

flag

Power Saving Mode entered when HALT

instruction is execute d

0 HALT (reset if watchdog enabled)

1 ACTIVE-HALT (no reset if watchdog enabled)

HALT OR ACTIVE-HALT

RUN

RUN

4096 CPU CYCLE

DELAY

RESET

OR

INTERRUPT

HALT

INSTRUCTION

FETCH

VECTOR

ST72589BW, ST72389BW

30/158

POWER SAVING MODES (Cont’d)

Standar d H ALT mode

In this mode the main os c illato r is turn ed off caus ing all internal processing to be stopped, including

the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get

their clock supply from another clock generator

(such as an external oscillator).

The HALT instruction when executed while the

Watchdog system is enabled, generates a Watchdog RESET.

When exiting HALT m ode by means of a RESET

or an interrupt, the oscillator is immediately turned

on and the 4096 CPU cycle delay is used to stabilize the oscillator.

Specific ACTIVE-HALT mode

As soon as t he in terrupt capability of the mai n oscillator is selected (OIE bit set), the HALT instruction will make the device enter a specific ACTIVEHALT power saving m ode i nstead of th e sta ndard

HALT one.

This mode con sists of having o nly the m ain osc illator and its associated counter running to keep a

wake-up time base. All other peripherals are not

clocked except the ones which get their clock supply from another clock generator (such as external

oscillator).

The safeguard against staying locked in this ACTIVE-HALT mode is insured by the oscillator interrupt.

Note: As soon as the interrupt capability of the oscillators is selected (OIE bit set), entering in AC TIVE-HALT mode while the Watchdog is active

does not generate a RESET.

This means that the device cannot to s pend more

than a defined delay in this power saving mode.

Figure 19. HALT modes flow-chart

HALT INSTRUCTION

OSCILLATOR

1

0

CPU

OSCILLATOR

PERIPHERALS

I1 AND I0 BITS

ON

OFF

10

OFF

Notes:

OIE BIT

CPU

OSCILLATOR

PERIPHERALS

I1 AND I0 BITS

OFF

OFF

10

OFF

RESET

EXTERNAL*

Y

N

N

Y

CPU

OSCILLATOR

PERIPHERALS

ON

OFF

OFF

INTERRUPT

HALT

ACTIVE-HALT

MAIN

FETCH RESET VECTOR

OR SERVICE INTERRUPT**

4096 clock cy cl es delay

CPU

OSCI LLATOR

PERIPHERALS

ON

ON

ON

External interrupt or internal interrupts with Exit from Halt Mode capability

*

**

Before servicing an interrupt, the CC register is pushed on the stac k.

WATCHDOG

YN

ENABLE

Loading...

Loading...