Page 1

PLC2/30 Programmable Controller

Programming and Operations Manual

Page 2

Important User Information

Because of the variety of uses for this equipment and because of the

differences between this solid state equipment and electromechanical

equipment, the user of and those responsible for applying this equipment

must satisfy themselves as to the acceptability of each application and

use of the equipment. In no event will Allen-Bradley Company, Inc. be

responsible or liable for indirect or consequential damages resulting from

the use or application of this equipment.

The illustrations, charts, and layout examples shown in this manual are

intended solely to illustrate the text of this manual. Because of the many

variables and requirements associated with any particular installation,

Allen-Bradley Company, Inc. cannot assume responsibility or liability for

actual use based upon the illustrative uses and applications.

No patent liability is assumed by Allen-Bradley Company, Inc. with

respect to use of information, circuits, equipment or software described in

this text.

Reproduction of the contents of this manual, in whole or in part, without

written permission of the Allen-Bradley Company, Inc. is prohibited.

1988 Allen-Bradley Company, Inc.

PLC is a registered trademark of Allen-Bradley Company, Inc.

WARNING: Warnings tell readers where people may be hurt if

procedures are not followed properly.

CAUTION: Cautions tell them where machinery may be

damaged or economic loss can occur if procedures are not

followed properly.

A Warning or Caution alerts you to:

a possible trouble spot

what causes the trouble to occur

the result of an improper action

how to avoid the situation

Page 3

Table of Contents

Introduction 11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.0 Introduction to This Manual 11. . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 General 11

1.2

Capabilities

1.2.1

Complementary I/O

Data Highway Compatibility

1.2.2

1.2.3 Industrial T

1.3

Additional Publications

1.4 Terms Used in This Manual 16

Hardware Considerations 21. . . . . . . . . . . . . . . . . . . . . . . . .

2.0 General 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Mode Select Switch

2.1

2.2 Memory Write Protect 22

2.3 RunTime Errors 23

2.4 Processor Diagnostic Indicators 24

2.5 PowerUp Recovery 25

2.6 Switch Group Assembly 25

Last State Switch

2.6.1

2.6.2 I/O Rack Number 26

2.7 Industrial Terminal 27

2.8 Local System Structure 27

2.9 Remote System Structure 28

2.10 Local/Remote System Structure 29

2.11 Hardware Addressing Modes 210

2.12 Auxiliary Power Supplies 210

2.12.1 1771P2 Auxiliary Power Supply 210

2.12.2 1777P2 Auxiliary Power Supply 211

2.12.3 1771P3, P4, and P5 Slot Power Supplies 211

2.12.4 1771P7 Power Supply 211

2.12.5 1771PSC Power Supply Chassis 211

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

erminal Compatibility

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14. . . . . . . . . . . . . . . . . . . . . . . . .

14. . . . . . . . . . . . . . . . . . . . .

15. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data Table 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.0 General 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Memory Structure 31

3.2 Memory Organization 32

3.2.1 Data Table 32

3.2.2 User Program 316

3.2.3 Message Storage Area 317

3.3 Hardware/Program Interface 317

3.3.1 Image Tables 317

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 4

Table of Contentsii

3.3.2 Instruction Address 318. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 Fundamental Operation 321

3.4 Data Table Documentation Forms 323

3.4.1 Data Table Word Map (1024 Word) 323

3.4.2 Data Table Map (128 Word) 324

3.4.3 Data Table Word Assignments (64 Word) 325

3.4.4 Data T

3.4.5 Sequencer T

3.4.6

3.4.7 Timer/Counter Assignments 329

3.4.8 Data Storage Assignments 329

able Bit Assignments

able Bit Assignments

I/O Assignments

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . .

326. . . . . . . . . . . . . . . . . . . . . . . .

327. . . . . . . . . . . . . . . . . . . .

328. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

Introduction

4.0 General 41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1

Notational Conventions

4.2 Ladder Diagram Logic 42

4.3 RelayType Instructions 43

4.3.1 Examine Instructions 43

Output Instructions

4.3.2

4.3.3 Branch Instructions 49

4.3.4 Ending a Program 412

4.3.5 Programming RelayType Instructions 413

4.4 Operating Instructions 414

4.4.1 Addressing 415

4.4.2 Help Directories 415

4.4.3 Searching 416

4.4.4

Editing

4.4.5 OnLine Programming 423

4.4.6 Clearing Memory 430

4.5 Program Recommendations 432

to Programming

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

41. . . . . . . . . . . . . . . . . . . . . . .

41. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

419. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timer and Counter Instructions 51. . . . . . . . . . . . . . . . . . . . .

5.0 General 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 Timer Instructions 52

5.1.1 Timer OnDelay Instruction 53

5.1.2 T

imer Of

fDelay Instruction 55. . . . . . . . . . . . . . . . . . . . . . . . .

5.1.3

Retentive T

Retentive T

5.1.4

5.1.5 Timer Accuracy for 10ms Timers 58

5.2 Counter Instructions 58

5.2.1 UpCounter Instruction 59

5.2.2 Counter Reset Instruction 511

5.2.3 DownCounter Instruction 512

5.2.4 Scan Counter Instruction 513

5.3 Cascading Timers or Counters 514

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

imer Instruction 56. . . . . . . . . . . . . . . . . . . . . . . . .

imer Reset Instruction 58. . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

Page 5

Table of Contents iii

5.4 Programming Timer and Counter Instructions 514. . . . . . . . . . . . .

5.5 Scan Time and Instruction Execution Times 517

5.5.1 Scan Time 517

5.5.2 Program for Determining Scan Time 518

5.6 Instruction Execution Time 519

5.6.1 Relay Type, Timer and Counter

Arithmetic, Output Override and I/O Update, Jump, and

Subroutine Instructions 519. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.2

WordtoFile, Sequencers, FIFO, W

Diagnostic, File Search, and Block Transfer Instructions 520. . . . . .

FiletoFile Move and File Complement

5.6.3

5.6.4

Logic Instructions FiletoFile AND, OR, XOR

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

, Data Manipulations,

ord and Bit Shifts, File

. . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

522. . . . . . . . . . . . . . . .

523. . . . . . . . . . . .

Data Manipulation Instructions 61. . . . . . . . . . . . . . . . . . . . .

6.0 General 61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Data Transfer Instructions 62

6.1.1

Get Instruction

Put Instruction

6.1.2

6.2 Data Comparison Instructions 64

6.2.1 Les and Equ Instructions 64

6.2.2

Get Byte and Limit T

6.2.3

Get Byte-Put Instruction

6.3 Programming Data Manipulation Instructions 69

Arithmetic Instructions

6.4

6.4.1 Add Instruction 612

6.4.2 Subtract Instruction 613

6.4.3

Multiply Instruction

6.4.4

Divide Instruction

6.5 Programming Arithmetic Instructions 615

6.6 BCD to Binary Conversion 616

6.6.1 Programming a BCD to Binary Conversion Instruction 617

6.7 BinarytoBCD Conversion 618

6.7.1 Programming a Binaryto BCD Conversion Instruction 618

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

62. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

est Instructions 67. . . . . . . . . . . . . . . . . . .

68. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . .

611. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

614. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

614. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . .

Output Override and I/O Update Instructions 71. . . . . . . . . . .

7.0 General 71. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 Output Overrides 71

7.2

I/O Updates

7.2.1 Scan Sequence 73

7.2.2

Immediate Input Instruction

7.2.3

Immediate Output Instruction

7.3

Programming Immediate I/O Instructions

7.4 Remote Fault Zone Programming 79

7.4.1 Dependent Programming 712

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

75. . . . . . . . . . . . . . . . . . . . . . . . .

76. . . . . . . . . . . . . . . . . . . . . . . .

78. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

Page 6

Table of Contentsiv

7.4.2 Independent Programming 713. . . . . . . . . . . . . . . . . . . . . . . . .

7.5

I/O Update T

7.5.1 Local Systems 715

7.5.2 Remote Systems 715

7.6 Watchdog Timer 716

imes 715. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peripheral Functions 81. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.0 General 81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1

Communication Rate Setting

8.2 Contact Histogram 82

8.3 Digital Cassette Recorder 84

8.3.1 Dumping Memory Content to Cassette Tape 84

8.3.2 Loading Memory from Cassette Tape 84

8.3.3 Verification 85

8.3.4 Program Verification 85

8.3.5 Displaying and Locating Errors 86

8.4 Data Cartridge Recorder 86

8.4.1 Dumping Memory Content onto Data Cartridge Tape 86

8.4.2 Loading Memory from a Data Cartridge Tape 87

8.4.3 Data Cartridge Verification 88

8.5 Ladder Diagram Dump 88

8.6 Total Memory Dump 88

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . .

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

81. . . . . . . . . . . . . . . . . . . . . . . . .

Report Generation 91. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.0 General 91. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.1 Report Generation Commands 93

9.1.1 Message Control Word File - MS, 0 94

9.1.2 Message Store - MS 95

9.1.3 Message Print - MP 96

9.1.4 Message Report - MR 97

9.1.5 Message Delete - MD 97

9.1.6 Message Index - MI 97

9.1.7 Control Codes and Special Commands 97

9.2

Manually Initiated Report Generation

9.3 Automatic Report Generation 912

9.3.1 Messages 16 913

9.3.2 Additional Messages 913

9.3.3 Example Programming 914

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

911. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Block Transfer 101. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.0 General 101. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.1 Basic Operation 101

10.2 Block Transfer Instructions 104

10.2.1 Data Address and Module Address 104

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

Page 7

Table of Contents v

10.2.2 Block Length 105. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.3 File Address 105

10.2.4

Enable Bit and Done Bit

10.3 Instruction Notes for Block Transfer Read and

Write Instructions 106

10.4 Causes of RunTime Errors 106

10.5 Programming Block Transfer Read and Write Instructions 106

10.6

Multiple Reads of Dif

10.7

Defining the Block T

10.8

Buf

fering Data 1012. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.9 Bidirectional Block Transfer 1014

10.9.1 Operation 1014

10.9.2 Data Address and Module Address 1017

10.9.3 File Address 1017

10.9.4 Block Length 1017

10.9.5 Programming Considerations 1018

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

106. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . .

ferent Block Lengths from One Module 108. .

ransfer Data Address Area 1011. . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

Jump Instructions and

11.0 General 111. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1 Jump Instruction 111

11.1.1 Programming Jump/ Subroutine Instructions 113

11.1.2

Multiple Jumps to the Same Label

11.2 Label Instruction 116

11.3 Jump to Subroutine Instruction 117

11.3.1 Subroutine Area 1110

11.3.2 Nested Subroutines 1111

11.3.3 Recursive Subroutine (Looping) Calls 1112

11.3.4 Subroutine Programming Considerations 1112

11.4 Return Instruction 1114

Subroutine Programming

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

. . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

111. . . . . . . .

113. . . . . . . . . . . . . . . . . . .

Data Transfer File Instructions 121. . . . . . . . . . . . . . . . . . . . . .

12.0 General 121. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1 File Concepts 121

12.1.1

File Definition

12.1.2

File Planning

12.1.3

File Instructions

12.1.4 Programming File Instructions 1211

12.1.5 File Instruction RunTime Error 1212

12.2 FiletoFile Move 1212

12.2.1 Programming FiletoFile Move Instructions 1214

12.3 FiletoWord Move 1215

12.3.1 Programming FiletoWord Move Instructions 1216

12.4 WordtoFile Move 1218

12.4.1 Programming WordtoFile Move Instructions 1219

12.5 Data Monitor Mode 1221

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

121. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

122. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

122. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 8

Table of Contentsvi

12.5.1 Accessing the Data Monitor Mode 1221. . . . . . . . . . . . . . . . . . .

12.5.2

Data Monitor Display

12.5.3 Cursor Controls 1225

12.5.4 Data Monitoring Procedures 1226

12.5.5 Entering and Changing Data 1227

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

1224. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Shift Register Instructions 131. . . . . . . . . . . . . . . . . . . . . . . . .

13.0 General 131. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1

Shift File Up

13.1.1

Programming Shift File Up Instruction

13.2

Shift File Down

13.2.1

Programming Shift File Down Instruction

13.3 FIFO Load and FIFO Unload 136

13.3.1 Programming FIFO Load and FIFO Unload Instruction 138

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . .

132. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

133. . . . . . . . . . . . . . . .

135. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

135. . . . . . . . . . . . . .

Bit Shifts 141. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.0 General 141. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.1

Bit Shift Left

14.1.1

Programming Bit Shift Left Instruction

Bit Shift Right

14.2

14.2.1

Programming Bit Shift Right Instruction

14.3

Examine Of

14.3.1 Programming Examine Of

14.4

Examine On Shift Bit

14.4.1

Programming Examine On Shift Bit Instruction

Set Shift Bit

14.5

14.5.1

Programming Set Shift Bit Instruction

14.6

Reset Shift Bit

14.6.1

Programming Reset Shift Bit Instruction

f Shift Bit

f Shift Bit Instruction

141. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

143. . . . . . . . . . . . . . . . .

145. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

146. . . . . . . . . . . . . . .

146. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

146. . . . . . . . . .

148. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

148. . . . . . . . . .

149. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

149. . . . . . . . . . . . . . . . .

1410. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1411. . . . . . . . . . . . . . .

Sequencer Instructions 151. . . . . . . . . . . . . . . . . . . . . . . . . . .

15.0 General 151. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.1 Sequencer Output Instruction 153

15.1.1 Sequencer Output Analogy 153

15.1.2 Operation of the Sequencer Output Instruction 154

15.1.3

Masking Output Data

15.1.4 Instruction Overview 156

15.1.5 Programming the Sequencer Output Instruction 156

15.2 Sequencer Input Instruction 1510

15.2.1 Operation of the Sequencer Input Instruction 1510

15.2.2 Masking Input Data 1510

15.2.3 Instruction Overview 1510

15.2.4 Programming the Sequencer Input Instruction 1511

15.3 Sequencer Load Instruction 1513

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . .

155. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . .

Page 9

Table of Contents vii

15.3.1 Operation of the Sequencer Load Instruction 1513. . . . . . . . . . .

15.3.2 Instruction Overview 1514

15.3.3 Programming the Sequencer Load Instruction 1514

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . .

File Logic Instructions 161. . . . . . . . . . . . . . . . . . . . . . . . . . . .

16.0 General 161. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16.1 FiletoFile Logic Instructions 161

16.1.1

FiletoFile AND

16.1.2

FiletoFile OR

16.1.3

FiletoFile XOR

16.1.4

File Complement

16.2 WordtoFile Logic Instructions 168

16.2.1 WordtoFile AND 169

16.2.2 WordtoFile OR 1611

16.2.3 WordtoFile XOR 1612

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

162. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

164. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

165. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

166. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

File Search and File Diagnostic Instructions 171. . . . . . . . . . .

17.0 General 171. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17.1 File Search 171

File Diagnostics

17.2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

174. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Troubleshooting Aids 181. . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.0 General 181. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.1

Bit Manipulation and Monitor

18.1.1

Bit Manipulation

18.1.2

Bit Monitor

18.2 Force On and Force Off Functions 183

18.3 Forced Address Display 184

18.4 Temporary End Instruction 185

18.5 ERR Message for an Illegal OP Code 185

Special

19.0 General 191. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.1 One Shot 191

19.1.1 Leading Edge OneShot 191

19.1.2 Trailing Edge OneShot 192

Programming T

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

echniques 191. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

182. . . . . . . . . . . . . . . . . . . . . . . .

182. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

183. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Addressing A1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.0 Appendix Objectives A1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.1 Addressing Your Hardware A1

A.2 Addressing Modes A2

A.2.1 2Slot Addressing A3

A.2.2 1Slot Addressing A8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 10

Table of Contentsviii

A.2.3 1/2Slot Addressing A11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.3 System Configurations A16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Number Systems B1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.0 General B1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1 Decimal Numbering System B1

B.2 Octal Numbering System B2

B.3 Binary Numbering System B3

B.3.1 Binary Coded Decimal B4

B.3.2 Binary Coded Octal B5

B.4 Hexadecimal Numbering System B6

. . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . .

Programming .01Second Timers C1. . . . . . . . . . . . . . . . . . . .

C.0 Introduction C1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.1 T

ime Base Selection

C.2 Timer Accuracy C2

C.3 10Msec Timers - T

C.4 Hardware/Processor Considerations C5

C.5 10Msec Timers - Programming Techniques C5

C.5.1 Scan Time C6

C.5.2 Program Execution C6

C.5.3 Programming Compensation C7

C.6 Program ScanT

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ypical Applications

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

ime Computation

C1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C4. . . . . . . . . . . . . . . . . .

C9. . . . . . . . . . . . . . . . . . . . .

Page 11

Introduction

Chapter

1

1.0

Introduction to This Manual

This manual presents the information you need to program and operate

your Allen-Bradley PLC-2/30 Programmable Controller.

After reading this manual, you should be able to:

establish system configurations consisting of:

- scanners

- interface modules

- input modules

- output modules

- power supplies

program:

- timers

- counters

- extended arithmetic functions

- relay-type functions

- and data transfer, for a few examples.

This manual is your entry into understanding the PLC-2/30 programmable

controller.

To find what the topics are in the individual chapters — Use the Table of

Contents.

1.1

General

To get an overview of what that chapter presents — Look in the

“General” section of each chapter.

To get a better understanding of slot addressing — Use the Appendix.

To find where a specific item is located in the text — Use the Index.

The PLC-2/30 programmable controller consists of:

The 1772-LP3 processor

An I/O structure (I/O chassis containing I/O modules)

11

Page 12

Chapter 1

Introduction

With a user-written program and appropriate I/O modules, the PLC-2/30

programmable controller can be used to control many types of industrial

applications such as:

Process control

Material handling

Palletizing

Measurement and gauging

Pollution control and monitoring

The 1772-LP3 processor has a read/write CMOS memory that stores user

program instructions, numeric values and I/O device status. The user

program is a set of instructions in a particular order that describes the

operations to be performed and the operating conditions. It is entered into

memory, rung by rung, in a ladder diagram and functional block display

format from the keyboard of a 1770-T3 or 1784–T50 terminal. The ladder

diagram symbols closely resemble the relay symbols used in hardwired

relay control systems. The functional block displays are an easy method of

programming and monitoring advanced instructions.

During program operation, the PLC-2/30 processor continuously monitors

the status of input devices and, based on user program instructions,

either energizes or de–energizes output devices. Because the memory is

programmable, the user program can be readily changed if required by the

application.

The PLC-2/30 processor’s functions include:

Relay-type functions (Examine On, Examine Off, Output Energize,

Output Latch, Output Unlatch and Branching)

Complete forced I/O

Data transfer

Data comparison

Three-digit, four-function arithmetic (+, –, ×, :–) :–:–

Timing functions: On-Delay and Off-Delay, Retentive and Nonretentive

with time bases of 1.0, 0.1 and 0.01 seconds (timing range 0.02 to 999

seconds).

Bidirectional counting (up or down) with a range of 0 to 999 counts.

Self-monitoring/diagnostic capabilities

Expandable data table

Memory capacity of 16,256 words

896 I/O device capacity is available in local or remote configurations.

896 inputs and 896 outputs when used with specific configurations.

Memory write protect

Program control instructions

- Jump

- Subroutines

12

Page 13

Chapter 1

Introduction

Functional Block Instructions

- Shift Register instructions

- File-to-File and Word-to-File Logic instructions

- File-to-File, Word-to-File and File-to-Word transfer instructions

Binary to BCD and BCD to Binary conversions

On-line programming

Data Highway and Data Highway II compatible

Sequencers

Contact histogram

Report generation

1.2

Capabilities

The data table for the 1772-LP3 processor can be expanded to 8,064 words

with an 8K memory or to 8,192 words with a 16K memory. However, an

8,064 word data table is impractical with an 8K memory since there would

be nothing available for the user program.

You can expand the data table from the default size of 128 words (1 rack)

to 256 words (2 racks, word address 377

word address 400

on, the data table must be expanded in 128-word

8

) in 2-word increments. From

8

sections. The I/O image tables, therefore, can be configured in size from

1 to 7 I/O racks. Each rack added, above one, increments by 10

the first

8

available address for timers and counters. Table 1.A lists the first available

timer/counter address when different numbers of racks are selected.

In addition, the processor can control up to 896 inputs and 896 outputs

for a total of 1,792 I/O points in a remote system of seven 128 I/O racks

(Table 1.A).

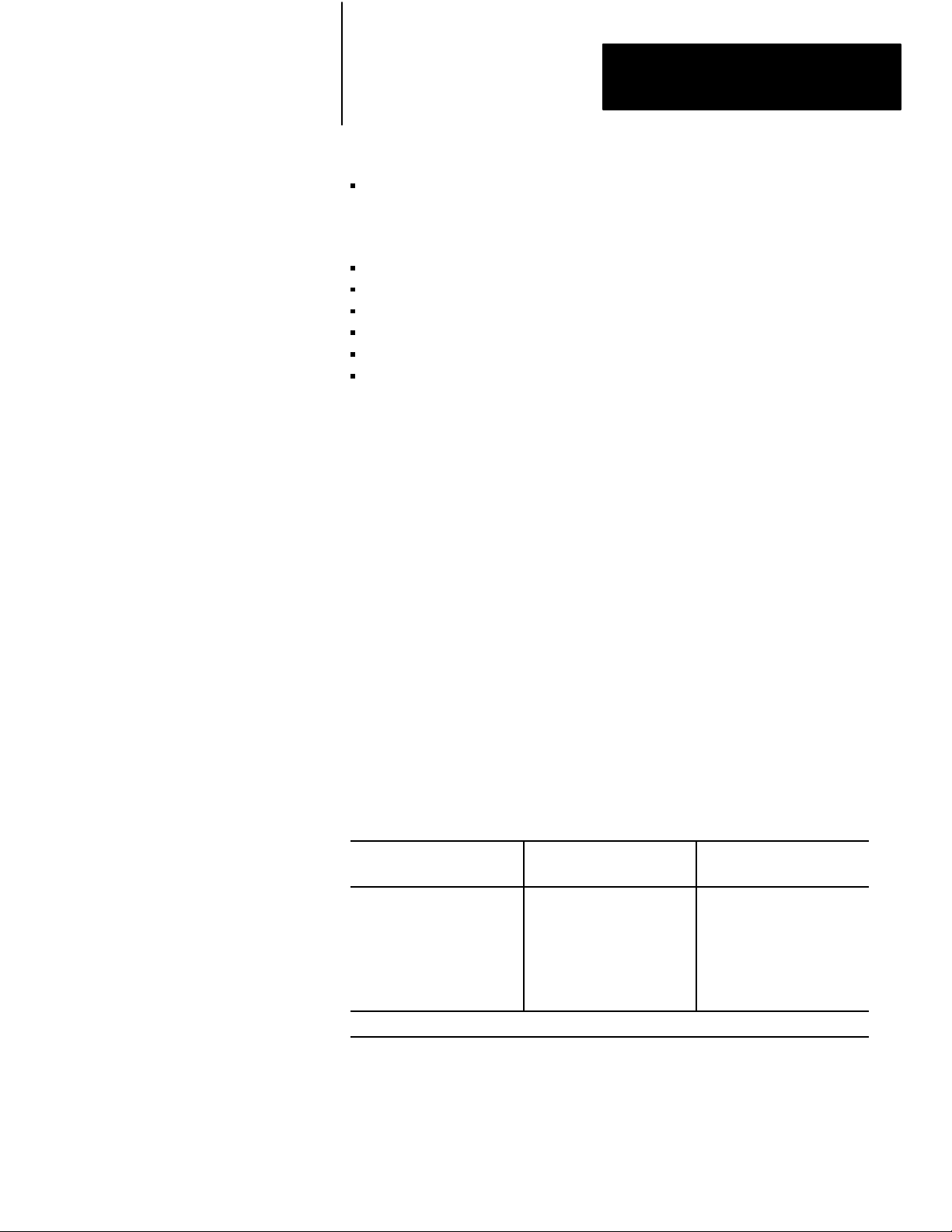

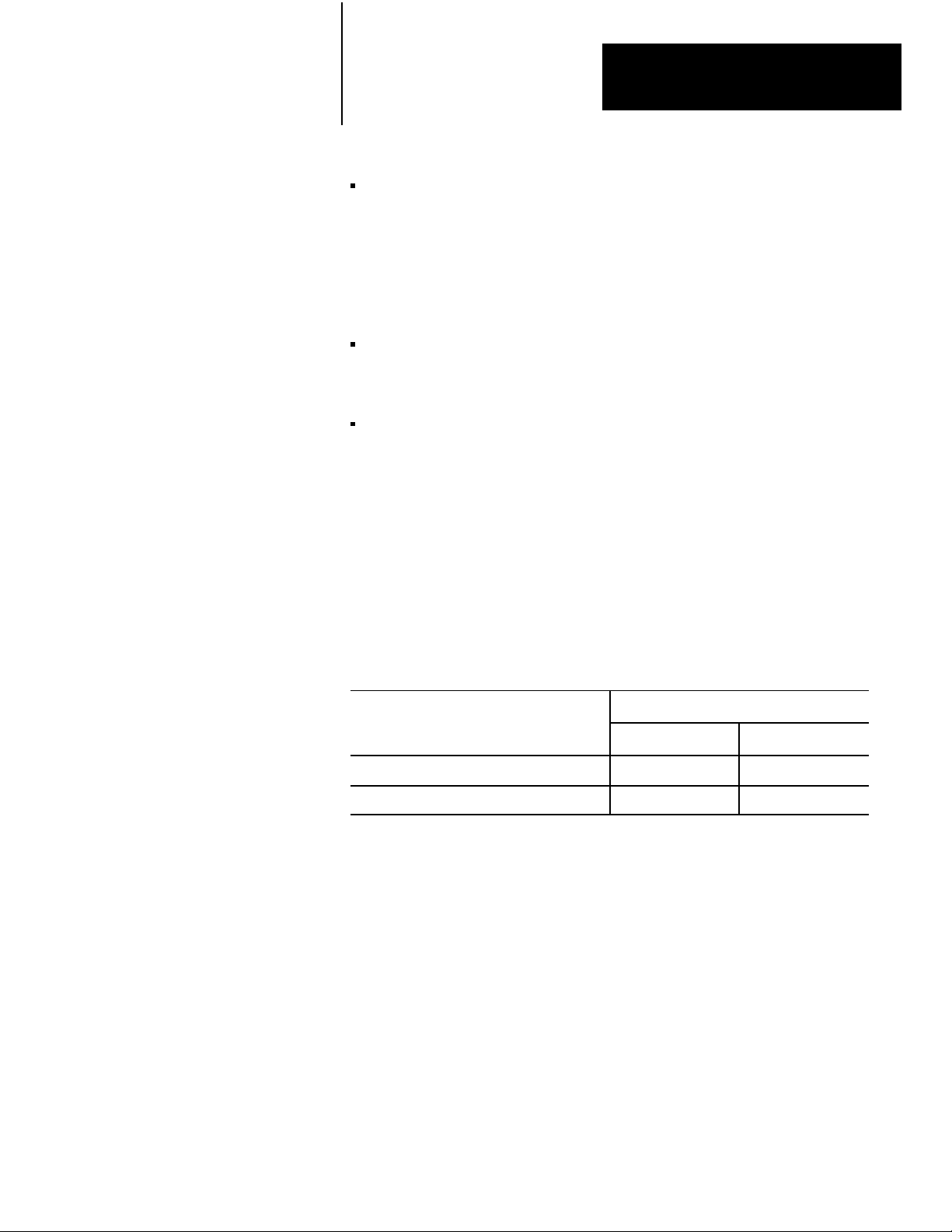

Table 1.A

PLC2/30

#I/O Racks Max. I/O Points1 (decimal)

Processor Capabilities (Cat. No. 1772LP3)

First Available T/C Address

(octal)

1

2

3

4

5

6

7

1

Without complementary I/O. With complementary I/O, maximum I/O points is double the tabulated number up to 1,792.

128

256

384

512

640

768

896

020

030

040

050

060

070

200

13

Page 14

Chapter 1

Introduction

1.2.1

Complementary

I/O

1.2.2

Data Highway Compatibility

When using a 1772-SD2 remote I/O scanner/distribution panel, the I/O

device capacity can be increased from 896 to 1,792 I/O. The increase is

accomplished through configuration of the racks and programming. For

more information, refer to the Remote I/O Scanner/Distribution Panel

Product Data (publication 1772-2.18).

With the proper interface module, the PLC-2/30 processor can be

connected to the Allen-Bradley Data Highway or other industry standard

buses. Table 1.B lists several “from-to” possibilities and the Allen-Bradley

module used to accomplish that function.

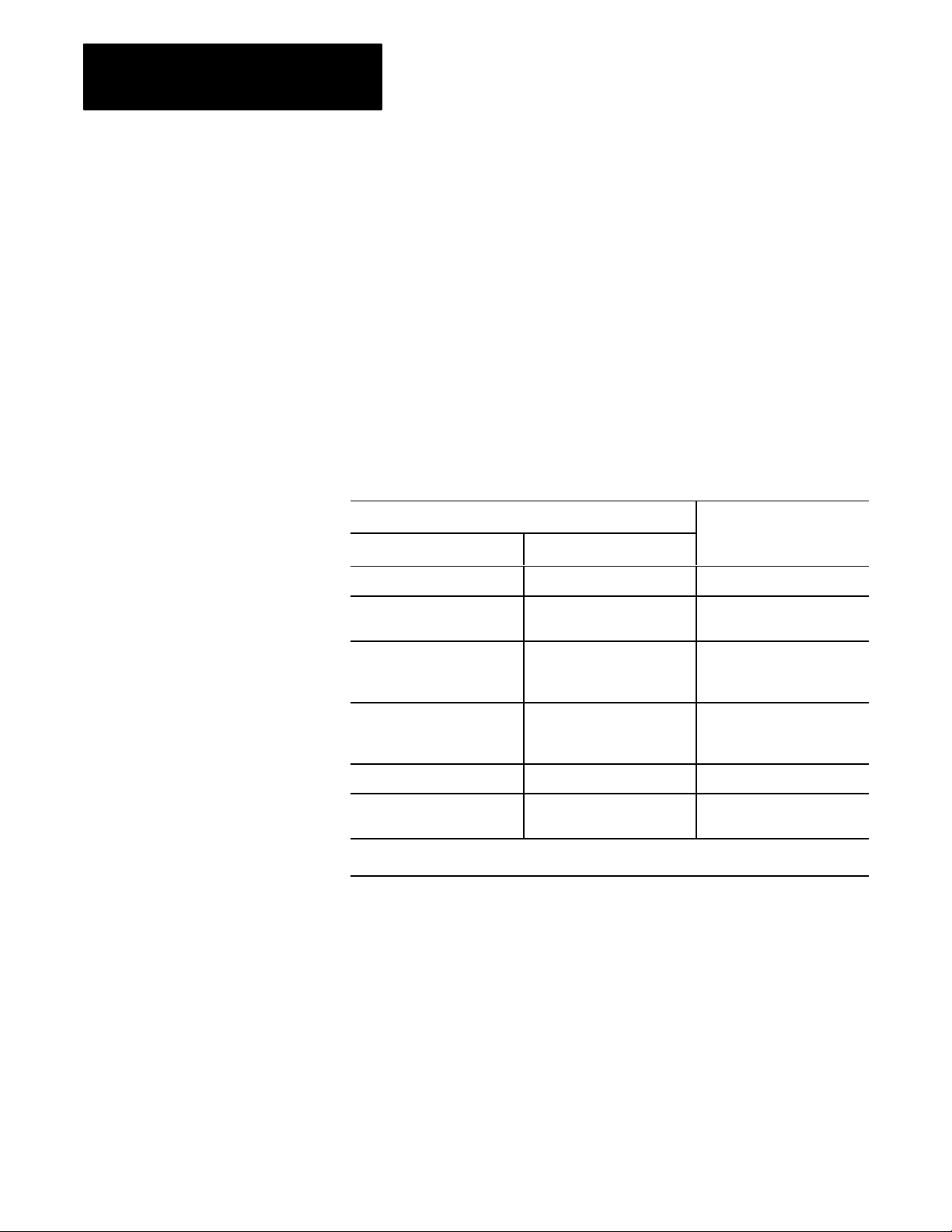

Table 1.B

Interface

Modules

Interface Locations -

From: To:

PLC2/30 Data Highway 1771KA2

PLC2/30 Data Highway II 1779KP2

Interface Module

1779KP2R

1.2.3

Industrial Terminal

Compatibility

PLC2/30 RS232 1771KG

1771KGM

1771KH

Data Highway Non AB

Data Highway Fisher Provox 1771KX1

Data Highway II Non AB

1

Non AllenBradley implies using Data Highway or Data Highway II to communicate with industry standard devices. See the

individual product brochures for specific connectivity information.

1

1

1771KE

1771KF

1770KF2

1779KFL

1779KFM

Industrial Terminals (cat. no. 1770-T1 or -T2) can be used on a limited

basis to program a PLC-2/30 programmable controller. Be aware that

only features supported by these terminals may be entered. The 1770-T3

and 1784-T50 terminals provide full PLC-2/30 capability. Refer to the

Industrial Terminal System User’s Manual (publication 1770-6.5.3 or

1784-6.5.1) for details.

14

Page 15

Chapter 1

Introduction

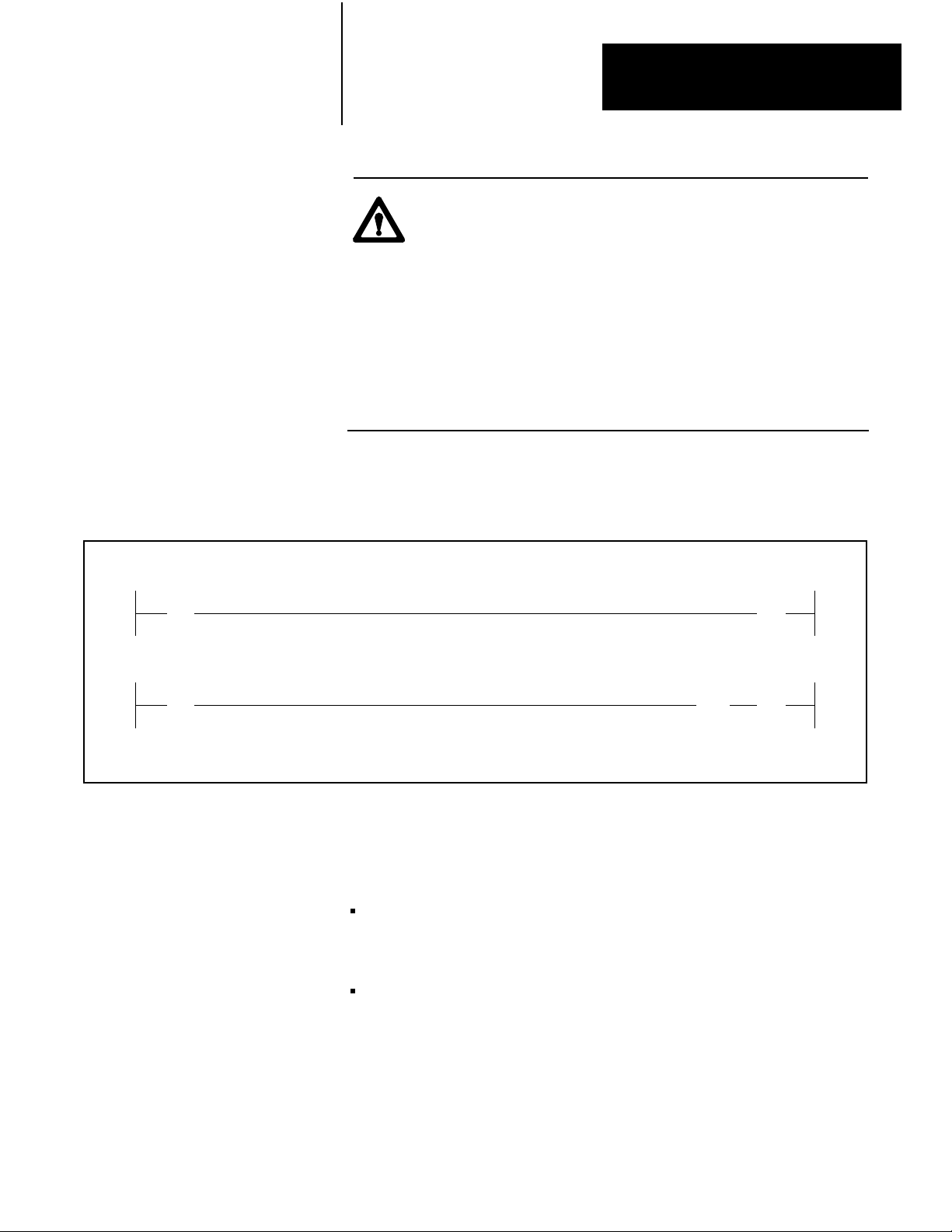

WARNING: Do not use a 1770-T1 or 1770-T2 industrial

terminal to edit or change a program or data table values

in PLC-2/30 memory that were generated using a 1770-T3

industrial terminal. Block instructions and instructions with

word addresses 4008 or greater will not be displayed properly

(Figure 1.1). The ERR message may appear randomly in the

user program at instructions and addresses that the -T1 and -T2

industrial terminals are not designed to handle. Changes to the

user program and/or data table with a -T1 or -T2 terminal could

result in unpredictable machine motion with possible damage to

equipment and/or injury to personnel.

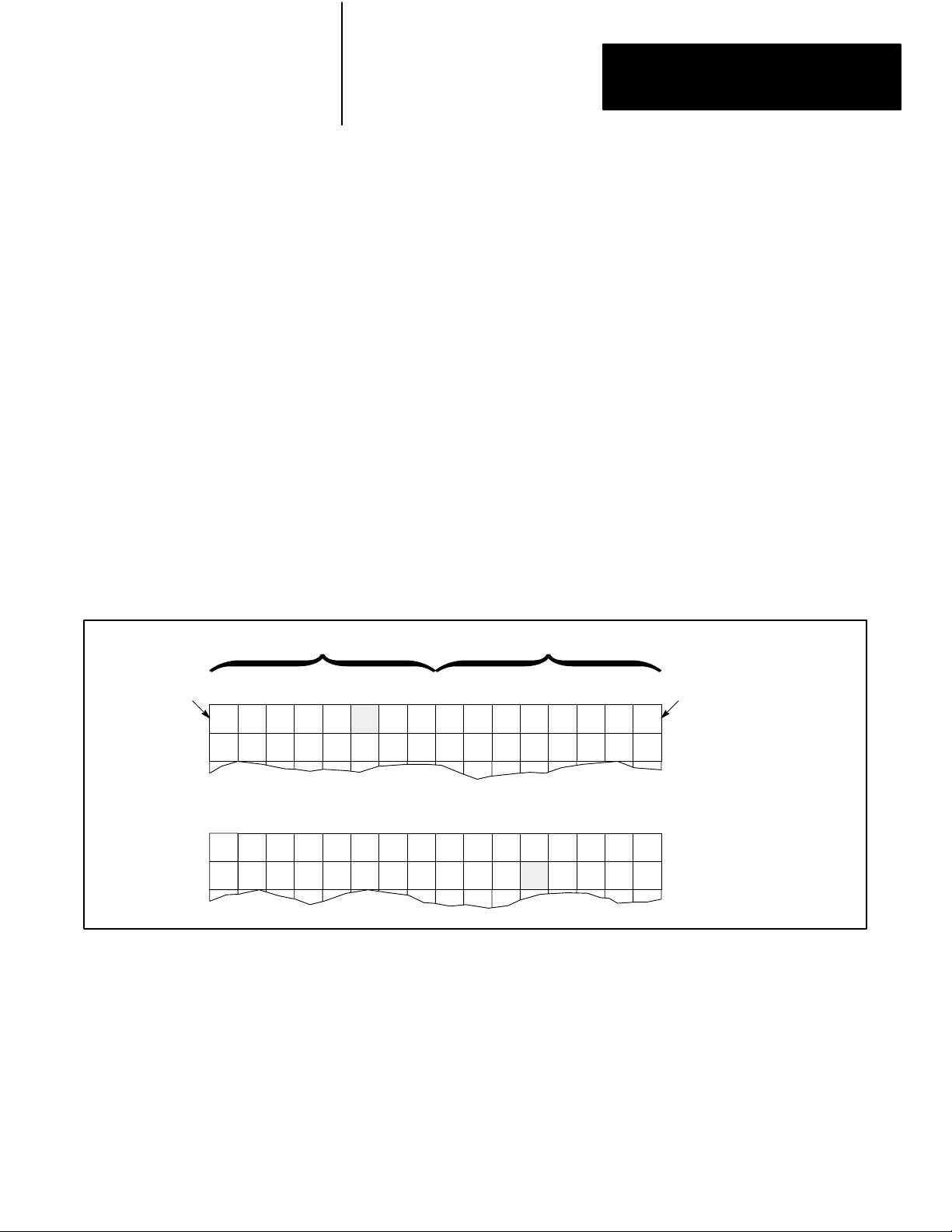

Figure 1.1

Message for Invalid Display of Processor Memory

ERR

113

][

14

11314

][

1.3

Additional Publications

1025

()

1770T3

Display (Actual content in processor memory)

1770T1 or T2 Display (Invalid display of processor memory)

ERR

16

02516

()

Additional information regarding PLC-2/30 programmable controller

components is available in:

PLC-2/20, PLC-2/30 Programmable Controller Assembly and

Installation Manual (publication 1772-6.6.2) contains necessary

information on installation, assembly, maintenance and troubleshooting.

Appendix C, Programming 0.01-Second Timers with the Mini-PLC-2

Programmable Controller.

15

Page 16

Chapter 1

Introduction

1.4

Terms Used in This Manual

We use the following terms to describe the various parts of your PLC-2/30

system.

Chassis — a hardware assembly used to house PC devices such as I/O

modules, adapter modules, processor modules, power supplies and some

processors (PLC-2/02, -2/16 and -2/17, for example).

I/O Group — The logical assignment of a specific input image table

word and its companion output image table word to a rack location. For

example: address 123 indicates an input module in rack 2, I/O group 3

This applies to all addressing modes.

Rack — an I/O addressing unit that corresponds to 8 input image table

words and 8 output image table words (128 input and 128 output

terminals).

Rack Fault — 1) The condition that occurs because of a loss of

communication between the processor and remote I/O chassis; 2) any

diagnostic indicator that lights up to signal a rack fault.

Slot — 1) The physical location where each module is placed within

a chassis; 2) a part of the Rack-Group-Slot addressing information for

intelligent I/O modules.

.

Slot Addressing — a method of assigning one input and one output image

table word to two slots, one slot, or one-half of a slot. (Appendix A is an

in-depth discussion on this topic.)

Slot Pair — two adjacent slots that can share image table words. Slot pairs

are: slots 0 and 1, 2 and 3, 4 and 5, and 6 and 7. (See Appendix A)

These and other terms are defined in Programmable Controller Terms

(publication no. PCGI–7.2).

16

Page 17

Chapter

Hardware Considerations

2

2.0

General

2.1

Select Switch

Mode

This chapter describes only those hardware items required when

programming or operating the PLC-2/30 programmable controller. For

more complete hardware information, refer to the PLC-2/20, PLC-2/30

Programmable Controller Assembly and Installation Manual (publication

no. 1772-6.6.2).

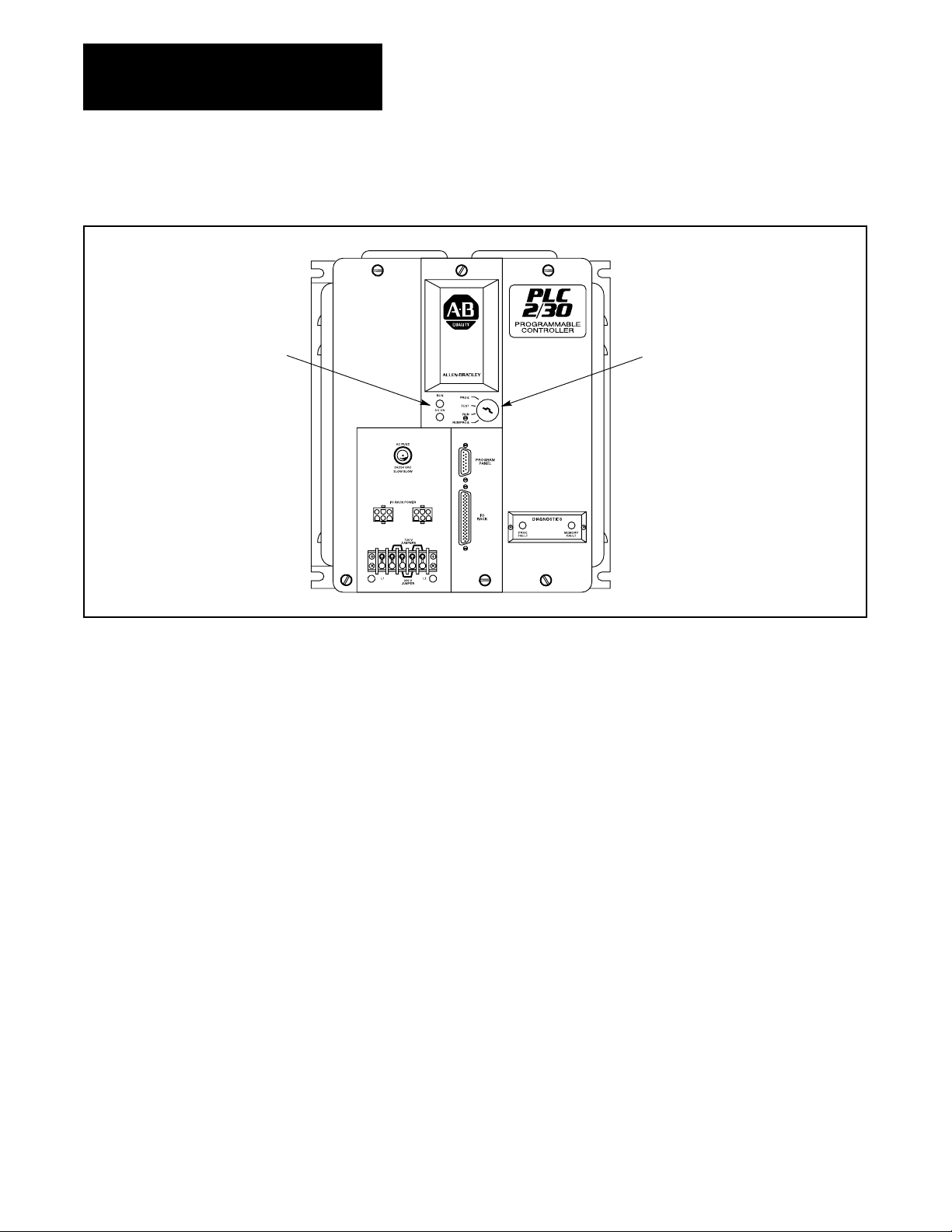

A four-position mode select switch (Figure 2.1) is located on the front of

the processor. You can select one of four positions with this switch:

PROG — This switch position places the processor in the program

mode. It is used when instructions are entered into memory. They can be

entered from an industrial terminal, a 1770-SA digital cassette recorder

or a 1770-SB data cartridge recorder. All outputs are disabled when the

switch is in this position.

TEST — This switch position places the processor in the test mode. The

user program is tested under simulated operating conditions without

actually energizing any output devices. All outputs are disabled in this

switch position.

RUN — This switch position places the processor in the run mode.

The user program will be executed and outputs are controlled by the

program. Changes to the user program or data table are not permitted in

this switch position.

RUN/PROG — This switch position places the processor in the

run/program mode. The processor functions as it does in the RUN

position. In this position, you can cause the processor to go into the

program or test mode without having to turn the switch to that position.

On-line changes to the program and/or data table are allowed in this

position with 1770-T3 or 1784-T50 industrial terminals.

The key can be removed from the processor in any of the four switch

positions.

21

Page 18

Chapter 2

Hardware Considerations

Diagnostic

Indicators

Figure 2.1

PLC2/30

Processor

Keylock

Mode

Select Switch

2.2

Memory

W

rite Protect

When the memory write protect jumper (Figure 2.2) is removed from a

1772-LH processor interface module, data table values can be changed

between word addresses 010

and 3778. These values can be changed only

8

when the processor is in the program mode or in the run/program mode

using on-line data change.

22

Page 19

Chapter 2

Hardware Considerations

Figure 2.2

Memory

W

rite Protect Jumper

HALFT

ONE WITH CALLOUT

2.3

RunTime

Errors

The remaining words in memory from 4008 to the end of memory,

including data table and user program, are protected and cannot be altered

by programming. The memory write protect feature guards against

unintentional changes to processor memory.

The processor and an industrial terminal can diagnose certain errors

occurring during the execution of the user program which result from

improper programming techniques. For example, it is possible to program

a series of instructions which require the processor to perform an operation

which it cannot do or perform an operation which is defined as illegal

(such as jump to a label that is not located closer to the end of program;

i.e., a jump backwards). These errors become apparent only while the

program is being executed, so are termed run-time errors. If a run-time

error occurs, the processor halts program execution and the PROCESSOR

FAULT indicator illuminates.

The first step in diagnosing run-time errors is to connect the industrial

terminal. It will display the message run-time error in the initial mode

select display. If the industrial terminal is already connected at the time

that a run-time error occurs, the ladder diagram is replaced by the mode

select display containing the error message. Run-time errors can be

detected by the industrial terminal when the processor is in either of two

23

Page 20

Chapter 2

Hardware Considerations

modes, program or remote program. (If the keyswitch is in

RUN/PROGRAM position, the industrial terminal automatically puts

the processor into remote program mode. If the keyswitch is in the RUN

position, or when it is connected to the processor through the 1771-KA2

communications adapter module, you must manually change the keyswitch

to the PROGRAM position).

WARNING: Forces are immediately removed if a Run-time

error occurs.

After returning the industrial terminal display to ladder diagram mode by

pressing [1][1] in mode selection operation, the industrial terminal displays

the instruction that caused the error with a message describing the run-time

error.

2.4

Processor Diagnostic

Indicators

After you have corrected the run-time error by editing the user program,

the processor can be restarted by switching to the run or run/program

mode.

Five indicators are located on the front of the processor (Figure 2.1). You

should become familiar with these indicators.

MEMORY FAULT — Illuminates when an error in the parity of data

retrieved from memory is detected. Changing the mode select switch to

the PROG position or cycling line power may clear this fault condition.

Reloading the program may also clear the fault.

BATTERY LOW — When the batteries for memory back-up are low,

this red indicator flashes on and off. Alkaline batteries will continue

to back up memory for about one week after the BATTERY LOW

indicator begins to flash. Lithium batteries have a longer life, but are

essentially dead when the indicator flashes. Regular replacement of

the batteries is recommended: for alkaline, every 6 to 12 months; for

lithium, every 2 years. (See the Assembly and Installation manual for

replacement details, publication no. 1772-6.6.2.)

The low battery bit, bit 027/00, will cycle on and off when a low battery

voltage condition is detected and the mode select switch is not in the

PROG position. Programming techniques can be used to examine this

bit and to control some type of alerting device when a low battery

condition exists.

24

Page 21

Chapter 2

Hardware Considerations

PROCESSOR FAULT — Illuminates when the logic circuits controlling

the processor scan fail or if processor error or run-time errors occur

which cause the processor to halt operation.

If the processor fault is a run-time error, the industrial terminal will

display RUN TIME ERROR when the keyswitch is in the PROGRAM

or RUN/PROGRAM position.

RUN — Illuminates when the processor is in the run or run/program

mode. It also indicates that outputs are being controlled by user

program.

DC ON — Illuminates when the 5.1V DC line to the logic circuitry in

the processor memory and I/O modules is satisfactory.

2.5

PowerUp

Recovery

2.6

Switch Group Assembly

When local I/O racks are powered by 1771-P3, -P4, -P5 or -P7 power

supplies, the processor control module (Cat. No. 1772-LG) may experience

a problem with these racks.

Upon recovery from a power lock (momentary or otherwise), processors in

the RUN or TEST mode attempt to read the local racks before the power

supplies are ready. This leads to a processor fault. The fault may be

identified by the conditions of the indicators:

Indicators

1772LG Module

Series A, Rev. L OFF ON

Series A, Rev. K or earlier OFF OFF

RUN

PROC FAULT

If the problem occurs, put the keyswitch in the program load position, then

return to RUN, or cycle power to the processor.

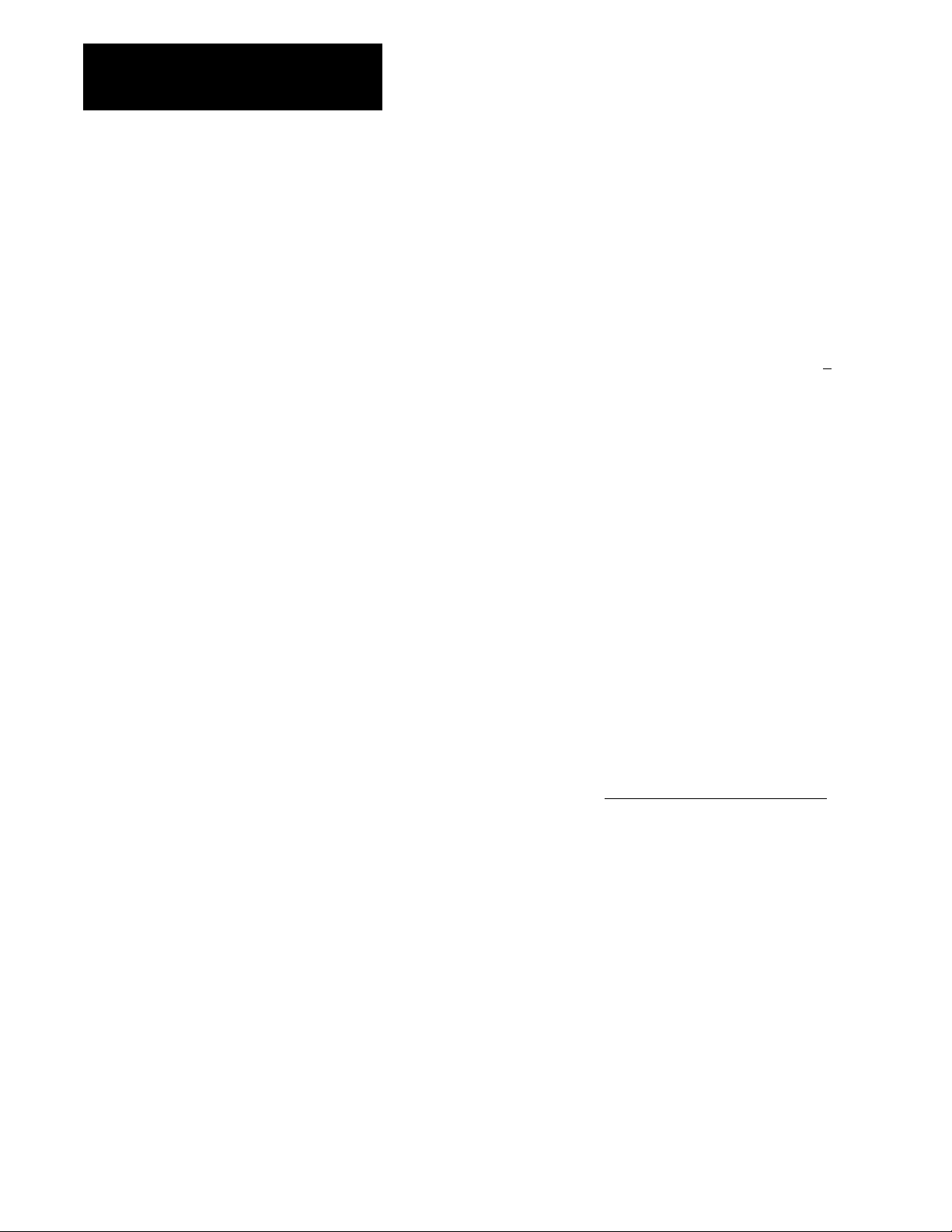

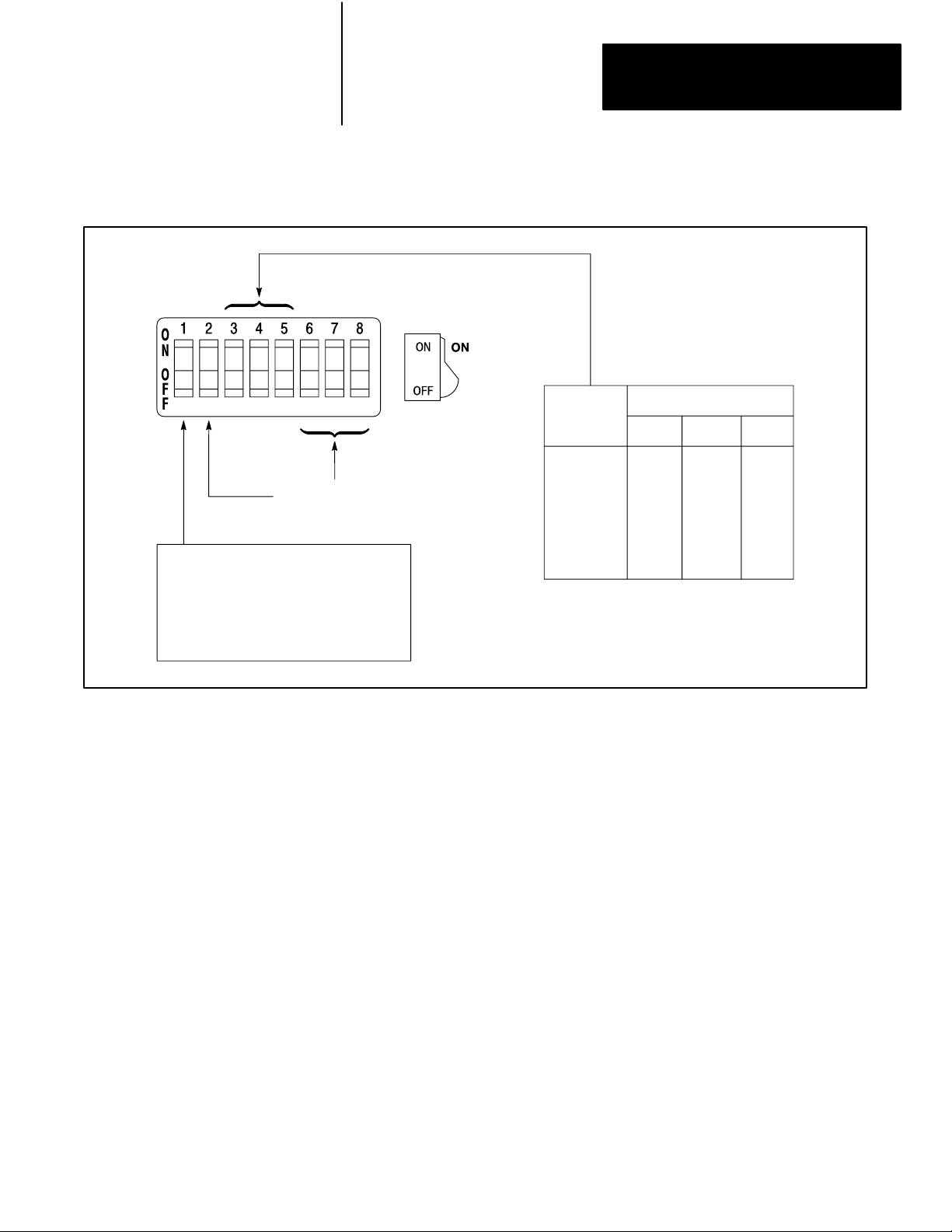

A switch group assembly is located on the I/O chassis backplane. It is used

to control output behavior when a fault occurs, to identify the I/O rack

number for local systems and to identify the addressing mode for remote

systems.

The switch and its functions, when used in local racks, are shown in

Figure 2.3. In this setup, the PLC-2/30 is communicating with the I/O

chassis through a 1771-AL Local I/O Adapter module.

25

Page 22

Chapter 2

Hardware Considerations

When using remote I/O (the 1772-SD2 scanner and the 1771-ASB remote

I/O Adapter), these switches will be set according to the adapter module’s

requirements.

2.6.1

Last State Switch

2.6.2

I/O Rack Number

The last state switch (switch no. 1) on the 1771 I/O chassis must be

properly set. ON indicates that the outputs are left in their last state when

a fault is detected. Machine operation can continue after fault detection.

OFF indicates that the outputs are de-energized when a fault is detected. In

addition, in remote systems, the switches on the 1772-SD2 Remote I/O

Scanner/Distribution panel and the 1771-ASB Remote I/O Adapter

must be properly set. Refer to publications 1772-2.18 and 1771-6.5.37,

respectively, for information on their switch settings.

WARNING: Switch No. 1 of the 1771 I/O chassis should be set

to OFF for most applications. This allows the processor to turn

controlled devices off when a fault is detected. If this switch is

set to ON, machine operation can continue after fault detection.

Damage to equipment and/or injury to personnel could result.

The setting of switches 3, 4 and 5 determines the I/O data table and

program address of the modules in this chassis — this is the local rack

number.

26

Improper setting of these switches will result in misdirected

communications between processor and the desired I/O rack.

Page 23

Chapter 2

Hardware Considerations

Figure 2.3

I/O Chassis Backplane Switch Settings for Local I/O Systems

1771

On:

Off:

2.7

Industrial Terminal

No significance should be set to OFF

Outputs remain in last state

when fault is detected.

Outputs deenergized when

fault is detected.

The 1770-T3 and 1784-T50 industrial terminals are the primary

programming terminals for the PLC-2/30 programmable controller. They

are used to load, edit, monitor and troubleshoot the user’s program in the

PLC-2/30 memory.

Local

Rack

Numbers

1

2

3

4

5

6

7

Switch

354

On

On

On

On

Off

Off

Off

On

On

Off

Off

On

On

Off

On

Off

On

Off

On

Off

On

2.8

Local System Structure

For detailed information about the 1770-T3 Industrial Terminal, refer to

the Industrial Terminal System User’s Manual, publication no. 1770-6.5.3.

For detailed information about the 1784-T50 Industrial Terminal, refer to

the Industrial Terminal T50 User’s Manual, publication no. 1784-6.5.1.

A local system has the processor and each I/O chassis within 3-6 cable feet

of each other. Up to 7 local I/O racks may be assigned.

For proper transmission of data between the PLC-2/30 processor and

local bulletin 1771 I/O modules, the I/O chassis must contain a local I/O

Adapter Module (Cat. No. 1771-AL). The local adapter module must be

installed in each I/O chassis used with the processor. Diagnostic indicators

27

Page 24

Chapter 2

Hardware Considerations

on the front panel of the local adapter module aid in troubleshooting. These

indicators are:

ACTIVE — Illuminates when proper communication is established

between the processor and the I/O chassis. It also indicates that DC

power is properly supplied to the I/O chassis. It is normally on.

RACK FAULT — Illuminates when I/O data is not in the proper format.

It is normally off.

Possible causes of a rack fault are:

Data parity error on address or control lines

Missing terminator plug

Disconnected/broken communications cable

No power at the processor.

An I/O Interconnect cable is required to connect between the PLC-2/30

and local I/O rack adapter modules. It is available in two sizes:

2.9

Remote System Structure

3 ft. I/O Interconnect cable (.92m) 1777–CA

6 ft. I/O Interconnect cable (1.85m) 1777-CB

I/O Cable Terminator Plug 1777-CP

(used to “close” the I/O interconnect cable link at the last I/O adapter

module)

A remote system allows the processor and the I/O chassis to be separated

by up to 10,000 cable feet (approx. 3,048 meters). Up to 7 remote I/O

racks may be assigned.

Proper transmission of data between the PLC-2/30 processor and

remote bulletin 1771 I/O modules requires a 1772-SD2 Remote I/O

Scanner/Distribution Panel plus a 1771-ASB Remote Adapter in each I/O

chassis. Connection between the PLC-2/30 processor and the 1772-SD2

is through a 1772-CS interconnect cable. Connection from the 1772-SD2

to a 1771-ASB Remote I/O Adapter and from one remote I/O adapter to

another is through 1770-CD twinaxial interconnect cable.

The front of the 1772-SD2 distribution panel has eight bicolor red/green

LED indicators. If the I/O chassis is used and serial communication is

valid, the RACK STATUS LED will be green. If the I/O chassis is not

used, the LED is off. For an I/O rack fault condition, the corresponding

RACK STATUS LED will be red. The rack 0 indicator will also go to red

if there is a dependent I/O fault.

28

Page 25

Chapter 2

Hardware Considerations

Three diagnostic indicators are located on the front of the 1771-ASB

adapter. These indicators are:

ACTIVE — Illuminates when proper communications have been

established between the 1772-SD2 distribution panel and the 1771-ASB

adapter, DC power is properly supplied to the I/O chassis and

1771-ASB adapter is actively controlling the I/O. The ACTIVE

indicator is normally on.

ADAPTER FAULT — Illuminates when the module is not operating

properly. It tells you that a fault has been detected and that the I/O

chassis has responded in the manner selected by the last state switch.

When this indicator is on, the other indicators are no longer valid. the

ADAPTER FAULT indicator is normally off.

I/O RACK FAULT — Illuminates when a fault has been detected at the

1771-ASB adapter, the I/O chassis, or the logic side of the I/O modules.

The I/O RACK FAULT is normally off.

2.10

Local/Remote

Structure

System

NOTE: For a full listing of the possible combinations of these

indicators (on, off or blinking), see the 1771-ASB User’s manual

(publication no. 1771-6.5.37).

A local/remote system has both nearby (3-6 cable-ft) and remote (up to

10,000 cable-ft) I/O chassis. Up to 2 local and 5 remote racks may be

assigned.

The PLC-2/30 processor system can also be configured with a combination

of local and remote I/O chassis. Each local chassis must have a 1771-AL

Local I/O Adapter module. And as previously stated, communication with

the remote chassis (one or more) requires a 1772-SD2 Remote Distribution

panel and one 1771-ASB Remote I/O Adapter in each chassis.

The 1772-SD2 distribution panel may be connected directly to the

processor interface module or up to two local I/O chassis may precede it.

Connection to the preceding local I/O chassis is made with a 1772-CS

interconnect cable.

NOTE: The 1772-SD2 must not be more than 10 cable feet from the

PLC-2/30 processor module.

29

Page 26

Chapter 2

Hardware Considerations

CAUTION: For proper system data communications, a

local/remote system structure with 2 local racks, you must use a

1777-CA cable (3 ft./.92m) between the processor and the two

local racks. You must also use the 1772-CS cable (3 ft./.92m)

from the second local rack to the distribution panel.

2.11

Hardware Addressing

Modes

2.12

Auxiliary Power Supplies

The term “addressing mode” refers to the method of hardware addressing

within individual I/O chassis. Appendix A, Hardware Addressing, provides

a complete presentation on 2-slot, 1-slot and 1/2-slot addressing. In

general:

Local I/O chassis that are communicating through a 1771-AL Local I/O

Adapter module can only be 2-slot addressed.

Remote I/O that are communicating through a 1771-ASB Series A

Remote I/O Adapter module can be addressed in either 2-slot or 1-slot

modes.

Remote I/O that are communicating through a 1771-ASB Series B

Remote I/O Adapter module can be addressed in either 2-slot, 1-slot or

1/2-slot modes.

NOTE: Processor-to-I/O chassis communication requires the setting of

I/O chassis backplane switches. See the 1771-ASB Remote I/O Adapter

manual (publication no. 1771-6.5.37) for this information.

The Series C programmable controller’s power supply provides 4 amperes

of current to power local I/O chassis or the 1772-SD2 distribution panel.

When the total output current required to power these modules exceeds the

supply, or a core memory is issued, an auxiliary power supply must be

used. The total output current must not exceed the rating of the auxiliary

power supply.

2.12.1

1771P2 Auxiliary Power

Supply

210

The 1771-P2 power supply provides 6.5 amperes to power one bulletin

1771 I/O chassis with a maximum 128 I/O. This includes the adapter and

the I/O modules in the chassis.

This power supply may be operated from either a 120 or a 220/240V AC

source.

Page 27

Chapter 2

Hardware Considerations

2.12.2

1777P2

Auxiliary Power

Supply

2.12.3

1771P3, P4, and P5 Slot

Power Supplies

The 1777-P2 Series C power supply provides 9 amperes to power one or

two bulletin 1771-I/O chassis. This includes the I/O adapter and the I/O

modules in each chassis. The power supply must be used to power the

1772-SD2 distribution panel when the PLC-2/30 processor contains a core

memory module.

This power supply may be operated from either a 120 or a 220/240V AC

source.

These power supply modules provide 5V DC for an I/O chassis. The -P3

and the -P4 operate on 120V AC; the -P5 operates on 240V DC. The -P3

supplies up to 3 amperes to an I/O chassis; the -P4 and -P5 supply up to 8

amperes to an I/O chassis.

You may place one of these modules in any slot of a Series B 1771

Universal I/O chassis except the adapter/processor slot. Follow the

recommendation of the Power Supply Considerations section of

publication no. 1771-2.111 when locating these modules in a

1771 Series B I/O chassis.

Full specifications are in publication no. 1771-2.111.

2.12.4

1771P7 Power Supply

2.12.5

1771PSC Power Supply

Chassis

The 1771-P7 power supply provides 16 amperes to power one bulletin

1771 I/O chassis. This includes the adapter and the I/O modules in the

chassis.

This power supply may be operated from either a 120 or a 220/240V AC

source.

NOTE: The 1771-P7 power supply may not be used in conjunction with a

slot power supply.

The 1771-PSC provides 4 slots for mounting modular power supplies to

provide up to 16 amperes to a 1771 Series B Universal I/O chassis. It can

also be used to mount communication modules that need only +5V DC and

a processor enable signal.

The power supply chassis may be mounted separately (when used with

communications modules) or mounted directly to 1771-A1B, A2B or A4B

I/O chassis (when supplying additional backplane current and/or when

supporting communications modules).

211

Page 28

Data Table

Chapter

3

3.0

General

3.1

Memory Structure

MSB LSB

This chapter introduces concepts and terminology necessary for a general

understanding of programmable controller memory. It explains the

memory organization of the PLC-2/30 programmable controller.

The memory of the processor can be thought of as a large arrangement of

storage points, each called a BInary digiT, or bit (Figure 3.1). A bit is the

smallest unit of information a memory is capable of retaining. Information

stored in each bit is represented as a 1 or 0. When a bit is on, it is

represented by a logic 1. When a bit is off, it is represented by a logic 0.

Figure 3.1

Memory

Upper Byte Lower Byte

17 16 15 14 13 12 11 10 07 06 05 04 03 02 01 00

1001110111000110001001011011100

W

ord Structure

1

Address 030

Word

W

ord Address 031

8

8

17 16 15 14 13 12 11 10 07 06 05 04 03 02 01 00

1001010110001000011110001001000

Each bit in a word is identified by a two-digit number using the octal

numbering system. Memory bits are numbered 00 through 07 and 10

through 17, with the least significant bit (LSB = 00

most significant bit (MSB = 17

) at the left.

8

A group of 8 bits forms a single byte. A byte is defined as the smallest

complete unit of information that can be transmitted to or from the

processor at a given time.

0

W

ord Address 1700

W

ord Address 1701

) at the right and the

8

8

8

31

Page 29

Chapter 3

Data Table

A group of 16 bits makes up a word. This word can be thought of as being

made up of two 8-bit bytes; a lower byte and an upper byte.

Because of its function in memory, one PLC-2/30 word may also be

thought of as a memory location: when a word is being used, an actual

physical location in memory is being accessed.

A specific bit in memory can be identified by combining the word address

and bit number to form the bit address, such as 030/12 or 1701/04. The bit

address is shown by writing the word address above the instruction and the

bit number below it.

3.2

Memory Organization

3.2.1

Data Table

The processor can have a memory capacity of up to 16,256 words. These

memory words are organized by their word address and are divided into

three major areas (Figure 3.2):

Data table

User program

-Main Program

-Subroutine Area

Message Storage Area

All input/output status and user program instructions are stored in one of

these parts (Figure 3.2).

Data table words, and/or the 16 bits in each word, are controlled and

utilized directly by the processor. The processor uses the status of input

devices and the control logic established in the user program to determine

the status of output devices. Transfer of input data from input devices and

transfer of output data to output devices occurs during the I/O scan. If

the output instruction’s status changed in the program, the actual output

device’s on/off status is updated during the I/O scan to reflect this change.

32

Page 30

Chapter 3

Data Table

Decimal

Words

Up to

16,256

Total

8

64

72

128

256

384

512

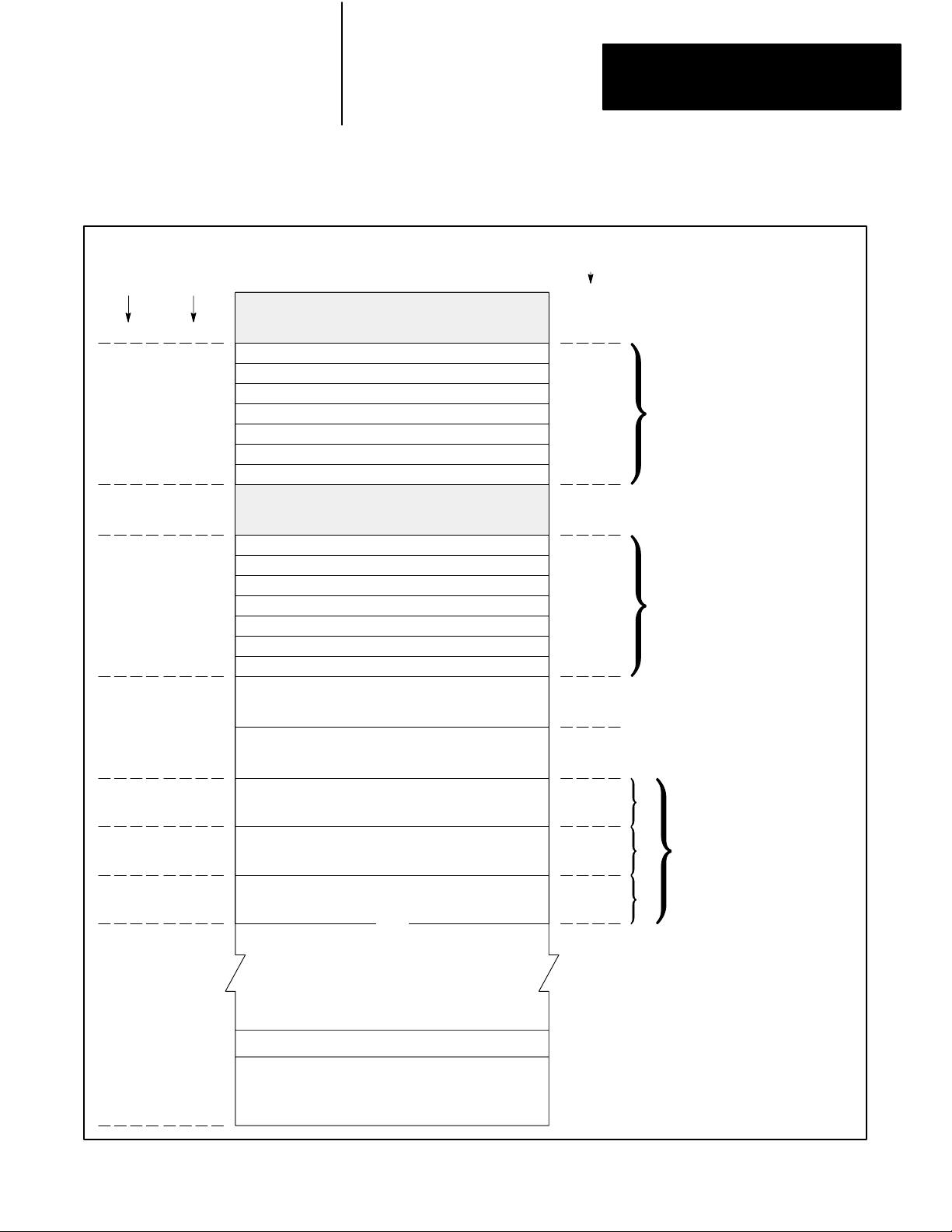

Figure 3.2

PLC2/30

Decimal

Words

Per Area

Processor W

8

Rack 1010017

Rack 2020027

Rack 3030037

Rack 4040047

Rack 5050057

Rack 6060067

56

8

56

128

128

128

4

128640

Rack 7070077

Processor W

Rack 11

Rack 2120127

Rack 3130137

Rack 4140147

Rack 5150157

Rack 6160167

Rack 7170177

T

imer/Counter ACC V

Internal Storage

T

imer/Counter Preset V

Internal Storage

User

(User Program Begins

After End of Last

Data T

End of Program

Message Storage

Memory Organization (Expanded Data T

ork Area

No. 1

1

ork Area

No. 2

10117

2

alues or

alues or

Expansion

1

Expansion

2

Expansion

3

(etc.)

Program Storage

able Expansion)

3

Octal

ord Address

W

000

007

010

77

100

107

110

177

200

277

300

377

400

577

600

777

1000

1177

1200

17777

able)

Output Image Table

Rack address areas that are

not configured as output image

table become available for

timer/counter accumulated

values or word/bit storage.

Input Image Table

Rack address areas that are

not configured as input image

table become available for

timer/counter preset values or

word/bit storage.

Data table can be expanded in

128 word increments (unused

sections are utilized for user

program storage) up to 8064

words maximum.

1

027 - Bits in this word are used by the

processor for battery low condition, message

generation, and data highway

output modules in rack 2, I/O group 7.

2

125 and 126 - These words are used to

indicate remote rack fault

I/O system. Do not put input modules in rack

2, I/O groups 5 or 6.

3

Report generation messages can be stored in

memory locations not used by data table or

user program.

4

Maximum data table size is 8192 words.

. Do not put

status

in a remote

33

Page 31

Chapter 3

Data Table

The first 128 words of the memory are set aside for data table storage.

This number includes 32 words for I/O image tables (i.e., 2 full racks),

16 words for processor work areas and 80 words for timers/counters. If

timers/counters are not required, you can reduce the data table to 48 words.

Expansion is in increments of two words until a table of 256 is reached,

and then in increments of 128 words. The data table can be adjusted to

accommodate the full I/O capacity of the PLC-2/30 processor.

NOTE: The data table expansion capability should be utilized practically.

The user should allow sufficient room for both data table and user

program.

When the data table is set to 256 words, up to 112 timer/counter

instructions can be programmed or 224 storage words are available. Users

can also tail or data table input/output capacity in increments of 128 I/O up

to 896 I/O.

The function of the data table may be explained in relation to inputs and

outputs. Discrete input and output modules cannot store information.

Discrete input and output modules cannot store information. They contain

interface circuits only. Input/output status information (on/off) is actually

stored in memory areas called I/O image tables. An image is defined as an

exact duplicate array of information, that is, the states stored in a different

medium.

Data Table Areas

The data table of the PLC-2/30 programmable controller can be divided

into six distinct areas, assuming default data table size has not been

changed (Figure 3.3). These areas are:

Processor work area 1

Output image table

Timer/counter accumulated values or bit/word storage

Processor work area 2

Input image table

Timer/counter preset values or bit/word storage

The data table area has a default size of 128 words and is configurable

from 48 up to 8,064 words (with 8K word memory) or 8,192 words (with

the 16K word memory). This area stores the information needed in the

execution of the user program, such as input and output device status,

3-digit numeric values, and the status of internal storage points.

34

Processor Work Areas 1 and 2

There are two processor work areas: processor work area no. 1 (addresses

000

to 0078) and processor work area no. 2 (addresses 1008 to 1078).

8

Page 32

Chapter 3

Data Table

These memory locations cannot be accessed by the user. Their word

addresses are not available for addressing of any kind. The processor uses

both areas for internal control functions.

Output Image Table

The primary function of the output image table is to control the status of

outputs wired to the output modules. If the output image table bit is on, its

corresponding output is on. If the bit is cleared to off, its corresponding

output is off. These bits are controlled by instructions in the user program.

The processor controls the status of bits in the output image table as it

generates output commands. Actual hardware outputs change state only if

corresponding output image table bits change state or if they are forced.

NOTE: PLC-2/30 output terminals can be forced on or off through the

industrial terminal. The output image table bits, corresponding to output

terminals which are forced, do not change state.

The output image table ordinarily begins with word 010

ends with word 027

. However, word 027 is reserved and output or block

8

and ordinarily

8

transfer modules must not be placed in rack 2, I/O group 7.

The output image table therefore contains 16 word addresses, or 256

bit addresses. Using the industrial terminal, the output image table can

be reduced to 8 word addresses (128 bit addresses), or increased from

16 word addresses to 56 (896 bit addresses). By changing memory

configuration to 896 I/O (seven 1771-A4B I/O chassis with 2-slot

addressing), the 896 bit addresses represent the maximum number of

discrete outputs the processor can control.

Each bit in the output image table may be associated with a hardware

terminal address, although this is not always the case, since a

corresponding output module may not actually be placed in this I/O rack

slot. If it is, however, the terminal address is the same as the bit address.

A secondary function of the output image table is to provide a storage area

for bits or words. Words and/or bits in the output image table not actually

used to store the on/off status of devices can be used for data storage.

NOTE: Although only 11 bits of word 027

are actually used as processor

8

control bits, the remaining bits must not be used since inadvertent

alteration of these bits could occur. The processor sets bit address 027/00

ON and OFF to indicate a low battery condition. This bit can be examined

by instructions in the user program. (See Section 2.4)

8

35

Page 33

Chapter 3

Data Table

CAUTION: Word 027 is reserved for processor use. Do not put

block transfer or output modules in rack 2, I/O group 7.

Timer/Counter Accumulated Values, Bit/Word Storage

This area of memory is used to store accumulated values of timer/counter

instructions. The area may also be used as storage for words and/or bits.

Word addresses 030

to 0778 bound this area when memory is configured

8

for 256 I/O (maximum) and 40 Timer/Counter Instructions (Figure 3.3).

NOTE: Each timer or counter used actually requires two words of data

table memory: one from the accumulated value area (030

other from the preset value area (130

to 1778).

8

to 0778) and the

8

Input Image Table

The input image table duplicates the status of the inputs wired to input

modules. If an input is on, its corresponding input image table bit is set

to on. If an input is off, its corresponding bit in memory is cleared to off.

These bits are monitored by instructions in the user program.

Input image table bits are updated each scan cycle to correspond to the

information supplied by input modules.

The input image table is bounded by word addresses 110

(Figure 3.3). This area contains 16 word addresses, or 256 bit addresses.

With the industrial terminal, the input image table can be reduced to 8

word addresses (128 bit addresses), or increased to 56 word addresses

(896 bit addresses). By changing memory configuration to 896 I/O (seven

1771-A4B I/O chassis), the 896 bit addresses represent the maximum

number of discrete inputs the processor can monitor.

to 127

8

8

36

In a local PLC-2/30 controller, the total bits used, which represent actual

hardware inputs and outputs together, cannot exceed 896 I/O. This number

represents the maximum I/O capability of the PLC-2/30 Programmable

Controller and is possible only when the system is programmed with the

1770-T3 or 1784-T50 industrial terminal.

Page 34

Chapter 3

Data Table

CAUTION: If a remote I/O configuration is being used, words

1258 and 1268 may be used to store remote I/O fault bits. If this

is the case, input modules must not be placed in these slots (rack

2, I/O groups 5 and 6): unexpected machine operation may

result.

37

Page 35

Chapter 3

Data Table

Total

Decimal

Words

8

24

Decimal

Words

Per Area

8

16

Figure 3.3

PLC2/30

Processor Work Area

Memory Organization (Default Configuration)

No. 1

Output

Image T

able

Octal

ord Address

W

000

007

010

026

027

030

Bit

Address

00

17

00

17

1

00

Up to

16,256

64

72

88

128

Timer/Counter

Accumulated V

40

Processor W

8

16

Preset V

40

alues (ACC)

Internal Storage

ork Area

No. 2

Input

Image T

able

Timer/Counter

alues (PR)

Internal Storage

User Program

17777

077

100

107

110

125

126

127

130

177

17

00

17

00

2

17

00

17

1

Bits in this word are used by the processor for

battery low condition, message generation,

and data highway. Do not put output modules

in rack 2, I/O group 7.

2

These words are used to indicate remote rack

fault status in a remote I/O system. Do not

put input modules in rack 2, I/O groups 5 or 6.

Default

Configured

Data T

able

(128 W

ords)

38

Page 36

Chapter 3

Data Table

Each bit in the input image table may have a corresponding real hardware

terminal on the I/O rack associated with it, although this may not always

be the case, since a corresponding input module may not actually be placed

in an I/O rack slot. If it does, the terminal address is the same as the bit