SC66 Hardware Design

Smart LTE Module Series

Rev: SC66_Hardware_Design_V1.0

Date: 2019-03-08

Status: Preliminary

www.quectel.com

Smart LTE Module Series

SC66 Hardware Design

Our aim is to provide customers with timely and comprehensive service. For any

assistance, please contact our company headquarters:

Quectel Wireless Solutions Co., Ltd.

7th Floor, Hongye Building, No.1801 Hongmei Road, Xuhui District, Shanghai 200233, China

Tel: +86 21 5108 6236

Email: info@quectel.com

Or our local office. For more information, please visit:

http://www.quectel.com/support/sales.htm

For technical support, or to report documentation errors, please visit:

http://www.quectel.com/support/technical.htm

Or email to: support@quectel.com

GENERAL NOTES

QUECTEL OFFERS THE INFORMATION AS A SERVICE TO ITS CUSTOMERS. THE INFORMATION

PROVIDED IS BASED UPON CUSTOMERS’ REQUIREMENTS. QUECTEL MAKES EVERY EFFORT

TO ENSURE THE QUALITY OF THE INFORMATION IT MAKES AVAILABLE. QUECTEL DOES NOT

MAKE ANY WARRANTY AS TO THE INFORMATION CONTAINED HEREIN, AND DOES NOT ACCEPT

ANY LIABILITY FOR ANY INJURY, LOSS OR DAMAGE OF ANY KIND INCURRED BY USE OF OR

RELIANCE UPON THE INFORMATION. ALL INFORMATION SUPPLIED HEREIN IS SUBJECT TO

CHANGE WITHOUT PRIOR NOTICE.

COPYRIGHT

THE INFORMATION CONTAINED HERE IS PROPRIETARY TECHNICAL INFORMATION OF QUECTEL

WIRELESS SOLUTIONS CO., LTD. TRANSMITTING, REPRODUCTION, DISSEMINATION AND

EDITING OF THIS DOCUMENT AS WELL AS UTILIZATION OF THE CONTENT ARE FORBIDDEN

WITHOUT PERMISSION. OFFENDERS WILL BE HELD LIABLE FOR PAYMENT OF DAMAGES. ALL

RIGHTS ARE RESERVED IN THE EVENT OF A PATENT GRANT OR REGISTRATION OF A UTILITY

MODEL OR DESIGN.

Copyright © Quectel Wireless Solutions Co., Ltd. 2019. All rights reserved.

SC66_Hardware_Design 1 / 118

Smart LTE Module Series

Revision

Date

Author

Description

1.0

2019-03-08

Jian WU

Initial

SC66 Hardware Design

About the Document

History

SC66_Hardware_Design 2 / 118

Smart LTE Module Series

SC66 Hardware Design

Contents

About the Document ................................................................................................................................... 2

Contents ....................................................................................................................................................... 3

Table Index ................................................................................................................................................... 6

Figure Index ................................................................................................................................................. 8

1 Introduction ........................................................................................................................................ 10

1.1. Safety Information ..................................................................................................................... 14

2 Product Concept ................................................................................................................................ 15

2.1. General Description .................................................................................................................. 15

2.2. Key Features ............................................................................................................................. 19

2.3. Functional Diagram ................................................................................................................... 22

2.4. Evaluation Board ....................................................................................................................... 24

3 Application Interfaces ....................................................................................................................... 25

3.1. General Description .................................................................................................................. 25

3.2. Pin Assignment ......................................................................................................................... 26

3.3. Pin Description .......................................................................................................................... 27

3.4. Power Supply ............................................................................................................................ 42

3.4.1. Power Supply Pins ......................................................................................................... 42

3.4.2. Decrease Voltage Drop .................................................................................................. 42

3.4.3. Reference Design for Power Supply .............................................................................. 43

3.5. Turn on and off Scenarios ......................................................................................................... 45

3.5.1. Turn on Module Using the PWRKEY ............................................................................. 45

3.5.2. Restart the Module ......................................................................................................... 46

3.6. VRTC Interface ......................................................................................................................... 47

3.7. Power Output ............................................................................................................................ 48

3.8. Battery Charge and Management ............................................................................................. 48

3.9. USB Interface ............................................................................................................................ 51

3.9.1. TYPE-C Interfaces ......................................................................................................... 51

3.9.2. DP Interfaces .................................................................................................................. 54

3.9.3. Host ................................................................................................................................ 56

3.10. UART Interfaces ........................................................................................................................ 56

3.11. (U)SIM Interfaces ...................................................................................................................... 58

3.12. SD Card Interface ..................................................................................................................... 61

3.13. GPIO Interfaces ........................................................................................................................ 63

3.14. I2C Interfaces ............................................................................................................................ 64

3.15. I2S Interface .............................................................................................................................. 65

3.16. SPI Interfaces ............................................................................................................................ 66

3.17. ADC Interfaces .......................................................................................................................... 66

3.18. LCM Interfaces .......................................................................................................................... 67

SC66_Hardware_Design 3 / 118

Smart LTE Module Series

SC66 Hardware Design

3.19. Touch Panel Interfaces ............................................................................................................. 71

3.20. Camera Interfaces..................................................................................................................... 73

3.20.1. Design Considerations ................................................................................................... 79

3.21. Sensor Interfaces ...................................................................................................................... 81

3.22. Audio Interfaces ........................................................................................................................ 82

3.22.1. Reference Circuit Design for Microphone Interfaces ..................................................... 83

3.22.2. Reference Circuit Design for Earpiece Interface ........................................................... 84

3.22.3. Reference Circuit Design for Headphone Interface ....................................................... 85

3.22.4. Reference Circuit Design for Loudspeaker Interface..................................................... 85

3.22.5. Audio Interfaces Design Considerations........................................................................ 85

3.23. Emergency Download Interface ................................................................................................ 86

4 Wi-Fi and BT ....................................................................................................................................... 87

4.1. Wi-Fi Overview .......................................................................................................................... 87

4.1.1. Wi-Fi Performance ......................................................................................................... 87

4.2. BT Overview .............................................................................................................................. 89

4.2.1. BT Performance ............................................................................................................. 90

5 GNSS ................................................................................................................................................... 91

5.1. GNSS Performance .................................................................................................................. 91

5.2. GNSS RF Design Guidelines .................................................................................................... 92

6 Antenna Interfaces ............................................................................................................................. 93

6.1. Main/Rx-diversity Antenna Interfaces ....................................................................................... 93

6.1.1. Main and Rx-diversity Antenna Interfaces Reference Design ....................................... 97

6.1.2. Reference Design of RF Layout..................................................................................... 97

6.2. Wi-Fi/BT Antenna Interface ....................................................................................................... 99

6.3. GNSS Antenna Interface ......................................................................................................... 100

6.3.1. Recommended Circuit for Passive Antenna ................................................................ 101

6.3.2. Recommended Circuit for Active Antenna ................................................................... 102

6.4. Antenna Installation ................................................................................................................. 102

6.4.1. Antenna Requirements ................................................................................................ 102

6.4.2. Recommended RF Connector for Antenna Installation ............................................... 103

7 Electrical, Reliability and Radio Characteristics .......................................................................... 105

7.1. Absolute Maximum Ratings .................................................................................................... 105

7.2. Power Supply Ratings ............................................................................................................. 105

7.3. Operation and Storage Temperatures ..................................................................................... 106

7.4. Current Consumption .............................................................................................................. 107

7.5. RF Output Power .................................................................................................................... 116

7.6. RF Receiving Sensitivity ......................................................................................................... 119

7.7. Electrostatic Discharge ........................................................................................................... 123

8 Mechanical Dimensions .................................................................................................................. 124

8.1. Mechanical Dimensions of the Module ................................................................................... 124

8.2. Recommended Footprint ........................................................................................................ 126

8.3. Top and Bottom View of the Module ....................................................................................... 127

SC66_Hardware_Design 4 / 118

Smart LTE Module Series

SC66 Hardware Design

9 Storage, Manufacturing and Packaging ........................................................................................ 128

9.1. Storage .................................................................................................................................... 128

9.2. Manufacturing and Soldering .................................................................................................. 129

9.3. Packaging ............................................................................................................................... 130

10 Appendix A References ................................................................................................................... 132

11 Appendix B GPRS Coding Schemes ............................................................................................. 135

12 Appendix C GPRS Multi-slot Classes ............................................................................................ 136

13 Appendix D EDGE Modulation and Coding Schemes ................................................................. 138

SC66_Hardware_Design 5 / 118

Smart LTE Module Series

SC66 Hardware Design

Table Index

TABLE 1: SC66-CE* FREQUENCY BANDS ..................................................................................................... 15

TABLE 2: SC66-A* FREQUENCY BANDS ....................................................................................................... 16

TABLE 3: SC66-J* FREQUENCY BANDS ........................................................................................................ 16

TABLE 4: SC66-E* FREQUENCY BANDS ....................................................................................................... 17

TABLE 5: SC66-W* FREQUENCY BANDS ...................................................................................................... 17

TABLE 6: SC66-MW*(2*2 MIMO WIFI) FREQUENCY BANDS ........................................................................ 18

TABLE 7: SC66 KEY FEATURES ..................................................................................................................... 19

TABLE 8: I/O PARAMETERS DEFINITION ....................................................................................................... 27

TABLE 9: PIN DESCRIPTION ........................................................................................................................... 27

TABLE 10: POWER DESCRIPTION ................................................................................................................. 48

TABLE 11: PIN DEFINITION OF CHARGING INTERFACE ............................................................................. 49

TABLE 12: PIN DEFINITION OF USB INTERFACE ......................................................................................... 51

TABLE 13: USB TRACE LENGTH INSIDE THE MODULE............................................................................... 54

TABLE 14: THE DIFFERENCES BETWEEN USB MODE AND DISPLAYPORT MODE ................................. 55

TABLE 15: USB2 CONFIGURATION ................................................................................................................ 56

TABLE 16: PIN DEFINITION OF UART INTERFACES ..................................................................................... 57

TABLE 17: PIN DEFINITION OF (U)SIM INTERFACES ................................................................................... 59

TABLE 18: PIN DEFINITION OF SD CARD INTERFACE ................................................................................ 61

TABLE 19: SD CARD SIGNAL TRACE LENGTH INSIDE THE MODULE ....................................................... 62

TABLE 20: PIN DEFINITION OF GPIO INTERFACES ..................................................................................... 63

TABLE 21: PIN DEFINITION OF I2C INTERFACES ......................................................................................... 65

TABLE 22: PIN DEFINITION OF I2S INTERFACE ........................................................................................... 65

TABLE 23: PIN DEFINITION OF SPI INTERFACES ........................................................................................ 66

TABLE 24: PIN DEFINITION OF ADC INTERFACES ....................................................................................... 66

TABLE 25: PIN DEFINITION OF LCM INTERFACES ....................................................................................... 67

TABLE 26: PIN DEFINITION OF TOUCH PANEL INTERFACES ..................................................................... 72

TABLE 27: PIN DEFINITION OF CAMERA INTERFACES ............................................................................... 74

TABLE 28: MIPI TRACE LENGTH INSIDE THE MODULE............................................................................... 79

TABLE 29: PIN DEFINITION OF SENSOR INTERFACES ............................................................................... 81

TABLE 30: PIN DEFINITION OF AUDIO INTERFACES ................................................................................... 82

TABLE 31: WI-FI TRANSMITTING PERFORMANCE ....................................................................................... 87

TABLE 32: WI-FI RECEIVING PERFORMANCE .............................................................................................. 88

TABLE 33: BT DATA RATE AND VERSIONS .................................................................................................... 90

TABLE 34: BT TRANSMITTING AND RECEIVING PERFORMANCE ............................................................. 90

TABLE 35: GNSS PERFORMANCE ................................................................................................................. 91

TABLE 36: PIN DEFINITION OF MAIN/RX-DIVERSITY ANTENNA INTERFACES ......................................... 93

TABLE 37: SC66-CE* MODULE OPERATING FREQUENCIES ...................................................................... 93

TABLE 38: SC66-A* MODULE OPERATING FREQUENCIES ......................................................................... 94

TABLE 39: SC66-J* MODULE OPERATING FREQUENCIES ......................................................................... 95

TABLE 40: SC66-E* MODULE OPERATING FREQUENCIES ......................................................................... 96

TABLE 41: PIN DEFINITION OF WI-FI/BT ANTENNA INTERFACE ................................................................ 99

SC66_Hardware_Design 6 / 118

Smart LTE Module Series

SC66 Hardware Design

TABLE 42: WI-FI/BT FREQUENCY................................................................................................................. 100

TABLE 43: PIN DEFINITION OF GNSS ANTENNA ........................................................................................ 100

TABLE 44: GNSS FREQUENCY ..................................................................................................................... 101

TABLE 45: ANTENNA REQUIREMENTS ........................................................................................................ 102

TABLE 46: ABSOLUTE MAXIMUM RATINGS ................................................................................................ 105

TABLE 47: SC66 MODULE POWER SUPPLY RATINGS ............................................................................... 105

TABLE 48: OPERATION AND STORAGE TEMPERATURES ........................................................................ 106

TABLE 49: SC66-CE* CURRENT CONSUMPTION ....................................................................................... 107

TABLE 50: SC66-A* CURRENT CONSUMPTION .......................................................................................... 109

TABLE 51: SC66-J* CURRENT CONSUMPTION ........................................................................................... 110

TABLE 52: SC66-E* CURRENT CONSUMPTION ........................................................................................... 112

TABLE 53: SC66-CE* RF OUTPUT POWER ................................................................................................... 116

TABLE 54: SC66-A* RF OUTPUT POWER ..................................................................................................... 116

TABLE 55: SC66-J* RF OUTPUT POWER ...................................................................................................... 117

TABLE 56: SC66-E* RF OUTPUT POWER ..................................................................................................... 118

TABLE 57: SC66-CE* RF RECEIVING SENSITIVITY ..................................................................................... 119

TABLE 58: SC66-A* RF RECEIVING SENSITIVITY ....................................................................................... 120

TABLE 59: SC66-J* RF RECEIVING SENSITIVITY ....................................................................................... 121

TABLE 60: SC66-E* RF RECEIVING SENSITIVITY ....................................................................................... 122

TABLE 61: ESD CHARACTERISTICS (TEMPERATURE: 25°C , HUMIDITY: 45%) ....................................... 123

TABLE 50: RECOMMENDED THERMAL PROFILE PARAMETERS ............................................................. 129

TABLE 63: REEL PACKAGING ....................................................................................................................... 131

TABLE 64: RELATED DOCUMENTS .............................................................................................................. 132

TABLE 65: TERMS AND ABBREVIATIONS .................................................................................................... 132

TABLE 66: DESCRIPTION OF DIFFERENT CODING SCHEMES ................................................................ 135

TABLE 67: GPRS MULTI-SLOT CLASSES .................................................................................................... 136

TABLE 68: EDGE MODULATION AND CODING SCHEMES ......................................................................... 138

SC66_Hardware_Design 7 / 118

Smart LTE Module Series

SC66 Hardware Design

Figure Index

FIGURE 1: FUNCTIONAL DIAGRAM ............................................................................................................... 24

FIGURE 2: PIN ASSIGNMENT (TOP VIEW)..................................................................................................... 26

FIGURE 3: VOLTAGE DROP SAMPLE ............................................................................................................. 42

FIGURE 4: STRUCTURE OF POWER SUPPLY .............................................................................................. 43

FIGURE 5: REFERENCE CIRCUIT OF POWER SUPPLY .............................................................................. 44

FIGURE 6: TURN ON THE MODULE USING DRIVING CIRCUIT ................................................................... 45

FIGURE 7: TURN ON THE MODULE USING KEYSTROKE ........................................................................... 45

FIGURE 8: AUTOMATIC BOOT REFERENCE CIRCUIT ................................................................................. 46

FIGURE 9: TIMING OF RESTARTING MODULE ............................................................................................. 46

FIGURE 10: RTC POWERED BY RECHARGEABLE BUTTON CELL ............................................................. 47

FIGURE 11: REFERENCE DESIGN FOR BATTERY CHARGING CIRCUIT ................................................... 50

FIGURE 12: USB TYPE-C INTERFACE REFERENCE DESIGN ..................................................................... 53

FIGURE 13: DISPLAY PORT INTERFACES .................................................................................................... 56

FIGURE 14: USB2 HOST ................................................................................................................................. 56

FIGURE 15: REFERENCE CIRCUIT WITH LEVEL TRANSLATOR CHIP (FOR UART6) .............................. 58

FIGURE 16: RS232 LEVEL MATCH CIRCUIT (FOR UART5) .......................................................................... 58

FIGURE 17: REFERENCE CIRCUIT FOR (U)SIM INTERFACE WITH AN 8-PIN (U)SIM CARD CONNECTOR

................................................................................................................................................................... 60

FIGURE 18: REFERENCE CIRCUIT FOR (U)SIM INTERFACE WITH A 6-PIN (U)SIM CARD CONNECTOR

................................................................................................................................................................... 60

FIGURE 19: REFERENCE CIRCUIT FOR SD CARD INTERFACE ................................................................. 62

FIGURE 20: LCM0 EXTERNAL BACKLIGHT DRIVE REFERENCE CIRCUIT ................................................ 69

FIGURE 21: REFERENCE CIRCUIT DESIGN FOR LCM1 INTERFACE ......................................................... 69

FIGURE 22: REFERENCE CIRCUIT DESIGN FOR LCM0 INTERFACE ......................................................... 70

FIGURE 23: REFERENCE CIRCUIT DESIGN FOR LCM1 INTERFACE ......................................................... 71

FIGURE 24: REFERENCE CIRCUIT DESIGN FOR TOUCH PANEL INTERFACES ....................................... 73

FIGURE 25: REFERENCE CIRCUIT DESIGN FOR TWO-CAMERA APPLICATIONS .................................. 76

FIGURE 26: REFERENCE CIRCUIT DESIGN FOR TWO-CAMERA APPLICATIONS .................................... 77

FIGURE 27: REFERENCE CIRCUIT DESIGN FOR THREE-CAMERA APPLICATIONS ................................ 78

FIGURE 28: REFERENCE CIRCUIT DESIGN FOR ANALOG ECM-TYPE MICROPHONE ........................... 83

FIGURE 29: REFERENCE CIRCUIT DESIGN FOR MEMS-TYPE MICROPHONE ........................................ 84

FIGURE 30: REFERENCE CIRCUIT DESIGN FOR EARPIECE IINTERFACE ............................................... 84

FIGURE 31: REFERENCE CIRCUIT DESIGN FOR HEADPHONE INTERFACE ........................................... 85

FIGURE 30: REFERENCE CIRCUIT DESIGN FOR LOUDSPEAKER INTERFACE ....................................... 85

FIGURE 33: REFERENCE CIRCUIT DESIGN FOR EMERGENCY DOWNLOAD INTERFACE ..................... 86

FIGURE 34: REFERENCE CIRCUIT DESIGN FOR MAIN AND RX-DIVERSITY ANTENNA INTERFACES .. 97

FIGURE 33: MICROSTRIP LINE DESIGN ON A 2-LAYER PCB ...................................................................... 98

FIGURE 34: COPLANAR WAVEGUIDE LINE DESIGN ON A 2-LAYER PCB .................................................. 98

FIGURE 35: COPLANAR WAVEGUIDE LINE DESIGN ON A 4-LAYER PCB (LAYER 3 AS REFERENCE

GROUND) .................................................................................................................................................. 98

FIGURE 36: COPLANAR WAVEGUIDE LINE DESIGN ON A 4-LAYER PCB (LAYER 4 AS REFERENCE

SC66_Hardware_Design 8 / 118

Smart LTE Module Series

SC66 Hardware Design

GROUND) .................................................................................................................................................. 99

FIGURE 37: REFERENCE CIRCUIT DESIGN FOR WI-FI/BT ANTENNA INTERFACE ................................ 100

FIGURE 38: REFERENCE CIRCUIT DESIGN FOR GNSS PASSIVE ANTENNA ......................................... 101

FIGURE 39: REFERENCE CIRCUIT DESIGN FOR GNSS ACTIVE ANTENNA ........................................... 102

FIGURE 40: DIMENSIONS OF THE U.FL-R-SMT CONNECTOR (UNIT: MM) .............................................. 103

FIGURE 41: MECHANICALS OF U.FL-LP CONNECTORS ........................................................................... 104

FIGURE 42: SPACE FACTOR OF MATED CONNECTOR (UNIT: MM) ......................................................... 104

FIGURE 43: MODULE TOP AND SIDE DIMENSIONS ................................................................................... 124

FIGURE 44: MODULE BOTTOM DIMENSIONS (TOP VIEW) ....................................................................... 125

FIGURE 45: RECOMMENDED FOOTPRINT (TOP VIEW) ............................................................................ 126

FIGURE 46: TOP VIEW OF THE MODULE .................................................................................................... 127

FIGURE 47: BOTTOM VIEW OF THE MODULE ............................................................................................ 127

FIGURE 48: RECOMMENDED REFLOW SOLDERING THERMAL PROFILE .............................................. 129

FIGURE 49: TAPE DIMENSIONS ................................................................................................................... 130

FIGURE 50: REEL DIMENSIONS ................................................................................................................... 131

SC66_Hardware_Design 9 / 118

Smart LTE Module Series

AT

BE

BG

HR

CY

CZ

DK

EE

FI

FR

DE

EL

HU

IE

IT

LV

LT

LU

MT

NL

PL

PT

RO

SK

SI

ES

SE

UK

SC66 Hardware Design

1 Introduction

This document defines the SC66 module and describes its air interface and hardware interface which are

connected with customers’ applications.

This document can help customers quickly understand module interface specifications, electrical and

mechanical details as well as other related information of SC66 module. Associated with application note

and user guide, customers can use SC66 module to design and set up mobile applications easily.

Hereby, [Quectel Wireless Solutions Co., Ltd.] declares that the radio equipment type [SC66-MW] is in

compliance with Directive 2014/53/EU.

The full text of the EU declaration of conformity is available at the following internet address:

http://www.quectel.com/support/technical.htm

The device is restricted to indoor use only when operating in the 5150 to 5350 MHz frequency range.

The device could be used with a separation distance of 20cm to the human body.

SC66_Hardware_Design 10 / 118

Smart LTE Module Series

5.38

4.48

4.48

5.05

4.54

SC66 Hardware Design

OEM/Integrators Installation Manual

Important Notice to OEM integrators

1. This module is limited to OEM installation ONLY.

2. This module is limited to installation in mobile or fixed applications, according to Part 2.1091(b).

3. The separate approval is required for all other operating configurations, including portable

configurations with respect to Part 2.1093 and different antenna configurations

4. For FCC Part 15.31 (h) and (k): The host manufacturer is responsible for additional testing to verify

compliance as a composite system. When testing the host device for compliance with Part

15 Subpart B, the host manufacturer is required to show compliance with Part 15 Subpart B while the

transmitter module(s) are installed and operating. The modules should be transmitting and the evaluation

should confirm that the module's intentional emissions are compliant (i.e. fundamental and out of band

emissions). The host manufacturer must verify that there are no additional unintentional emissions other

than what is permitted in Part 15 Subpart B or emissions are complaint with the transmitter(s) rule(s).

The Grantee will provide guidance to the host manufacturer for Part 15 B requirements if needed.

End Product Labeling

When the module is installed in the host device, the FCC/IC ID label must be visible through a window on

the final device or it must be visible when an access panel, door or cover is easily re-moved. If not, a

second label must be placed on the outside of the final device that contains the following text: “Contains

FCC ID: XMR201905SC66MW”

“Contains IC: 10224A-20195SC66MW “

The FCC ID/IC ID can be used only when all FCC/IC compliance requirements are met.

Antenna Installation

(1) The antenna must be installed such that 20 cm is maintained between the antenna and users,

(2) The transmitter module may not be co-located with any other transmitter or antenna.

(3) Only antennas of the same type and with equal or less gains as shown below may be used with this

module. Other types of antennas and/or higher gain antennas may require additional authorization for

operation.

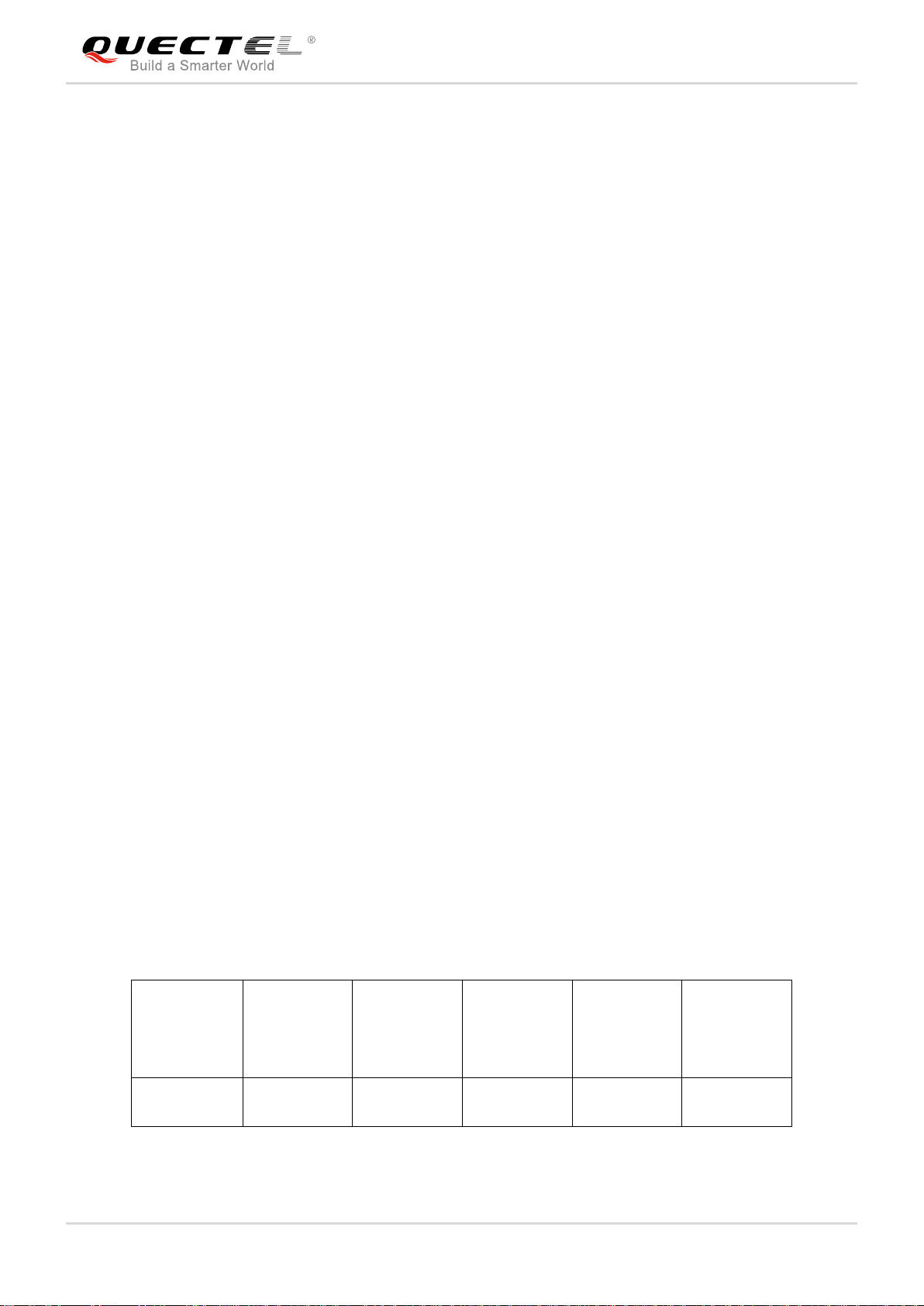

In the event that these conditions cannot be met (for example certain laptop configurations or co-location

Antenna

type

External

antenna

2.4GHz

band

Peak Gain

(dBi)

5.2GHz

band

Peak Gain

(dBi)

5.3GHz

band

Peak Gain

(dBi)

5.5GHz

band

Peak Gain

(dBi)

5.8GHz

band

Peak Gain

(dBi)

SC66_Hardware_Design 11 / 118

Smart LTE Module Series

SC66 Hardware Design

with another transmitter), then the FCC/IC authorization is no longer considered valid and the FCC ID/IC

ID cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for

re-evaluating the end product (including the transmitter) and obtaining a separate FCC/IC authorization.

Manual Information to the End User

The OEM integrator has to be aware not to provide information to the end user regarding how to install or

remove this RF module in the user’s manual of the end product which integrates this module. The end

user manual shall include all required regulatory information/warning as show in this manual.

Federal Communication Commission Interference Statement

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

(1) This device may not cause harmful interference, and (2) this device must accept any interference

received, including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant

to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful

interference in a residential installation. This equipment generates, uses and can radiate radio frequency

energy and, if not installed and used in accordance with the instructions, may cause harmful interference

to radio communications. However, there is no guarantee that interference will not occur in a particular

installation. If this equipment does cause harmful interference to radio or television reception, which can

be determined by turning the equipment off and on, the user is encouraged to try to correct the

interference by one of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

Any changes or modifications not expressly approved by the party responsible for compliance could void

the user's authority to operate this equipment. This transmitter must not be co-located or operating in

conjunction with any other antenna or transmitter.

Industry Canada Statement

This device complies with Industry Canada’s licence-exempt RSSs. Operation is subject to the

following two conditions:

(1) This device may not cause interference; and

(2) This device must accept any interference, including interference that may cause undesired

operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts

de licence. L'exploitation est autorisée aux deux conditions suivantes:

SC66_Hardware_Design 12 / 118

Smart LTE Module Series

SC66 Hardware Design

(1) l'appareil ne doit pas produire de brouillage, et

(2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est

susceptible d'en compromettre le fonctionnement."

The device could automatically discontinue transmission in case of absence of information to transmit, or

operational failure. Note that this is not intended to prohibit transmission of control or signaling information

or the use of repetitive codes where required by the technology.

The device for operation in the band 5150–5250 MHz is only for indoor use to reduce the potential for

harmful interference to co-channel mobile satellite systems;

The maximum antenna gain permitted for devices in the bands 5250–5350 MHz and 5470–5725 MHz

shall comply with the e.i.r.p. limit; and

The maximum antenna gain permitted for devices in the band 5725–5825 MHz shall comply with the

e.i.r.p. limits specified for point-to-point and non point-to-point operation as appropriate.

L'appareil peut interrompre automatiquement la transmission en cas d'absence d'informations à

transmettre ou de panne opérationnelle. Notez que ceci n'est pas destiné à interdire la transmission

d'informations de contrôle ou de signalisation ou l'utilisation de codes répétitifs lorsque cela est requis par

la technologie.

Le dispositif utilisé dans la bande 5150-5250 MHz est réservé à une utilisation en intérieur afin de réduire

le risque de brouillage préjudiciable aux systèmes mobiles par satellite dans le même canal;

Le gain d'antenne maximal autorisé pour les dispositifs dans les bandes 5250-5350 MHz et 5470-5725

MHz doit être conforme à la norme e.r.p. limite; et

Le gain d'antenne maximal autorisé pour les appareils de la bande 5725-5825 MHz doit être conforme à

la norme e.i.r.p. les limites spécifiées pour un fonctionnement point à point et non point à point, selon le

cas.

CAN ICES-3(B)/ NMB-3(B)

Radiation Exposure Statement

This equipment complies with FCC/IC radiation exposure limits set forth for an uncontrolled environment.

This equipment should be installed and operated with minimum distance 20 cm between the radiator &

your body.

SC66_Hardware_Design 13 / 118

Smart LTE Module Series

Full attention must be given to driving at all times in order to reduce the risk of an

accident. Using a mobile while driving (even with a handsfree kit) causes

distraction and can lead to an accident. Please comply with laws and regulations

restricting the use of wireless devices while driving.

Switch off the cellular terminal or mobile before boarding an aircraft. The operation

of wireless appliances in an aircraft is forbidden to prevent interference with

communication systems. If the device offers an Airplane Mode, then it should be

enabled prior to boarding an aircraft. Please consult the airline staff for more

restrictions on the use of wireless devices on boarding the aircraft.

Wireless devices may cause interference on sensitive medical equipment, so

please be aware of the restrictions on the use of wireless devices when in

hospitals, clinics or other healthcare facilities.

Cellular terminals or mobiles operating over radio signals and cellular network

cannot be guaranteed to connect in all possible conditions (for example, with

unpaid bills or with an invalid (U)SIM card). When emergent help is needed in such

conditions, please remember using emergency call. In order to make or receive a

call, the cellular terminal or mobile must be switched on in a service area with

adequate cellular signal strength.

The cellular terminal or mobile contains a transmitter and receiver. When it is ON, it

receives and transmits radio frequency signals. RF interference can occur if it is

used close to TV set, radio, computer or other electric equipment.

In locations with potentially explosive atmospheres, obey all posted signs to turn

off wireless devices such as your phone or other cellular terminals. Areas with

potentially explosive atmospheres include fuelling areas, below decks on boats,

fuel or chemical transfer or storage facilities, areas where the air contains

chemicals or particles such as grain, dust or metal powders, etc.

SC66 Hardware Design

1.1. Safety Information

The following safety precautions must be observed during all phases of operation, such as usage, service

or repair of any cellular terminal or mobile incorporating SC66 module. Manufacturers of the cellular

terminal should send the following safety information to users and operating personnel, and incorporate

these guidelines into all manuals supplied with the product. If not so, Quectel assumes no liability for

customers’ failure to comply with these precautions.

SC66_Hardware_Design 14 / 118

Smart LTE Module Series

Type

Frequency Bands

LTE-FDD

B1/B3/B5/B8

LTE-TDD

B34/B38/B39/B40/B41

WCDMA

B1/B8

TD-SCDMA

B34/B39

EVDO/CDMA

BC0

GSM

900/1800MHz

Wi-Fi 802.11a/b/g/n/ac

2402MHz~2482MHz; 5180MHz~5825MHz

SC66 Hardware Design

2 Product Concept

2.1. General Description

SC66 is a series of Smart LTE module based on Qualcomm platform and Android operating system, and

provides industrial grade performance. Its general features are listed below:

Support worldwide LTE-FDD, LTE-TDD, DC-HSDPA, DC-HSUPA, HSPA+, HSDPA, HSUPA,

WCDMA, TD-SCDMA, EVDO/CDMA, EDGE and GPRS coverage

Support short-range wireless communication via Wi-Fi 802.11a/b/g/n/ac and BT5.0 LE standards

Integrate GPS/GLONASS/BeiDou satellite positioning systems

Support multiple audio and video codecs

Built-in high performance AdrenoTM 512 graphics processing unit

Provide multiple audio and video input/output interfaces as well as abundant GPIO interfaces

SC66 are available in six variants: SC66-MW*, SC66-CE*, SC66-A*, SC66-J*, SC66-E*, SC66-W*.

The following table shows the supported frequency bands of SC66.

Table 1: SC66-CE* Frequency Bands

SC66_Hardware_Design 15 / 118

SC66 Hardware Design

BT5.0

2402MHz~2480MHz

GNSS

GPS: 1575.42MHz±1.023MHz

GLONASS: 1597.5MHz~1605.8MHz

BeiDou: 1561.098MHz±2.046MHz

Type

Frequency Bands

LTE-FDD

B2/B4/B5/B7/B12/B13/B14/B17/B25/B26/B66/B71

LTE-TDD

B41(200M)

WCDMA

B2/B4/B5

Wi-Fi 802.11a/b/g/n/ac

2402MHz~2482MHz; 5180MHz~5825MHz

BT 5.0

2402MHz~2480MHz

GNSS

GPS: 1575.42MHz±1.023MHz

GLONASS: 1597.5MHz~1605.8MHz

BeiDou: 1561.098MHz±2.046MHz

Type

Frequency Bands

LTE-FDD

B1/B3/B5/B8/B11/B18/B19/B21/B26/B28(A+B)

LTE-TDD

B41(120M)

WCDMA

B1/B6/B8/B19

Wi-Fi 802.11a/b/g/n/ac

2402MHz~2482MHz; 5180MHz~5825MHz

BT 5.0

2402MHz~2480MHz

GNSS

GPS: 1575.42MHz±1.023MHz

GLONASS: 1597.5MHz~1605.8MHz

BeiDou: 1561.098MHz±2.046MHz

Table 2: SC66-A* Frequency Bands

Smart LTE Module Series

Table 3: SC66-J* Frequency Bands

SC66_Hardware_Design 16 / 118

SC66 Hardware Design

Type

Frequency Bands

LTE-FDD

B1/B2/B3/B4/B5/B7/B8/B20/B28(A+B)

LTE-TDD

B38/B39/B40/B41(200M)

WCDMA

B1/B2/B4/B5/B8

GSM

B2/B3/B5/B8

Wi-Fi 802.11a/b/g/n/ac

2402MHz~2482MHz; 5180MHz~5825MHz

BT 5.0

2402MHz~2480MHz

GNSS

GPS: 1575.42MHz±1.023MHz

GLONASS: 1597.5MHz~1605.8MHz

BeiDou: 1561.098MHz±2.046MHz

Type

Frequency Bands

LTE-FDD

/

LTE-TDD

/

WCDMA

/

TD-SCDMA

/

CDMA

/

GSM

/

Wi-Fi 802.11a/b/g/n/ac

2402MHz~2482MHz; 5180MHz~5825MHz

BT 5.0

2402MHz~2480MHz

GNSS

/

Table 4: SC66-E* Frequency Bands

Smart LTE Module Series

Table 5: SC66-W* Frequency Bands

SC66_Hardware_Design 17 / 118

Smart LTE Module Series

“*” means under development. SC66-A、SC66-J、SC66-E、SC66-MW support WIFI_MIMO

Type

Frequency Bands

LTE-FDD

/

LTE-TDD

/

WCDMA

/

TD-SCDMA

/

CDMA

/

GSM

/

Wi-Fi 802.11a/b/g/n/ac

2402MHz~2482MHz; 5180MHz~5825MHz

BT 5.0

2402MHz~2480MHz

GNSS

/

NOTE

SC66 Hardware Design

Table 6: SC66-MW*(2*2 MIMO WIFI) Frequency Bands

SC66 is an SMD type module which can be embedded into applications through its 324 pins (including

152 LCC pads and 172 LGA pads). With a compact profile of 43.0mm × 44.0mm × 2.85mm, SC66 can

meet almost all requirements for M2M applications such as smart metering, smart home, security, routers,

wireless POS, mobile computing devices, PDA phone, tablet PC, etc.

SC66_Hardware_Design 18 / 118

Smart LTE Module Series

Features

Details

Application Processor

Customized 64-bit ARM v8-compliant applications processorCustomized

64-bit ARM v8-compliant applications processor

Kryo Gold: quad high-performance cores targeting 2.2 GHz

Kryo Silver: quad low-power cores targeting 1.843 GHz

two quad-core processors with 1MB L2 cache

Modem system

LTE Cat 6(FDD and TDD), 2*20 CA(40MHz)

GPU

Adreno 512 up to 650 MHzAdreno 512 up to 650 MHz

Memory

32GB eMMC + 3GB LPDDR4x(default)

64GB eMMC + 4GB LPDDR4x (optional)

Operating System

Android 9

Power Supply

VBAT Supply Voltage: 3.55V~4.4V

Typical 4.0V

Transmitting Power

Class 4 (33dBm±2dB) for EGSM900

Class 1 (30dBm±2dB) for DCS1800

Class E2 (27dBm±3dB) for EGSM900 8-PSK

Class E2 (26dBm±3dB) for DCS1800 8-PSK

Class 3 (24dBm+1/-3dB) for WCDMA bands

Class 3 (24dBm+3/-1dB) for EVDO/CDMA BC0

Class 2 (24dBm+1/-3dB) for TD-SCDMA bands

Class 3 (23dBm±2dB) for LTE-FDD bands

Class 3 (23dBm±2dB) for LTE-TDD bands

LTE Features

Support 3GPP R12 Cat 6* and Cat 4

Support 1.4 MHz to 20MHz RF bandwidth

Support Multiuser MIMO in DL direction

Cat 6* FDD: Max 300Mbps (DL)/Max 50Mbps (UL)

Cat 6* TDD: Max 265Mbps (DL)/Max 30Mbps (UL)

Cat 4 FDD: Max 150Mbps (DL)/Max 50Mbps (UL)

Cat 4 TDD: Max 130Mbps (DL)/Max 30Mbps (UL)

UMTS Features

Support 3GPP R9 DC-HSDPA/DC-HSUPA/HSPA+/HSDPA/HSUPA/WCDMA

Support QPSK, 16-QAM and 64-QAM modulation

DC-HSDPA: Max 42Mbps (DL)

DC-HSUPA: Max 11.2Mbps (UL)

SC66 Hardware Design

2.2. Key Features

The following table describes the detailed features of SC66 module.

Table 7: SC66 Key Features

SC66_Hardware_Design 19 / 118

Smart LTE Module Series

WCDMA: Max 384Kbps (DL)/Max 384Kbps (UL)

TD-SCDMA Features

Support CCSA Release 3 TD-SCDMA

Max 4.2Mbps (DL)/Max 2.2Mbps (UL)

CDMA2000 Features

Support 3GPP2 CDMA2000 1X Advanced, CDMA2000 1x EV-DO Rev.A

EVDO: Max 3.1Mbps (DL)/Max 1.8 Mbps (UL)

1X Advanced: Max 307.2Kbps (DL)/Max 307.2Kbps (UL)

GSM Features

R99

CSD: 9.6kbps, 14.4kbps

GPRS

Support GPRS multi-slot class 33 (33 by default)

Coding scheme: CS-1, CS-2, CS-3 and CS-4

Max 107Kbps (DL), 85.6Kbps (UL)

EDGE

Support EDGE multi-slot class 33 (33 by default)

Support GMSK and 8-PSK for different MCS (Modulation and Coding

Scheme)

Downlink coding schemes: CS 1-4 and MCS 1-9

Uplink coding schemes: CS 1-4 and MCS 1-9

Max 296Kbps (DL), 236.8Kbps (UL)

WLAN Features

2.4GHz/5GHz, support 802.11a/b/g/n/ac, maximally up to 433Mbps

Support AP and STA mode

Bluetooth Features

BT5.0 LE

GNSS Features

GPS/GLONASS/BeiDou

SMS

Text and PDU mode

Point-to-point MO and MT

SMS cell broadcast

LCM Interfaces

Support for MIPI_DSI and DP overTYPE-C for dual screen display

MIPI_DSI Supports up to 2560x1600@60fps

DP supports 4K@30fps

Camera Interfaces

Support three groups of 4-lane MIPI_CSI, up to 2.1Gbps per lane

Support 3 cameras (4-lane + 4-lane + 4-lane) or 4 cameras (4-lane + 4-lane +

2-lane + 1-lane)

up to 24MP with dual ISP

Video Codec

Video encoding and decoding: up to 4K @30fps

Concurrency: encoding up to 1080P @30fps; decoding up to 1080P @60fps

Audio Interfaces

Audio Input

Three analog microphone inputs, integrating internal bias voltage

Audio Output

Class AB stereo headphone output

Class AB earpiece differential output

Class D speaker differential amplifier output

SC66 Hardware Design

SC66_Hardware_Design 20 / 118

Smart LTE Module Series

1. 1) Within operation temperature range, the module is 3GPP compliant.

Audio Codec

EVRC, EVRC-B, EVRC-WB; G.711, G.729A/AB; GSM-FR, GSM-EFR,

GSM-HR; AMR-NB, AMR-WB, AMR-eAMR, AMR-BeAMR

USB Interface

Compliant with USB 3.1 and 2.0 specifications, with transmission rates up to

10Gbps on USB 3.1 and 480Mbps on USB 2.0.

Support USB OTG

Used for AT command communication, data transmission, software

debugging and firmware upgrade

UART Interfaces

4 UART Interfaces: DEBUG UART、UART6、UART1 and LPI_UART_2

UART6: 4-wire UART interface with RTS/CTS hardware flow control,

max rate up to 4Mbps

UART1: terface

DEBUG: 2-wire UART interface used for debugging

LPI_UART_2:low power uart, use is not recommended for the time being

SD Card Interface

Support SD 3.0

Support SD card hot-plug

(U)SIM Interfaces

2 (U)SIM interfaces

Support USIM/SIM card: 1.8V/2.95V

Support Dual SIM Dual Standby (supported by default)

I2C Interfaces

It supports up to five I2C interfaces, used for peripherals such as TP, camera,

sensor, etc.

I2S Interface

Supports two I2S, one of which is low power I2S

ADC Interfaces

2 general purpose ADC interfaces

SPI Interfaces

One SPI interfaces, only support master mode

Real Time Clock

Supported

Antenna Interfaces

Main antenna, Rx-diversity antenna, GNSS antenna and Wi-Fi/BT antenna

interfaces

Physical Characteristics

Size: (43.0±0.15)mm × (44.0±0.15)mm × (2.85±0.2)mm

Package: LCC + LGA

Weight: approx. 13.0g

Temperature Range

Operating temperature range: -35°C ~ +65°C

1)

Extended temperature range: -40°C ~ +75°C

2)

Storage temperature range: -40°C ~ +90°C

Firmware Upgrade

Over USB interface

RoHS

All hardware components are fully compliant with EU RoHS directive

NOTES

SC66 Hardware Design

SC66_Hardware_Design 21 / 118

Smart LTE Module Series

2. 2) Within extended temperature range, the module remains the ability to establish and maintain a

voice, SMS, data transmission, emergency call, etc. There is no unrecoverable malfunction. There

are also no effects on radio spectrum and no harm to radio network. Only one or more parameters like

P

out

might reduce in their value and exceed the specified tolerances. When the temperature returns to

the normal operating temperature levels, the module will meet 3GPP specifications again.

3. “*” means under development.

SC66 Hardware Design

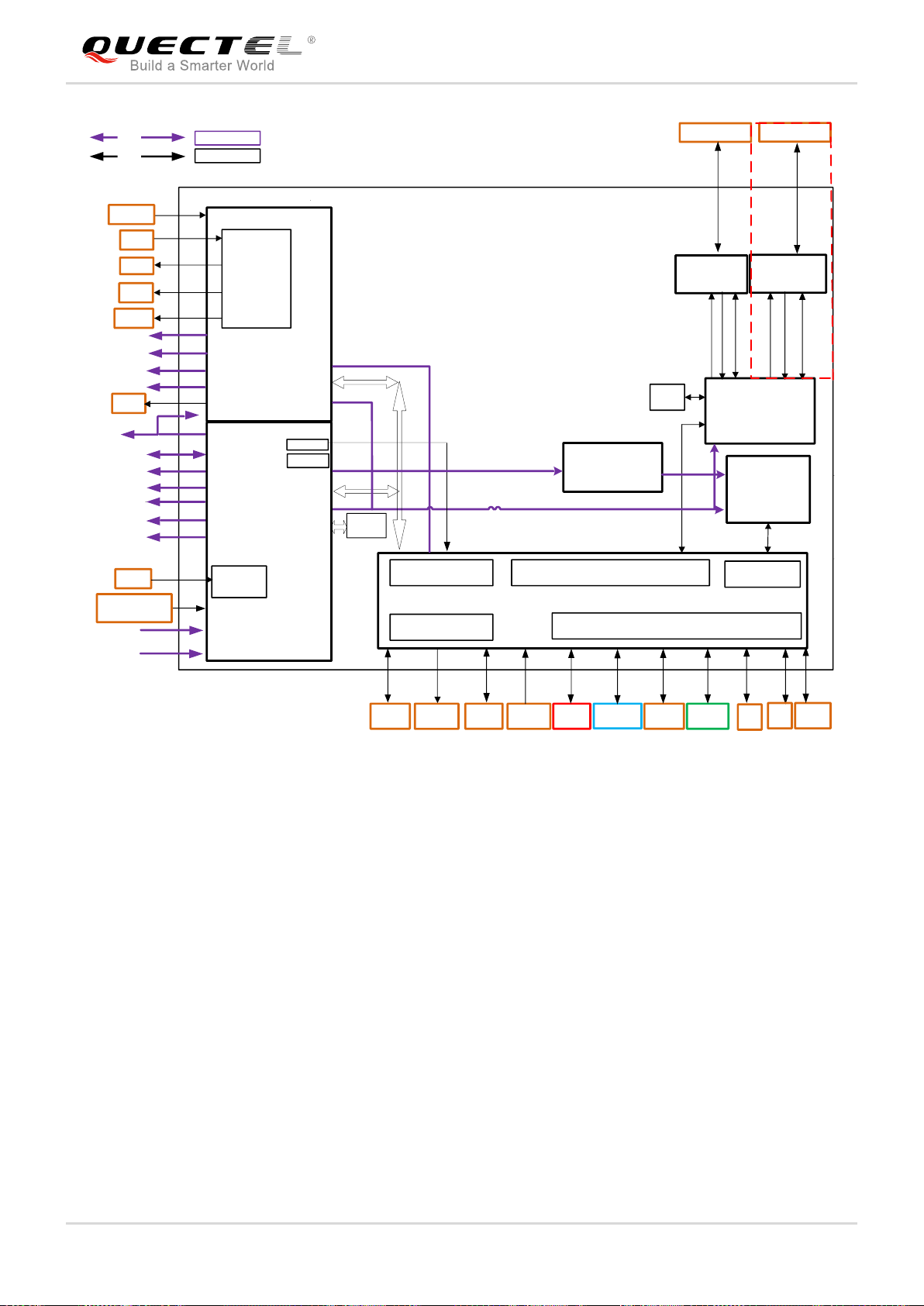

2.3. Functional Diagram

The following figure shows a block diagram of SC66 and illustrates the major functional parts.

Power management

Radio frequency

Baseband

LPDDR4X+eMMC flash

Peripheral interfaces

-- USB interface

-- (U)SIM interfaces

-- UART interfaces

-- SD card interface

-- I2C interfaces

- I2S interfaces

-- SPI interfaces

--ADC interfaces

-- LCM (MIPI) interfaces

-- TP (touch panel) interfaces

-- Camera (MIPI) interfaces

-- Audio interfaces

SC66_Hardware_Design 22 / 118

Smart LTE Module Series

Baseband

WCN

LPDDR

eMMC

FEM

XO

ANT_WIFI/BT

SD 3.0

UART

2×(U)SIM

USB

2.0&3.1

CAM

TPLCMSPI

EAR

SPK

MICs

RFCLK

BBCLK

MEM

Multimedia

Connectivity

Air Interface

Porcessors

Codec

Power

Signal

Power

Function

38.4MHZ

38.4

M

XO

Headset

VDD_RF

VOL_UP

VRTC

USIM1_VDD

USIM2_VDD

LDO13A_1P8

LDO11A_1P8

LDO14A_1P8

BATTERY

VPH_PWR

VBUS

GPIOs

13.2

769

I2C

I2S

PWRKEY

VOL DOWN

PM660L

SD_PU_VDD

SD_VDD

ADCs

LDO7B_3P125

LDO3B_2P8

HK ADC

&MPPs

PM660

PWM

PM-3003A

FEM

ANT_WIFI/BT

SC66 Hardware Design

This diagram just used for SC66-MW

SC66_Hardware_Design 23 / 118

Smart LTE Module Series

Baseband

Tranceiver

WCN

LPDDR

eMMC

FEM

XO

ANT_ GNSS

ANT_WIFI/BT

SD 3.0

UART

2×(U)SIM

USB

2.0&3.1

CAM

TPLCMSPI

EAR

SPK

MICs

RFCLK

BBCLK

MEM

Multimedia

Connectivity

Air Interface

Porcessors

Codec

Power

Signal

Power

Function

38.4MHZ

Duplexs

PA

Switch

SAW

LNA

SAW

SAW

Switch

SAW

ANT_DRX

ANT_ MAIN

38.4

M

XO

Headset

APT

VDD_RF

VOL_UP

C

1

VRTC

USIM1_VDD

USIM2_VDD

LDO13A_1P8

LDO11A_1P8

LDO14A_1P8

BATTERY

VPH_PWR

VBUS

GPIOs

13.2

769

I2C

I2S

PWRKEY

VOL DOWN

PM660L

SD_PU_VDD

SD_VDD

ADCs

LDO7B_3P125

LDO3B_2P8

HK ADC

&MPPs

PM660

PWM

PM-3003A

0欧姆跳贴

FEM

ANT_WIFI/BT

The red dotted frame is WIFI_MIMO path, which is not supported by SC66-CE and SC66-W.

NOTE

SC66 Hardware Design

-

2.4. Evaluation Board

Figure 1: Functional Diagram

In order to help customers develop applications with SC66 conveniently, Quectel supplies the evaluation

board, USB to RS232 converter cable, USB Type-C data cable, power adapter, earphone, antenna and

other peripherals to control or test the module.

SC66_Hardware_Design 24 / 118

Smart LTE Module Series

SC66 Hardware Design

3 Application Interfaces

3.1. General Description

SC66 is equipped with 324-pin 1.0mm pitch SMT pads that can be embedded into cellular application

platform. The following chapters provide the detailed description of pins/interfaces listed below.

Power supply

Turn on and off function

VRTC interface

Power Output

Charging interface

USB interface

UART interfaces

(U)SIM interfaces

SD card interface

GPIO interfaces

I2C interfaces

I2S interfaces

SPI interfaces

ADC interfaces

LCM interfaces

TP (touch panel) interfaces

Camera interfaces

Sensor interfaces

Audio interfaces

Emergency download interface

SC66_Hardware_Design 25 / 118

Smart LTE Module Series

313

314

315

316

317

318

319

306

307

308

309

310

311

312

299

300

301

302

303

304

305

292

293

294

295

296

297

298

285

286

287

288

289

290

291

278

279

280

281

282

283

284

271

272

273

274

275

276

277

264

265

266

268

269

270

267

257

258

259

261

262

263

260

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

39

41

42

43

44

45

46

47

48

49

51

52

53

54

40

50

55

56

57

585960

616263

64

323

321

322

2

4

25

26

27

29

28

30

31

32

33

34

35

36

37

38

656667

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

109

111

112

113

114

115

116

117

118

120

121

122

123

124

125

126

128

129

130

131

132

133

134

135

136

137

138

139

141

142

143

144

145

146

147

148

149

150

151

152

127

140

153

154

155

156

157

158

159

160

161

162

163

164

165

166

119

GND POWER AUDIO USB

(U)SIM SD TP LCM

CAMERA ANT UART GPIO

RESERVED

OTHERS

108

110

182

183

184

185

186

187

188

189

190

191

192

193

194

195

211

212

213

214

215

216

217

218

219

220

221

244

243

242

241

240

239

238

237

236

235

234

320

324

SC66 Hardware Design

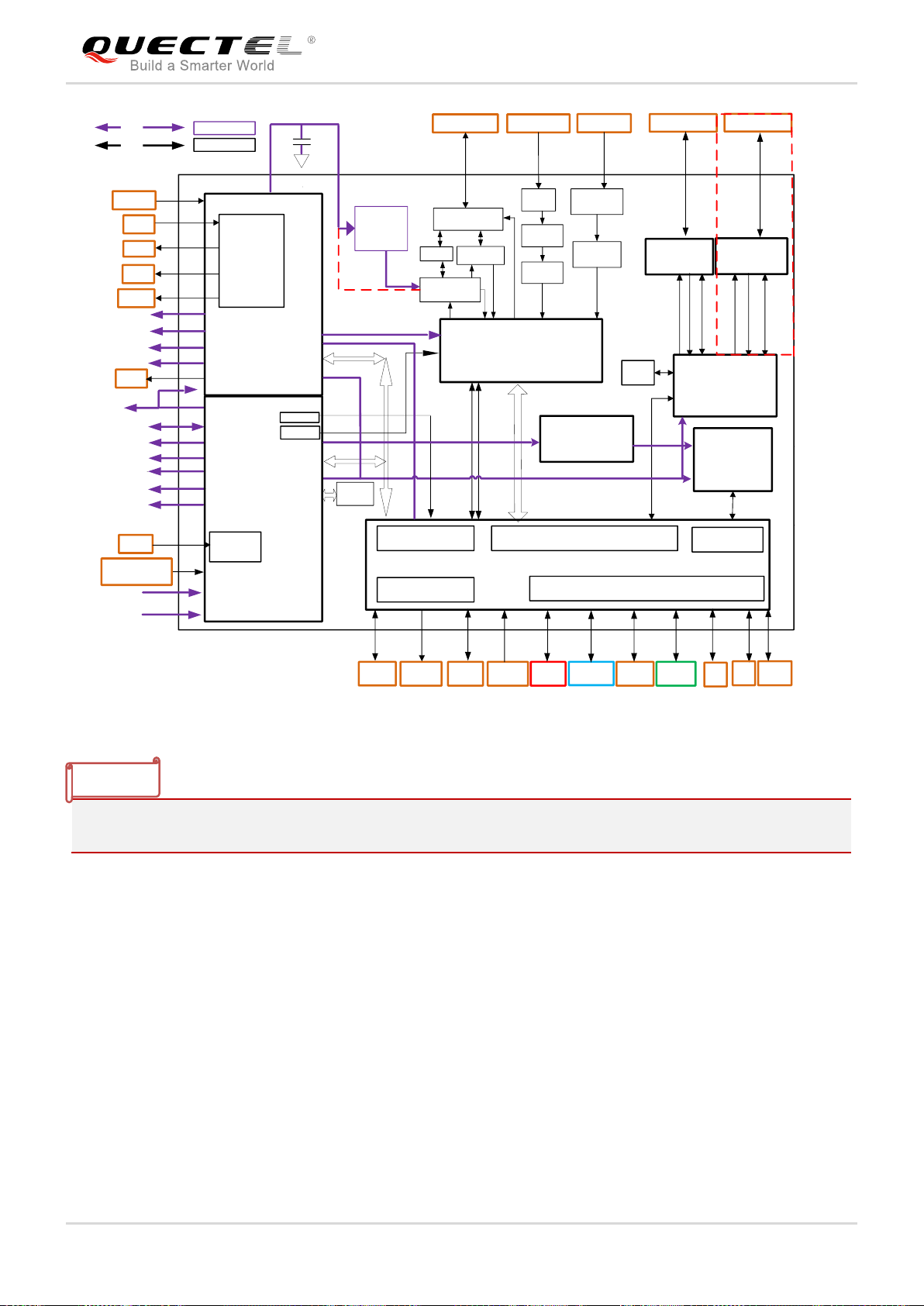

3.2. Pin Assignment

The following figure shows the pin assignment of SC66 module.

Figure 2: Pin Assignment (Top View)

SC66_Hardware_Design 26 / 118

SC66 Hardware Design

Type

Description

IO

Bidirectional

DI

Digital input

DO

Digital output

PI

Power input

PO

Power output

AI

Analog input

AO

Analog output

OD

Open drain

Power Supply

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

VBAT

36,37, 38

PI/PO Power supply for the

module

Vmax=4.4V

Vmin=3.55V

Vnorm=4.0V

It must be able to

provide sufficient

current up to 3.0A.

It is suggested to

use a TVS to

increase voltage

surge withstand

capability.

VDD_RF

1, 2

PO

Connect to external

bypass capacitors to

eliminate voltage

fluctuation of RF

part.

Vmax=4.4V

Vmin=3.55V

Vnorm=4.0V

Do not load

externally.

VRTC

16

PI/P

Power supply for

VOmax=3.2V;

3.3. Pin Description

Table 8: I/O Parameters Definition

Smart LTE Module Series

The following tables show the SC66’s pin definition and electrical characteristics.

Table 9: Pin Description

SC66_Hardware_Design 27 / 118

Smart LTE Module Series

O

internal RTC circuit

When VBAT is not

connected

:

VI=2.1V~3.25V

LDO13A_1

P8

9

PO

1.8V output power

supply

Vnorm=1.8V

IOmax=20mA

Power supply for

external GPIO’s

pull up circuits and

level shift circuit.

LDO7B_3P

125

157

PO

3.125V output power

supply

Vnorm=3.125V

IOmax=150mA

Power supply only

for DP switch

LDO11A_1P

8

10

PO

1.8V output power

supply

Vnorm=1.8V

IOmax=150mA

Power supply for

I/O VDD of

cameras, LCDs

and TP etc.

LDO14A_1

P8

158

PO

1.8V output power

supply

Vnorm=1.8V

IOmax=150mA

Power supply for

Sensors. Add a

1.0uF~4.7uF

bypass capacitor if

used.

If unused, keep

this pin open.

LDO3B_2P

8

12

PO

2.8V output power

supply

Vnorm=2.8V

IOmax=600mA

Power supply for

sensor and LCM.

Add a 1.0uF~2.2uF

bypass capacitor if

used.

If unused, keep

this pin open.

VPH_PWR

30

PO

VBAT output power

supply

Vnorm=VBAT

IOmax=1000mA

Power supply for

other ICs.ICs

GND

3,4,18 ,

20,24,

31,34,

35,40,

Ground

SC66 Hardware Design

SC66_Hardware_Design 28 / 118

Smart LTE Module Series

43,47,

56,62,

87,98,

101,112,

125,128,

130,133,

135,148,

150,159,

160,163,

166,170,

173,176,

182,193,

195,219,

225,243,

257~323

Audio Interfaces

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

MIC_BIAS

167

AO

Microphone bias

voltage

VO=1.6V~2.9V

MIC1_P

44

AI

Microphone positive

input for channel 1

MIC1_M

45

AI

Microphone

negative input for

channel 1

MIC_GND

168

Microphone

reference ground

If unused, it should

be connected to

GND

MIC2_P

46

AI

Microphone

Headset mic input

SC66 Hardware Design

SC66_Hardware_Design 29 / 118

Smart LTE Module Series

positive input for

headset

MIC3_P

169

AI

Microphone

positive input for

second mic

Second mic input

EAR_P

53

AO

Earpiece positive

output

EAR_M

52

AO

Earpiece negative

output

SPK_P

55

AO

Speaker positive

output

SPK_M

54

AO

Speaker negative

output

HPH_R

51

AO

Headphone right

channel output

HPH_REF

50

AI

Headphone

reference ground

It should be

connected to main

GND

HPH_L

49

AO

Headphone left

channel output

HS_DET

48

AI

Headset insertion

detection

Default high level

USB Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

USB_VBUS

41, 42

PI/P

O

Charging power

input.

Power supply

output for OTG

device.

USB/charger

insertion

detection.

Vmax=10V

Vmin=3.6V

Vnorm=5.0V

USB2_HS_

DM

25

IO

USB 2.0

differential data

bus (minus)

USB 2.0 standard

compliant

90Ω differential

impedance.

USB2_HS_

DP

26

IO

USB 2.0

differential data

bus (plus)

USB1_HS_

DM

33

IO

USB 2.0

differential data

bus (minus)

USB 2.0 standard

compliant

90Ω differential

impedance;

One part of the

SC66 Hardware Design

SC66_Hardware_Design 30 / 118

Smart LTE Module Series

USB1_HS_

DP

32

IO

USB 2.0

differential data

bus (plus)

TYPE-C.

USB_SS2_T

X_P

165

IO

USB 3.1

differential

transmit (plus)

USB 3.1 channel2

standard compliant

90Ω differential

impedance.

USB_SS2_T

X_M

164

IO

USB 3.1

differential

transmit (minus)

USB_SS2_

RX_P

162

IO

USB 3.1

differential receive

(plus)

USB_SS2_

RX_M

161

IO

USB 3.1

differential receive

(minus)

USB_SS1_

RX_P

171

IO

USB 3.1

differential receive

(plus)

USB 3.1 channel1

standard compliant

90Ω differential

impedance.

USB_SS1_

RX_M

172

IO

USB 3.1

differential receive

(minus)

USB_SS1_T

X _P

174

IO

USB 3.1

differential

transmit (plus)

90Ω differential

impedance.

USB_SS1_T

X _M

175

IO

USB 3.1

differential

transmit (minus)

USB_CC1

224

AI

USB Type-C

detection channel

1

When micro usb is

used ,it can be

used as ID pin

USB_CC2

223

AI

USB Type-C

detection channel

2

UUSB_TYP

EC

23

DI

TYPE-C&uUSB

configuration

control pin

When USB

TYPE-C is used, it

should be

connected to

VPH_PWR

through 10K

resistor. When

uUSB is used, it

should be

connected to GND

SC66 Hardware Design

SC66_Hardware_Design 31 / 118

Smart LTE Module Series

through 10K

resistor.

SS_DIR_IN

21

DI

CC status

detection pin

When USB

TYPE-C is used, it

should be

connected to

SS_DIR_OUT.

When uUSB is

used, it should be

connected to GND.

SS_DIR_OU

T

226

DO

CC status output

pin

When USB

TYPE-C is used, it

should be

connected to

SS_DIR_IN. When

uUSB is used, it

should be kept

open.

(U)SIM Interfaces

Pin Name

Pin

No.

I/O

Description

DC Characteristics

Comment

USIM1_DET

145

DI

(U)SIM1 card

hot-plug detection

VILmax=0.63V

VIHmin=1.17V

Active Low.

Require external

pull-up to 1.8V.

If unused, keep

this pin open.

USIM1_RST

144

DO

(U)SIM1 card

reset signal

VOLmax=0.4V

VOHmin=

0.8 × USIM1_VDD

USIM1_CLK

143

DO

(U)SIM1 card

clock signal

USIM1_DATA

142

IO

(U)SIM1 card data

signal

VILmax=

0.2 × USIM1_VDD

VIHmin=

0.7 × USIM1_VDD

VOLmax=0.4V

VOHmin=

0.8 × USIM1_VDD

USIM1_VDD

141

PO

(U)SIM1 card

power supply

Either 1.8V or

2.95V (U)SIM card

is supported.

USIM2_DET

256

DI

(U)SIM2 card

detection

VILmax=0.63V

VIHmin=1.17V

Active Low.

Need external

SC66 Hardware Design

SC66_Hardware_Design 32 / 118

Smart LTE Module Series

pull-up to 1.8V.

If unused, keep

this pin open.

USIM2_RST

207

DO

(U)SIM2 card

reset signal

VOLmax=0.4V

VOHmin=

0.8 × USIM2_VDD

USIM2_CLK

208

DO

(U)SIM2 card

clock signal

VOLmax=0.4V

VOHmin=

0.8 × USIM2_VDD

USIM2_DATA

209

IO

(U)SIM2 card data

signal

VILmax=

0.2 × USIM2_VDD

VIHmin=

0.7 × USIM2_VDD

VOLmax=0.4V

VOHmin=

0.8 × USIM2_VDD

USIM2_VDD

210

PO

(U)SIM2 card

power supply

Either 1.8V or

2.95V (U)SIM card

is supported.

UART Interfaces

Pin Name

Pin

I/O

Description

DC Characteristics

Comment

DEBUG_TXD

5

DO

DEBUG transmit

data.

Debug port by

default.

VOLmax=0.45V

VOHmin=1.35V

1.8V power

domain.

If unused, keep

these pins open.

DEBUG_RXD

6

DI

DEBUG receive

data.

Debug port by

default.

VILmax=0.63V

VIHmin=1.17V

UART1_TXD

7

DO

UART1 transmit

data

VOLmax=0.45V

VOHmin=1.35V

UART1_RXD

8

DI

UART1 receive

data

VILmax=0.63V

VIHmin=1.17V

UART6_RXD

198

DI

UART6 receive

data

VILmax=0.63V

VIHmin=1.17V

UART6_TXD

199

DO

UART6 transmit

data

VOLmax=0.45V

VOHmin=1.35V

UART6_RTS

245

DO

UART6 request to

send

VOLmax=0.45V

VOHmin=1.35V

UART6_CTS

246

DI

UART6 clear to

send

VILmax=0.63V

VIHmin=1.17V

SC66 Hardware Design

SC66_Hardware_Design 33 / 118

Smart LTE Module Series

LPI_UART_2_T

XD

60

DO

UART2 transmit

data

VOLmax=0.45V

VOHmin=1.35V

LPI_UART_2_R

XD

61

DI

UART2 receive

data

VILmax=0.63V

VIHmin=1.17V

SD Card Interface

Pin Name

Pin

I/O

Description

DC Characteristics

Comment

SD_CLK

70

DO

High speed digital

clock signal of SD

card

1.8V SD card:

VOLmax=0.45V

VOHmin=1.4V

2.95V SD card:

VOLmax=0.368V

VOHmin=2.125V

SD_CMD

69

IO

Command signal

of SD card

1.8V SD card:

VILmax=0.58V

VIHmin=1.27V

VOLmax=0.45V

VOHmin=1.4V

2.95V SD card:

VILmax=0.737V

VIHmin=1.843V

VOLmax=0.368V

VOHmin=2.125V

SD_DATA0

68

IO

High speed

bidirectional digital

signal lines of SD

card

SD_DATA1

67

IO

SD_DATA2

66

IO

SD_DATA3

65

IO

SD_DET

64

DI

SD card insertion

detection

VILmax=0.63V

VIHmin=1.17V

Active low.

SD_VDD

63

PO

Power supply for

SD card

Vnorm=2.95V

IOmax=600mA

SD_PU_VDD

179

PO

2.95V output

Vnorm=1.8V/2.95V

IOmax=50mA

Power supply for

SD card’s pull-up

circuit.

TP (Touch Panel) Interfaces

Pin Name

Pin N

I/O

Description

DC Characteristics

Comment

SC66 Hardware Design

SC66_Hardware_Design 34 / 118

Smart LTE Module Series

TP0_RST

138

DO

Reset signal of

touch panel (TP0)

VOLmax=0.45V

VOHmin=1.35V

1.8V power

domain. Active low.

TP0_INT

139

DI

Interrupt signal of

touch panel (TP0)

VILmax=0.63V

VIHmin=1.17V

1.8V power

domain.

TP0_I2C_SCL

140

OD

I2C clock signal of

touch panel (TP0)

1.8V power

domain.

TP0_I2C_SDA

206

OD

I2C data signal of

touch panel (TP0)

1.8V power

domain.

LCM Interfaces

Pin Name

Pin

No.

I/O

Description

DC Characteristics

Comment

PWM

152

DO

PWM Output

LCD0_RST

127

DO

LCD0 reset signal

VOLmax=0.45V

VOHmin=1.35V

1.8V power domain

It should not be

pulled up.

LCD0_TE

126

DI

LCD0 tearing

effect signal

VILmax=0.63V

VIHmin=1.17V

1.8V power

domain.

DSI0_CLK_N

116

AO

LCD0 MIPI clock

signal (negative)

85Ω differential

impedance.

DSI0_CLK_P

115

AO

LCD0 MIPI clock signal

(positive)

DSI0_LN0_N

118

AO

LCD0 MIPI lane 0 data

signal (negative)

85Ω differential

impedance.

DSI0_LN0_P

117

AO

LCD0 MIPI lane 0 data

signal (positive)

DSI0_LN1_N

120

AO

LCD0 MIPI lane 1 data

signal (negative)

85Ω differential

impedance.

DSI0_LN1_P

119

AO

LCD0 MIPI lane 1 data

signal (positive)

DSI0_LN2_N

122

AO

LCD0 MIPI lane 2 data

signal (negative)

85Ω differential

impedance.

DSI0_LN2_P

121

AO

LCD0 MIPI lane 2 data

signal (positive)

DSI0_LN3_N

124

AO

LCD0 MIPI lane 3 data

signal (negative)

85Ω differential

impedance.

DSI0_LN3_P

123

AO

LCD0 MIPI lane 3 data

signal (positive)

Camera Interfaces

SC66 Hardware Design

SC66_Hardware_Design 35 / 118

Smart LTE Module Series

Pin Name

Pin

No.

I/O

Description

DC

Characteristics

Comment

CSI1_CLK_N

89

AI

MIPI clock signal of rear

camera (negative)

85Ω differential

impedance.

CSI1_CLK_P

88

AI

MIPI clock signal of rear

camera (positive)

CSI1_LN0_N

91

AI

MIPI lane 0 data signal of

rear camera (negative)

85Ω differential

impedance.

CSI1_LN0_P

90

AI

MIPI lane 0 data signal of

rear camera (positive)

CSI1_LN1_N

93

AI

MIPI lane 1 data signal of

rear camera (negative)

85Ω differential

impedance.

CSI1_LN1_P

92

AI

MIPI lane 1 data signal of

rear camera (positive)

CSI1_LN2_N

95

AI

MIPI lane 2 data signal of

rear camera (negative)

85Ω differential

impedance.

CSI1_LN2_P

94

AI

MIPI lane 2 data signal of

rear camera (positive)

CSI1_LN3_N

97

AI

MIPI lane 3 data signal of

rear camera (negative)

85Ω differential

impedance.

CSI1_LN3_P

96

AI

MIPI lane 3 data signal of

rear camera (positive)

CSI2_CLK_N

184

AI

MIPI clock signal of depth

camera (negative)

85Ω differential

impedance.

CSI2_CLK_P

183

AI

MIPI clock signal of depth

camera (positive)

CSI2_LN0_N

186

AI

MIPI lane 0 data signal of

depth camera (negative)

85Ω differential

impedance.

CSI2_LN0_P

185

AI

MIPI lane 0 data signal of

depth camera (positive)

CSI2_LN1_N

188

AI

MIPI lane 1 data signal of

depth camera (negative)

85Ω differential

impedance.

CSI2_LN1_P

187

AI

MIPI lane 1 data signal of

depth camera (positive)

CSI2_LN2_N

190

AI

MIPI lane 2 data signal of

depth camera (negative)

85Ω differential

impedance.

CSI2_LN2_P

189

AI