M50Hardware Design

M50

Quectel Cellul ar Engine

Hardware Design

M50_HD_V2.0

M50_HD_V2.0 - 1 -

M50Hardware Design

Quecctel

Confidential

Document Title M50 Hardware Design

Revision 2.0

Date 2012-06-26

Status Released

Document Control ID M50_HD_V2.0

General Notes

Quectel offers this information as a service to its customers, to support application and

engineering efforts that use the products de signed by Quectel. The information provid ed is

based upon requirements specifically provided for customers of Quectel. Quectel has not

undertaken any independent search for additional information, relevant to any information

that may be in the customer’s possession. Furthermore, system validation of this product

designed by Quectel within a larger electronic system remains the responsibility of the

customer or t he custome r’s syste m inte gra tor. All speci ficati ons suppl ie d her ein a re subjec t to

change.

Copyright

This d ocument contains propri etary te chnical inf ormation of Quecte l Co., Ltd. Copying this

document, distribution to others, a nd communica tion of the contents there of, are forbidden

without permission. Offenders are liable to the payment of damages. All rights are reserved in

the event of a patent grant or registration of a utility model or design. All specifications

supplied herei n are subject to change wit hout notice at any time.

Copyright © Shanghai Quectel Wireless Solutions Ltd. 2012.

M50_HD_V2.0 - 2 -

M50Hardware Design

Quecctel

Confidential

Contents

Contents ................................................................................................................................................... 3

Table Index .............................................................................................................................................. 5

Figure Index ............................................................................................................................................ 6

0. Revi s io n hi stor y .................................................................................................................................. 8

1. Introduction ....................................................................................................................................... 9

1.1. Related documents.................................................................................................................... 9

1.2. Terms and ab brevi ations ......................................................................................................... 10

1.3. Safety cautions ........................................................................................................................ 12

2. Product concept ............................................................................................................................. 15

2.1. Key fe at u re s ............................................................................................................................ 15

2.2. Functional diagram ................................................................................................................. 17

2.3. Evaluation board ..................................................................................................................... 18

3. Application interface ...................................................................................................................... 19

3.1. Pin of module .......................................................................................................................... 20

3.1.1. Pin assignment .............................................................................................................. 20

3.1.2. Pin description .............................................................................................................. 22

3.2. O pe r ating mo de s ..................................................................................................................... 29

3.3. Power supply........................................................................................................................... 30

3.3.1. Pow e r features of module ............................................................................................ 30

3.3.2. Decrease supply voltage drop ...................................................................................... 30

3.3.3. Reference design for power supply ............................................................................. 31

3.3.4. Monitor power supply .................................................................................................. 32

3.4. Power on and down scena rios ................................................................................................ 32

3.4.1. Pow e r on ....................................................................................................................... 32

3.4.2. Pow e r dow n .................................................................................................................. 34

3.4.3. Restart ........................................................................................................................... 36

3.5. Charge interface ...................................................................................................................... 38

3.6. Power saving ........................................................................................................................... 38

3.6.1. Minimum functionality mode ...................................................................................... 38

3.6.2. SLEEP mode................................................................................................................. 39

3.6.3. Wake up module f ro m S LEE P mode .......................................................................... 39

.7. Summary of state transition ................................................................................................... 39

3

3.8. RTC backup............................................................................................................................. 40

3.9. Serial in terfaces ...................................................................................................................... 41

3.9.1. UART Port .................................................................................................................... 42

3.9.2. Debug Port .................................................................................................................... 46

3.9.3. Auxiliary UART Port ................................................................................................... 46

3.9.4. UART application ........................................................................................................ 47

3.10. Audio interfaces .................................................................................................................... 50

3.10. 1. De c rease TD D noise and ot her noise ........................................................................ 51

3.10.2. Microphone interfaces design.................................................................................... 51

M50_HD_V2.0 - 3 -

M50Hardware Design

Quecctel

Confidential

3.10. 3. Receiver and s peaker int erface de sign ...................................................................... 52

3.10.4. Earphone interface design.......................................................................................... 54

3.10. 5. L ou d speake r interf ace de sign ................................................................................... 54

3.10. 6. Audio ch a r a cteristics .................................................................................................. 55

3.11. SIM card interface ................................................................................................................ 55

3.11.1. S I M car d a ppl icati o n .................................................................................................. 55

3.11. 2. 6 Pin SIM cassette ...................................................................................................... 57

3.11. 3. 8 Pi n SIM c asse tt e ...................................................................................................... 58

3.12. SD card interface .................................................................................................................. 60

3.13. PCM interface ....................................................................................................................... 62

3.13. 1. C on figuration .............................................................................................................. 62

3.13.2. Timing ......................................................................................................................... 63

3.13. 3. Refere n ce de sign ........................................................................................................ 64

3.13. 4. AT co m ma n d .............................................................................................................. 64

3.14. ADC ....................................................................................................................................... 66

3.15. Behaviors of the RI............................................................................................................... 66

3.16. Network status indication..................................................................................................... 69

3.17. Operating status indication .................................................................................................. 69

4. Antenna interface........................................................................................................................... 71

4.1. RF reference design ................................................................................................................ 71

4.2. RF output power ..................................................................................................................... 72

4.3. RF receiving sensitivity.......................................................................................................... 72

4.4. O pe r ating fre quencie s............................................................................................................. 72

4.5. RF cable soldering .................................................................................................................. 73

5. Electrical, reliability and radio characteristics ......................................................................... 74

5.1. Absolute maximum ratings .................................................................................................... 74

5.2. Operating temperature ............................................................................................................ 74

5.3. Power supply ratings .............................................................................................................. 75

5.4. Current consumption .............................................................................................................. 76

5.5. Electro-static discharge .......................................................................................................... 78

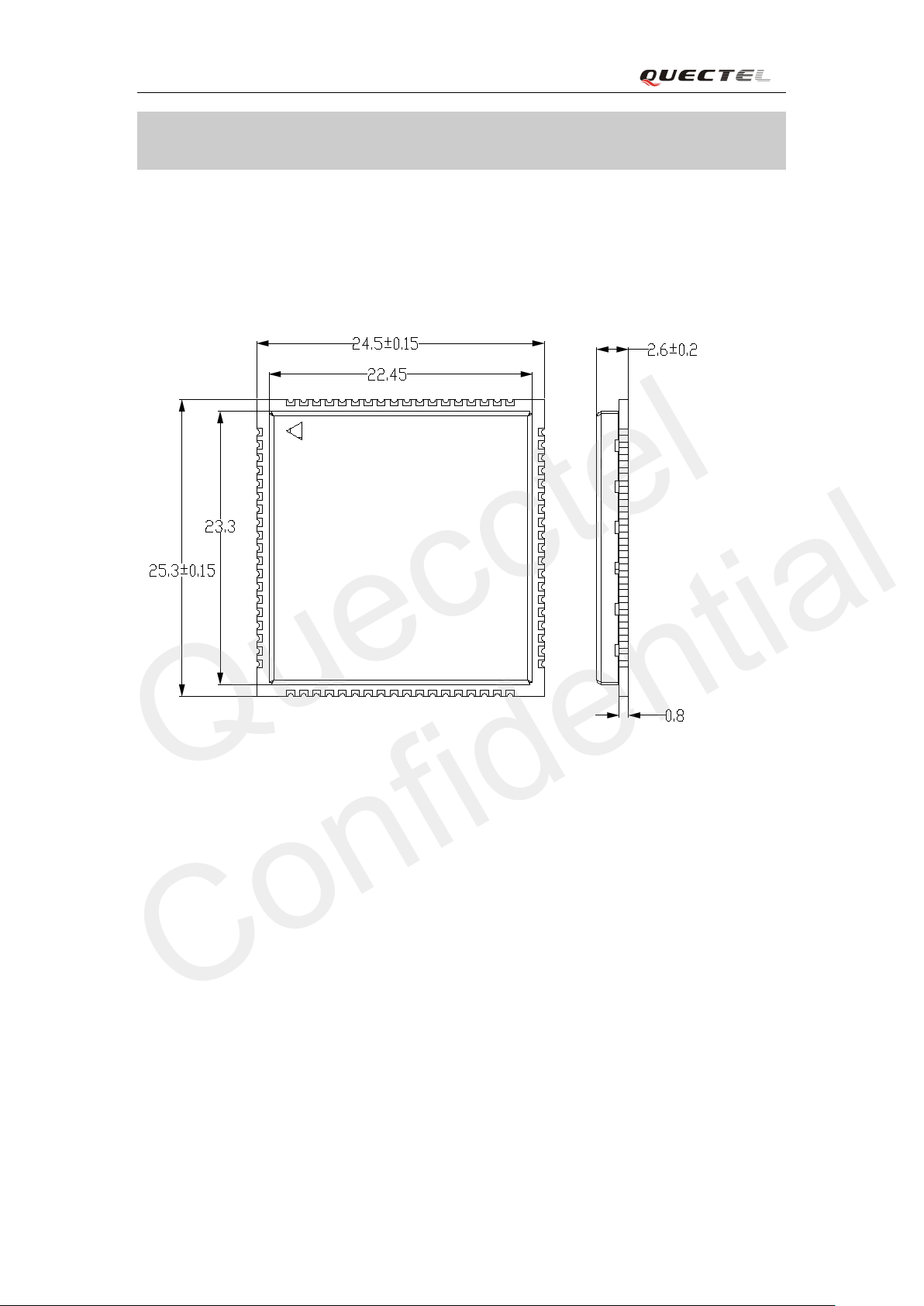

6. Mechanical dimensions ................................................................................................................ 79

.1. Mechanical dimensions of module ........................................................................................ 79

6

6.2. Re c o mmende d f ootprint with o ut bottom centre p a ds .......................................................... 81

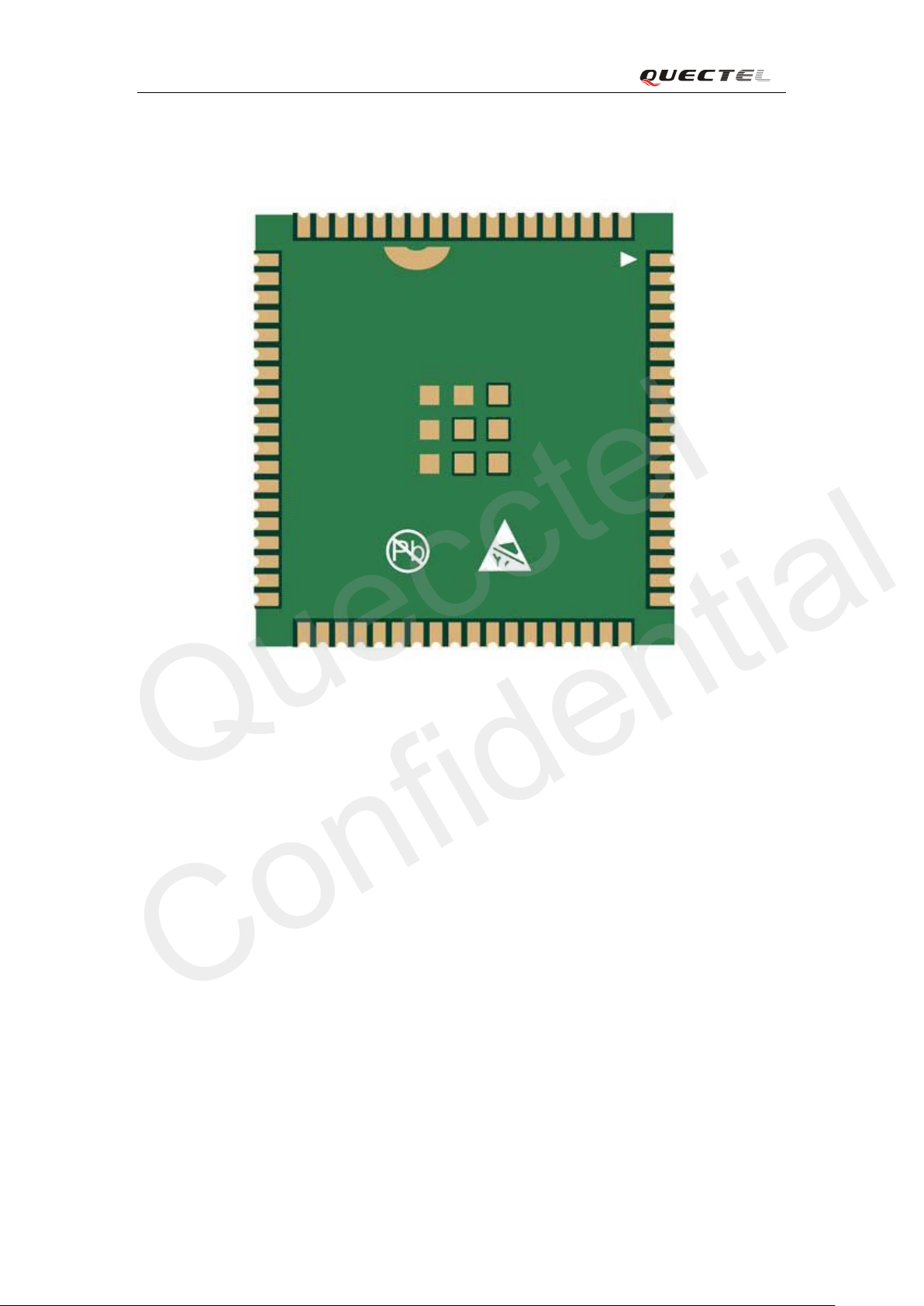

6.4. Top view of the module ......................................................................................................... 82

6.5. Bottom view of the module.................................................................................................... 83

7. Storage and manufacturing ......................................................................................................... 84

7.1. Storage ..................................................................................................................................... 84

7.2. Soldering ................................................................................................................................. 85

7.3. Packaging ................................................................................................................................ 86

Appendix A: GPRS coding schemes ............................................................................................. 87

Appendix B: GPRS multi-slot classes............................................................................................ 88

M50_HD_V2.0 - 4 -

M50Hardware Design

Quecctel

Confidential

Table Index

TABLE 1: RELATED DOCUMENTS ..................................................................................................... 9

TABLE 2: TERMS AND ABBREVIATIONS........................................................................................ 10

TABLE 3: MODULE KEY FEATURES ................................................................................................ 15

TABLE 4: CODING SCHEMES AND MAXIMUM NET DATA RATES OVER AIR INTERFACE .. 17

TABLE 5: M50 PIN ASSIGNMENT ..................................................................................................... 21

TABLE 6: PIN DESCRIPTION ............................................................................................................. 22

TABLE 7: OVERVIEW OF OPERATING MODES.............................................................................. 29

TABLE 8: PIN DEFINITION OF THE CHARGING ............................................................................ 38

TABLE 9: SUMMARY OF STATE TRANSITION ............................................................................... 39

TABLE 10: LOGIC LEVELS OF THE UART INTERFACES.............................................................. 42

TABLE 11: PIN DEFINITION OF THE UART IN TERFACES ............................................................ 42

TABLE 12: PIN DEFINITION OF AUDIO INTERFACES .................................................................. 50

TABLE 13: AOUT3 OUTPUT CHARACTERISTICS .......................................................................... 51

TABLE 14: TYPICAL ELECTRET MICROPHONE CHARACTERISTICS ....................................... 55

TABLE 15: TYPICAL SPEAKER CHARACTERISTICS .................................................................... 55

TABLE 16: PIN DEFINITION OF THE SIM INTERFACE ................................................................. 56

TABLE 17: PIN DESCRIPTION OF AMPHENOL SIM CARD HOLDER ......................................... 58

TABLE 18: PIN DESCRIPTION OF MOLEX SIM CARD HOLDER ................................................. 59

TABLE 19: PIN DEFINITION OF THE SD CARD INTERFACE ....................................................... 60

TABLE 20: PIN NAME OF THE SD CARD AND MICRO SD CARD ............................................... 61

TABLE 21: PIN DEFINITION OF PCM INTERFACE......................................................................... 62

TABLE 22: CONFIGURATION ............................................................................................................ 62

TABLE 23: QPCMON COMMAND DESCRIPTION .......................................................................... 65

TABLE 24: QPCMVOL COMMAND DESCRIPTION ........................................................................ 65

TABLE 25: PIN DEFINITION OF THE ADC....................................................................................... 66

TABLE 26: CHARACTERISTICS OF THE ADC ................................................................................ 66

TABLE 27: BEHAVIORS OF THE RI .................................................................................................. 66

TABLE 28: WORKING STATE OF THE NETLIGHT ......................................................................... 69

TABLE 29: PIN DEFINITION OF THE STATUS................................................................................. 69

TABLE 30: PIN DEFINITION OF THE RF_ANT ................................................................................ 71

TABLE 31: THE MODULE CONDUCTED RF OUTPUT POWER .................................................... 72

TABLE 32: THE MODULE CONDUCTED RF RECEIVING SENSITIVITY .................................... 72

TABLE 33: THE MODULE OPERATING FREQUENCIES ................................................................ 72

TABLE 34: ABSOLUTE MAXIMUM RATINGS................................................................................. 74

TABLE 35: OPERATING TEMPERATURE ......................................................................................... 74

TABLE 36: THE MODULE POWER SUPPLY RATINGS ................................................................... 75

TABLE 37: THE MODULE CURRENT CONSUMPTION .................................................................. 76

TABLE 38: THE ESD ENDURANCE (TEMPERATURE:25℃,HUMIDITY:45 %)............................ 78

TABLE 39: DESCRIPTION OF DIFFERENT CODING SCHEMES .................................................. 87

TABLE 40: GPRS MULTI-SLOT CLASSES ........................................................................................ 88

M50_HD_V2.0 - 5 -

M50Hardware Design

Quecctel

Confidential

Figure Index

FIGURE 1: MODULE FUNCTIONAL DIAGRAM ............................................................................. 18

FIGURE 2: PIN ASSIGNMENT ............................................................................................................ 20

FIGURE 3: VOLTAGE RIPPLE DURING TRANSMITTING ............................................................. 30

FIGURE 4: REFERENCE CIRCUIT FOR THE VBAT INPUT ............................................................ 31

FIGURE 5: REFERENCE CIRCUIT FOR POWER SUPPLY .............................................................. 31

FIGURE 6: TURN ON THE MODULE USING DRIVING CIRCUIT................................................. 32

FIGURE 7: TURN ON THE MODULE USIN G KE Y STROKE ........................................................... 33

FIGURE 8: TIMING OF TURNING ON SYSTEM .............................................................................. 33

FIGURE 9: TIMING OF TURNING OFF THE MODULE................................................................... 34

FIGURE 10: REFERENCE CIRCUIT FOR EMERG_OFF BY USING DRIVING CIRCUIT ............ 36

FIGURE 11: REFERENCE CIRCUIT FOR EMERG_OFF BY USING BUTTON .............................. 36

FIGURE 12: TIMING OF RESTARTING SYSTEM ............................................................................ 37

FIGURE 13: TIMING OF RESTAR TING SYSTEM AFTER EMERGENCY SHUTDOWN .............. 37

FIGURE 14: RTC SUPPLY FROM NON-CHARGEABLE BATTERY ............................................... 40

FIGURE 15: RTC SUPPLY FROM RECHARGEABLE BATTERY .................................................... 40

FIGURE 16: RTC SUPPLY FROM CAPACITOR ................................................................................ 40

FIGURE 17: SEIKO XH414H-IV01E CHARGE CHARACTERISTICS ............................................. 41

FIGURE 18: REFERENCE DESIGN FOR FULL-FUNCTION UART ................................................ 44

FIGURE 19: REFERENCE DESIGN FOR UART PORT ..................................................................... 44

FIGURE 20: REFERENCE DESIGN FOR UART PORT WITH HARDWARE FLOW CONTROL... 45

FIGURE 21: REFERENCE DESIGN FOR FIRMWARE UPGRADE .................................................. 45

FIGURE 22: REFERENCE DESIGN FOR DEBUG PORT .................................................................. 46

FIGURE 23: REFERENCE DESIG N FOR AUXILIAR Y UART PORT ............................................... 47

FIGURE 24: LEVEL MATCH DESIGN FOR 3.3V SYSTEM.............................................................. 47

FIGURE 25: LEVEL MATCH DESIGN FOR 5V SYSTEM................................................................. 48

FIGURE 26: LEVEL MATCH DESIGN FOR RS-232 .......................................................................... 49

FIGURE 27: REFERENCE DESIG N FOR AIN1&AIN2...................................................................... 52

FIGURE 28: REFERENCE DESIG N FOR AOUT1 .............................................................................. 52

FIGURE 29: HANDSET INTERFACE DESIGN FOR AOUT2 ........................................................... 53

FIGURE 30: SPEAKER INTERF A CE DESIGN WITH AN AMPLIFIER F OR AOUT2 ..................... 53

FIGURE 31: EARPHONE INTERFACE DESIGN ............................................................................... 54

FIGURE 32: LOUD SPEAKER INTERFACE DESIGN ....................................................................... 54

FIGURE 33: REFERENCE CIRCUIT OF THE 8 PINS SIM CARD .................................................... 56

FIGURE 34: REFERENCE CIRCUIT OF THE 6 PINS SIM CARD .................................................... 57

FIGURE 35: AMPHENOL C707 10M006 512 2 SIM CARD HOLDER .............................................. 58

FIGURE 36: MOLEX 91228 SIM CARD HOLDER ............................................................................ 59

FIGURE 37: REFERENCE CIRCUIT OF SD CARD ........................................................................... 60

FIGURE 38: LONG SYNCHRONIZATION & SIGN EXTENSION DIAGRAM ............................... 63

FIGURE 39: LONG SYNCHRONIZATION & ZERO PADDING DIAGRAM ................................... 63

FIGURE 40: SHORT SYNCHRONIZATION & SIGN EXTENSION DIAGRAM .............................. 63

FIGURE 41: SHORT SYNCHRONIZATION & ZERO PADDING DIAGRAM ................................. 64

M50_HD_V2.0 - 6 -

M50Hardware Design

Quecctel

Confidential

FIGURE 42: REFERENCE DESIGN FOR PCM .................................................................................. 64

FIGURE 43: RI BEHAVIOR OF VOICE CALLING A S A RECEIVER .............................................. 67

FIGURE 44: RI BEHAVIOR OF DATA CALLING AS A RECEIVER ................................................ 67

FIGURE 45: RI BEHAVIOR AS A CALLER ........................................................................................ 67

FIGURE 46: RI BEHAVIOR OF URC OR SMS RECEIVED .............................................................. 68

FIGURE 47: REFERENCE DESIGN FOR NETLIGHT ....................................................................... 69

FIGURE 48: REFERENCE DESIGN FOR STATUS ............................................................................ 70

FIGURE 49: REFERENCE DESIGN FOR RF ...................................................................................... 71

FIGURE 50: RF SOLDERING SAMPLE.............................................................................................. 73

FIGURE 51: M50 TOP A ND SIDE DIMENSIONS .............................................................................. 79

FIGURE 52: M50 BOTTOM DIMENSIONS ........................................................................................ 80

FIGURE 53: RECOMMENDED FOOTPRINT WITHOUT BOTTOM CENTRE PADS .................... 81

FIGURE 55: TOP VIEW OF THE MODULE ....................................................................................... 82

FIGURE 56: BOTTOM VIEW OF THE MODULE .............................................................................. 83

FIGURE 57: PASTE A PPLICATION .................................................................................................... 85

FIGURE 58: RAMP-SOAK-SPIKE REFLOW PROFILE .................................................................... 86

FIGURE 59: MODULE TRAY .............................................................................................................. 86

FIGURE 60: RADIO BLOCK STRUCTURE OF CS-1, CS-2 AND CS-3 ........................................... 87

FIGURE 61: RADIO BLOCK STRUCTURE OF CS-4 ........................................................................ 87

M50_HD_V2.0 - 7 -

M50Hardware Design

Quecctel

Confidential

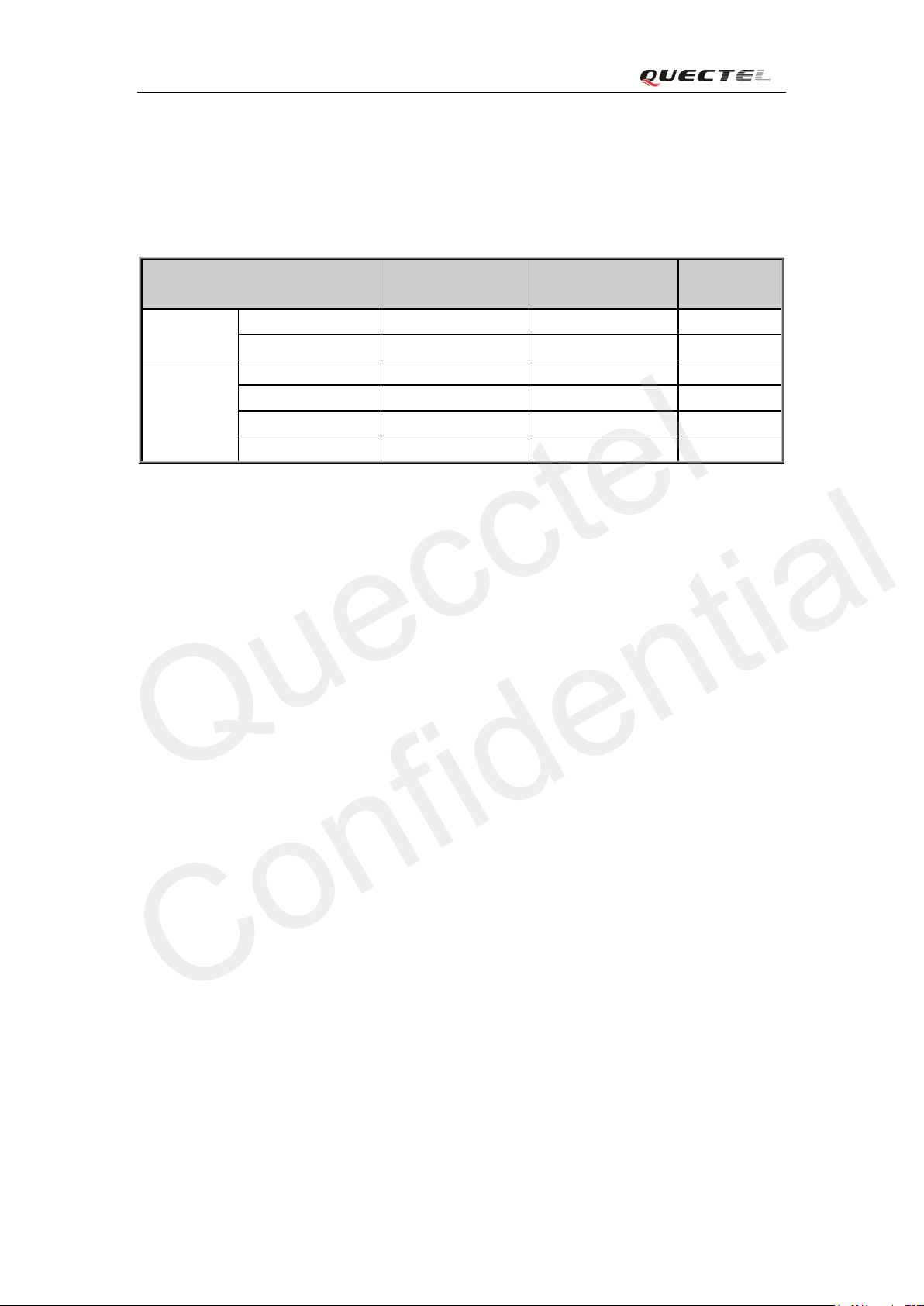

0. Revision history

Revision Date Author Description of change

1.0 2011-12-20 Ray XU Initial

1.1 2012-02-03 Ray XU 1. Updated PCM interface

2. Updated SD interface

3. Updated charging interface

4. Updated timing of turn ing on the module

1.2 2012-07-20 Bal y BAO 1. Deleted the USB interface

2. Deleted the camera interface

1.3 2012-10-22 Mountain Z H OU 1. Updated functional diagram

2. Update d re fe rence des ign cir c uit

3. Update d a udio char a cteris tics

4. Updated VRTC DC characteristics

5. Updated SLEEP current consumption

6. Update d i nternet se r vice protocol s

7. Updated SIM pins’ name

8. Modified PCM function

9. Deleted F AX function

2.0 2012-06-16 Ray XU 1. Update the m odule si ze

2. Update the pin layout

M50_HD_V2.0 - 8 -

M50 Hardware Design

Draft new

Digital cellular telecommunications (Phase 2+); AT

Data Circuit

DCE) interface for

Short Message Service (SMS) and Cell Broadcast

hase 2+);

Digital cellular telecommunications (Phase 2+);

Digital cellular telecommunications (Phase 2+);

Quecctel

Confidential

1. Introduction

This do cument defines the M50 module and describes the hardware interface of M50 which are

connected with the customer application and the air interface.

This do cument can help customers quickl y unders tan d module interface specifications, electrical

and mechanical details. Associated with application notes and user guide, customers can use

M50module to design and set up mobile applications easily.

1.1. Related document s

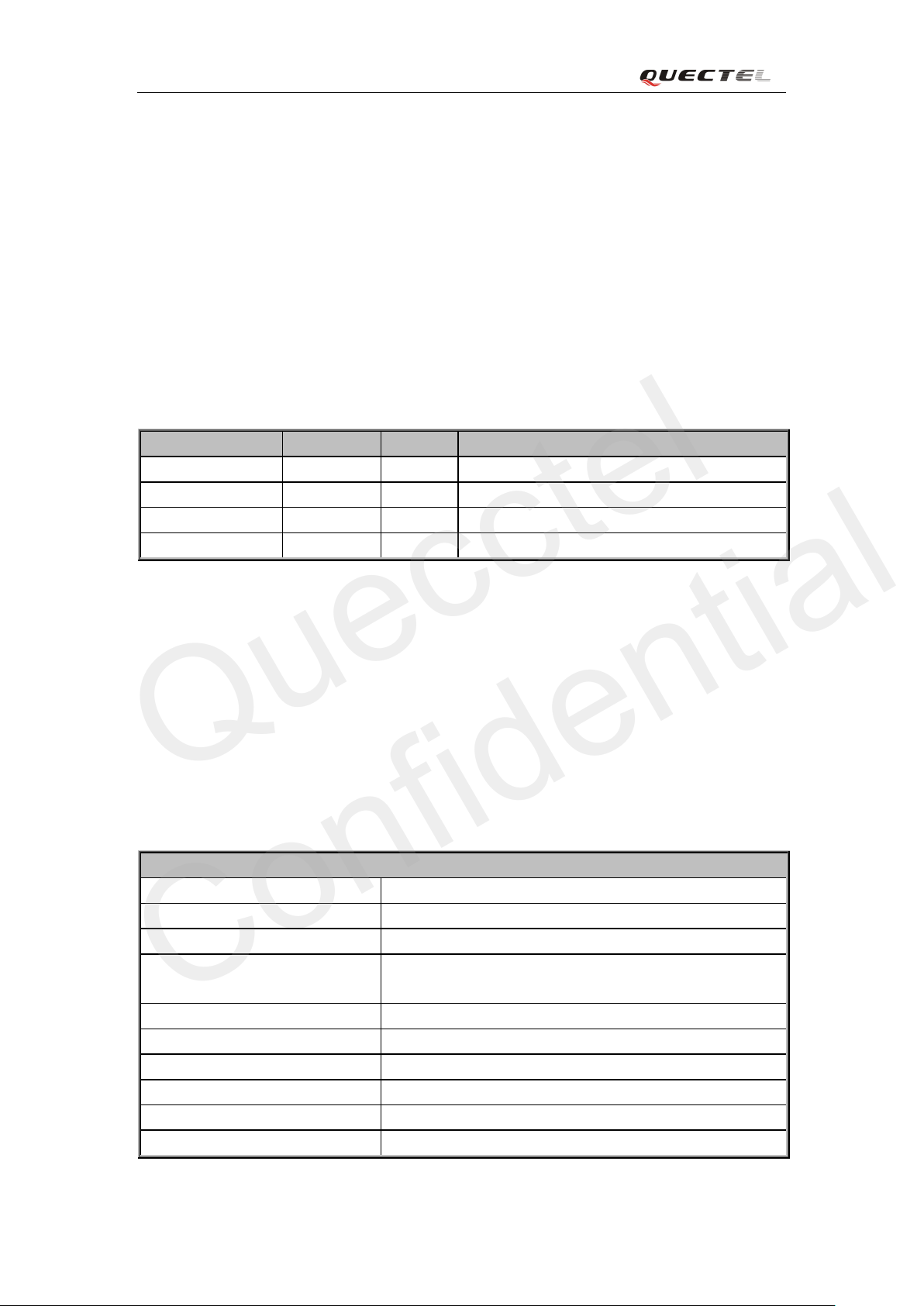

Table 1: Related documents

SN Document name Remark

[1] M50_ ATC AT commands set

[2] ITU-T

rec omme nda ti on V.25t er

[3] GSM 07.07

[4] GSM 07.10 Supp ort GSM 07 .1 0 multipl exing proto co l

[5] GSM 07.05 Digital cellular telecommunications (Phase 2+); Use

[6] GSM 11.1 4 Digital cellular telecommunications (P

[7] GSM 11.11

[8] GSM 03.38

[9] GSM 11.10 Digital cellular teleco mmuni cations (P h ase 2); Mobile

[10] GSM_UART_AN UART port application note

[11] GSM_FW_Upgrade_AN01 GSM Firm w a re upgrade appl icatio n not e

[12] M10_EVB_UGD

Serial asynchronous automatic dialing and control

command set for GSM Mobile Equipment (ME)

of Data Terminal Equipment –

terminating Equipment (DTE –

Service (CBS)

Specification of the SIM Application Toolkit for the

Subscriber Identity module – Mobile Equipment (SIM

– ME) interfa ce

Specification of the Subscriber Identity module –

Mobile Equipment (SIM – ME) interface

Alphabets and language-specific information

Station (MS) conformance specification; Part 1:

Conformance specificat ion

M10 EVB user gui d

e

M50_HD_V2.0 - 9 -

M50 Hardware Design

Quecctel

Confidential

1.2. T erm s and abbreviations

Table 2: Te rms and abb reviati o ns

Abbreviation Description

ADC Analog-to-Digital Converter

AMR Adaptive Multi-Rate

ARP Antenna Reference Point

ASIC Application Specific Integrated Circuit

BER Bit Error Rate

BOM Bill Of Material

BTS Base Transceiver Station

CHAP Challenge Handshake Authentication Protocol

CS Coding Scheme

CSD Circuit Switched Data

CTS Clear To Send

DAC Digital-to-An alo g Co nverter

DRX Discontinuous Reception

DSP Digital Signal Processor

DCE Data Communications Equipment (typically module)

DTE Data Terminal Equipment (typically computer, external co ntroller)

DTR Data Terminal Ready

DTX Discontinuous Transmission

EFR Enhanced Full Rate

EGSM Enha nced GSM

EMC Electromagnetic Comp atibilit y

ESD Electrostatic Discharge

ETS European Telecomm unica tion Sta nda rd

FCC Federal Communications Commission (U.S.)

FDMA Frequency Division Multiple Access

FR Full R ate

GMSK Gaussian Minimum Shift Keying

GPRS G enera l Packet Radio Service

GSM Global System for Mobile Communications

HR Half R at e

I/O Input/Output

IC Integrate d Circuit

IMEI International Mobile Equipment Identity

Imax Maximum Load Current

Inorm Normal Current

kbps Kilo Bits Per Second

LED Light Emitting Diode

M50_HD_V2.0 - 10 -

M50 Hardware Design

Quecctel

Confidential

Li-Ion Lithium-Ion

MO Mobile Ori ginated

MS Mobile Station (GSM engine)

MT Mobile Terminated

PAP Password Authentication Protocol

PBCCH Packet Switched Broadcast Control Channel

PCB Printe d Circuit B oard

PDU Protocol Data Unit

PPP Point-to-Point Protocol

RF Radio Frequency

RMS Root Mean Square (value)

RTC Real Time Clock

RX Receive Direction

SIM Subscriber Identification Module

SMS Short Message Service

TDMA Time Division Multiple Access

TE Terminal Equipment

TX Transmitting Direction

UART Unive rs al Asyn c hr o no us Receiver & Transmitter

URC Unsolicited Result Code

USSD Unstructured Supplementary Service Data

VSWR Voltage Standing Wave Ratio

Vmax Maximum Voltage Value

Vnorm Normal Voltage Value

Vmin Minimum Voltage Value

VIHmax Maximum Input High Level Voltage Value

VIHmin Minimum Input High Level Voltage Value

VILmax Maximum Input Low Level Voltage Value

VILmin Minimum Input Low Level Voltage Value

VImax Absolute Maximum Input Voltage Value

VImin Absolute Minimum Input Voltage Value

VOHmax Maximum Output Hi gh Level Voltage Value

VOHmin Minimum Outp ut High Leve l Volta ge V al ue

VOLmax M ax i m u m Ou tput Low Leve l Volta ge V al ue

VOLmin Minim um Outp ut L ow Level Vol t a ge Value

Phonebook abbreviations

LD SIM Last Dialing phoneb oo k (l ist of num bers m ost recent ly dialed)

MC Mobile Equipment list of unanswered MT Calls (missed calls)

ON SIM (or ME) Own Numbers (MSISDNs) list

RC Mob ile Equipment list of Received Calls

SM SIM phonebook

M50_HD_V2.0 - 11 -

M50 Hardware Design

station, fuel

safety haza r d.

Quecctel

Confidential

1.3. Safety cautions

The following safety precauti ons must be observed during all phases of the operation, such as

usage, service or repair of any cellular terminal or mobile incorporating M50module.

Manufacturers of t he cell ula r termi nal sho uld se nd the follo wing sa fety i nform ation t o use rs and

operating personnel and to incorpo rat e the se gui de li nes int o al l manual s supplied with the pr o du ct.

If not so, Quectel does not take on any liability for customer failure to comply with these

precautions.

When i n a hos pit al or ot her healt h c are f acili ty, obse rve the rest ricti ons about the

use of mo bi l e. Switch the cellular terminal or mobile off. Medical equipment may

be sensitive to not operate n o rm ally for RF energy interference.

Switch off the cell ul ar te rmin al or mobi le bef ore boa rdin g an air craft . Make sure

it switched off. The ope ratio n o f wirel ess appli a n ces i n an ai r c raft is f or bidde n to

preve nt inte rfere nce wit h commu nic atio n syst e ms. Forget to think much of these

inst ruct ions ma y l ead to the flight safety or offend against local legal action, or

both.

Do not ope r ate t he cell ul ar te rmi nal or mobil e i n t he pre se nce o f fl amm able gas

or fume. Switch off the cellul ar t ermin al when you a re near pet rol

depot, chemical plant o r where bl astin g operat ions are i n progre ss. Ope ratio n of

any electrical equipment in potentially explosive atmosphere can constitute a

Your cellular terminal or mobile receives and transmits radio frequency energy

while swi t ched o n. RF i nte rfe re n ce can oc cur i f i t is use d clo se t o TV set, radio,

comput er or other electric equipment.

Road s afe ty co mes first! Do no t us e a hand-held cellular terminal or mobile while

driving a vehicle, unless it is securely mounted in a holder for hands-free

operation. Before making a call with a hand-held terminal or mobile, park the

vehicle.

M50_HD_V2.0 - 12 -

M50 Hardware Design

Quecctel

Confidential

GSM cellular terminals or mobiles operate over radio frequency signal and

According to the R&TTE Directive 1999/95/CE, all wireless equipment and

telecommuni cations terminals sold in EU must meet all the stipulated he alth,

safety RF, EMC requirements th at pro vi de fo r CE m ar k. Que cte l M odul e M50

is fully in ac co r da n ce with all the di rective s of EU.

cellular network and cannot be guaranteed to connect in all conditions, for

exam ple no mobil e fee o r an inv ali d SI M card. Whi le you are in t his condition

and need emergent help, Please Remember using emergency call. In order to

make or receive call, the cellul ar termina l or mobile must be swit che d on and in

a servi ce area with a d e quat e cel lular sign al strength.

Some net works d o not allo w for e merge ncy c all if certai n net work se rvice s or

phone feat ures are in use ( e .g. lock fu n cti o ns, fixed diali n g et c . ) . You m a y have

to deactivate t h ose features bef ore you c an ma ke an eme r ge n c y c all .

Also, some networks require that a valid SIM card be properly inserted in

cellular terminal or mobile.

1.4. Directives and standard s

The M50 module is designed to comply with the FCC statements. FCC ID: XMR201211M50.

The Host system using M50, should have label indicated contains FCC ID: XMR201211M50.

1.4.1. FCC Statemen t

1. This devi ce complies with Part 15 o f the FCC rules. Oper ation is subje ct to the following

conditions:

a) Thi s device ma y not c aus e harmful interference.

b) This device must accept any interference received, including interference that may cause

undesired operation.

2. Changes or modi fications not expressl y approved by the party responsible for compliance

coul d void the user ’s authority to operate the equipment.

1.4.2. FCC Radiation exposure statement

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled

environment. This equipment should be installed and operated with minimum distance 20cm

between the radiator and your body as well as kept minimum 20cm from radio antenna depending

on the Mobile status of this module usage.

M50_HD_V2.0 - 13 -

M50 Hardware Design

Quecctel

Confidential

The m a nu al of t he host syste m, whi ch uses M50, must include RF exposure warning statement to

advi ce use r shoul d keep mi nim um 20c m fr om the r adi o ante n n a o f M 50 m od ul e depe nding on the

Mobile status.

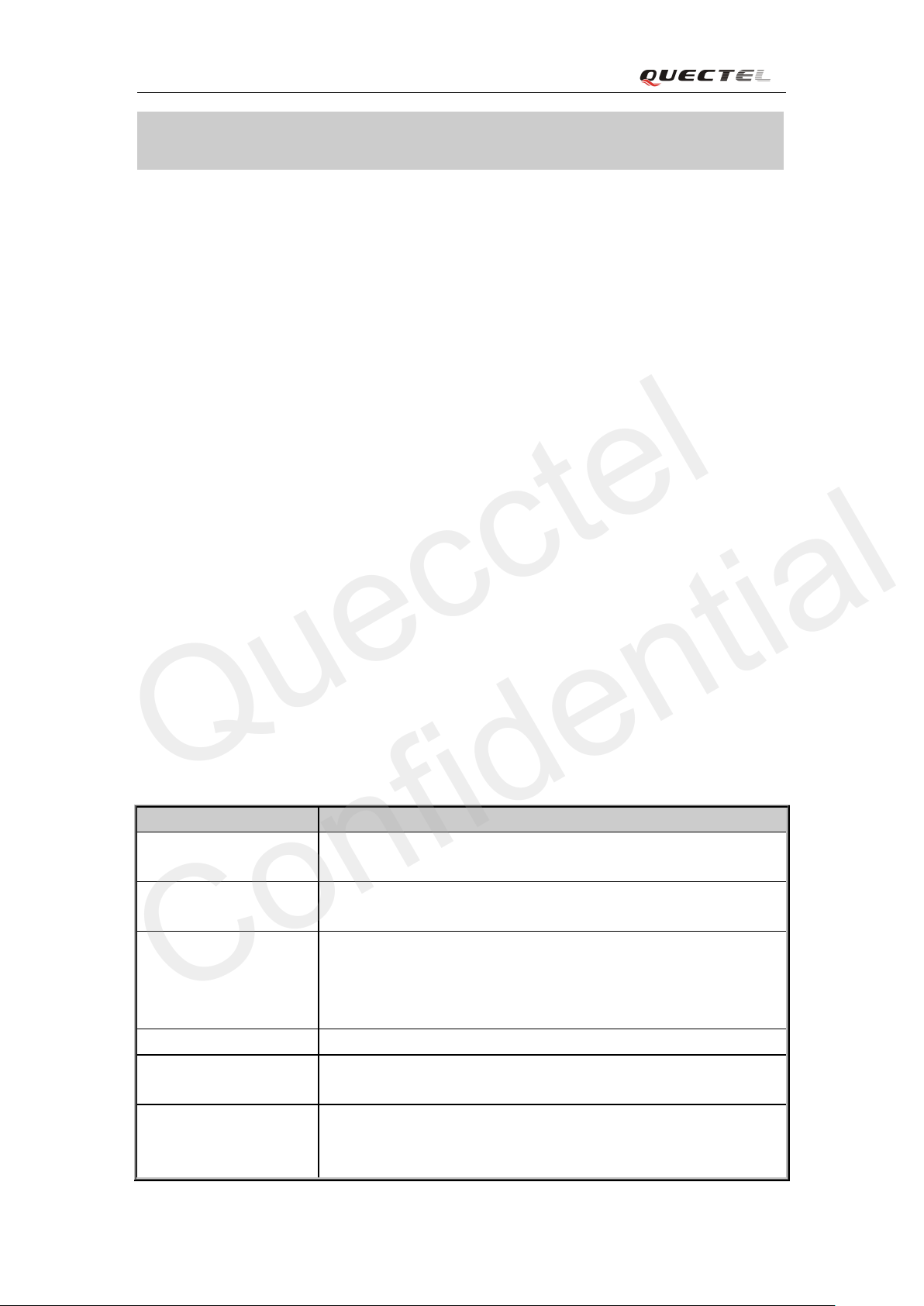

The following list of antenna is indicating the maximum permissible antenna gain.

Type Maxim u m Gain

(850Hz/900Hz)

External

Antenna

Internal

Antenna

This radio module must not be installed to co-locate and operate simu

ltaneously with other radios in host system;

additional testing and equipment authorization may be required to op

erating simultaneously with other radios.

Monopole 0.5dBi 2dBi 50Ω

Vehicular antenna 0.5dBi 2dBi 50Ω

Monopole 0.5dBi 2dBi 50Ω

PIFA 0.5dBi 2dBi 50Ω

FPC 0.5dBi 2dBi 50Ω

PCB 0.5dBi 2dBi 50Ω

Maxim u m Gain

(1800Hz/1900Hz)

Impedance

M50_HD_V2.0 - 14 -

M50 Hardware Design

Quecctel

Confidential

2. Product concept

M50 is a Quad-band GSM/GPRS engine that works at frequencies of GSM850MHz,

GSM900MHz, DCS1800MHz and PCS1900MHz. The M50 features GPRS multi-slot class 12

and supports the GPRS coding schemes CS-1, CS-2, CS-3 and CS-4. For more details about

GPRS multi-slot cl as s es a nd co ding sche me s, plea se re fer to the Appendix A an d Appendix B.

With a tin y profile of 24.5mm×25.3mm

for M2M applications, including Vehicles and Personal Tracking, Se c urity S yst em, Wireless POS,

Industrial PDA, Smart Metering, and Remote Maintenance & Control etc.

M50 is an SMD type module with LCC package, which can be embedded in customer’s

applications. It provides abundant hardware inter faces bet ween the module and customer’s hos t

board.

Designed with power s avin g techni que , t he curre nt consumpti on of M50 is as l ow as 1.3 mA i n

SLEEP mode when DRX is 5.

M50 is integra te d with Internet service protocols, su c h as TCP, UD P , F TP and P PP . Exten ded AT

commands h ave been developed for customer to use these Internet service protocols easily.

The module fully complies with the RoHS directive of the European Union.

×2.6mm, the module can meet almost all the requirements

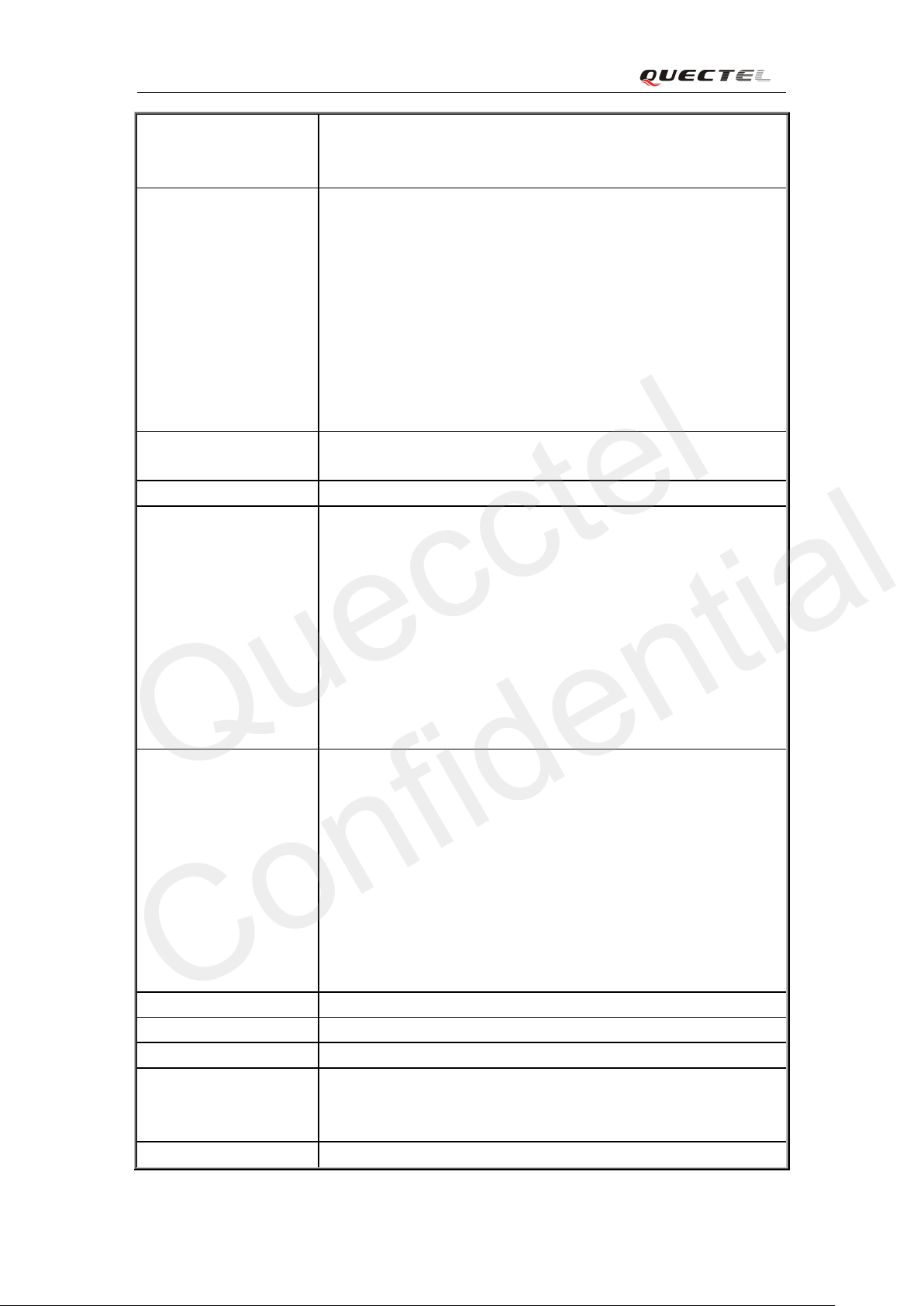

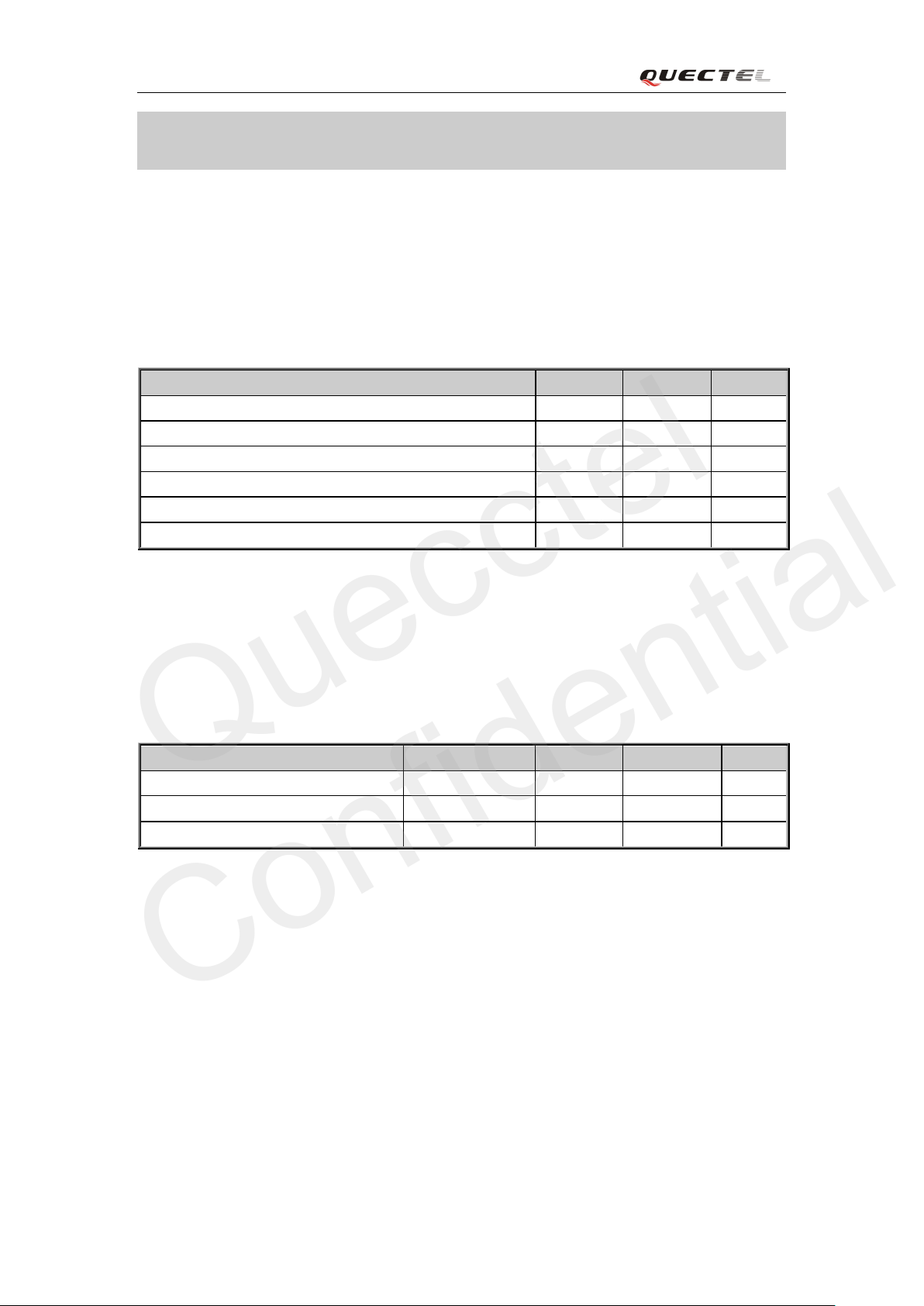

2.1. Key features

Table 3: Module key features

Feature Description

Power supply Single supply voltage 3.3V~ 4.6V

Typical supply voltage 4.0V

Pow er saving Typical p o we r consumpt i on i n SLEEP mode: 1.3 mA@ DRX=5

1.2 mA@ DRX=9

Frequency bands Quad-band: GSM850, GSM900, DCS1800, PCS1900.

The module can se arch these frequency bands automatically

The frequency bands can be set by AT command.

Compliant with GSM Phase 2/2+

GSM class Small MS

Trans mi tt ing po wer Class 4 ( 2W) at GSM850 and GSM900

Cla ss 1 ( 1W) at DCS1800 and PCS1900

GPRS connectivity GPRS multi-sl o t clas s 12 (default)

GPRS multi-slot clas s 1~12 (configurable)

GPRS mobile station class B

M50_HD_V2.0 - 15 -

M50 Hardware Design

Quecctel

Confidential

Te mp er at ure rang e Nor m al o pe r ation: -35°C ~ +80°C

Restricted operation: -40°C ~ -35° C and +80°C ~ +85°C

Storage temperature: -45°C ~ +90°C

DATA GPRS:

CSD:

SMS Text and PDU mode

SIM interface Sup port SIM c ar d: 1.8V, 3V

Audi o features Speech codec modes:

UART interfaces UART Port:

Phonebook ma nagement Support phonebook types: SM, ME, ON, M C, RC, DC, LD, LA

SIM Application Toolkit Support SAT class 3, GSM 11.14 Release 99

Real time clock Supported

Ph ys ical ch aract eri s ti cs Size:

Firmware upgrade Firmware upgrade via UART Port

GP RS data do wnl ink tra ns fer: m ax. 85. 6 kbps

GPRS d at a uplink t r an sfer: ma x. 85.6 kbps

Coding scheme: CS-1, CS-2, CS-3 and CS-4

Support the protocols PAP (Password Authentication Protocol)

usually used for PPP connections

Internet service protocols

TCP/UDP/FTP/PPP/HTTP/NTP/PING

Support Packet Broadcast Control Channel (PBCCH)

CSD tr an s mi s sion rat e s: 2. 4, 4. 8, 9. 6, 14.4 kbp s non-transparent

Support Unstructured Supplementary Service Data (USSD)

SMS storage: SIM card

Half Rate (ETS 06.20)

Full Rate (ETS 06.10)

Enhanced Full Rate (ETS 06.50 / 06.60 / 06.80)

Adaptive Multi-Rate (AMR)

Echo Suppress ion

E cho C ancel latio n

Noi se Re d u ction

Embedded one amplifier o f clas s A B with maximum driving

power up to 800mW

Seven lines on UART port interface

Used for AT command, G P R S dat a a n d CSD d ata

Multiplexing function

Sup port aut obaudi n g f ro m 4800 bps to 11520 0 bp s

Debug Port:

Two lines on debug port interface DBG_TXD and DBG_RXD

De bu g P o rt only use d fo r firmware deb ugging

Auxiliary Port:

Used for AT command

24.5 (±0.15) × 25.3 (±0.15) × 2.6 (±0.2) mm

Weight: 3.3g

1)

M50_HD_V2.0 - 16 -

M50 Hardware Design

Quecctel

Confidential

Antenna interface Connected to antenna pad with 50 Ohm impedance control

1)When the module works in this temperature range, the deviations from the GSM specification

may occur. For example, the frequency error or the phase error will be increased.

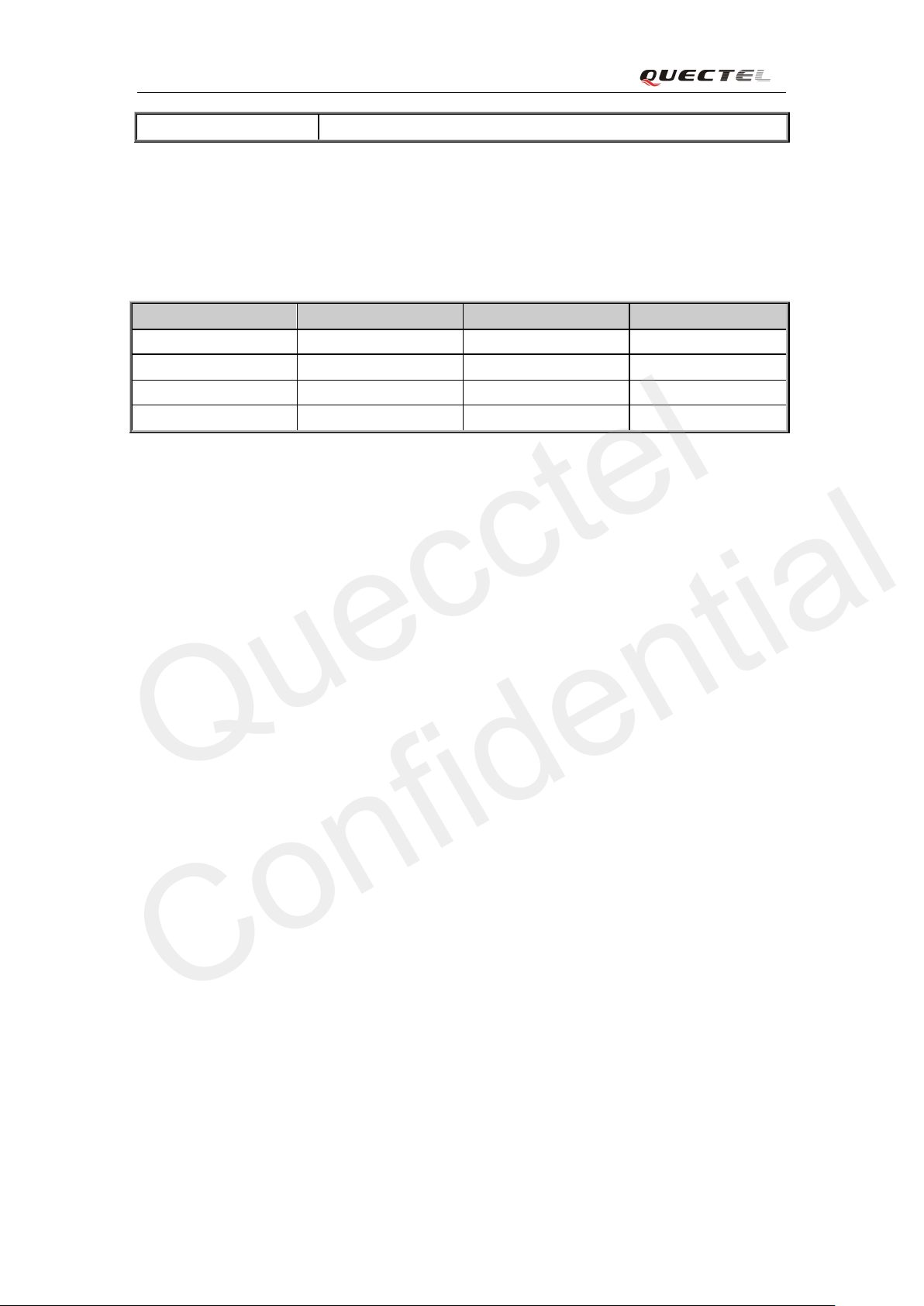

Table 4: Coding schemes and maximum net data rates over air interface

Coding scheme 1 Timeslot 2 Time slot 4 Times l ot

CS-1 9.05kbps 18.1kbps 36.2kbps

CS-2 13.4kbps 26.8kbps 53.6kbps

CS-3 15.6kbps 31.2kbps 62.4kbps

CS-4 21.4kbps 42.8kbps 85.6kbps

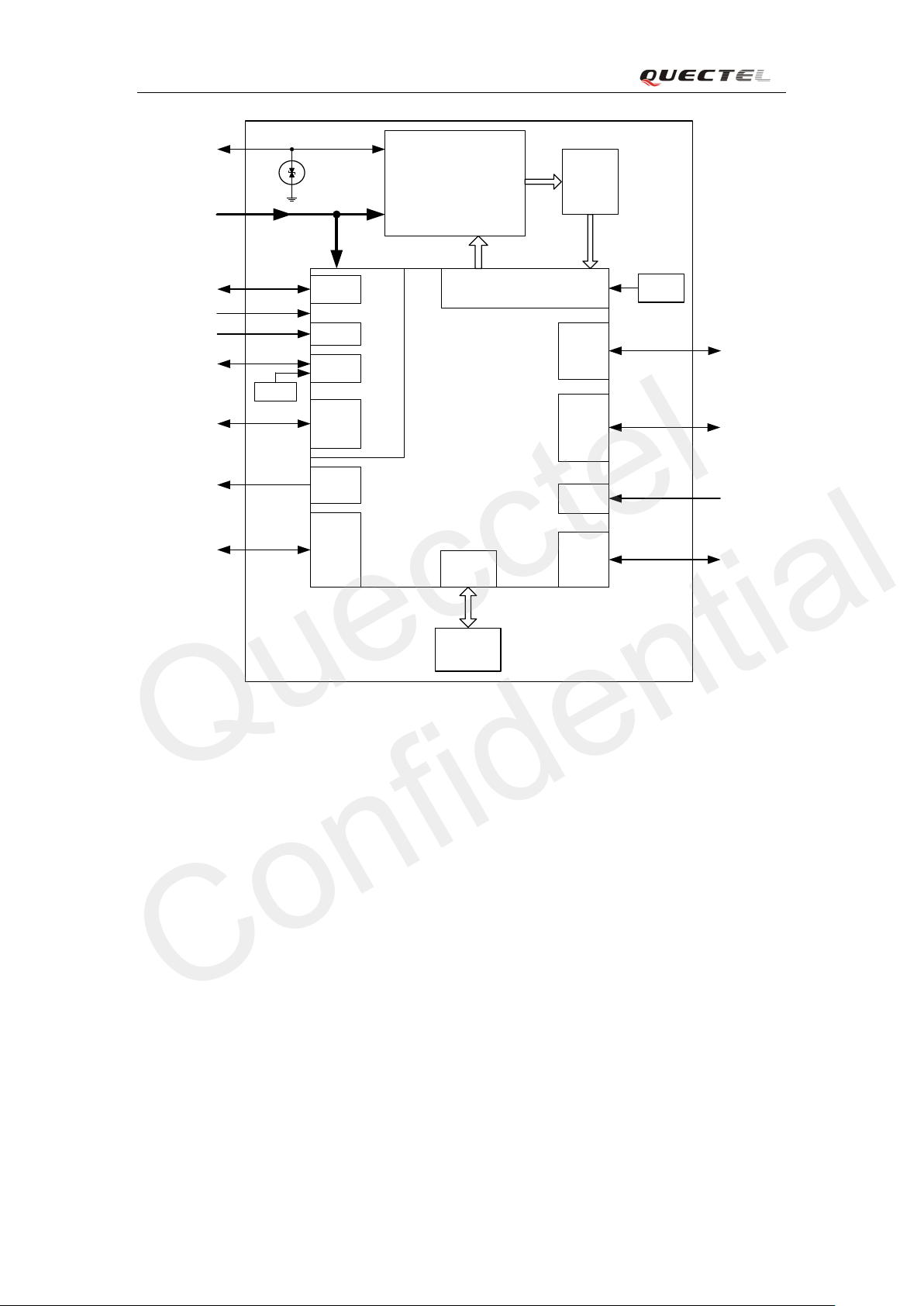

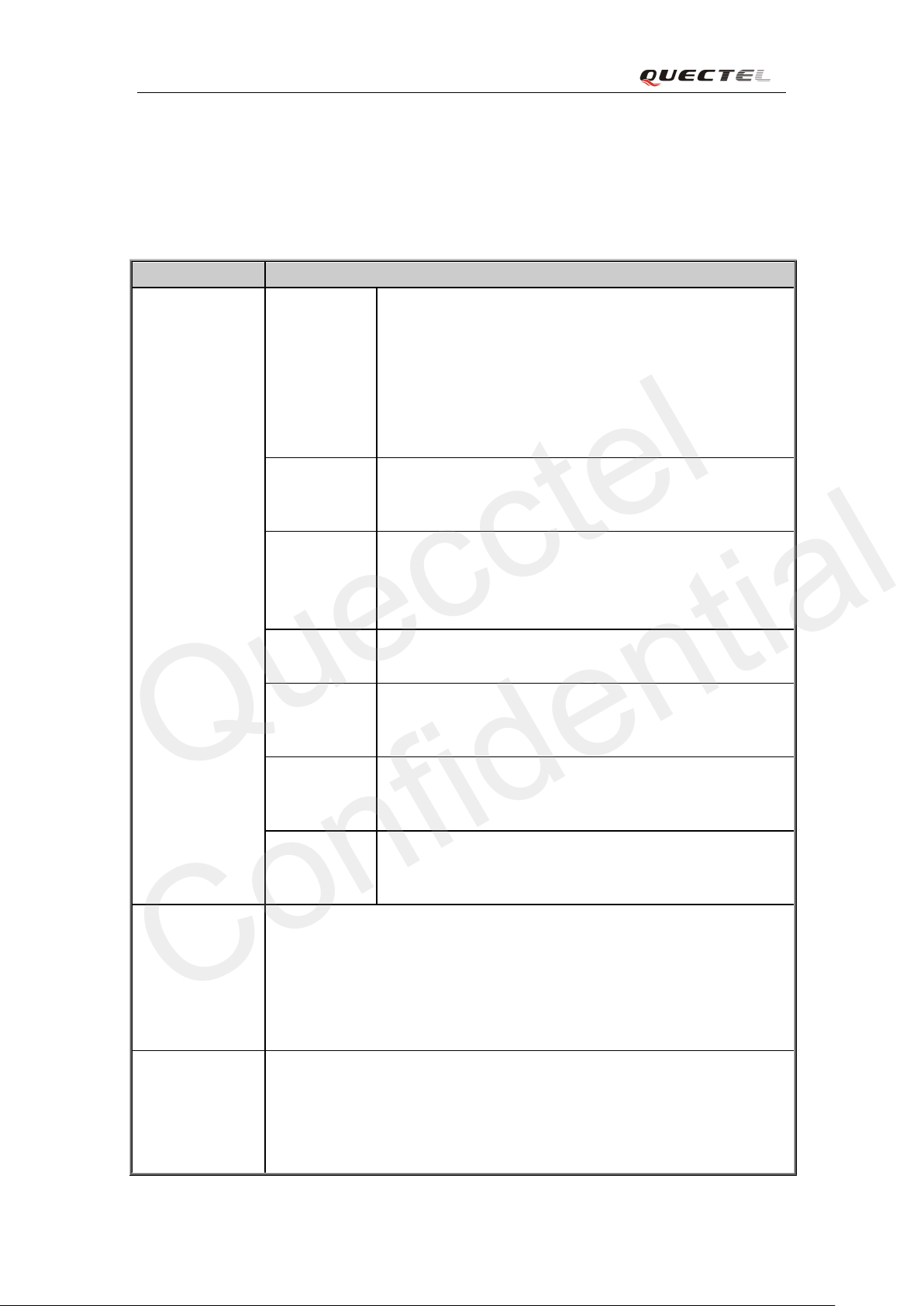

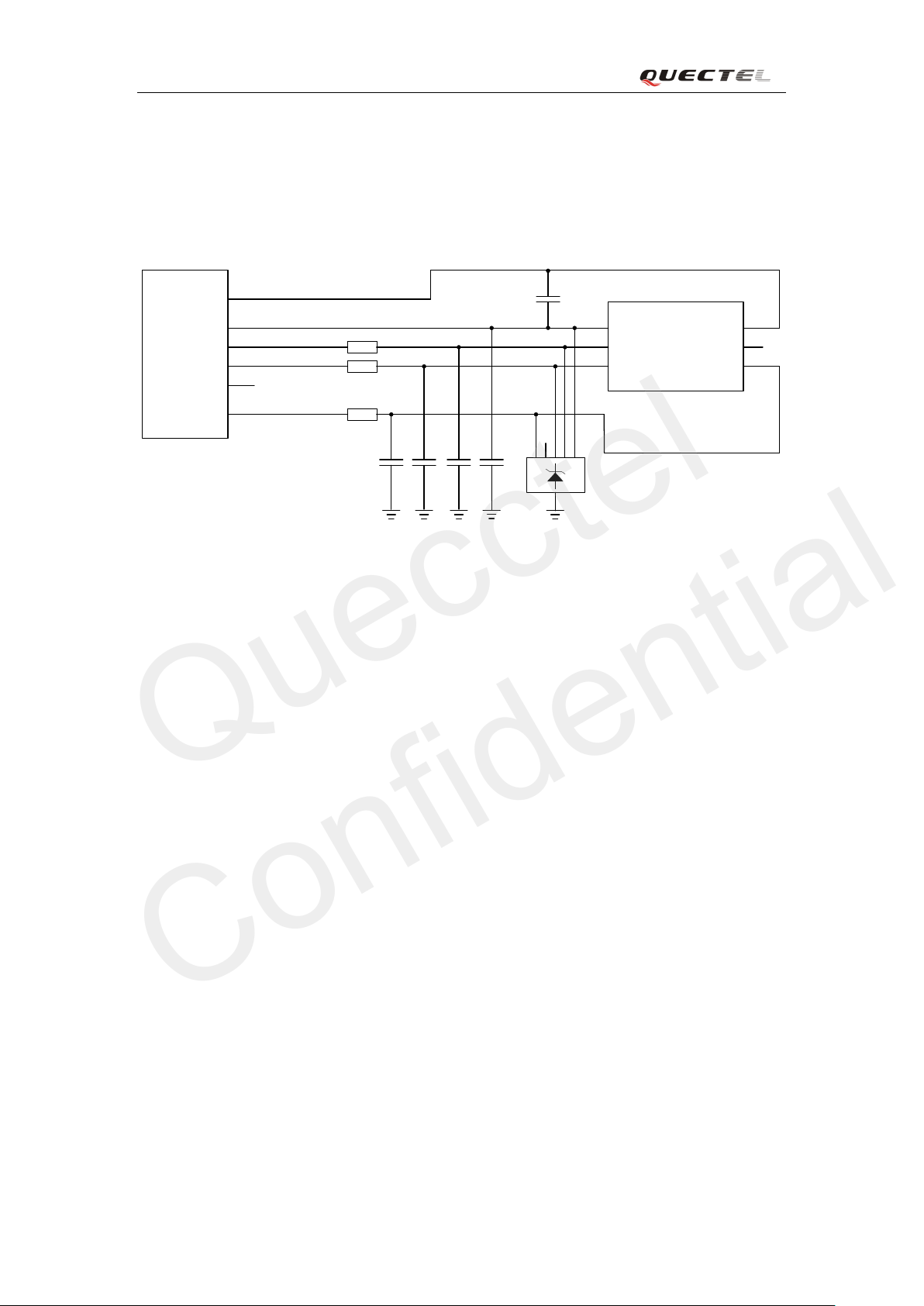

2.2. Fu n c ti o nal di ag r a m

The following figure shows a block diagram of the M50 module and illustrates the major

functional parts:

Power management

Baseband

Serial Flash

The radio frequency part

The peripheral interface

—Charge interface

—PCM interface

—SD interface

—SIM interface

—Audio interface

—Serial interface

—Power supply

—RF interface

—ADC

—Turn on/off interface (PWRKEY & EMERG_OFF)

M50_HD_V2.0 - 17 -

M50 Hardware Design

BB&RF

RF PAM

SAW

Filter

Serial

Flash

32KHz

26MHz

RF Transceiver

Audio

RTC

GPIO

Serial

Interface

Memory

Interface

PCM

Interface

SIM

Interface

SD

Interface

ADC

RF_ANT

VBAT

PWRKEY

EMERG_OFF

VRTC

ADC

STATUS&

NETLIGHT

UART

SIM

Interface

Audio

SD

Interface

PCM

Inteface

Reset

ESD

PMU

Charge

Interface

Charge

Quecctel

Confidential

Figure 1: Module functional diagram

2.3. Evaluatio n bo ard

In orde r t o he lp cu st o mer to deve lop a pplicat i o ns with M50 , Quectel supplies an evaluation board

(EVB) , RS -232 to USB cable , powe r adapte r, e arphone , ante nna and ot her pe riphe rals to control

or test the module. For details, please refer to the document [ 12].

M50_HD_V2.0 - 18 -

M50 Hardware Design

Quecctel

Confidential

3. Application interface

The mo dul e is equi pped w it h 83-pin SMT pads and i t ad opts LCC package. Detailed descriptions

on Sub -interfaces included in these pads are given in the following chapters:

Power supply

Power on/down

Charge interface

RTC

Serial interfaces

Audio interfaces

SIM interface

SD interface

PCM interface

ADC

M50_HD_V2.0 - 19 -

M50 Hardware Design

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

575859606162636465666768697071727374

Top view

75

76

77

78

79

80

81

82

83

SIM_PRESENCE

RESERVED

VRTC

VDD_EXT

GND

GND

RF_ANT

GND

GND

GND

VBAT

VBAT

VBAT

VBAT

RESERVED

RESERVED

RESERVED

RESERVED

ADC1

ADC0

RESERVED

NETLIGHT

SPK2P

AGND

MIC2P

MIC2N

MIC1P

MIC1N

SPK1N

SPK1P

LOUDSPKN

LOUDSPKP

STATUS

PWRKEY

EMERG_OFF

PCM_IN

PCM_CLK

RESERVED

RESERVED

TXD_AUX

RXD_AUX

DBG_TXD

DBG_RXD

RESERVED

DCD

RI

DTR

CTS

RTS

RXD

TXD

SIM1_GND

SIM1_RST

SIM1_CLK

SIM1_DATA

SIM1_VDD

VBAT GND

PCMRFUART

Power

SIM

Reserved Audio

ADC

Other

SD

PCM_OUT

PCM_SYNC

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

SD_CMD

SD_CLK

SD_DATA0

GND

RESERVED

RESERVED

RESERVED

RESERVED

GND

GND

GND

GND

Quecctel

Confidential

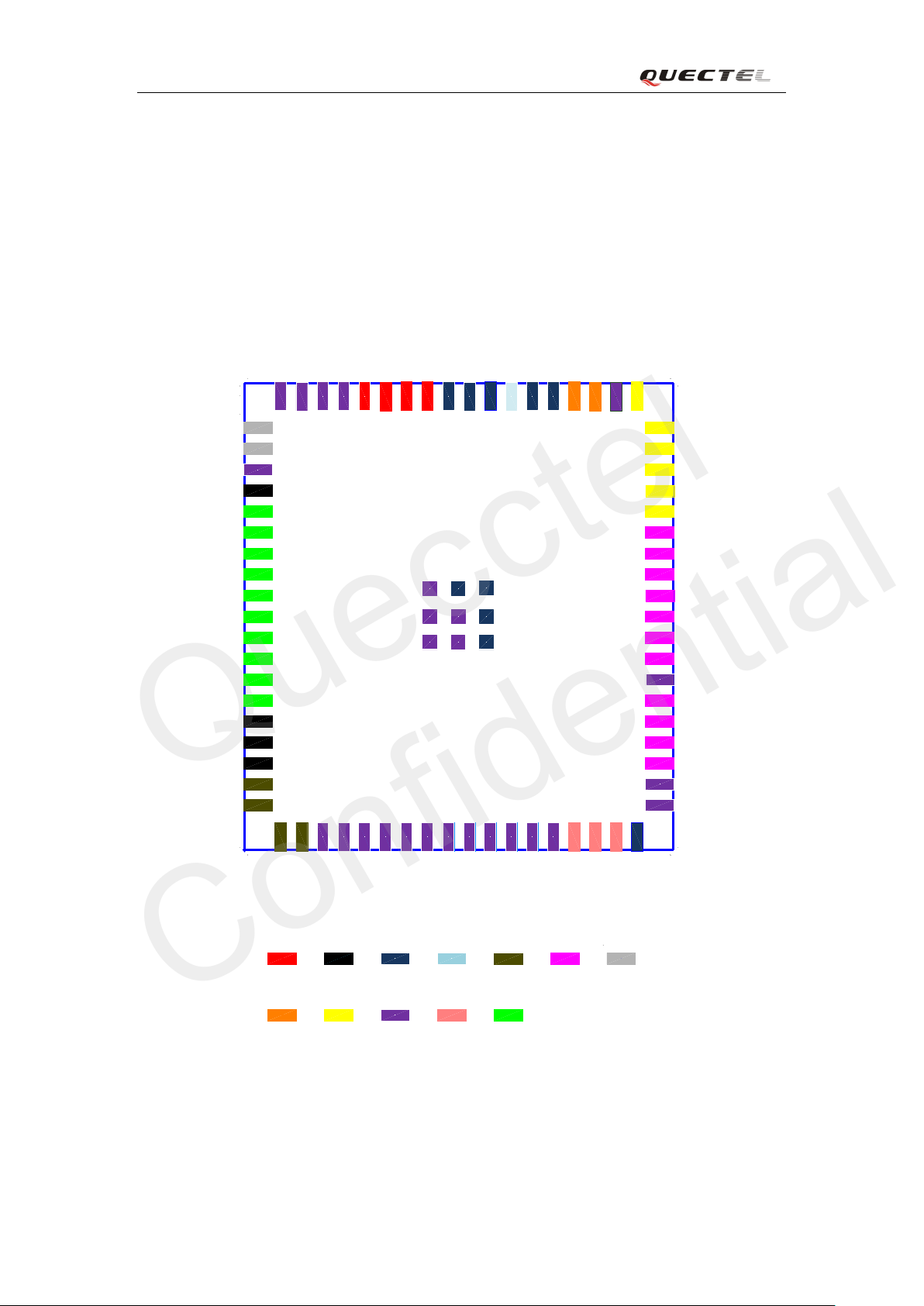

3.1. Pin of module

3.1.1. Pin assignment

Figure 2: Pin assignment

M50_HD_V2.0 - 20 -

M50 Hardware Design

管脚号

管脚名

输入/输出

管脚号

管脚名

输入/输出

Quecctel

Confidential

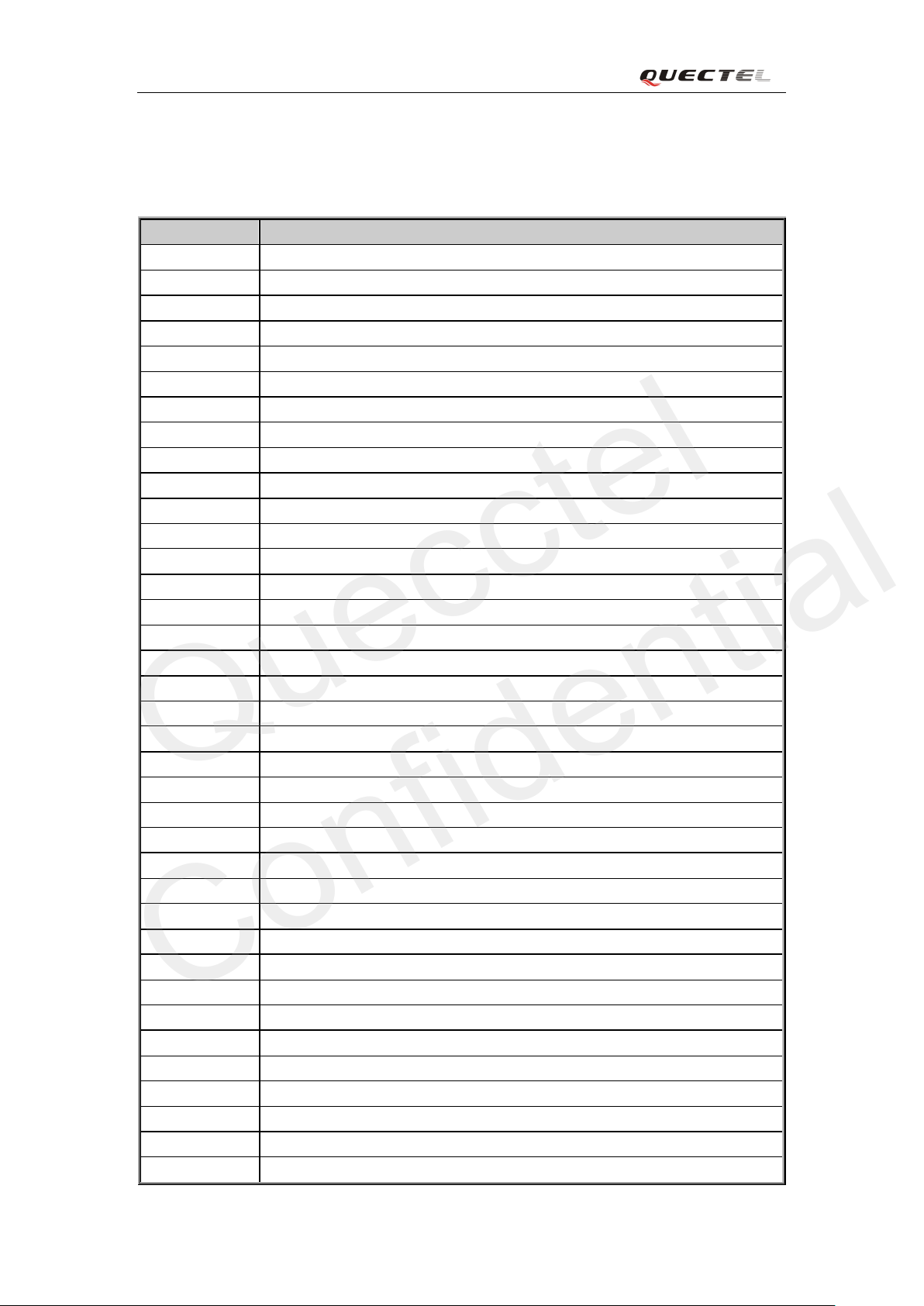

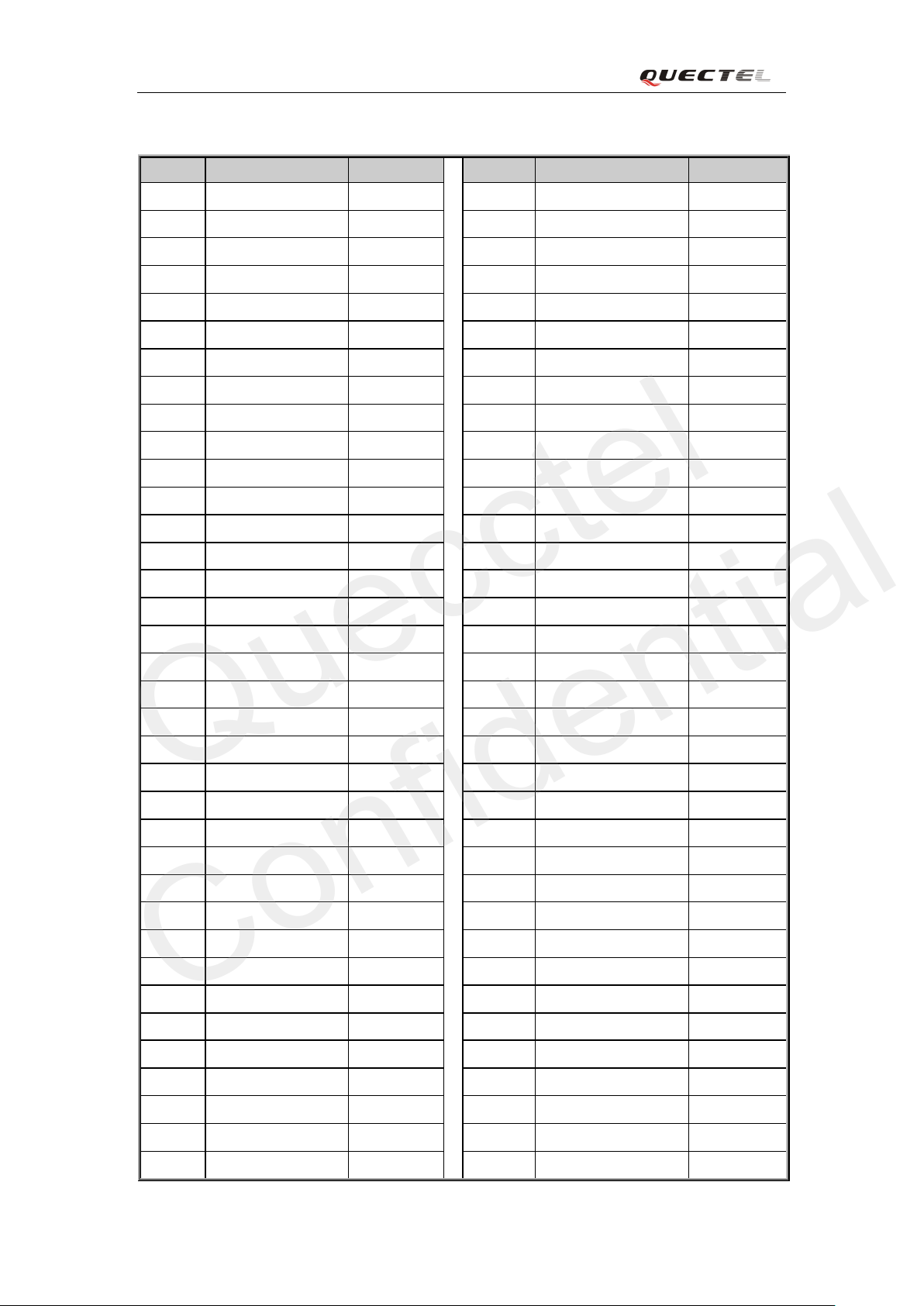

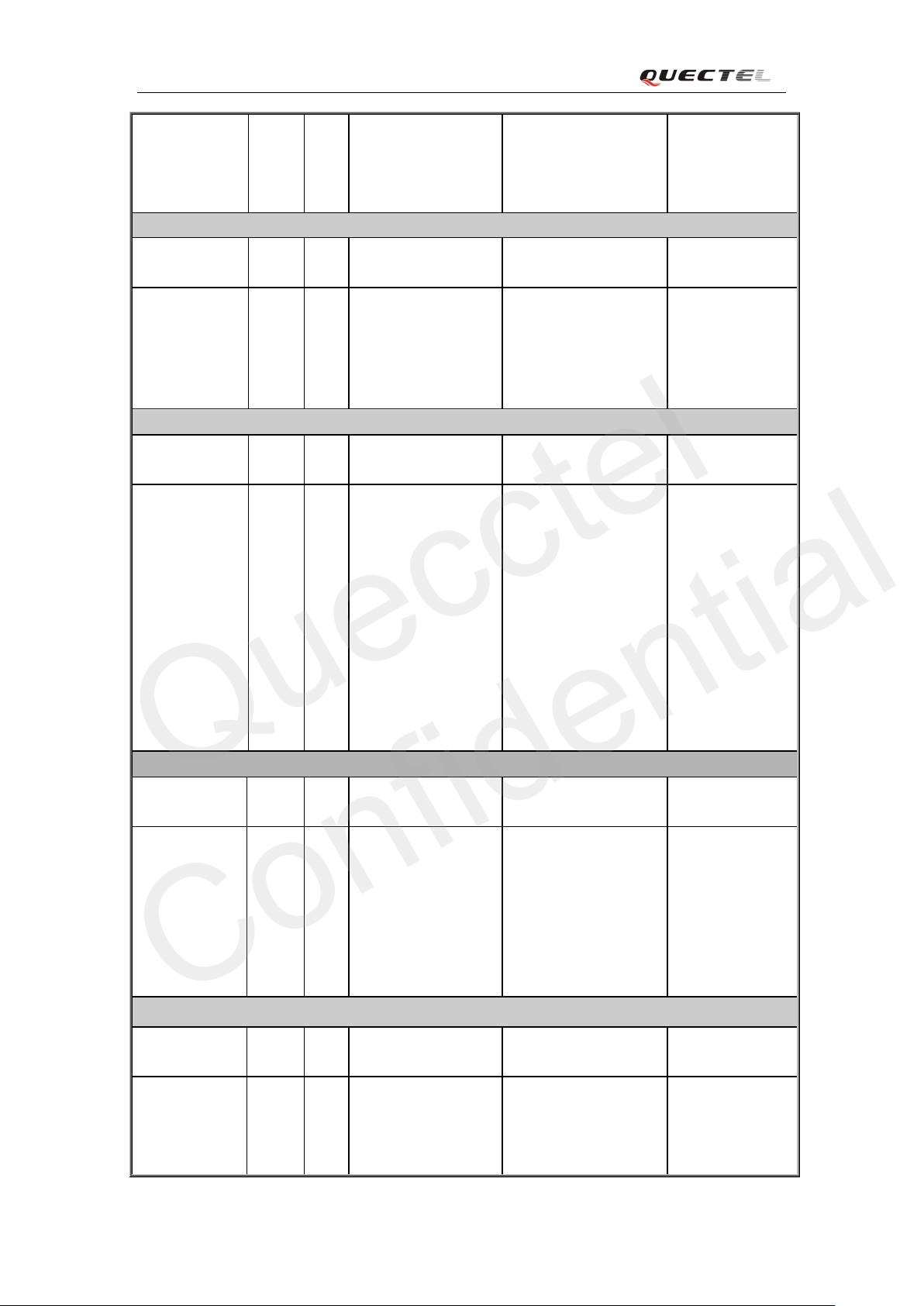

Table 5: M50 pin assignment

1 ADC1 I 2 ADC0 I

3 RESERVED 4 NETLIGHT O

5 SPK2P O 6 AGND

7 MIC2P I 8 MIC2N I

9 MIC1P I 10 MIC1N I

11 SPK1N O 12 SPK1P O

13 LOUDSPKN O 14 LOUDSPKP O

15 STAT US O 16 PWRKEY I

17 EMERG_OFF I 18 PCM_IN I

19 PCM_CLK O 20 PCM_OUT O

21 PCM_SYNC O 22 RESERVED

23 RESERVED 24 RESERVED

25 RESERVED 26 RESERVED

27 RESERVED 28 RESERVED

29 RESERVED 30 RESERVED

31 RESERVED 32 RESERVED

33 RESERVED 34 SD_CMD O

35 SD_CLK O 36 SD_DATA0 I/O

37 GND 38 RESERVED

39 RESERVED 40 TXD_AUX O

41 RXD_AUX I 42 DBG_TXD O

43 DBG_RXD I 44 RESERVED

45 DCD O 46 RI O

47 DTR I 48 CTS O

49 RTS I 50 RXD I

51 TXD O 52 SIM_GND

53 SIM_RST

55 SI M_ DATA I/O 56 SIM_VDD O

57 SIM_PRESENCE I 58 RESERVED

59 VRTC I/O 60 VDD_EXT O

61 GND 62 GND

63 RF_ANT I/O 64 GND

65 GND 66 GND

O 54 SIM_CLK O

67 VBAT I 68 VBAT I

69 VBAT I 70 VBAT I

71 RESERVED 72 RESERVED

M50_HD_V2.0 - 21 -

M50 Hardware Design

Quecctel

Confidential

73 RESERVED 74 RESERVED

75 RESERVED 76 RESERVED

77 RESERVED 78 RESERVED

79 GND 80 GND

81 GND 82 GND

83 GND

Note: Keep all reserved pins open.

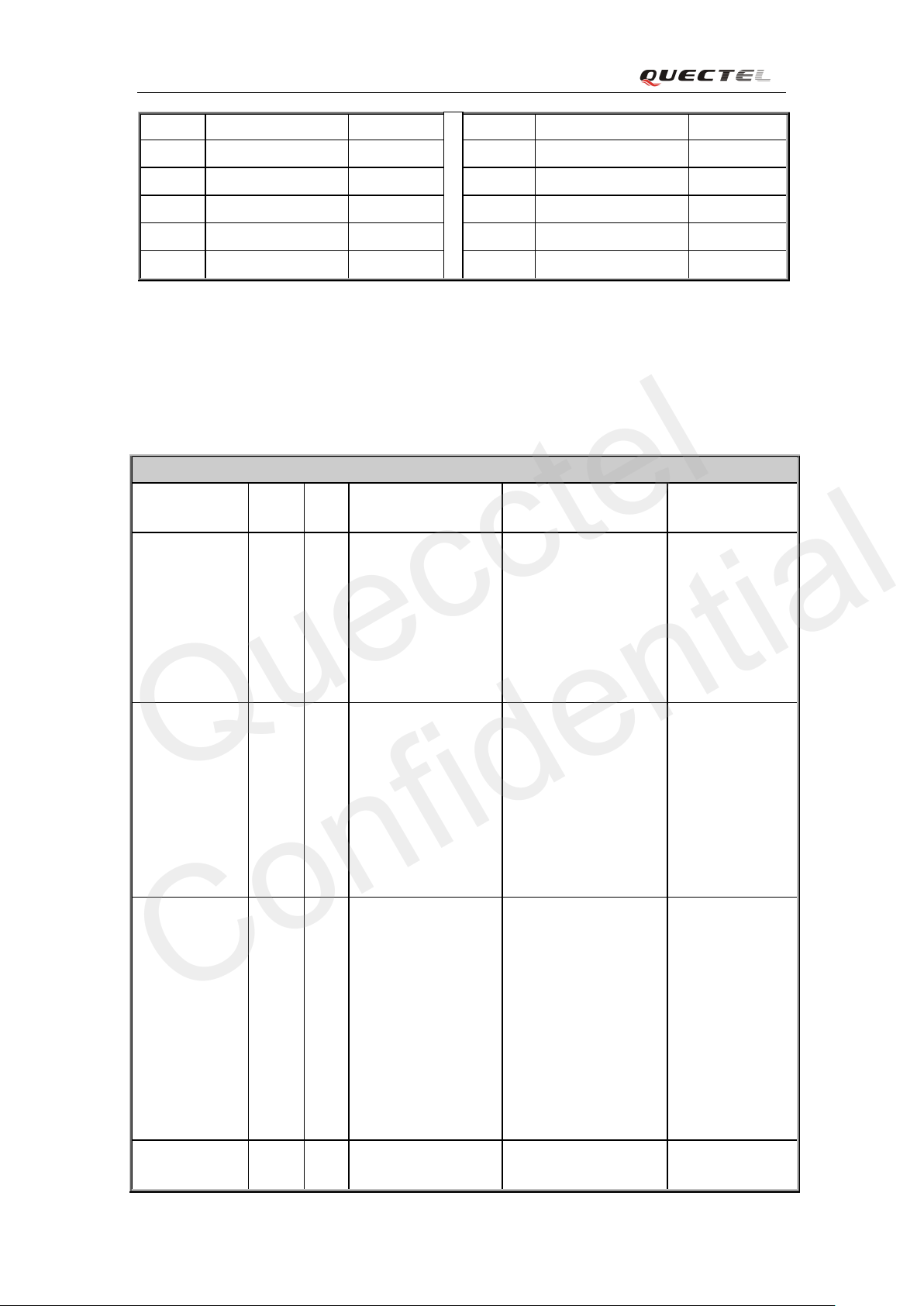

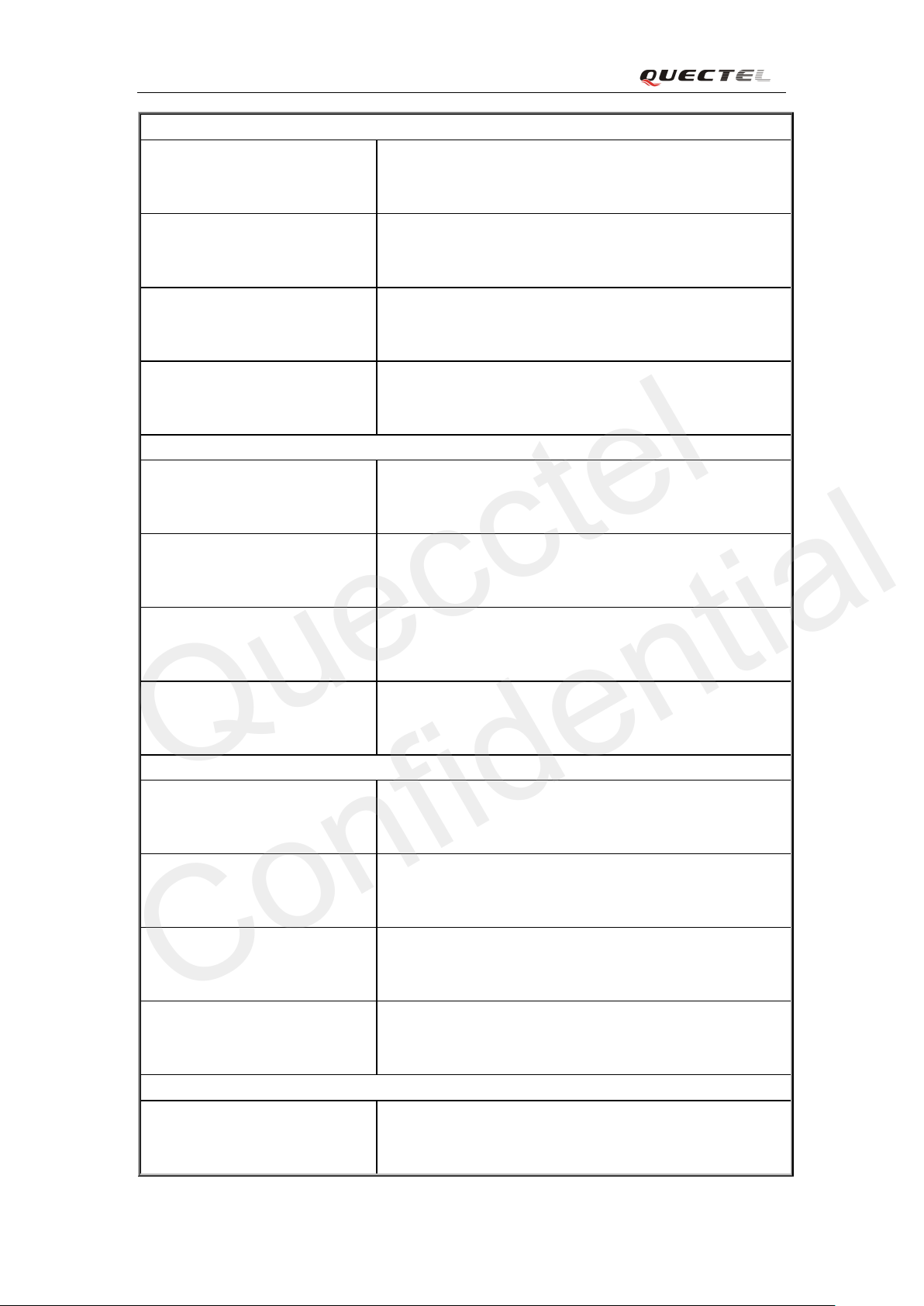

3.1.2. Pin description

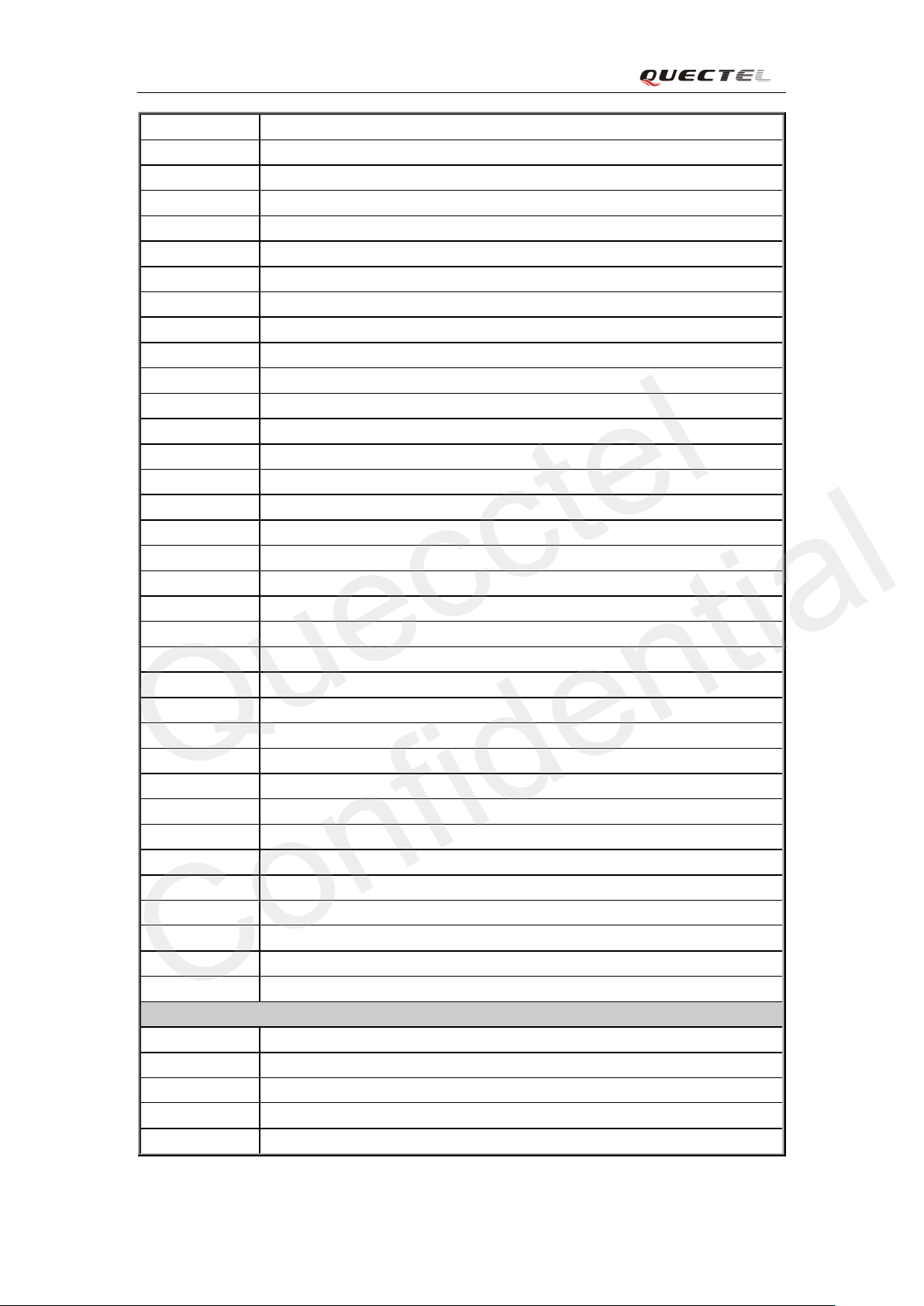

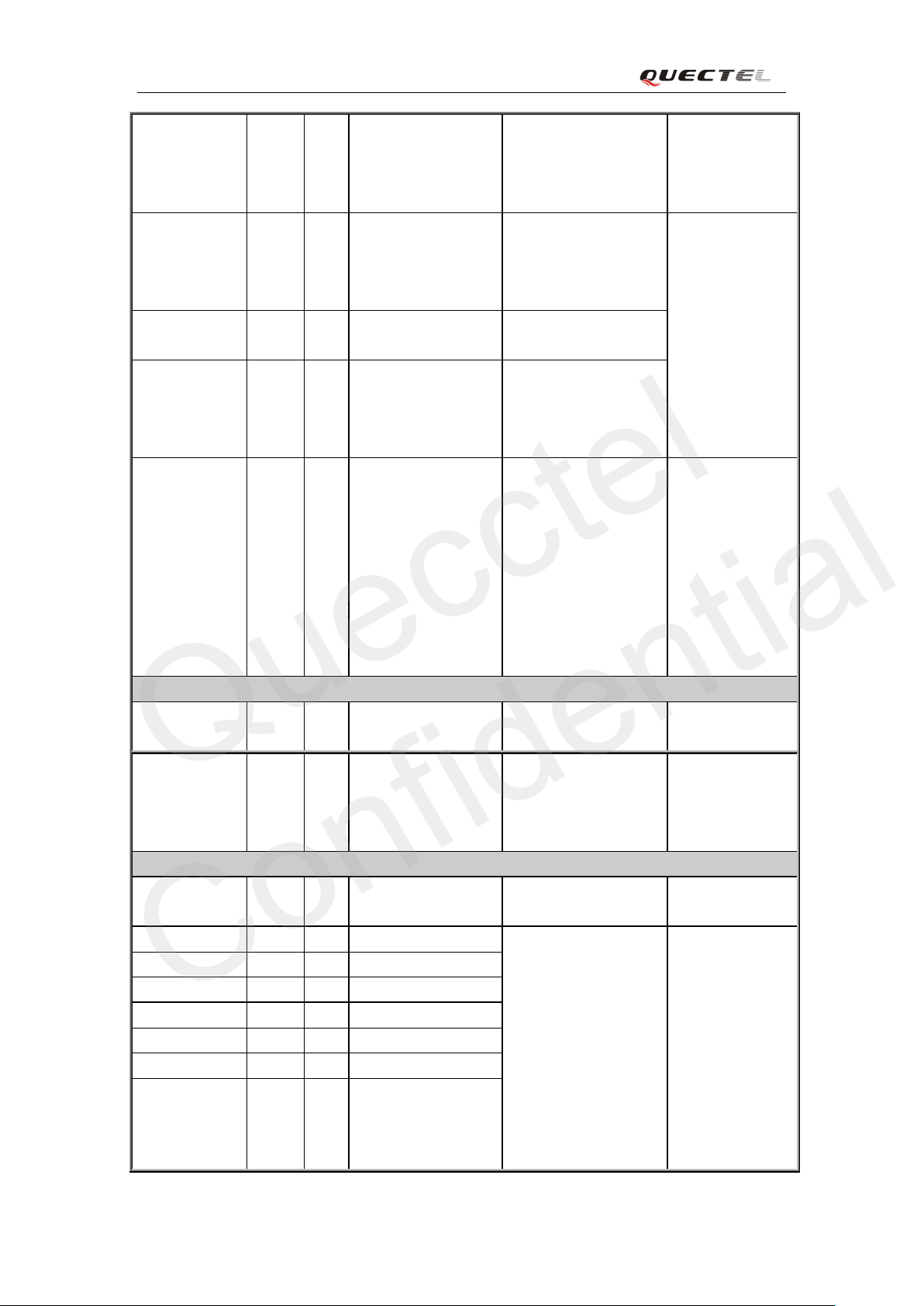

Table 6: Pin description

Power supply

PIN NAME PIN

NO.

VBAT 67,

68,

69,

70

VRTC 59 I/O Power supply for

VDD_EXT 60 O Suppl y 2.8V volt a ge

GND 37,

61,

I/O DESCRIPTION DC

CHARACTERISTICS

I Main power supply

of module:

VBAT=3.3V~4.6V

RTC when VB AT is

not supplied for the

system.

Chargi n g f or backup

battery or golden

capacitor when the

VBAT is supplied.

for external circuit.

Ground

Vm ax= 4.6V

Vmin=3.3V

Vnorm=4.0V

VImax=3.3V

VImin=1.5V

VInorm=2.8V

VOmax=2.85V

VOmin=2.6V

VOnorm=2.8V

Iout(max)= 1mA

Iin=2.6~5 uA

Vmax=2.9V

Vmin=2.7V

Vnorm=2.8V

Imax=20mA

COMMENT

Make sure that

supply sufficient

current in a

transmitting

burst which

typica lly rises to

1.6A.

If unused, keep

this pin open.

1. If unused,

keep this pin

open.

2. Re co mmended

to add a

2.2~4.7uF

bypass capacitor

when supplying

power for

ext e rnal cir cuit .

M50_HD_V2.0 - 22 -

M50 Hardware Design

Quecctel

Confidential

62,

64,

65,

66,

Tu rn on /off

PIN NAME PIN

NO.

PWRKEY 15 I Turn on/off control.

Emergency shutdown

PIN NAME PIN

NO.

EMERG_OFF 17 I Emergency off.

Module indicator

PIN NAME PIN

NO.

STAT US 16 O Indicate module

Audio in t e rface

I/O DESCRIPTION DC

CHARACTERISTICS

VILmax=

PWRKE Y sh ou l d be

pulle d down for a

moment to turn on

or off the system.

I/O DESCRIPTION DC

Pulled dow n fo r at

least 20ms , whi c h

will turn of f the

module in case of

emergency. Use it

only when normal

shutdown t hrough

PWRKEY or A T

command cannot

perform well.

I/O DESCRIPTION DC

operat in g status.

High level indicates

module is power-on

and low level

indicates

power-down.

0.1×VBAT

VIHmin=

0.6×VBAT

VI max=V BAT

CHARACTERISTICS

VILmax=0.4V

VIHmin=2.2V

V

open

CHARACTERISTICS

VOHmin=

0.85×VDD_EXT

VOLmax=

0.15×VDD_EXT

max=2.8V

COMMENT

Pulled up to

VBAT internally.

COMMENT

Open

drain/collector

driver required in

cellular device

application.

If unused, keep

this pin open.

COMMENT

If unused, keep

this pi n open.

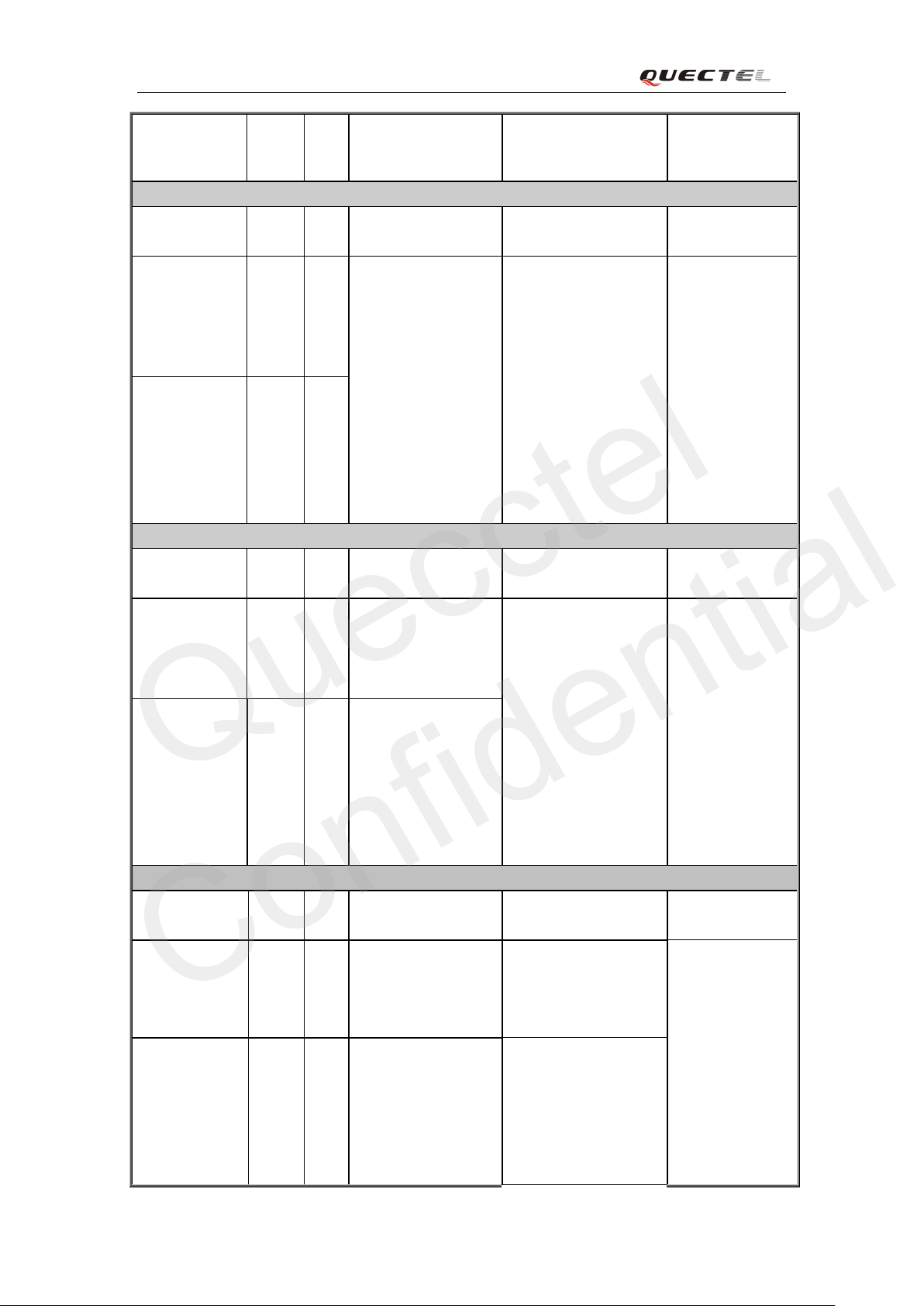

PIN NAME PIN

MIC1P

MIC1N

M50_HD_V2.0 - 23 -

NO.

9, 10 I Channe l one for

I/O DESCRIPTION DC

CHARACTERISTICS

I f unused, keep

positive and

negative voice-band

input

COMMENT

these pins open.

M50 Hardware Design

Quecctel

Confidential

MIC2P

MIC2N

SPK1P

SPK1N

SPK2P 5 O Channe l t wo for

AGND 6 Analo g gr o und.

LOUDSPKN

LOUDSPKP

Net status indicator

PIN NAME PIN

7, 8 I Ch a nnel two for

positive and

negative voice-band

input

12, 11 O Channe l o ne for

positive and

negative voice-band

output

voice-band output

Constitute a pse udo

diffe rent ial ch annel

with SPK2P.

13,

14

NO.

O Channel three of

positive and

negative voice-band

output

I/O DESCRIPTION DC

1. If unuse d,

keep these pins

open.

2. Support both

1. If unused,

CHARACTERISTICS

voice a n d

ringtone output.

keep these pins

open.

2. Embedded

amplifier of class

AB internally.

3. Support both

voice a n d

ringtone output.

COMMENT

NETLIGHT 4 O Netw or k status

indication

UART Port

PIN NAME PIN

NO.

DTR 47 I Data terminal ready VILmin=0V

RXD 50 I Receive data

TXD 49 O Transmit data

RTS 51 I Request to send

CTS 48 O Clear to send

RI 46 O Ring indicator

DCD 45 O Data carrier

I/O DESCRIPTION DC

detection

VOHmin=

0.85×VDD_EXT

VOLmax=

0.15×VDD_EXT

CHARACTERISTICS

VILmax=

0.25×VDD_EXT

VIHmin=

0.75×VDD_EXT

VIHmax=

VDD_EXT+0.3

VOHmin=

0.85×VDD_EXT

VOLmax=

If unused, keep

this pin open.

COMMENT

If only use TXD,

RXD and GND

to co mmu n icat e ,

recommend

pulling down

RTS an d ke e ping

othe r pin s open.

M50_HD_V2.0 - 24 -

If unused, keep

Quecctel

Confidential

M50 Hardware Design

0.15×VDD_EXT

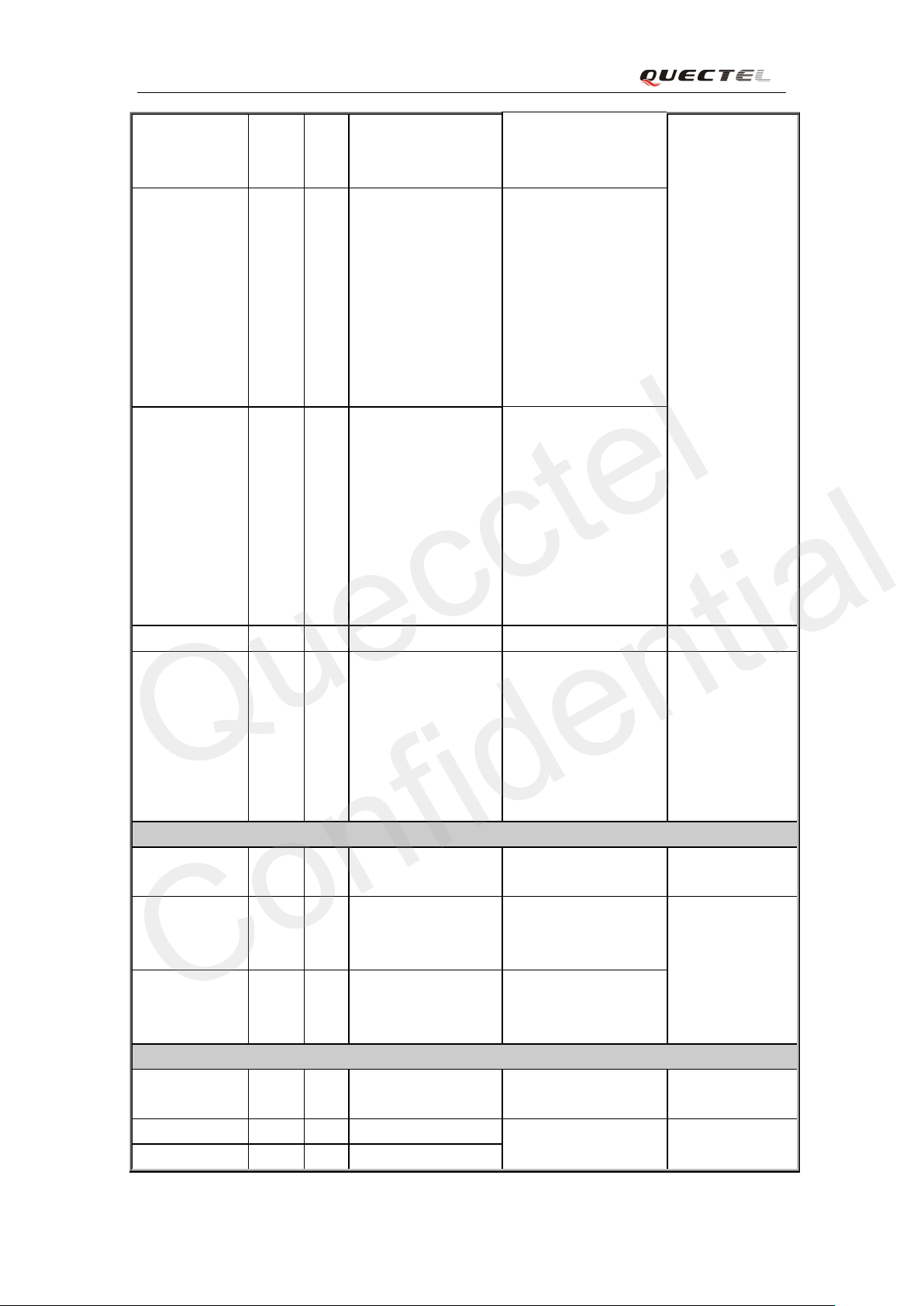

Debug Port

PIN NAME PIN

NO.

DBG_TXD 42 O UART interface for

DBG_RXD 43 I

Auxiliary UART Port

PIN NAME PIN

NO.

TXD_AUX 40 O T ransmit da ta VILmin=0V

RXD_AUX 41 I Receive data

SIM interface

PIN NAME PIN

NO.

SIM_VDD 56 O Power sup ply for

SI M_ DATA 54 I/O SIM data 3V:

I/O DESCRIPTION DC

CHARACTERISTICS

VILmin=0V

debu gging only.

I/O DESCRIPTION DC

I/O DESCRIPTION DC

SIM card

VILmax=

VIHmin=

VIHmax=

VOHmin=

VOLmax=

CHARACTERISTICS

VILmax=

VIHmin=

VIHmax=

VOHmin=

VOLmax=

CHARACTERISTICS

The voltage can be

selected by firmware

automatically. Either

1.8V or 3V.

VOLmax=0.4

VOHmin=

1.8V:

VOLmax=

0.25×VDD_EXT

0.75×VDD_EXT

VDD_EXT+0.3

0.85×VDD_EXT

0.15×VDD_EXT

0.25×VDD_EXT

0.75×VDD_EXT

VDD_EXT+0.3

0.85×VDD_EXT

0.15×VDD_EXT

SIM_VDD-0.4

COMMENT

If unused, keep

these pins open.

COMMENT

these pin s open.

COMMENT

A ll signals of

SIM interface

should be

protected a gai nst

ESD with a TVS

diode a rra y.

Max i mu m c ab l e

length is 200mm

from the module

pad to SIM card

M50_HD_V2.0 - 25 -

M50 Hardware Design

Quecctel

Confidential

0.15×SIM_VDD

VOHmin=

SIM_VDD-0.4

SIM_CLK 55 O SIM clock 3V:

VOLmax=0.4

VOHmin=

0.9×SIM_VDD

1.8V:

VOLmax=

0.12×SIM_VDD

VOHmin=

0.9×SIM_VDD

SIM_RST 53 O SIM reset 3V:

VOLmax=0.36

VOHmin=

0.9×SIM_VDD

1.8V:

VOLmax=

0.2×SIM_VDD

VOHmin=

0.9×SIM_VDD

SIM_GND 52 SIM ground

SIM_PRESEN

CE

ADC

PIN NAME PIN

ADC0 2 I General purpose

ADC1 1 I General purpose

PCM

PIN NAME PIN

PCM_CLK 19 O PCM cloc k VILmin=0V

PCM_IN 18 I PCM data i nput

57 I SIM card detection VILmin=0V

VILmax=

0.25×VDD_EXT

VIHmin=

0.75×VDD_EXT

VIHmax=

VDD_EXT+0.3

I/O DESCRIPTION DC

NO.

analog to digital

converter.

analog to digital

converter.

I/O DESCRIPTION DC

NO.

CHARACTERISTICS

Volt a ge range: 0V to

2.8V

Volt a ge range: 0V to

2.8V

CHARACTERISTICS

VILmax=

holder.

If unused, keep

this pin open.

COMMENT

Please give

priority to the

use of ADC0.

If unused, keep

these pins open.

COMMENT

M50_HD_V2.0 - 26 -

M50 Hardware Design

Quecctel

Confidential

PCM_OUT 20 O PCM data output 0.25×VDD_EXT

PCM_SYNC 21 O PCM frame

synchronization

SD card

PIN NAME PIN

NO.

SD_CMD 34 O SD command VILmin=0V

SD_CLK 35 O SD cl ock

SD_DATA0 36 I/O SD data

RF inter face

PIN NAME PIN

NO.

RF_ANT 63 I/O RF antenna pad Impedance of 50Ω

Other interface

PIN NAME PIN

NO.

DOWNLOAD 3 I VILmin=0V

RESERVED 22~

33,

38~

39,

44,

58,

I/O DESCRIPTION DC

I/O DESCRIPTION DC

I/O DESCRIPTION DC

Keep these pins

VIHmin=

0.75×VDD_EXT

VIHmax=

VDD_EXT+0.3

VOHmin=

0.85×VDD_EXT

VOLmax=

0.15×VDD_EXT

CHARACTERISTICS

VILmax=

0.25×VDD_EXT

VIHmin=

0.75×VDD_EXT

VIHmax=

VDD_EXT+0.3

VOHmin=

0.85×VDD_EXT

VOLmax=

0.15×VDD_EXT

CHARACTERISTICS

CHARACTERISTICS

VILmax=

0.25×VDD_EXT

VIHmin=

0.75×VDD_EXT

VIHmax=

VDD_EXT+0.3

COMMENT

COMMENT

COMMENT

Keep this pin

open.

open.

M50_HD_V2.0 - 27 -

M50 Hardware Design

Quecctel

Confidential

71~

75

M50_HD_V2.0 - 28 -

M50 Hardware Design

, the power

no GPRS

, power

decided by the PCL, worki ng RF band and

Quecctel

Confidential

3.2. Operating modes

The table below briefly summarizes the various operating modes in the following chapters.

Table 7: Overview of operating modes

Mode Function

Norm al operation GSM/GPRS

SLEEP

GSM IDLE Firmware is active. The module has registered to the GSM

GSM TALK GSM connection is ongoing. In this mode

GPRS IDLE T he mo dule is no t regi stere d t o GPRS net w ork. The m odule

The m odul e will aut omati c all y go int o SLE EP m ode if DTR

is set to hi gh level and there is no i nterrupt ( such a s GPIO

inter r upt or dat a on UART port).

In this case, the cu rre nt consum ption of mo dule will re duce

to the minimal level.

During SLEEP mode, the module can still receive paging

mess age a nd S M S f ro m t he syst em nor m ally.

net wor k, and the mod ule is read y t o send and re ceive GSM

data.

consumption is decided by the configuration of Power

Contr ol Level ( P C L) , dynamic DTX co ntr ol and the working

RF ban d.

is not reachable through GPRS channel.

GPRS

STANDBY

GPRS

READY

GPRS DATA There is GPRS data in transfer. In this mode

Power down Normal shutdown by sending the “AT+QPOWD=1” command, using the

PWRKEY or the EMERG_OFF

disc onne cts t he po wer suppl y fro m the b ase band p art of the m odul e, and onl y

the po wer su pply f or t he RTC i s remained. Softw are is not act i ve. The UART

interfaces are not accessible. Operating voltage (connected to VBAT) remains

Minimum

functionality

mode (without

removing power

supply)

applied.

“AT+CFUN” command can set the module to a minimum functionalit y mo de

witho ut re movi ng t he power s upply. I n thi s case, the RF p art of the mod ule

will n ot wor k or the SIM card will not be a cces sible , or both RF p art and SIM

card will be disabled, but the UART port is still accessible. The power

consumption in this case is very low.

The module is registered to GPRS network, but

PDP context i s active . The SGSN k nows the Routin g Are a

where the module is located at.

The PDP context is active, but no data transfer is ongoing.

The module is ready to receive or send GPRS data. The

SGSN knows the cell where the module is located at.

consu mption is

GPRS multi-slot configuration.

1)

pin. The power management ASIC

M50_HD_V2.0 - 29 -

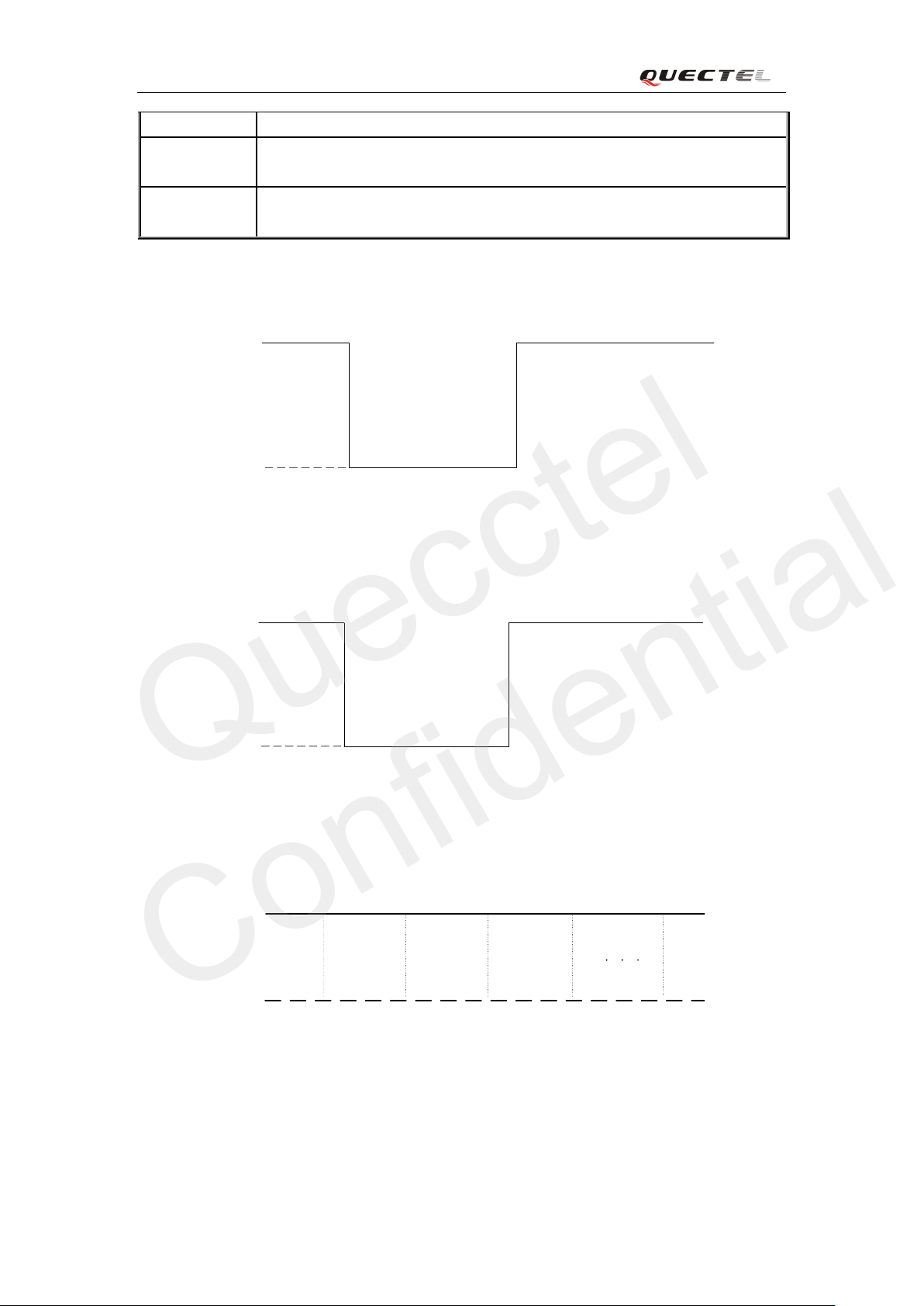

M50 Hardware Design

Vdrop

4.615ms

577us

I

VBAT

VBAT

Burst:1.6A

Quecctel

Confidential

1) Use the EMERG_OFF pin only while failing to turn off the module by the command

“A T+Q POW D=1” and th e PWRKEY pin. Please refer to the Section 3.4.2.4.

3.3. Power supply

3.3.1. Power features of module

The power supply is one of the key issues in the de signi n g G SM terminals. Due to the 577us radio

burst e mi ss i o n i n GSM eve r y 4. 615ms, powe r suppl y must be able to de li ver high curr e nt peaks i n

a burst period. During these peaks, drops on the supply voltage must not exceed minimum

working voltage of module.

For t he M50 module , the max cu rre nt con sum ptio n coul d re ach to 1.6 A duri ng a tr ans mit bu rst . It

will cause a large voltage drops on the VBAT. In order to ensure stable operation of the module, it

is recommended that the max voltage drop during th e transmit burst does not exc eed 400mV.

Figure 3: Voltage ripple during transmitting

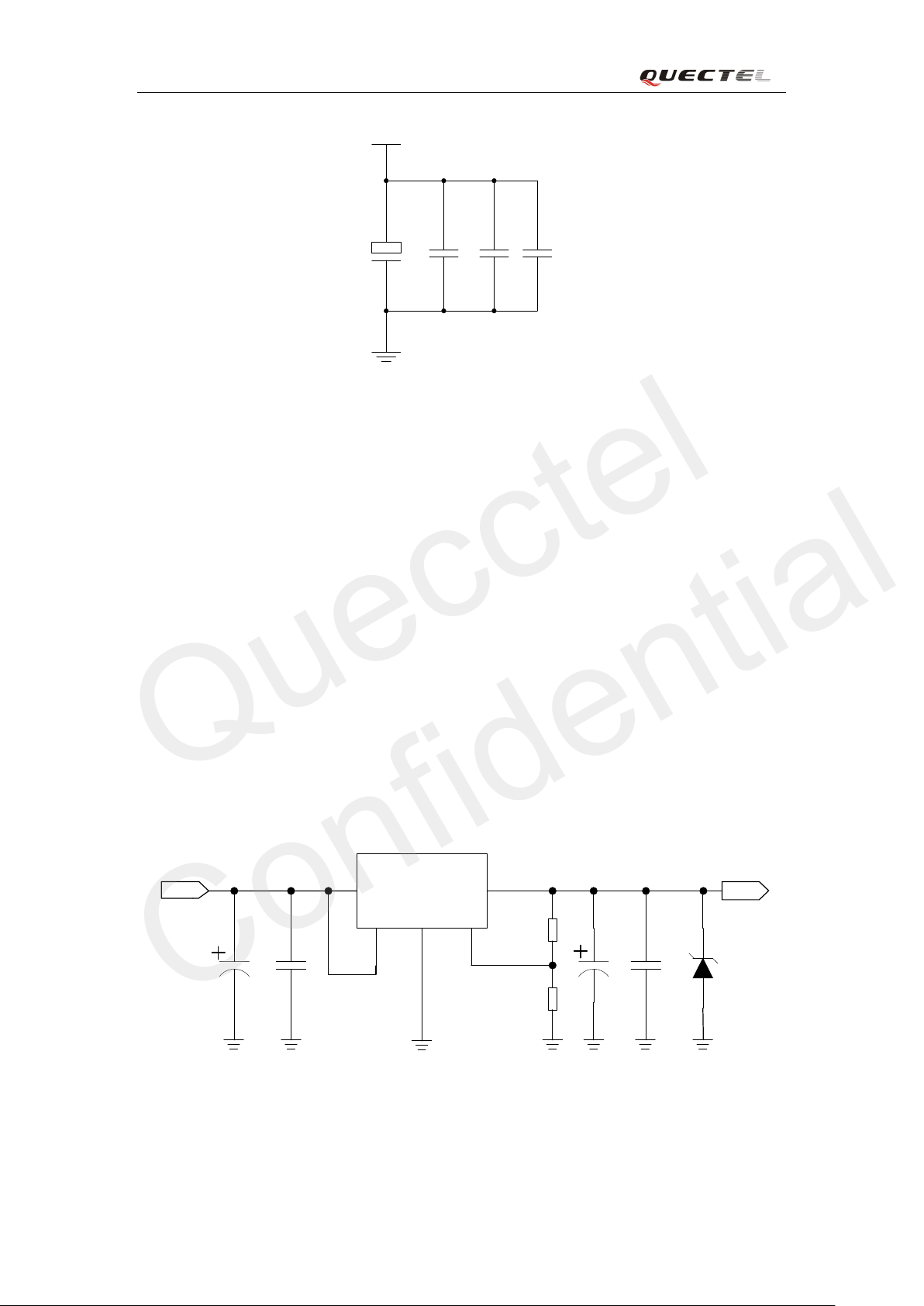

3.3.2. Decrease su pp l y voltag e d rop

The po wer su pply r an g o f the m od ule i s 3.3V t o 4.6V. Make sure t h at the input volt a ge wil l ne ver

drop belo w 3 .3V even i n a trans mi t t ing b ur st . If the po wer voltage dro ps be low 3.3V, the mod ule

coul d turn of f auto mati cally. F or bette r po wer per forman ce, it is reco mmende d to pl ace a 10 0uF

tantalum capacitor with low ESR (ESR=0.7Ω) and ceramic capacitor 100nF , 33pF an d 10pF near

the VBAT pin. The reference circuit is illustrated in Figure 4.

The VBAT rout e should be wide enough to ensure that there is not too much voltage drop

occurring during transmit bu rst. T he widt h of t ra ce s houl d be n o le ss t ha n 2mm and t he p rinci pl e

of the VBAT route is the longer route, the wi de r trace.

M50_HD_V2.0 - 30 -

M50 Hardware Design

VBAT

C2C1

+

C3 C4

GND

100uF 100nF 10pF

0603

33pF

0603

DC_IN

C1

C2

MIC29302 U1

IN OUT

EN

GND

ADJ

2 4

1

3

5

VBAT

100nF

C3

470uFC4100nF

R1

D1

120K

51K

R2

470uF

Quecctel

Confidential

Figure 4: Reference circuit for the VBAT input

3.3.3. Reference design for power supply

The po wer des ign for t he m od ul e is ver y imp ortant , since t he pe r form ance of po wer su pply fo r the

module largely depends on the power source. The power supply is capable of providing the

sufficient current up to 2A at least. If the voltage drop between the input and output is not too high,

it is suggested to use a LDO as module’s power supply. If there is a big voltage difference

bet ween t he i np ut s our ce and t he de si re d out pu t (V BAT) , a swit che r p ower co nve rte r is prefe r t o

use as a po wer supply.

Figure 5 show s a r eferenc e design for +5V input power source . The designed ou tput for the power

suppl y i s 4. 16V and the m axi mum l o ad curre nt is 3A. In add itio n, in o rder t o get a st a ble o ut put

voltage, a zener diode is placed close to the pins of VBAT. As to the zener diode, it is suggested to

use a zener dio de w hich reve r se zener vol tage is 5. 1V a nd dissip a ti o n po wer is mo re t h a n 1 Watt.

M50_HD_V2.0 - 31 -

Figure 5: Reference circuit for power supply

M50 Hardware Design

Turn on pulse

PWRKEY

4.7K

47K

Quecctel

Confidential

3.3.4. Monitor power supply

To monit or t he su ppl y v olt age, customer can use the “ AT+ CBC” c omman d which i nclude s three

parameters: charging status, remaining battery capacity and voltage value (in mV). It returns the

0~100 percent of battery capacity and actual value measured between VBAT and GND. The

volt age i s a ut o m atically measured in pe ri od of 5s. The di s played volt a ge (in mV ) is a v e r a ged over

the last measuring period before the “AT+CBC” command i s executed .

For details, pleas e refer to the document [1].

3.4. Power on and d own scenarios

3.4.1. Power on

Customer’s ap plication can t u rn on the module by dri vi ng the pin PWRKE Y to a low leve l voltage ,

and af te r STATUS pin output s a high le ve l , PW RKEY pin c a n be relea s ed. Cus to mer ma y mo ni tor

the le ve l o f t he STATUS pin t o j udge whe t her t he mo dule is po we r-on or not . An ope n colle cto r

driver circuit is sugge sted to control t he PWRKEY. A simple reference circuit i s illustrated as

below.

Figure 6: Tu rn on the module using driving circuit

Note: The module is set to autobauding mode (AT+IPR=0) in default configuration. In the

autobauding mode, the URC “RDY” after powering on is not sent to host controller. When the

module receives AT command, it will be powered on after a delay of 2 or 3 seconds. Host

controller should fir stly send an “AT” or “at” string in order that the module can detect baud

rate of host controller, and it should send the second or the third “AT” or “at” string until

receiving “OK” string from the module. Then an “AT+IPR=x;&W” should be sent to set a fixed

baud rat e for the module and sav e the confi gurati on to flash memory of the module. After these

configurations, the URC “RDY” would b e received from the UART Port o f the module every

time when the module is powered on. Refer to the section “AT+IPR” in document [1].

M50_HD_V2.0 - 32 -

M50 Hardware Design

S1

PWRKEY

TVS1

Close to S1

EMERG_OFF

(INPUT)

VDD_EXT

(OUTPUT)

V

IL

<0.1*VBAT

V

IH

> 0.6*VBAT

VBAT

PWRKEY

(INPUT)

54ms

STATUS

(OUTPUT)

800ms

>1s

OFF

BOOTING

MODULE

STATUS

RUNNING

2

1

Quecctel

Confidential

The other way to control the PWRKEY is using a button directly. A TVS component is

indispensable to be placed nearby the button for ESD protection. When pressing the key,

electrostatic strike may generate from finger. A reference circuit is shown in the following figure.

Figure 7: Turn on the module using keystroke

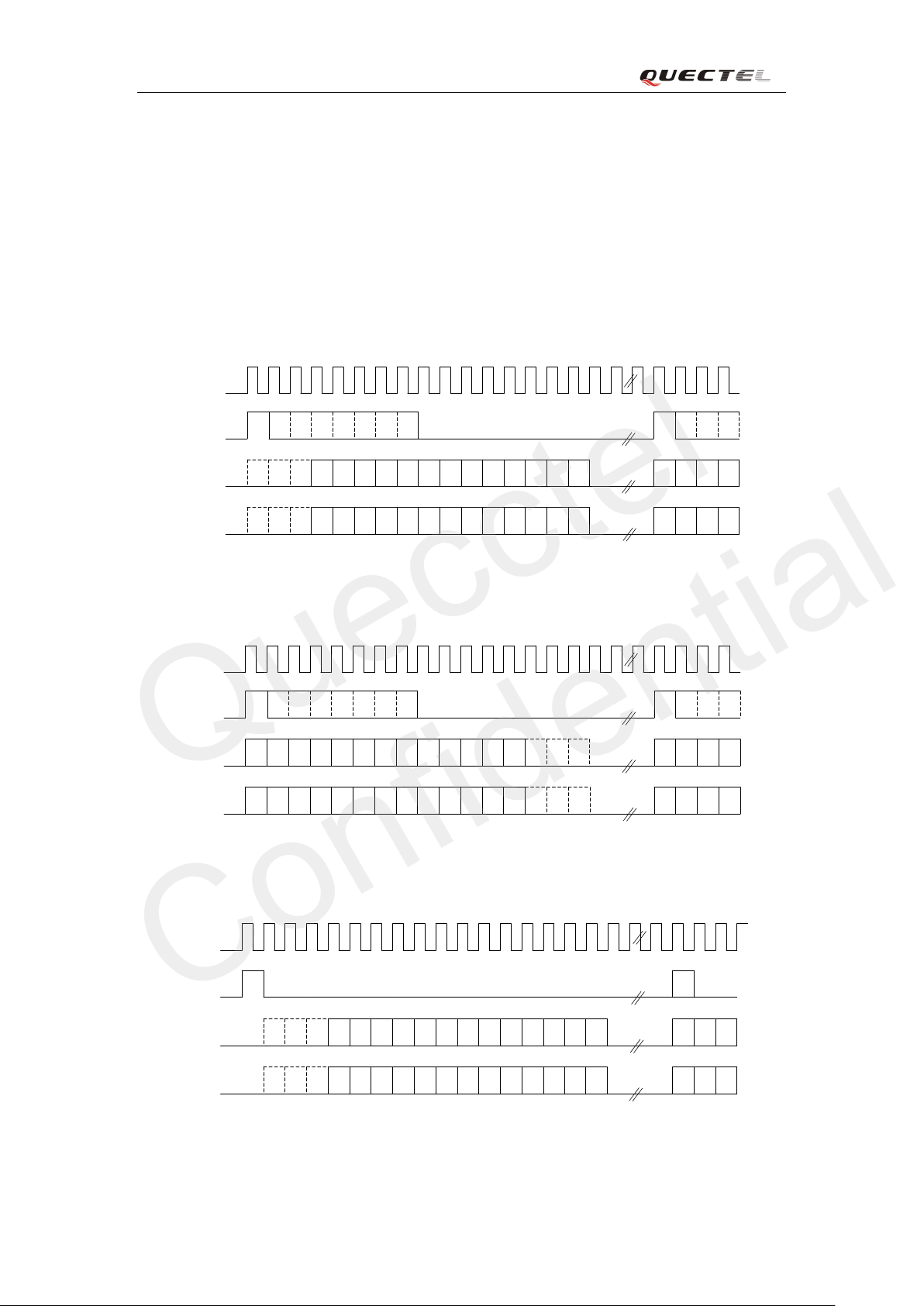

The power-on sc enarios is illustrated as the following figure.

① Make sure that VBAT is stable before pulling down P WRKEY pi n. The time between them

② EMERG_OFF should be floated when it is unused

M50_HD_V2.0 - 33 -

is recommended 30ms.

Figure 8: Timing of turning on system

M50 Hardware Design

VBAT

PWRKEY

(INPUT)

STATUS

(OUTPUT)

EMERG_OFF

(INPUT)

Logout net about 2s to 12s

0.6s<Pulldown<1s

>160us

Quecctel

Confidential

3.4.2. Power down

The following procedures can be used to turn off the module:

Normal power down procedure: Turn off module using the PWRKEY pin

Normal pow e r down procedure: Turn off module using command “AT+QPO WD”

Over-voltage or under-voltage automatic shutdown: Take effect when over-voltage or

under-voltage is detected

Emergent po wer down proce du re : Turn off mod ul e us ing the EM E R G_ O FF pin

3.4.2.1. Power d own module using the PWRKEY pin

Customer’s application can turn off the module by driving the PWRKEY to a low level voltage for

a certain time. The power dow n scenario is illustrated in F igure 9.

The power down procedure causes the module to log off from the network and allows the

firmware t o save importa nt dat a be fore co mpletely dis connecti ng the p ower sup ply, thus it is a

safe way.

Before the compl eti on of the powe r do wn pro ced ure, the modul e send s out t he res ult code s hown

below:

Note: This result code does not appear when autobauding is active and DTE and DCE are not

correctly synchronized after start-up. The module is recommended to set a fixe d baud rate.

Afte r th at m ome nt, no f urthe r AT com man ds c an be e xe cute d. T he n the mo dule ent e rs the power

down mode, only the RTC is still active. The power down mode can also be indicated by the

M50_HD_V2.0 - 34 -

Figure 9: Timing of turning off the module

NORMAL POWER DOWN

M50 Hardware Design

Quecctel

Confidential

STATUS pin, which is a low level voltage in this mode.

3.4.2.2. Power d own m odule using AT comm and

Customer’s application can turn off the module via AT command “AT+QPOWD=1”. This

command will let the module to log off from the network and allow the firmware to save

impo rtant dat a be fo re c omplete ly dis c on necti n g the po w e r supply, thus it is a safe wa y.

Before t he compl etion o f the power down proce dure t he module s ends out the result code shown

below:

NORMAL POWER DOWN

Afte r that m oment, n o furthe r AT com mands c an be exe cuted. And t hen the module enter s the

power down mode, onl y the RTC is still active. The power down mo de can al so be i ndi cate d by

STATUS pin, which is a low level voltage in this mode.

Please refer to the document [1] for d e tail s ab ou t the AT command “AT+QPOWD”.

3.4.2.3. Over-voltage or under-voltage automatic shutdown

The m odul e will c onst ant ly m on ito r the v olt age ap plied o n the V BAT, if t he volt a ge i s ≤ 3.5V,

the followi n g UR C wil l be prese n t e d:

UNDER_VOL TAGE WARNING

If the voltage is ≥ 4.5V, the followi n g URC will be presented:

OVER_VOL TAGE WARNING

The normal input voltage range is from 3.3V to 4.6V. If the voltage is > 4.6V or < 3.3V, t he

mod ule would automatically shutdown itself.

If the voltage is < 3.3V, the following URC will be presented:

UNDER_V OLTAGE POWER DOWN

If the voltage is > 4.6V, the following URC will be presented:

OVE R_VOLTAGE POWER DOWN

Note: These re sult cod e s do not appear when autobauding is active and DTE a nd DCE are not

M50_HD_V2.0 - 35 -

M50 Hardware Design

Emergency

shutdown pulse

EMERG_OFF

4.7K

47K

S2

EMERG_OFF

TVS2

Close to S2

Quecctel

Confidential

correctly synchronized after start-up. The module is recommended to set to a fixed baud rate.

Afte r that moment , no f u rt her AT commands c an be execut ed. T he mo dule logs o ff f rom netwo rk

and e nters power down m ode, an d only RT C is still active . The power down mode can also be

indicated by the pin STATUS, which is a low level voltage in this mode.

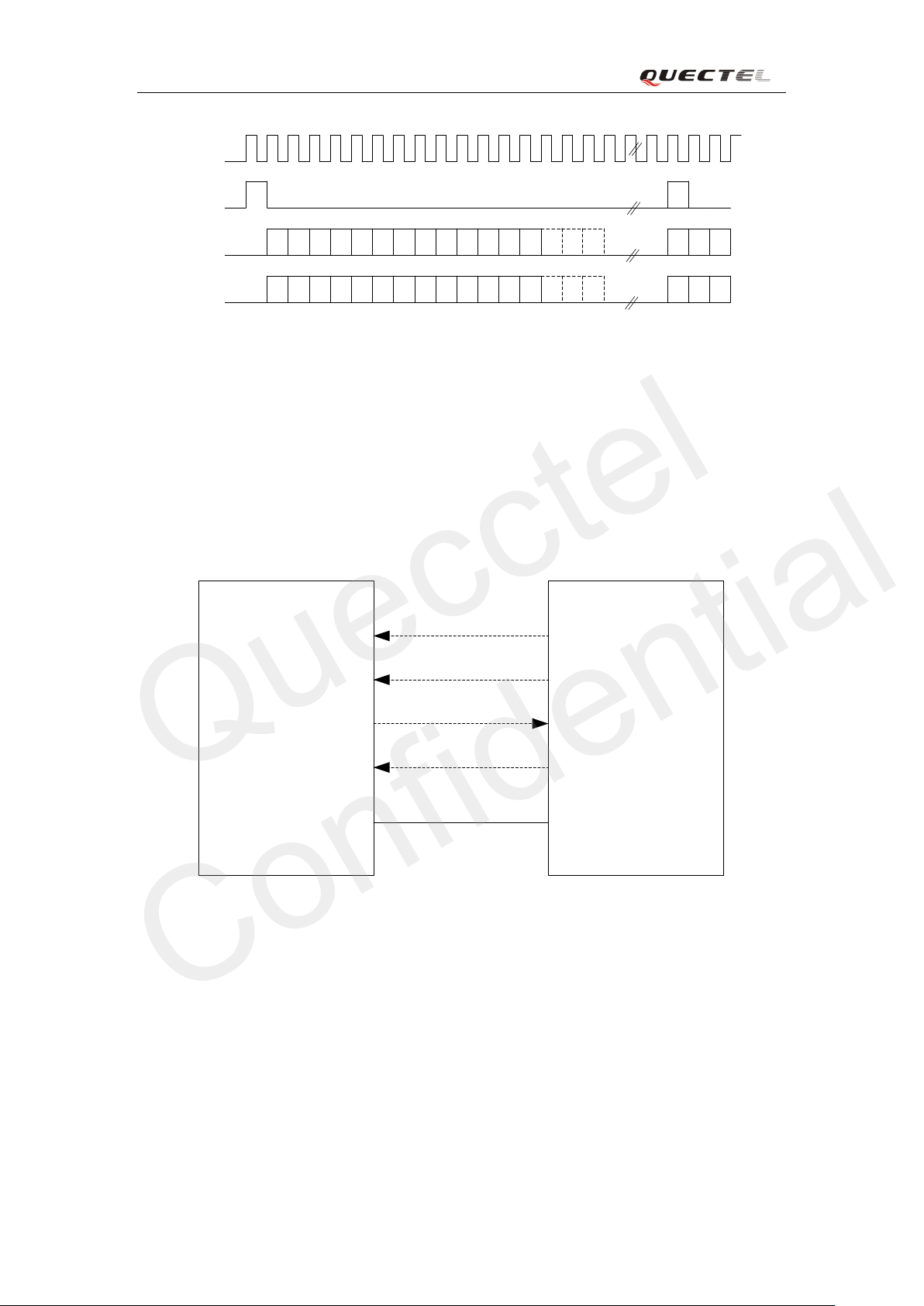

3.4.2.4. Emergency shutdown using EMERG_OFF pin

The mo dul e c an be s hut down by d riving the pin EMERG_OFF to a low level volta ge ove r 20 ms

and then rele asin g it. The EMERG_OFF li ne c a n be d ri ve n by an open-drain/colle ctor d river or a

button. T he cir c uit is illustrated as the following figures.

3.4.3. Restart

Figure 10: Reference circuit for EMERG_OFF by using driving circuit

Figure 11:

Referen ce ci rcuit for EMERG_OFF by using button

Customer’s appl icatio n can re start t he mod ul e by dr i ving the P WRKEY to a low level volt a ge f o r

a certa in ti me, whi ch is simi l ar to t he way o f tu rnin g on m od ule. Bef ore rest arti n g the modul e , at

M50_HD_V2.0 - 36 -

M50 Hardware Design

PWRKEY

(INPUT)

STATUS

(OUTPUT)

Delay >0.5s

Turn off

Restart

Pull down the PWRKEY

to turn on the module

EMERG_OFF

(INPUT)

STATUS

(OUTPUT)

Delay >2s

6us

Pulldown >20ms

PWRKEY

(INPUT)

Quecctel

Confidential

least 500ms should be delayed after detecting the low level of STATUS. The restart timing is

illustrated as the following figure.

Figure 12:

The mod ul e c a n al s o be restarted by the P WR KE Y after emerg ency shu tdown.

Figure 13: Timing of restarting system after emergency shutdown

Timing of restarting system

M50_HD_V2.0 - 37 -

M50 Hardware Design

Quecctel

Confidential

3.5. Charge interface

M50 provides charging function for rechargeable Li-Ion or Lithium Polymer battery. It is

introduced simply in this document. If customer wants to get more i nformati on about c harging ,

please re fe r t o the document [13] .

Table 8: Pin definition of the charging

Name Pin I/O Description.

GATDRV 74 O Charge dri ving

CHGLDO 73 I Charger power supply source

CHGDET 72 I Charger detection

ISENSE 71 I Cu rrent s e n s e

BAT SN S 70 I VBAT voltage sense

3.6. Power saving

Upon system requirement, there are several actions to drive the module to enter low current

consumption status. For example, “AT+CFUN” can be used to set module into minimum

functionality mode and DTR hardware interface signal can be used to lead system to SLEEP

mode.

3.6.1. Minimum functionality mode

Minim um functi onalit y mode red uces the fu nction ality of the module to a minim um level, th us

minimize the current consumption when the slow clocking mode is activated at the same time.

This m ode is set with the “AT +CFUN ” com mand whi ch p rovide s the ch oice o f the fun ctiona lit y

level s <f un>=0, 1, 4.

0: mi nimum functionality

1: full functionality (default)

4: disable both transmitting and receiving of RF part

If the mod ule is set t o minim um fun ctional ity b y “AT+CF UN=0” , the RF fun ctio n and SIM c ard

funct ion wo ul d be dis abl ed. In thi s case , t he U ART po rt i s s till accessible, but all AT commands

correlative with RF function or SIM card function will be not accessible.

If the mod ule has bee n set by “AT+ CFUN =4” , t he R F f un ct i o n will be di sable d, the UART port i s

still active. In this case, all AT commands correlative with RF function will be not accessible.

After the module is set by “AT+CFUN=0” or “A T+CFUN=4”, it can return to full functionality by

M50_HD_V2.0 - 38 -

M50 Hardware Design

Quecctel

Confidential

“AT+CFUN=1”.

For detailed information about “AT+CFUN”, please refer to the docum e nt [1].

3.6.2. SLEEP mode

The SLEEP mode is disabled in default firmware configuration. Customer’s application can

enable t his mode b y “AT + QSCL K=1” . On the othe r h and, t he def ault sett i ng is “AT +QS C LK= 0”

and in this mode, the module cannot enter SLEEP mode.

When “AT +QSC LK=1” is se nt t o the m odule , cust ome r’s appl icati on ca n cont rol t he m odule t o

enter or exit f rom the SLEEP mo de throu gh pin DTR. Whe n D TR is se t to high l evel, and t here is

no on-ai r or hardw are inte rrupt su ch as GPI O inter rupt or dat a on UART port, the mo dule will

enter SLEE P mo de au t o m atically. In thi s mode, t he modu le can st il l rece ive voice , SMS o r G PRS

paging from network but the UART port is not accessible.

3.6.3. Wake up module from SLEEP mode

When the module is in the SLEEP m ode , the followi ng metho ds c a n wa ke up the modu l e.

If the D TR P in is set lo w, it wo uld wa ke u p the mo dul e fro m the SLE EP mo de. The UA RT

port will be active within 20ms after DTR is changed to low level.

Receive a voice or data call from network wakes up module.

Receive an SMS from network wakes up module.

Note: DTR pin should be held at low level during communication between the module and

DTE.

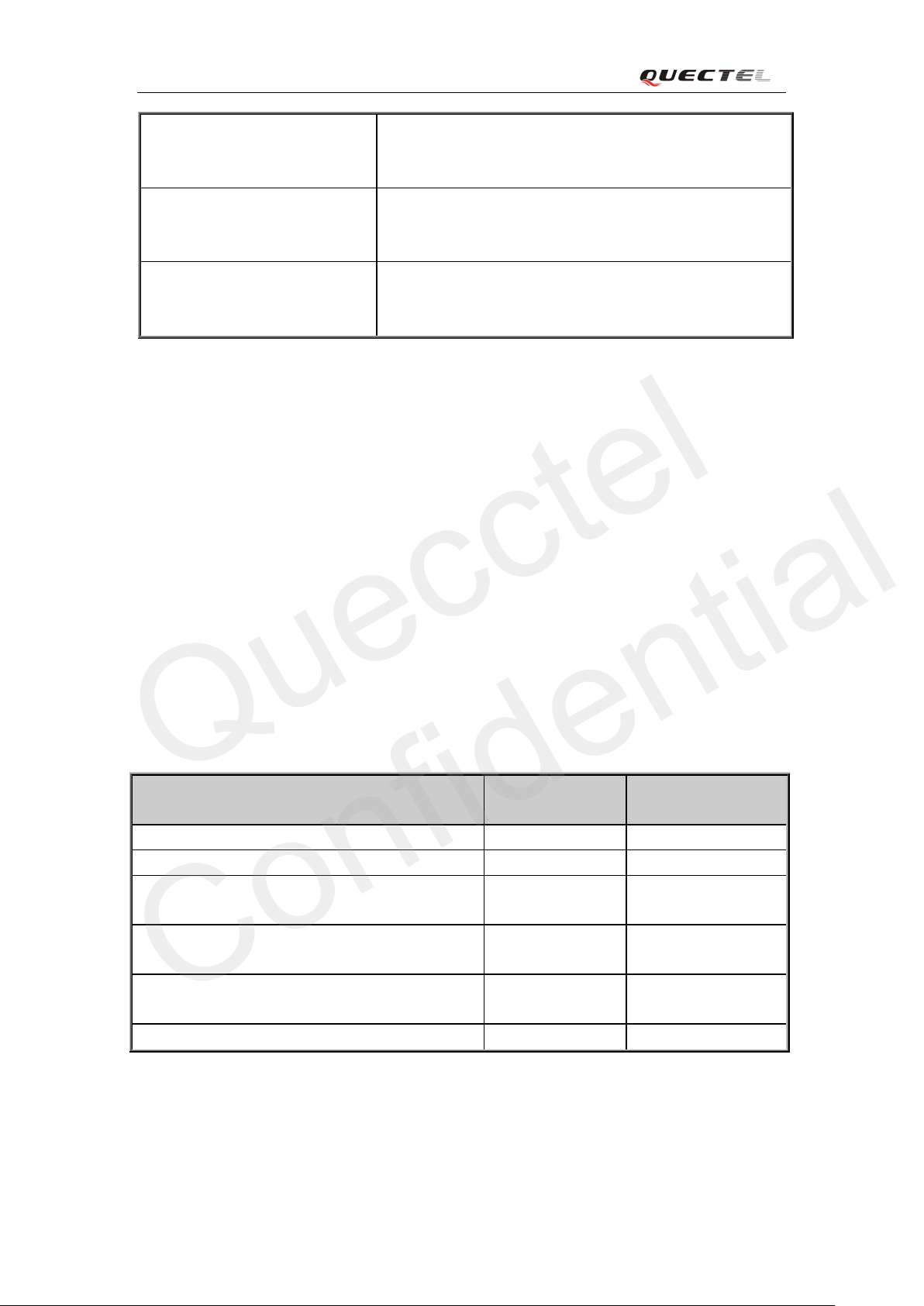

3.7. Summary of state transition

Table 9: Summary of state trans i tion

Current mode Next mode

Power down N or m al mode SLEEP mode

Power down Use PWRKEY

Norm al m ode AT+QPOWD, use

SLEEP mode Use PWRKEY pin, or

PWRKEY pi n , or use

EM ERG_OFF p in

use EMERG_OFF pin

Use AT command

Pull DTR down or

incoming call or

SMS or GPRS

“AT+QSCLK=1” and pull

DTR up

M50_HD_V2.0 - 39 -

M50 Hardware Design

Module

RTC Core

1.5K

VRTC

Non-chargeable

Backup Battery

VRTC

Rechargeable

Backup Battery

Module

RTC Core

1.5K

VRTC

Large Capacitance

Capacitor

Module

RTC Core

1.5K

Quecctel

Confidential

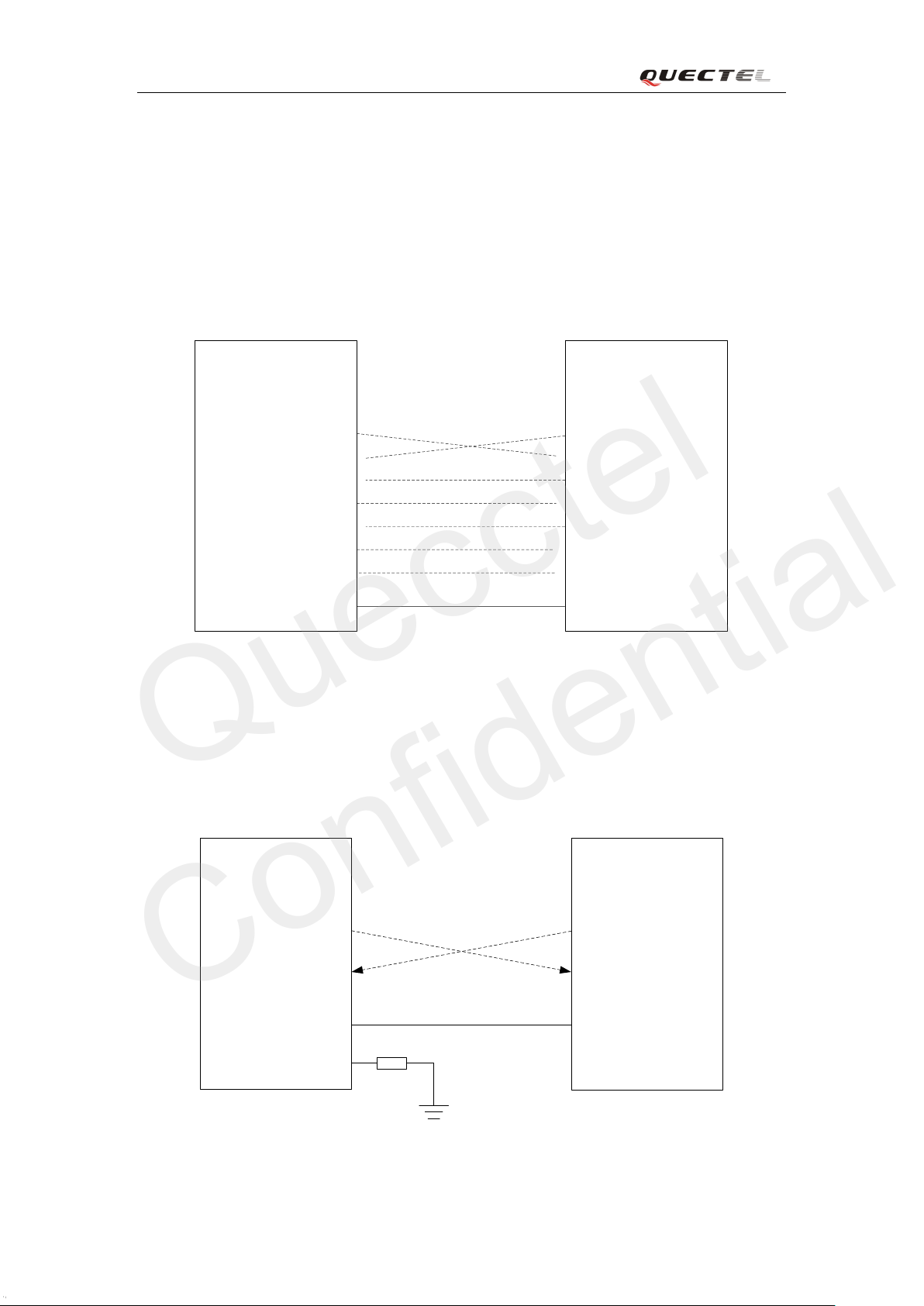

3.8. RTC backup

The RT C (Real Time Clock) can be supplied by an external capacitor or battery (rechargeable or

non-chargeable) through the pin VRT C. A 1.5K resistor has been integrated in the module for

current limiting. A coin-cell battery or a super-cap can be use d to ba ckup powe r supply for RTC .

The following figures show various sample circuits for RTC backup.

Figure 14:

Figure 15: RTC supply from rechargeable battery

RTC supply from non-chargeable battery

Figure 16:

M50_HD_V2.0 - 40 -

RTC supply from capacitor

M50 Hardware Design

Quecctel

Confidential

Coin-type rechargeable capacitor such as XH414H-IV 01E f rom Seiko can be used.

Figure 17: Seiko X H414H-IV01E Charge Characteristic s

3.9. Serial interfaces

The mo dule p rovide s three serial ports: UART Port, Debug Port and Auxiliary UART Port. The

module is designed as a DCE (Data Communication Equipment), following the traditional

DCE-DTE ( D ata Te rminal E q uipme nt) conne ction. Aut o baudin g function support s baud rate from

4800bps to 115200bps.

The UART Port:

TXD: Send data to RXD of DTE.

RX D: Re cei ve dat a f r om TXD of DTE.

RTS: Request to send.

CTS: Clear to send.

DTR: DTE is ready and inform DCE ( t hi s pin can w ake t he module up).

RI: Ring indicator (when t he call, SMS, data of the module are coming, the module will

output signal to inform DTE).

DCD: D ata carrier detection (the v alidity of t his pin demonstrates t he communication link is

set up).

Note: The module disables hardware flow control by default. When hardware flow control is

required, RTS and CTS should be connected to the host. AT c ommand “AT+IFC=2,2” is used to

enable hardware flow control. AT command “AT+IFC=0,0” is used to disable the hardware

flow control. For more det ails, please refer to the docum e nt [1].

M50_HD_V2.0 - 41 -

M50 Hardware Design

Quecctel

Confidential

The Debug Port

DBG_TXD: Send data to the COM port of computer.

DBG_RXD : R e cei ve dat a fro m t h e COM port of computer.

The Auxiliary UART Port

TXD_AUX: Send data to the RXD of DTE.

RXD_AUX: Receive data from the TXD of DTE.

The logic levels are described in the following table.

Table 10: Logic lev els of the UART interfaces

Parameter Min Max Unit

VIL 0 0.25×VDD_EXT V

VIH 0.75×VDD_EXT VDD_EXT +0.3 V

VOL 0.15×VDD_EXT V

VOH 0.85×VDD_EXT V

Table 11: Pin definition of the UART interfaces