Page 1

UG96 Hardware Design

UMTS/HSPA Module Series

Rev. UG96_Hardware_Design_FCC

Date: 2015-07-20

www.quectel.com

Page 2

UMTS/HSPA Module Series

UG96 Hardware Design

Our aim is to provide customers with timely and comprehensive service. For any

assistance, please contact our company headquarters:

Quectel Wireless Solutions Co., Ltd.

Office 501, Building 13, No.99, Tianzhou Road, Shanghai, China, 200233

Tel: +86 21 5108 6236

Mail: info@quectel.com

Or our local office, for more information, please visit:

http://www.quectel.com/support/salesupport.aspx

For technical support, to report documentation errors, please visit:

http://www.quectel.com/support/techsupport.aspx

Or Email: Support@quectel.com

GENERAL NOTES

QUECTEL OFFERS THIS INFORMATION AS A SERVICE TO ITS CUSTOMERS. THE INFORMATION

PROVIDED IS BASED UPON CUSTOMERS’ REQUIREMENTS. QUECTEL MAKES EVERY EFFORT

TO ENSURE THE QUALITY OF THE INFORMATION IT MAKES AVAILABLE. QUECTEL DOES NOT

MAKE ANY WARRANTY AS TO THE INFORMATION CONTAINED HEREIN, AND DOES NOT ACCEPT

ANY LIABILITY FOR ANY INJURY, LOSS OR DAMAGE OF ANY KIND INCURRED BY USE OF OR

RELIANCE UPON THE INFORMATION. THE INFORMATION SUPPLIED HEREIN IS SUBJECT TO

CHANGE WITHOUT PRIOR NOTICE.

COPYRIGHT

THIS INFORMATION CONTAINED HERE IS PROPRIETARY TECHNICAL INFORMATION OF

QUECTEL CO., LTD. TRANSMITTABLE, REPRODUCTION, DISSEMINATION AND EDITING OF THIS

DOCUMENT AS WELL AS UTILIZATION OF THIS CONTENTS ARE FORBIDDEN WITHOUT

PERMISSION. OFFENDERS WILL BE HELD LIABLE FOR PAYMENT OF DAMAGES. ALL RIGHTS

ARE RESERVED IN THE EVENT OF A PATENT GRANT OR REGISTRATION OF A UTILITY MODEL

OR DESIGN.

Copyright © Quectel Wireless Solutions Co., Ltd. 2015. All rights reserved.

UG96_Hardware_Design Confidential / Released 1 / 75

Page 3

UMTS/HSPA Module Series

Revision

Date

Author

Description

1.0

2015-02-28

Tony GAO/

Cat WANG

Initial

UG96 Hardware Design

About the Document

History

UG96_Hardware_Design Confidential / Released 2 / 75

Page 4

UMTS/HSPA Module Series

UG96 Hardware Design

Contents

About the Document ................................................................................................................................... 2

Contents ....................................................................................................................................................... 3

Table Index ................................................................................................................................................... 5

Figure Index ................................................................................................................................................. 6

1 Introduction .......................................................................................................................................... 8

1.1. Safety Information...................................................................................................................... 9

2 Product Concept ................................................................................................................................ 10

2.1. General Description ................................................................................................................. 10

2.2. Directives and Standards ........................................................................................................ 11

2.3. Key Features ........................................................................................................................... 11

2.4. Functional Diagram ................................................................................................................. 13

2.5. Evaluation Board ..................................................................................................................... 15

3 Application Interface ......................................................................................................................... 16

3.1. General Description ................................................................................................................. 16

3.2. Pin Assignment ........................................................................................................................ 17

3.3. Pin Description ......................................................................................................................... 18

3.4. Operating Modes ..................................................................................................................... 23

3.5. Power Saving ........................................................................................................................... 24

3.5.1. Sleep Mode .................................................................................................................... 24

3.5.1.1. UART Application ................................................................................................. 24

3.5.1.2. USB Application with Suspend Function ............................................................. 25

3.5.1.3. USB Application without Suspend Function ........................................................ 26

3.5.2. Minimum Functionality Mode ......................................................................................... 27

3.6. Power Supply ........................................................................................................................... 27

3.6.1. Power Supply Pins ......................................................................................................... 27

3.6.2. Decrease Voltage Drop .................................................................................................. 28

3.6.3. Reference Design for Power Supply .............................................................................. 29

3.6.4. Monitor the Power Supply .............................................................................................. 30

3.7. Turn on and off Scenarios ....................................................................................................... 30

3.7.1. Turn on Module .............................................................................................................. 30

3.7.2. Turn off Module .............................................................................................................. 32

3.7.2.1. Turn off Module Using AT Command ................................................................... 32

3.7.2.2. Emergency Shutdown .......................................................................................... 33

3.7.2.3. Automatic Shutdown ............................................................................................ 35

3.8. Reset the Module..................................................................................................................... 35

3.9. RTC Interface .......................................................................................................................... 37

3.10. UART Interface ........................................................................................................................ 38

3.11. USIM Card Interface ................................................................................................................ 40

UG96_Hardware_Design Confidential / Released 3 / 75

Page 5

UMTS/HSPA Module Series

UG96 Hardware Design

3.12. USB Interface .......................................................................................................................... 42

3.13. PCM and I2C Interface ............................................................................................................ 44

3.14. Network Status Indication ........................................................................................................ 47

3.15. Operating Status Indication ..................................................................................................... 48

4 Antenna Interface ............................................................................................................................... 49

4.1. GSM/UMTS Antenna Interface ................................................................................................ 49

4.1.1. Pin Definition .................................................................................................................. 49

4.1.2. Operating Frequency ..................................................................................................... 49

4.1.3. Reference Design .......................................................................................................... 50

4.2. Antenna Installation ................................................................................................................. 51

4.2.1. Antenna Requirement .................................................................................................... 51

4.2.2. Install the Antenna with RF Connector .......................................................................... 51

5 Electrical, Reliability and Radio Characteristics ............................................................................ 54

5.1. Absolute Maximum Ratings ..................................................................................................... 54

5.2. Power Supply Ratings ............................................................................................................. 54

5.3. Operating Temperature ............................................................................................................ 55

5.4. Current Consumption .............................................................................................................. 55

5.5. RF Output Power ..................................................................................................................... 59

5.6. RF Receiving Sensitivity .......................................................................................................... 60

5.7. Electrostatic Discharge ............................................................................................................ 60

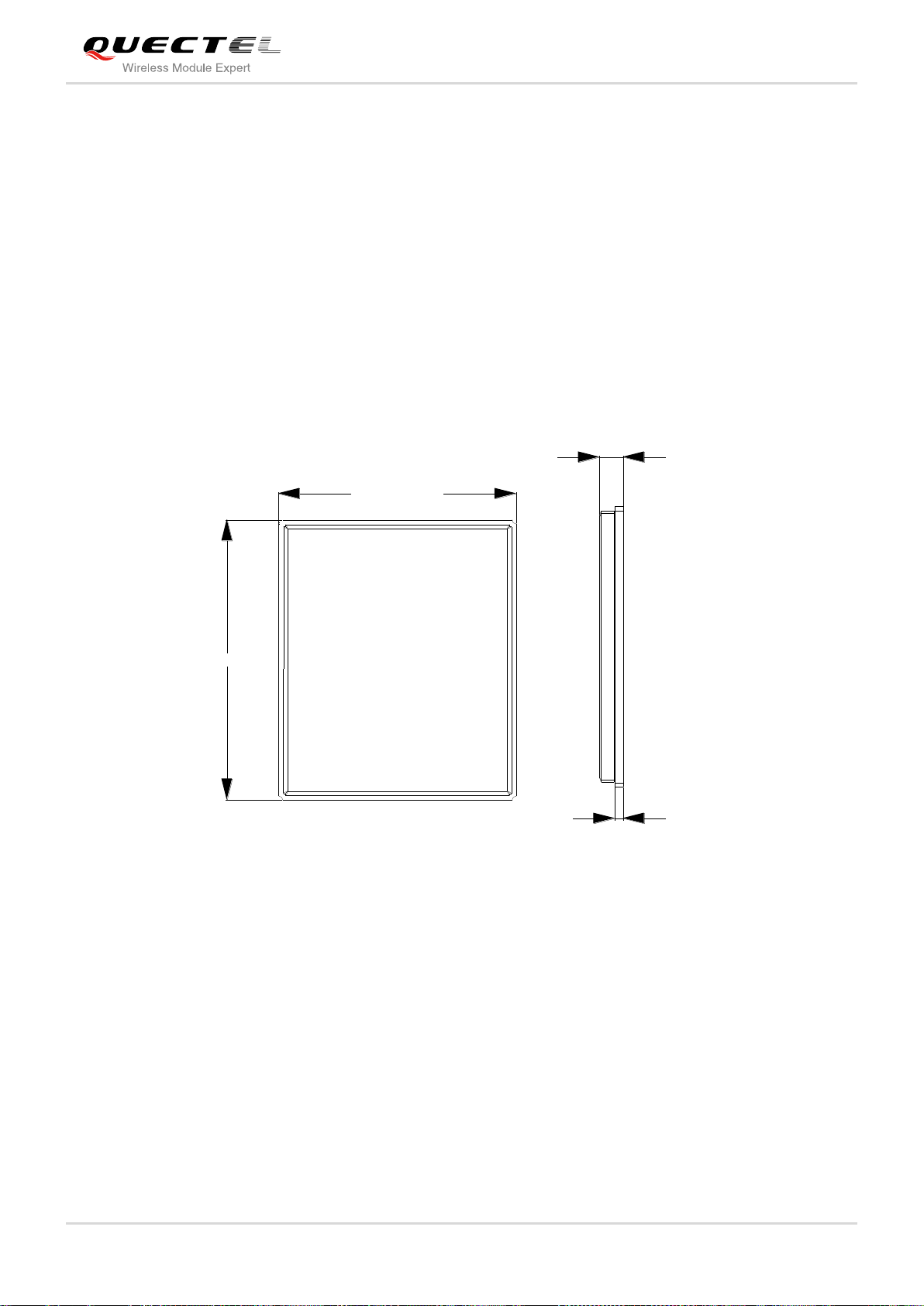

6 Mechanical Dimensions .................................................................................................................... 61

6.1. Mechanical Dimensions of the Module.................................................................................... 61

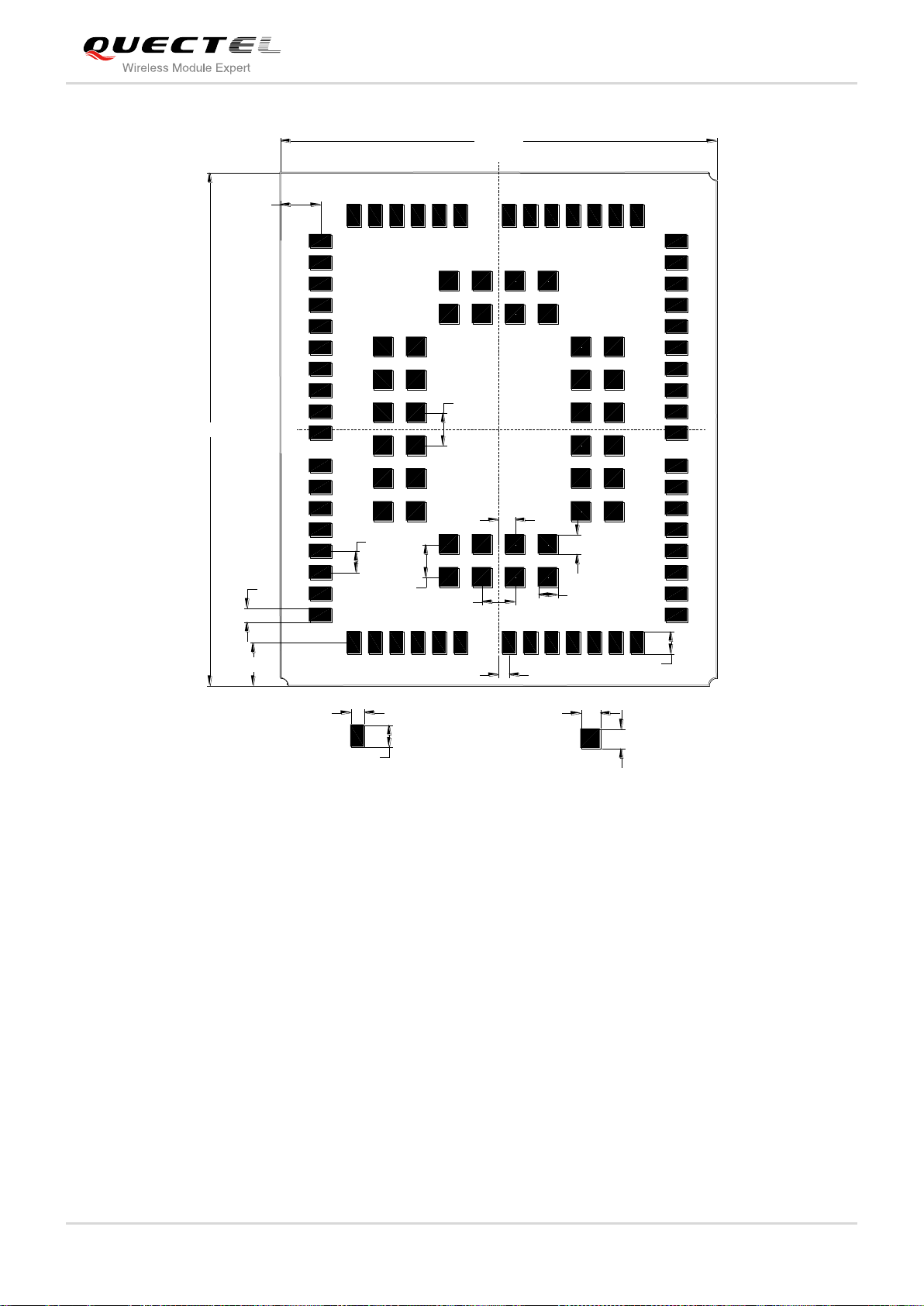

6.2. Footprint of Recommendation ................................................................................................. 63

6.3. Top View of the Module ........................................................................................................... 65

6.4. Bottom View of the Module ...................................................................................................... 65

7 Storage and Manufacturing .............................................................................................................. 66

7.1. Storage..................................................................................................................................... 66

7.2. Manufacturing and Welding ..................................................................................................... 66

7.3. Packaging ................................................................................................................................ 68

8 Appendix A Reference ....................................................................................................................... 70

9 Appendix B GPRS Coding Scheme ................................................................................................. 74

10 Appendix C GPRS Multi-slot Class .................................................................................................. 75

11 Appendix D EDGE Modulation and Coding Scheme ..................................................................... 76

UG96_Hardware_Design Confidential / Released 4 / 75

Page 6

UMTS/HSPA Module Series

UG96 Hardware Design

Table Index

TABLE 1: FREQUENCY BANDS OF UG96 MODULE...................................................................................... 10

TABLE 2: UG96 KEY FEATURES ...................................................................................................................... 11

TABLE 3: IO PARAMETERS DEFINITION ........................................................................................................ 18

TABLE 4: PIN DESCRIPTION ........................................................................................................................... 18

TABLE 5: OVERVIEW OF OPERATING MODES ............................................................................................. 23

TABLE 6: VBAT AND GND PINS ....................................................................................................................... 27

TABLE 7: PWRKEY PIN DESCRIPTION .......................................................................................................... 30

TABLE 8: PWRDWN_N PIN DESCRIPTION .................................................................................................... 33

TABLE 9: RESET_N PIN DESCRIPTION ......................................................................................................... 35

TABLE 10: PIN DEFINITION OF THE MAIN UART INTERFACE ..................................................................... 38

TABLE 11: LOGIC LEVELS OF DIGITAL I/O .................................................................................................... 38

TABLE 12: PIN DEFINITION OF THE USIM INTERFACE ............................................................................... 41

TABLE 13: USB PIN DESCRIPTION ................................................................................................................ 43

TABLE 14: PIN DEFINITION OF PCM AND I2C INTERFACE .......................................................................... 45

TABLE 15: PIN DEFINITION OF NETWORK INDICATOR ............................................................................... 47

TABLE 16: WORKING STATE OF THE NETWORK INDICATOR..................................................................... 47

TABLE 17: PIN DEFINITION OF STATUS ........................................................................................................ 48

TABLE 18: PIN DEFINITION OF THE RF ANTENNA ....................................................................................... 49

TABLE 19: THE MODULE OPERATING FREQUENCIES ................................................................................ 49

TABLE 20: ANTENNA CABLE REQUIREMENTS ............................................................................................. 51

TABLE 21: ANTENNA REQUIREMENTS .......................................................................................................... 51

TABLE 22: ABSOLUTE MAXIMUM RATINGS .................................................................................................. 54

TABLE 23: THE MODULE POWER SUPPLY RATINGS .................................................................................. 54

TABLE 24: OPERATING TEMPERATURE ........................................................................................................ 55

TABLE 25: THE MODULE CURRENT CONSUMPTION .................................................................................. 55

TABLE 26: CONDUCTED RF OUTPUT POWER EDGE .................................................................................. 59

TABLE 27: CONDUCTED RF RECEIVING SENSITIVITY ................................................................................ 60

TABLE 28: REEL PACKING .............................................................................................................................. 69

TABLE 29: RELATED DOCUMENTS ................................................................................................................ 70

TABLE 30: TERMS AND ABBREVIATIONS ...................................................................................................... 70

TABLE 31: DESCRIPTION OF DIFFERENT CODING SCHEMES .................................................................. 74

TABLE 32: GPRS MULTI-SLOT CLASSES ...................................................................................................... 75

TABLE 33: EDGE MODULATION AND CODING SCHEME ............................................................................. 76

UG96_Hardware_Design Confidential / Released 5 / 75

Page 7

UMTS/HSPA Module Series

UG96 Hardware Design

Figure Index

FIGURE 1: FUNCTIONAL DIAGRAM ............................................................................................................... 15

FIGURE 2: PIN ASSIGNMENT (TOP VIEW) .................................................................................................... 17

FIGURE 3: UART SLEEP APPLICATION ......................................................................................................... 25

FIGURE 4: USB APPLICATION WITH SUSPEND FUNCTION ........................................................................ 26

FIGURE 5: USB SLEEP APPLICATION WITHOUT SUSPEND FUNCTION .................................................... 26

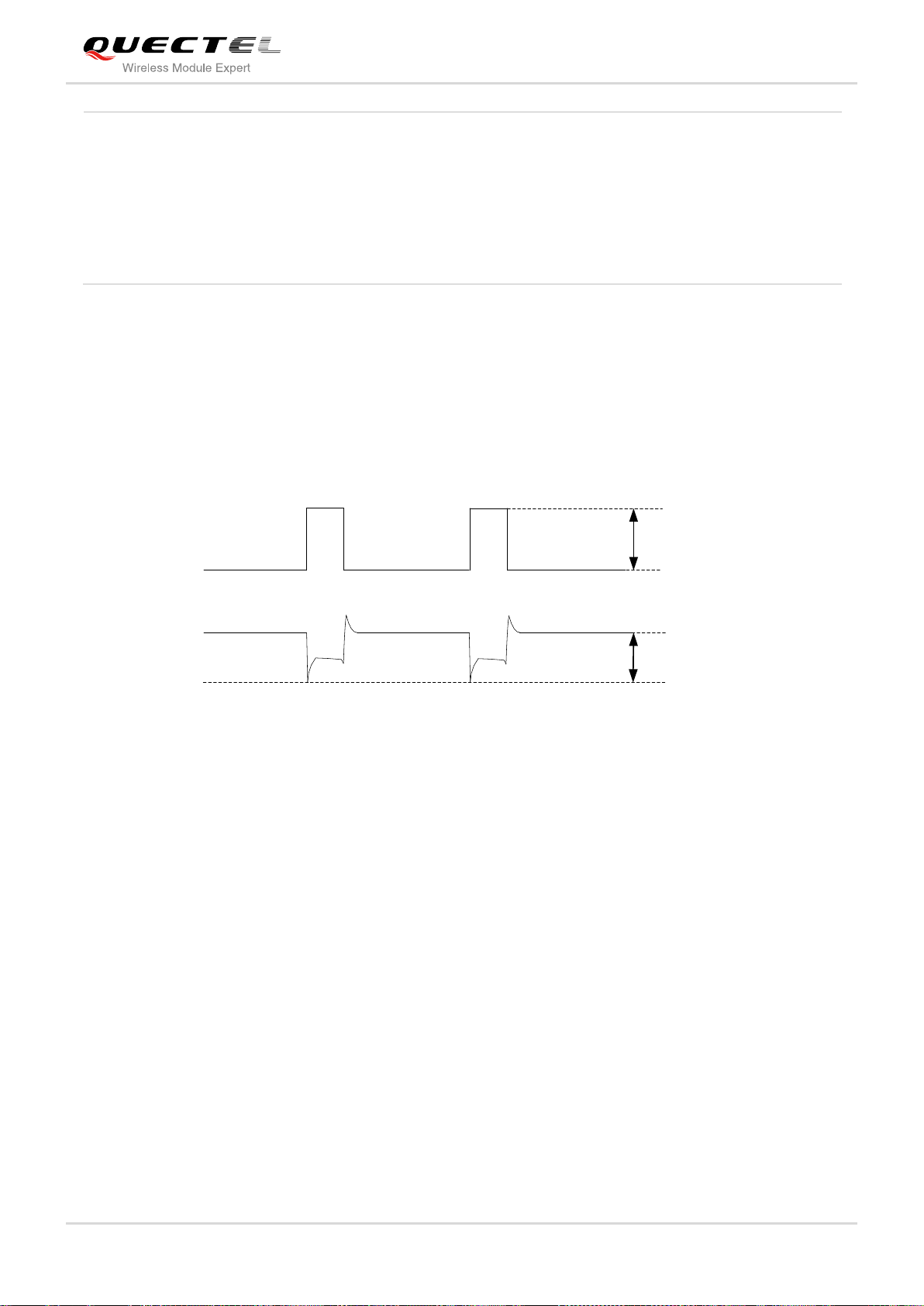

FIGURE 6: VOLTAGE DROP DURING TRANSMITTING BURST .................................................................... 28

FIGURE 7: STAR STRUCTURE OF THE POWER SUPPLY............................................................................ 29

FIGURE 8: REFERENCE CIRCUIT OF POWER SUPPLY .............................................................................. 29

FIGURE 9: TURN ON THE MODULE USING DRIVING CIRCUIT ................................................................... 30

FIGURE 10: TURN ON THE MODULE USING KEYSTROKE ......................................................................... 31

FIGURE 11: TIMING OF TURNING ON MODULE ........................................................................................... 31

FIGURE 12: TIMING OF TURNING OFF THROUGH AT COMMAND ............................................................. 32

FIGURE 13: TURN OFF THE MODULE USING DRIVING CIRCUIT ............................................................... 33

FIGURE 14: TURN OFF THE MODULE USING KEYSTROKE ........................................................................ 34

FIGURE 15: TIMING OF EMERGENCY SHUTDOWN ..................................................................................... 34

FIGURE 16: REFERENCE CIRCUIT OF RESET_N BY USING DRIVING CIRCUIT ...................................... 36

FIGURE 17: REFERENCE CIRCUIT OF RESET_N BY USING BUTTON ...................................................... 36

FIGURE 18: TIMING OF RESETTING MODULE ............................................................................................. 36

FIGURE 19: RTC SUPPLY FROM CAPACITOR .............................................................................................. 37

FIGURE 20: REFERENCE CIRCUIT OF LOGIC LEVEL TRANSLATOR ......................................................... 39

FIGURE 21: REFERENCE CIRCUIT WITH TRANSISTOR CIRCUIT .............................................................. 39

FIGURE 22: RS232 LEVEL MATCH CIRCUIT .................................................................................................. 40

FIGURE 23: REFERENCE CIRCUIT OF THE 8-PIN USIM CARD .................................................................. 41

FIGURE 24: REFERENCE CIRCUIT OF THE 6-PIN USIM CARD .................................................................. 42

FIGURE 25: REFERENCE CIRCUIT OF USB APPLICATION ......................................................................... 43

FIGURE 26: TEST POINTS OF FIRMWARE UPGRADE ................................................................................. 44

FIGURE 27: PCM MASTER MODE TIMING ..................................................................................................... 45

FIGURE 28: REFERENCE CIRCUIT OF PCM APPLICATION WITH AUDIO CODEC .................................... 46

FIGURE 29: REFERENCE CIRCUIT OF THE NETLIGHT ............................................................................... 47

FIGURE 30: REFERENCE CIRCUIT OF THE STATUS ................................................................................... 48

FIGURE 31: REFERENCE CIRCUIT OF ANTENNA INTERFACE ................................................................... 50

FIGURE 32: DIMENSIONS OF THE UF.L-R-SMT CONNECTOR (UNIT: MM) ................................................ 52

FIGURE 33: MECHANICALS OF UF.L-LP CONNECTORS (UNIT: MM) .......................................................... 52

FIGURE 34: SPACE FACTOR OF MATED CONNECTOR (UNIT: MM) ........................................................... 53

FIGURE 35: UG96 TOP AND SIDE DIMENSIONS ........................................................................................... 61

FIGURE 36: UG96 BOTTOM DIMENSION (TOP VIEW) .................................................................................. 62

FIGURE 37: RECOMMENDED FOOTPRINT (TOP VIEW) .............................................................................. 63

FIGURE 38: RECOMMENDED STENCIL OF UG96 (TOP VIEW) ................................................................... 64

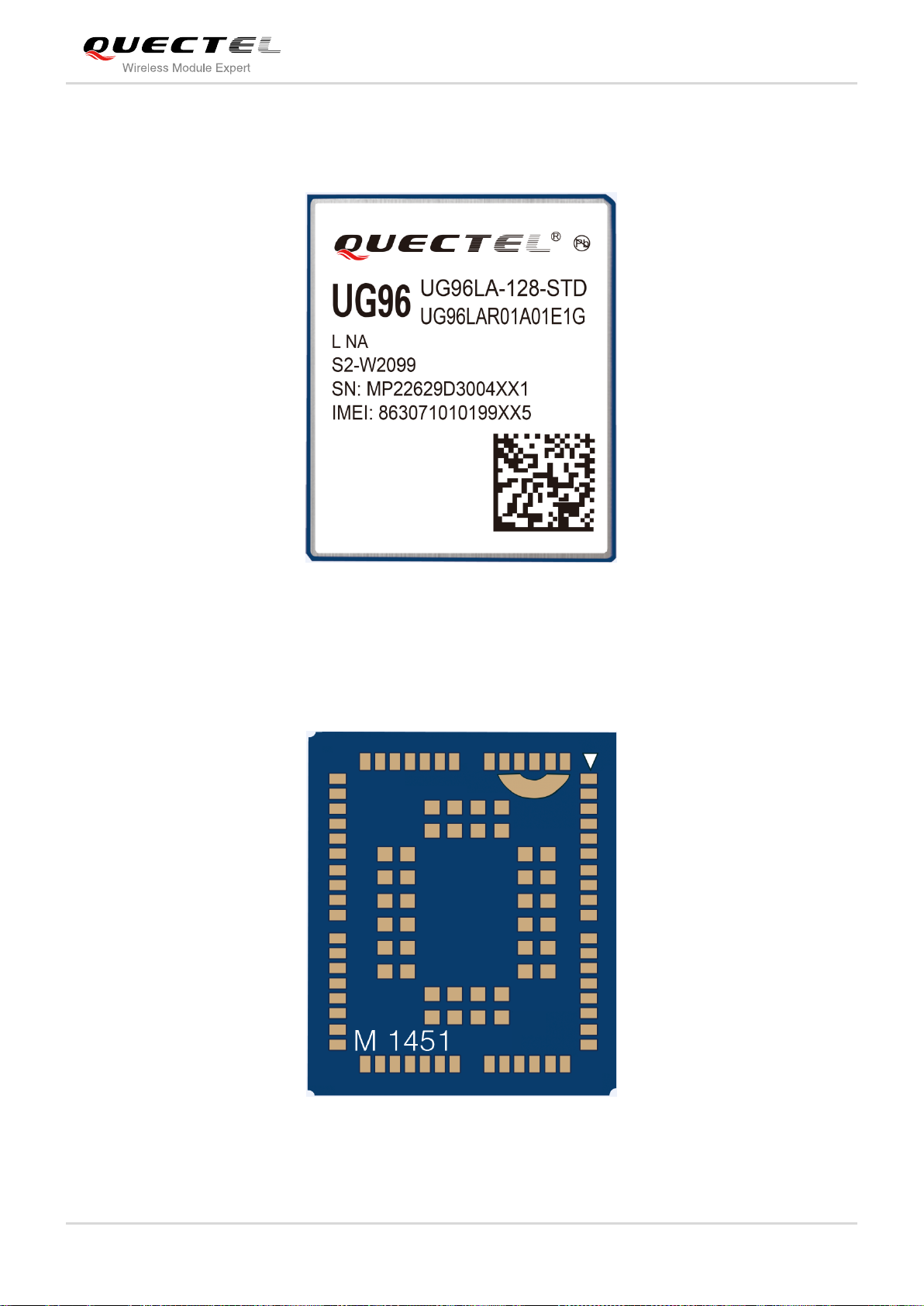

FIGURE 39: TOP VIEW OF THE MODULE ...................................................................................................... 65

FIGURE 40: BOTTOM VIEW OF THE MODULE .............................................................................................. 65

FIGURE 41: REFLOW SOLDERING PROFILE ................................................................................................ 67

UG96_Hardware_Design Confidential / Released 6 / 75

Page 8

UMTS/HSPA Module Series

UG96 Hardware Design

FIGURE 42: TAPE AND REEL SPECIFICATION .............................................................................................. 68

FIGURE 43: DIMENSIONS OF REEL ............................................................................................................... 69

UG96_Hardware_Design Confidential / Released 7 / 75

Page 9

UMTS/HSPA Module Series

UG96 Hardware Design

1 Introduction

This document defines the UG96 module and describes its hardware interface which are connected with

your application and the air interface.

This document can help you quickly understand module interface specifications, electrical and

mechanical details. Associated with application notes and user guide, you can use UG96 module to

design and set up mobile applications easily.

UG96_Hardware_Design Confidential / Released 8 / 75

Page 10

UMTS/HSPA Module Series

Full attention must be given to driving at all times in order to reduce the risk of an

accident. Using a mobile while driving (even with a handsfree kit) cause distraction

and can lead to an accident. You must comply with laws and regulations restricting

the use of wireless devices while driving.

Switch off the cellular terminal or mobile before boarding an aircraft. Make sure it

switched off. The operation of wireless appliances in an aircraft is forbidden to

prevent interference with communication systems. Consult the airline staff about

the use of wireless devices on boarding the aircraft, if your device offers a Airplane

Mode which must be enabled prior to boarding an aircraft.

Switch off your wireless device when in hospitals or clinics or other health care

facilities. These requests are desinged to prevent possible interference with

sentitive medical equipment.

Cellular terminals or mobiles operate over radio frequency signal and cellular

network and cannot be guaranteed to connect in all conditions, for example no

mobile fee or an invalid SIM card. While you are in this condition and need

emergent help, please remember using emergency call. In order to make or

receive call, the cellular terminal or mobile must be switched on and in a service

area with adequate cellular signal strength.

Your cellular terminal or mobile contains a transmitter and receiver. When it is ON ,

it receives and transmits radio frequency energy. RF interference can occur if it is

used close to TV set, radio, computer or other electric equipment.

In locations with potencially explosive atmospheres, obey all posted signs to turn

off wireless devices such as your phone or other cellular terminals. Areas with

potencially exposive atmospheres including fuelling areas, below decks on boats,

fuel or chemical transfer or storage facilities, areas where the air contains

chemicals or particles such as grain, dust or metal powders.

UG96 Hardware Design

1.1. Safety Information

The following safety precautions must be observed during all phases of the operation, such as usage,

service or repair of any cellular terminal or mobile incorporating UG96 module. Manufacturers of the cellular

terminal should send the following safety information to users and operating personnel and to incorporate

these guidelines into all manuals supplied with the product. If not so, Quectel does not take on any liability

for customer failure to comply with these precautions.

UG96_Hardware_Design Confidential / Released 9 / 75

Page 11

UMTS/HSPA Module Series

Module

GSM

850

EGSM

900

DCS

1800

PCS

1900

UMTS

800

UMTS

850

UMTS

900

UMTS

1900

UMTS

2100

UG96

√ √ √ √ √ √ √ √ √

1)

UG96 module includes Data-only and Telematics versions. Data-only version does not support voice

function, Telematics version supports it.

NOTE

UG96 Hardware Design

2 Product Concept

2.1. General Description

UG96 module is an embedded 3G wireless communication module, supports GSM/GPRS/EDGE and

UMTS/HSDPA/HSUPA networks. It can also provide voice functionality1) for your specific application.

UG96 offers a maximum data rate of 7.2Mbps on downlink and 5.76Mbps on uplink in HSPA mode.

GPRS supports the coding schemes CS-1, CS-2, CS-3 and CS-4. EDGE supports CS1-4 and MCS1-9

coding schemes. The following table shows the frequency bands of UG96 module.

Table 1: Frequency Bands of UG96 Module

More details about GPRS/EDGE multi-slot configuration and coding schemes, please refer to Appendix

B, C and D.

With a tiny profile of 26.5mm × 22.5mm × 2.2mm, UG96 can meet almost all requirements for M2M

application such as automotive, metering, tracking system, security solutions, routers, wireless POS, etc..

UG96 is an SMD type module, which can be embedded in application through its 102 LGA pads.

UG96 is integrated with internet service protocols like TCP/UDP and PPP. Extended AT commands have

been developed for you to use these internet service protocols easily.

UG96_Hardware_Design Confidential / Released 10 / 75

Page 12

UMTS/HSPA Module Series

Part

Number

Frequency Range (MHz)

Peak Gain

(XZ-V)

Average

Gain(XZ-V)

VS

WR

Impedance

3R007

UMTS800:830~885MHz

UMTS850/GSM850:824~894MHz

UMTS900/EGSM900:880~960MHz

DCS1800:1710~1880MHz

UMTS1900/PCS1900: 1850~1990MHz

UMTS2100:1920~2170MHz

1 dBi typ.

1 dBi typ.

2 max

50Ω

Feature

Details

UG96 Hardware Design

2.2. Directives and Standards

The UG96 module is designed to comply with the FCC statements. FCC ID: XMR201508UG96

The Host system using UG96 should have label “contains FCC ID: XMR201508UG96”.

2.2.1. 2.2.1. FCC Statement

Changes or modifications not expressly approved by the party responsible for compliance could void the

user’s authority to operate the equipment.

2.2.2. FCC Radiation Exposure Statement

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment.

This equipment should be installed and operated with minimum distance 20cm between the radiator and

your body as well as kept minimum 20cm from radio antenna depending on the Mobile status of this

module usage. This module should NOT be installed and operating simultaneously with other radio. The

manual of the host system, which uses UG96, must include RF exposure warning statement to advice

user should keep minimum 20cm from the radio antenna of UG96 module depending on the Mobile status.

Note: If a portable device (such as PDA) uses UG96 module, the device needs to do permissive change

and SAR testing.

The following list indicates the performance of antenna gain in certificate testing.

2.3. Key Features

The following table describes the detailed features of UG96 module.

Table 2: UG96 Key Features

UG96_Hardware_Design Confidential / Released 11 / 75

Page 13

UMTS/HSPA Module Series

Power Supply

Supply voltage: 3.3V~4.3V

Typical supply voltage: 3.8V

Frequency Bands

GSM 4-band: 850/900/1800/1900MHz

UMTS 5-band: 800/850/900/1900/2100MHz

Transmission Data

HSDPA category 8: Max 7.2Mbps

HSUPA category 6: Max 5.76Mbps

UMTS: Max 384kbps (DL)/Max 384kbps (UL)

EDGE: Max 236.8kbps (DL)/Max 236.8kbps (UL)

GPRS: Max 85.6kbps (DL)/Max 85.6kbps (UL)

CSD: 14.4kbps

HSPA/UMTS Features

Compliant with 3GPP Release 7

WCDMA data rate is corresponded with 3GPP R99/R4

384kbps on downlink and 384kbps on uplink

Support both QPSK and 16-QAM modulations

GSM/GPRS/EDGE

Data Features

GPRS:

Support GPRS multi-slot class 12

Coding scheme: CS-1, CS-2, CS-3 and CS-4

Maximum of four Rx time slots per frame

EDGE:

Support EDGE multi-slot class 12

Support GMSK and 8-PSK for different MCS (Modulation and Coding

scheme)

Downlink coding schemes: CS 1-4 and MCS 1-9

Uplink coding schemes: CS 1-4 and MCS 1-9

CSD:

CSD transmission rates: 14.4kbps non-transparent

Support Unstructured Supplementary Services Data (USSD)

Internet Protocol Features

Support TCP/UDP/PPP protocols

Support the protocols PAP (Password Authentication Protocol) and

CHAP (Challenge Handshake Authentication Protocol) usually used

for PPP connections

SMS

Text and PDU mode

Point to point MO and MT

SMS cell broadcast

SMS storage: SIM card by default

USIM Interface

Support USIM card: 1.8V, 3.0V

Support USIM and SIM

PCM Interface

Used for audio function with external codec

Supports 8, 16, 32 bit mode with short frame synchronization

Support master mode

UART Interface

Support one UART interface

7-wire on UART interface, without DSR

Support RTS and CTS hardware flow control

UG96 Hardware Design

UG96_Hardware_Design Confidential / Released 12 / 75

Page 14

UMTS/HSPA Module Series

Baud rate 300 to 921600bps

Default autobauding 4800 to 115200bps

Used for AT command, data transmission or firmware upgrade

Multiplexing function

USB Interface

Compliant with USB 1.1/2.0 specification (slave only), the data transfer

rate can reach up to 480Mbps

Used for AT command communication, data transmission, software

debug and firmware upgrade

USB Driver: Support Windows XP, Windows Vista, Windows 7,

Windows 8, Windows CE5.0/6.0*, Linux, Android

AT Commands

Compliant with 3GPP TS 27.007, 27.005 and Quectel enhanced AT

commands

Real Time Clock

Implemented

Network Indication

One pin NETLIGHT to indicate network connectivity status

Antenna Interface

GSM/UMTS antenna, 50Ω

Physical Characteristics

Size: 22.5±0.15 × 26.5±0.15 × 2.2±0.2mm

Interface: LGA

Weight: 3.1g

Temperature Range

Normal operation: -35°C ~ +80°C

Restricted operation: -40°C ~ -35°C and +80°C ~ +85°C 1)

Storage temperature: -45°C ~ +90°C

Firmware Upgrade

USB interface or UART interface

RoHS

All hardware components are fully compliant with EU RoHS directive

1.

1)

Means when the module works within this temperature range, RF performance might degrade. For

example, the frequency error or the phase error would increase.

2. * means this feature is under development.

NOTES

UG96 Hardware Design

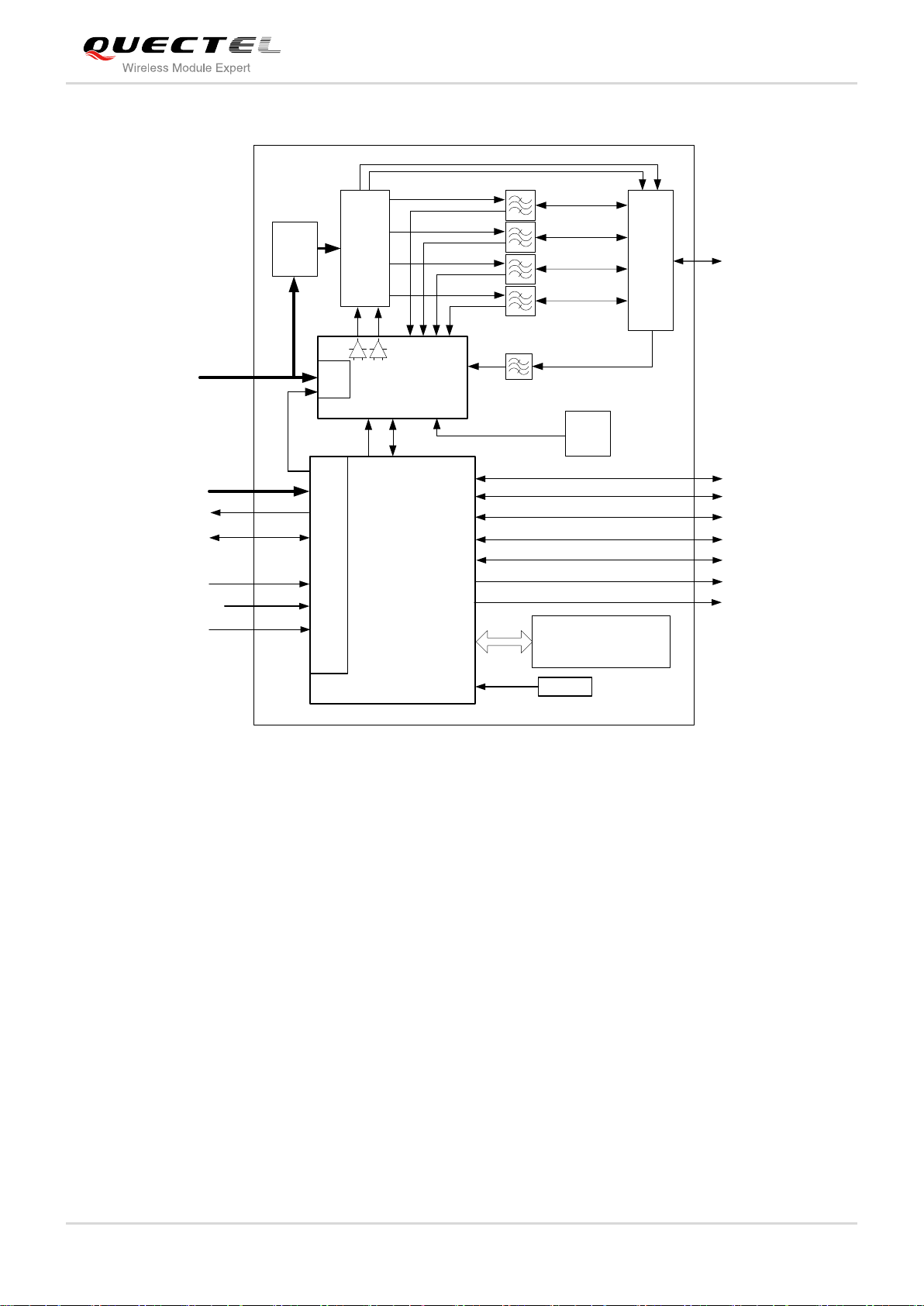

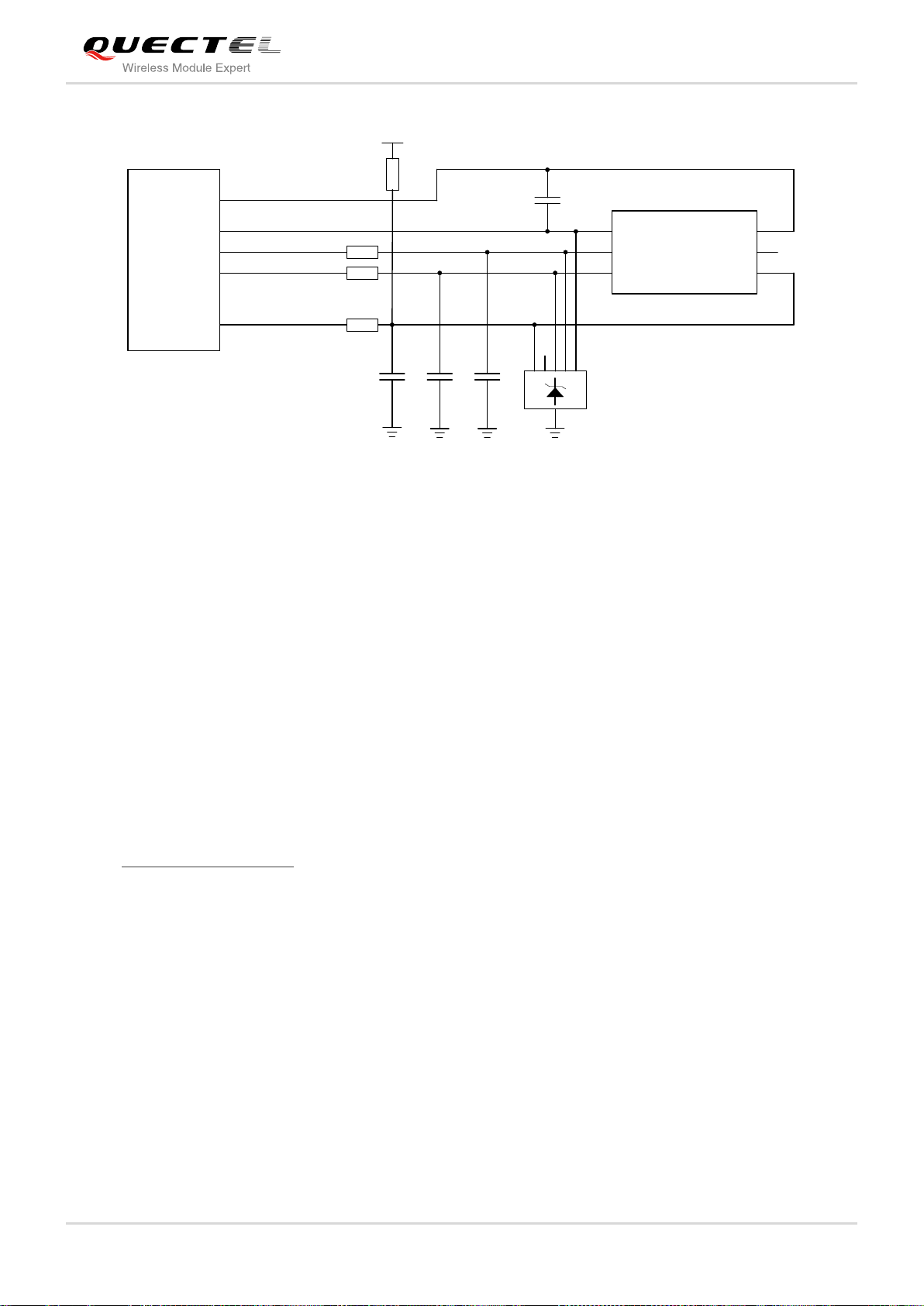

2.4. Functional Diagram

The following figure shows a block diagram of UG96 and illustrates the major functional parts.

RF transceiver

Baseband

UG96_Hardware_Design Confidential / Released 13 / 75

Page 15

UMTS/HSPA Module Series

UG96 Hardware Design

DDR+NAND flash

Radio frequency

Peripheral interface

--UART interface

--USIM card interface

--USB interface

--PCM interface

--I2C interface

--Status indication

--Control interface

UG96_Hardware_Design Confidential / Released 14 / 75

Page 16

UMTS/HSPA Module Series

PWRKEY

RESET_N

32kHz

PMU

Baseband

MCP

RF_ANT

USIM

STATUS

UART

VBAT_BB

USB

VBAT_RF

B1

VDD_EXT

VRTC

Nand+DDR

PWRDWN_N

RF

Transceiver

NETLIGHT

26MHz

DCXO

B2/PCS1900

GSM TX LB

Duplexer

PCM

PMU

Reset

I2C

PA

ASM

B5/B6/GSM850

B8/GSM900

DC/DC

B1

B2

B5/B6

B8

PM_HPM_L

GSM TX HB

DCS1800

UG96 Hardware Design

2.5. Evaluation Board

In order to help you to develop applications with UG96, Quectel supplies an evaluation board

(UMTS<E-EVB), RS-232 to USB cable, USB data cable, power adapter, earphone, antenna and other

peripherals to control or test the module. For details, please refer to document [2].

UG96_Hardware_Design Confidential / Released 15 / 75

Figure 1: Functional Diagram

Page 17

UMTS/HSPA Module Series

UG96 Hardware Design

3 Application Interface

3.1. General Description

UG96 is equipped with a 62-pin 1.1mm pitch SMT pads plus 40-pin ground pads and reserved pads that

connect to customer’s cellular application platform. Sub-interfaces included in these pads are described in

detail in the following chapters:

Power supply

RTC interface

UART interface

USIM interface

USB interface

PCM interface

Status indication

UG96_Hardware_Design Confidential / Released 16 / 75

Page 18

UMTS/HSPA Module Series

RESERVED

PCM_SYNC

PCM_CLK

PCM_DIN

PCM_DOUT

RESERVED

RESERVED

PWRKEY

PWRDWN_N

RESET_N

RESERVED

1

2

3

4

5

6

7

11

12

13

14

15

16

17

18

50

51

52

53

54

55

58

59

60

61

62

USB_DM

AP_READY

STATUS

NETLIGHT

RESERVED

RESERVED

RESERVED

CLK_OUT

RESERVED

RESERVED

RESERVED

VDD_EXT

DTR

GND

USIM_CLK

USIM_DATA

USIM_RST

USIM_VDD

RI

DCD

CTS

TXD

RXD

VBAT_BB

VBAT_BB

USIM_GND

GND

RESERVED

31

30

29

28

27

26

23

22

21

20

19

10

9

USB_DP

USB_VBUS

RESERVED

GND

RESERVED

RESERVED

RTS

I2C_SCL

I2C_SDA

8

49

48

47

46

45

44

43

40

41

42

39

38

37

36

35

34

33

32

24

57

56

GND

GND

RF_ANT

GND

GND

RESERVED

VBAT_RF

VBAT_RF

GND

GND

RESERVED

VRTC

GND

USIM_PRESENCE

63

64

65

66

67

68

83

84

85

86

87

88

98

97

96

95

94

93

78

77

76

75

74

73

91 92

89 90

71

72

69

70

80 79

82 81

100

99

102 101

POWER USB UART

USIM

OTHERS

GND

RESERVED

PCM

ANT

25

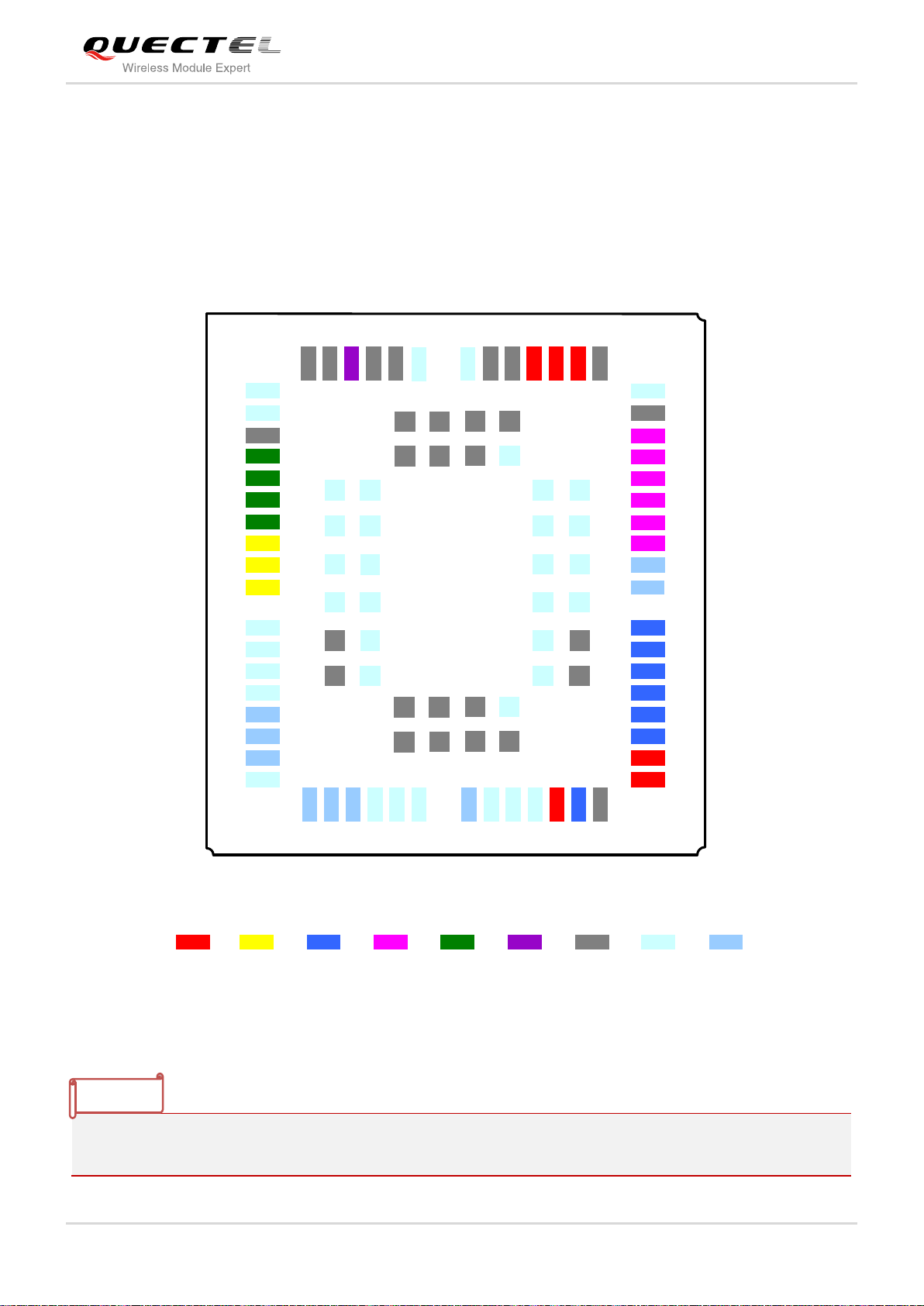

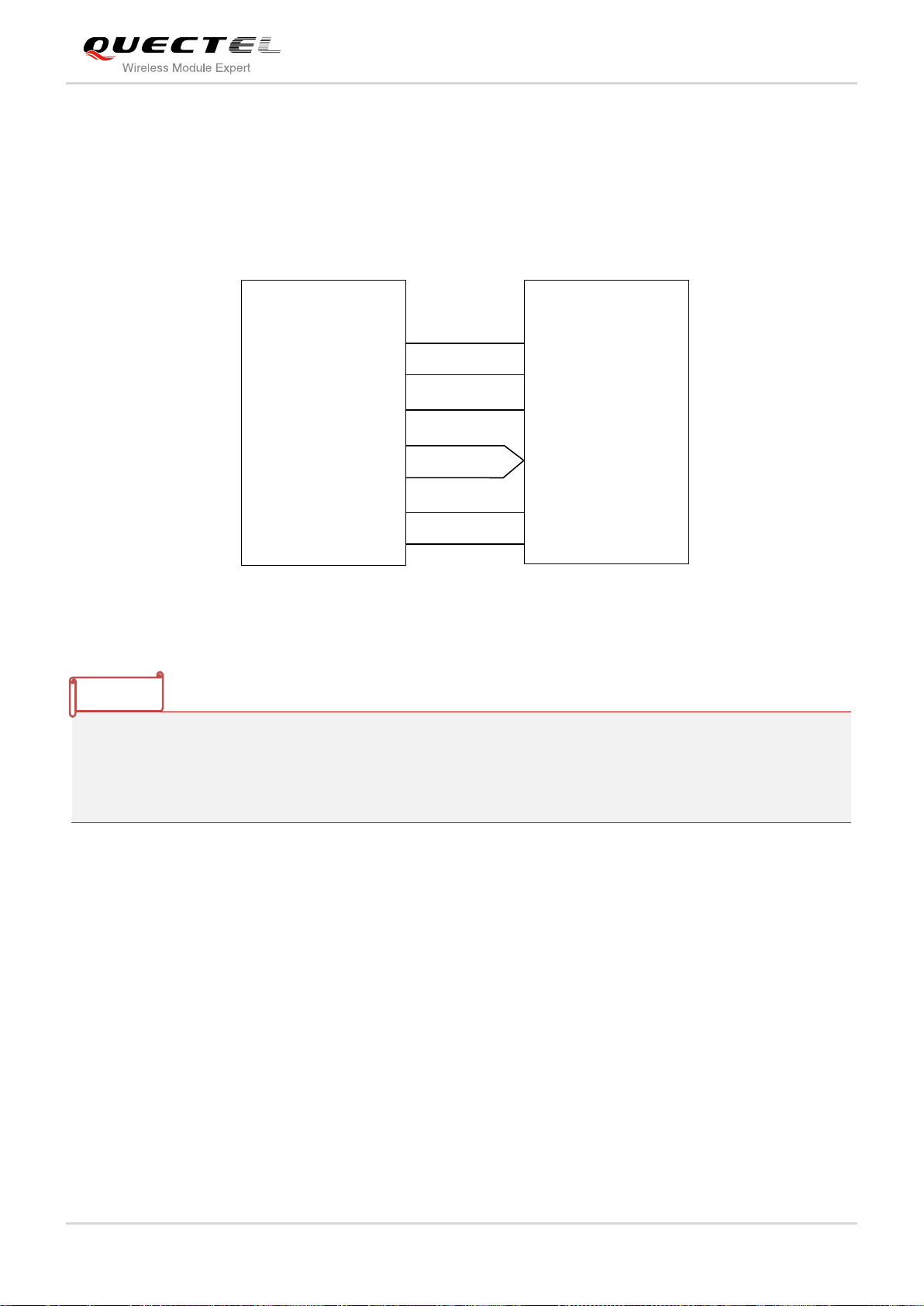

1. Keep all RESERVED pins and unused pins unconnected.

2. GND pads should be connected to ground in the design.

NOTES

UG96 Hardware Design

3.2. Pin Assignment

The following figure shows the pin assignment of the UG96 module.

Figure 2: Pin Assignment (Top View)

UG96_Hardware_Design Confidential / Released 17 / 75

Page 19

UMTS/HSPA Module Series

Type

Description

IO

Bidirectional input/output

DI

Digital input

DO

Digital output

PI

Power input

PO

Power output

AI

Analog input

AO

Analog output

OD

Open drain

Power Supply

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

VBAT_BB

32, 33

PI

Power supply for

module baseband

part.

Vmax=4.3V

Vmin=3.3V

Vnorm=3.8V

It must be able to

provide sufficient

current in a transmitting

burst which typically

rises to 2.0A.

VBAT_RF

52, 53

PI

Power supply for

module RF part.

Vmax=4.3V

Vmin=3.3V

Vnorm=3.8V

VRTC

51

PI/

PO

Power supply for

internal RTC circuit.

Vnorm=1.8V when

VBAT≥3.3V

VI=1V~1.9V at

IIN max=2uA when

VBAT is not applied

If unused, keep this pin

open.

VDD_EXT

29

PO

Provide 1.8V for

external circuit.

Vnorm=1.8V

IOmax=20mA

Power supply for

external GPIO’s pull up

circuits.

UG96 Hardware Design

3.3. Pin Description

The following tables show the UG96’s pin definition.

Table 3: IO Parameters Definition

Table 4: Pin Description

UG96_Hardware_Design Confidential / Released 18 / 75

Page 20

UMTS/HSPA Module Series

If unused, keep this pin

open.

GND

3, 31, 48,

50, 54, 55,

58, 59, 61,

62, 67~74,

79~82,

89~91,

100~102

Ground

Turn On/Off

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

PWRKEY

15

DI

Turn on the module.

RPU≈200kΩ

VIHmax=2.1V

VIHmin=1.3V

VILmax=0.5V

Pull-up to VRTC

internally.

Active low.

PWRDWN_N

16

DI

Turn off the module.

RPU≈4.7kΩ

VIHmax=2.1V

VIHmin=1.3V

VILmax=0.5V

Pull-up to VRTC

internally.

Active low.

If unused, keep this

pin open.

RESET_N

17

DI

Reset the module.

RPU≈200kΩ

VIHmax=2.1V

VIHmin=1.3V

VILmax=0.5V

Pull-up to VRTC

internally.

Active low.

If unused, keep this

pin open.

Status Indication

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

STATUS

20

DO

Indicate the module

operating status.

VOHmin=1.3V

VOLmax=0.5V

1.8V power domain.

If unused, keep this

pin open.

NETLIGHT

21

DO

Indicate the module

network status.

VOHmin=1.3V

VOLmax=0.5V

1.8V power domain.

If unused, keep this

pin open.

USB Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

USB_VBUS

8

PI

USB insert

detection.

Vmax=5.25V

Vmin=2.5V

Vnorm=5.0V

USB insert detection.

UG96 Hardware Design

UG96_Hardware_Design Confidential / Released 19 / 75

Page 21

UMTS/HSPA Module Series

USB_DP

9

IO

USB differential data

bus.

Compliant with USB

2.0 standard

specification.

Require differential

impedance of 90Ω.

USB_DM

10

IO

USB differential data

bus.

Compliant with USB

2.0 standard

specification.

Require differential

impedance of 90Ω.

USIM Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

USIM_GND

47

Specified ground for

USIM card.

USIM_VDD

43

PO

Power supply for

USIM card.

For 1.8V USIM:

Vmax=1.85V

Vmin=1.75V

For 3.0V USIM:

Vmax=2.9V

Vmin=2.8V

Either 1.8V or 3.0V is

supported by the

module automatically.

USIM_DATA

45

IO

Data signal of USIM

card.

For 1.8V USIM:

VILmax=0.35V

VIHmin=1.25V

VOLmax=0.25V

VOHmin=1.25V

For 3.0V USIM:

VILmax=0.5V

VIHmin=2.05V

VOLmax=0.25V

VOHmin=2.05V

Pull-up to USIM_VDD

with 4.7K resistor

internally.

USIM_CLK

46

DO

Clock signal of USIM

card.

For 1.8V USIM:

VOLmax=0.25V

VOHmin=1.25V

For 3.0V USIM:

VOLmax=0.25V

VOHmin=2.05V

USIM_RST

44

DO

Reset signal of

USIM card.

For 1.8V USIM:

VOLmax=0.25V

VOHmin=1.25V

For 3.0V USIM:

VOLmax=0.3V

VOHmin=2.05V

UG96 Hardware Design

UG96_Hardware_Design Confidential / Released 20 / 75

Page 22

UMTS/HSPA Module Series

USIM_

PRESENCE

42

DI

USIM card input

detection.

VILmax=0.35V

VIHmin=1.3V

VIHmax=1.85V

1.8V power domain.

External pull-up

resistor is required.

Main UART Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

RI

39

DO

Ring indicator.

VOLmax=0.25V

VOHmin=1.55V

1.8V power domain.

If unused, keep this

pin open.

DCD

38

DO

Data carrier

detection.

VOLmax=0.25V

VOHmin=1.55V

1.8V power domain.

If unused, keep this

pin open.

CTS

36

DO

Clear to send.

VOLmax=0.25V

VOHmin=1.55V

1.8V power domain.

If unused, keep this

pin open.

RTS

37

DI

Request to send.

VILmax=0.35V

VIHmin=1.3V

VIHmax=1.85V

1.8V power domain.

If unused, keep this

pin open.

DTR

30

DI

Data terminal ready.

VILmax=0.35V

VIHmin=1.3V

VIHmax=1.85V

1.8V power domain.

If unused, keep this

pin open.

TXD

35

DO

Transmit data.

VOLmax=0.25V

VOHmin=1.55V

1.8V power domain.

If unused, keep this

pin open.

RXD

34

DI

Receive data.

VILmax=0.35V

VIHmin=1.3V

VIHmax=1.85V

1.8V power domain.

If unused, keep this

pin open.

RF Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

RF_ANT

60

IO

RF antenna.

50Ω impedance

PCM Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

PCM_IN

6

DI

PCM data input.

VILmin=-0.3V

VILmax=0.35V

VIHmin=1.3V

VIHmax=1.85V

1.8V power domain.

If unused, keep this

pin open.

PCM_OUT

7

DO

PCM data output.

VOLmax=0.25V

VOHmin=1.55V

1.8V power domain.

If unused, keep this

pin open.

UG96 Hardware Design

UG96_Hardware_Design Confidential / Released 21 / 75

Page 23

UMTS/HSPA Module Series

PCM_SYNC

5

DO

PCM data frame

sync signal.

VOLmax=0.25V

VOHmin=1.55V

1.8V power domain.

In master mode, it is

an output signal.

If unused, keep this

pin open.

PCM_CLK

4

DO

PCM data bit clock.

VOLmax=0.25V

VOHmin=1.55V

1.8V power domain.

In master mode, it’s

an output signal.

If unused, keep this

pin open.

I2C Interface

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

I2C_SCL

40

OD

I2C serial clock.

1.8V power domain.

External pull-up

resistor is required.

If unused, keep this

pin open.

I2C_SDA

41

OD

I2C serial data.

1.8V power domain.

External pull-up

resistor is required.

If unused, keep this

pin open.

Other Pins

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

AP_READY

19

DI

Application

processor sleep

state detection.

VILmin=-0.3V

VILmax=0.35V

VIHmin=1.3V

VIHmax=1.85V

1.8V power domain.

If unused, keep this

pin open.

CLK_OUT

25

DO

Clock output.

Provide a digital clock

output for an external

audio codec.

If unused, keep this

pin open.

RESERVED Pins

Pin Name

Pin No.

I/O

Description

DC Characteristics

Comment

RESERVED

1, 2,

11~14,

18,

22~24,

26~28,

Reserved

Keep these pins

unconnected.

UG96 Hardware Design

UG96_Hardware_Design Confidential / Released 22 / 75

Page 24

UMTS/HSPA Module Series

49,

56, 57,

63~66,

75~78,

83~88,

92~99

The function of AP_READY is under development.

Mode

Details

Normal Operation

GSM Idle

The module has registered to the GSM network and is ready to

send and receive data.

GSM Talk/Data

GSM connection is ongoing. In this mode, the power consumption

is decided by the configuration of power control level (PCL),

dynamic DTX control and the working RF band.

GPRS Idle

The module is ready for GPRS data transfer, but no data transfer

is going on. In this case, power consumption depends on network

setting and GPRS configuration.

GPRS Data

There is GPRS data in transfer (PPP, TCP or UDP). In this mode,

power consumption is decided by the PCL, working RF band and

GPRS multi-slot configuration.

EDGE Idle

The module is ready for data transfer in EDGE mode, but no data

is currently sent or received. In this case, power consumption

depends on network settings and EDGE configuration.

EDGE Data

There is EDGE data in transfer (PPP, TCP or UDP).

UMTS Idle

The module has registered to the UMTS network and the module

is ready to send and receive data.

UMTS

Talk/Data

UMTS connection is ongoing. In this mode, the power

consumption is decided by network setting (e.g. TPC pattern) and

data transfer rate.

NOTE

UG96 Hardware Design

3.4. Operating Modes

The table below briefly summarizes the various operating modes referred in the following chapters.

Table 5: Overview of Operating Modes

UG96_Hardware_Design Confidential / Released 23 / 75

Page 25

UMTS/HSPA Module Series

HSPA Idle

The module has registered to the HSPA network and the module

is ready to send and receive data.

HSPA Data

HSPA data transfer is ongoing. In this mode, the power

consumption is decided by network setting (e.g. TPC pattern) and

data transfer rate.

Minimum

Functionality

Mode

AT+CFUN command can set the module entering into a minimum functionality mode

without removing the power supply. In this case, both RF function and USIM card will

be invalid.

Sleep Mode

In this mode, the current consumption of the module will be reduced to the minimal

level. During this mode, the module can still receive paging message, SMS and voice

call from the network normally.

Power Down

Mode

In this mode, the power management unit shuts down the power supply for the

baseband part and RF part. Only the power supply for RTC remains. Software is not

active. The serial interface is not accessible. Operating voltage (connected to

VBAT_RF and VBAT_BB) remains applied.

UG96 Hardware Design

3.5. Power Saving

UG96 is able to reduce its current consumption to a minimum value during the sleep mode. The following

section describes power saving procedure of UG96.

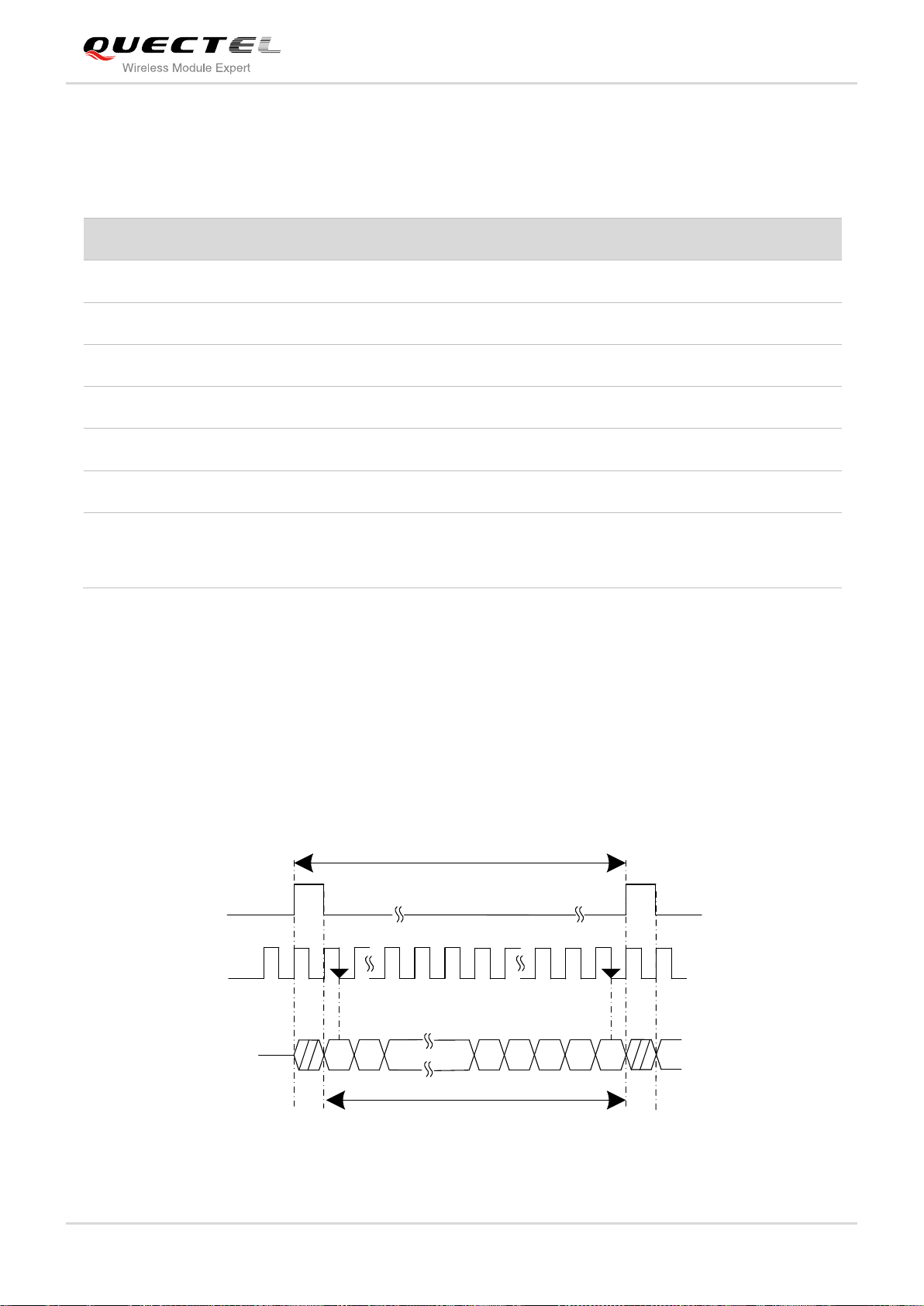

3.5.1.1. UART Application

If application processor communicates with module via UART interface, the following preconditions can

let the module enter into the sleep mode.

Execute AT command AT+QCFG="uart/power",0,0 to set UART into auto on/off mode.

Execute AT command AT+QSCLK=1 to enable the sleep mode.

Drive DTR to high level.

UG96_Hardware_Design Confidential / Released 24 / 75

Page 26

UMTS/HSPA Module Series

RXD

TXD

RI

DTR

AP_READY

TXD

RXD

EINT

GPIO

GPIO

Module

Processor

GND

GND

UG96 Hardware Design

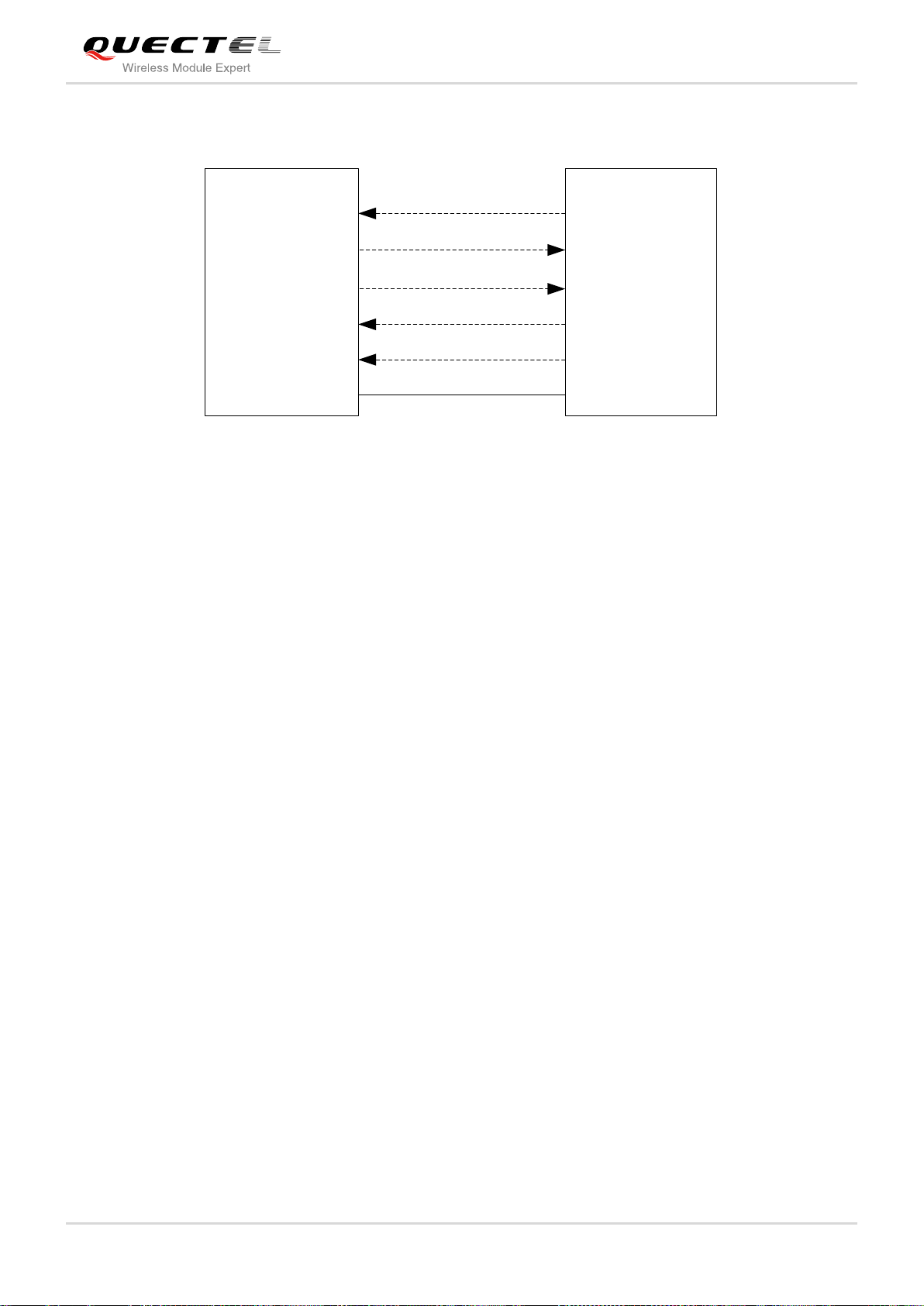

The following figure shows the connection between the module and application processor.

Figure 3: UART Sleep Application

The RI of module is used to wake up the processor, and AP_READY will detect the sleep state of

processor (can be configured to high level or low level detection). You should pay attention to the level

match shown in dotted line between module and processor. Drive DTR pin to low level to wake up the

module.

In sleep mode for UART application, the UART port is not accessible.

3.5.1.2. USB Application with Suspend Function

If application processor communicates with module via USB interface, and processor supports USB

suspend function, the following preconditions can let the module enter into the sleep mode.

Execute AT command AT+QCFG="uart/power",0,0 to set UART into auto on/off mode.

Execute AT command AT+QSCLK=1 to enable the sleep mode.

The processor’s USB bus which is connected with the module USB interface enters into suspended

state.

UG96_Hardware_Design Confidential / Released 25 / 75

Page 27

UMTS/HSPA Module Series

USB_VBUS

USB_DP

USB_DM

VDD

USB_DP

USB_DM

Module

Processor

GND GND

RI EINT

USB_VBUS

USB_DP

USB_DM

VDD

USB_DP

USB_DM

Module Processor

RI

EINT

Power

Switch

GPIO

GND

GND

UG96 Hardware Design

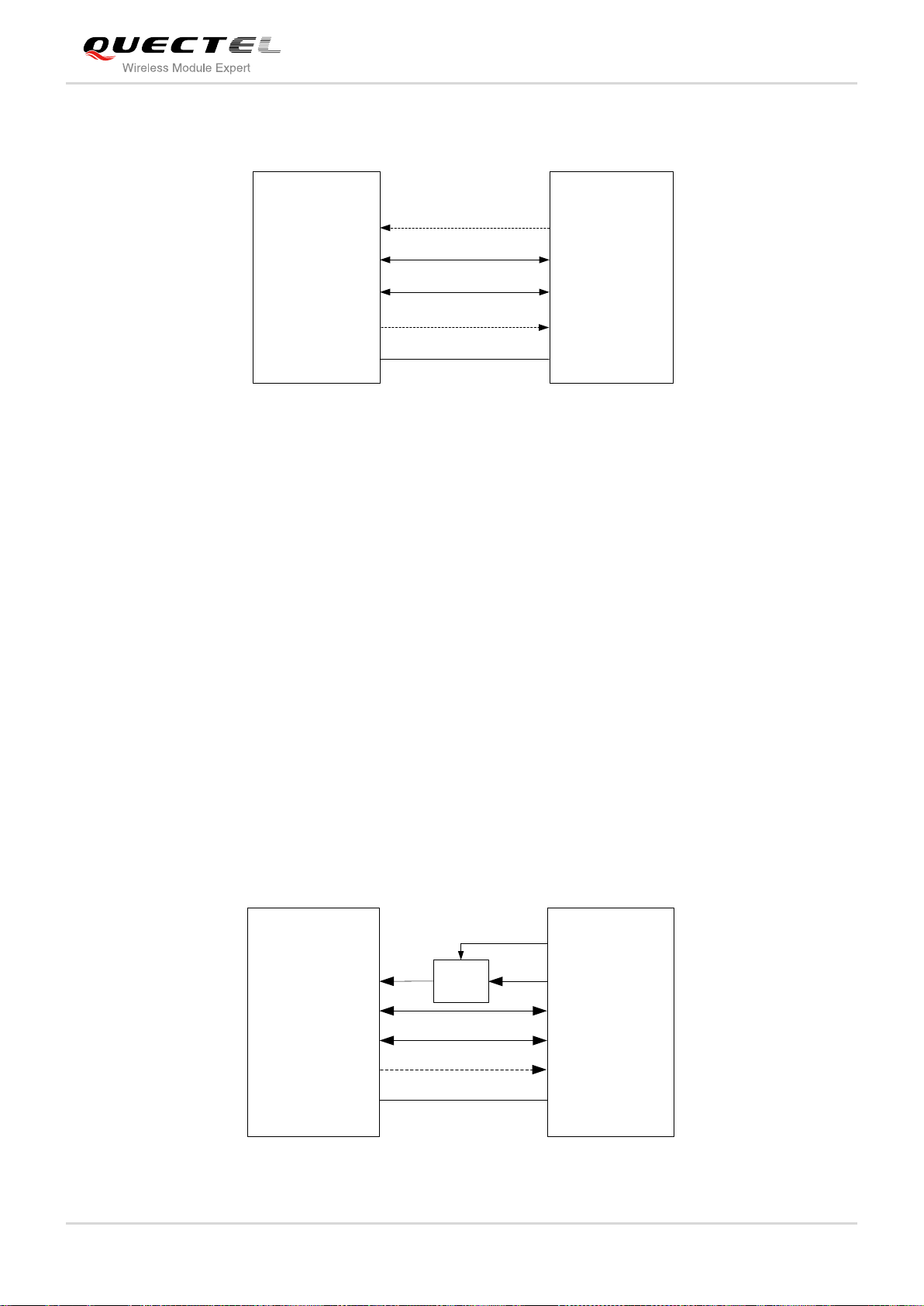

The following figure shows the connection between the module and processor.

Figure 4: USB Application with Suspend Function

When the processor’s USB bus returns to resume state, the module will be woken up.

3.5.1.3. USB Application without Suspend Function

If application processor communicates with module via USB interface, and processor does not support

USB suspend function, you should disconnect USB_VBUS with additional control circuit to let the module

enter into sleep mode.

Execute AT command AT+QCFG="uart/power",0,0 to set UART into auto on/off mode.

Execute AT command AT+QSCLK=1 to enable the sleep mode.

Disconnect USB_VBUS.

Supply power to USB_VBUS will wake up the module.

The following figure shows the connection between the module and application processor.

UG96_Hardware_Design Confidential / Released 26 / 75

Figure 5: USB Sleep Application without Suspend Function

Page 28

UMTS/HSPA Module Series

1. In sleep mode, the module can still receive paging message, SMS, voice call and TCP/UDP data from

the network normally.

2. The function of AP_READY is under development.

Pin Name

Pin No.

Description

Min.

Typ.

Max.

Unit

VBAT_RF

52, 53

Power supply for module RF

part.

3.3

3.8

4.3

V

VBAT_BB

32, 33

Power supply for module

baseband part.

3.3

3.8

4.3

V

NOTES

UG96 Hardware Design

Minimum functionality mode reduces the functionality of the module to minimum level, thus minimizes the

current consumption at the same time. This mode can be set as below:

Command AT+CFUN provides the choice of the functionality levels: <fun>=0, 1, 4.

AT+CFUN=0: Minimum functionality, RF part and USIM card will be closed.

AT+CFUN=1: Full functionality (by default).

AT+CFUN=4: Disable RF function (airplane mode). All AT commands related to RF function are not

accessible.

For detailed information about command AT+CFUN, please refer to document [1].

3.6. Power Supply

UG96 provides four VBAT pins dedicated to connect with the external power supply. There are two

separate voltage domains for VBAT.

VBAT_RF with two pads for module RF.

VBAT_BB with two pads for module baseband.

The following table shows the VBAT pins and ground pins.

Table 6: VBAT and GND Pins

UG96_Hardware_Design Confidential / Released 27 / 75

Page 29

UMTS/HSPA Module Series

GND

3, 31, 48, 50

54, 55, 58,

59, 61, 62,

67~74,

79~82,

89~91,

100~102

Ground

- - -

-

< 400mV

Current

VBAT

≤ 2.0A

burst

burst

Min. 3.3V

UG96 Hardware Design

The power supply range of the module is 3.3V~ 4.3V. Make sure the input voltage will never drop below

3.3V. If the voltage drops below 3.3V, the module will turn off automatically. The following figure shows the

voltage drop during transmitting burst in 2G network, the voltage drop will be less in 3G network.

Figure 6: Voltage Drop during Transmitting Burst

To decrease voltage drop, a bypass capacitor of about 100µF with low ESR should be used. Multi-layer

ceramic chip (MLCC) capacitor can provide the best combination of low ESR. The main power supply

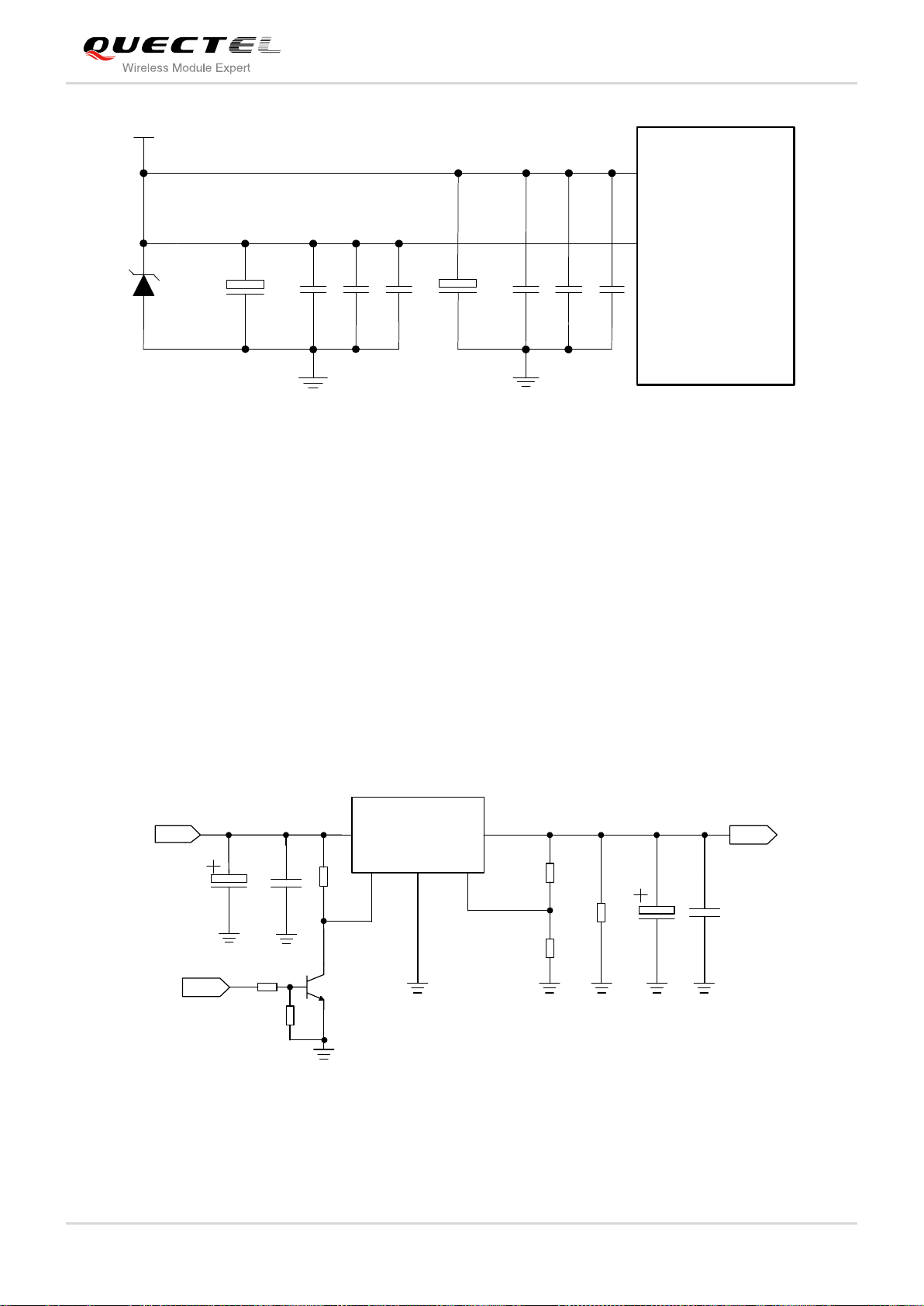

from an external application has to be a single voltage source and splits into to two sub paths with star

structure. The width of VBAT_BB trace should be no less than 1mm, and the width of VBAT_RF trace

should be no less than 2mm, and the principle of the VBAT trace is the longer, the wider.

Three ceramic capacitors (100nF, 33pF, 10pF) are recommended to be applied to the VBAT pins. The

capacitors should be placed close to the UG96’s VBAT pins. In addition, in order to get a stable power

source, it is suggested that you should use a zener diode of which reverse zener voltage is 5.1V and

dissipation power is more than 0.5W. The following figure shows star structure of the power supply.

UG96_Hardware_Design Confidential / Released 28 / 75

Page 30

UMTS/HSPA Module Series

Module

VBAT_RF

VBAT_BB

VBAT

C1

100uF

C6

100nFC733pFC810pF

+

+

C2

100nF

C5

100uF

C3

33pF

C4

10pF

D1

5.1V

DC_IN

C1

C2

MIC29302WU U1

IN

OUT

EN

GND

ADJ

2 4

1

3

5

VBAT

100nF

C3

470uF

C4

100nF

R2

100K

47K

R3

470uF

470R

51K

R4

R1

1%

1%

MCU_POWER

_ON/OFF

47K

4.7K

R5

R6

UG96 Hardware Design

Figure 7: Star Structure of the Power Supply

3.6.3. Reference Design for Power Supply

The power design for the module is very important, since the performance of power supply for the module

largely depends on the power source. The power supply is capable of providing the sufficient current up to

2A at least. If the voltage drop between the input and output is not too high, it is suggested that a LDO

should be used to supply power for module. If there is a big voltage difference between the input source

and the desired output (VBAT), a buck converter is preferred to be used as a power supply.

The following figure shows a reference design for +5V input power source. The designed output for the

power supply is about 3.8V and the maximum load current is 3A.

Figure 8: Reference Circuit of Power Supply

UG96_Hardware_Design Confidential / Released 29 / 75

Page 31

UMTS/HSPA Module Series

It is suggested that you should switch off power supply for module in abnormal state, and then switch on

power to restart module.

Pin Name

Pin No.

Description

DC Characteristics

Comment

PWRKEY

15

Turn on the module.

VIHmax=2.1V

VIHmin=1.3V

VILmax=0.5V

Pull-up to VRTC

internally with 200kΩ

resistor.

Turn on pulse

PWRKEY

4.7K

47K

≥ 100ms

NOTE

UG96 Hardware Design

The command AT+CBC can be used to monitor the VBAT_BB voltage value displayed in millivolt. For

more details, please refer to document [1].

3.7. Turn on and off Scenarios

Turn on the module using the PWRKEY. The following table shows the pin definition of PWRKEY.

Table 7: PWRKEY Pin Description

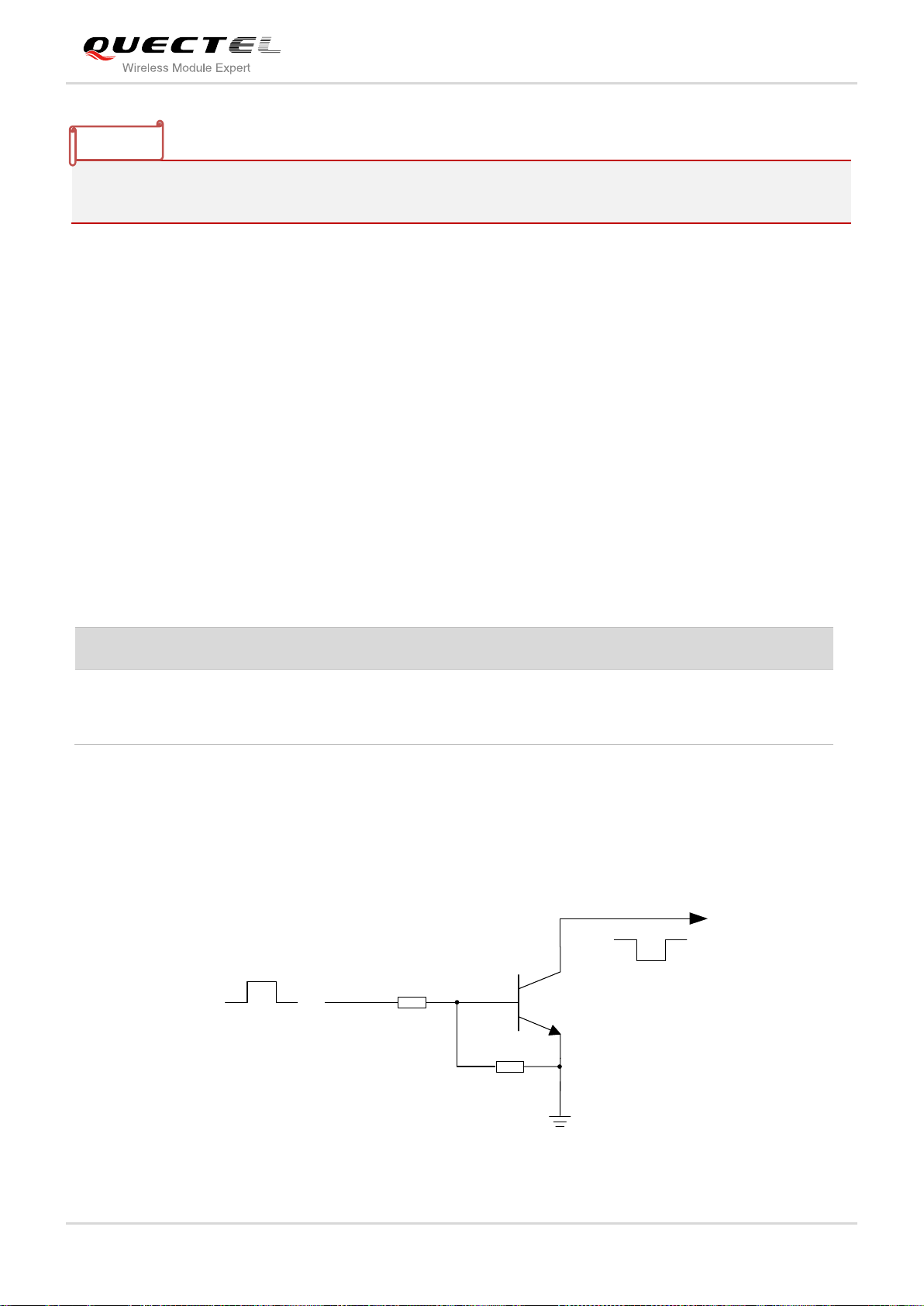

When UG96 is in power down mode, it can be turned on to normal mode by driving the PWRKEY pin to a

low level at least 100ms. It is recommended to use an open drain/collector driver to control the PWRKEY.

The STATUS pin output a high level after UG96 is turned on. A simple reference circuit is illustrated in the

following figure.

UG96_Hardware_Design Confidential / Released 30 / 75

Figure 9: Turn on the Module Using Driving Circuit

Page 32

UMTS/HSPA Module Series

PWRKEY

S1

Close to S1

TVS

V

IL

≤ 0.5V

V

IH

≥ 1.3V

VBAT

PWRKEY

(Input)

≥ 100ms

OFF

BOOTING

Module

Status

RUNNING

1

≥ 3.5s

RESET_N

STATUS

>2.3s

① Make sure that VBAT is stable before pulling down PWRKEY pin, the recommended delay time is at

least 30ms. It is not suggested that pull down PWRKEY pin all the time.

NOTE

UG96 Hardware Design

The other way to control the PWRKEY is using a button directly. A TVS component is indispensable to be

placed nearby the button for ESD protection. When pressing the key, electrostatic strike may generate

from finger. A reference circuit is shown in the following figure.

Figure 10: Turn on the Module Using Keystroke

The turn on scenarios is illustrated as the following figure.

Figure 11: Timing of Turning on Module

UG96_Hardware_Design Confidential / Released 31 / 75

Page 33

UMTS/HSPA Module Series

VBAT

AT+QPOWD

Log off network about 2s to 40s

RUNNING

Power-down procedure

OFF

Module

Status

STATUS

RXD

UG96 Hardware Design

The following procedures can be used to turn off the module:

Normal power down procedure: Turn off the module using command AT+QPOWD.

Emergency power down procedure: Turn off the module using the PWRDWN_N pin.

Automatic shutdown: Turn off the module automatically if under-voltage or over-voltage is detected.

3.7.2.1. Turn off Module Using AT Command

There are several different ways to turn off the module. It is recommended to turn off the module from AT

command AT+QPOWD. It is a safe way to turn off the module. This command will let the module log off

from the network and allow the firmware to save important data before completely disconnecting the

power supply.

The power-down scenario is illustrated as the following figure.

During power-down procedure, module will log off from network and save important data. After logging off,

module sends out “OK”, and then sends out “POWERED DOWN” and shuts down the internal power

supply. The power on VBAT pins is not allowed to be turned off before the URC “POWERED DOWN” is

output to avoid data loss. If logging off is not done within 40s, module will shut down internal power supply

forcibly.

After that moment, the module enters the power down mode, no other AT commands can be executed,

only the RTC is still active. Please refer to document [1] for details about the AT command of

AT+QPOWD.

UG96_Hardware_Design Confidential / Released 32 / 75

Figure 12: Timing of Turning off through AT Command

Page 34

UMTS/HSPA Module Series

Pin Name

Pin No.

Description

DC Characteristics

Comment

PWRDWN_N

16

Turn off the module

VIHmax=2.1V

VIHmin=1.3V

VILmax=0.5V

Pull-up to VRTC

internally with 4.7kΩ

resistor.

Turn off pulse

PWRDWN_N

4.7K

47K

≥ 100ms

UG96 Hardware Design

3.7.2.2. Emergency Shutdown

The module can be shut down by the pin PWRDWN_N. It should only be used under emergent situation.

The following table shows the pin definition of PWRDWN_N.

Table 8: PWRDWN_N Pin Description

Driving the PWRDWN_N to a low level voltage at least 100ms, the module will execute power-down

procedure after PWRDWN_N is released. It is recommended to use an open drain/collector driver to

control the PWRDWN_N. The level of STATUS pin is low after UG96 is turned off. A simple reference

circuit is illustrated in the following figure.

The other way to control the PWRDWN_N is using a button directly. A TVS component is indispensable to

be placed nearby the button for ESD protection. When pressing the key, electrostatic strike may generate

from finger. A reference circuit is shown in the following figure.

UG96_Hardware_Design Confidential / Released 33 / 75

Figure 13: Turn off the Module Using Driving Circuit

Page 35

UMTS/HSPA Module Series

PWRDWN_N

S2

Close to S2

TVS

VBAT

PWRDWN_N

≥100ms

RUNNING

Power-down procedure

OFF

STATUS

Module

Status

Use the PWRDWN_N only when turning off the module by the command AT+QPOWD or the RESET_N

pin failed.

NOTE

UG96 Hardware Design

Figure 14: Turn off the Module Using Keystroke

The emergency shutdown scenario is illustrated as the following figure.

Figure 15: Timing of Emergency Shutdown

UG96_Hardware_Design Confidential / Released 34 / 75

Page 36

UMTS/HSPA Module Series

The value of voltage threshold can be revised by AT command, refer to document [1] for details.

Pin Name

Pin No.

Description

DC Characteristics

Comment

RESET_N

17

Reset the module.

VIHmax=2.1V

VIHmin=1.3V

VILmax=0.5V

Pull-up to VRTC

internally with 200kΩ

resistor.

Active low.

NOTE

UG96 Hardware Design

3.7.2.3. Automatic Shutdown

The module will constantly monitor the voltage applied on the VBAT, if the voltage ≤ 3.5V, the following

URC will be presented:

+QIND: “vbatt”,-1

If the voltage ≥ 4.21V, the following URC will be presented:

+QIND: “vbatt”,1

The uncritical voltage is 3.3V to 4.3V, If the voltage > 4.3V or < 3.3V the module would automatically shut

down itself.

If the voltage < 3.3V, the following URC will be presented:

+QIND: “vbatt”,-2

If the voltage > 4.3V, the following URC will be presented:

+QIND: “vbatt”,2

3.8. Reset the Module

The RESET_N can be used to reset the module.

Table 9: RESET_N Pin Description

The module can be reset by driving the RESET_N to a low level voltage for more than 100ms and then

releasing.

UG96_Hardware_Design Confidential / Released 35 / 75

Page 37

UMTS/HSPA Module Series

Reset pulse

RESET_N

4.7K

47K

≥ 100ms

RESET_N

S3

Close to S3

TVS

VIL ≤ 0.5V

VIH ≥ 1.3V

VBAT

≥ 100ms

RESTARTING

Module

Status

RESET_N

RUNNING

> 5s

STATUS

> 3s

RUNNING

OFF

UG96 Hardware Design

The recommended circuit is similar to the PWRKEY control circuit. You can use open drain/collector

driver or button to control the RESET_N.

Figure 16: Reference Circuit of RESET_N by Using Driving Circuit

Figure 17: Reference Circuit of RESET_N by Using Button

The reset scenario is illustrated as the following figure.

Figure 18: Timing of Resetting Module

UG96_Hardware_Design Confidential / Released 36 / 75

Page 38

UMTS/HSPA Module Series

Large

Capacitance

Capacitor

Module

RTC

Core

1K

VRTC

C

UG96 Hardware Design

3.9. RTC Interface

The RTC (Real Time Clock) can be powered by an external capacitor through the pin VRTC when the

module is powered down and there is no power supply for the VBAT. If the voltage supply at VBAT is

disconnected, the RTC can be powered by the capacitor. The capacitance determines the duration of

buffering when no voltage is applied to UG96.

The capacitor is charged from the internal LDO of UG96 when there is power supply for the VBAT. A

serial 1KΩ resistor has been placed on the application inside the module. It limits the input current of the

capacitor.

The following figure shows the reference circuit for VRTC backup.

Figure 19: RTC Supply from Capacitor

In order to evaluate the capacitance of capacitor according to the backup time, you have to consider the

following parameters:

VRTC - The starting voltage of the capacitor. (Volt)

VRTC

- The minimum voltage acceptable for the RTC circuit.(Volt)

MIN

I - The current consumption of the RTC circuitry when VBAT = 0.(Ampere)

B

- Backup Time.(Second)

Time

C - The backup capacitance. (Farad)

When the power is off and only VRTC is running, the way of calculating the backup capacitor as follows:

C= B

*I/ (VRTC-VRTC

Time

MIN

)

For example, when the capacitor is 1000uF:

VRTC=1.8V

VRTC

MIN

=1.0V

I=2uA

C=1000uF

The backup time is about 400s.

UG96_Hardware_Design Confidential / Released 37 / 75

Page 39

UMTS/HSPA Module Series

Pin Name

Pin No.

I/O

Description

Comment

DTR

30

DI

Data terminal ready

1.8V power domain

RXD

34

DI

Receive data

1.8V power domain

TXD

35

DO

Transmit data

1.8V power domain

CTS

36

DO

Clear to send

1.8V power domain

RTS

37

DI

Request to send

1.8V power domain

DCD

38

DO

Data carrier detection

1.8V power domain

RI

39

DO

Ring indicator

1.8V power domain

Parameter

Min.

Max.

Unit

VIL

-0.3

0.35

V

VIH

1.3

1.85

V

VOL 0 0.25

V

VOH

1.55

1.8

V

UG96 Hardware Design

3.10. UART Interface

The module provides 7 lines UART interface.

UART interface supports 300, 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800

and 921600bps baud rate, and the default is auto-baud rate 4800~115200. This interface can be used for

data transmission, AT communication or firmware upgrade.

The module is designed as the DCE (Data Communication Equipment), following the traditional

DCE-DTE (Data Terminal Equipment) connection. The following table shows the pin definition of UART

interface.

Table 10: Pin Definition of the Main UART Interface

The logic levels are described in the following table.

Table 11: Logic Levels of Digital I/O

UG96_Hardware_Design Confidential / Released 38 / 75

Page 40

UMTS/HSPA Module Series

VCCA VCCB

OE

A1

A2

A3

A4

A5

A6

A7

A8

GND

B1

B2

B3

B4

B5

B6

B7

B8

VDD_EXT

RI

DCD

RTS

RXD

DTR

CTS

TXD

51K

51K

0.1uF

0.1uF

RI_3.3V

DCD_3.3V

RTS_3.3V

RXD_3.3V

DTR_3.3V

CTS_3.3V

TXD_3.3V

VDD_3.3V

TXS0108EPWR

10K

120K

MCU/ARM

/TXD

/RXD

VDD_EXT

4.7K

VCC_MCU

4.7K

4.7K

VDD_EXT

TXD

RXD

RTS

CTS

DTR

RI

/RTS

/CTS

GND

GPIO DCD

Module

GPIO

EINT

VDD_EXT

4.7K

GND

1nF

1nF

UG96 Hardware Design

UG96 provides one 1.8V UART interface. A level shifter should be used if your application is equipped

with a 3.3V UART interface. A level shifter TXS0108EPWR provided by Texas Instruments is

recommended. The following figure shows the reference design of the TXS0108EPWR.

Figure 20: Reference Circuit of Logic Level Translator

Please visit http://www.ti.com for more information.

Another example with transistor translation circuit is shown as below. The circuit of dotted line can refer to

the circuit of solid line. Please pay attention to direction of connection. Input dotted line of module should

refer to input solid line of the module. Output dotted line of module should refer to output solid line of the

module. The transistor translation circuit supports a maximum data rate of 0.5Mbps.

UG96_Hardware_Design Confidential / Released 39 / 75

Figure 21: Reference Circuit with Transistor Circuit

Page 41

UMTS/HSPA Module Series

TXS0108EPWR

DCD_3.3V

RTS_3.3V

DTR_3.3V

RXD_3.3V

RI_3.3V

CTS_3.3V

TXD_3.3V

DCD

RTS

DTR

RXD

RI

CTS

TXD

DCD_1.8V

RTS_1.8V

DTR_1.8V

RXD_1.8V

RI_1.8V

CTS_1.8V

TXD_1.8V

VCCA

Module

GND GND

VDD_EXT VCCB

3.3V

DIN1

ROUT3

ROUT2

ROUT1

DIN4

DIN3

DIN2

DIN5

R1OUTB

FORCEON

/FORCEOFF

/INVALID

3.3V

DOUT1

DOUT2

DOUT3

DOUT4

DOUT5

RIN3

RIN2

RIN1

VCC GND

OE

Translator

DB9M

PC side

DCD

RTS

DTR

TXD

RI

CTS

RXD

DSR

GND

1

2

3

4

5

6

7

8

9

1. The module disables the hardware flow control by default. When hardware flow control is required,

RTS and CTS should be connected to the host. AT command AT+IFC=2,2 is used to enable

hardware flow control. AT command AT+IFC=0,0 is used to disable the hardware flow control. For

more details, please refer to document [1].

2. Rising edge on DTR will let the module exit from the data mode by default. It can be disabled by AT

commands. Refer to document [1] for details.

3. DCD is used as data mode indication. Refer to document [1] for details.

4. It is suggested that you should set USB_DP, USB_DM and USB_VBUS pins as test points and then

place these test points on the DTE for debug.

NOTES

UG96 Hardware Design

The following figure is an example of connection between UG96 and PC. A voltage level translator and a

RS-232 level translator chip must be inserted between module and PC, since the UART interface does

not support the RS-232 level, while supports the 1.8V CMOS level only.

Figure 22: RS232 Level Match Circuit

3.11. USIM Card Interface

The USIM card interface circuitry meets ETSI and IMT-2000 SIM interface requirements. Both 1.8V and

3.0V USIM cards are supported.

UG96_Hardware_Design Confidential / Released 40 / 75

Page 42

UMTS/HSPA Module Series

Pin Name

Pin No. I/O

Description

Comment

USIM_PRESENCE

42

DI

USIM card detection input.

1.8V power domain.

USIM_VDD

43

PO

Power supply for USIM card.

Either 1.8V or 3.0V is

supported by the module

automatically.

USIM_RST

44

DO

Reset signal of USIM card.

USIM_DATA

45

IO

Data signal of USIM card.

Pull-up to USIM_VDD with

4.7k resistor internally.

USIM_CLK

46

DO

Clock signal of USIM card.

USIM_GND

47

Specified ground for USIM

card.

USIM_VDD

USIM_GND/GND

USIM_RST

USIM_CLK

USIM_DATA

USIM_PRESENCE

22R

22R

22R

VDD_EXT

51K

100nF USIM holder

GND

GND

ESD

33pF 33pF 33pF

VCC

RST

CLK

IO

VPP

GND

GND

USIM_VDD

15K

Module

UG96 Hardware Design

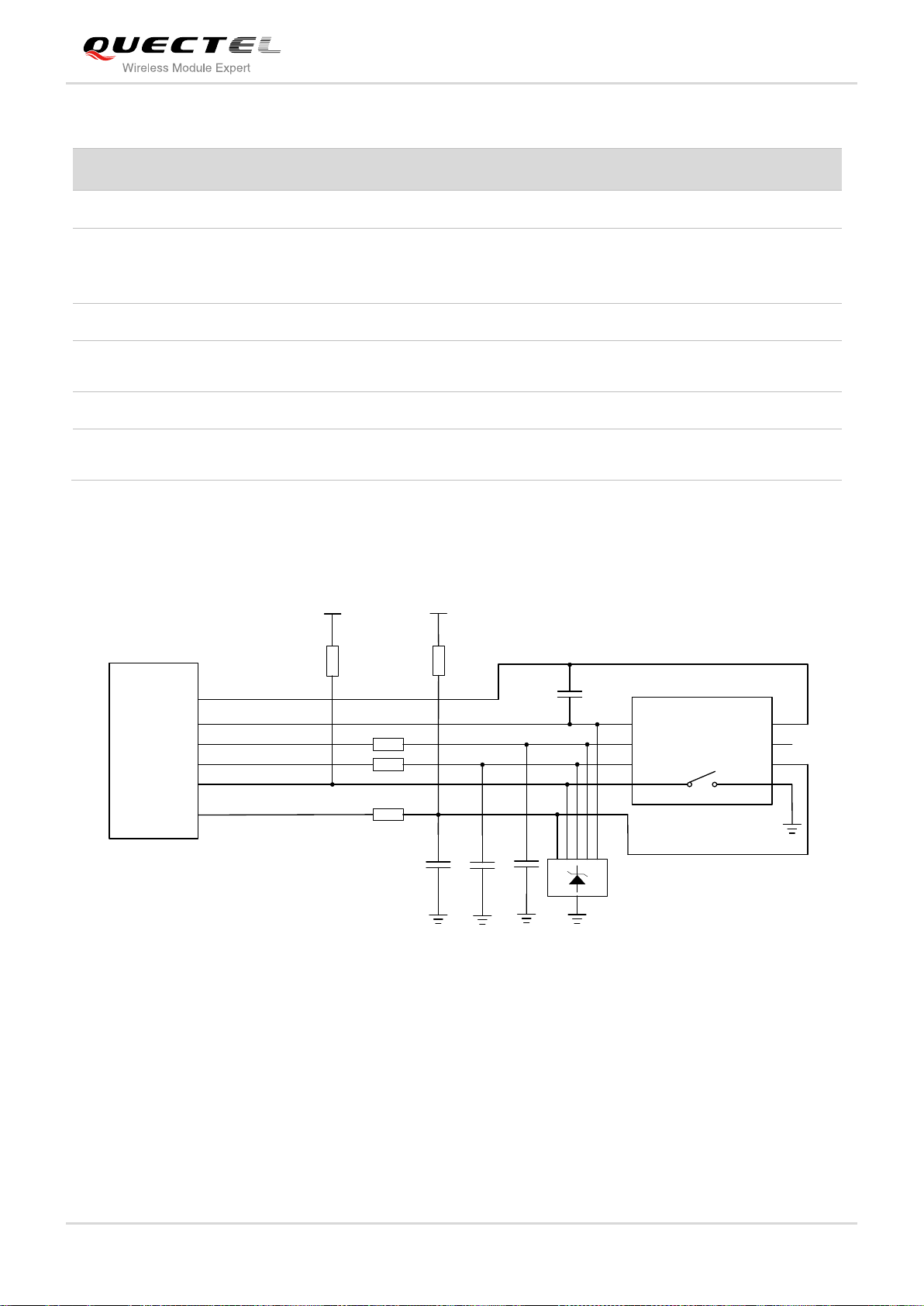

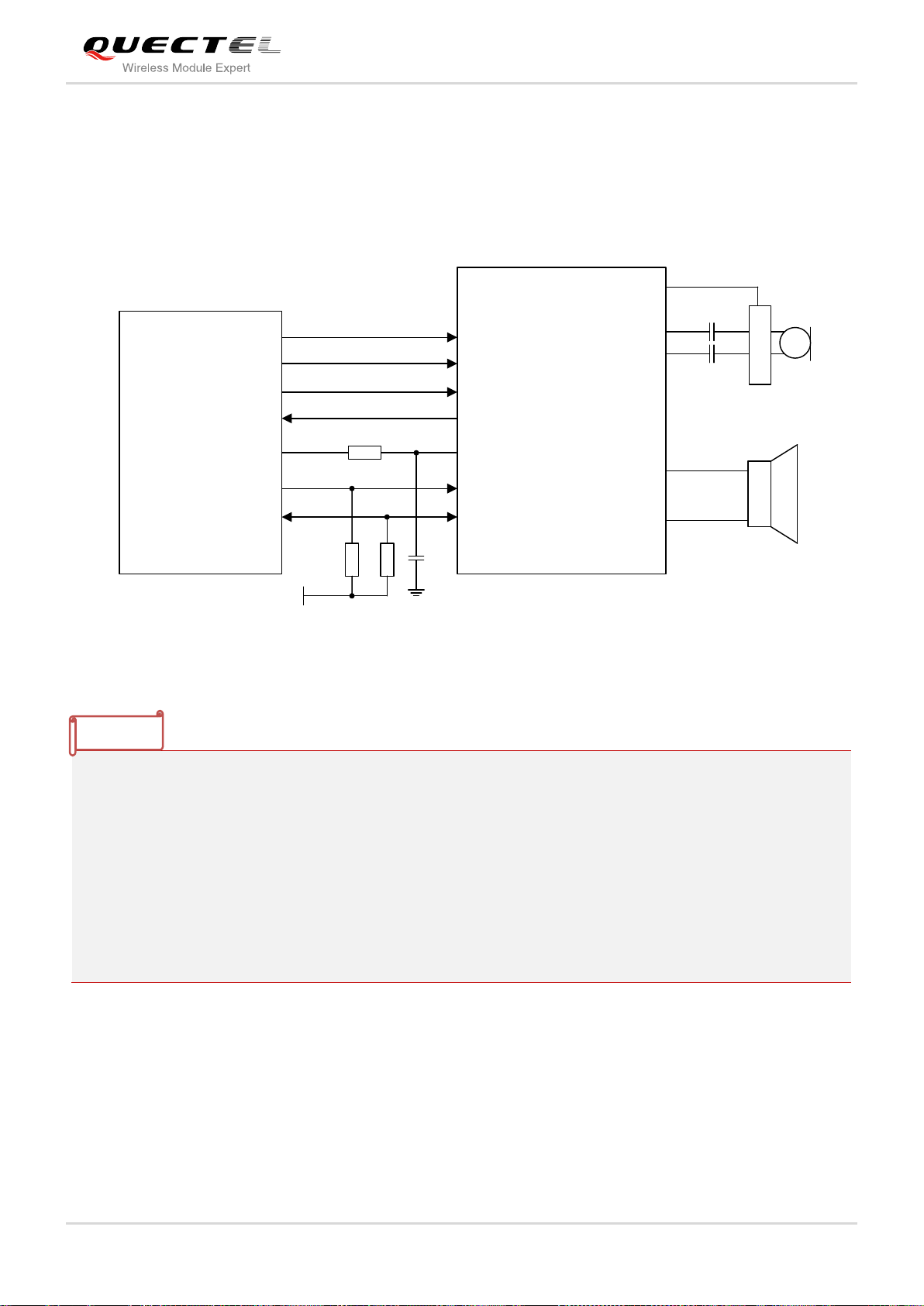

Table 12: Pin Definition of the USIM Interface

UG96 supports USIM card hot-plugging via the USIM_PRESENCE pin. The following figure shows the

reference design of the 8-pin USIM card.

If you do not need the USIM card detection function, keep USIM_PRESENCE unconnected. The

reference circuit for using a 6-pin USIM holder is illustrated as the following figure.

UG96_Hardware_Design Confidential / Released 41 / 75

Figure 23: Reference Circuit of the 8-Pin USIM Card

Page 43

UMTS/HSPA Module Series

Module

USIM_VDD

USIM_GND

USIM_RST

USIM_CLK

USIM_DATA

22R

22R

22R

100nF

USIM holder

GND

ESD

33pF 33pF 33pF

VCC

RST

CLK IO

VPP

GND

GND

15K

USIM_VDD

UG96 Hardware Design

Figure 24: Reference Circuit of the 6-Pin USIM Card

In order to enhance the reliability and availability of the USIM card in customer’s application, please follow

the criteria below in the USIM circuit design:

Keep layout of USIM card as close as possible to the module. Assure the length of the trace is as less

than 200mm as possible.

Keep USIM card signal away from RF and VBAT alignment.

Assure the ground between module and USIM holder short and wide. Keep the width of ground and

USIM_VDD no less than 0.5mm to maintain the same electric potential. The decouple capacitor of

USIM_VDD should be less than 1uF and must be near to USIM holder.

To avoid cross-talk between USIM_DATA and USIM_CLK, keep them away with each other and

shield them with surrounded ground.

In order to offer good ESD protection, it is recommended to add TVS such as WILL

(http://www.willsemi.com). The 22Ω resistors should be added in series between the module and the

USIM card so as to suppress the EMI spurious transmission and enhance the ESD protection. The

33pF capacitors are used for filtering interference of EGSM900. Please note that the USIM peripheral

circuit should be close to the USIM holder.

The pull-up resistor on USIM_DATA line can improve anti-jamming capability when long layout trace

and sensitive occasion is applied, and should be placed close to the USIM holder.

3.12. USB Interface

UG96 contains one integrated Universal Serial Bus (USB) transceiver which complies with the USB

1.1/2.0 specification and supports high speed (480Mbps) and full speed (12Mbps) mode. The USB

interface is primarily used for AT command, data transmission, software debug and firmware upgrade.

UG96_Hardware_Design Confidential / Released 42 / 75

Page 44

UMTS/HSPA Module Series

Pin Name

Pin No. I/O

Description

Comment

USB_DP

9

IO

USB differential data bus (positive).

Require differential

impedance of 90Ω.

USB_DM

10

IO

USB differential data bus (minus).

Require differential