Philips ne570 DATASHEETS

INTEGRATED CIRCUITS

NE570/571/SA571

Compandor

Product specification 1990 Jun 7

IC17 Data Handbook

Philips Semiconductors Product specification

NE570/571/SA571Compandor

DESCRIPTION

The NE570/571 is a versatile low cost dual gain control circuit in

which either channel may be used as a dynamic range compressor

or expandor. Each channel has a full-wave rectifier to detect the

average value of the signal, a linerarized temperature-compensated

variable gain cell, and an operational amplifier.

The NE570/571 is well suited for use in cellular radio and radio

communications systems, modems, telephone, and satellite

broadcast/receive audio systems.

FEA TURES

•Complete compressor and expandor in one IChip

•T emperature compensated

•Greater than 110dB dynamic range

•Operates down to 6VDC

•System levels adjustable with external components

•Distortion may be trimmed out

•Dynamic noise reduction systems

•Voltage-controlled amplifier

APPLICA TIONS

•Cellular radio

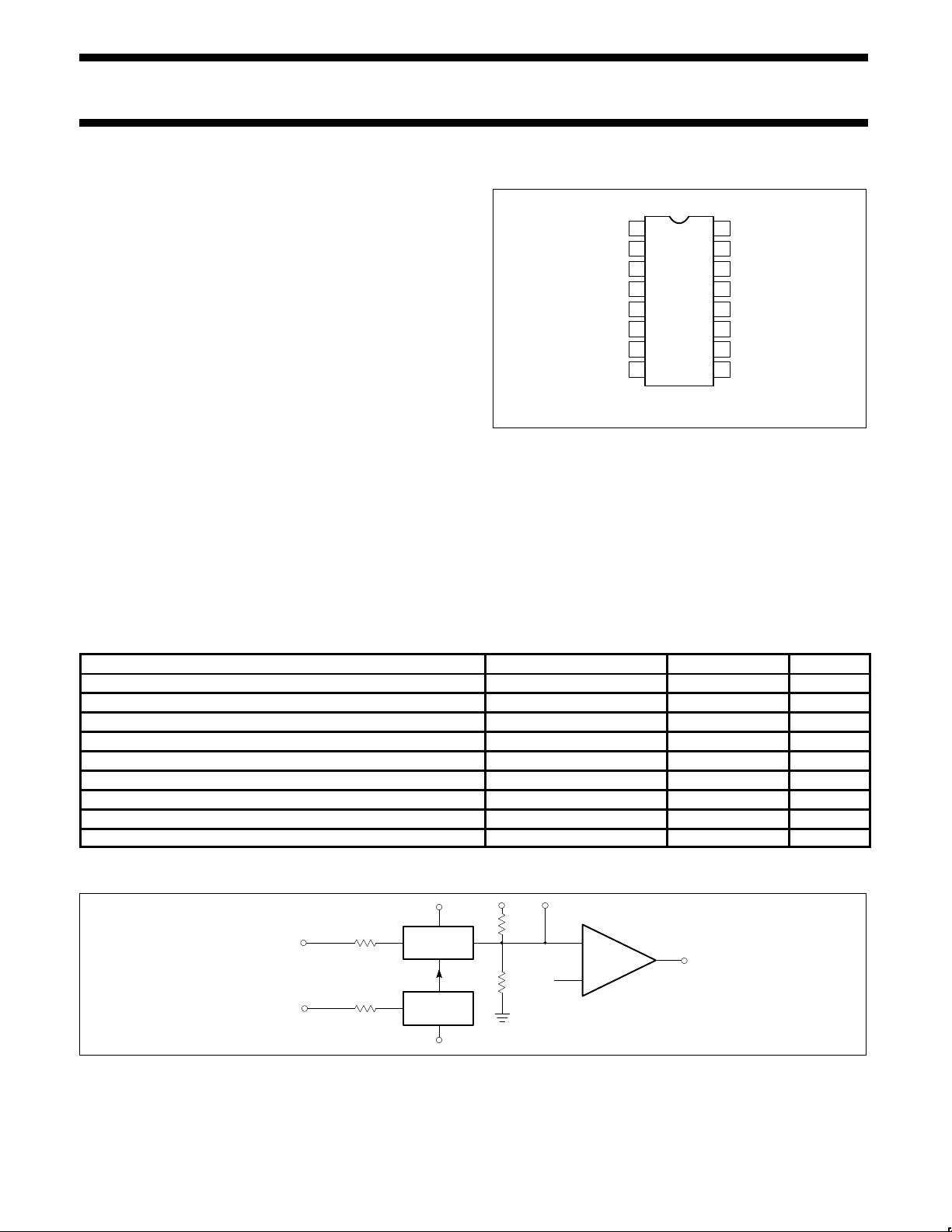

PIN CONFIGURATION

D, F, and N Packages

GND

1

2

3

4

5

6

1

3

7

8

TOP VIEW

RECT CAP 1

RECT IN 1

AG CELL IN 1

INV. IN 1

RES. R

OUTPUT 1

THD TRIM 1

NOTE:

1. SOL - Released in Large SO Package Only.

Figure 1. Pin Configuration

•T elephone trunk compandor—570

•T elephone subscriber compandor—571

•High level limiter

•Low level expandor—noise gate

•Dynamic filters

•CD Player

1

16

RECT CAP 2

15

RECT IN 2

14

AG CELL IN 2

13

V

CC

12

INV. IN 2

11

RES. R3 2

OUTPUT 2

10

THD TRIM 2

9

SR00675

ORDERING INFORMATION

DESCRIPTION TEMPERATURE RANGE ORDER CODE DWG #

16-Pin Plastic Small Outline Large (SOL) 0 to +70°C NE570D SOT162-1

16-Pin Ceramic Dual In-Line Package (Cerdip) 0 to +70°C NE570F 0582B

16-Pin Plastic Dual In-Line Package (DIP) 0 to +70°C NE570N SOT28-4

16-Pin Plastic Small Outline Large (SOL) 0 to +70°C NE571D SOT162-1

16-Pin Ceramic Dual In-Line Package (Cerdip) 0 to +70°C NE571F 0582B

16-Pin Plastic Dual In-Line Package (DIP) 0 to +70°C NE571N SOT28-4

16-Pin Plastic Small Outline Large (SOL) -40 to +85°C SA571D SOT162-1

16-Pin Ceramic Dual In-Line Package (Cerdip) -40 to +85°C SA571F 0582B

16-Pin Plastic Dual In-Line Package (DIP) -40 to +85°C SA571N SOT28-4

BLOCK DIAGRAM

∆G IN

RECT IN

R2 20k

R1 10k

THD TRIM

VARIABLE

RECTIFIER

GAIN

R3

RECT CAP

Figure 2. Block Diagram

R3 20k

R4 30k

INVERTER IN

V

REF

1.8V

–

OUTPUT

+

SR00676

1990 Jun 7 853-0812 99768

2

Philips Semiconductors Product specification

NE570/571/SA571Compandor

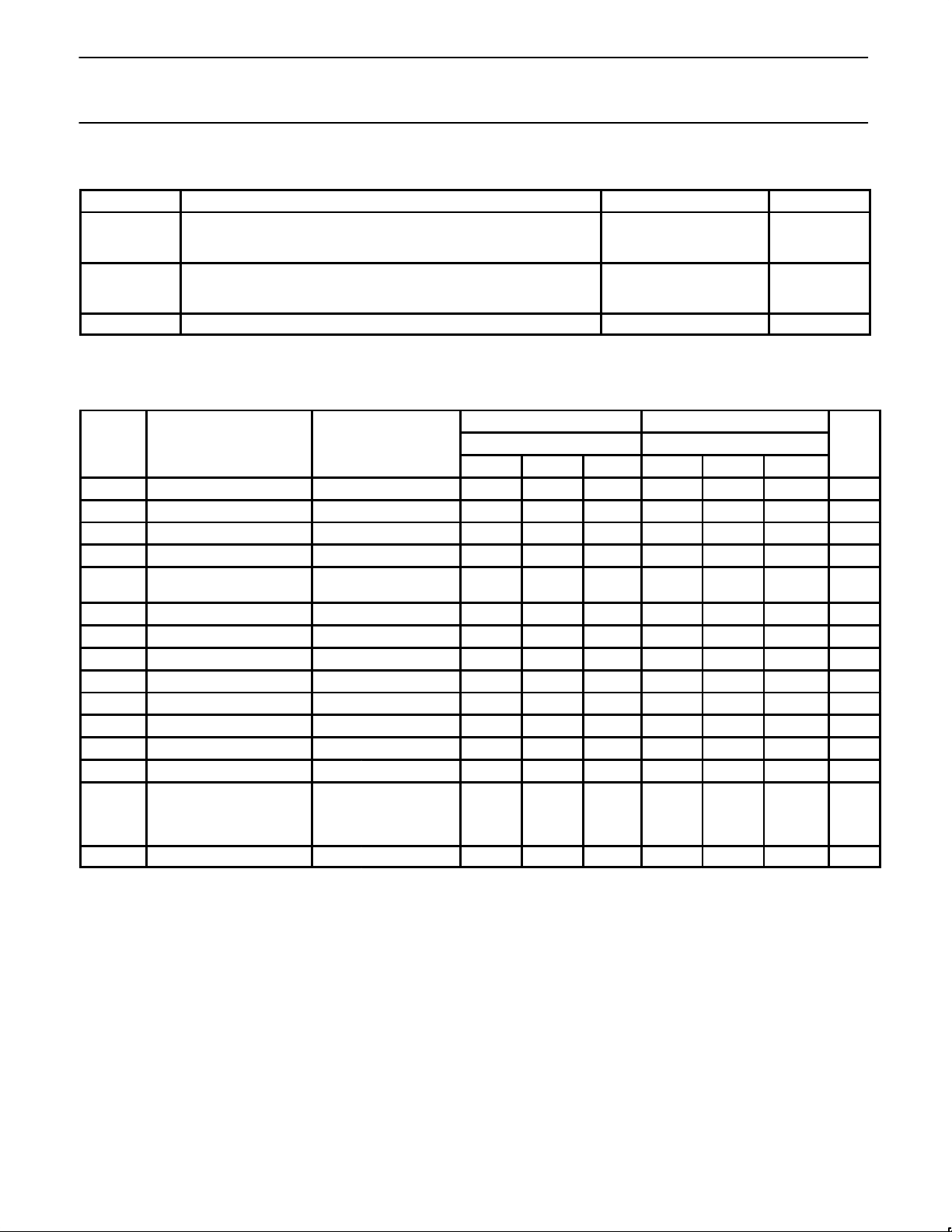

ABSOLUTE MAXIMUM RATINGS

SYMBOL PARAMETER RATING UNITS

Maximum operating voltage

V

CC

570

571

Operating ambient temperature range

T

A

P

D

Power dissipation 400 mW

NE

SA

AC ELECTRICAL CHARACTERISTICS

VCC = +6V, TA = 25°C; unless otherwise stated.

LIMITS LIMITS

SYMBOL PARAMETER TEST CONDITIONS NE570 NE/SA571

MIN TYP MAX MIN TYP MAX

V

I

I

OUT

SR Output slew rate ±.5 ±.5 V/µs

NOTES:

1. Input to V

2. Measured at 0dBm, 1kHz.

3. Expandor AC input change from no signal to 0dBm.

4. Relative to value at T

5. Electrical characteristics for the SA571 only are specified over -40 to +85°C temperature range.

6. 0dBm = 775mV

Supply voltage 6 24 6 18 V

CC

Supply current No signal 3.2 4.8 3.2 4.8 mA

CC

Output current capability ±20 ±20 mA

Gain cell distortion

2

Untrimmed

Trimmed

0.3

0.05

1.0

Resistor tolerance ±5 ±15 ±5 ±15 %

Internal reference voltage 1.7 1.8 1.9 1.65 1.8 1.95 V

Output DC shift

Expandor output noise No signal, 15Hz-20kHz

Unity gain level

Gain change

Reference drift

Resistor drift

Tracking error (measured

relative to value at unity

gain) equals [V

gain)] dB - V

3

6

2, 4

4

4

- VO (unity

O

dBm

2

Untrimmed ±20 ±100 ±30 ±150 mV

1

20 45 20 60 µV

1kHz -1 0 +1 -1.5 0 +1.5 dBm

±0.1 ±0.2 ±0.1 dB

±5 ±10 +2, -25 +20, -50 mV

+1, -0 +8, -0 %

Rectifier input,

= +6dBm, V1 = 0dB

V

2

V

= -30dBm, V1 = 0dB

2

+0.2

+0.2

-0.5, +1

Channel separation 60 60 dB

and V2 grounded.

1

= 25°C.

A

.

RMS

24

18

0 to 70

-40 to +85

0.5

0.1

+0.2

+0.2

5

2.0 %

-1, +1.5

VDC

°C

UNITS

dB

1990 Jun 7

3

Philips Semiconductors Product specification

NE570/571/SA571Compandor

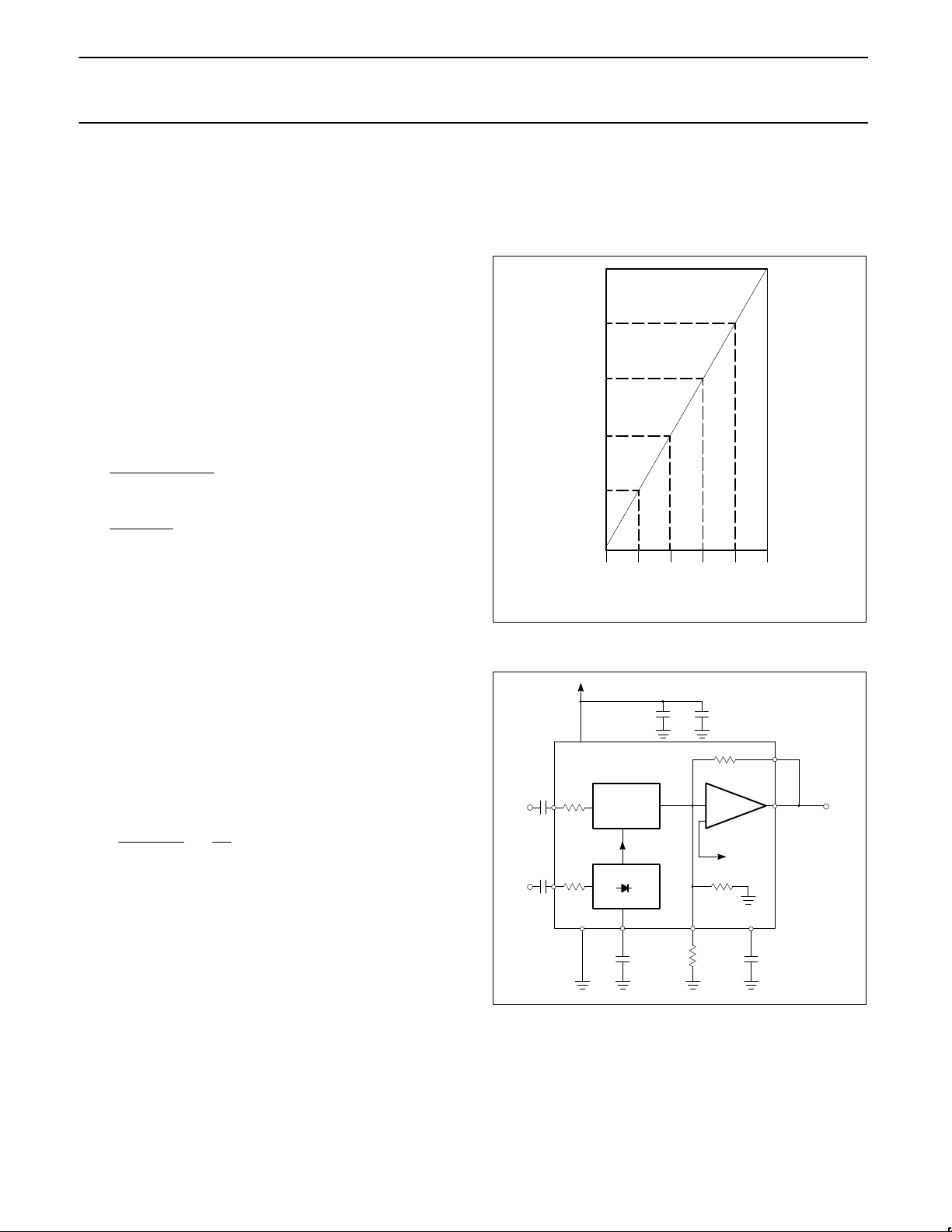

CIRCUIT DESCRIPTION

The NE570/571 compandor building blocks, as shown in the block

diagram, are a full-wave rectifier, a variable gain cell, an operational

amplifier and a bias system. The arrangement of these blocks in the

IC result in a circuit which can perform well with few external

components, yet can be adapted to many diverse applications.

The full-wave rectifier rectifies the input current which flows from the

rectifier input, to an internal summing node which is biased at V

The rectified current is averaged on an external filter capacitor tied

to the C

terminal, and the average value of the input current

RECT

controls the gain of the variable gain cell. The gain will thus be

proportional to the average value of the input signal for

capacitively-coupled voltage inputs as shown in the following

equation. Note that for capacitively-coupled inputs there is no offset

voltage capable of producing a gain error. The only error will come

from the bias current of the rectifier (supplied internally) which is

less than 0.1µA.

|V

G

V

IN

R

REF

1

|avg

or

|V

|avg

G

IN

R

1

The speed with which gain changes to follow changes in input signal

levels is determined by the rectifier filter capacitor. A small capacitor

will yield rapid response but will not fully filter low frequency signals.

Any ripple on the gain control signal will modulate the signal passing

through the variable gain cell. In an expander or compressor

application, this would lead to third harmonic distortion, so there is a

trade-off to be made between fast attack and decay times and

distortion. For step changes in amplitude, the change in gain with

time is shown by this equation.

G(t) (G

G

final

G

initial

)e t

final

; 10k x C

RECT

The variable gain cell is a current-in, current-out device with the ratio

I

controlled by the rectifier. IIN is the current which flows from

OUT/IIN

the ∆G input to an internal summing node biased at V

REF

following equation applies for capacitively-coupled inputs. The

output current, I

V

IN

I

IN

, is fed to the summing node of the op amp.

V

R

OUT

REF

2

V

IN

R

2

A compensation scheme built into the ∆G cell compensates for

temperature and cancels out odd harmonic distortion. The only

distortion which remains is even harmonics, and they exist only

because of internal offset voltages. The THD trim terminal provides

a means for nulling the internal offsets for low distortion operation.

The operational amplifier (which is internally compensated) has the

non-inverting input tied to V

, and the inverting input connected to

REF

the ∆G cell output as well as brought out externally. A resistor, R

brought out from the summing node and allows compressor or

expander gain to be determined only by internal components.

The output stage is capable of ±20mA output current. This allows a

+13dBm (3.5V

) output into a 300Ω load which, with a series

RMS

resistor and proper transformer, can result in +13dBm with a 600Ω

output impedance.

A bandgap reference provides the reference voltage for all summing

nodes, a regulated supply voltage for the rectifier and ∆G cell, and a

. The

REF

3

, is

bias current for the ∆G cell. The low tempco of this type of reference

provides very stable biasing over a wide temperature range.

The typical performance characteristics illustration shows the basic

input-output transfer curve for basic compressor or expander

circuits.

+20

.

+10

0

–10

–20

–30

–40

–50

–60

–70

–80

COMPRESSOR INPUT LEVEL OR EXPANDOR OUTPUT LEVEL (dBm)

–40 –30 –20 –10 0 +10

COMPRESSOR OUTPUT LEVEL

EXPANDOR INPUT LEVEL (dBm)

OR

SR00677

Figure 3. Basic Input-Output Transfer Curve

TYPICAL TEST CIRCUIT

VCC = 15V

5.12

8.2k

10µF

20k

30k

V

REF

8.9

200pF

6.11

7.10

V

O

SR00678

0.1µF

13

2.2µF

3.14

2.15

2.2

20k

10k

V

1

V

2

∆G

4 1.16

2.2

Figure 4. Typical Test Circuit

INTRODUCTION

Much interest has been expressed in high performance electronic

gain control circuits. For non-critical applications, an integrated

circuit operational transconductance amplifier can be used, but

when high-performance is required, one has to resort to complex

discrete circuitry with many expensive, well-matched components.

1990 Jun 7

4

Loading...

Loading...