Philips 74HCT243U, 74HCT243N, 74HCT243DB, 74HCT243D, 74HC243NB Datasheet

...

DATA SH EET

Product specification

File under Integrated Circuits, IC06

December 1990

INTEGRATED CIRCUITS

74HC/HCT243

Quad bus transceiver; 3-state

For a complete data sheet, please also download:

•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

December 1990 2

Philips Semiconductors Product specification

Quad bus transceiver; 3-state 74HC/HCT243

FEATURES

• Non-inverting 3-state outputs

• 2-way asynchronous data bus communication

• Output capability: bus driver

• ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT243 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT243 are quad bus transceivers featuring

non-inverting 3-state bus compatible outputs in both send

and receive directions.

They are designed for 4-line asynchronous 2-way data

communications between data buses.

The output enable inputs (

OEA and OEB) can be used to

isolate the buses.

The “243” is similar to the “242” but has non-inverting (true)

outputs.

QUICK REFERENCE DATA

GND = 0 V; T

amb

=25°C; tr=tf= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (PD in µW):

PD=CPD× V

CC

2

× fi+ ∑ (CL× V

CC

2

× fo) where:

fi= input frequency in MHz

fo= output frequency in MHz

∑ (CL× V

CC

2

× fo) = sum of outputs

CL= output load capacitance in pF

VCC= supply voltage in V

2. For HC the condition is VI= GND to V

CC

For HCT the condition is VI= GND to VCC− 1.5 V

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”

.

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

t

PHL/ tPLH

propagation delay

An to Bn;

Bn to A

n

CL= 15 pF; VCC= 5 V 6 11 ns

C

I

input capacitance 3.5 3.5 pF

C

I/O

input/output capacitance 10 10 pF

C

PD

power dissipation capacitance per transceiver notes 1 and 2 26 34 pF

December 1990 3

Philips Semiconductors Product specification

Quad bus transceiver; 3-state 74HC/HCT243

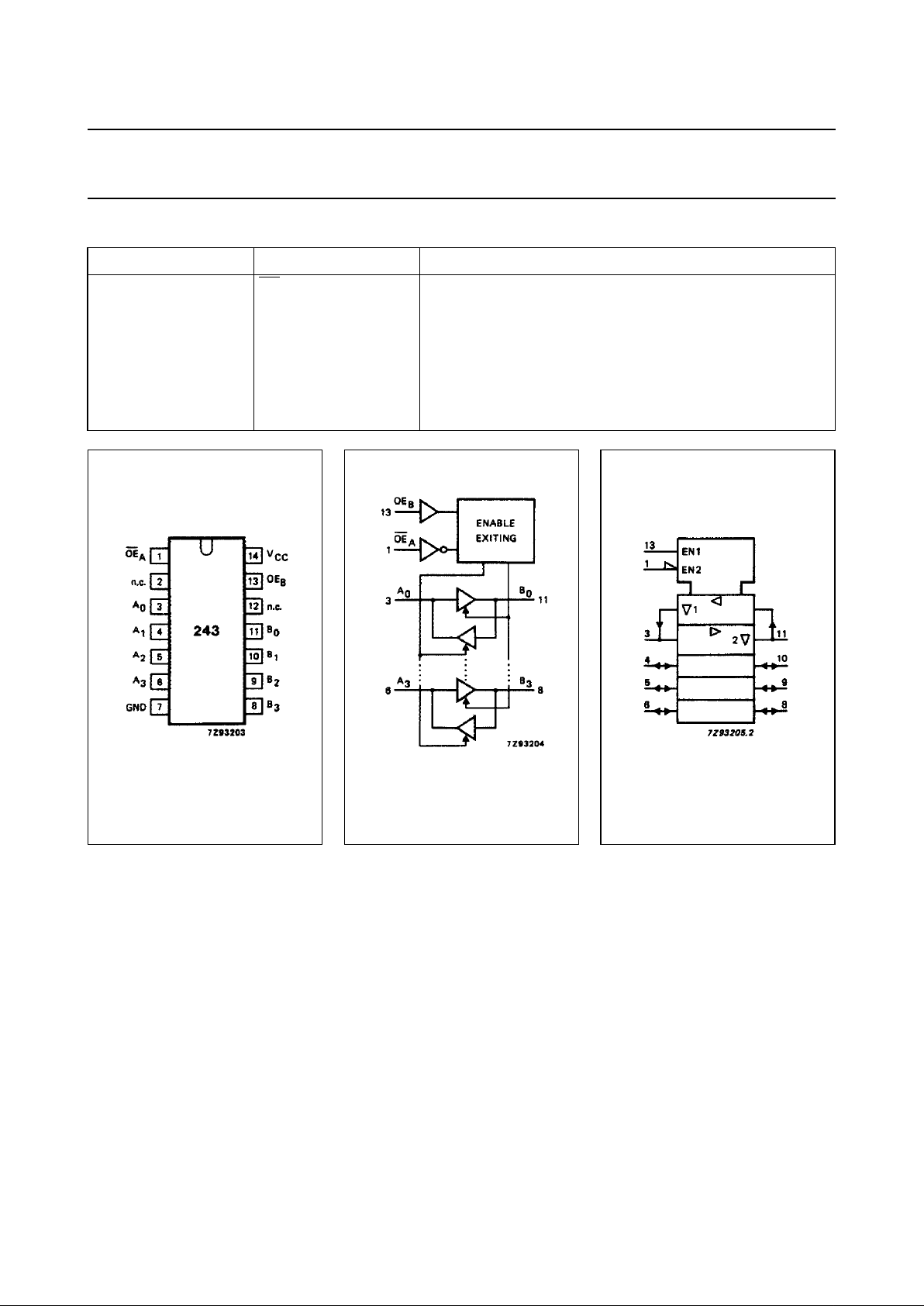

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1

OE

A

output enable input (active LOW)

2, 12 n.c. not corrected

3, 4, 5, 6 A

0

to A

3

data inputs/outputs

7 GND ground (0 V)

11, 10, 9, 8 B

0

to B

3

data inputs/outputs

13 OE

B

output enable input

14 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

Loading...

Loading...