MiTAC MSC-1610 User Manual

1

MSC-1610

Socket 370

w/VGA w/Dual LAN w/Audio

PCI Half-Size CPU Card

User’s Manual

MiTAC INC.

No.2, Chung-Hsiao street, Chidu, Keelung , Taiwan.

Tel : 886-2-2456-2255

Fax : 886-2-2456-9595

Part Number: : 5611M1610879 R1.1

Copyright © 2002 MiTAC INC.

2

Copyright Notice

Copyright © 2002 by MiTAC INC.

All Rights Reserved. Printed in Taiwan.

This publication is protected by copyright and all rights are

reserved. No part or whole of it may be reproduced or

transmitted in any form or by any means, electronic or

mechanical, including photocopying and recording without prior

consent of MiTAC INC.

The information in this document has been carefully checked

and is believed to be accurate. However, MiTAC INC.. assumes

no responsibility for any errors that may appear in this document.

The material contained herein is for informational purposes only.

The information contained in this document is subject to change

without any notices.

Acknowledgments

Award is a registered trademark of Award Software International,

Inc.

IBM, PC/AT, PS/2 and OS/2 are trademarks of International

Business Machines Corporation.

Intel, Pentium and Pentium/MMX are registered trademarks of

Intel Corporation.

Windows 95/98/ Me/ 2002/ XP and Windows NT are registered

trademarks of Microsoft Corporation.

All other product names or trademarks are properties of their

respective owners.

Contents

3

About This Manual

This manual provides information on the MSC-1610 single board

computer.

Chapter 1

provides general information, system assignment

tables, features and specifications of MSC-1610.

Chapter 2

contains dimensional drawings, jumper setting

information and connector pin assignments.

Chapter 3

describes component installations, device driver

installations, watchdog timer installation, and DiskOn Chip

installations.

Chapter 4

describes AWARD BIOS setup information, BIOS

POST code and how to update BIOS.

Contents

4

Contents

CHAPTER 1: INTRODUCTION............................................... 1

1.1 CHECK LIST ........................................................................................... 1

1.2 FEATURES .............................................................................................. 1

1.3 SPECIFICATIONS ..................................................................................... 4

1.4 SYSTEM ASSIGNMENTS.......................................................................... 3

11..44..11 II//OO PPoorrtt AAddddrreessss MMaapp..............................................................................................................................................................3

3

11..44..22 DDMMAA CChhaannnneell AAssssiiggnnmmeennttss............................................................................................................................................4

4

11..44..33 IInntteerrrruupptt AAssssiiggnnmmeennttss..............................................................................................................................................................4

4

11..44..44 MMeemmoorryy AAddddrreessss MMaapp..............................................................................................................................................................5

5

11..44..55 SSyysstteemm TTiimmeerr MMaapp........................................................................................................................................................................5

5

CHAPTER 2: HARDWARE CONFIGURATION ................... 6

2.1 COMPONENTS LOCATION ....................................................................6

2.2 JUMPERS ................................................................................................ 7

22..22..11 CCPPUU BBaassee SSppeeeedd SSeelleecctt ((JJPP1111,, JJPP1122))............................................................................................................8

8

22..22..22 PPoowweerr SSoouurrccee ((JJPP11,, JJ44,, JJ11))............................................................................................................................................8

8

22..22..33CCOOMM22 MMooddee SSeelleecctt ((JJPP22))....................................................................................................................................................8

8

22..22..44 VVGGAA EEnnaabbllee // DDiissaabbllee ((JJPP1100))......................................................................................................................................8

8

22..22..55 LLCCDD VVoollttaaggee SSeelleeccttiioonn ((JJPP55))........................................................................................................................................8

8

22..22..66 DDiisskk OOnn CChhiipp ((MM--SSyysstteemm)) AAddddrreessss SSeelleecctt ((JJPP99))............................................................................9

9

22..22..77 WWaattcchh DDoogg TTiimmeerr ((JJPP88))........................................................................................................................................................9

9

22..22..88 RRTTCC CCMMOOSS CClleeaarr ((JJPP1100))..................................................................................................................................................9

9

22..22..99 EETTHHEERRNNEETT PPoorrtt 11 EEnnaabbllee // DDiissaabbllee ((JJPP44))..........................................................................................9

9

22..22..1100 EETTHHEERRNNEETT PPoorrtt 22EEnnaabbllee // DDiissaabbllee ((JJPP77))........................................................................................9

9

2.3 CONNECTORS....................................................................................... 10

22..33..11 SSttaannddbbyy PPoowweerr CCoonnnneeccttoorr ((JJ11))............................................................................................................................112

2

22..33..22 FFrroonntt PPaanneell CCoonnnneeccttoorr ((JJ44))......................................................................................................................................112

2

22..33..33 EExxtteerrnnaall KKeeyybbooaarrdd CCoonnnneeccttoorr ((JJ22))................................................................................................................112

2

22..33..44 UUSSBB PPoorrtt 11 ccoonnnneeccttoorr ((UUSSBB11))................................................................................................................................112

2

22..33..55 IInnffrraarreedd CCoonnnneeccttoorr ((IIRR))....................................................................................................................................................112

2

22..33..66 EExxtteerrnnaall PPoowweerr CCoonnnneeccttoorr ((PP11))..........................................................................................................................113

3

22..33..77 PPSS22 KKeeyybbooaarrdd // MMoouussee CCoonnnneeccttoorr ((KKBBMMSS))......................................................................................113

3

22..33..88 VVGGAA CCRRTT CCoonnnneeccttoorr ((VVGGAA))......................................................................................................................................113

3

22..33..99 LLCCDD CCoonnnneeccttoorr ((LLCCDD))......................................................................................................................................................114

4

22..33..1100 HHDDDD ((IIDDEE)) CCoonnnneeccttoorrss ((IIDDEE11,, IIDDEE22))..................................................................................................115

5

Contents

5

22..33..1111 FFDDDD CCoonnnneeccttoorr ((FFDDDD))................................................................................................................................................116

6

22..33..1122 SSeerriiaall PPoorrtt 22 CCoonnnneeccttoorr ((CCOOMM22)) –– RRSS223322//442222//448855 CCoonnnneeccttoorr..............117

7

22..33..1133 CCPPUU FFaann CCoonnnneeccttoorr ((FFAANN11))................................................................................................................................117

7

22..33..1144 LLAANN PPoorrtt CCoonnnneeccttoorr ((LLAANN11//LLAANN22))..........................................................................................................117

7

22..33..1155 PPaarraalllleell PPoorrtt //CCOOMM11//UUSSBB22//AAuuddiiooCCoonnnneeccttoorr((CCNN11))........................................................118

8

CHAPTER 3: SYSTEM INSTALLING .................................. 19

3.1 INSTALLING THE DIMMS..................................................................... 20

3.2 INSTALLING THE CPU .......................................................................... 21

3.3 COMPLETING THE INSTALLATION ......................................................... 22

3.4 VIA SERVICE PACK (VIA 4IN 1).......................................................... 22

33..44..11 VVIIAA 44 iinn 11 DDrriivveerr IInnssttaallllaattiioonn PPrroocceedduurree::............................................................................................222

2

33..44..22 AAbboouutt VVIIAA 44 IINN 11 ddrriivveerrss::..............................................................................................................................................223

3

3.5 INSTALLING AUDIO DRIVER .............................................................. 24

3.6 INSTALLING VGA DRIVER .................................................................. 25

33..66..11 VVGGAA DDrriivveerr ffoorr WWiinnddoowwss 9955//9988............................................................................................................................225

5

33..66..22 VVGGAA DDrriivveerr ffoorr WWiinnddoowwss NNTT 44..00........................................................................................................................226

6

33..66..33 VVGGAA DDrriivveerr ffoorr WWiinnddoowwss 22000000..............................................................................................................................229

9

33..66..44 VVGGAA DDrriivveerr ffoorr WWiinnddoowwss XXPP....................................................................................................................................330

0

3.7 CONFIGURING ETHERNET INTERFACE ..................................................31

33..77..11 CCoonnnneecctt tthhee NNeettwwoorrkk CCaabbllee........................................................................................................................................331

1

33..77..22 MMaakkiinngg aa SSeettuupp FFllooppppyy DDiisskk....................................................................................................................................332

2

33..77..33 CCoonnffiigguurriinngg tthhee NNeettwwoorrkk aanndd IInnssttaalllliinngg tthhee DDrriivveerrss............................................................332

2

3.8 INSTALLING DISKONCHIP OF M-SYSTEMS........................................... 39

33..88..11 IInnssttaalllliinngg tthhee DDiisskk--OOnn--CChhiipp 22000000 ::................................................................................................................339

9

33..88..22 CCoonnffiigguurriinngg tthhee DDiisskkOOnnCChhiipp 22000000 aass tthhee bboooott ddeevviiccee::..................................................440

0

33..88..33 CCoonnffiigguurriinngg tthhee DDiisskkOOnnCChhiipp 22000000 aass tthhee ffiirrsstt ddrriivvee::........................................................440

0

CHAPTER 4: BIOS CONFIGURATION ............................... 42

4.1 ENTERING SETUP ................................................................................. 42

4.2 THE MAIN MENU................................................................................. 43

4.3 STANDARD CMOS SETUP ................................................................... 44

4.4 IDE PRIMARY MASTER........................................................................ 45

4.5 ADVANCED BIOS FEATURES ............................................................... 46

4.6 ADVANCED CHIPSET FEATURES ........................................................... 47

4.7 INTEGRATED PERIPHERALS .................................................................. 48

4.8 POWER MANAGEMENT SETUP ............................................................. 49

Contents

6

4.9 PC HEALTH STATU S............................................................................. 50

4.10 FREQUENCY/VOLTAGE CONTROL ...................................................... 51

4.11 LOAD FALL-SAFE DEFAULTS.............................................................. 52

4.12 LOAD OPTIMIZED DEFAULTS ............................................................. 53

4.13 POWER ON BOOT............................................................................... 53

4.14 BIOS REFERENCE – POST CODES.................................................... 54

4.15 UPDATING BIOS................................................................................ 59

1

C h a p t e r 1

Introduction

This chapter gives a brief introduction and provides the

specifications of the MSC-1610 Half-sized single board computer.

1.1 Check List

Before getting started, please check if your

MSC-1610package includes the following items:

MSC-1610 Socket 370 CPU board x 1pc

Driver & Utility CD x 1pc

FDD cable x 1 pc

HDD cable x 1 pc

Printer extension cable with bracket x 1 pc

Audio extension cable with bracket x 1 pc

COM1/COM2 cable with bracket x 1pc

USB extension cable. (Option)

User’s manual x 1 pc

1.2 Features

The MSC-1610 is a full featured, industrialized, half-size

single board computer with a high-frequency Intel Pentium

III

®

, or Celeron® processor (FC-PGA & FC-PGA2 package)

that brings advanced CPU technology and processing power

to the latest PCI applications. The Via Apollo Pro133T

Chipset built into the single board computer is the most

efficient and reliable way to upgrade existing PCI systems to

Pentium III technology.

MSC-1610 User’s Manual

2

The MSC-1610 uses the PCI form factor with Socket 370 to

fit in FC-PGA and FC-PGA2 processor from Intel. The PCI

design contains one gold leaf edge connectors compatible

with PCI connectors to allow all peripherals to interface with

the processor. This lets the MSC-1610 take advantage of the

high pin density and strict electro-mechanical criteria

imposed on PCI connectors.

The MSC-1610single board computer is further enhanced by

the CHIPS 69030 Graphics Accelerator to deliver the most

advanced graphics and video support available. The 69030

supports a wide variety of monochrome and color panels,

such as: Single-Panel, Single-Drive (SS) and Dual-Panel,

Dual-Drive (DD), standard and high resolution, passive STN

and active matrix TFT LCD, and EL panels. With HiQColor

technology, up to 256 gray scales are supported on passive

STN LCDs. Up to 16.7M different colors can be displayed

on passive STN LCDs and up to 16.7M colors on 24 bit

active matrix LCDs.

The MSC-1610combines the many features needed for

system operation into one compact single board computer.

These include 10/100 TX LAN adapter, Ultra/DMA drive

controllers, high performance serial ports, enhanced parallel

port, and the latest BIOS features. Additional enhancements

to the MSC-1610 include four USB ports and a

programmable watchdog timer. Single dual in-line memory

module (DIMM) sockets support up to 512MB of

synchronous DRAM (SDRAM) memory. An internal 64-bit

second level (L2) cache supports 128/512k of memory. The

L2 cache speed is half the CPU core frequency. The Celeron

L2 cache equals 128k running at full CPU core.

Chapter 1: Introduction

3

The VIA Apollo Pro133T chipset in the MSC-1610

incorporates the latest microprocessor technology from Intel

to provide the increased bandwidth needed to operate your

system bus at speeds up to 133MHz. (The VIA Apollo

Pro133T chipset uses one chipset for three 66MHz

100MHz and 133MHz system designed in Pentium III, and

Celeron processors with speeds of 733, 850 and 1.26 GHz.).

The VIA Apollo Pro133T chipset is a two-chip set

comprised of the VT82C694T North Bridge Controller and

the VT82C686B South Bridge Controller. PC100/133

SDRAM provide the bandwidth necessary for running

demanding software and Internet applications while

benefiting from the reliability and cost advantages of

SDRAM infrastructure. The VIA Apollo Pro133T chipset is

a PCI Rev 2.2 compliant that supports 3.3V and 5V 33MHz

PCI operations. The VIA694T chip includes Desktop Power

Management support, enhanced DMA controller and an

integrated IDE controller with Ultra DMA/100 support. In

addition, it provides USB host interface support for four

USB ports and a System Management Bus (SMB) with

support for DIMM Serial PD.

MSC-1610 User’s Manual

4

1.3 Specifications

Processors Supported

Intel Pentium III

- FC-PGA2 133Mhz FSB (1.13GHz-1.26GHz)

- FC-PGA 100 /133MHZ (500E-1GHz)

Intel Celeron (FC-PGA & FC-PGA2)

- FC-PGA2 100MHz FSB (1AGHz- 102GHz)

- FC-PGA 66 / 100MHz (533A-1GHz)

Processor Clock Frequency and Bus Speed

66 /100 /133MHz internal frequency and bus speed

Memory Capacity

32MB minimum

512MB maximum

DIMM Support

1 DIMM, gold contacts, 168-pin

Non-ECC / ECC compatible

Memory Speed Required

64 / 72-bit SDRAM ( 66 / 100 / 133 MHz )

BIOS

Hi-Flex Pentium AWARD BIOS, Flash EPROM

support, Plug-and-Play compatible

2Mb flash upgradeable supporting BIOS upgrade via

software

Full support for Year 2000 and leap-year date functions

Chapter 1: Introduction

5

Chipset

VIA Apollo Pro133 chipset

- VT82C694T North Bridge Controller

- VT82C696B South Bridge Controller

C&T 69030 AGP bus with Windows accelerator and

Video playback.

Display

C&T 69030 integrated 4M SDRAM for the

graphics/video frame buffer.

C&T 69000 integrated 2M SDRAM for option.

- Support 1/4 VGA, VGA, SVGA, XGA, SXGA,and

UXGA panels. It includes the Chips’ proprietary

TMED ™ technology to support 16 million colors on

STN/ DSTN panels.

-Display connector: DB-15 VGA connector for CRT

monitor and 2x20 pin header for Flat-panel

LAN Controller

Dual INTEL 82559 Ethernet controller, 10/100 Tx

with RJ-45 connector.

LAN2 for option.

EIDE Disk Controller (dual port)

Four fixed disk drives supported (two each on primary

and secondary)

PIO Mode 4 and Ultra DMA/100 supported.

Full support for LS-120 HD floppy drive.

Floppy Diskette Controller (dual port)

Support 2.88MB,1.44MB/720KB and 1.2MB/360KB

floppy drives.

MSC-1610 User’s Manual

6

Serial Ports

One RS232, 16C550-compatible, FIFO buffer

One RS-232/RS-422/RS-485 selectable

Parallel Port

Single parallel port controller with bi-directional

compatibility

EPP and ECP enhanced port modes.

PS/2 Keyboard and Mouse port

Microsoft compatible

6-pin mini-DIN connector at rear panel

Power supplied through +5VDC self-healing fuse

Universal Serial Bus (USB)

Universal Host Controller Interface (UHCI)

configuration

Four USB connectors at rear panel via separate cable

and bracket assembly (optional)

Power supplied through +5VDC self-healing fuse

Sound

AC’97 supported with full duplex, independent sample

rate converter for audio recording and playback

Watchdog Timer

Reset CPU automatically if CPU stops operating

Reset CPU automatically if +5VDC varies more than

10%

Jumper or software disable/enable

MSC-1610 User’s Manual

2

Disk On Chip of M-system

Support one Single Chip Flash Disk in 32Pin DIP

JEDEC socket.

Real-time Clock

SGS-THOMSON M48T86MH1 compatible

256 bytes of battery-backed RAM

On chip lithium battery with 10 years data retention.

Operating Environment

Temperature: 0 to 55 °C

Humidity: 5 to 90% RHNC

Storage Environment

Temperature: -40 to 85 °C

Humidity: 10 to 90% RHNC

Power Requirements

+5V and +12V

Notes: 1) +5V current draw is processor dependent.

2) Onboard +3.3 V is regulated down from the +5V source.

Chapter 1: Introduction

3

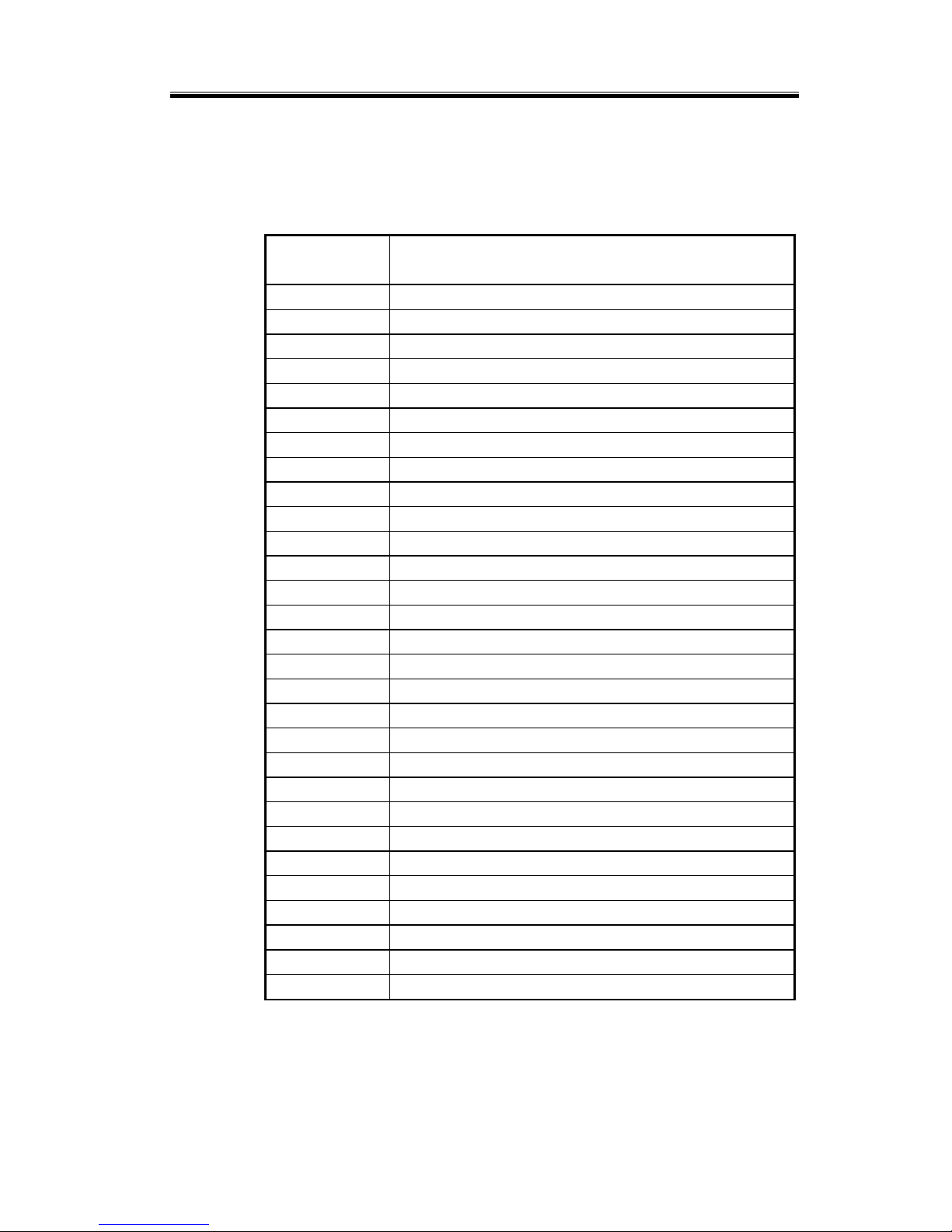

1.4 System Assignments

1.4.1 I/O Port Address Map

Address

( HEX )

Device

000-01F DMA controller 1

020-021 Interrupt controller 1

040-05F Timer 1 & 2

043 Disable Watch-dog timer operation (read)

060-06F Keyboard controller

070-07F Real Time Clock, Non_Maskable interrupt

080-09F DMA page register

0A0-0BF Interrupt controller 2

0C0-0DF DMA controller 2

0F0 Clear math. Coprocessor busy signal

0F1 Reset math. Coprocessor

0F8-0FF Math. Coprocessor

1F0-1F8 Fixed disk controller

200-207 Game port

278-27F Parallel port #2 (LPT3)

2E8-2EF Serial port #4 (COM 4)

2F8-2FF Serial port #2 (COM 2)

300-31F Prototype card / Streaming Tape Adapter

378-37F Parallel port #1 (LPT2)

380-38F SDLC, Bisynchronous 2

3A0-3AF SDLC, Bisynchronous 1

3B0-3BF Monochrome Display, Parallel port 0 (LPT1)

3C0-3CF EGA card

3D0-3DF CGA card

3E8-3EF Serial port #3 (COM3)

3F0-3F7 Floppy Disk controller

3F8-3FF Serial port #1 (COM1)

443 Enable Watch-dog timer operation (read)

CF8-CFF Chipset Address

MSC-1610 User’s Manual

4

1.4.2 DMA Channel Assignments

Channel Function

0 Available

1 Available

2 Floppy disk ( 8 bit transfer )

3 Available

4 Cascade for DMA controller 1

5 Available

6 Available

7 Available

1.4.3 Interrupt Assignments

Interrupt # Interrupt Source

IRQ 0 Interval timer

IRQ 1 Keyboard

IRQ 2 Interrupt from controller 2 (cascade)

IRQ 3 Serial port 2

IRQ 4 Serial port 1

IRQ 5 Parallel port 2

IRQ 6 Floppy disk controller

IRQ 7 Parallel port 1

IRQ 8 Real-time clock

IRQ 9 Cascade to controller 1 (IRQ 2)

IRQ 10 Available

IRQ 11 Available

IRQ 12 PS/2 Mouse

IRQ 13 Math coprocessor

IRQ 14 Hard disk controller (Primary)

IRQ 15 Hard disk controller (Secondary)

Chapter 1: Introduction

5

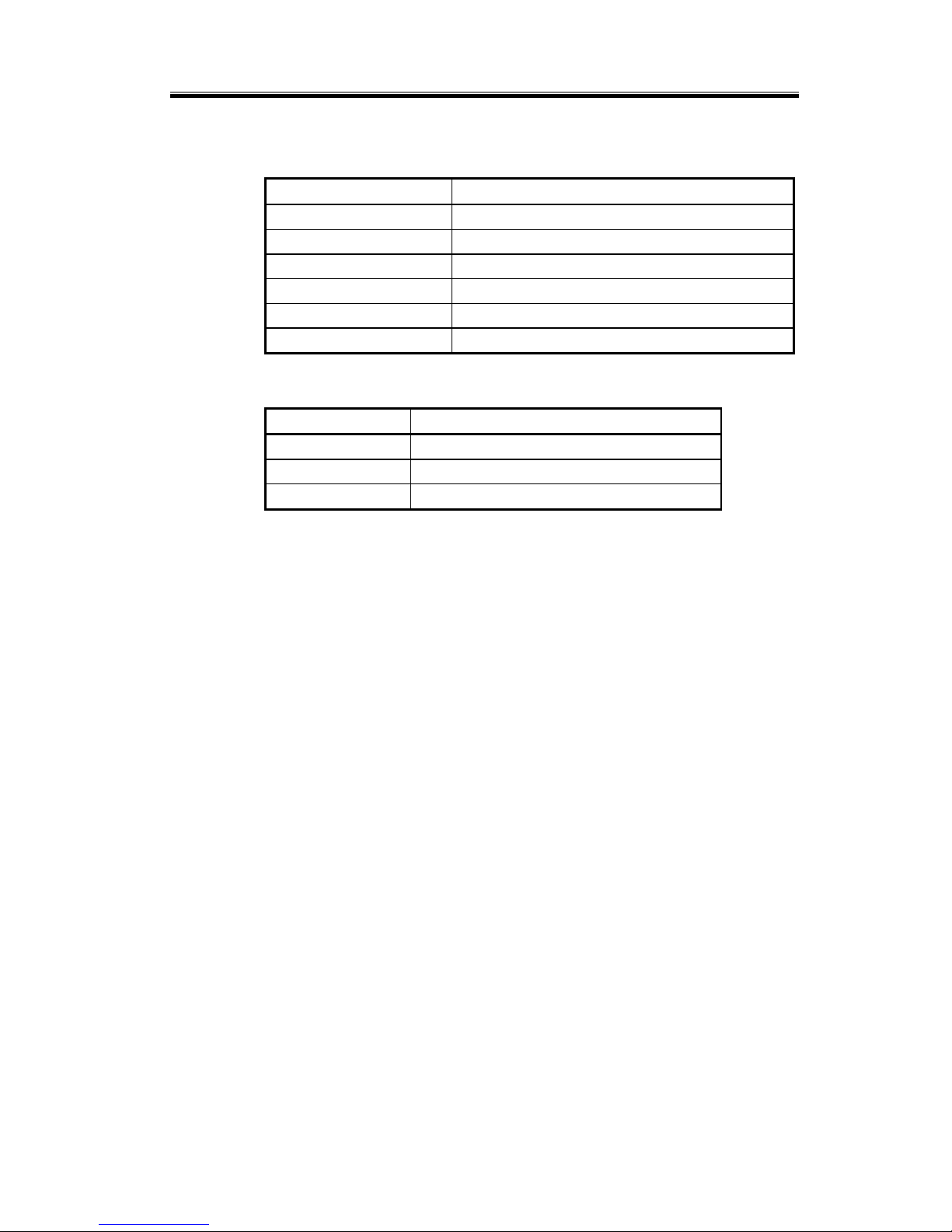

1.4.4 Memory Address Map

Address ( HEX ) Device

0000000-009FFFF System memory

00A0000-00BFFFF Display memory

00C0000-00C7FFF VGA BIOS ROM

00C8000-00EFFFF I/O device BIOS ROM or RAM buffer

00F0000-00FFFFF System BIOS ROM

0100000-BFFFFFF System extension memory

1.4.5 System Timer Map

Timer # Assignment

1 System timer interrupt

2 DRAM Refresh Request

3 Speaker tone generator

6

C h a p t e r 2

Hardware Configuration

This chapter explains how to properly set the jumpers and

how to use the connectors of MSC-1610.

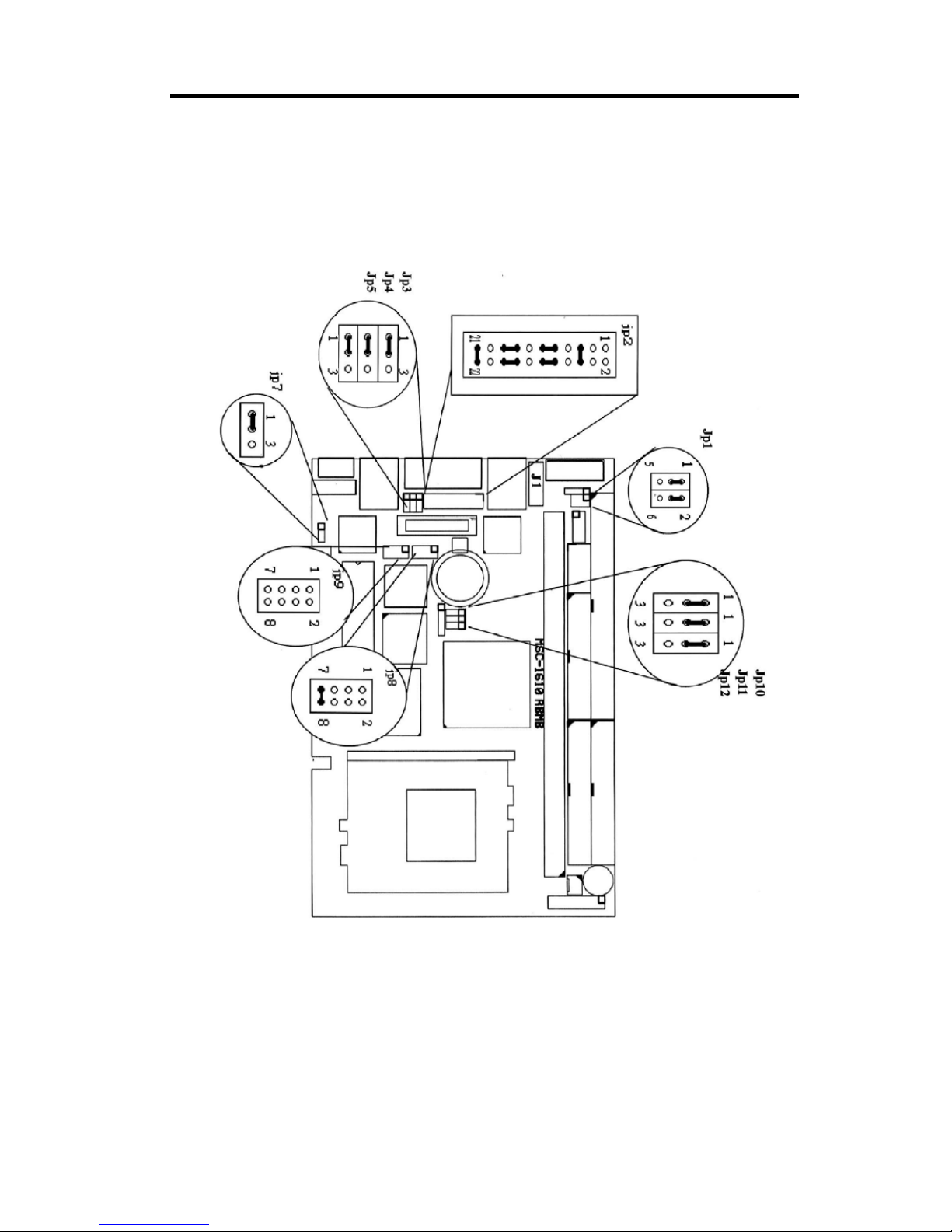

2.1 Components Location

This figure shows the locations of all sockets, jumpers,

connectors and major components on the MSC-1610. All

configuration of the MSC-1610 are in correct positions when it

is shipped from the factory. MSC-1610 will function as

required without modification. However, in order to allow

system tuning, some of the jumpers are designed to be user

configurable.

Chapter 2: Hardware Configuration

7

2.2 Jumpers

The location of the various jumpers on the MSC-1610 are as

shown below:

The succeeding sections provide details on how to properly

set these jumpers.

MSC-1610 User’s Manual

8

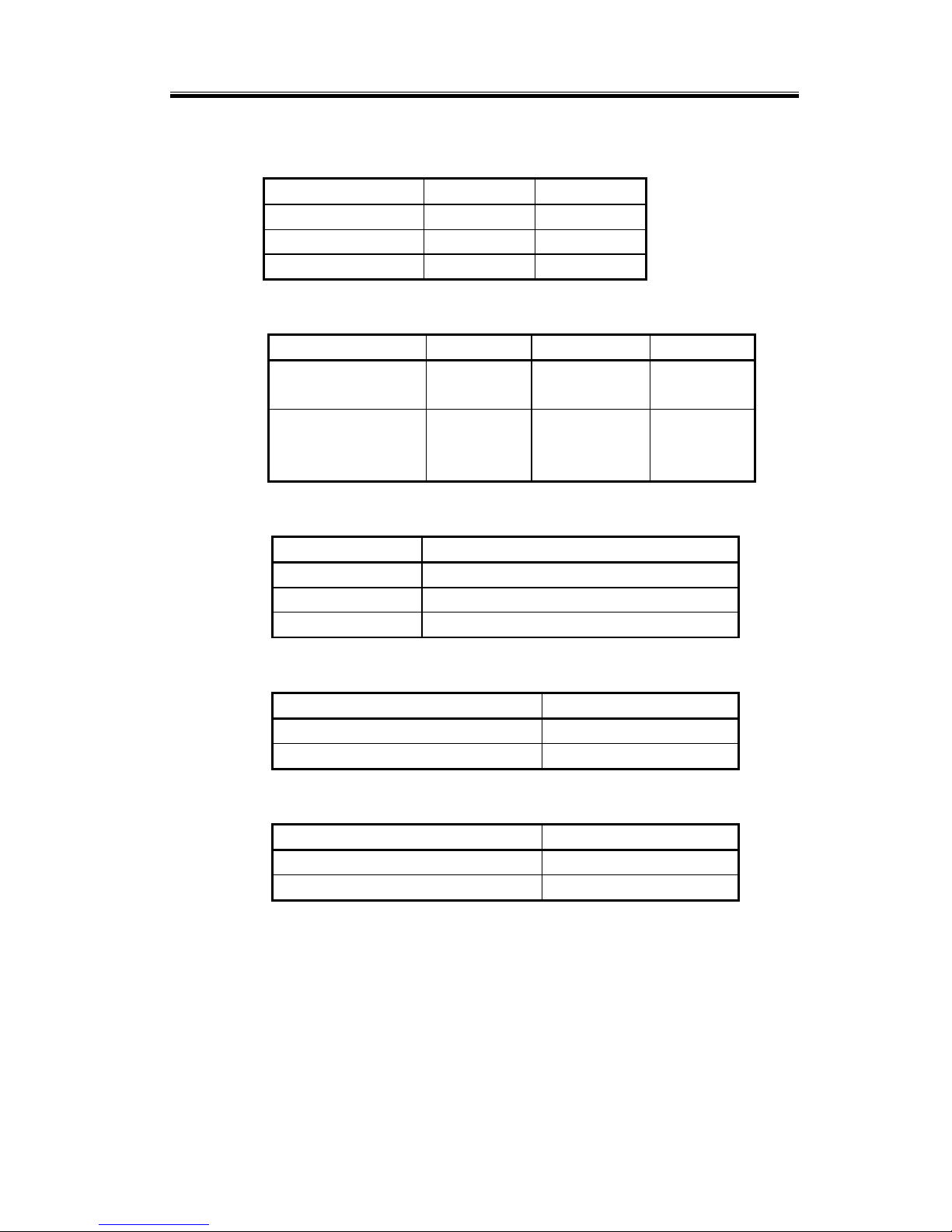

2.2.1 CPU Base Speed Select (JP11, JP12)

CPU clock JP11 JP12

66.6MHZ 2-3 2-3

100MHz 1-2 2-3

Auto /133 MHz *1-2 *1-2

2.2.2 Power Source (JP1, J4, J1)

Power Source JP1 J4 J1

Use AT

Power Supply

3-5,

4-6

NC NC

Use ATX Power

Supply on

Backplane

*1-3,

*2-4

17-18 to

Power Switch

Cable to

Backplane

2.2.3COM2 Mode Select (JP2)

Mode JP2

RS232 *5-6,9-11,10-12,15-17,16-18,21-22

RS422 3-4,7-9,8-10,13-15,14-16,21-22

RS485 1-2,7-9,8-10,19-20

2.2.4 VGA Enable / Disable (JP10)

Enable / Disable JP10

On board VGA ENABLE *1-2

On board VGA DISABLE 2-3

2.2.5 LCD Voltage Selection (JP5)

Voltage Selector JP5

5V *1-2

3.3V 2-3

Chapter 2: Hardware Configuration

9

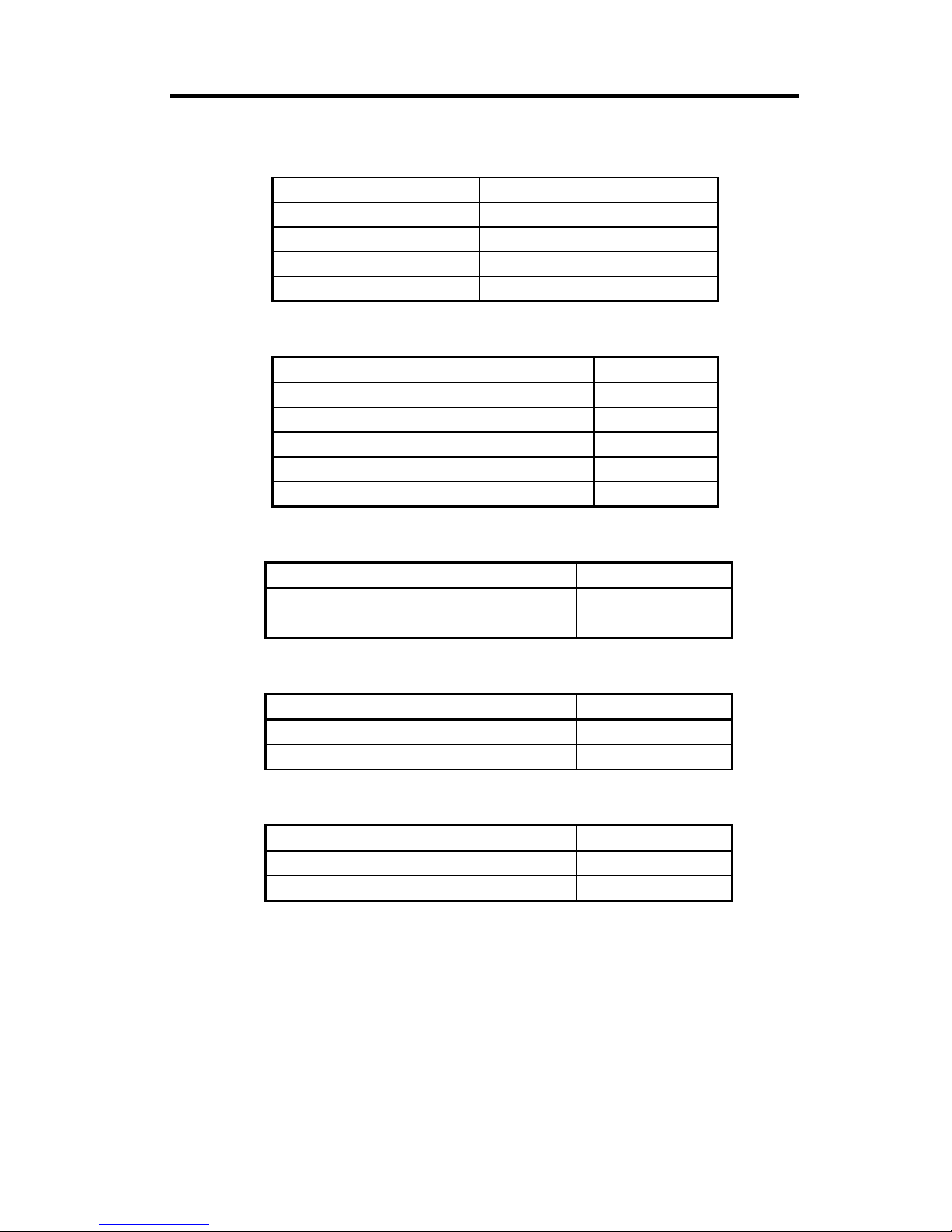

2.2.6 Disk On Chip (M-System) Address Select (JP9)

I/O ADDRESS JP9

D0000-D1FF *1-2

D200-D3FF 3-4

D400-D5FF 5-6

D600-D7FF 7-8

2.2.7 Watch Dog Timer (JP8)

Watch Dog Timer JP8

1 Sec. 1-2

10 Sec. *3-4

30 Sec. 5-6

Enable 7-8(open)

Disable *7-8(close)

2.2.8 RTC CMOS Clear (JP10)

CMOS Selection JP10

Normal *1-2

Clear CMOS 2-3

2.2.9 ETHERNET Port 1 Enable / Disable (JP4)

Enable / Disable JP4

On board ETHERNET ENABLE *1-2

On board ETHERNET DISABLE 2-3

2.2.10 ETHERNET Port 2Enable / Disable (JP7)

Enable / Disable JP7

On board ETHERNET ENABLE *1-2

On board ETHERNET DISABLE 2-3

Loading...

Loading...