Mitac 8599 Service Manual

SERVICE MANUAL FOR

SERVICE MANUAL FOR

SERVICE MANUAL FOR

8599

8599

85998599

8599

8599

85998599

8599

8599

85998599

BY:

Repair Technology Research Department /EDVD

Repair Technology Research Department /EDVD

Star

Star

Jun.2004

Meng

Meng

Contents

8599

8599

N/B Maintenance

N/B Maintenance

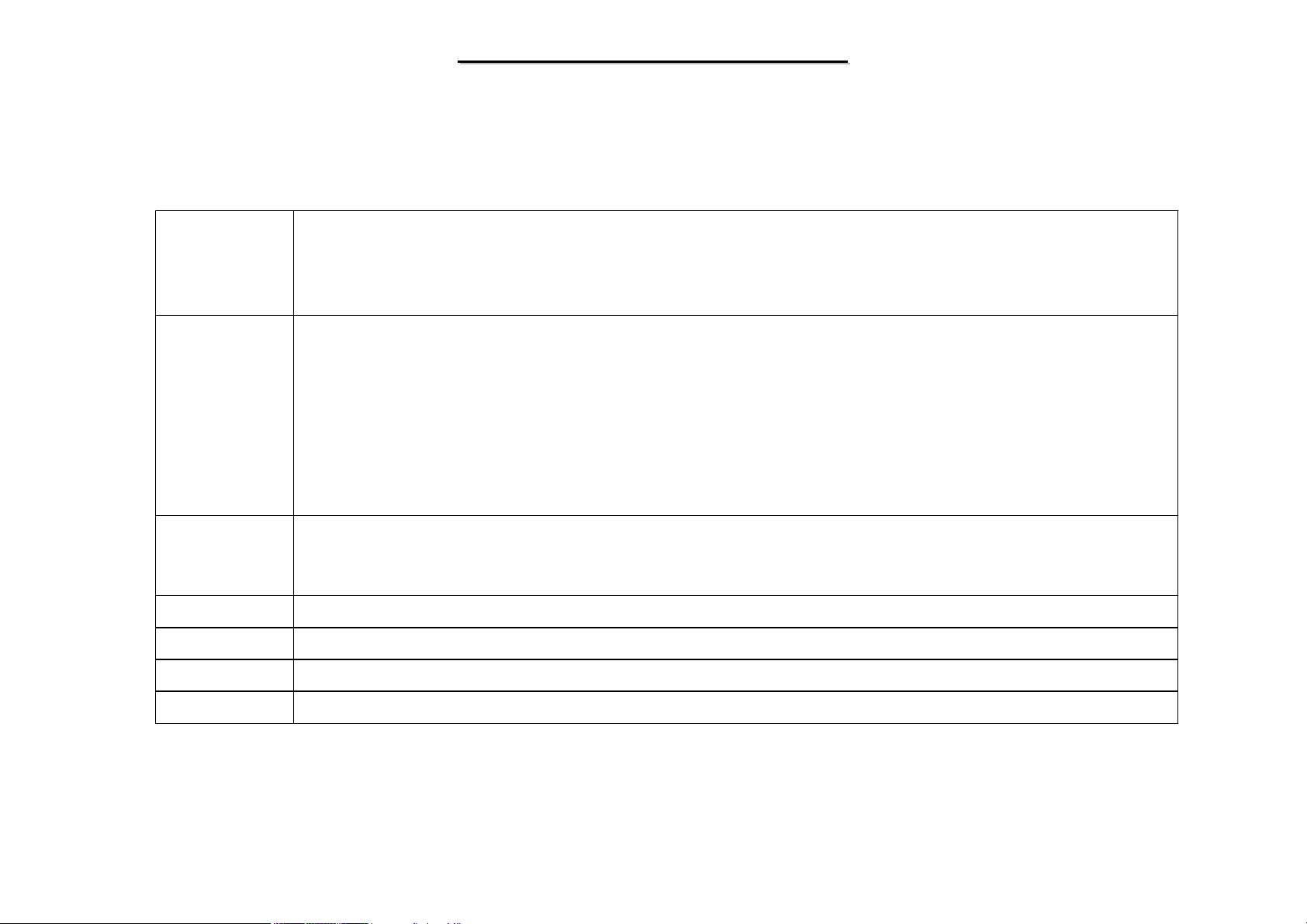

1. Hardware Engineering Specification ………………………………………………………………………

1.1 Introduction ………………………………………………………………………………………………………………..

1.2 Hardware System…………………………………………………………………………………………………………..

1.3 Electrical Characteristic ………………………………………………………………………………………………….

1.4 Appendix 1 : SiS963L GPIO Definition ………………………………………………………………………………….

1.5 Appendix 2 : Keyboard Controller Pins Definition ……………………………………………………………………..

1.6 Appendix 3: Audio Performance …………………………………………………………………………………………

2. System View and Disassembly ……………………………………………………………………………..

2.1 System View ……………………………………………………………………………………………………………….

2.2 System Disassembly ……………………………………………………………………………………………………….

3. Definition & Location of Connectors / Switches …………………………………………………………..

3.1 Mother Board ……………………………………………………………………………………………………………...

4. Definition & Location of Major Components ……………………………………………………………..

4

4

7

37

42

43

45

46

46

49

69

69

72

4.1 Mother Board ……………………………………………………………………………………………………………...

5. Pin Description of Major Component …….……………………………………………………………….

5.1 Inter Pentium 4 Processor mFC-PGA 478 Pins …………………………………………………………………………

5.2 SiS M661FX (IGUI Host Memory Controller) …………………………………………………………………………

5.3 SiS963L (MuTIOL®Media I/O South Bridge) ………………………………………………………………………….

72

73

73

78

83

1

Contents

8599

8599

N/B Maintenance

N/B Maintenance

6. System Block Diagram ……………………………………………………………………………………..

7. Maintenance Diagnostics …………………………………………………………………………………..

7.1 Introduction ……………………………………………………………………………………………………………….

7.2 Error Codes ……………………………………………………………………………………………………………….

7.3 Debug Tool …………………………………………………………………………………………………………………

8. Trouble Shooting ……………………………………………………………………………………………

8.1 No Power …………………………………………………………………………………………………………………..

8.2 Battery Can not Be Charged ……………………………………………………………………………………………..

8.3 No Display …………………………………………………………………………………………………………………

8.4 LCD No Display or Picture Abnormal …………………………………………………………………………………..

8.5 External Monitor No Display or Color Abnormal ………………………………………………………………………

8.6 TV Test Error ……………………………………………………………………………………………………………..

8.7 Memory Test Error ……………………………………………………………………………………………………….

8.8 Keyboard (K/B) Touch-Pad (T/P) Test Error …………………………………………………………………………..

8.9 Hard Driver Test Error …………………………………………………………………………………………………..

8.10 CD-ROM Driver Test Error …………………………………………………………………………………………….

8.11 USB Port Test Error …………………………………………………………………………………………………….

8.12 PC Card Socket Test Error ……………………………………………………………………………………………..

8.13 Mini-PCI Socket Test Error …………………………………………………………………………………………..

8.14 Audio Failure …………………………………………………………………………………………………………….

89

90

90

91

93

94

96

99

101

105

107

109

111

113

115

117

119

123

125

127

2

Contents

8599

8599

N/B Maintenance

N/B Maintenance

8.15 LAN Test Error ………….………………………………………………………………………………………………

9. Spare Parts List ……………………………………………………………………………… …………….

10. System Exploded Views …………………………………………………………………………………..

11. Circuit Diagram …………………………………………………………………………………………..

12. Reference Material ………………………………………………………………………………………..

130

132

143

144

172

3

8599

8599

N/B Maintenance

N/B Maintenance

1. Hardware Engineering Specification

1.1 Introduction

1.1.1 General Description

This document describes the system hardware engineer specification for 8599 portable notebook computer system.The

8599 notebook computer is a new mainstream high performance easy assembly notebook in the MiTAC notebook

family.

1.1.2 System Overview (1)

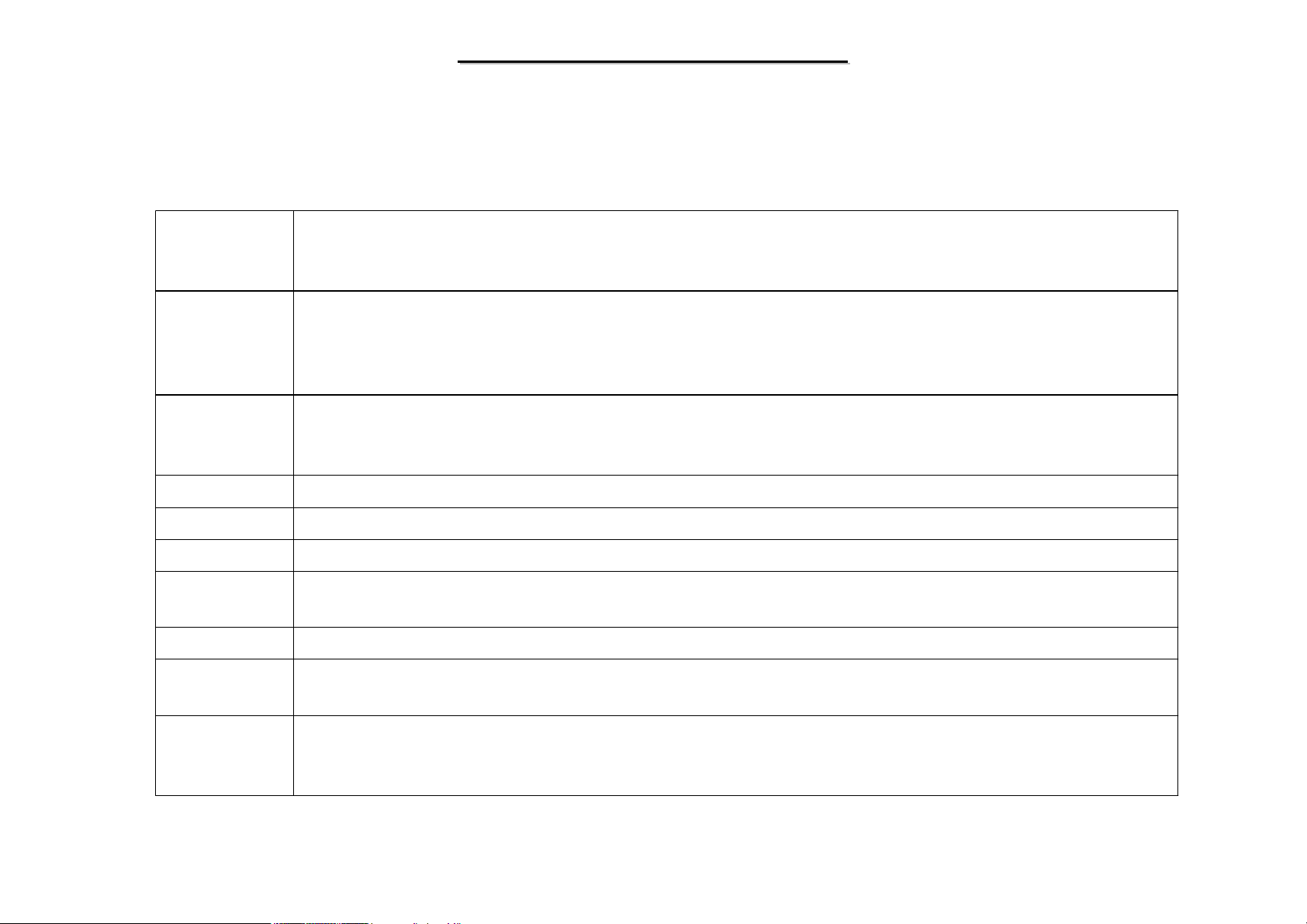

Table 1. Hardware Specification

CPU

Core logic

L2 Cache

System BIOS

- Intel DT NW P4 2.4G,2.5G,2.53G,2.6G,2.66G,2.8G,3.06Ghz(p) w/z HT - FSB 800/533 MHz

- Intel DT NW Celeron 2.0G~2.8G w/z - FSB 400MHz

- Intel DT Prescott Celeron 2.4G,2.53G,2.66G,2.8G,3.06G,3.2G w/z - FSB 533MHz

- Intel Northwood Mobile P4 2.40G,2.66G,2.80G,3.06G

- Thermal ceiling 81.8W

- SiS M661FX + SiS963L

- 512KB OD for N/W DT & Mobile P4,128KB for N/W Celeron,256KB for Prescott Celeron

-Insyde 256KB(P) Flash EPROM (Include System BIOS and VGA BIOS)

-ACPI 1.0b;DMI 2.3.1 compliant

-Plug & Play capability

4

8599

8599

1.1.2 System Overview (2)

Continue to the previous page

N/B Maintenance

N/B Maintenance

Memory

ROM Drive

HDD

Keyboard

PCMCIA

- 0MB on board;Expandable up to 1024MB

- Expandable with combination of optional 128MB/256MB/512MB memory

- 184-pin DDR 266/333/400 DROM Memory Module x 2

- 12.7mm Height

- CD/DVD ROM Drive

- Combo Drive

- Super Combo Drive

- 2.5” 8.45/9.5 mm height:10/15/20/40GB

- Support Ultra-DMA 66/100 function

- User removable by latch,design reserve for screw fix

- Support External FDD w/z USB 1/F; 3.5” Format for 720KB/1.2MB/1.44MBExt.FDD

- 15” XGA/TFT display; Resolution:1024x768Display

- SiS M661FX Int. w/64MB SMAVideo Controller

- 19mm key pitch/ 3.0mm key stroke/ 307mm length

- Windows Logo Key x 1; Application Key x 1

- Glide pad with 2x buttons and direction Scroll buttonPointing Device

- Type II x 1 without ZV

- Cardbus Support

Indictor

- 3 LEDs for Power/battery/charge status (on display Housing/cover)

- 1 LEDs for Radio wave status Power LED (BTO: Wireless LAN only)

- 5 LEDs for HDD Access,ODD Access, Num lock, Cap lock and Scroll Lock

5

8599

8599

1.1.2 System Overview (3)

Continue to the previous page

N/B Maintenance

N/B Maintenance

Audio System

I/O Port

Communication

Battery

- Sound Blaster Pro compatible

- Built-in mono microphone

- AC97 2.2 Codec

- 2X 2W Speakers

- USB port (2.0, backward compatible with USB 1.1) x 6

- RJ-11 port x 1

- RJ-45 port x 1

- DC input x 1

- VGA monitor port x 1

- Audio-out x 1

- Mic-in x 1

- S-Video TV-Out x 1 (NTSC/PAL)

- Built-in 56Kbps V.90 modem

- Built-in 10/100 based-T LAN

- One Mini-PCI slot and antenna reserved for wireless LAN

- 8 cell (2000mAH/3.7V) Li-ION smart battery

- Universal AC adapter 90W(P); Input: 100-240V,50/60hZ AC (support power on charge)AC adapter

- 332x285x42 (max) (P)Dimensions

- 3.5kg (P)Weight

6

8599

8599

N/B Maintenance

N/B Maintenance

1.2 Hardware System

1.2.1 CPU Module

The Intel®Northwood DT Pentium®4 processor, Intel’s most advanced, most powerful processor, is based on the

new Intel®NetBurst™micro-architecture. The Pentium 4 processor is designed to deliver performance across

applications and usages where end users can truly appreciate and experience the performance. These applications

include Internet audio and streaming video,image processing, video content creation, speech, 3D, CAD, games,

multi-media, and multi-tasking user environments. The Intel Northwood DT Pentium 4processor delivers this

world-class performance for consumer enthusiast and business professional DT users as well as for entry-level

workstation users.

Highlights of the Northwood DT Pentium 4 Processor:

Available at speeds ranging from2.26G/2.4G/2.5G/ 2.53G/2.66G/2.8G/3.06G Hz

Featuring the new Intel NetBurst™micro-architecture

Fully compatible with existing Intel Architecture-based software

Internet Streaming SIMD Extensions 2

Intel®MMX™media enhancement technology

Memory cache ability up to 4 GB of addressable memory space and system memory scalability up to 64GB of

physical memory

Support for uni-processor designs

Based upon Intel’s 0.13 micron manufacturing process

7

8599

8599

Intel Pentium 4 Processor Product Feature:

The Intel NetBurst™micro-architecture delivers a number of new and innovative features including Hyper

Pipelined Technology, 400 or 533 MHz System Bus, Execution Trace Cache, and Rapid Execution Engine as

well as a number of enhanced features Advanced Transfer Cache, Advanced Dynamic Execution, Enhanced

Floating-point and Multi-media Unit, and Streaming SIMD Extensions 2. Many of these new innovations and

advances were made possible with improvements in processor technology, process technology, and circuit

design that could not previously be implemented in high-volume, manufacturability solutions. The features and

resulting benefits of the new micro-architecture are defined below.

Hyper Pipelined Technology

The hyper-pipelined technology of the NetBurst™micro-architecture doubles the pipeline depth compared to

N/B Maintenance

N/B Maintenance

theP6 micro-architecture used on today’s Pentium III processors. One of the key pipelines, the branch

prediction / recovery pipeline, is implemented in 20 stages in the NetBurst™micro-architecture, compared to 10

stages in the P6 micro-architecture. This technology significantly increases the performance, frequency, and

scalability of the processor.

400/533 MHz System Bus:

The Northwood DT Pentium 4 processor supports Intel’s highest performance desktop system bus by delivering

3.2 or 4.3GBof data per second into and out of the processor. This is accomplished through a physical signaling

scheme of quad pumping the data transfers over a100/133-MHz clocked system bus and a buffering scheme

allowing for sustained 400/533-MHz data transfers. This compares to 1.06 GB/s delivered on the Pentium III

processor’s 133-MHz system bus.

8

8599

8599

Level 1 Execution Trace Cache:

In addition to the 8KB data cache, the Pentium 4 processor includes an Execution Trace Cache that stores up

to12K decoded micro-ops in the order of program execution. This increases performance by removing the

decoder from the main execution loop and makes more efficient usage of the cache storage space since

instructions that are branched around are not stored. The result is a means to deliver a high volume of

instructions to the processor’s execution units and a reduction in the overall time required to recover from

branches that have been mis-predicted.

Rapid Execution Engine:

Two Arithmetic Logic Units (ALUs) on the Pentium 4 processor are clocked at twice the core processor

frequency. This allows basic integer instructions such as Add, Subtract, Logical AND,Logical OR, etc. to

N/B Maintenance

N/B Maintenance

execute in half a clock cycle. For example, the Rapid Execution Engine on a 1.50 GHz Pentium 4 processor

runs at 3 GHz.

512KB, Level 2 Advanced Transfer Cache:

The Level 2 Advanced Transfer Cache (ATC) is 512KB in size and delivers a much higher data throughput

channel between the Level 2 cache and the processor core. The Advanced Transfer Cache consists of a 256bit(32-byte) interface that transfers data on each core clock. As a result,the Northwood DT Pentium 4 processor

1.6 GHz can deliver a data transfer rate of 48 GB/s.This compares to a transfer rate of 16 GB/s on the Pentium

III processor at 1 GHz. Features of the ATC include:

Non-Blocking, full speed, on-die Level 2 cache

8-way set associativity

9

8599

8599

256-bit data bus to the level 2 cache

Data clocked into and out of the cache every clock cycle

Advanced Dynamic Execution:

The Advanced Dynamic Execution engine is a very deep, out-of-order speculative execution engine that keeps

the execution units executing instructions. The Pentium 4 processor can also view 126 instructions in flight and

handle up to 48 loads and 24 stores in the pipeline. It also includes an enhanced branch prediction algorithm

that has the net effect of reducing the number of branch mis-predictions by about 33% over the P6 generation

processor’s branch prediction capability. It does this by implementing a 4KB branch target buffer that stores

more detail on the history of past branches, as well as by implementing a more advanced branch prediction

algorithm.

N/B Maintenance

N/B Maintenance

Enhanced Floating-Point and Multimedia Unit:

The Pentium 4 processor expands the floating-point registers to a full 128-bit and adds an additional register

for data movement which improves performance on both floating-point and multimedia applications..

Internet Streaming SIMD Extensions 2 (SSE2):

With the introduction of SSE2, the NetBurst™micro-architecture now extends the SIMD capabilities that MMX

technology and SSE technology delivered by adding 144 new instructions. These instructions include 128-bit

SIMD integer arithmetic and 128-bit SIMD double-precision floating-point operations. These new instructions

reduce the overall number of instructions required to execute a particular program task and as a result can

contribute to an overall performance increase. They accelerate a broad range of applications, including video,

speech,and image, photo processing, encryption, financial,engineering and scientific applications.

10

8599

8599

Features Used for Test and Performance / Thermal Monitoring:

Built-in Self Test (BIST) provides single stuck-at fault coverage of the microcode and large logic arrays, as

well as testing of the instruction cache, data cache, Translation Look aside Buffers (TLBs), and ROMs.

IEEE 1149.1 Standard Test Access Port and Boundary Scan mechanism enables testing of the Pentium 4

processor and system connections through a standard interface.

Internal performance counters can be used for performance monitoring and event counting.

Includes a new Thermal Monitor feature that allows motherboards to be cost effectively designed to

expected application power usages rather than theoretical maximums.

N/B Maintenance

N/B Maintenance

1.2.2 SiS M661FX Graphics/Memory Controller

The SiSM661FX chipset features a SiS Real256E GPU, an AGP-8X port, and a Shared Memory Architecture

DDR400 unified memory controller, supporting Intel Hyper Threading Technology Pentium 4 microprocessors series

with FSB 800MHZ. The integrated Real256E GPU features a high performance 3D / 2D Graphics engine, a video

accelerator, a MPEG1/II motion compensation decoder, and a video link(Muxed with AGP port) to support the TV-out

& digital flat panel. The SiSM661FX, adopting the SMA, eliminates the need and thus the cost of the frame buffer

memory by organizing the frame buffer,32MB or 64MB, in the system memory. The SiSM661FX, via the secondgeneration 1GB/s Multi-threaded I/O link, interconnects the SiS963 Media I/O that integrates one EHCI compliant

USB2.0 host controller, 2 OHCI compliant USB 1.1 host controllers, dual ATA-133 IDE controllers, AC-97 V2.2

compliant audio controller, and the 10/100M bit Ethernet MAC controller with standard MII interface. Figure 1

illustrates a Pentium 4 PC system diagrams based on SiSM661FX and SiS963 chipsets.

11

8599

8599

The SiSM661FX Host Interface features the AGTL & AGTL+ compliant bus driver technology with integrated on-die

termination to support Intel Pentium 4 series processors with FSB 800MHz. The AGP interface supports the external

AGP slot with AGP 4X/8X capability and Fast Write Transactions. The SiSM661FX incorporates the second

generation 1GB/s MuTIOL1G interface, comprising the transaction layer, link layer, and physical layer, to bridge the

SiS963 Media I/O. As seen in table 1, the SiSM661FX comprises two PCI devices sitting on the bus 0, and one PCI

device on the Bus 1.The device 0 stands for the SiSM661FX entity with device ID 0661h, and IDSEL equal to AD11.

The device 1 functions a virtual PCI to PCI bridge to connect the AGP device, with device ID equal to 0002h, and

IDSEL equal to AD12. The device 0 in the bus 1 represents the integrated Real256E GPU, with device ID equal to

6330h. The integrated GUI device 6330h cannot work concurrently with an external AGP graphics device. When an

external AGP device is installed in the system, the built-in GUI will be disabled. Figure 2 illustrates a graphic

subsystem based on the integrated GUI in SiSM661FX.

The integrated Real256E GPU features a high performance 3D accelerator with 2 Pixel / 4 Texture, and a 128 bit 2D

N/B Maintenance

N/B Maintenance

accelerator with 1T pipeline BITBLT engine. Two 12 bit DDR digital video links interfaced to SiS 301/2 Video

Bridge is incorporated to expand the SiSM661FX functionality to support the secondary display, in addition to the

default primary CRT display. The SiS301 Video Bridge features an NTSC/PAL video encoder with Macro Vision Ver.

7.1.L1 option for TV display, a TMDS transmitter with Bi-linear scaling capability to support up to UXGA TFT LCD

panel, and an analog RGB port to support the secondary CRT. The primary CRT display and the extended secondary

display, namely TV, TFT LCD, or 2'nd CRT, features the Dual Display Capability in the sense that both can generate

the display in independent resolutions, color depths, and frame rates. Table 2 details the capability of the video overlay

capability in SiSM661FX+SiS301/302 subsystem. In a summary, in the mirror mode, two separate H/W video overlay

engines, and two separate subpicture engines work simultaneously to deliver high quality video overlay with

subpicture in the respective display consoles simultaneously, say in the LCD, and CRT for the presentation application.

However, in the dual display mode, only one H/W video overlay, and one subpicture engine can be enabled to overlay

the video display and the subpicture in one display while the support of the second video overlay with subpicture in.

12

8599

8599

the second display can only be realized through software engine.

Two separate buses, the 64 bit Host-to-GUI bus, and the 128 bit IGUI-to-Memory Controller bus are devised to ensure

concurrency of Host-to-GUI, and GUI-to-MC streaming. In the DDR-400 memory subsystem, the 128 bit IGUI-toMC bus attains 3.2 GB/s, around 52% wider bandwidth than the AGP 8X one. The DDR-400 unified memory

controller mainly comprises the Memory Arbiter, the M-data/M-Command Queues, and the Memory Interface. The

Memory Arbiter arbitrates a plenty of memory access requests from the GUI or AGP controller, Host Controller, and

the I/O bus masters based a default optimized priority list with the capability of dynamically prioritizing the I/O bus

master requests to offer a privileged service to 1) the isochronous downstream transfer to guarantee the min. latency,

& timely deliver, or 2) the PCI master downstream transfer to curb the latency within the max. tolerant period of 10us.

Prior to the memory access requests pushed into the M-data queue, any command complaint to the paging mechanism

is generated and pushed into the M-CMD queue. The M-data/M-CMD queue further orders and forwards these

queuing requests to the Memory Interface in an effort to utilizing the memory bandwidth to its utmost by scheduling

N/B Maintenance

N/B Maintenance

the command requests in the background when the data request streamlines in the foreground.

Features :

PC2001 Comp liance

High Performance Host Interface

- Supports Intel Pentium 4 processor family with data transfer rate

- Supports Hyper-Threading Technology

- Supports 12 outstanding transactions and out-of-order completion

- Supports Quasi-synchronous/asynchronous Host-to-DRAM timing

- Supports Master delivery System bus Interrupt

13

8599

8599

- Supports zero-wait state for contiguous CPU write data

- Supports 128K/256K/512K/1M/2M/4M/8M/16M TSEG SMRAM

- Supports Defer Function to maximize bus utilization

- Supports Dynamic Bus Inversion

- AGTL+ & AGTL compliant bus driver with auto compensation

64 Bit High Performance DDR400/DDR333/DDR266 Memory Controller

- Supports DDR400/DDR333/DDR266 SDRAM

- Supports up to 2 un-buffered DIMM DDR400

- Supports up to 3 un-buffered DIMM DDR333

- Up to 1 GB per DIMM with maximum memory size up to 3 GB

N/B Maintenance

N/B Maintenance

- Supports 32Mb, 64Mb, 128Mb, 256Mb, 512Mb, 1Gb SDRAM technology with page size from 2KB up to 32 KB

- Supports up to 24 open pages

- Sustains DDR SDRAM CAS Latency at options of 2, 2.5, & 3 clocks

- Auto-compensation SSTL-2.5v driver optimizing for performance and stability

- Supports Suspend to DRAM function

- Programmable shared frame buffer size 32MB or 64MB for display memory

- 128KB SMRAM space re-mapping to A0000h, B0000h, or E0000h

Integrated A.G.P. Compliant Target/66MHz Host-to-PCI Bridge

- Universal AGP v3.0 Compliant

- Support 1.5V AGP Interface Only

14

8599

8599

- Supports Graphic Window Size from 4MBytes to 512MBytes

- Supports Pipelined Process in CPU-to-A.G.P. Access

- Supports 8 Way, 16 Entries Page Table Cache for GART to Enhance A.G.P. Controller Read/Write Performance

- Supports PCI-to-PCI Bridge Function for Memory Write from 33Mhz PCI Bus to A.G.P. device

- Supports AGP 8X/4X Interface w/ Fast Write Transaction

- Supports Hardware Enforced Coherence Outside GART Range for A.G.P. Transaction

- Supports Data Bus Inversion and Calibration Cycle

High Throughput SiS MuTIOL® 1G Interconnecting to SiS963 MuTIOL 1G Media I/O

- Bi-directional 16 bit data bus

- Perform 1GB/s bandwidth in 133MHz x 4 mode

N/B Maintenance

N/B Maintenance

- Distributed arbitration strategy with long contiguous data streaming

- Packet based, pipelining, and split transaction scheme

Dedicated Isochronous Response Queue

- Priority promotion for upstream Isochronous DMA memory read requests originated from real-time I/O device

controllers, such as USB or audio/modem

- Dedicated Isochronous response queue serving Isochronous downstream transfers responsive to the memory read

requests originated from real-time I/O device controllers, such as USB or audio/modem. Offers privilege service

to guarantee minimum latency & timely delivery

High Performance & High Quality 3D Graphics Accelerator

- Built-in a high performance 256-bit 3D engine

15

8599

8599

-- Built-in 32-bit floating point format VLIW triangle setup engine

-- Built-in 2 pixel rendering pipelines and 4 texture units

-- Built-in hardware stereo auto rendering engine

-- Supports Ultra-AGPIITM up to 2.7GB/s bandwidth

-- Up to 133 MHz 3D engine clock speed

-- Peak polygon rate: 11.6 M polygon/sec @ 1 pixel/polygon with Gouraud shaded, point-sampled, linear and

bilinear texture mapping

-- Peak fill rate: 333 M pixel/sec, 666 M texture/sec @ 10,000 pixel/polygon with Gouraud shaded and two

bilinear textured, Z buffered and alpha blended

- Built-in a high quality 3D engine

-- Supports flat, and Gouraud shading

-- Supports high quality dithering

N/B Maintenance

N/B Maintenance

-- Supports Z-test, stencil test, Alpha-test, and scissors clipping test

-- Supports 16 ROPs

-- Supports Z-buffer, stencil buffer

-- Supports 16/24/32 bits integer Z buffer format and 32 bits floating point Z format

-- Supports 16/32 BPP render buffer format

-- Supports 1/2/4/8 stencil buffer format

-- Supports per-pixel texture perspective correction

-- Supports point-sampled, linear, bi-linear, and dual bi-linear texture filtering

-- Supports up to 2 pixels with 4 bi-linear texels within single cycles

-- Supports up to 2048x2048 texture size

-- Supports rectangle structure texture

16

8599

8599

-- Supports 16/24/32 bpp RGB/ARGB texture format

-- Supports DTX1, DTX2, DTX3 texture compression formats

-- Supports texture transparency, blending, wrapping, mirror, and clamping

-- Supports fogging, alpha blending

-- Supports vertex fogging and fog table

-- Supports specular lighting

-- Supports 2X/4X multi-sampling full scene anti-aliasing

-- Supports back face culling

-- Supports auto-stereo rendering

High Performance 2D Graphics Accelerator

- Built-in hardware command queue

N/B Maintenance

N/B Maintenance

- Built-in Direct Draw Accelerator

- Built-in GDI 2000 Accelerator

- Built-in an 1T pipelined 128-bit BITBLT graphics engine with the following functions:

-- 256 raster operations

-- Rectangle fill

-- Trapezoid fill

-- Color expansion

-- Enhanced color expansion

-- Line-drawing with styled pattern

-- NT fractional point line-drawing with styled pattern

-- Multiple scan line

17

8599

8599

-- Built-in 256 bytes pattern registers

-- Built-in 8x8 mask registers

-- Rectangle clipping

-- Transparent BitBlt with source and destination keys (16 ROPs)

-- Gradient color fill

-- Anti-aliasing text drawing

-- Alpha blended Bitblt

-- YUV to RGB color transform Bitblt

-- Source data in command queue Bitbl

-- YUV420 to YUV422 format conversion Bitblt

- Supports memory-mapped, zero wait-state, burst engine write

- Built-in 64x64x2 bit-mapped mono hardware cursor

N/B Maintenance

N/B Maintenance

- Built-in 64x64x16 bit-mapped blended color hardware cursor

- Maximum 128MB frame buffer with linear addressing

- Built-in engine write-buffer with byte-merge

- Supports Ultra-AGPIITM 2.7GB/s for DDR333 and 3.2GB/s for DDR400 data read for all 2D Graphics engine

functions

- Built-in source read-buffer to minimize engine wait-state

- Built-in destination read-buffer to minimize engine wait-state

Complete TV-OUT/Digital Flat Panel Solution

- Built-in secondary CRT controller to support independent display of secondary CRT, LCD and TV-out

18

8599

8599

- AGP signals multiplexed with two 165MHz dot clock 12-bit DDR digital video link connecting to SiS video

bridge (SiS301, and SiS302) supporting

-- NTSC/PAL video output with max. resolution 1024x768x32@60NI

-- Digital LCD monitor with max. resolution 1600x1200x32@60NI

-- The secondary CRT with max. resolution 1600x1200x32@60NI

-- The Independent dual view support of the CRT+LCD, CRT+TV, LCD+TV combinations.

MPG-2/1 Video Decoder

- MPEG-2 ISO/IEC 13818-2 MP@HL and MPEG-1 ISO/IEC 11172-2 standards compliant

- Built-in advanced hardware DVD acceleration logic

- Support AGP bus master/LFB-mode code fetching

- Half pixel resolution in motion compensation

N/B Maintenance

N/B Maintenance

- Supports up to 20 Mbit/sec bit rate decoding

- Support VCD, DVD and HDTV (all ATSC modes) decoding

- Direct DVD to TV playback

Video Accelerator

- Supports video windows with overlay function

- Supports YUV-to-RGB color space conversion

- Supports bi-linear video interpolation with integer increments of 1/2048

- Supports graphics and video overlay function

-- Independent graphics and video formats

19

8599

8599

-- 16 color-key and/or chroma-key operations

-- Support YUV or RGB format chroma key

-- Rectangular video window mode

-- Video only mode

-- VCD, DVD and up to HDTV playback mode

-- Supports reading-back of current refresh scan line

- Supports tearing free double buffer flipping

- Supports RGB555, RGB565, YUV422, and YUV420 video playback format

- Supports filtered horizontal up and down scaling playback

- Supports de-interlaced function to improve field-display sources display quality

- Supports DVD sub-picture playback overlay

N/B Maintenance

N/B Maintenance

- Supports DVD playback auto-flipping

- Built-in video playback line buffers to support 1920x1080 video playback

- Supports DVD sub-picture playback overlay

- Built-in video line buffers and sub-picture buffers for DVD quality video

- Built-in independent Gamma correction RAM

- Supports DCI Drivers

- Supports Direct Draw Drivers

High Integration

- Built-in CRT FIFOs to support ultra high resolution graphics modes and reduce CPU wait-state

- Built-in programmable 24-bit true-color RAMDAC up to 333 MHz pixel clock

20

8599

8599

-- Built-in reference voltage generator and monitor sense circuit

-- Supports downloadable 24 bits RAMDAC for gamma correction in high color and true color modes

-- Support programmable 4 levels DAC current ratio (700, 750, 800, 850 mv)

-- Support programmable pedestal level (0, 0.75mv)

-- Support programmable 4 levels slew rate control

- Built-in two clock generators for CRT, 2D, 3D and MPEG Engine

- Built-in TV Encoder Interface

Power Management

- Supports VESA Display Power Management Signaling (DPMS) compliant VGA monitor for power management

- Supports direct I/O command to force graphics controller into standby/suspend/off state

N/B Maintenance

N/B Maintenance

- Power down internal Gamma/Palette SRAM in direct color mode

- Supports PCI power management configuration registers for supporting ACPI power down controller

- Power down all internal macro cells such as SRAM, DAC, clock generator when power saving mode

- Supports clock stopping for video accelerator, 2D, 3D and MPEG decoder when disabled

- Supports auto clock throttling for 2D engine, 3D engine

21

8599

8599

N/B Maintenance

N/B Maintenance

1.2.3 SiS963L MuTIOL 1G Media I/O

The SiS963L MuTIOL 1G Media I/O integr ates one Universal Serial Bus 2.0 Ho st Controllers, the Audio Controller

with AC 97 Interface, the Ethernet MAC Controller w/ standard MII interface, two Universal Serial Bus 1.1 Host

Controllers, the IDE Master/Slave controllers, and SiS MuTIOL 1G technology. T he PCI to LPC bridge, I/O

Advanced Programmable Interrupt Controller, legacy system I/O and legacy power management functionalities are

integrated as well.

The high-speed host controller implements an EHCI compliant interface that provides 480Mb/s bandwidth for six

USB 2.0 ports. The two USB1.1 host controllers implement an OHCI compliant interface and each USB1.1 host

controller provide s 12Mb/s bandwidth for three USB 1.1 ports. The totally six USB ports can be automatically routed

to support a High-speed USB 2.0 de vice or Full- or Low-speed USB 1.1 device. Besides, each port can be optionally

configured as the wake-up source. Legacy USB devices as well as over current detection are als o implemented. The

Integrated AC97 v2.2 compliance Audio Controller that features a 6-channels of audio speaker out and HSP v.90

modem support. Additionally, the AC97 interface supports 4 separate SDATAIN pins that is capable of supporting

multiple audio co decs with one separate modem codec.

The integrated Fast Ethernet MAC Controller features an IEEE 802.3 and IE EE 802.3x complian t MAC with external

LAN physical layer chip supporting full duplex 10 Base-T, 100 Base-T Ethernet, or with external Home networkin g

physical laye r chip supporting 1Mb/s & 10Mb/s Home networking. Additionally, 5 wake-up Frames, Magic Packet

and link status changed wake-u p function in G1/G2 states are supported. For storing Mac address, two schemes are

provided: 1. Store in internal APC register or 2. Store in external EEPROM.

The integrated IDE Master/Slave controllers features Dual Independent IDE channe ls supporting PIO mode 0,1,2,3,4,

and Ultra DMA 33/66/100/133. It provides two separate data paths for the dual IDE channels that sustain the high data

transfer rate in the multitasking environment.

22

8599

8599

SiS963L supports 6 PCI masters and complies with PCI 2.2 specification. It also incorporates the legacy system I/O

like: two 8237A compatible DMA controllers, three 8254 compatible programmable 16-bit counters, hardwired

keyboard controller and PS2 mouse interface, Real Time clock with 512B CMOS SRAM and two 8259A compatible

Interrupt controllers. Besides, the I/O APIC managing up to 24 interrupts with both Serial and FSB interrupt delivery

modes is supported.

The integrated power management module incorporates the ACPI 1.0b compliance functions, the APM 1.2

compliance functions, and the PCI bus power management interface spec. v1.1. Numerous power-up events and power

down events are also supported. 25 general purposed I/O pins are provided to give an easy to use logic for specific

application. In addition, the SiS963L supports Deeper Sleep power state for Intel Mobile processor. For AMD

processor, the SiS963L use the CPUSTP# signal to reduce processor voltage during C3 and S1 state.

A high bandwidth and mature SiS MuTIOL 1G technology is incorporated to connect SiS MuTIOL 1G North Bridge

N/B Maintenance

N/B Maintenance

and SiS963L MuTIOL1G Media I/O together. SiS MuTIOL 1G technology is developed into three layers, the Multithreaded I/O Channels Layer delivering 1.2GB bandwidth to connect embedded DMA Master devices and external

PCI masters to interface to Multi-threaded I/O Channels layer, the Multi-threaded I/O Packet Layer in SiS963L to

transfer data w/ 1GB/s bandwidth from/to Multi-threaded I/O Channels layer to/from SiS MuTIOL 1G North Bridge,

and the Multi-threaded I/O Packet Layer in SiS MuTIOL 1G North Bridge to transfer data w/ 1GB/s from/to memory

sub-system to/from the Multi-threaded I/O Packet Layer in SiS963L.

23

8599

8599

Features :

Meet PC2001 Requirements

Support AMD Hammer CPU and HyperTransport Technology.

Support Watchdog Timer Hardware Requirements for Microsoft Windows .NET Server

High performance SiS MuTIOL 1G Technology Interconn ecting SiS North bridge and South bridge chips

- Bi-directional 16-bit data bus

- Perform 1GB/s bandwidth in 133MHz x 4 mode

- Distributed arbitration strategy with long contiguous data streaming

- Packet based, pipelining, and split transaction scheme

N/B Maintenance

N/B Maintenance

Integrated Multi-threaded I/O link ensures concurrency of upstream /down stream data transfer

with1.2GB/s bandwidth

Multiple DMA Bus Architecture

- Concurrent Servicing of all DMA Devices: Dual IDE Controllers, two USB 1.1 HC, One USB 2.0 HC, MAC

Controller, Audio/Modem DMA Controller

- Separate 32 Bit Input and Output Data Bus Scheme for each DMA Device

- Advanced Performance Merits of Split & Pipelined Transaction and Concurrent

- Execution among Multi-I/O Devices

- Support isochronous request and continuous packet transmission

24

8599

8599

Integrated MuTIOL 1G to PCI Bridge

- PCI 2.2 Specification Compliance

- Supports up to 6 PCI Masters

- Two Prefetch cache Buffers support 2 delayed transactions

- Each PCI request can be programmed at one of four level priority

- Write Promotion Mechanism to Guarantee the 10 µs Time Limit of PCI Memory Write

Dual IDE Master/Slave Controller

- Integrated Multithreaded I/O Link Mastering with Read Pipelined Streaming

- Dual Independent IDE Channels Each with 32 DW FIFO

- Native and Compatibility Mode

N/B Maintenance

N/B Maintenance

- PIO Mode 0, 1, 2, 3, 4 and Multiword DMA Mode 0, 1, 2

- Ultra DMA 33/66/100/133

- ATA/ATAPI 48-bit addressing compliance and support greater than 137Gbytes device.

- Silicon Integrated Series Termination Resistors

- Silicon Integrated IDE Bus pull up / down resistors

- PCI 2.2 Specification Compliance

- Bus master programming interface (SFF-8038i) specification compliance

Universal Serial Bus Host Controller

- Integrated Multithreaded IO Link Mastering

- Two Independent OHCI USB 1.1 Host Controllers and One EHCI USB 2.0 Host Controller, support up to six ports

25

8599

8599

- Supports wake-up from S1-S3

- Legacy Keyboard/Mouse support

- Supports only one Debug port at port 0(first port), it is at USB 2.0 transfer rate.

Integrated Fast Ethernet MAC Controller

- Multithread I/O link Mastering with Read/Write Concurrent transaction

- IEEE 802.3 and 802.3x Standard Compatible

- Supports Enhanced Software and Automatic Polling schemes to access PHY registers

- Supports full duplex 10base-T, 100base-Tx, 1 Mb/s & 10 Mb/s Home Networking

- Support ACPI v1.0b and PCI Power Management v1.1 Standard

- Support 5 Wake-up Frame, Magic Packet, and Link Status changed wake-up function at G1/G2 state

N/B Maintenance

N/B Maintenance

- Integrated 128-bit multicast hash table

- Support 2K bytes transmit and receive Data FIFO

- MAC address store scheme from external 4-pin EEPROM or Internal APC register

Integrated Audio Controller with AC97 Interface.

- AC97 v2.2 compliance

- 6 Channels of AC97 speaker outputs and V.90 HSP-Modem

- 4 Separate SDATAIN pins supporting multiple Audio Codecs and one Modem Codec

- Supports Audio and Modem function with Multithreaded I/O link mastering

- Supports two Consumer Audio Digital interface: traditional Consumer Digital Audio Out and AC97 V2.2

Compliance Consumer Audio Digital Interface

26

8599

8599

- Supports VRA Mode for both AC97 Audio Link and Consumer Audio Digital Interface

Advanced Power Management

- Meets ACPI 1.0b Requirements

- Meets APM 1.2 Requirements

- ACPI Sleep States Include S1, S3, S4, S5

- CPU Power States Include C0, C1, C2 C3, C4

- Supports Intel Deeper Sleep Power State for Intel mobile processor.

- Reduce AMD processor voltage during S1/C3 state

- Power Button with Override only wake up by Power Button

- RTC Day-of-Month, Month-of-Year Alarm

N/B Maintenance

N/B Maintenance

- 24-bit Power Management Timer

- LED Blinking in S0, S1 and S3 States

- ACPI System Wake-up Events

- ACPI S1 Wake-up Events: Power Button, PS/2 keyboard Hot-Key/Any-key and Mouse, RTC Alarm, Modem,

Ring-In, LAN, PME#, AC’97 Wake-Up, USB Wake-Up, and 1394 Wake-up

- ACPI S3 Wake-up Events: Power Button, PS/2 keyboard Hot-Key/Any-key and Mouse, RTC Alarm, Modem,

Ring-In, GPIO7, LAN, PME#, AC’97 Wake-Up, USB Wake-Up, and 1394 Wake-up.

- ACPI S4/S5 Wake-up Events: Power Button, PS/2 keyboard Hot-Key/Any-Key and Mouse, RTC Alarm, Modem,

Ring-In, GPIO7, LAN, PME#, AC’97 Wake-Up, and P1394 Wake-up.

- Software Watchdog Timer

- PCI Bus Power Management Interface Spec. 1.1

27

8599

8599

- Support PCI CLKRUN and STP_PCI function (for Mobile only)

- Support RTC32KHz output from GPIO18 (for Mobile only)

- Integrated 32-bit Random Number Generator

- Support one GTL-level input signal used to instantly power off the system

- Support one GTL-level input signal used to assert SMI#/SCI#

Integrated DMA Controller

- Two 8237A Compatible DMA Controllers

- 8/16- bit DMA Data Transfer

Integrated Interrupt Controller

N/B Maintenance

N/B Maintenance

- Two 8259A Compatible Interrupt Controllers for up to 15 interrupts

- Programmable Level or Edge Triggered Interrupts

- Support Serial Interrupt

- Support 8 PCI interrupts for internal device

- Support Message Interrupt Delivery Mode

- Integrated I/O APIC in Serial Mode or FSB Interrupt Delivery Model for up to 24 Interrupts

Three 8254 Compatible Programmable 16-bit Counters

- System Timer Interrupt

- Generate Refresh Request

- Speaker Tone Output

28

8599

8599

Integrated Keyboard Controller

- Hardwired Logic Provides Instant Response

- Supports PS/2 Mouse Interface

- System Sleep and Power-Up by Hot-Key

- KBC and PS2 Mouse Can Be Individually Disabled

Integrated High-Performance Event Timer

- Support three timers operating at 32- or 64-bit mode

Integrated PCI to LPC Bridge

- LPC 1.0 Compliance

N/B Maintenance

N/B Maintenance

- Support Two Master/DMA devices

Integrated Real Time Clock (RTC) with 512B CMOS SRAM

- Supports ACPI Day-of-Month and Month-of-Year Alarm

Universal Serial Bus Host Controller

NAND Tree for Ball Connectivity Testing

371-Balls BGA Package

1.8V Core with Mixed 1.5V, 1.8V, 2.65V and 3.3V I/O CMOS Technology

29

Loading...

Loading...