R

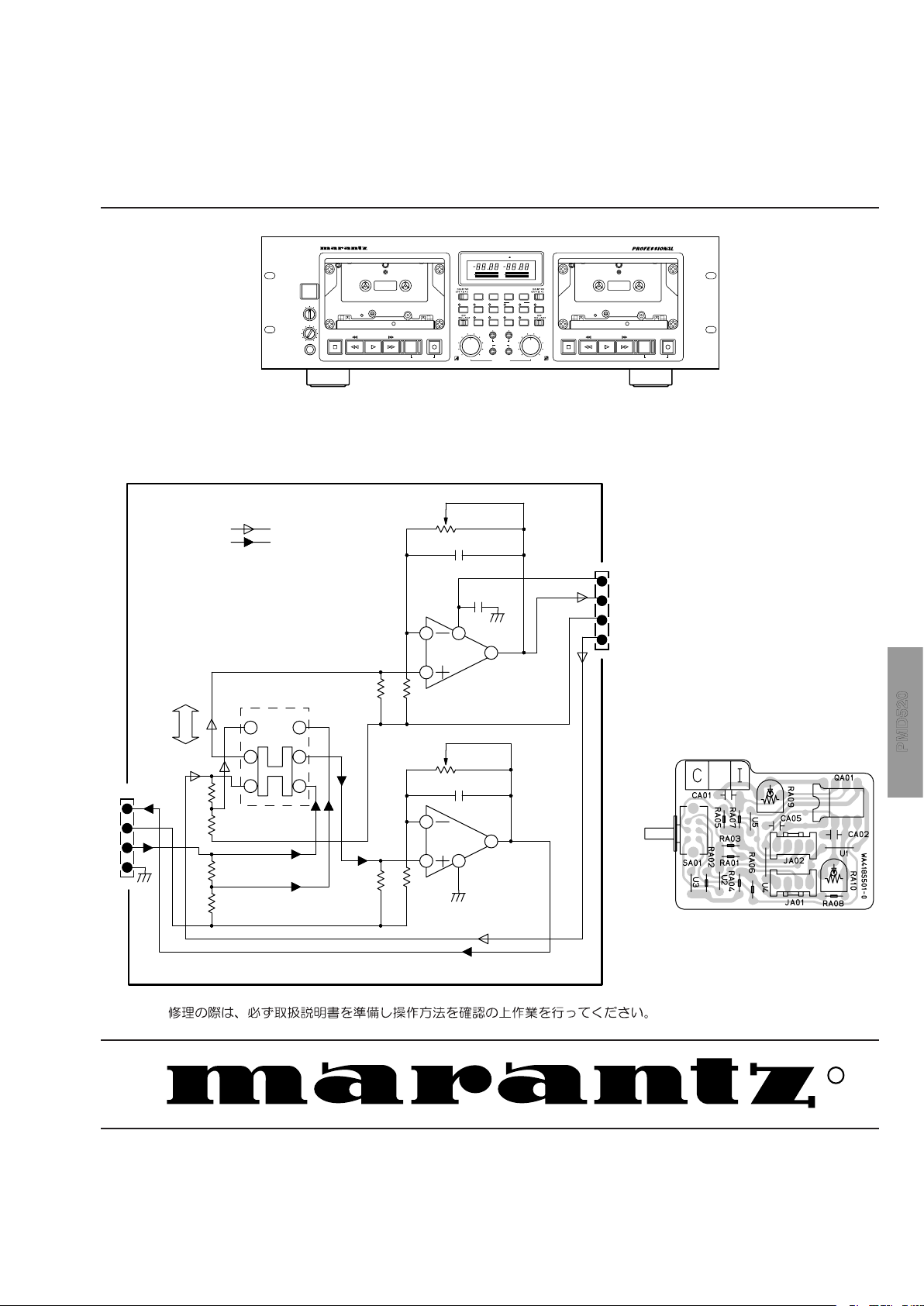

PMD520

Service

OVERLAP

REC

A B

A+B

HP SELECT

HP LEVEL

PHONES

POWER

AUTO

REW

5

4

3

2

1

0 10

9

8

7

6

FINE SPEED

BALANCE

5

4

3

2

1

0 10

9

8

7

6

REC LEVEL

DC SERVO CONTROLLED MOTOR / AUTO TAPE SELECTOR

3HEAD

L

0 3 +6dB36101520

R

STOP PLAY REC MUTE REC

AUTO BIA S

TAPE TIME RESET RESET TAPE TIME

CONT

MONITOR

TIMER

TIMER

A+B

BIAS

RESET

BIAS

RESET

HIGH NORM

MONITOR

TAPE SPEED

L

0 3 +6dB36101520

R

DC SERVO CONTROLLED MOTOR / AUTO TAPE SELECTOR

3HEAD

STOP PLAY REC MUTE REC

AUTO BIA S

FULLY INDEPENDENT DOUBLE CASETTE DECK PMD520

REC/PLAY REC/PLAY

DOLBY BÐC NR HX PRO

QA01

NJM2068DD

(1/2)

1

2

3

8

CA01

100p

CA05

0.1u

A-GND

RA07

2.2k

RA09

3.3k

1 3

2

CA02

100p

QA01

NJM2068

(2/2)

7

6

5

4

RA06

220K

A-GND

RA10

3.3k

1 3

2

RA08

2.2k

RA01

27K

RA03

2.7k

RA04

2.7k

RA02

27K

JA02

4

3

2

1

A-GND

RA05

220k

SA01

3

2

1

6

5

4

JA01

4

3

2

1

0dB

-20dB

Rch

Rch

Lch

Lch

(5)

(6)

(7)

(8)

Lch

Rch

Rch

PA01

WA418S5010

(1)

(4)

(3)

(2)

PA01

QA01

PMD520/F1B

Manual

PMD520FB は

このサービスマニュアルには

その他の部分は

参照して下さい。

74PMD520/02B PMD520U

74PMD520/02B PMD520U

74PMD520/02B PMD520U

Fully Independent Double Cassette Deck

の電源部分の変更 及び 入力 ATT 回路 (PA01) を追加した製品です。

との相違部分のみを記載しております。

のサービスマニュアル (

418S855010

または

4822 725 51174

) を

Printed in Japan

PMD520

418S855020 MIT

First Issue 2001.09

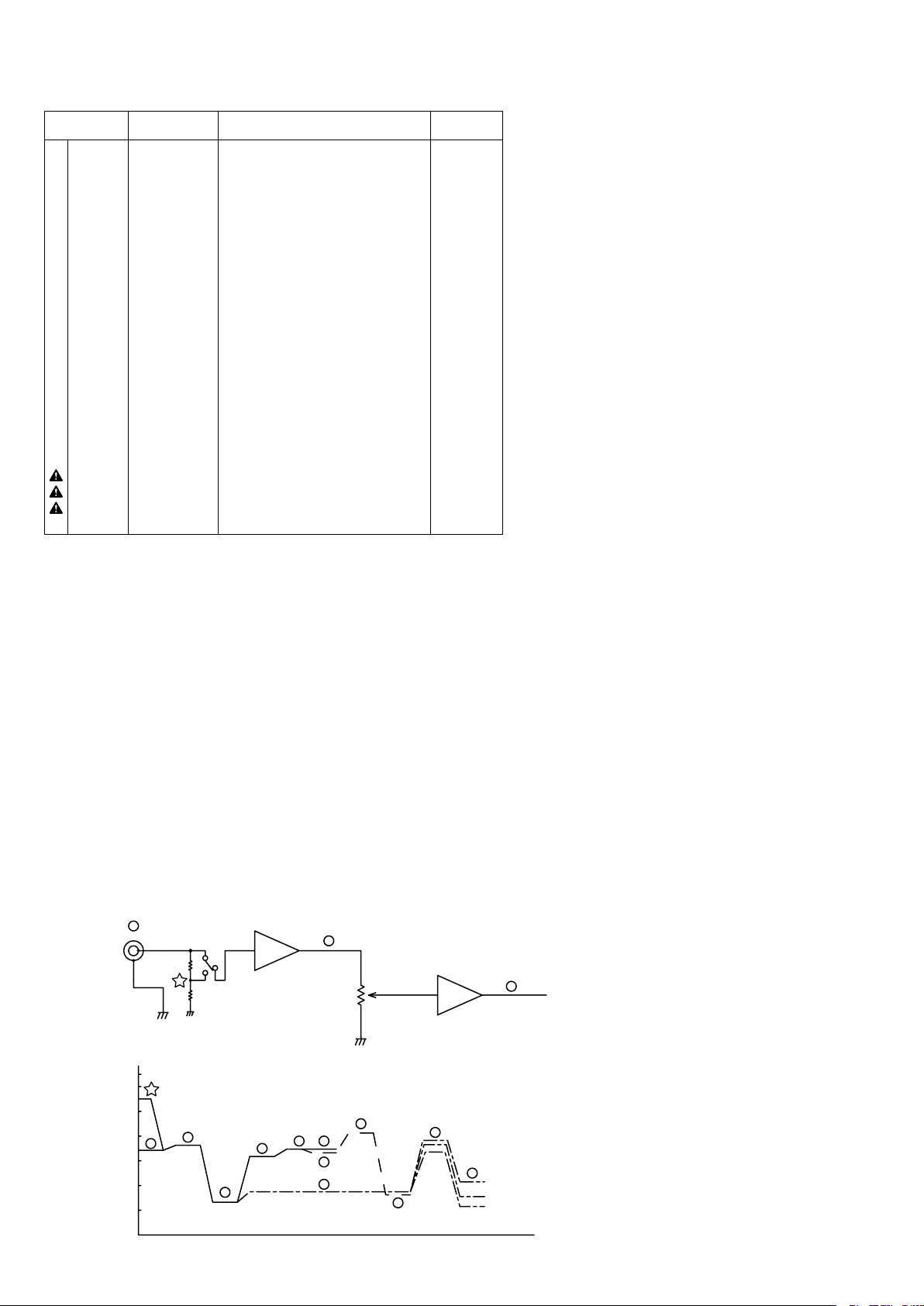

Pos. No. PARTS NO. DESCRIPTION Page

PA01 ATT CIRCUIT BOARD PA01 New

CA01 DK16101300 100pF K 50V PA01 New

CA02 DK16101300 100pF K 50V PA01 New

CA05 DD38104010 0.1µF +80%-20% 50V DC PA01 New

RA01 GD05273160 27kΩ ±5% 1/6W PA01 New

RA02 GD05273160 27kΩ ±5% 1/6W PA01 New

RA03 GD05272160 2.7kΩ ±5% 1/6W PA01 New

RA04 GD05272160 2.7kΩ ±5% 1/6W PA01 New

RA05 GD05224160 220kΩ ±5% 1/6W PA01 New

RA06 GD05224160 220kΩ ±5% 1/6W PA01 New

RA07 GD05222160 2.2kΩ ±5% 1/6W PA01 New

RA08 GD05222160 2.2kΩ ±5% 1/6W PA01 New

RA09 RA03320780 VR. 3.3kΩ PA01 New

RA10 RA03320780 VR. 3.3kΩ PA01 New

QA01 HC10053090 IC NJM-2068-DD PA01 New

SA01 SS02021710 SW. SSAA22-B NON-SHORTING PA01 New

QU01 HS418ST1R Microprocessor(programmed)

TMP87PM41N

P800 59p

J092 YJ04002360 AC INLET 2P SOT-16C Exv. 47p

L001 TS15725180 MAINS TRANSF. Exv. 47p

W001 ZC01801050 MAINS CORD FOR JAPAN Exv. 47p

002T 418S851110 USER GUIDE Exv. 47p

*

【 変更追加は以下の部分 】

-30

-20

-10

0

10

LEVEL [dBV]

LEVEL DIAGRAM

-26.9dBV

3

B QF02

A QF01

2

LINE INPUT

400Hz

1

-3.9dBV

B QG41

A QG01

REC VOL.CENTER

1

2

3

4

5

6

7

8 9

10

11

12

METAL

HIGH

NORMAL

-5.4dBV

1

1

20

25

15

1. TECHNICAL SPECIFICATIONS

Input Sensitivity

Line A (F) .......................................................................................................................................................... 1V

Line B (F) ................................................................................................................................................... 100mV

Input Impedance

Line A (F) ...................................................................................................................................................... 25k

Line B (F) .................................................................................................................................................... 100k

Power Supply

Power Requirement

F Version ............................................................................................................................. 100V AC 50/60Hz

2. LEVEL DIAGRAM

2

Ω

Ω

Line A

input

Loop

Through

out

Line B

input

A

A,B

A, B

A

B:Rec VR

A:Rec VR

Count Rec

sw A

0dB

-20dB

3. BLOCK DIAGRAM

LINE_A_L1

LINE_A_R1

A-GND

JP01

JP02

JG01

7

8

10

9

A-GND

4.7/25v

CG05

4.7/25v

CG06

QG01

NJM4558

7

6

5

8

QG01

1

2

3

4

2.2k

RG05

2.2k

RG06

220k

RG03

220k

RG04

22/16v

CG03

22/16v

CG04

VCC/2_A

VCC/2_A

100p

CG01

100p

CG02

220k

RG01

220k

RG02

0.1

CG30

+12V

A-GND

1.5k

RG94

VCC/2_A

3.3k

RG91

1.5k

RG93

3.3k

RG92

JG01

1

2

3

22/16v

CG07

22/16v

CG08

JG52

1

2

3

4

JG51

1

2

3

4

LINE_A_R1

LINE_A_L1

L

R

LOOP

THROUGH

OUT

6V

6V

6V

6V

6V

6V

A LINE AMP,SELECTOR

INPUT

L

R

LINE A

(3/3)

(1/3)

4. CONNECTION DIAGRAM

・PA01 は PG01 基板上にコネクタでマウントされています。

5. SCHEMATIC DIAGRAM

・LINE A OUT LEVEL ADJ 部 (PG01-1/8:13p 参照 )

・電源部は USA Version と同じ回路図 (P851:31p 参照 )

3

6. EXPLODED VIEW

P G 0 1

5 1 2 8

3 X 8 ( M )

5 1 2 8

3 X 8 ( M )

5 1 2 8

3 X 8 ( M )

5 1 2 8

3 X 8 ( M )

9 0 0 G

9 0 8 G ( U O N L Y )

5 1 5 0

3 X 8 ( U )

J 0 9 2

P A 0 1

F O N L Y

9. ELECTRICAL ADJUSTMENTS

・調整部は 3 箇所 (51p, 53p 参照 )

2. S.R.L Setting

1) Apply a 1kHz, Line A : 1100 mV(F) / 100 mV(U, /02), Line

B : 100 mV to the LINE INPUT jacks.

2) Put the unit in RECORD mode and adjust the REC LEVEL

control to obtain 388 mV of signal at the DOLBY test points

J601 (Deck A) and J651 (Deck B).

3) Adjust the output of the audio oscillator applied to the LINE

INPUT jacks to 70.8 mV (-3 dB). This is the rated recording

condition for the STANDARD RECORDING LEVEL

(S.R.L.).

9.4 LINE OUTPUT LEVEL ADJUSTMENT

1) Connect the audio oscillator to the LINE INPUT jacks.

2) Connect the VTVM to LINE OUTPUT jacks.

3) Set the MONITOR switch to the source position.

4) Set the REC volume to the center click position.

5) Supply 100 mV to the LINE INPUT jacks.

6) Adjust the following semi-xed resistor to set Line A :

1100 mV(F) / 100 mV(U, /02), Line B : 100 mV from the

LINE OUTPUT jacks;

Line A は SW. : SA01(PA01) を -20dB 側にする。

注:

9.7 REC/PLAY-BACK FREQUENCY RESPONSE

ADJUSTMENT

1) Insert the AC-225 tape in the holder.

2) Set the REC volume to the center position.

3) Supply 1kHz Line A : 330 mV(F) / 30 mV(U, /02), Line B :

30 mV to the line input jacks.

4) Record the 400Hz and 12.5kHz signals by turns.

5) Playback the section just recorded, and adjust the

following semi-xed resistor so that the level of differences between 400Hz and 12.5kHz are within 1.0dB;

CH. ADJUSTMENT POINT MECHA.

L R901 A

R R902 A

L R951 B

R R952 B

6) Only check HIGH POSITION and METAL tapes.

CH. ADJUSTMENT POINT MECHA. Ver.

L RA09 (SA01:-20dB, PA01) A F

R RA10 (SA01:-20dB, PA01) A F

L RG91 A U, /02

R RG92 A U, /02

L RG95 B

R RG96 B

4

Loading...

Loading...