Page 1

Intel® 810A3 Chipset Platform

Design Guide

July 2000

Order Number: 298186-002

Page 2

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in med ical, life saving, or life sustaini ng applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

®

The Intel

Current characterized errata are available on request.

I

Implementations of the I

810A3 Chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

2

C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel.

2

C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and

North American Philips Corporation.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by:

calling 1-800-548-4725 or

by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2000

*Third-party brands and names are the property of their respective owners.

Intel® 810A3 Chipset Design Guide

Page 3

Contents

1 Introduction................................................................................................................1-1

1.1 About This Design Guide..............................................................................1-1

1.1.1 Terminology and Definitions ...................................... ...... ....... ...... ...1-2

1.1.2 References.......................................................................................1-7

1.2 System Overview..........................................................................................1-7

1.2.1 Graphics and Memory Controll er Hub (GMCH) ............................ ...1-8

1.2.2 I/O Controller Hub (82801AA ICH)...................................................1-9

1.2.3 System Configurations.....................................................................1-9

1.3 Platform Initiatives.......................................................................................1-10

1.3.1 Hub Interface .................................................................................1-10

1.3.2 Manageability.................................................................................1-10

1.3.3 AC’97.............................................................................................1-11

1.3.4 Low Pin Count (LPC) Interface......................................................1-12

2 PGA370 Processor Design Guidelines......................................................................2-1

2.1 Electrical Differences for Flexible PGA370 Designs.....................................2-1

2.2 PGA370 Socket Definition Details ................................................................2-2

2.2.1 Processor Pin Definition Comparison ..............................................2-3

2.2.2 Layout Guidelines for Intel

2.2.3 Undershoot/Overshoot Requirements .............................................2-9

2.2.4 BSEL[1:0] Implementation for PGA370 Designs .............................2-9

2.2.5 CLKREF Circuit Implementation....................................................2-10

2.2.6 Undershoot/Overshoot Requirements ...........................................2-10

2.2.7 Connecting RESET# and RESET2# on a Flexible

PGA370 Design .............................................................................2-11

2.2.8 Reset Strapping Options................................................................2-11

2.2.9 Voltage Regulation Differences .....................................................2-12

2.2.10 Decoupling Guidelines for Flexible PGA370 Designs....................2-12

2.2.11 Thermal/EMI Differences ...............................................................2-13

2.2.12 Debug Port Changes .....................................................................2-14

®

Pentium® III Processors......................2-4

3 SC242 Processor Design Guidelines.........................................................................3-1

3.1 Intel

3.2 Determine General Topology and Layout.....................................................3-3

3.3 Solution Space..............................................................................................3-3

3.4 Minimizing Crosstalk.....................................................................................3-4

3.5 Motherboard Layout Rules for Non-AGTL+ (CMOS) Signals.......................3-4

3.6 THRMDP and THRMDN........................ ....... ...... ....... ...... ....... ...... ....... ...... ...3-5

3.7 Additional Considerations.............................................................................3-5

3.8 Motherboard Frequency Select for SC242 Designs .....................................3-6

3.9 S.E.C.C. 2 Grounding Retention Mechanism (GRM)....................................3-7

4 Layout and Routing Guidelines..................................................................................4-1

4.1 General Recommendations ............. ...... ....... ...... ..........................................4-1

4.2 Nominal Board Stackup................................................................................4-1

4.3 Component Quadrant Layouts......................................................................4-2

4.4 Intel

Intel® 810A3 Chipset Design Guide iii

®

Pentium® III Processors Layout Guidelines........................................3-1

3.9.1 Motherboard Interfaces....................................................................3-7

®

810A3 Chipset Component Placement...............................................4-4

Page 4

4.5 System Memory Layout Guidelines..............................................................4-5

4.5.1 System Memory Solution Space......................................................4-5

4.5.2 System Memory Routing Example...................................................4-6

4.5.3 System Memory Connectivity ..........................................................4-7

4.6 Display Cache Interface................................................................................4-7

4.6.1 Display Cache Solution Space .............................. ....... ...... ....... ......4-8

4.7 Hub Interface ................................................................................................4-9

4.7.1 Data Signals ............................................. ....... ...... ....... ...... ....... ....4-10

4.7.2 Strobe Signals ...............................................................................4-10

4.7.3 HREF Generation/Distribution .......................................................4-10

4.7.4 Compensation................................................................................4-11

4.8 Ultra ATA/66 ...............................................................................................4-12

4.8.1 IDE Routing Guidelines .................................................................4-12

4.8.2 Ultra ATA/66 Detection..................................................................4-15

4.9 AC’97..........................................................................................................4-18

4.9.1 Audio/Modem Riser Card (AMR)...................................................4-18

4.9.2 AC’97 Routing................................................................................4-19

4.9.3 Motherboard Implementation.........................................................4-21

4.10 USB ............................................................................................................4-22

4.11 IOAPIC (I/O Advanced Programmable Interrupt Controller).......................4-23

4.12 PCI..............................................................................................................4-24

4.13 RTC ............................................................................................................4-24

4.13.1 RTC Crystal ...................................................................................4-24

4.13.2 External Capacitors .......................................................................4-25

4.13.3 RTC Layout Considerations...........................................................4-26

4.13.4 RTC External Battery Connection..................................................4-26

4.13.5 RTC External RTCRESET Circuit..................................................4-27

4.13.6 VBIAS DC Voltage and Noise Measurements..............................4-27

4.14 Processor PLL Filter Recommendation......................................................4-28

4.14.1 Processor PLL Filter Recommendation .........................................4-28

4.14.2 Topology........................................................................................4-28

4.14.3 Filter Specification .........................................................................4-28

4.14.4 Recommendation for Intel Platforms..............................................4-30

4.14.5 Custom Solutions................................ ...... ....... ..............................4-31

4.15 RAMDAC/Display Interface ........................................................................4-32

4.15.1 Reference Resistor (Rset) Calculation...........................................4-33

4.15.2 RAMDAC Board Design Guidelines...............................................4-33

4.16 DPLL Filter Design Guidelines....................................................................4-35

4.16.1 Filter Specification .........................................................................4-36

4.16.2 Recommended Routing/Component Placement............................4-37

4.16.3 Example LC Filter Components.....................................................4-37

5 Advanced System Bus Design ..................................................................................5-1

5.1 AGTL+ Design Guidelines............................................................................5-1

5.1.1 Initial Timing Analysis......................................................................5-2

5.1.2 Determine General Topology, Layout, and Routing Desired...........5-3

5.1.3 Pre-Layout Simulation .....................................................................5-3

5.1.4 Place and Route Board....................................................................5-5

5.1.5 Post-Layout Simulation....................................................................5-7

5.1.6 Validation.........................................................................................5-8

5.2 Theory.........................................................................................................5-10

5.2.1 AGTL+ ...........................................................................................5-10

iv Intel® 810A3 Chipset Design Guide

Page 5

5.2.2 Timing Requirements.....................................................................5-10

5.2.3 Cross-Talk Theory .........................................................................5-11

5.3 More Details and Insight.............................................................................5-13

5.3.1 Textbook Timing Equations ...........................................................5-13

5.3.2 Effective Impedance and Tolerance/Variation ...............................5-14

5.3.3 Power/Reference Planes, PCB Stackup, and High

Frequency Decoupling...................................................................5-14

5.3.4 Clock Routing......... ....... ...... ...........................................................5 -1 7

5.4 Definitions of Flight Time Measurements/Corrections and Signal Quality..5-18

5.4.1 V

Guardband............................................................................5-18

REF

5.4.2 Ringback Levels.............................................................................5-18

5.4.3 Overdrive Region...........................................................................5-18

5.4.4 Flight Time Definition and Measurement .......................................5-19

5.5 Conclusion ..................................................................................................5-19

6 Clocking.....................................................................................................................6-1

6.1 Clock Generation ............................. ...... ....... ...... ....... ...... ....... ...... ................6- 1

6.2 Clock Architecture......... ...... ....... ...... ...... ....... ...... ....... ...................................6-2

6.3 Clock Routing Guidelines .... ....... ...... ...... .......................................................6- 3

6.4 Capacitor Sites..............................................................................................6-6

6.5 Clock Power Decoupling Guideli nes................................ ....... ...... ....... ...... ...6-6

7 System Design Considerations..................................................................................7-1

7.1 Power Delivery..............................................................................................7-1

7.1.1 Intel

®

810A3 Chipset Power Delivery ..............................................7-1

7.1.2 LED Indicator for S0-S5 States........................................................7-5

7.2 Decoupling Guidelines..................................................................................7-6

7.2.1 Vcc

Decoupling........................................................................7-6

CORE

7.2.2 Phase Lock Loop (PLL) Decoupling ................................................7-6

7.2.3 82810A3 GMCH Decoupling Guidelines..........................................7-7

7.2.4 Ground Flood Planes........................................................................7-8

7.3 Thermal Design Power .................................................................................7-8

7.4 Power Sequencing........................................................................................7-9

8 Design Checklist ........................................................................................................8-1

8.1 Design Review Checklist ........................................................ ...... ....... ...... ...8-1

8.1.1 Design Checklist Summary........................... ...... ....... ...... ....... ...... ...8-1

8.2 Pullup and Pulldown Resistor Values .........................................................8-15

8.3 RTC.............................................................................................................8-16

8.4 Power Management Signals.......................................................................8-16

8.4.1 Power Button Implementation........................................................8-18

9 Third-Party Vendor Information..................................................................................9-1

A PCI Devices/Functions/Registers/Interrupts ............................................................. A-1

Intel® 810A3 Chipset Design Guide v

Page 6

Figures

1-1 Intel® 810A3 Chipset ....................................................................................1-9

1-2 AC'97 with Audio and Modem Codec Connections....................................1-12

2-1 Topology for 370-Pin Socket Designs with Single Ended

Termination (SET) ........................................................................................2-6

2-2 Routing for THRMDP and THRMDN ............................................................2-8

2-3 BSEL[1:0] Circuit Implementation for PGA370 Designs...............................2-9

2-4 Examples for CLKREF Divider Circuit ........................................................2-10

2-5 RESET# Schematic for PGA370 Designs ................................. ...... ....... ....2-11

2-6 Capacitor Placement on the Motherboard..................................................2-12

2-7 TAP Connector Comparison............................ ...... ....... ...... ....... ...... ....... ....2-14

3-1 Intel

3-2 Routing for THRMDP and THRMDN ............................................................3-5

3-3 System Bus Frequency Selection Topology for SC242................................3-6

3-4 Hole Locations and Keep-out Zones for Support Components ....................3-7

3-5 Detailed Drawing of Minimum Ground Pad Size and Location.....................3-8

4-1 Nominal Board Stackup................................................................................4-2

4-2 GMCH Quadrant Layout (topview) ...............................................................4-2

4-3 ICH 241-uBGA Quadrant Layout (topview) ..................................................4-3

4-4 uATX Placement Example for PGA370 Processors.....................................4-4

4-5 System Memory Topologies .........................................................................4-5

4-6 System Memory Routing Example ...............................................................4-6

4-7 System Memory Connectivity .......................................................................4-7

4-8 Display Cache (Topology 1) .........................................................................4-7

4-9 Display Cache (Topology 2) .........................................................................4-8

4-10 Display Cache (Topology 3) .........................................................................4-8

4-11 Display Cache (Topology 4) .........................................................................4-9

4-12 Hub Interface Signal Routing Example.........................................................4-9

4-13 Single Hub Interface Reference Divider Circuit..........................................4-11

4-14 Locally Generated Hub Interface Reference Dividers ................................4-11

4-15 IDE Min/Max Routing and Cable Lengths...................................................4-12

4-16 Ultra ATA/66 Cable.....................................................................................4-13

4-17 Resistor Schematic for Primary IDE Connectors........................................4-14

4-18 Resistor Schematic for Secondary IDE Connectors...................................4-14

4-19 Host-Side IDE Cable Detection ..................................................................4-16

4-20 Host-Side IDE Cable Detection ..................................................................4-17

4-21 Host-Side IDE Cable Detection ..................................................................4-17

4-22 Tee Topology AC'97 Trace Length Requirements for ATX ........................4-20

4-23 Daisy-Chain Topology AC'97 Trace Length Requirements for ATX...........4-20

4-24 USB Data Signals.......................................................................................4-23

4-25 PCI Bus Layout Example for 4 PCI Connectors.........................................4-24

4-26 External Circuitry for the ICH RTC..............................................................4-25

4-27 A Diode Circuit to Connect RTC External Battery ......................................4-26

4-28 RTCRESET External Circuit for the ICH RTC ............................................4-27

4-29 Filter Topology............................................................................................4-28

4-30 Filter Specification ......................................................................................4-29

4-31 Using Discrete R.........................................................................................4-30

4-32 No Discrete R .............................................................................................4-31

4-33 Core Reference Model................................................................................4-31

4-34 Schematic of RAMDAC Video Interface .....................................................4-32

®

Pentium® III Uni-Processor Configuration ..........................................3-3

vi Intel® 810A3 Chipset Design Guide

Page 7

4-35 RAMDAC Component and Routing Guidelines ..........................................4-34

4-36 Recommended RAMDAC Reference Resistor Placement and

Connections................................................................................................4-35

4-37 Recommended LC Filter Connection..........................................................4-36

4-38 Frequency Response (see Table 4-13).......................................................4-38

5-1 PICD[1,0] Uni-Processor Topology...............................................................5-7

5-2 Test Load vs. Actual System Load ...............................................................5-9

5-3 Aggressor and Victim Networks..................................................................5-11

5-4 Transmission Line Geometry: (A) Microstrip (B) Stripline...........................5-11

5-5 One Signal Layer and One Reference Plane..............................................5-15

5-6 Layer Switch with One Reference Plane ....................................................5-15

5-7 Layer Switch with Multiple Reference Planes (same type).........................5-15

5-8 Layer Switch with Multiple Reference Planes.............................................5-16

5-9 One Layer with Multiple Reference Planes.................................................5-16

5-10 Overdrive Region and V

5-11 Rising Edge Flight Time Measurement.......................................................5-19

6-1 Intel

®

810A3 Chipset Clock Architecture ......................................................6-2

Guardband.....................................................5-19

REF

6-2 Different Topologies for the Clock Routing Guidelines .................................6-5

6-3 Example of Capacitor Placement Near Clock Input Receiver.......................6-6

7-1 Intel

®

810A3 Chipset Power Delivery Architecture.......................................7-2

7-2 82810A3 GMCH Power Plane Decoupling ...................................................7-8

7-3 G3-S0 Transistion.........................................................................................7-9

7-4 S0-S3-S0 Transition....................................................................................7-10

7-5 S0-S5-S0 Transition....................................................................................7-11

8-1 Pullup Resistor Example.............................................................................8-15

8-2 PWRGOOD and PWROK Logic .................................................................8-17

Intel® 810A3 Chipset Design Guide vii

Page 8

Tables

2-1 Platform Pin Definition Comparison for Single Processor Designs ..............2-2

2-2 Processor Pin Definition Comparison...........................................................2-3

2-3 Intel

®

Pentium® III Processor and GMCH AGTL+ Parameters for

Example Calculations ................... ...... ..........................................................2-4

2-4 Example T

2-5 Example T

FLT_MIN

FLT_MIN

Calculations FOR 100 MHz Bus.....................................2-5

Calculations (Frequency Independent)...........................2-5

2-6 Segment Descriptions and Lengths for Figure 2-1.......................................2-6

2-7 Trace Width (Space Gu id eli nes)............................ .......................................2-6

2-8 Routing Guidelines for Non-AGTL+ Signals.................................................2-8

2-9 Example Resistor Values for CLKREF Divider Circuit (3.3V Source).........2-10

3-1 Intel

®

Pentium® III Processor and GMCH AGTL+ Parameters for

Example Calculations ................... ...... ..........................................................3-1

3-2 Example T

3-3 Example T

FLT_MAX

FLT_MIN

Calculations for 100 MHz Bus .......................................3-2

Calculations (Frequency Independent)...........................3-2

3-4 Segment Descriptions and Lengths for Figure 3-2 ......................................3-3

3-5 Trace Width: Spa ce Guid el ine s ........... ...... ....... ...... ....... ...... ..........................3-3

3-6 Routing Guidelines for Non-AGTL+ Signals.................................................3-4

4-1 System Memory Routing ..............................................................................4-5

4-2 Display Cache Routing (Topology 1)............................................................4-8

4-3 Display Cache Routing (Topology 2)............................................................4-8

4-4 Display Cache Routing (Topology 3)............................................................4-8

4-5 Display Cache Routing (Topology 4)............................................................4-9

4-6 AC’97 Configuration Combinations.............................................................4-18

4-7 Recommended USB Trace Characteristics................................................4-23

4-8 Inductor.......................................................................................................4-30

4-9 Capacitor ....................................................................................................4-30

4-10 Resistor.......................................................................................................4-30

4-11 DPLL LC Filter Component Example..........................................................4-37

4-12 Additional DPLL LC Filter Component Example.........................................4-38

4-13 Resistance Values for Frequency Response Curves (see Figure 4-38).....4-39

5-1 Trace Width Spa ce Guid elines..... ...................................... ....... ...... ....... ......5-6

5-2 Host Clock Routing.......................................................................................5-6

6-1 Intel

®

810A3 Chipset Clocks.........................................................................6-1

6-2 Group Skew and Jitter Limits at the Pins of the Clock Chip .........................6-3

6-3 Signal Group and Resistor............................................................................6-3

6-4 Layout Dimensions .......................................................................................6-4

7-1 Intel

7-2 Intel

®

810A3 Chipset Power Map.................................................................7-3

®

810A3 Chipset Voltage Regulator Specifications ...............................7-4

7-3 Power Sequencing Timing Definitions........................................................7-12

8-1 AGTL+ Connectivity Checklist for 370-Pin Socket Processors.....................8-2

8-2 CMOS Connectivity Checklist for 370-Pin Socket Processors .....................8-3

8-3 TAP Checklist for a 370-Pin Sock et Proc es sor ...........................................8-3

8-4 Miscellaneous Checklist for 370-Pin Socket Processors..............................8-4

8-5 AGTL+ Connectivity Checklist for SC242 Processors..................................8-5

8-6 CMOS Connectivity Checklist for SC242 Processors...................................8-6

8-7 TAP Checklist for SC242 Process or s................................. ....... ...... ....... ......8- 6

8-8 Miscellaneous Checklist for SC242 Processors ...........................................8-6

8-9 Special Consideration Checklist ...................................................................8-7

8-10 Clock Generator Checklist............................................................................8-7

viii Intel® 810A3 Chipset Design Guide

Page 9

8-11 ICH Checklist................................................................................................8-8

8-12 ICH Checklist................................................................................................8-9

8-13 GMCH Checklist .........................................................................................8-10

8-14 System Memory Checklist ..........................................................................8-10

8-15 Display Cache Checklist.............................................................................8-11

8-16 LPC Super I/O Checklist.............................................................................8-11

8-17 IDE Checklist ..............................................................................................8-11

8-18 Clock Generator Checklist............... ...... ....... ...... ....... ...... ...........................8-12

8-19 FWH Flash BIOS Checklist.........................................................................8-12

8-20 PCI Bus Checklist.......................................................................................8-12

8-21 USB / Keyboard / Mouse Checklist.............................................................8-13

8-22 AC’97 Checklist...........................................................................................8-13

8-23 Power Delivery Checklist............................................................................8-14

9-1 Super I/O... ....... ...... .................................................................................... ...9-1

9-2 Clock Generation ................ ..........................................................................9-1

9-3 Memory Vendors...........................................................................................9-1

9-4 Voltage Regulator Vendors...........................................................................9-1

9-5 Flat Panel......................................................................................................9-1

9-6 TV-Out ..........................................................................................................9-2

9-7 Software DVD ...............................................................................................9-2

9-8 AC’97 ............................................................................................................9-2

9-9 TMDS Transmitters.......................................................................................9-3

9-10 TV Encoders.................................................................................................9-3

9-11 Combo TMDS Transmitters/TV Encoders ....................................................9-3

9-12 LVDS Transmitter .........................................................................................9-3

A-1 PCI Devices and Functions.......................................................................... A-1

A-2 PCI Devices and Registers.......................................................................... A-1

A-3 PCI Devices and Interrupts.......................................................................... A-2

Intel® 810A3 Chipset Design Guide ix

Page 10

Revision History

Revision Description Date

001 Initial Release April 2000

002

• Minor edits throughout for clarity

• Added Section 7.2.4, Ground Flood Plane

July 2000

x Intel® 810A3 Chipset Design Guide

Page 11

Introduction

1

Page 12

This page is intentionally left blank

Page 13

Introduction

Introduction

This design guide provides motherboard design guidelines for Intel 810A3 chipset systems.

These design guidelines have been developed to ensure maximum flexibility for board designers

while reducing the risk of board related issues. In addition to design guidelines, this document

discusses Intel

The debug recommendations should be consulted when debugging an Intel

system; however, the debug recommendations should be understood before completing board

design to ensure that the debug port, in addition to other debug features, will be implemen ted

correctly.

•

Please note these earlier design guides are still current:

Intel

chipset device for Intel

Intel

82810E chipset device for the Intel

Bus designs.

1.1 About This Design Guide

This design guide is intended for hardware designers who are experienced with PC architectures

and board design. The design guide assumes that the designer has a working knowledge of the

vocabulary and practices of PC hardware design.

•

Chapter 1, “Introduction”—This chapter introduces the designer to the organization and

purpose of this design guide, and provides a list of references of related documents. This

chapter also provides an overview of the Intel

•

Chapter 2, “PGA370 Processor Design Guidelines”—This chapter provides design guidelines

for the PGA370 processor including processor-specific layout guidelines.

•

Chapter 3, “SC242 Processor Design Guidelines”—This chapter provides design guidelines

for the SC242 processor including processor-specific layout guidelines.

•

Chapter 4, “Layout and Routing Guidelines”—This chapter provides a detailed set of

motherboard layout and routing guidelines, except for processor-specific layout guidelines.

The motherboard functional units are covered (e.g., chipset component placement, system bus

routing, system memory layout, display cache interface, hub interface, IDE, AC’97, USB,

interrupts, SMBUS, PCD, LPC/FWH Flash BIOS, and RTC). For the PGA370 processor

specific layout guidelines, refer to Chapter 2, “PGA370 Processor Design Guidelines”. For the

SC242 processor spcific layout guidelines, refer to Chapter 3, “SC242 Processor Design

Guidelines”.

•

Chapter 5, “Advanced System Bus Design”—The goal of this chapter is to provide the system

designer with the information needed for the implementation of 133 MHz and 100 MHz

AGTL+ bus PCB layout.

•

Chapter 6, “Clocking”— This chapter provides motherboard clocking guidelines (e.g., clock

architecture, routing, capacitor sites, clock power decoupling, and clock skew).

•

Chapter 7, “System Design Con sider ations”— This chapter includes guidelines regarding

power deliver, decoupling, thermal, and power sequencing.

•

Chapter 8, “Design Checklist”— This chapter provides a design review checklist. ATA/66

detection, calculation of pullup/pulldown resistors, minimizing RTC ESD, and power

management signals are also discussed.

810A3 chipset system design issues (e.g., thermal requirements).

®

810 Chipset Design Guide, order number 290657, references the Intel

®

810E Chipset Platform Design Guide, order number 290675, references the Intel

®

Celeron™ processor 66 MHz Front Side Bus designs.

®

Pentium®

810A3 chipset

®

82810A2

processor 100 MHz / 133 MHz Front Side

III

®

810A3 chipset.

1

®

Intel®810A3 Chipset Design Guide 1-1

Page 14

Introduction

•

Chapter 9, “Third-Party Vendor Information”— This chapter includes information regarding

various third-party vendors who provide products to support the Intel

•

Appendix A, “PCI Devices/Functions/Registers/In ter rup ts”— This appendix lists the PCI

devices and functions supported by the Intel

component PCI Vendor ID, Device ID, Revision ID, Class code, Sub-class code, and

Programming Interface code values. In addition, component APIC interrupt and ISA/PCI

IRQs are listed.

1.1.1 Terminology and Definitions

Term Definition

Aggressor A network that transmits a coupled signal to another network is called

the aggressor network.

AGTL+

T

he processor system bus uses a bus technology called AGTL+, or

Assisted Gunning Transceiver Logic. AGTL+ buffers are open-drain

and require pull-up resistors for providing the high logic level and

termination. The processor AGTL+ output buffers differ from GTL+

buffers with the addition of an active pMOS pull-up transistor to “assist”

the pull-up resistors during the first clock of a low-to-high voltage

transition. Additionally, the processor Single Edge Connector (S.E.C.)

cartridge contains 56 Ω pull-up resistors to provide termination at each

bus load.

®

810A3 chipset.

®

810A3 chipset. Also included are a list of

Bus Agent A component or group of components that, when combined, represent a

single load on the AGTL+ bus.

Core power rail A power rail that is only on during

rails are on when the PSON signal is asserted to the ATX power supply.

The core power rails that are distributed

supply are: ±5V, ±12V and +3.3V.

Corner Describes how a component performs when all parameters that could

impact performance are adjusted to have the same impact on

performance. Examples of these parameters include variations in

manufacturing process, operating temperature, and operating voltage.

The results in performance of an electronic component that may change

as a result of corners include (but are not limited to): clock to output

time, output driver edge rate, output drive current, and input drive

current. Discussion of the “slow” corner would mean having a

component operating at its slowest, weakest drive strength performance.

Similar discussion of the “fast” corner would mean having a component

operating at its fastest, strongest drive strength performance. Operation

or simulation of a component at its slow corner and fast corner is

expected to bound the extremes between slowest, weakest performance

and fastest, strongest performance.

full-power

directly

operation. These power

from the ATX power

1-2

Intel®810A3 Chipset Design Guide

Page 15

Introduction

Term Definition

Cross-talk The reception on a victim network of a signal imposed by aggressor

network(s) through inductive and capacitive coupling between the

networks.

•

Backward Cross-talk - coupling which creates a signal in a victim

network that travels in the opposite direction as the aggressor’s

signal.

•

rward Cross-talk - coupling which creates a signal in a victim

Fo

network that travels in the same direction as the aggressor’s signal.

•

Even Mode Cross-talk - coupling from multiple aggressors when all

the aggressors switch in the same direction that the victim is

switching.

•

Odd Mode Cross-talk - coupling from multiple aggressors when all

the aggressors switch in the opposite direction that the victim is

switching.

Derived power rail A derived power rail is any power rail that is ge nerated from ano ther

power rail using an on-board voltage regulator. For example, 3.3VSB is

usually derived (on the motherboard) from 5VSB using a voltage

regulator.

Dual power rail A dual power rail is derived from different rails at different times

(depending on the power state of the system). Usually, a dual power rail

is derived from a standby supply during suspend operation and derived

from a core supply during full-power operation.

Edge Finger The cartridge electrical contact that interfaces to the SC242 connector.

Intel®810A3 Chipset Design Guide 1-3

Page 16

Introduction

Term Definition

Flight Time Flight Time is a term in the timing equation that includes the signal

propagation delay, any effects the system has on the T

of the driver,

CO

plus any adjustments to the signal at the receiver needed to gu arantee the

setup time of the receiver.

More precisely, flight time is defined to be:

•

The time difference between a signal at the input pin of a receiving

agent crossing V

(adjusted to meet the receiver manufacturer’s

REF

conditions required for AC timing specifications; i.e., ringback,

etc.), and the output pin of the driving agent crossing V

REF

if the

driver was driving the Test Load used to specify the driver’s AC

timings.

See Section for details regarding flight time simulation and

validation.

The V

Guardband takes into account sources of noise that may

REF

affect the way an AGTL+ signal becomes valid at the receiver. See

the definition of the V

•

Maximum and Minimum Flight Time - Flight time variations can

Guardband.

REF

be caused by many different parameters. The more obvious causes

include variation of the board dielectric constant, changes in load

condition, cross-talk, V

noise, V

TT

noise, variation in

REF

termination resistance and differences in I/O buffer performance as

a function of temperature, voltage and manufacturing process.

Some less obvious causes include effects of Simultaneous

Switching Output (SSO) and packaging effects.

•

The Maximum Flight Time is the largest flight time a network will

experience under all variations of condi ti ons . Maximu m fl ight time

is measured at the appropriate V

•

The Minimum Flight Time is the smallest flight time a network

Guardband boundary.

REF

will experience under all variations of conditions. Minimum flight

time is measured at the appropriate V

Guardband boundary.

REF

1-4

For more information on flight time and the V

Pentium

®

II Processor Developer’s Manual.

Guardband, see the

REF

Full-power operation During full-power operation, all components on the motherboard r emain

powered. Note that full-power operation includes both the full-on

operating state (S0) and the processor Stop Grant state (S1).

GTL+ GTL+ is the bus technology used by the Pentium Pro processor. This is

an incident wave switching, open-drain bus with pull-up resistors that

provide both the high logic level and termination. It is an enhancement

to the GTL (Gunning Transceiver Logic) technology. See the Pentium

®

II Processor Developer’s Manual for more details of GTL+.

Network The trace of a Printed Circuit Board (PCB) that completes an electrical

connection between two or more components.

Network Length The distance between extreme bus agents on the network and does not

include the distance connecting the end bus agents to the termination

resistors.

Intel®810A3 Chipset Design Guide

Page 17

Term Definition

Introduction

Overdrive Region Is the voltage range, at a receiver, located above and below V

signal integrity analysis. See the Pentium

®

II Processor Developer’s

REF

for

Manual for more details.

Overshoot Maximum voltage allowed for a signal at the processor core pad. See

each process’s Electrical, Mechanical, and Thermal Specification for

overshoot specificatio n.

Pad A feature of a semiconductor die contained within an internal logic

package on the S.E.C cartridge substrate used to connect the die to the

package bond wires. A pad is only observable in simulation.

Pin A feature of a logic package contained within the S.E.C. cartridge used

to connect the package to an internal substrate trace.

Power rails An ATX power supply has 6 power rails: +5V, -5V, +12V, -12V,

+3.3V, +5VSB. In addition to these power rails, several other power

rails can be created with voltage regulators.

Ringback Ringback is the voltage that a signal rings back to after achieving its

maximum absolute value. Ringback may be due to reflections, driver

oscillations, etc. See the respective Processor’s Electrical, Mechanical,

and Thermal Specification for ringback specification.

Settling Limit Defines the maximum amount of ringing at the receiving pin that a

signal must reach before its next transition. See the respective

Processor’s Electrical, Mechanical, and Thermal Specification for

settling limit specification.

Setup Window Is the time between the beginning of Setup to Clock (T

SU_MIN

) and the

arrival of a valid clock edge. This window may be different for each

type of bus agent in the system.

Simultaneous

Switching Output

(SSO) Effects

Refers to the difference in electrical timing parameters and degradation

in signal quality caused by multiple signal ou tputs simultaneously

switching voltage levels (e.g., high-to-low) in the opposite direction

from a single signal (e.g., low-to-high) or in the same direction (e.g.,

high-to-low). These are respectively called odd-mode switching and

even-mode switching. This simultaneous switching of multiple outputs

creates higher current swings that may cause additional propagation

delay (or “pushout”), or a decrease in propagation delay (or “pull-in”).

These SSO effects may impact the setup and/or hold times and are not

always taken into account by simulations. System timing budgets s hould

include margin for SSO effects.

Standby power rail A power rail that in on during suspend operation (these rails are also on

during full-power operation). These rails are on at all times (when the

power supply is plugged into AC power). The only standby power rail

that is distributed directly from the ATX power supply is 5VSB (5V

Standby). There can be other standby rails that are created with voltage

regulators.

Stub The branch from the trunk terminating at the pad of an agent.

Suspend operation During suspend operation, power i s remov ed from s ome compo nents on

the motherboard. The customer reference board supports three suspend

states: processor Stop Grant (S1), Suspend-to-RAM (S3) and Soft-off

(S5).

Intel®810A3 Chipset Design Guide 1-5

Page 18

Introduction

Term Definition

Suspend-To-RAM

(STR)

In the STR state, the system state is stored in main memory and all

unnecessary system logic is turned off. Only main memory and logic

required to wake the system remain powered.

Test Load Intel uses a 50 Ω test load for specifying its components.

Trunk The main connection, excluding interconnect branches, terminating at

agent pads.

Undershoot Maximum voltage allowed for a signal to extend below V

at the

SS

processor core pad. See the respective Processor’s Electrical,

Mechanical, and Thermal Specification for undershoot specifications.

Victim A network that receives a coupled cross-talk signal from another

network is called the victim network.

V

Guardband A guardband (DV

REF

realistic model accounting for noise such as cross-talk, V

noise.

V

REF

) defined above and below V

REF

to provide a more

REF

noise, and

TT

1-6

Intel®810A3 Chipset Design Guide

Page 19

1.1.2 References

•

Intel® 82810 Chipset: Intel® 82810/82810-DC 100 Graph ics and Memor y Con tr oller (GMCH)

Datasheet (Document Number: 290656)

•

Intel® 82801AA (ICH) and 82810AB (ICH0) I/O Controller Hub

(Document Number: 290655)

•

Intel® 82802AB/AC FirmWare Hub (FWH) Datasheet

•

Intel® Celeron Processor Data sh eet

•

Intel® Celeron Processor Specification Update

•

Intel® 810 Chipset Clock Synthesizer/Driver Specification

•

PPGA 370 Power Delivery Guidelines

•

Intel® Pentium® II Processor AGTL+ Guidelines

•

Intel® Pentium® II Processor Power Distribution Guidelines (

•

Intel® Pentium® II Processor Developer's Manual

•

Intel® Pentium II Processor at 350MHz, 400MHz and 450MHz Datasheet (Document

Number: 243657)

•

Intel® Pentium II Processor Specification Update (Document Number: 243337)

•

Intel® Pentium III Processor Datasheet (Document Number: 244452)

•

Intel® Pentium III Processor Specification Update (Document Number: 244453)

•

AP-907: Intel®Pentium III Power Distribution Guidelines (Document Number: 245085)

•

PCI Local Bus Specification, Revision 2.2

•

Universal Serial Bus Specification, Revision 1.0

Introduction

Datasheet

(Document Number: 290658)

(Document Number: 243658)

(Document Number: 243748)

(Document Number: 243330)

Document Number: 243332)

(Document Number: 243341)

1.2 System Overview

The Intel 810A3 chipset is the first generation Integrated Graphics chipset designed for the Intel

Celeron

engines executing in parallel to deliver high performance 3D, 2D, and motion compensation video

capabilities. An integrated centralized memory arbiter allocates memory bandwidth to multiple

system agents to optimize system memory utilization. A new chipset component interconnect, the

hub interface, is designed into the Intel

channel between the memory controller hub and the I/O hub controller.

The Intel

through the Firmware Hub component.

An ACPI compliant Intel

Suspend to RAM (S3), Suspend to Disk (S4), and Soft-off (S5) power management states. Through

the use of an appropriate LAN device, the Intel

remote administration and troubl esh oot i ng .

The Intel

traditionally integrated into the I/O subsystem of PCIsets/AGPsets. This re mov e s m a ny of the

conflicts experienced when installing hardware and drivers into legacy ISA systems. The

elimination of ISA provides true plug-and-play for the Intel

Intel®810A3 Chipset Design Guide 1-7

TM

processor. The graphics accelerator architecture consists of dedicated multi-media

810A3 chipset to provide an efficient communication

810A3 chipset architecture also enables a new security and manageability infrastructure

810A3 chipset platform can support the Full-on (S0), Stop Grant (S1),

810A3 chipset also supports wake-on-LAN* for

810A3 chipset architecture removes th e requirement for the ISA expansi on bus that was

810A3 chipset platform.

Page 20

Introduction

Traditionally, the ISA interface was used for audio and modem devices. The addition of AC’97

allows the OEM to use software configurable AC’97 audio and modem coder/decoders (codecs)

instead of the traditional ISA devices.

The Intel

The GMCH integrates a 66/100MHz, P6 family system bus controller, integrated 2D/3D graphics

accelerator, 100 MHz SDRAM controller and a high-speed hub interface for communication with

the I/O Controller Hub (ICH). The integrates an Ultra ATA/33 (82801AB ICH0) or Ultra ATA/66

(82801AA ICH) controller, USB host controller, LPC interface controller, FWH Flash BIOS

interface controller, PCI interface controller, AC’97 digital controller and a hub interface for

communication with the GMCH.

The Intel

product line. The Intel

architecture and executes MMX

communication performance.

The Intel

Plastic Pin Grid Array (PPGA) package for use in low cost systems in the Basic PC market

segment. The Intel

Pentium II processor with support limited to single processor-based systems. The Intel

processor PPGA includes an integrated 128 KB second level cache with separate 16K instruction

and 16K data level one caches. The second level cache is capable of caching 4 GB of system

memory.

810A3 chipset contains two core components:

•

Host Controller

— 82810A3 Graphics and Memory Controller Hub (GMCH)

— 82810A3-DC100 Graphics and Memory Controller Hub (GMCH)

•

I/O Controller Hub

— 82801AA (ICH)

— 82801AB (ICH0)

®

Celeron™ processor PPGA is the next addition to the Intel Celeron™ processor

®

Celeron™ processor PPGA is based on a P6 family processor core, but is provided in a

®

Celeron™ processor PPGA implements a Dynamic Execution micro-

®

Celeron™ processor PPGA utilizes the AGTL+ system bus used by the

TM

media technology instructions for enhanced media and

®

Celeron™

1.2.1 Graphics and Memory Controller Hub (GMCH)

The GMCH provides the interconnect between the SDRAM and the rest of the system logic:

•

421 Mini BGA

•

Integrated Graphics controller

•

230 MHz RAMDAC

processors with a 66, or 100 MHz

III

Intel®810A3 Chipset Design Guide

1-8

•

Support for Intel Celeron and Intel Pentium

system bus.

•

100 MHz SDRAM interface supporting 64 MB/256 MB/512 MB with 16Mb/64Mb/128Mb

SDRAM technology

•

Optional 100 MHz 4 MB Display Cache

•

Downstream hub interface for access to the ICH

•

TV-Out/Flat Panel Display support

Page 21

1.2.2 I/O Controller Hub (82801AA ICH)

The I/O Controller Hub provides the I/O subsystem with access to the rest of the system:

•

241 Mini BGA

•

Upstream hub interface for access to the GMCH

•

PCI 2.2 interface with 6 PCI Req/Grant Pairs

•

Bus Master IDE controller; supports Ultra ATA/66.

•

USB controller

•

SMBus controller

•

FWH interface (FWH Flash BIOS)

•

LPC interface

•

AC’97 2.1 interface

•

Integrated System Management Contro l ler

•

Alert-on-LAN

•

Interrupt controller

1.2.3 System Configurations

Introduction

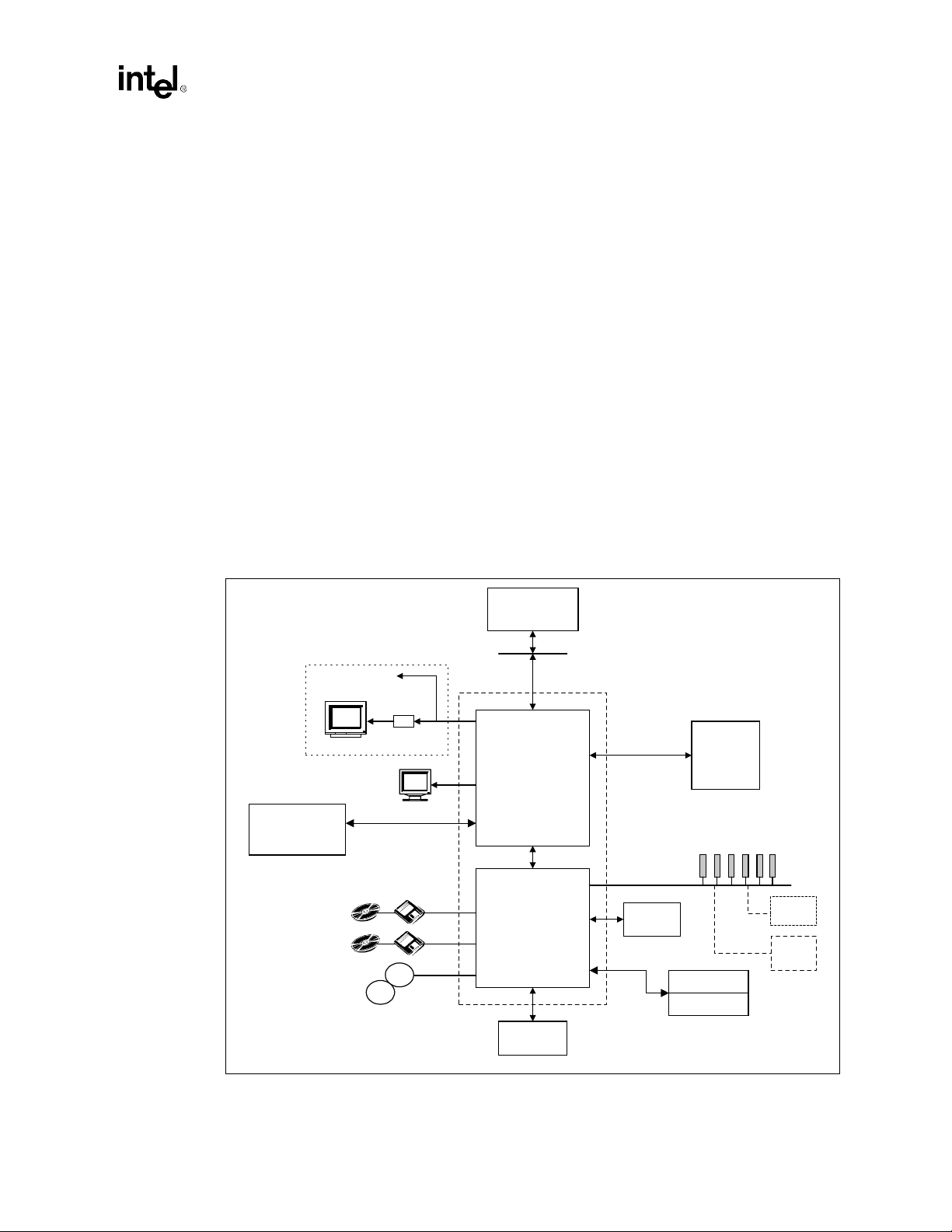

Figure 1-1. Intel 810A3 Chipset

Digital Video Out

TV

Display Cache

(4 MB SDRAM,100 MHz)

2 IDE Ports

Ultra ATA/66

2 USB

Ports

USB

Encoder

Display

USB

Processor

System Bus (66/100 MHz)

Intel® 810A3 Chipset

®

82810A3

Intel

(GMCH)

- Memory Controller

- Graphcs Controller

- 3D Engine

- 2D Engine

- Video Engine

ICH

(I/O Controller Hub)

64 Bit /

100 MHz Only

PCI Bus

Super

I/O

AC'97

System

Memory

PCI Slots

(ICH=6 Req/Gnt pairs)

Audio Codec

Modem Codec

ISA

Option

LAN

Option

FWH Flash

BIOS

Intel®810A3 Chipset Design Guide 1-9

Page 22

Introduction

1.3 Platform Initiatives

1.3.1 Hub Interface

As I/O speeds increase, the demand placed on the PCI bus by the I/O bridge has become

significant. With the addition of AC’97 and Ultra ATA/66, coupled with the existing USB, I/O

requirements could impact PCI bus performance. The Intel

architecture ensures that the I/O subsystem (both PCI and the integrated I/O features (IDE, AC’97,

USB, etc.)), receives adequate bandwidth. By placing the I/O bridge on the hub interface (instead

of PCI), the hub architecture ensures that both the I/O fu nctions integrated into the ICH and the PCI

peripherals obtain the bandwidth necessary for peak performance.

1.3.2 Manageability

The Intel 810A3 chipset platform i ntegrates s everal f unctions d esig ned to manag e the sys tem and

lower the total cost of ownership (TCO) of the system. These system management functions are

designed to report errors, diagnose the s ystem, and recov e r f rom system lo ckup s witho ut the aid of

an external microcontroller.

810A3 Chipset’s hub interface

TCO Timer

The ICH integrates a programmable TCO T imer. This timer is used to detect system locks. The first

expiration of the timer generates an SMI# which the system can use to recover from a software

lock. The second expiration of the timer causes a system reset to recover from a hardware lock.

Processor Present Indicator

The ICH looks for the processor to fetch the first instruction after reset. If the processor does not

fetch the first instruction, the ICH will reboot the system.

Function Disable

The ICH provides the ability to disable the following functions: AC'97 Modem , AC'97 Audio,

IDE, USB or SMBus. Once disabled, these functions no longer decode I/O, memory, or PCI

configuration space. Also, no interrupts or power management events are generated from the

disabled functions.

Intruder Detect

The ICH provides an input signal (INTRUDER#) that can be attached to a switch that is activated

by the system case being opened. The ICH can be programmed to gen erate an SMI# o r TCO ev ent

due to an active INTRUDER# signal.

Alert-On-LAN*

The ICH supports Alert-On-LAN*. In response to a TCO event (intruder detect, thermal event,

processor not booting) the ICH sends a hardcoded message over the SMBus. A LAN controller

supporting the Alert-On-LAN* protocol can decode this SMBu s message and s end a message ov er

the network to alert the network manager.

1-10

Intel®810A3 Chipset Design Guide

Page 23

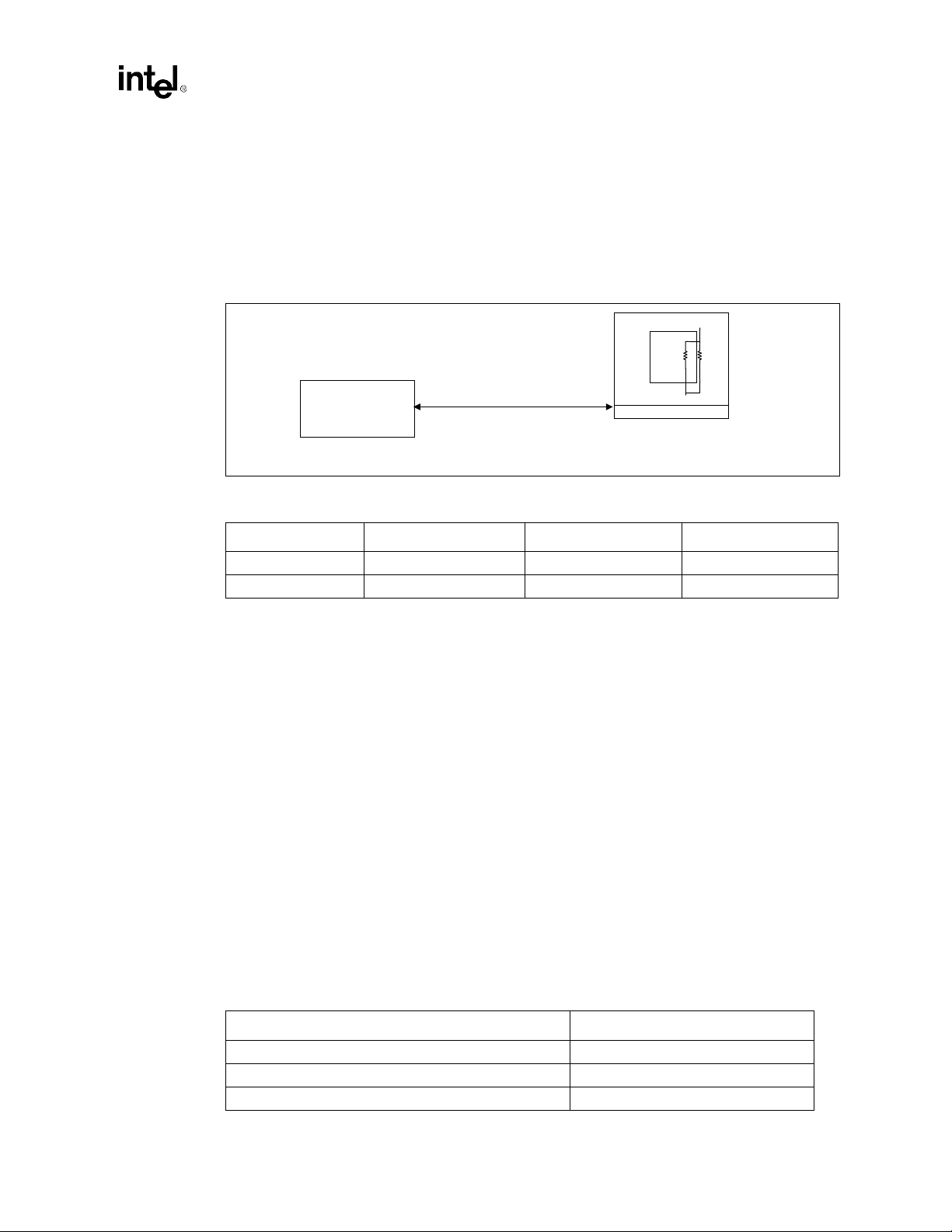

1.3.3 AC’97

The Audio Codec ’97 (AC’97) Specification defines a digital link that can be used to attach an

audio codec (AC), a modem codec (MC), an audio/modem codec (AMC), or both an AC and an

MC. The AC’97 Specification defines the interface between the system logic and the audio or

modem codec known as the AC’97 Digital Link.

The ability to add cost-effective audio and modem solutions as the platform migrates away from

ISA is important. The AC’97 audio and modem components are software configurable, reducing

configuration errors. The Intel

replaces ISA audio and modem functionality, but also improves overall platform integration by

incorporating the AC’97 digital link. Using the Intel

link reduces cost and eases migration from ISA.

The ICH is an AC’97 compliant controller that supports up to two codecs with independent PCI

functions for audio and modem. The ICH communicates with the codec(s) via a digital serial link

called the AC-link. All digital audio/modem streams and command/status information is

communicated over the AC-lin k. Microph one in put and le ft and r ight au dio channel s are sup porte d

for a high quality t wo-speake r audi o solu tion. Wake on ring from suspend is al so s upported wit h an

appropriate modem codec.

Introduction

810A3 chipset’s AC’97 (with the appropriate codecs) not only

810A3 chipset’s integrated AC’97 digital

By using an audio codec, the AC’97 digital link allows for cost-effective, high-quality, in tegrated

audio on the Intel

implemented with the use of a modem codec. Several system options exist when implementing

AC’97. The Intel

810A3 chipset platform. In addition, an AC’97 soft modem can be

810A3 chipset’s integrated digital link allows two external codecs to be

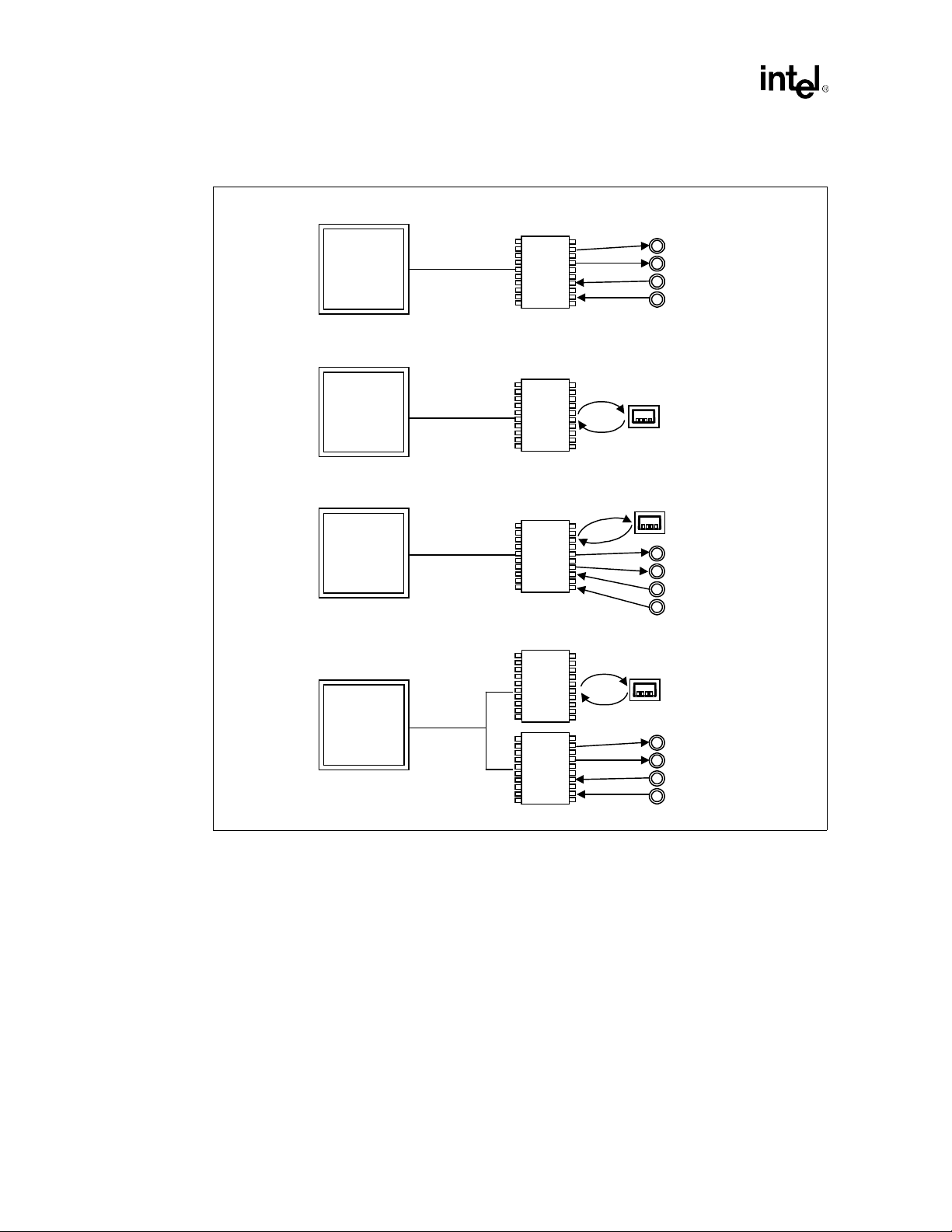

connected to the ICH. The system designer can provide audio with an aud io codec (Figure 1-2 a) or

a modem with a modem codec (Figure 1-2 b). For systems requir ing both audio and a modem,

there are two solutions. The audio codec and the modem codec can be integrated into an AMC

(Figure 1-2 c), or separate audio and modem codecs can be connected to the ICH (Figure 1-2 d).

The modem implementation for different countries should be considered as telephone systems

vary. By using a split design, the audio codec can be on-board and the modem codec can be placed

on a riser. Intel is developing an AC’97 digital link connector. With a single integrated codec, or

AMC, both audio and modem can be routed to a connector near the rear panel where the external

ports can be located.

Intel®810A3 Chipset Design Guide 1-11

Page 24

Introduction

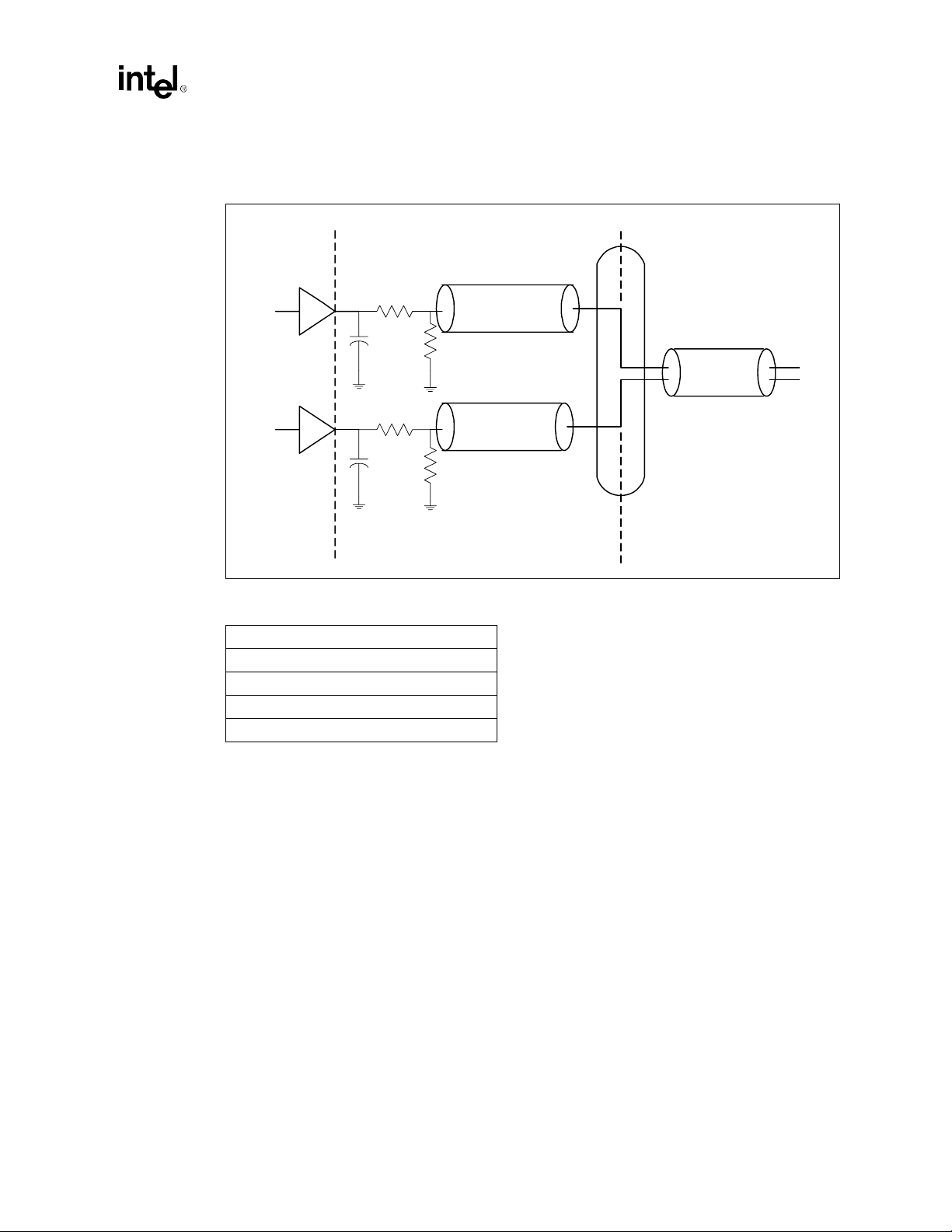

Figure 1-2. AC'97 with Audio and Modem Codec Connections

a) AC'97 With Audio Codec

ICH

(241 mBGA)

b) AC'97 With Modem Codec

ICH

(241 mBGA)

c) AC'97 With Audio/Modem Codec

ICH

(241 mBGA)

d) AC'97 With Audio and Modem Codec

ICH

(241 mBGA)

AC'97 Digital

Link

AC'97 Digital

Link

AC'97 Digital

Link

AC'97

Digital Link

Modem

Modem

Modem

AC'97

Audio

Codec

AC'97

Codec

AC'97

Audio/

Codec

AC'97

Codec

AC'97

Audio

Codec

Audio Ports

Modem Port

Modem Port

Audio Ports

Modem Port

Audio Ports

1.3.4 Low Pin Count (LPC) Interface

In the Intel 810A3 chipset platform, the Super I/O (SIO) component has m igrated to th e Low Pin

Count (LPC) interface. Migration to the LPC interface allows for lower cost Super I/O designs.

The LPC Super I/O component requires the same feature set as traditional Super I/O components.

It should include a keyboard and mouse controller, floppy disk controller and serial and parallel

ports. In addition to the Super I/O features, an integrated game port is recommended because the

AC’97 interface does not provide support for a game port. In a system with ISA audio, the game

port typically existed on the audio card. The fifteen pin game port connector provides for two

joysticks and a two-wire MPU-401 MIDI interface. Consult your preferred Super I/O vendor for a

comprehensive list of devices offered and features supported.

In addition, depending on system requirements, a device bay controller and USB hub could be

integrated into the LPC Super I/O component. For systems requiring ISA sup por t, an ISA-I RQ to

serial-IRQ converter is required. Potentially, this converter could be integrated into the Super I/O.

1-12

a_m_conn.vsd

Intel®810A3 Chipset Design Guide

Page 25

PGA370 Processor

Design Guidelines

2

Page 26

This page is intentionally left blank

Page 27

PGA370 Processor Design Guidelines

This chapter provides PGA370 processor design guidelines including the PGA370

socket, Layout Guidelines, BSEL implementation, CLKREF, Undershoot/Overshoot

requirements, Reset, Decoupling guidelines, Thermal/EMI differences, and Debug Port

changes. The layout guidelines are processor-specific and should be us ed in conjunction

with the Chapter 4, “Layout and Routing Guidelines”. For this chapter, the following

terminology applies:

•

Legacy PGA370 refers to today’s Intel® 810A3 chipset platforms utilizing the

PGA370 socket for the microprocessor. In general, these designs support 66/100

MHz host bus operation, VRM 8.2 DC-DC Converter Guidelines, and Intel

Celeron processors.

•

Flexible PGA370 refers to new generation Intel® 810A3/810E chipset platforms

utilizing the PGA370 socket and designed for microprocessor flexibility. In

general, these designs support 66/100 MHz bus operation for the Intel

chipset and 66/100/133 MHz host bus operation for the Intel

VRM 8.4 DC-DC Converter Guidelines and Intel

®

Intel

Pentium®

processor PGA single processor based designs.

III

®

Celeron, and

®

810E chipset ,

2.1 Electrical Differences for Flexible PGA370 Designs

®

810A3

2

®

There are several electrical changes between the legacy and flexible PGA370 design.

They include:

•

Changes to the PGA370 socket pin definitions. Intel® Pentium®

utilize a superset of the Intel

•

Addition of VTT (AGTL+ termination voltage) delivery to the PGA370 socket.

•

Additional PLL reference voltage, 1.25V, on new CLKREF pin.

•

More stringent undersh oot/oversh oot requirements for CMOS and AGTL+ signals.

•

Addition of on-die Rtt (AGTL+ termination resistors) for the Intel® Pentium®

processor. Requirement remains for on-motherboard Rtt implementation if

supporting the Intel

processors, the reset signals (RESET#) still requires termination to V

motherboard.

Celeron processor pin definition.

Celeron (PPGA). If only supporting Intel® Pentium®

processors

III

on the

TT

III

III

Intel®810A3 Chipset Design Guide 2-1

Page 28

PGA370 Processor Design Guidelines

2.2 PGA370 Socket Definition Details

The following tables compare legacy pin names and functions to new flexible pin names and

functions. Designers need to pay close attention to the notes section for this table for compatibility

concerns regarding these pin changes.

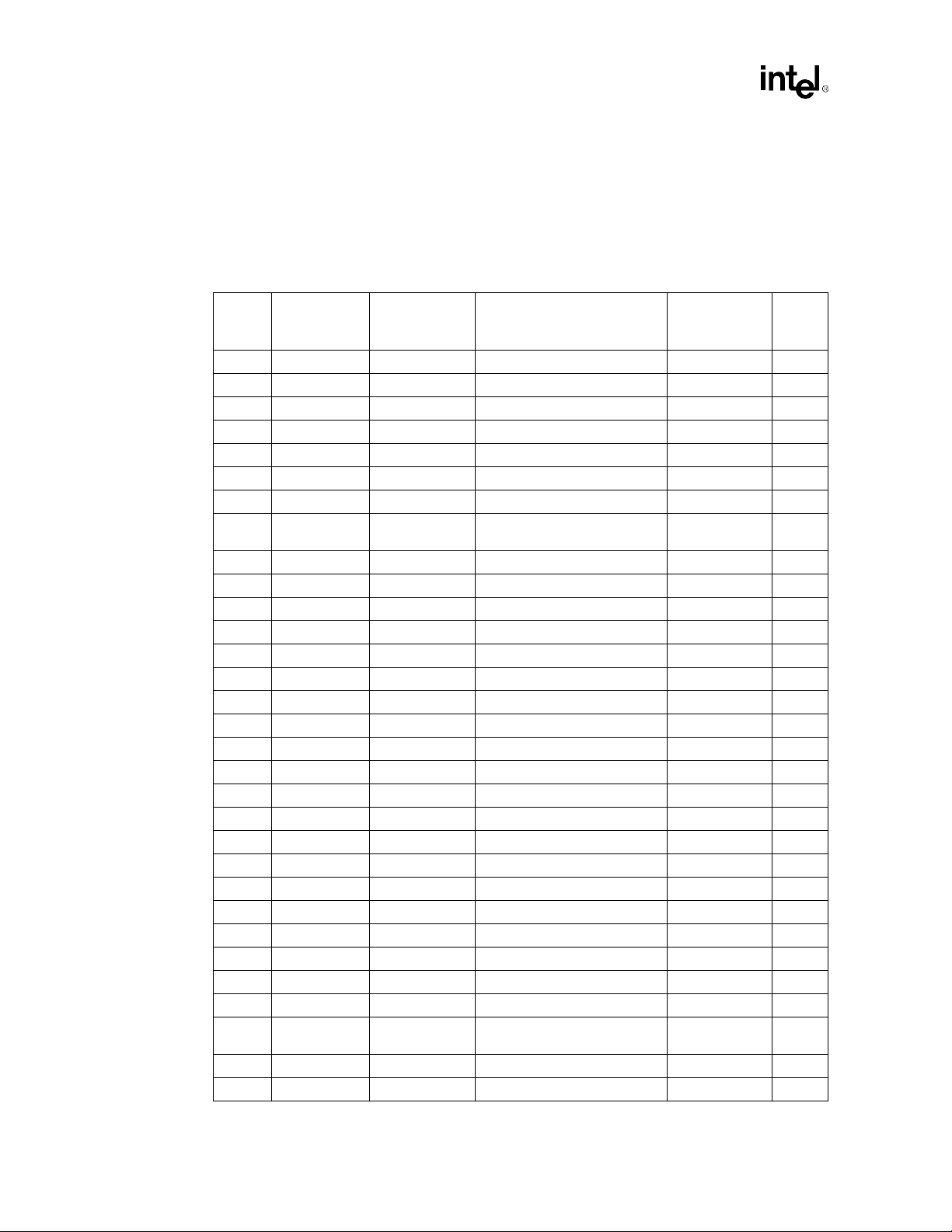

Table 2-1. Platform Pin Definition Comparison for Single Processor Designs

Pin #

A29 Reserved DEP7# Data bus ECC data AGTL+, I/O 2

A31 Reserved DEP3# Data bus ECC data AGTL+, I/O 2

A33 Reserved DEP2# Data bus ECC data AGTL+, I/O 2

AC1 Reserved A33# Additional AGTL+ address AGTL+, I/O 2

AC37 Reserved RSP# Response parity AGTL+, I 2

AF4 Reserved A35# Additional AGTL+ address AGTL+, I/O 2

AH20 Reserved VTT AGTL+ termination voltage Power

AH4 Reserved RESET#

AJ31 GND BSEL1 System bus frequency select CMOS, I/O 1

AK16 Reserved VTT AGTL+ termination voltage Power

AK24 Reserved AERR# Address parity error AGTL+, I/O 2

AL11 Reser ved AP0# Address parity AGTL+, I/O 2

AL13 Reserved VTT AGTL+ termination voltage Power

AL21 Reserved VTT AGTL+ termination voltage Power

AM2 GND Reserved Reserved Reserved 1

AN11 Reserved VTT AGTL+ termination voltage Power

AN13 Reserved AP1# Address parity AGTL+, I/O 2

AN15 Reserved VTT AGTL+ termination voltage Power

AN23 Reserved RP# Request parity AGTL+, I/O

B36 Reserved BINIT# Bus initialization AGTL+, I/O 2

C29 Reserved DEP5# Data bus ECC data AGTL+, I/O 2

C31 Reserved DEP1# Data bus ECC data AGTL+, I/O 2

C33 Reserved DEP0# Data bus ECC data AGTL+, I/O 2

E29 Reserved DEP6# Data bus ECC data AGTL+, I/O 2

E31 Reserved DEP4# Data bus ECC data AGTL+, I/O 2

G35 Reserved VTT AGTL+ termination voltage Power

V4 Reserved BERR# Bus er ror AGTL+, I/O 2

W3 Reserved A34# Additional AGTL+ address AGTL+, I/O 2

X4 RESET# RESET2#

X6 Reserved A32# Additional AGTL+ address AGTL+, I/O 2

Y33 GND CLKREF 1.25V PLL reference Power 1

Legacy

PGA370

pin name

Flexible

PGA370

pin name

Function Type Notes

Processor reset (Intel

®

Pentium

Processor reset (Value

processors)

III)

®

AGTL+, I 3

AGTL+, I 3

2-2

Intel®810A3 Chipset Design Guide

Page 29

PGA370 Processor Design Guidelines

NOTES:

1. These signals were previously defined as ground (Vss) connections in legacy designs utilizing the PGA370

socket to provide termination for unused inputs. For new Flexible PGA370 designs, use the new signal

definitions. These new signal definitions are backwards compatible with the Intel® Celeron processor

(PPGA).

2. While these signals are not used with Intel

support these functions. Only the Intel

platform.

3. The AGTL + reset signal, RESET#, is delivered to pin X4 on Legacy PGA370 designs. On Flexible PGA370

designs it is delivered to X4 and AH4 pins. See Figure 2-1 for more details.

®

810A3 chipset designs, they are available for chipsets that do

®

Pentium® III processor offers these capabilities in the PGA370

2.2.1 Processor Pin Definition Comparison

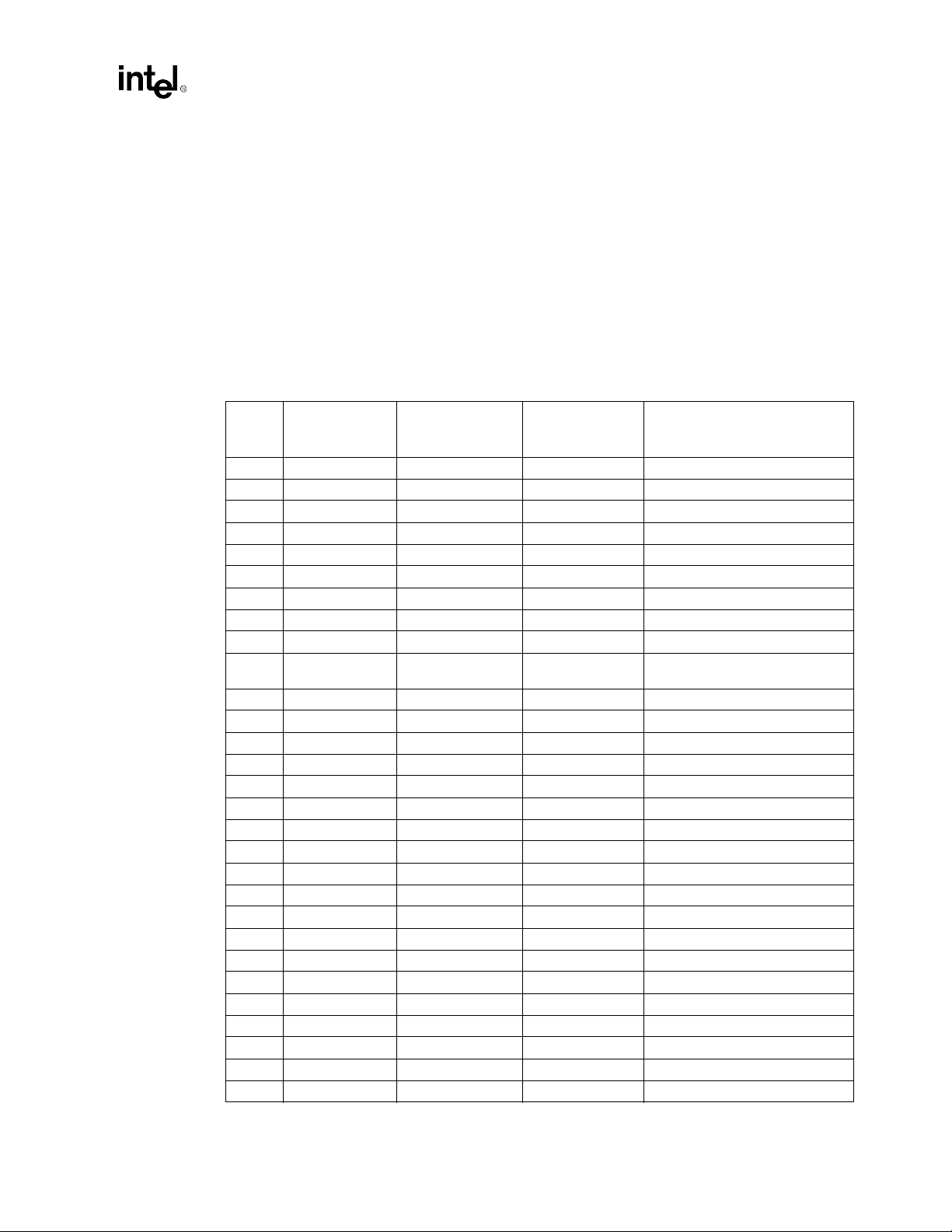

T a ble 2-2. Processor Pin Definition Comparison

®

Intel

Pin #

A29 Reserved Reserved DEP7# Data bus ECC data

A31 Reserved Reserved DEP3# Data bus ECC data

A33 Reserved Reserved DEP2# Data bus ECC data

AA33 Reserved Reserved VTT AGTL+ termination voltage

AA35 Reserved Reserved VTT AGTL+ termination voltage

AC1 Reserved Reserved A33# Additional AGTL+ address

AC37 Reserved Reserved RSP# Response parity

AF4 Reserved Reserved A35# Additional AGTL+ address

AH20 Reserved Reserved VTT AGTL+ termination voltage

AH4 Reserved Reserved RESET#

AJ31 GND BSEL1 BSEL1 S ystem bus fr equency select

AK16 Reserved Reserved VTT AGTL+ termination voltage

AK24 Reserved Reserved AERR# Address parity error

AL11 Reserved Reserved AP0# Address parity

AL13 Reserved Reserved VTT AGTL+ termination voltage

AL21 Reserved Reserved VTT AGTL+ termination voltage

AM2 GND Reserved Reserved Reserved

AN11 Reserved Reserved VTT AGTL+ termination voltage

AN13 Reserved Reserved AP1# Address parity

AN15 Reserved Reserved VTT AGTL+ termination voltage

AN21 Reserved Reserved VTT AGTL+ termination voltage

AN23 Reserved Reserved RP # Request parity

B36 Reserved Reserved BINIT# Bus initialization

C29 Reserved Reserved DEP5# Data bus ECC data

C31 Reserved Reserved DEP1# Data bus ECC data

C33 Reserved Reserved DEP0# Data bus ECC data

E23 Reserved Reserved VTT AGTL+ termination voltage

E29 Reserved Reserved DEP6# Data bus ECC data

E31 Reserved Reserved DEP4# Data bus ECC data

CeleronTM

(PPGA)

pin name

Intel

®

pin name

Pentium® III

128K

Intel

®

pin name

Pentium® III

256K

Function

Processor reset (Intel

processor-256K)

Pentium III

Intel®810A3 Chipset Design Guide 2-3

Page 30

PGA370 Processor Design Guidelines

Table 2-2. Processor Pin Definition Comparison (Continued)

®

Intel

Pin #

G35 Reserved Reserved VTT AGTL+ termination voltage

S33 Reserved Reserved VTT AGTL+ termination voltage

S37 Reserved Reserved VTT AGTL+ termination voltage

U35 Reserved Reserved VTT AGTL+ termination voltage

U37 Reserved Reserved VTT AGTL+ termination voltage

V4 Reserved Reserved B ERR# Bus error

W3 Reserved Reserved A34# Additional AGTL+ address

X4 RESET# RESET# RESET2#

X6 Reserved Reserved A32# Additional AGTL+ address

Y33 GND Reserved CLKREF 1.25V PLL reference

CeleronTM

(PPGA)

pin name

Intel

®

pin name

Pentium® III

128K

Intel

®

pin name

Pentium® III

256K

Function

Processor reset (Celeron PPGA,

Intel Pentium III 128K)

2.2.2 Layout Guidelines for Intel® Pentium® III Processors

The following layout guide supports designs using Intel Celeron processors and Intel®

Pentium

66 MHz for the Intel

The solution proposed in this segment requires the motherboard design to terminate the system bus

AGTL+ sig na l s with a 56 Ω ±5% Rtt. The Intel

®

processor with the Intel 810A3 chipset. The solution covers system bus speeds of

III

Celeron processor and 100 MHz for the Intel® Pentium®

®

Pentium®

processor must also be configured

III

processors.

III

to 110Ω internal Rtt.

Note: 133 MHz system bus frequency is not supported on the Intel

810A3 chipset.

Initial Timing Analysis

Table 2-3 lists the AGTL+ component timings of the processors and 82810A3 GMCH defined at

the pins. These timings are for r eference only; obtain each processor’s specifications fr om its

respective processor Electrical, Mechanical, and Thermal Specification and appropriate

Intel

810A3 chipset component specification.

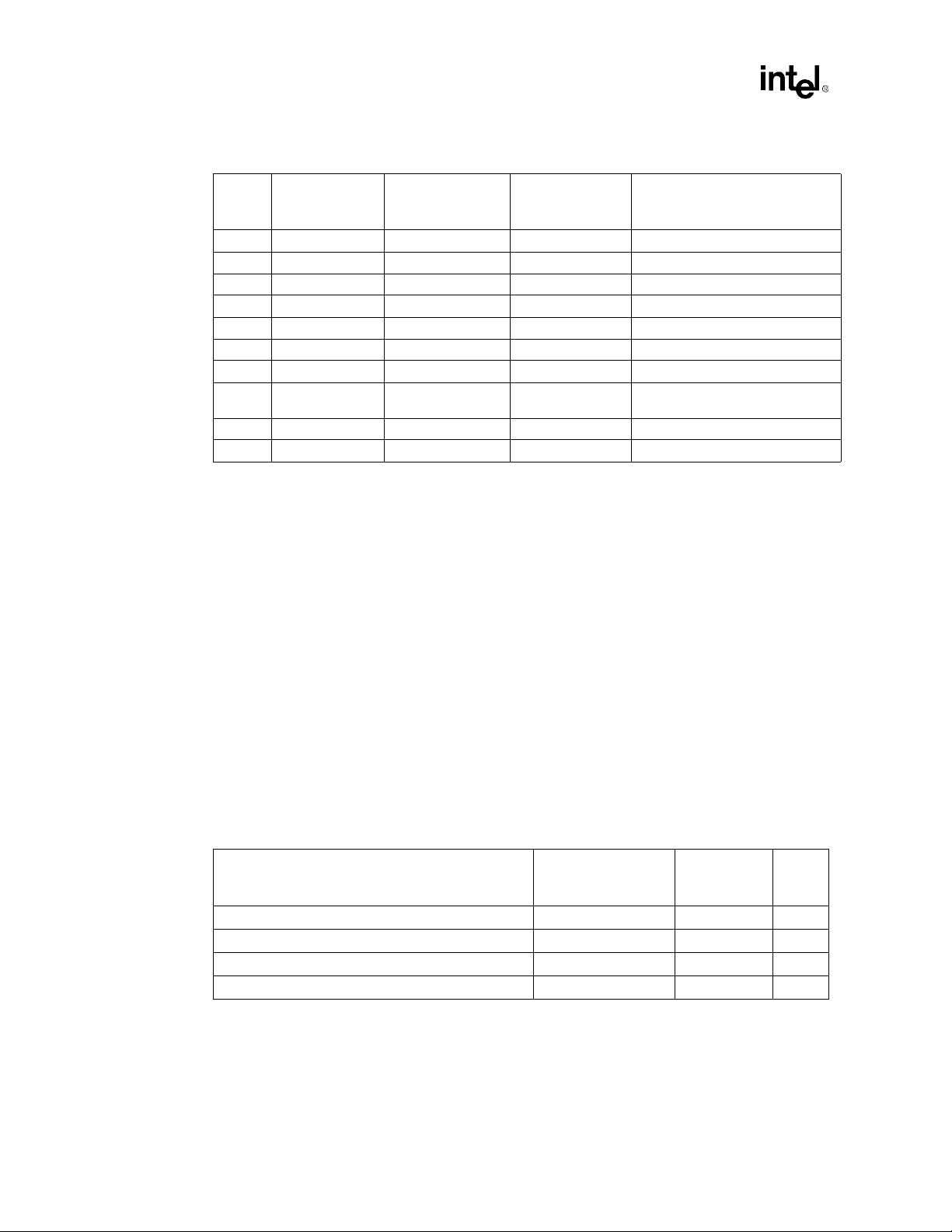

Table 2-3. Intel® Pentium® III Processor and GMCH AGTL+ Parameters for Example

Calculations

®

Intel

IC Parameters

Clock to Output maximum (T

Clock to Output minimum (T

Setup time (T

Hold time (T

) 1.20 2.72 2,3

SU_MIN

) 1.0 0.10

HOLD

Pentium® III

Processor Core at

100 MHz System Bus

)3.255.352

CO_MAX

)0.401.272

CO_MIN

GMCH at

100 MHz

System Bus

Notes

2-4

NOTES:

1. A ll times in nanoseconds.

2.

Numbers in table are for reference only

appropriate component documentation for valid timing parameter values.

3. T

= 2.72 ns assumes the GMCH sees a minimum edge rate equal to 0.3 V/ns.

SU_MIN

. These timing parameters are subject to change. Check the

Intel®810A3 Chipset Design Guide

Page 31

PGA370 Processor Design Guidelines

Table 2-4 gives an example AGTL+ initial maximum flight time and Table 2-5 is an example

minimum flight time calculation for a 100 MHz processor system using the Intel

processor/Intel

jitter were used. Clock skew and clock jitter values are dependent on the clock components

and distribution method chos en for a particular design and must be budgeted into the initial

timing equations as appropriate for each design.

Table 2-4 and Table 2-5 are derived assuming:

•

CLK

SKEW

two host clock outputs together (“ganging”) at clock driver output pins, and the PCB clock

routing skew is 150 ps. System timing budget must assume 0.175 ns of clock driver skew if

outputs are not tied together and a clock driver that meets the CK810 Clock Synthesizer/Driver

Specification is being used.)

•

CLK

JITTER

See the appropriate Intel

Specification for details on clock skew and jitter specifications. Exact details of host clock r outi ng

topology are provided with the platform design guideline.

Table 2-4. Example T

Driver Receiver

Processor GMCH 10 3.25 2.72 0.20 0.25 0.40 3.18

GMCH Processor 10 5.35 1.20 0.20 0.25 0.40 2.60

810A3 chipset system bus. Note that assumed values for clock skew and clock

Pentium

= 0.20 ns (Note: Assumes clock driver p in-to-p in skew is redu ced to 50 ps by tying

= 0.250 ns

810A3 chipset documentation, and CK810 Clock Synthesizer/Driver

Clk

1

SKEW

Clk

JITTERMADJ

Recommended

T

FLT_MAX

FLT_MIN

Calculations FOR 100 MHz Bus

Clk

Period

T

2

CO_MAXTSU_MIN

III

3

NOTES:

1. A ll times in nanoseconds.

2. BCLK period = 10 ns @ 100 MHz.

3. The flight times in this column include margin to account for the following phenomena that Intel has observed

when multiple bits are switching simultaneously. These multi-bit effects can adversely affect flight time and

signal quality and are sometimes not accounted for in simulation. Accordingly, maximum flight times depend

on the baseboard design and additional adjustment factors or margins are recommended.

SSO push-out or pull-in.

•

Rising or falling edge rate degradation at the receiver caused by inductance in the current return path,

•

requiring extrapolation that causes additional delay.

Cross-talk on the PCB and internal to the package can cause variation in the signals.

•

There are additional effects that

should be budgeted as appropriate to the baseboard design. Examples include:

The effective board propagation constant (S

•

— Dielectric constant (

— The type of trace connecting the components (stripline or microstrip).

— The length of the trace and the load of the components on the trace. Note that the board propagation

constant multiplied by the trace length is a

the flight time.

Table 2-5. Example T

Driver Receiver T

Processor GMCH 0.10 0.15 0.35 0.40 0.20

GMCH Proces sor 1.0 0.15 0.35 1.27 0.23

NOTES:

1. A ll times in nanoseconds.

FLT_MIN

may not

) of the PCB material.

ε

r