Page 1

80C196KB

数控原理与维修 http://www.agreenleaf.cn

User’s Guide

November 1990

Order Number: 270651-003

Page 2

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

数控原理与维修 http://www.agreenleaf.cn

otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of

Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

*Third-party brands and names are the property of their respective owners.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be

obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT©INTEL CORPORATION, 1996

Page 3

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

CONTENTS PAGE

1.0 CPU OPERATION

1.1 Memory Controller ААААААААААААААААААА 2

1.2 CPU Control ААААААААААААААААААААААААА 2

1.3 Internal Timing АААААААААААААААААААААА 2

2.0 MEMORY SPACE АААААААААААААААААААААА 4

2.1 Register File ААААААААААААААААААААААААА 4

2.2 Special Function Registers АААААААААА 4

2.3 Reserved Memory Spaces ААААААААААА 8

2.4 Internal ROM and EPROM ААААААААААА 8

2.5 System Bus ААААААААААААААААААААААААА 9

3.0 SOFTWARE OVERVIEW АААААААААААААА 9

3.1 Operand Types АААААААААААААААААААААА 9

3.2 Operand Addressing АААААААААААААААА 10

3.3 Program Status Word ААААААААААААААА 12

3.4 Instruction Set АААААААААААААААААААААА 14

3.5 80C196KB Instruction Set

Additions and Differences

3.6 Software Standards and

Conventions ААААААААААААААААААААААААА 22

3.7 Software Protection Hints ААААААААААА 23

4.0 PERIPHERAL OVERVIEW АААААААААААА 23

4.1 Pulse Width Modulation Output

(D/A) АААААААААААААААААААААААААААААААА 24

4.2 Timers ААААААААААААААААААААААААААААА 24

4.3 High Speed Inputs (HSI) АААААААААААА 24

4.4 High Speed Outputs (HSO) ААААААААА 24

4.5 Serial Port АААААААААААААААААААААААААА 24

4.6 A/D Converter ААААААААААААААААААААА 26

4.7 I/O Ports ААААААААААААААААААААААААААА 26

4.8 Watchdog Timer АААААААААААААААААААА 26

5.0 INTERRUPTS ААААААААААААААААААААААААА 27

5.1 Interrupt Control АААААААААААААААААААА 29

5.2 Interrupt Priorities АААААААААААААААААА 29

5.3 Critical Regions АААААААААААААААААААА 31

5.4 Interrupt Timing АААААААААААААААААААА 31

5.5 Interrupt Summary АААААААААААААААААА 32

ААААААААААААААААААААА 1

АААААААААААА 22

CONTENTS PAGE

6.0 Pulse Width Modulation Output

(D/A)

ААААААААААААААААААААААААААААААААААА 33

6.1 Analog Outputs ААААААААААААААААААААА 35

7.0 TIMERS АААААААААААААААААААААААААААААА 36

7.1 Timer1 ААААААААААААААААААААААААААААА 36

7.2 Timer2 ААААААААААААААААААААААААААААА 36

7.3 Sampling on External Timer

Pins ААААААААААААААААААААААААААААААААА 36

7.4 Timer Interrupts АААААААААААААААААААА 37

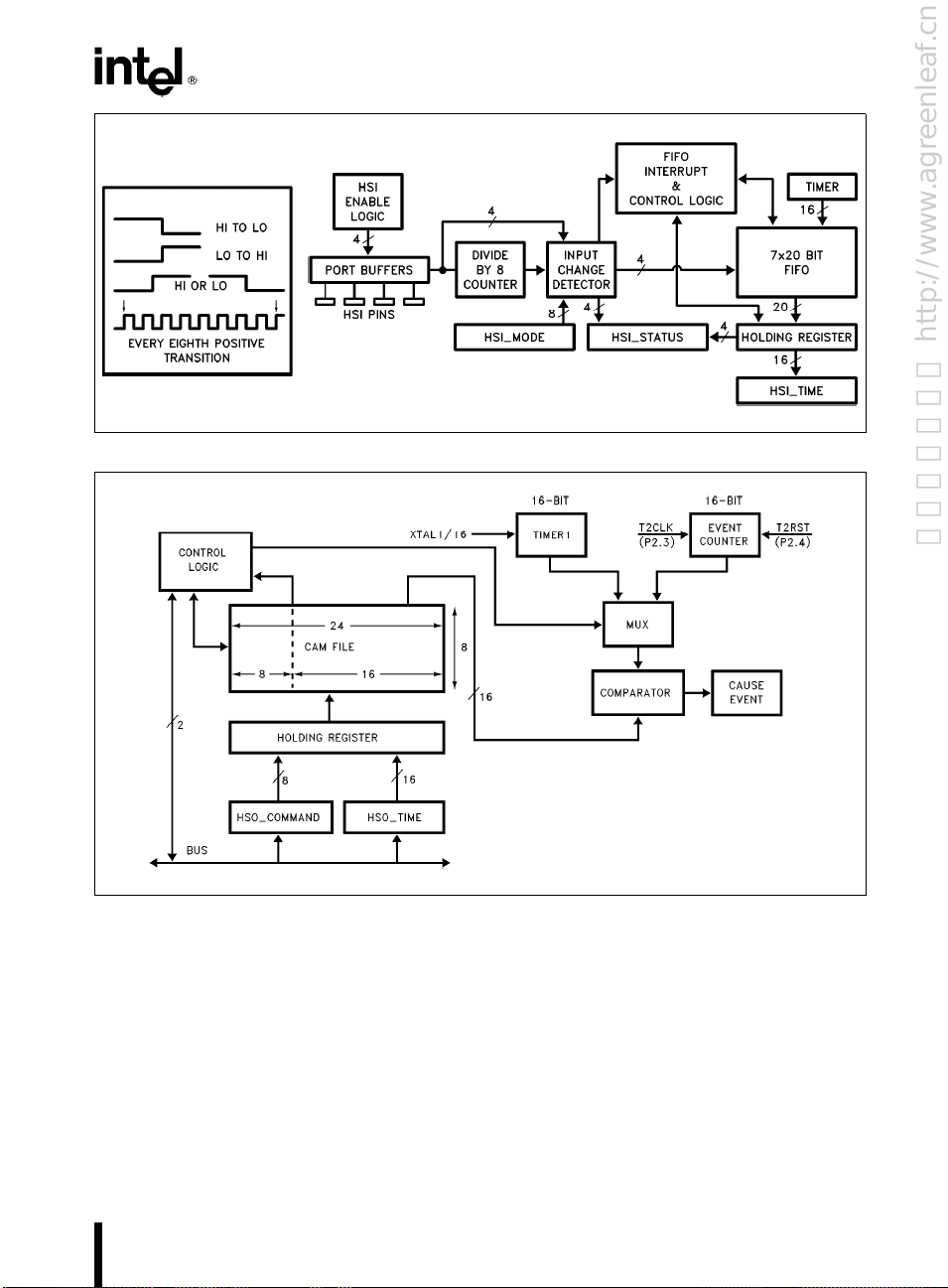

8.0 HIGH SPEED INPUTS АААААААААААААААА 38

8.1 HSI Modes ААААААААААААААААААААААААА 39

8.2 HSI Status ААААААААААААААААААААААААА 39

8.3 HSI Interrupts АААААААААААААААААААААА 40

8.4 HSI Input Sampling ААААААААААААААААА 40

8.5 Initializing the HSI АААААААААААААААААА 40

9.0 HIGH SPEED OUTPUTS АААААААААААААА 40

9.1 HSO Interrupts and Software

Timers ААААААААААААААААААААААААААААААА 41

9.2 HSO CAM АААААААААААААААААААААААААА 42

9.3 HSO Status АААААААААААААААААААААААА 43

9.4 Clearing the HSO and Locked

Entries ААААААААААААААААААААААААААААААА 43

9.5 HSO Precautions ААААААААААААААААААА 44

9.6 PWM Using the HSO ААААААААААААААА 44

9.7 HSO Output Timing ААААААААААААААААА 45

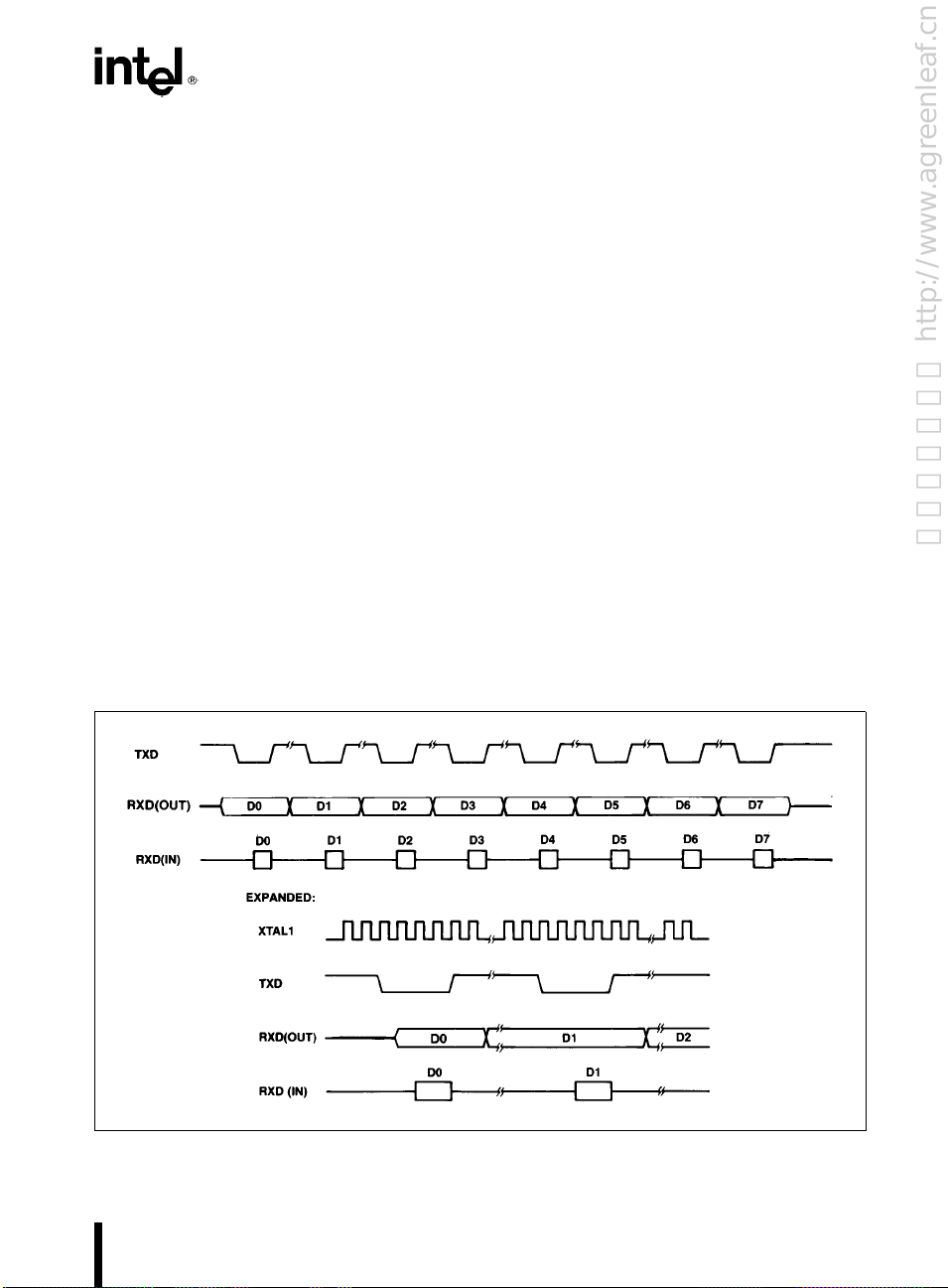

10.0 SERIAL PORT ААААААААААААААААААААААА 45

10.1 Serial Port Status and Control ААААА 47

10.2 Serial Port Interrupts АААААААААААААА 49

10.3 Serial Port Modes ААААААААААААААААА 49

10.4 Multiprocessor

Communications ААААААААААААААААААААА 51

11.0 A/D CONVERTER ААААААААААААААААААА 51

11.1 A/D Conversion Process АААААААААА 53

11.2 A/D Interface Suggestions АААААААА 53

11.3 The A/D Transfer Function АААААААА 54

11.4 A/D Glossary of Terms АААААААААААА 58

Page 4

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

CONTENTS PAGE

12.0 I/O PORTS

12.1 Input Ports АААААААААААААААААААААААА 60

12.2 Quasi-Bidirectional Ports АААААААААА 60

12.3 Output Ports АААААААААААААААААААААА 62

12.4 Ports 3 and 4/AD0 –15 АААААААААААА 63

13.0 MINIMUM HARDWARE

CONSIDERATIONS АААААААААААААААААААА 64

13.1 Power Supply ААААААААААААААААААААА 64

13.2 Noise Protection Tips ААААААААААААА 64

13.3 Oscillator and Internal Timings ÀÀÀÀ 64

13.4 Reset and Reset Status ААААААААААА 65

13.5 Minimum Hardware

Connections

14.0 SPECIAL MODES OF

OPERATION

14.1 Idle Mode ААААААААААААААААААААААААА 69

14.2 Powerdown Mode ААААААААААААААААА 69

14.3 ONCE and Test Modes АААААААААААА 70

АААААААААААААААААААААААААА 60

ААААААААААААААААААААААААА 68

ААААААААААААААААААААААААААА 69

CONTENTS PAGE

15.0 EXTERNAL MEMORY

INTERFACING

15.1 Bus Operation АААААААААААААААААААА 71

15.2 Chip Configuration Register ААААААА 72

15.3 Bus Width ААААААААААААААААААААААААА 75

15.4 HOLD/HLDA Protocol ААААААААААААА 76

15.5 AC Timing Explanations ААААААААААА 78

15.6 Memory System Examples АААААААА 83

15.7 I/O Port Reconstruction ААААААААААА 85

16.0 USING THE EPROM ААААААААААААААААА 85

16.1 Power-Up and Power-Down ААААААА 85

16.2 Reserved Locations ААААААААААААААА 86

16.3 Programming Pulse Width

Register (PPW) АААААААААААААААААААААА 87

16.4 Auto Configuration Byte

Programming Mode

16.5 Auto Programming Mode АААААААААА 88

16.6 Slave Programming Mode ААААААААА 90

16.7 Run-Time Programming ААААААААААА 92

16.8 ROM/EPROM Memory Protection

Options

16.9 Algorithms АААААААААААААААААААААААА 94

ААААААААААААААААААААААААА 71

АААААААААААААААААА 88

АААААААААААААААААААААААААААААА 93

Page 5

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

bus controller

slave PC

The 80C196KB family is a CHMOS branch of the

MCS

-96 family. Other members of the MCS-96 fami-

É

ly include the 8096BH and 8098. All of the MCS-96

components share a common instruction set and architecture. However the CHMOS components have enhancements to provide higher performance at lower

power consumptions. To further decrease power usage,

these parts can be placed into idle and powerdown

modes.

MCS-96 family members are all high-performance microcontrollers with a 16-bit CPU and at least 230 bytes

of on-chip RAM. They are register-to-register machines, so no accumulator is needed, and most operations can be quickly performed from or to any of the

registers. In addition, the register operations can control the many peripherals which are available on the

chips. These peripherals include a serial port, A/D converter, PWM output, up to 48 I/O lines and a HighSpeed I/O subsystem which has 2 16-bit timer/counters, an 8-level input capture FIFO and an 8-entry programmable output generator.

Typical applications for MCS-96 products are closedloop control and mid-range digital signal processing.

MCS-96 products are being used in modems, motor

controls, printers, engine controls, photocopiers, antilock brakes, air conditioner temperature controls, disk

drives, and medical instrumentation.

There are many members of the 80C196KB family, so

to provide easier reading this manual will refer to the

80C196KB family generically as the 80C196KB.

Where information applies only to specific components

it will be clearly indicated.

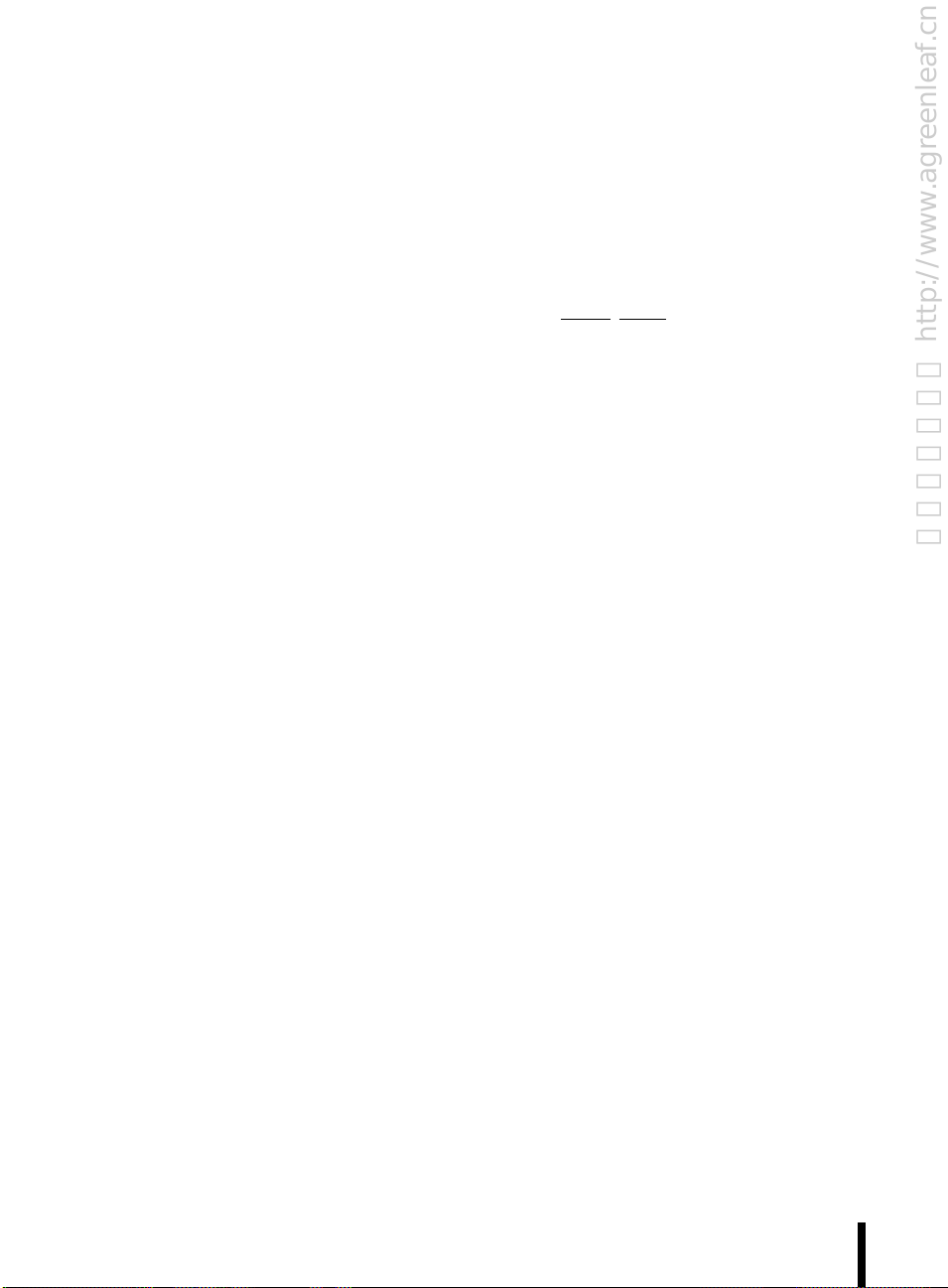

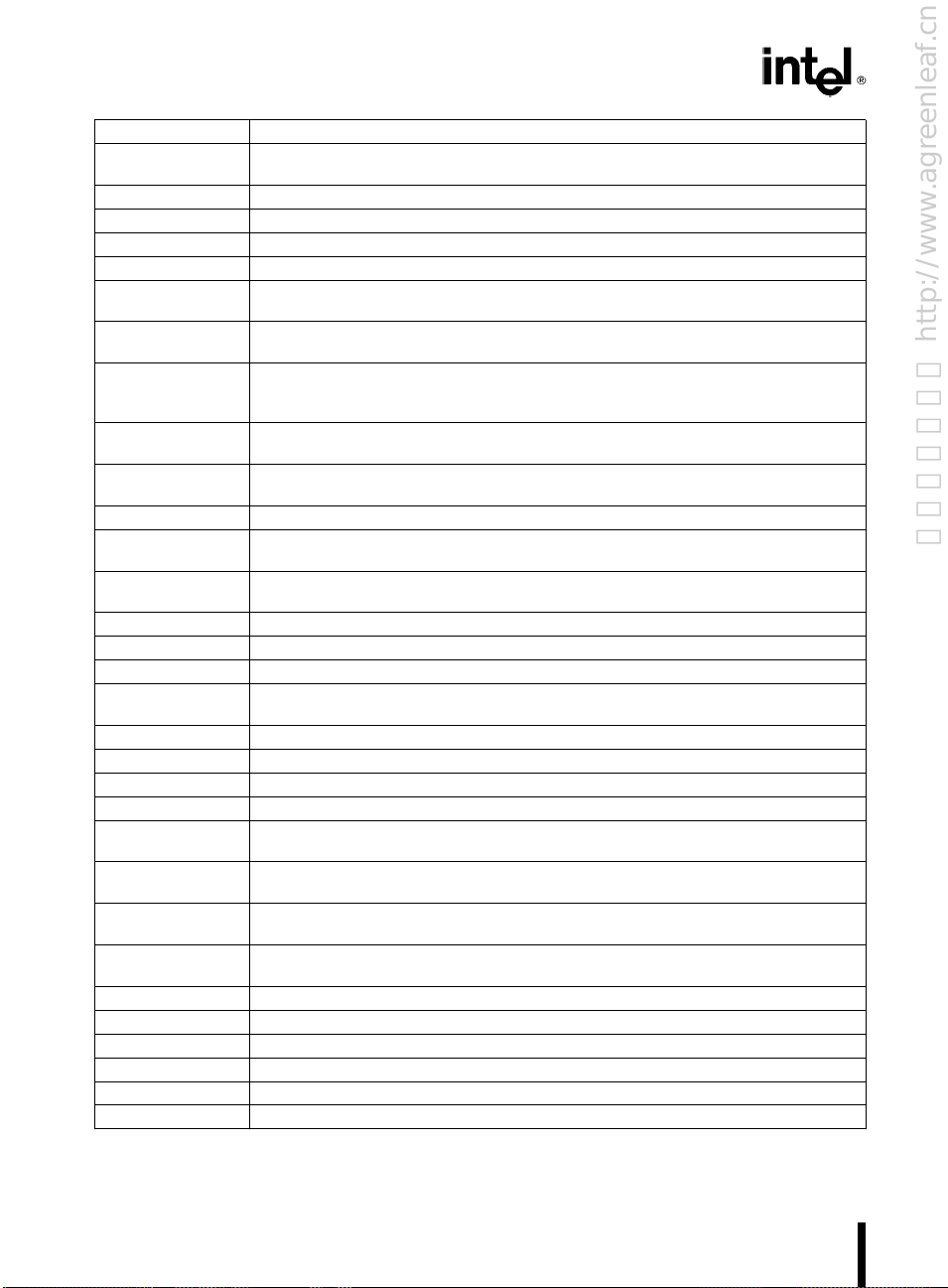

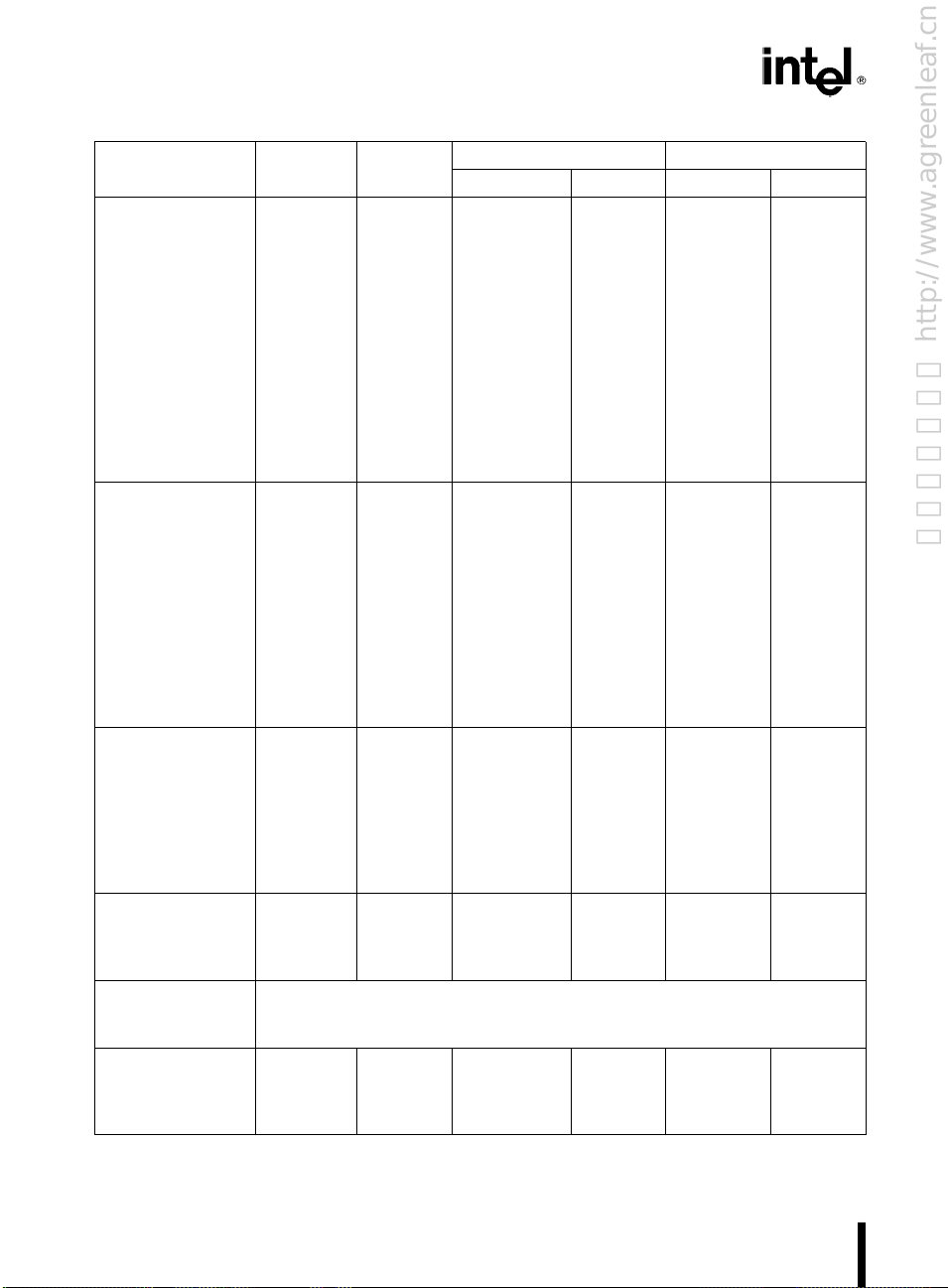

The 80C196KB can be separated into four sections for

the purpose of describing its operation. A block diagram is shown in Figure 1-1. There is the CPU and

architecture, the instruction set, the peripherals and the

bus unit. Each of the sections will be sub-divided as the

discussion progresses. Let us first examine the CPU.

1.0 CPU OPERATION

The major components of the CPU on the 80C196KB

are the Register File and the Register/Arithmetic Logic Unit (RALU). Communication with the outside

world is done through either the Special Function Registers (SFRs) or the Memory Controller. The RALU

does not use an accumulator. Instead, it operates directly on the 256-byte register space made up of the

Register File and the SFRs. Efficient I/O operations

are possible by directly controlling the I/O through the

SFRs. The main benefits of this structure are the ability

to quickly change context, absence of accumulator bottleneck, and fast throughput and I/O times.

270651– 1

Figure 1-1. 80C196KB Block Diagram

1

Page 6

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

The CPU on the 80C196KB is 16 bits wide and connects to the interrupt controller and the memory controller by a 16-bit bus. In addition, there is an 8-bit bus

which transfers instruction bytes from the memory controller to the CPU. An extension of the 16-bit bus connects the CPU to the peripheral devices.

1.1 Memory Controller

The RALU talks to the memory, except for the locations in the register file and SFR space, through the

memory controller. Within the memory controller is a

bus controller, a four byte queue and a Slave Program

Counter (Slave PC). Both the internal ROM/EPROM

bus and the external memory bus are driven by the bus

controller. Memory access requests to the bus controller can come from either the RALU or the queue, with

queue accesses having priority. Requests from the

queue are always for instruction at the address in the

slave PC.

By having program fetches from memory referenced to

the slave PC, the processor saves time as addresses seldom have to be sent to the memory controller. If the

address sequence changes because of a jump, interrupt,

call or return, the slave PC is loaded with a new value,

the queue is flushed, and processing continues.

Execution speed is increased by using a queue since it

usually keeps the next instruction byte available. The

instruction execution times shown in Section 3 show

the normal execution times with no wait states added

and the 16-bit bus selected. Reloading the slave PC and

fetching the first byte of the new instruction stream

takes 4 state times. This is reflected in the jump taken/

not-taken times shown in the table.

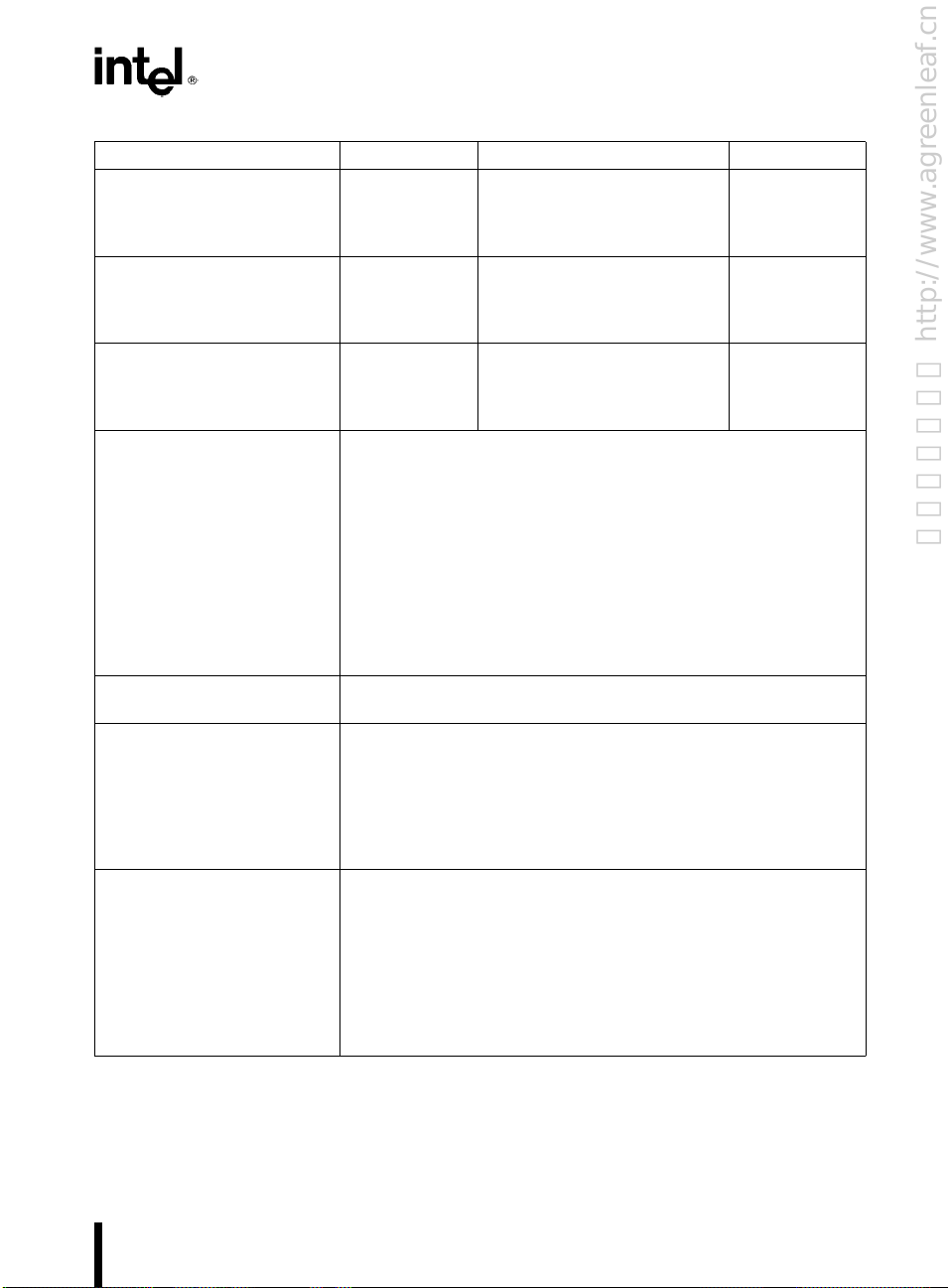

REGISTER/ALU (RALU)

Most calculations performed by the 80C196KB take

place in the RALU. The RALU, shown in Figure 1-2,

contains a 17-bit ALU, the Program Status Word

(PSW), the Program Counter (PC), a loop counter, and

three temporary registers. All of the registers are 16bits or 17-bits (16

registers have the ability to perform simple operations

to off-load the ALU.

A separate incrementor is used for the Program Counter (PC) as it accesses operands. However, PC changes

due to jumps, calls, returns and interrupts must be handled through the ALU. Two of the temporary registers

have their own shift logic. These registers are used for

the operations which require logical shifts, including

Normalize, Multiply, and Divide. The ‘‘Lower Word’’

and ‘‘Upper Word’’ are used together for the 32-bit

instructions and as temporary registers for many instructions. Repetitive shifts are counted by the 6-bit

‘‘Loop Counter’’.

A third temporary register stores the second operand of

two operand instructions. This includes the multiplier

during multiplications and the divisor during divisions.

To perform subtractions, the output of this register can

be complemented before being placed into the ‘‘B’’ input of the ALU.

Several constants, such as 0, 1 and 2 are stored in the

RALU to speed up certain calculations. (e.g. making a

2’s complement number or performing an increment or

decrement instruction.) In addition, single bit masks for

bit test instructions are generated in the constant register based on the 3-bit Bit Select register.

a

sign extension) wide. Some of the

When debugging code using a logic analyzer, one must

be aware of the queue. It is not possible to determine

when an instruction will begin executing by simply

watching when it is fetched, since the queue is filled in

advance of instruction execution.

1.2 CPU Control

A microcode engine controls the CPU, allowing it to

perform operations with any byte, word or double word

in the 256 byte register space. Instructions to the CPU

are taken from the queue and stored temporarily in the

instruction register. The microcode engine decodes the

instructions and generates the correct sequence of

events to have the RALU perform the desired function.

Figure 1-2 shows the memory controller, RALU, instruction register and the control unit.

2

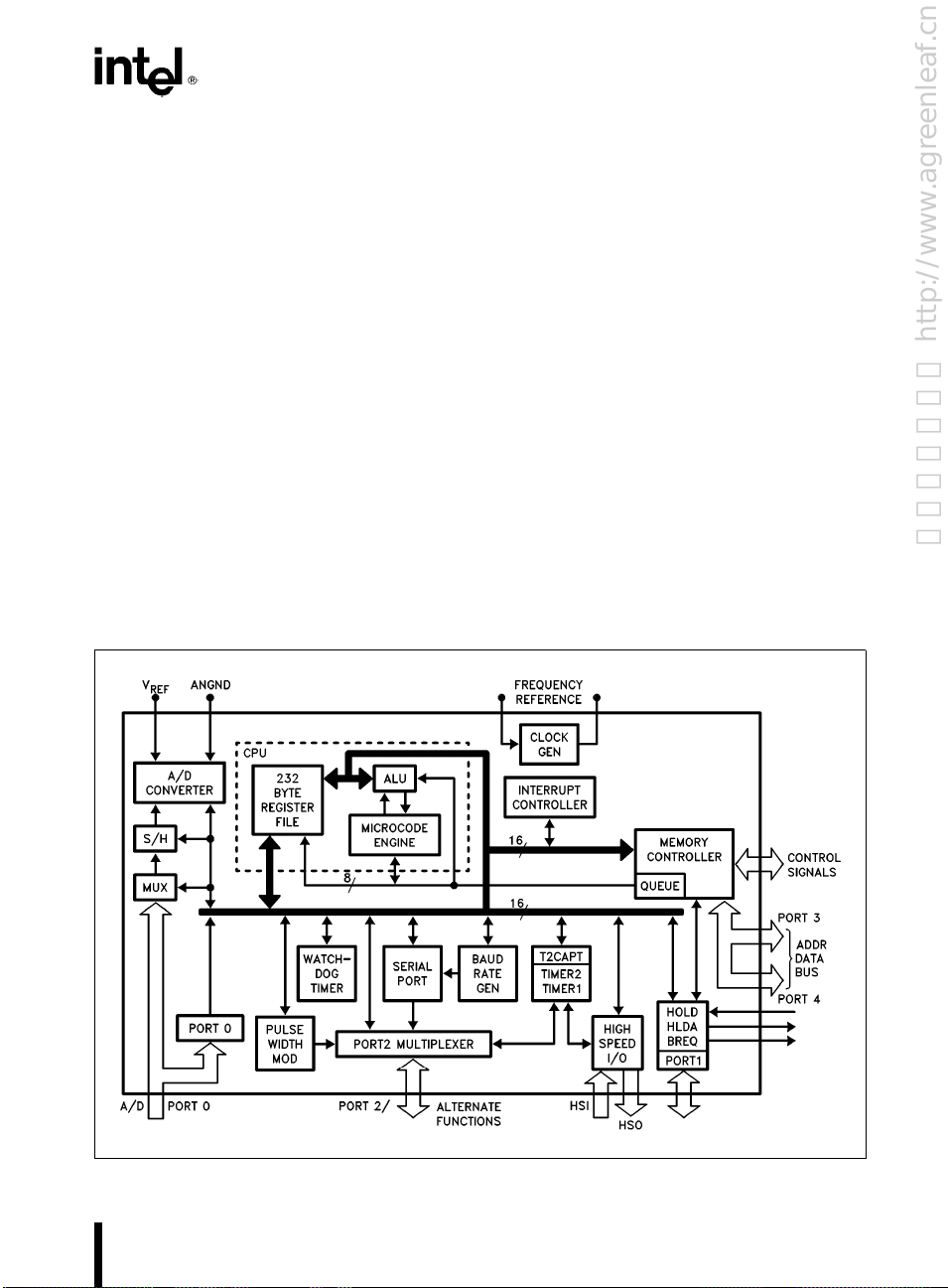

1.3 Internal Timing

The 80C196KB requires an input clock on XTAL1 to

function. Since XTAL1 and XTAL2 are the input and

output of an inverter a crystal can be used to generate

the clock. Details of the circuit and suggestions for its

use can be found in Section 13.

Internal operation of the 80C196KB is based on the

crystal or external oscillator frequency divided by 2.

Every 2 oscillator periods is referred to as one ‘‘state

time’’, the basic time measurement for all 80C196KB

operations. With a 12 MHz oscillator, a state time is

167 nanoseconds. With an 8 MHz oscillator, a state

time is 250 nanoseconds, the same as an 8096BH running with a 12 MHz oscillator. Since the 80C196KB

will be run at many frequencies, the times given

throughout this chapter will be in state times or

‘‘states’’, unless otherwise specified. A clock out

Page 7

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

master PC

270651– 2

Figure 1-2. RALU and Memory Controller Block Diagram

3

Page 8

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

约8K(8064字节)

48K

约8K(7934字节)

程序代码

(CLKOUT) signal, shown in Figure 1-3, is provided as

an indication of the internal machine state. Details on

timing relationships can be found in Section 13.

270651– 3

Figure 1-3. Internal Clock Waveforms

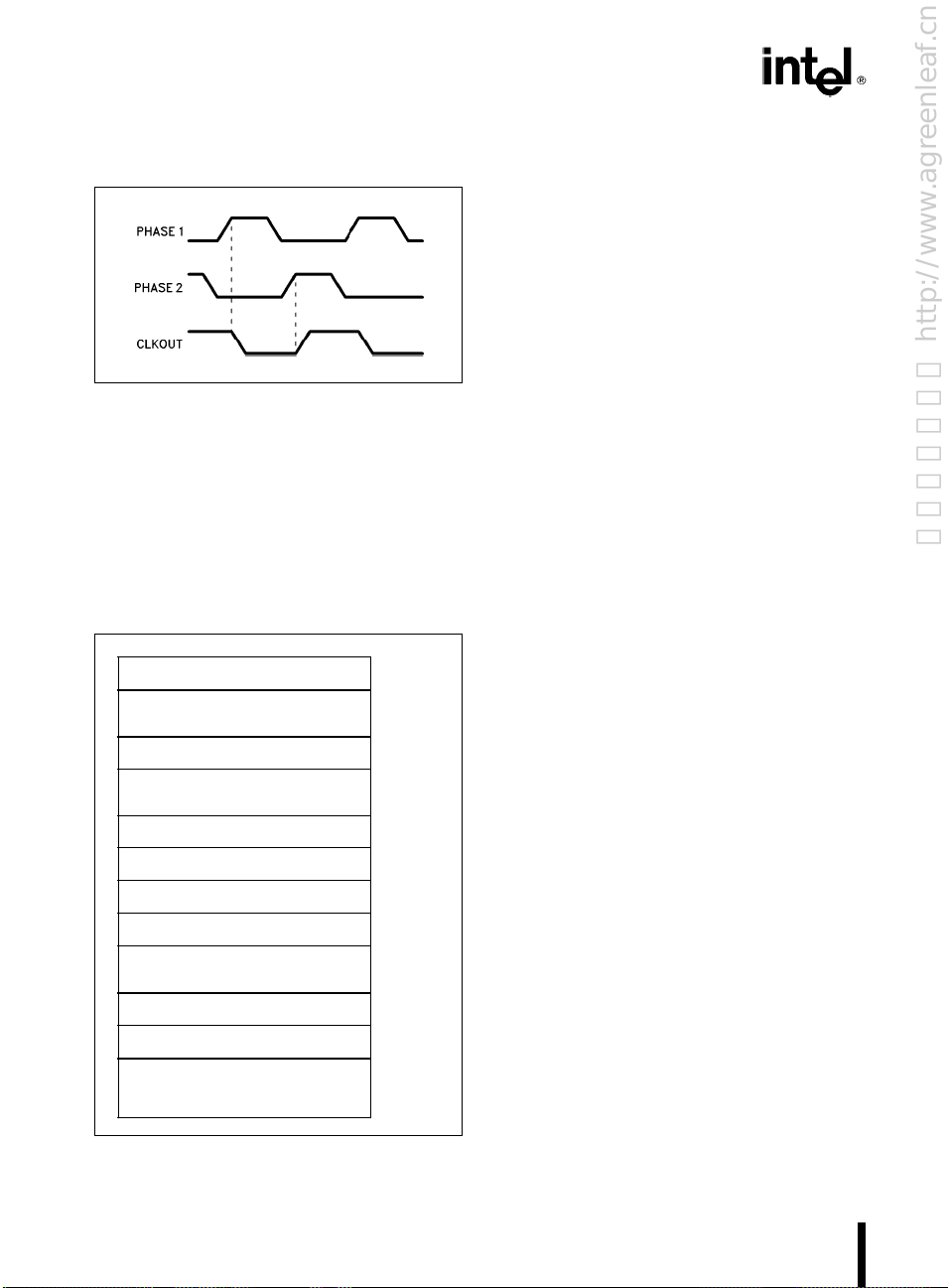

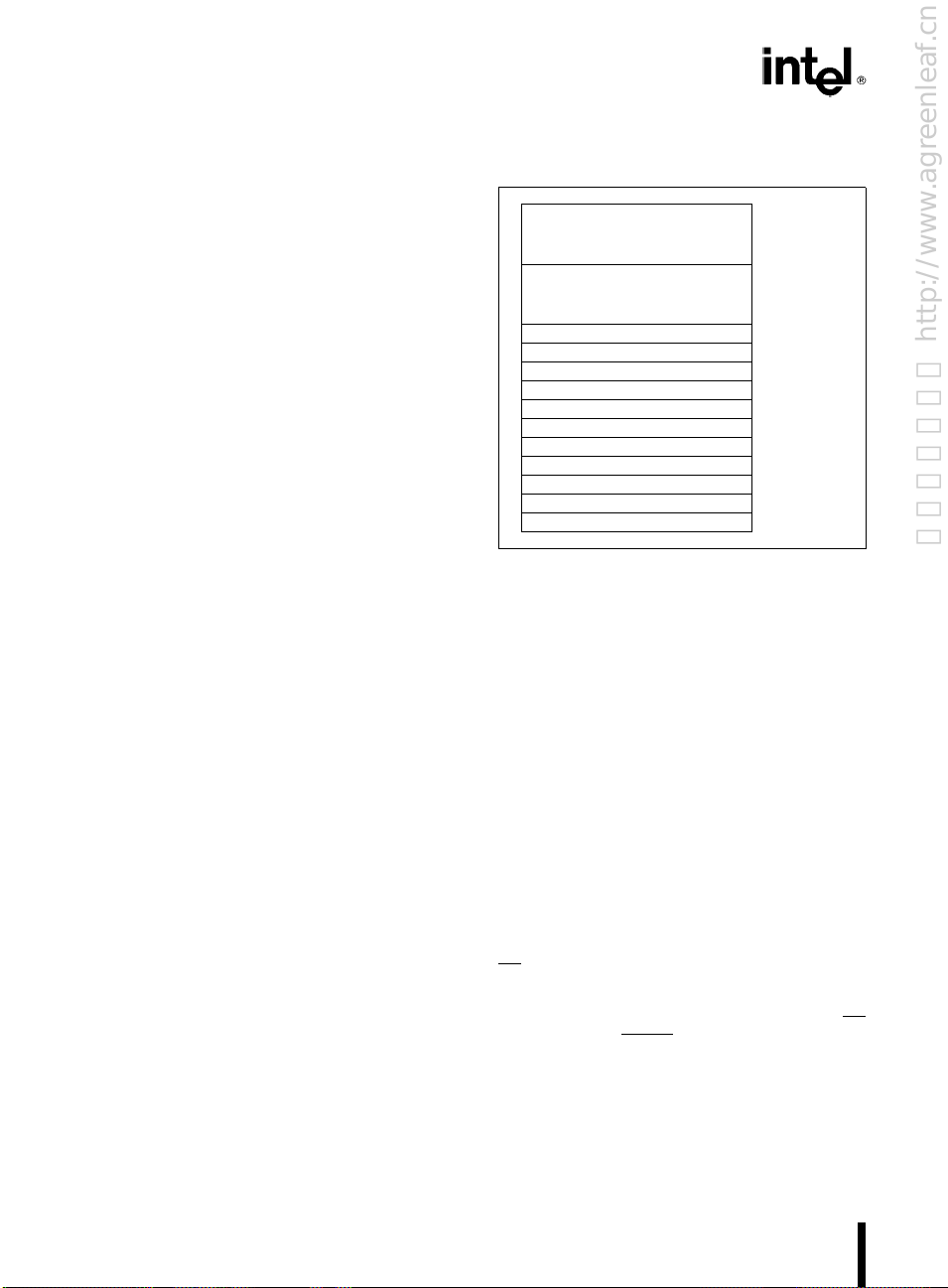

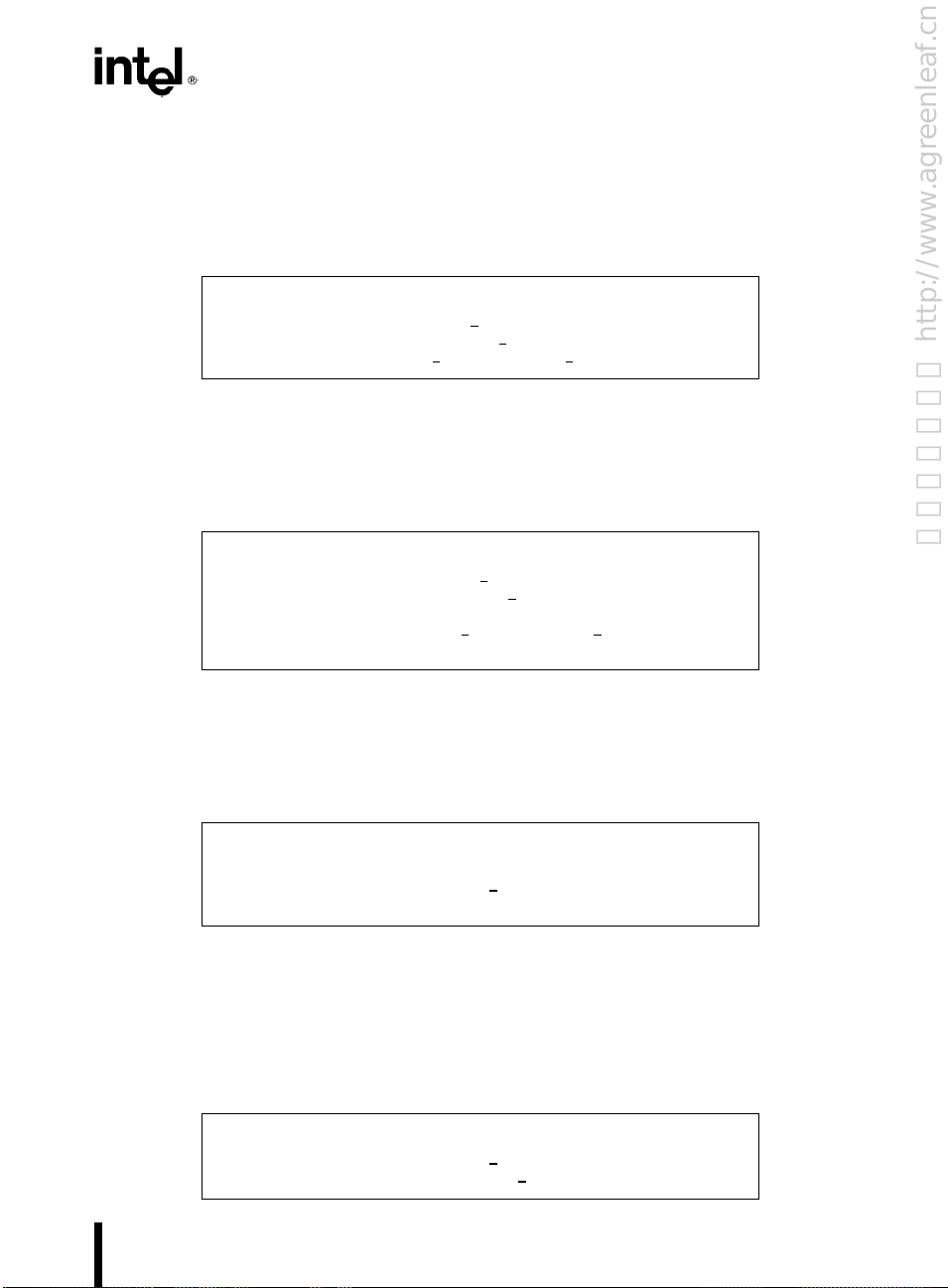

2.0 MEMORY SPACE

The addressable memory space on the 80C196KB consists of 64K bytes, most of which is available to the user

for program or data memory. Locations which have

special purposes are 0000H through 00FFH and

1FFEH through 2080H. All other locations can be

used for either program or data storage or for memory

mapped peripherals. A memory map is shown in Figure

2-1.

EXTERNAL MEMORY OR I/O

INTERNAL ROM/EPROM OR

EXTERNAL MEMORY*

RESERVED

UPPER 8 INTERRUPT VECTORS

(NEW ON 80C196KB)

ROM/EPROM SECURITY KEY

RESERVED

CHIP CONFIGURATION BYTE

RESERVED

LOWER 8 INTERRUPT VECTORS

PLUS 2 SPECIAL INTERRUPTS

PORT 3 AND PORT 4

EXTERNAL MEMORY OR I/O

INTERNAL DATA MEMORY - REGISTER FILE

(STACK POINTER, RAM AND SFRS)

EXTERNAL PROGRAM CODE MEMORY

0FFFFH

4000H

2080H

2040H

2030H

2020H

2019H

2018H

2014H

2000H

1FFEH

0100H

0000H

2.1 Register File

Locations 00H through 0FFH contain the Register File

and Special Function Registers, (SFRs). The RALU

can operate on any of these 256 internal register locations, but code can not be executed from them. If an

attempt to execute instructions from locations 000H

through 0FFH is made, the instructions will be fetched

from external memory. This section of external memory is reserved for use by Intel development tools

The internal RAM from location 018H (24 decimal) to

0FFH is the Register File. It contains 232 bytes of

RAM which can be accessed as bytes (8 bits), words

(16 bits), or double-words (32 bits). Since each of these

locations can be used by the RALU, there are essentially 232 ‘‘accumulators’’. This memory region, as well as

the status of the majority of the chip, is kept intact

while the chip is in the Powerdown Mode. Details on

Powerdown Mode are discussed in Section 14.

Locations 18H and 19H contain the stack pointer.

These are not SFRs and may be used as standard RAM

if stack operations are not being performed. Since the

stack pointer is in this area, the RALU can easily operate on it. The stack pointer must be initialized by the

user program and can point anywhere in the 64K memory space. Operations to the stack cause it to build

down, so the stack pointer should be initialized to 2

bytes above the highest stack location, and must be

word aligned.

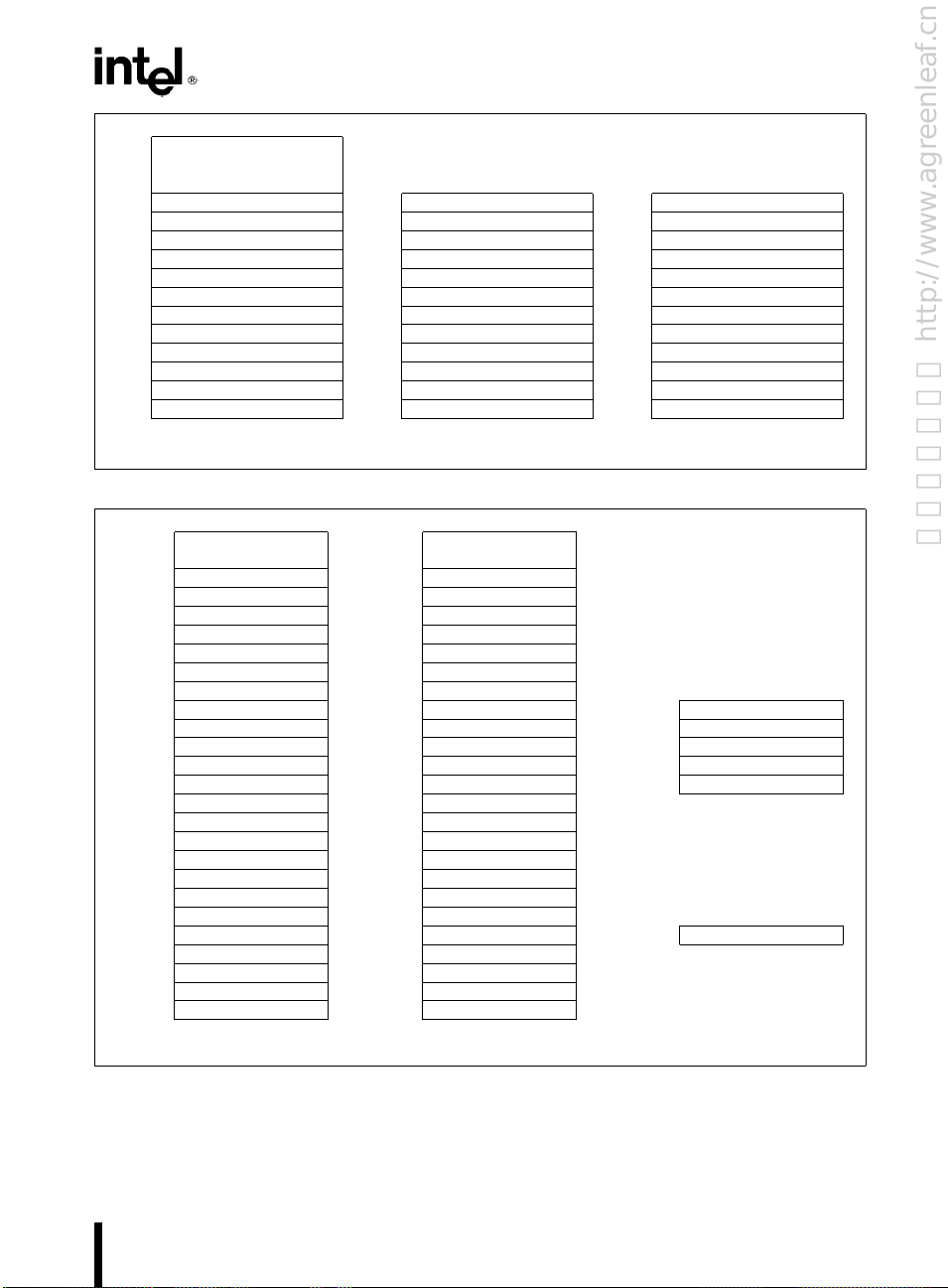

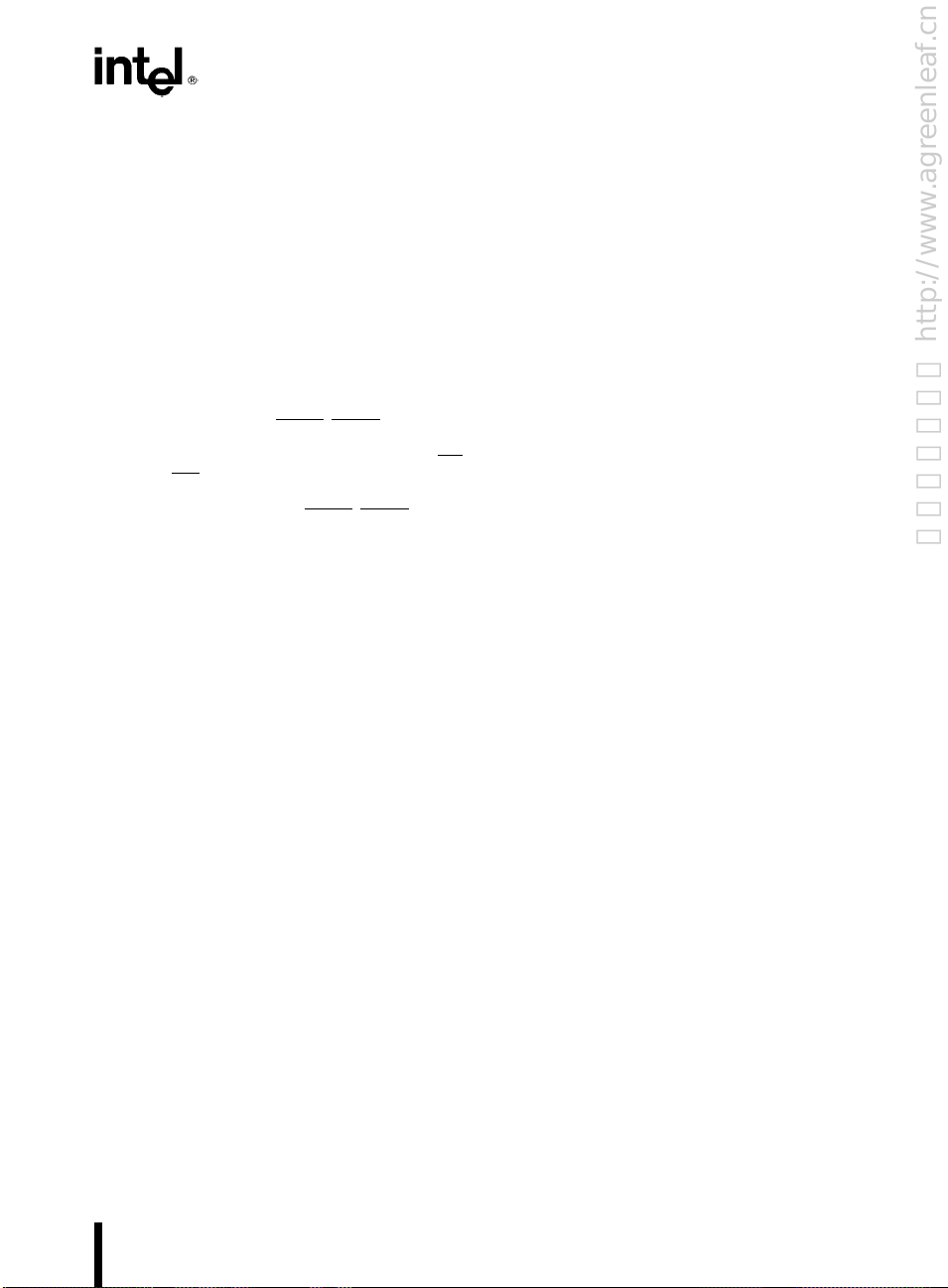

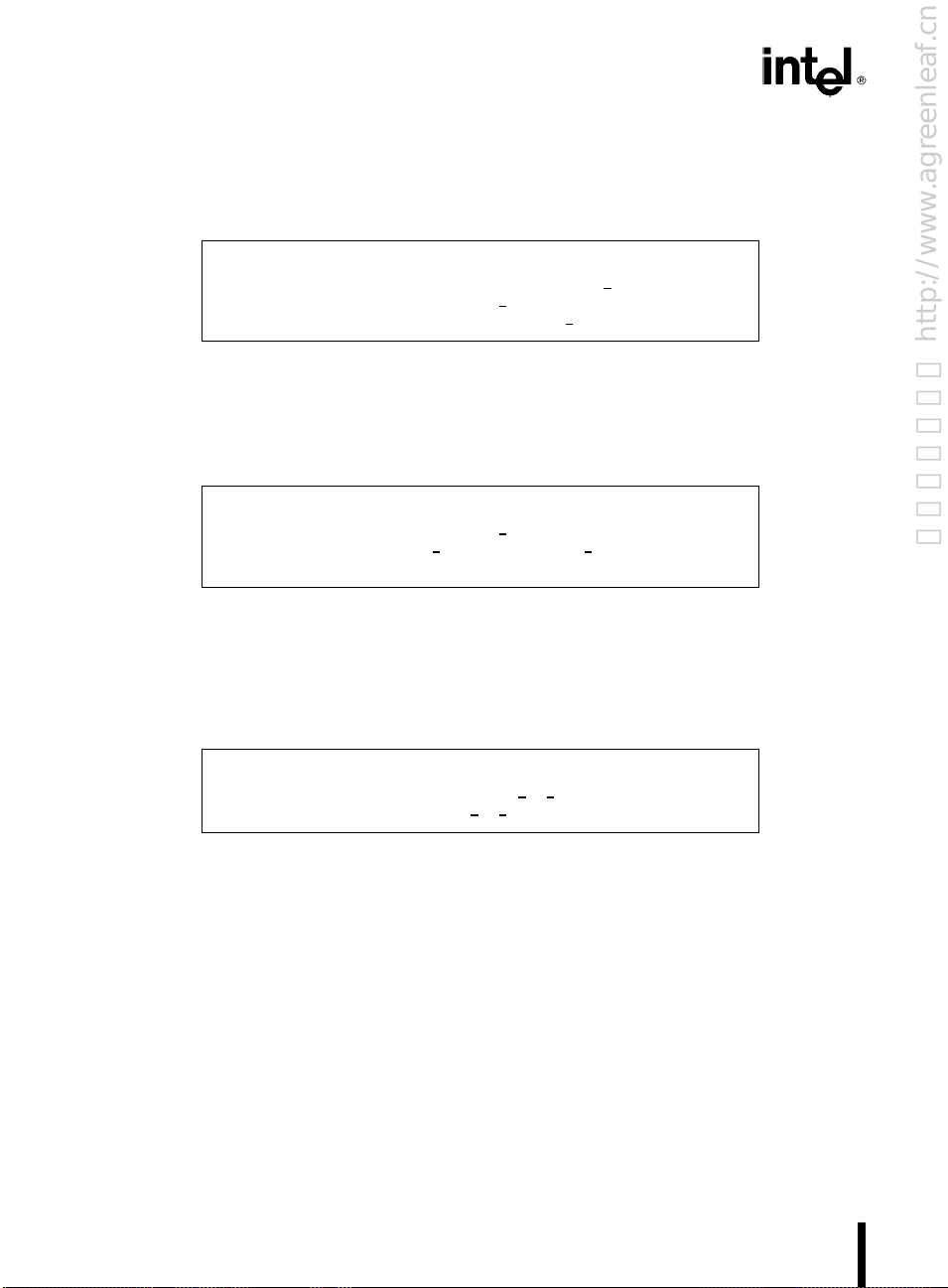

2.2 Special Function Registers

Locations 00H through 17H are the I/O control registers or SFRs. All of the peripheral devices on the

80C196KB (except Ports 3 and 4) are controlled

through these registers. As shown in Figure 2-2, three

SFR windows are provided on the 80C196KB.

Switching between the windows is done using the Window Select Register (WSR) at location 14H in all of the

windows. The PUSHA and POPA instructions push

and pop the WSR so it is easy to change between windows. Only three values may be written to the WSR, 0,

14 and 15. Other values are reserved for use in future

parts and will cause unpredictable operation.

Window 0, the register window selected with WSR

is a superset of the one used on the 8096BH. As depicted in Figure 2-3, it has 24 registers, some of which have

different functions when read than when written. Registers which are new to the 80C196KB or have changed

functions from the 8096 are indicated in the figure.

e

0,

Figure 2-1. 80C196KB Memory Map

4

Page 9

Listed registers

数控原理与维修 http://www.agreenleaf.cn

are present in

all three windows

16H 16H 16H

14H

12H

10H 10H 10H

0EH 0EH 0EH

0CH

0AH 0AH 0AH

08H

06H 06H 06H

04H 04H 04H

02H 02H 02H

00H

WSR

INT MASK1/PEND1

TIMER2

INT MASK/PEND

ZERO REG

READ/WRITE PROGRAMMING WRITE/READ

e

0 WSRe14 WSRe15

WSR

14H

12H

0CH

08H

00H

WSR

INT MASK1/PEND1

T2 CAPTURE

INT MASK/PEND

ZERO REG

14H

12H

0CH

08H

00H

Figure 2-2. Multiple Register Windows

80C196KB USER’S GUIDE

WSR

INT MASK1/PEND1

T2 CAPTURE

INT MASK/PEND

ZERO REG

19H

18H 18H

17H *IOS2 17H PWMÐCONTROL

16H IOS1 16H IOC1

15H IOS0 15H IOC0

14H *WSR 14H *WSR

13H *INTÐMASK 1 13H *INTÐMASK 1

12H *INTÐPEND 1 12H *INTÐPEND 1

11H *SPÐSTAT 11H *SPÐCON

10H PORT2 10H PORT2 10H RESERVED**

0FH PORT1 0FH PORT1 0FH RESERVED**

0EH PORT0 0EH BAUD RATE 0EH RESERVED**

0DH TIMER2 (HI) 0DH TIMER2 (HI) 0DH *T2 CAPTURE (HI)

0CH TIMER2 (LO) 0CH TIMER2 (LO) 0CH *T2 CAPTURE (LO)

0BH TIMER1 (HI) 0BH *IOC2

0AH TIMER1 (LO) 0AH WATCHDOG

09H INTÐPEND 09H INTÐPEND OTHER SFRS IN WSR 15 BECOME

08H INTÐMASK 08H INTÐMASK

07H SBUF(RX) 07H SBUF(TX)

06H HSIÐSTATUS 06H HSOÐCOMMAND

05H HSIÐTIME (HI) 05H HSOÐTIME (HI)

04H HSIÐTIME (LO) 04H HSOÐTIME (LO) 04H PPW

03H ADÐRESULT (HI) 03H HSIÐMODE WSRe14

02H ADÐRESULT (LO) 02H ADÐCOMMAND

01H ZERO REG (HI) 01H ZERO REG (HI) *NEW OR CHANGED REGISTER

00H ZERO REG (LO) 00H ZERO REG (LO)

STACK POINTER

WHEN READ WHEN WRITTEN

19H

e

0 BE WRITTEN OR READ

WSR

STACK POINTER

READABLE IF THEY WERE WRITABLE

IN WSR

WERE READABLE IN WSR

FUNCTION FROM 8096BH

**RESERVED REGISTERS SHOULD NOT

WSR

e

0, AND WRITABLE IF THEY

e

e

15

0

Figure 2-3. Special Function Registers

5

Page 10

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

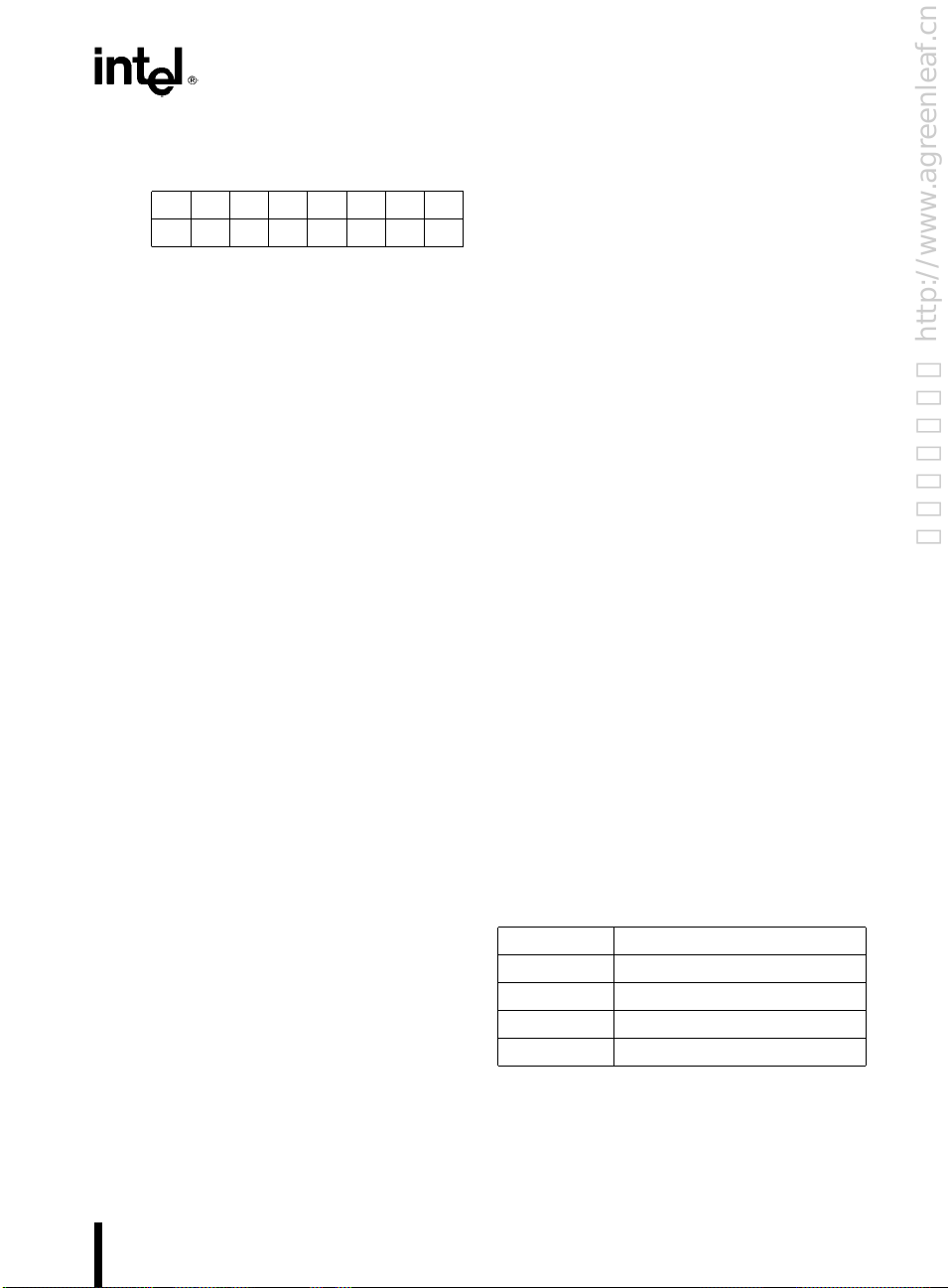

Register Description

R0 Zero Register - Always reads as a zero, useful for a base when indexing and as a

ADÐRESULT A/D Result Hi/Low - Low and high order results of the A/D converter

ADÐCOMMAND A/D Command Register - Controls the A/D

HSIÐMODE HSI Mode Register - Sets the mode of the High Speed Input unit.

HSIÐTIME HSI Time Hi/Lo - Contains the time at which the High Speed Input unit was triggered.

HSOÐTIME HSO Time Hi/Lo - Sets the time or count for the High Speed Output to execute the

HSOÐCOMMAND HSO Command Register - Determines what will happen at the time loaded into the

HSIÐSTATUS HSI Status Registers - Indicates which HSI pins were detected at the time in the HSI

SBUF(TX) Transmit buffer for the serial port, holds contents to be outputted. Last written value

SBUF(RX) Receive buffer for the serial port, holds the byte just received by the serial port.

INTÐMASK Interrupt Mask Register - Enables or disables the individual interrupts.

INTÐPEND Interrupt Pending Register - Indicates that an interrupt signal has occurred on one of

WATCHDOG Watchdog Timer Register - Written periodically to hold off automatic reset every 64K

TIMER1 Timer 1 Hi/Lo - Timer1 high and low bytes.

TIMER2 Timer 2 Hi/Lo - Timer2 high and low bytes.

IOPORT0 Port 0 Register - Levels on pins of Port 0. Reserved in Window 15.

BAUDÐRATE Register which determines the baud rate, this register is loaded sequentially.

IOPORT1 Port 1 Register - Used to read or write to Port 1. Reserved in Window 15

IOPORT2 Port 2 Register - Used to read or write to Port 2. Reserved in Window 15

SPÐSTAT Serial Port Status - Indicates the status of the serial port.

SPÐCON Serial Port Control - Used to set the mode of the serial port.

IOS0 I/O Status Register 0 - Contains information on the HSO status. Writes to HSO pins

IOS1 I/O Status Register 1 - Contains information on the status of the timers and of the

IOC0 I/O Control Register 0 - Controls alternate functions of HSI pins, Timer 2 reset

IOC1 I/O Control Register 1 - Controls alternate functions of Port 2 pins, timer interrupts

PWMÐCONTROL Pulse Width Modulation Control Register - Sets the duration of the PWM pulse.

INTÐPEND1 Interrupt Pending register for the 8 new interrupt vectors (also INTÐPENDING1)

INTÐMASK1 Interrupt Mask register for the 8 new interrupt vectors

IOC2 I/O Control Register 2 - Controls new 80C196KB features

IOS2 I/O Status Register 2 - Contains information on HSO events

WSR Window Select Register - Selects register window

constant for calculations and compares.

command in the Command Register.

HSO Time registers.

Time registers and the current state of the pins. In Window 15 - Writes to pin

detected bits, but not current state bits.

is readable in Window 15.

Writable in Window 15.

the sources and has not been serviced. (also INTÐPENDING)

state times. Returns upper byte of WDT counter in Window 15.

Reserved in Window 15.

in Window 15.

HSI.

sources and Timer 2 clock sources.

and HSI interrupts.

Figure 2-4. Special Function Register Description

6

Page 11

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

Programming control and test operations are done in

Window 14. Registers in this window that are not labeled should be considered reserved and should not be

either read or written.

In register Window 15 (WSR

the SFRs is changed, so that those which were readonly in Window 0 space are write-only and vice versa.

The only major exception to this is that Timer2 is read/

write in Window 0, and T2 Capture is read/write

ADÐCOMMAND (02H) Ð Read the last written command

ADÐRESULT (02H, 03H) Ð Write a value into the result register

HSIÐMODE (03H) Ð Read the value in HSIÐMODE

HSIÐTIME (04H, 05H) Ð Write to FIFO Holding register

HSOÐTIME (04H, 05H) Ð Read the last value placed in the holding register

HSIÐSTATUS (06H) Ð Write to status bits but not to HSI pin bits. (Pin bits are 1, 3, 5, 7)

HSOÐCOMMAND (06H) Ð Read the last value placed in the holding register

SBUF(RX) (07H) Ð Write a value into the receive buffer

SBUF(TX) (07H) Ð Read the last value written to the transmit buffer

WATCHDOG (0AH) Ð Read the value in the upper byte of the WDT

TIMER1 (0AH, 0BH) Ð Write a value to Timer1

TIMER2 (0CH, 0DH) Ð Read/Write the Timer2 capture register.

IOC2 (0BH) Ð Last written value is readable, except bit 7 (Note 1)

BAUDÐRATE (0EH) Ð No function, cannot be read

PORT0 (0EH) Ð No function, no output drivers on the pins

SPÐSTAT (11H) Ð Set the status bits, TI and RI can be set, but it will not cause an interrupt

SPÐCON (11H) Ð Read the current control byte

IOS0 (15H) Ð Writing to this register controls the HSO pins. Bits 6 and 7 are inactive for

IOC0 (15H) Ð Last written value is readable, except bit 1 (Note 1)

IOS1 (16H) Ð Writing to this register will set the status bits, but not cause interrupts. Bits

IOC1 (16H) Ð Last written value is readable

IOS2 (17H) Ð Writing to this register will set the status bits, but not cause interrupts.

PWMÐCONTROL (17H) Ð Read the duty cycle value written to PWMÐCONTROL

NOTE:

1. IOC2.7 (CAM CLEAR) and IOC0.1 (T2RST) are not latched and will read as a 1 (precharged bus).

Being able to write to the read-only registers and vice-versa provides a lot of flexibility. One of the most useful

advantages is the ability to set the timers and HSO lines for initial conditions other than zero.

e

15), the operation of

(Timer2 read/write is done with WSR

writes.

6 and 7 are not functional.

in Window 15. (Timer2 was read-only on the 8096.)

Registers which can be read and written in Window 0

can also be read and written in Window 15.

Figure 2-4 contains brief descriptions of the SFR registers. Detailed descriptions are contained in the section

which discusses the peripheral controlled by the register. Figure 2-5 contains a description of the alternate

function in Window 15.

e

0)

Figure 2-5. Alternate SFR Function in Window 15

7

Page 12

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

Within the SFR space are several registers and bit locations labeled ‘‘RESERVED’’. These locations should

never be written or read. A reserved bit location should

always be written with 0 to maintain compatibility with

future parts. Values read from these locations may

change from part to part or over temperature and voltage. Registers and bits which are not labeled should be

treated as reserved registers and bits. Note that the default state of internal registers is 0, while that for external memory is 1. This is because SFR functions are

typically disabled with a zero, while external memory is

typically erased to all 1s.

Caution must be taken when using the SFRs as sources

of operations or as base or index registers for indirect or

indexed operations. It is possible to get undesired results, since external events can change SFRs and some

SFRs clear when read. The potential for an SFR to

change value must be taken into account when operating on these registers. This is particularly important

when high level languages are used as they may not

always make allowances for SFR-type registers. SFRs

can be operated on as bytes or words unless otherwise

specified.

2.3 Reserved Memory Spaces

Locations 1FFEH and 1FFFH are used for Ports 3 and

4 respectively, allowing easy reconstruction of these

ports if external memory is used. An example of reconstructing the I/O ports is given in Section 15. If ports 3

and 4 are not going to be reconstructed and internal

ROM/EPROM is not used, these locations can be

treated as any other external memory location.

Many reserved and special locations are in the memory

area between 2000H and 2080H. In this area the 18

interrupt vectors, chip configuration byte, and security

key are located. Figure 2-6 shows the locations and

functions of these registers. The interrupts, chip configuration, and security key registers are discussed in Sections 5, 16, and 17 respectively. With one exception, all

unspecified addresses in locations 2000H through

207FH, including those marked ‘‘Reserved’’ are reserved by Intel for use in testing or future products.

They must be filled with the Hex value FFH to insure

compatibility with future devices. Location 2019H

should contain 20H to prevent possible bus contention

during the CCB fetch cycle. NOTE: 1. This exception

applies only to systems with a 16-bit bus and external

program memory. 2. Previously designed systems

which do not experience bus contention don’t need to

change the contents of this location. Refer to Section

15.2 for more information about bus contention during

CCB fetch.

EXTERNAL MEMORY

OR I/O

INTERNAL PROGRAM

STORAGE ROM/EPROM

OR

EXTERNAL MEMORY 2080H

RESERVED 2074H– 207FH

VOLTAGE LEVELS 2072H –2073H

SIGNATURE WORD 2070H– 2071H

RESERVED 2040H– 206FH

INTERRUPT VECTORS 2030H –203FH

SECURITY KEY 2020H– 202FH

RESERVED 2019H– 201FH

CHIP CONFIGURATION BYTE 2018H

RESERVED 2015H– 2017H

PPW 2014H

INTERRUPT VECTORS 2000H– 2013H

FFFFH

4000H

Figure 2-6. Reserved Memory Spaces

Resetting the 80C196KB causes instructions to be

fetched starting from location 2080H. This location was

chosen to allow a system to have up to 8K of RAM

continuous with the register file. Further information

on reset can be found in Section 13.

2.4 Internal ROM and EPROM

When a ROM part is ordered, or an EPROM part is

programmed, the internal memory locations 2080H

through 3FFFH are user specified, as are the interrupt

vectors, Chip Configuration Register and Security Key

in locations 2000H through 207FH. Location 2014H

contains the PPW (Programming Pulse Width) register. The PPW is used solely to program 87C196KB

EPROM devices and is a reserved location on ROM

and ROMless devices.

Instruction and data fetches from the internal ROM or

EPROM occur only if the part has ROM or EPROM,

EA

is tied high, and the address is between 2000H and

3FFFH. At all other times data is accessed from either

the internal RAM space or external memory and instructions are fetched from external memory. The EA

pin is latched on RESET rising. Information on programming EPROMs can be found in Section 16.

8

Page 13

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

The 80C196KB provides a ROM/EPROM lock feature

to allow the program to be locked against reading

and/or writing the internal program memory. In order

to maintain security, code can not be executed out of

the last three locations of internal ROM/EPROM if

the lock is enabled. Details on this feature are in Section 17.

2.5 System Bus

There are several modes of system bus operation on the

80C196KB. The standard bus mode uses a 16-bit multiplexed address/data bus. Other bus modes include an

8-bit mode and a mode in which the bus size can dynamically be switched between 8-bits and 16-bits.

Hold/Hold Acknowledge (HOLD

signals are available to create a variety of memory systems. The READY line extends the width of the RD

(read) and WR (write) pulses to allow access of slow

memories. Multiple processor systems with shared

memory can be designed using HOLD

the 80C196KB off the bus. Details on the System Bus

are in Section 15.

/HLDA) and Ready

/HLDA to keep

3.0 SOFTWARE OVERVIEW

This section provides information on writing programs

to execute in the 80C196KB. Additional information

can be found in the following documents:

MCSÉ-96 MACRO ASSEMBLER USER’S GUIDE

Order Number 122048 (Intel Systems)

Order Number 122351 (DOS Systems)

MCS

-96 UTILITIES USER’S GUIDE

É

Order Number 122049 (Intel Systems)

Order Number 122356 (DOS Systems)

PL/M-96 USER’S GUIDE

Order Number 122134 (Intel Systems)

Order Number 122361 (DOS Systems)

C-96 USER’S GUIDE

Order Number 167632 (DOS Systems)

Throughout this chapter short sections of code are used

to illustrate the operation of the device. For these sections it is assumed that the following set of temporary

registers has been declared:

AX, BX, CX, and DX are 16-bit registers.

AL is the low byte of AX, AH is the high byte.

BL is the low byte of BX

CL is the low byte of CX

DL is the low byte of DX

These are the same as the names for the general data

registers used in the 8086. It is important to note that in

the 80C196KB these are not dedicated registers but

merely the symbolic names assigned by the programmer to an eight byte region within the on-board register

file.

3.1 Operand Types

The MCS-96 architecture supports a variety of data

types likely to be useful in a control application. To

avoid confusion, the name of an operand type is capitalized. A ‘‘BYTE’’ is an unsigned eight bit variable; a

‘‘byte’’ is an eight bit unit of data of any type.

BYTES

BYTES are unsigned 8-bit variables which can take on

the values between 0 and 255. Arithmetic and relational

operators can be applied to BYTE operands but the

result must be interpreted in modulo 256 arithmetic.

Logical operations on BYTES are applied bitwise. Bits

within BYTES are labeled from 0 to 7, with 0 being the

least significant bit.

WORDS

WORDS are unsigned 16-bit variables which can take

on the values between 0 and 65535. Arithmetic and

relational operators can be applied to WORD operands

but the result must be interpreted modulo 65536. Logical operations on WORDS are applied bitwise. Bits

within words are labeled from 0 to 15 with 0 being the

least significant bit. WORDS must be aligned at even

byte boundaries in the MCS-96 address space. The least

significant byte of the WORD is in the even byte address and the most significant byte is in the next higher

(odd) address. The address of a word is the address of

its least significant byte. Word operations to odd addresses are not guaranteed to operate in a consistent

manner.

SHORT-INTEGERS

SHORT-INTEGERS are 8-bit signed variables which

can take on the values between

Arithmetic operations which generate results outside of

the range of a SHORT-INTEGER will set the overflow

indicators in the program status word. The actual numeric result returned will be the same as the equivalent

operation on BYTE variables.

b

128 anda127.

9

Page 14

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

INTEGERS

INTEGERS are 16-bit signed variables which can take

on the values between

metic operations which generate results outside of the

range of an INTEGER will set the overflow indicators

in the program status word. The actual numeric result

returned will be the same as the equivalent operation on

WORD variables. INTEGERS conform to the same

alignment and addressing rules as do WORDS.

BITS

BITS are single-bit operands which can take on the

Boolean values of true and false. In addition to the normal support for bits as components of BYTE and

WORD operands, the 80C196KB provides for the direct testing of any bit in the internal register file. The

MCS-96 architecture requires that bits be addressed as

components of BYTES or WORDS, it does not support

the direct addressing of bits that can occur in the MCS51 architecture.

DOUBLE-WORDS

DOUBLE-WORDS are unsigned 32-bit variables

which can take on the values between 0 and

4,294,967,295. The MCS-96 architecture provides direct support for this operand type for shifts, as the dividend in a 32-by-16 divide and the product of a 16-by-16

multiply, and for double-word comparisons. For these

operations a DOUBLE-WORD variable must reside in

the on-board register file of the 80C196KB and be

aligned at an address which is evenly divisible by 4. A

DOUBLE-WORD operand is addressed by the address

of its least significant byte. DOUBLE-WORD operations which are not directly supported can be easily

implemented with two WORD operations. For consistency with Intel provided software the user should adopt

the conventions for addressing DOUBLE-WORD operands which are discussed in Section 3.5.

LONG-INTEGERS

LONG-INTEGERS are 32-bit signed variables which

can take on the values between

a

2,147,483,647. The MCS-96 architecture provides direct support for this data type for shifts, as the dividend

in a 32-by-16 divide and the product of a 16-by-16 multiply, and for double-word comparisons.

b

32,768 anda32,767. Arith-

b

2,147,483,648 and

LONG-INTEGERS can also be normalized. For these

operations a LONG-INTEGER variable must reside in

the onboard register file of the 80C196KB and be

aligned at an address which is evenly divisible by 4. A

LONG-INTEGER is addressed by the address of its

least significant byte.

LONG-INTEGER operations which are not directly

supported can be easily implemented with two INTEGER operations. For consistency with Intel provided

software, the user should adopt the conventions for addressing LONG operands which are discussed in Section 3.6.

3.2 Operand Addressing

Operands are accessed within the address space of the

80C196KB with one of six basic addressing modes.

Some of the details of how these addressing modes

work are hidden by the assembly language. If the programmer is to take full advantage of the architecture, it

is important that these details be understood. This section will describe the addressing modes as they are handled by the hardware. At the end of this section the

addressing modes will be described as they are seen

through the assembly language. The six basic address

modes which will be described are termed register-direct, indirect, indirect with auto-increment, immediate,

short-indexed, and long-indexed. Several other useful

addressing operations can be achieved by combining

these basic addressing modes with specific registers

such as the ZERO register or the stack pointer.

REGISTER-DIRECT REFERENCES

The register-direct mode is used to directly access a

register from the 256 byte on-board register file. The

register is selected by an 8-bit field within the instruction and the register address must conform to the operand type’s alignment rules. Depending on the instruction, up to three registers can take part in the calculation.

Examples

ADD AX,BX,CX ; AX:4BX0CX

MUL AX,BX ; AX:4AX*BX

INCB CL ; CL:4CL01

10

Page 15

INDIRECT REFERENCES

数控原理与维修 http://www.agreenleaf.cn

in advance

The indirect mode is used to access an operand by placing its address in a WORD variable in the register file.

The calculated address must conform to the alignment

rules for the operand type. Note that the indirect address can refer to an operand anywhere within the address space of the 80C196KB, including the register

80C196KB USER’S GUIDE

file. The register which contains the indirect address is

selected by an eight bit field within the instruction. An

instruction can contain only one indirect reference and

the remaining operands of the instruction (if any) must

be register-direct references.

Examples

LD AX,[AX] ; AX:4MEM

ADDB AL,BL,[CX] ; AL:4BL0MEM

POP [AX] ; MEM

INDIRECT WITH AUTO-INCREMENT REFERENCES

This addressing mode is the same as the indirect mode

except that the WORD variable which contains the indirect address is incremented after it is used to address

the operand. If the instruction operates on BYTES or

Examples

LD AX,[BX]0 ; AX:4MEM

ADDB AL,BL,[CX]0 ; AL:4BL0MEM

PUSH [AX]0 ; SP:4SP12;

IMMEDIATE REFERENCES

This addressing mode allows an operand to be taken

directly from a field in the instruction. For operations

on BYTE or SHORT-INTEGER operands this field is

eight bits wide. For operations on WORD or

Examples

ADD AX,#340 ; AX:4AX0340

PUSH #1234H ; SP:4SP12; MEM

DIVB AX,#10 ; AL:4AX/10; AH:4AX MOD 10

WORD(AX):4MEM WORD(SP); SP:4SP02

; MEM

; AX:4AX02

WORD(AX)

BYTE(CX)

SHORT-INTEGERS the indirect address variable will

be incremented by one. If the instruction operates on

WORDS or INTEGERS the indirect address variable

will be incremented by two.

WORD(BX); BX:4BX02

BYTE(CX); CX:4CX01

WORD(SP):4MEM WORD(AX)

INTEGER operands the field is 16 bits wide. An instruction can contain only one immediate reference and

the remaining operand(s) must be register-direct references.

WORD(SP):41234H

SHORT-INDEXED REFERENCES

In this addressing mode an eight bit field in the instruction selects a WORD variable in the register file which

contains an address. A second eight bit field in the instruction stream is sign-extended and summed with the

WORD variable to form the address of the operand

which will take part in the calculation.

Examples

LD AX,12[BX] ; AX:4MEM

MULB AX,BL,3[CX] ; AX:4BL*MEM

Since the eight bit field is sign-extended, the effective

address can be up to 128 bytes before the address in the

WORD variable and up to 127 bytes after it. An instruction can contain only one short-indexed reference

and the remaining operand(s) must be register-direct

references.

WORD(BX012)

BYTE(CX03)

11

Page 16

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

LONG-INDEXED REFERENCES

This addressing mode is like the short-indexed mode

except that a 16-bit field is taken from the instruction

and added to the WORD variable to form the address

of the operand. No sign extension is necessary. An in-

struction can contain only one long-indexed reference

and the remaining operand(s) must be register-direct

references.

Examples

AND AX,BX,TABLE[CX] ; AX:4BX AND MEM

ST AX,TABLE[BX] ; MEM

ADDB AL,BL,LOOKUP[CX] ; AL:4BL0MEM

ZERO REGISTER ADDRESSING

The first two bytes in the register file are fixed at zero

by the 80C196KB hardware. In addition to providing a

fixed source of the constant zero for calculations and

comparisons, this register can be used as the WORD

Examples

ADD AX,1234[0] ; AX:4AX0MEM

POP 5678[0] ; MEM

STACK POINTER REGISTER ADDRESSING

The system stack pointer in the 80C196KB is accessed

as register 18H of the internal register file. In addition

to providing for convenient manipulation of the stack

pointer, this also facilitates the accessing of operands in

the stack. The top of the stack, for example, can be

Examples

PUSH [SP] ; DUPLICATE TOP

LD AX,2[SP] ; AX:4NEXT

WORD(5678):4MEM WORD(SP)

; SP:4SP02

WORD(TABLE0BX):4AX

WORD(TABLE0CX)

BYTE(LOOKUP0CX)

variable in a long-indexed reference. This combination

of register selection and address mode allows any location in memory to be addressed directly.

WORD(1234)

accessed by using the stack pointer as the WORD variable in an indirect reference. In a similar fashion, the

stack pointer can be used in the short-indexed mode to

access data within the stack.

OF STACK

TO TOP

ASSEMBLY LANGUAGE ADDRESSING MODES

The MCS-96 assembly language simplifies the choice of

addressing modes to be used in several respects:

Direct Addressing. The assembly language will choose

between register-direct addressing and long-indexed

with the ZERO register depending on where the operand is in memory. The user can simply refer to an operand by its symbolic name: if the operand is in the register file, a register-direct reference will be used, if the

operand is elsewhere in memory, a long-indexed reference will be generated.

Indexed Addressing. The assembly language will

choose between short and long indexing depending on

the value of the index expression. If the value can be

expressed in eight bits then short indexing will be used,

if it cannot be expressed in eight bits then long indexing

will be used.

12

These features of the assembly language simplify the

programming task and should be used wherever possible.

3.3 Program Status Word

The program status word (PSW) is a collection of Boolean flags which retain information concerning the state

of the user’s program. There are two bytes in the PSW;

the actual status word and the low byte of the interrupt

mask. Figure 3-1 shows the status bits of the PSW. The

PSW can be saved in the system stack with a single

operation (PUSHF) and restored in a like manner

(POPF). Only the interrupt section of the PSW can be

accessed directly. There is no SFR for the PSW status

bits.

Page 17

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

CONDITION FLAGS

The PSW bits on the 80C196KB are set as follows:

PSW:

76543210

ZNVVTCX IST

Figure 3-1. PSW Register

Z: The Z (Zero) flag is set to indicate that the opera-

tion generated a result equal to zero. For the addwith-carry (ADDC) and subtract-with-borrow

(SUBC) operations the Z flag is cleared if the result is non-zero but is never set. These two instructions are normally used in conjunction with

the ADD and SUB instructions to perform multiple precision arithmetic. The operation of the Z

flag for these instructions leaves it indicating the

proper result for the entire multiple precision calculation.

N: The Negative flag is set to indicate that the opera-

tion generated a negative result. Note that the N

flag will be in the algebraically correct state even

if an overflow occurs. For shift operations, including the normalize operation and all three forms

(SHL, SHR, SHRA) of byte, word and double

word shifts, the N flag will be set to the same

value as the most significant bit of the result. This

will be true even if the shift count is 0.

V: The oVerflow flag is set to indicate that the opera-

tion generated a result which is outside the range

for the destination data type. For the SHL, SHLB

and SHLL instructions, the V flag will be set if the

most significant bit of the operand changes at any

time during the shift. For divide operations, the

following conditions are used to determine if the V

flag is set:

For the

operation: V is set if Quotient is:

UNSIGNED

BYTE DIVIDE

UNSIGNED

WORD DIVIDE

SIGNED

BYTE or

DIVIDE

SIGNED

WORD or

DIVIDE

l

255(0FFH)

l

65535(0FFFFH)

k

b

127(81H)

l

127(7FH)

k

b

32767(8001H)

l

32767(7FFFH)

VT: The oVerflow Trap flag is set when the V flag is

set, but it is only cleared by the CLRVT, JVT and

JNVT instructions. The operation of the VT flag

allows for the testing for a possible overflow condition at the end of a sequence of related arithmetic operations. This is normally more efficient

than testing the V flag after each instruction.

C: The Carry flag is set to indicate the state of the

arithmetic carry from the most significant bit of

the ALU for an arithmetic operation, or the state

of the last bit shifted out of an operand for a shift.

Arithmetic Borrow after a subtract operation is

the complement of the C flag (i.e. if the operation

generated a borrow then C

e

0.)

X: Reserved. Should always be cleared when writing

to the PSW for compatibility with future products.

I: The global Interrupt disable bit disables all inter-

rupts when cleared except NMI, TRAP, and unimplemented opcode.

ST: The ST (STicky bit) flag is set to indicate that

during a right shift a 1 has been shifted first into

the C flag and then been shifted out. The ST flag

is undefined after a multiply operation. The ST

flag can be used along with the C flag to control

rounding after a right shift. Consider multiplying

two eight bit quantities and then scaling the result

down to 12 bits:

MULUB AX,CL,DL ;AX:4CL*DL

SHR AX,#4 ;Shift right 4

places

If the C flag is set after the shift, it indicates that the

bits shifted off the end of the operand were greater-than

or equal-to one half the least significant bit (LSB) of the

result. If the C flag is clear after the shift, it indicates

that the bits shifted off the end of the operand were less

than half the LSB of the result. Without the ST flag,

the rounding decision must be made on the basis of the

C flag alone. (Normally the result would be rounded up

if the C flag is set.) The ST flag allows a finer resolution

in the rounding decision:

C ST Value of the Bits Shifted Off

0 0 Valuee0

010

k

Valuek(/2 LSB

1 0 Valuee(/2 LSB

1 1 Valuel(/2 LSB

Figure 3-2. Rounding Alternatives

Imprecise rounding can be a major source of error in a

numerical calculation; use of the ST flag improves the

options available to the programmer.

13

Page 18

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

INTERRUPT FLAGS

The lower eight bits of the PSW individually mask the

lowest 8 sources of interrupt to the 80C196KB. These

mask bits can be accessed as an eight bit byte (INT

MASKÐaddress 8) in the on-board register file. A separate register (INTÐMASK1Ðaddress 13H) contains

the control bits for the higher 8 interrupts. A logical ‘1’

in these bit positions enables the servicing of the corresponding interrupt. Bit 9 in the PSW is the global interrupt disable. If this bit is cleared then interrupts will be

locked out. Note that the interrupts are collected in the

INTÐPEND registers even if they are locked out. Execution of the corresponding service routines will proceed according to their priority when they become enabled. Further information on the interrupt structure of

the 80C196KB can be found in Section 5.

3.4 Instruction Set

The MCS-96 instruction set contains a full set of arithmetic and logical operations for the 8-bit data types

BYTE and SHORT INTEGER and for the 16-bit data

types WORD and INTEGER. The DOUBLE-WORD

and LONG data types (32 bits) are supported for the

products of 16-by-16 multiplies and the dividends of

32-by-16 divides, for shift operations, and for 32-bit

compares. The remaining operations on 32-bit variables

can be implemented by combinations of 16-bit operations. As an example the sequence:

ADD AX,CX

ADDC BX,DX

performs a 32-bit addition, and the sequence

SUB AX,CX

SUBC BX,DX

performs a 32-bit subtraction. Operations on REAL

(i.e. floating point) variables are not supported directly

by the hardware but are supported by the floating point

library for the 80C196KB (FPAL-96) which implements a single precision subset of draft 10 of the IEEE

standard for floating point arithmetic. The performance

of this software is significantly improved by the

80C196KB NORML instruction which normalizes a

32-bit variable and by the existence of the ST flag in the

PSW.

In addition to the operations on the various data types,

the 80C196KB supports conversions between these

types. LDBZE (load byte zero extended) converts a

BYTE to a WORD and LDBSE (load byte sign extended) converts a SHORT-INTEGER into an INTEGER.

WORDS can be converted to DOUBLE-WORDS by

simply clearing the upper WORD of the DOUBLEWORD (CLR) and INTEGERS can be converted to

LONGS with the EXT (sign extend) instruction.

Ð

The MCS-96 instructions for addition, subtraction, and

comparison do not distinguish between unsigned words

and signed integers. Conditional jumps are provided to

allow the user to treat the results of these operations as

either signed or unsigned quantities. As an example, the

CMPB (compare byte) instruction is used to compare

both signed and unsigned eight bit quantities. A JH

(jump if higher) could be used following the compare if

unsigned operands were involved or a JGT (jump if

greater-than) if signed operands were involved.

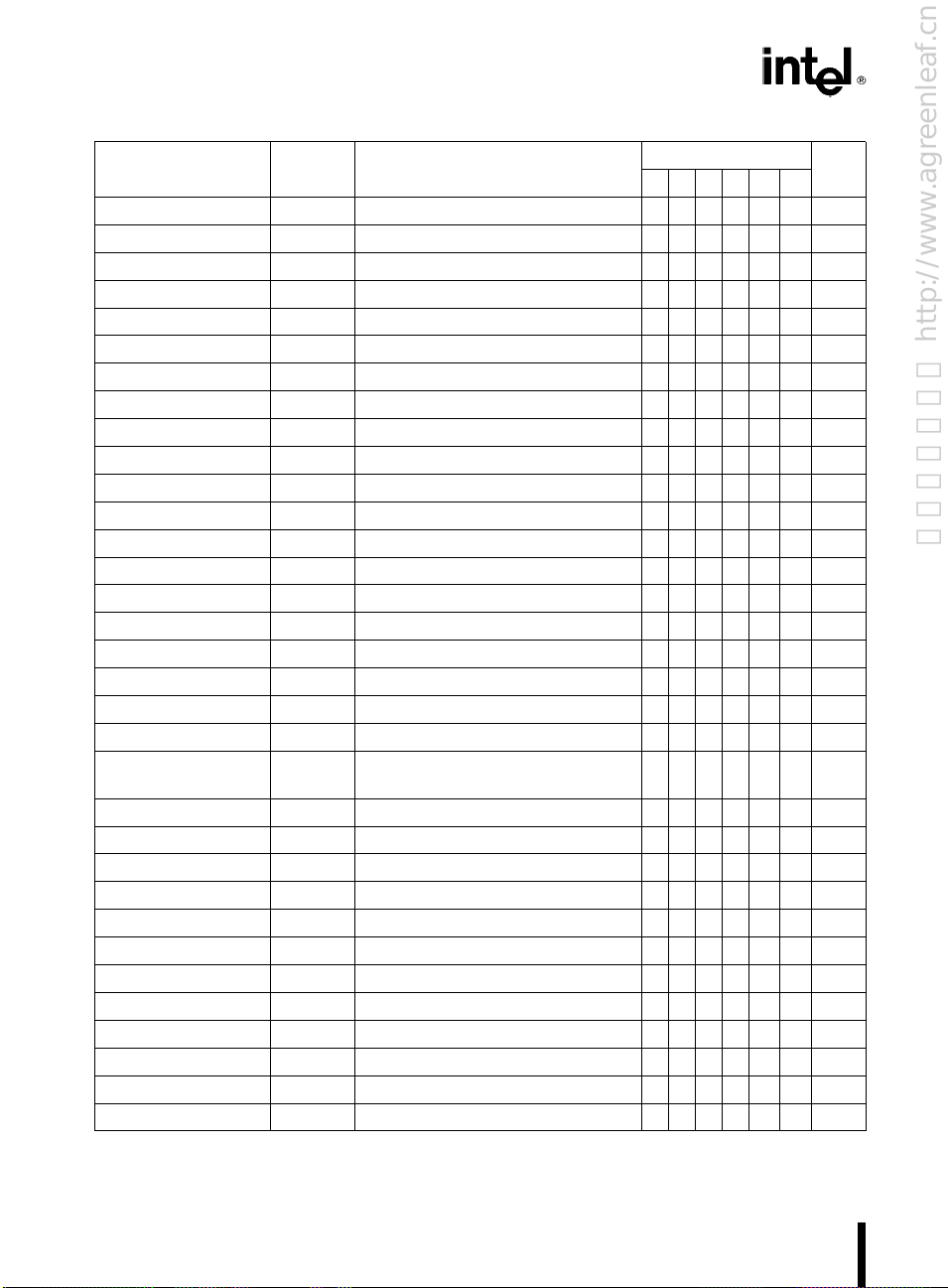

Tables 3-1 and 3-2 summarize the operation of each of

the instructions. Complete descriptions of each instruction and its timings can be found in the MCS-96 family

Instruction Set chapter.

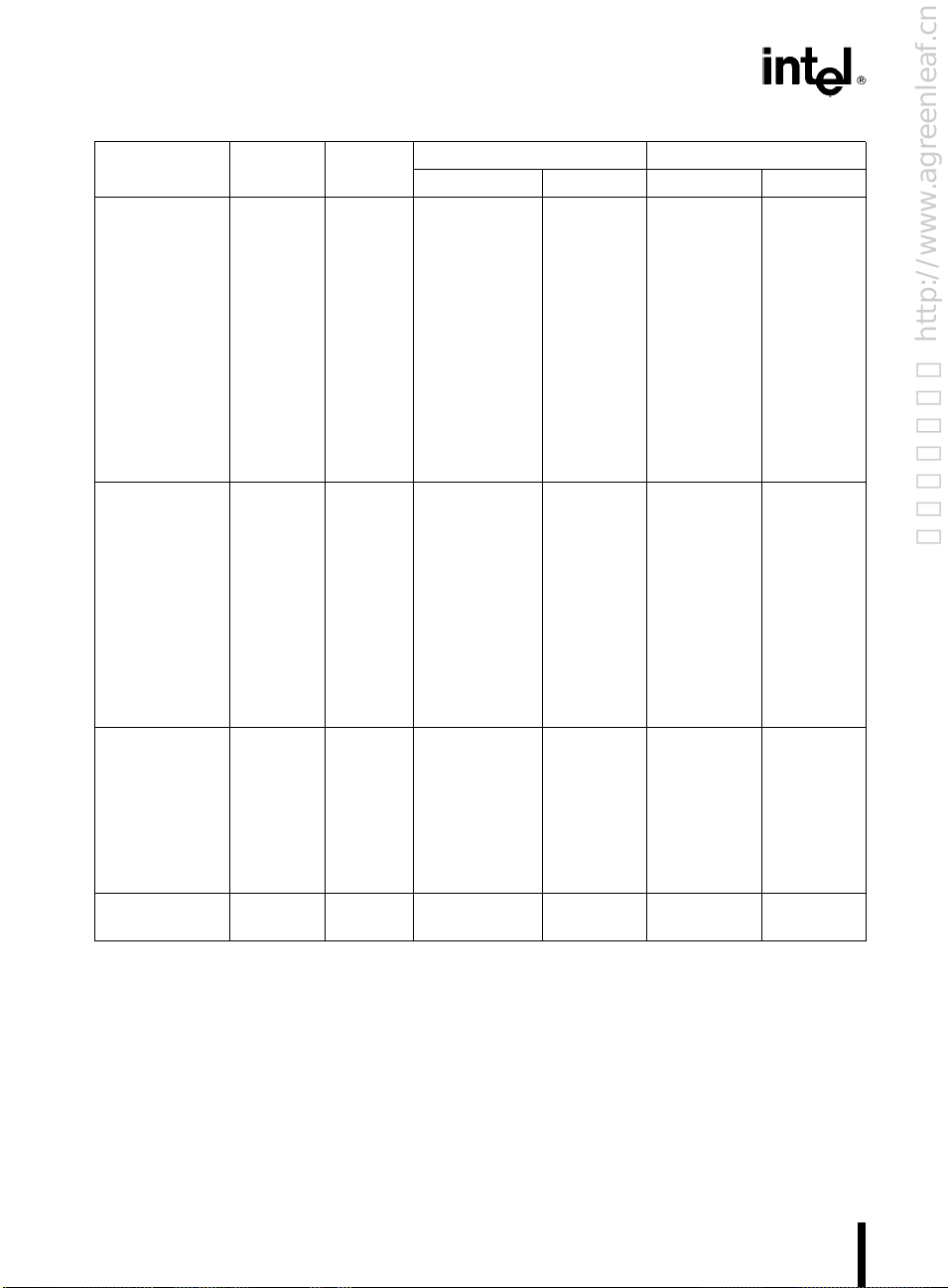

The execution times for the instruction set are given in

Figure 3-3. These times are given for a 16-bit bus with

no wait states. On-chip EPROM/ROM space is a 16bit, zero wait state bus. When executing from an 8-bit

external memory system or adding wait states, the CPU

becomes bus limited and must sometimes wait for the

prefetch queue. The performance penalty for an 8-bit

external bus is difficult to measure, but has shown to be

between 10 and 30 percent based on the instruction

mix. The best way to measure code performance is to

actually benchmark the code and time it using an emulator or with TIMER1.

The indirect and indexed instruction timings are given

for two memory spaces: SFR/Internal RAM space (0–

0FFH), and a memory controller reference (100H–

0FFFFH). Any instruction that uses an operand that is

referenced through the memory controller (ex. Add

r1,5000H[0]) takes 2– 3 states longer than if the operand was in the SFR/Internal RAM space. Any data

access to on-chip ROM/EPROM is considered to be a

memory controller reference.

Flag Settings. The modification to the flag setting is

shown for each instruction. A checkmark (

that the flag is set or cleared as appropriate. A hyphen

means that the flag is not modified. A one or zero (1) or

(0) indicates that the flag will be in that state after the

instruction. An up arrow (

struction may set the flag if it is appropriate but will

not clear the flag. A down arrow (

flag can be cleared but not set by the instruction. A

question mark (?) indicates that the flag will be left in

an indeterminant state after the operation.

) indicates that the in-

u

) indicates that the

v

&

) means

14

Page 19

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

Table 3-1A. Instruction Summary

Mnemonic Operands Operation (Note 1)

ADD/ADDB 2 DwDaA

ADD/ADDB 3 DwBaA

ADDC/ADDCB 2 DwDaAaC

SUB/SUBB 2 DwDbA

SUB/SUBB 3 DwBbA

SUBC/SUBCB 2 DwDbAaCb1

CMP/CMPB 2 DbA

MUL/MULU 2 D,Da2

MUL/MULU 3 D,Da2

MULB/MULUB 2 D,Da1

MULB/MULUB 3 D,Da1

DIVU 2 Dw(D,Da2) /A,Da2wremainder

DIVUB 2 Dw(D,Da1) /A,Da1wremainder

DIV 2 Dw(D,Da2) /A,Da2wremainder

DIVB 2 Dw(D,Da1) /A,Da1wremainder

AND/ANDB 2 DwD AND A

AND/ANDB 3 DwB AND A

OR/ORB 2 DwDORA

XOR/XORB 2 DwD (ecxl. or) A

LD/LDB 2 DwA

ST/STB 2 AwD

LDBSE 2 DwA; Da1wSIGN(A)

LDBZE 2 DwA; Da1w0

PUSH 1 SPwSPb2; (SP)wA

POP 1 Aw(SP); SPa2

PUSHF 0 SPwSPb2; (SP)wPSW; 0 0 0 0 0 0

POPF 0 PSWw(SP); SPwSPa2; I

SJMP 1 PCwPCa11-bit offset

LJMP 1 PCwPCa16-bit offset

BR[indirect

SCALL 1 SPwSPb2;

LCALL 1 SPwSPb2; (SP)wPC;

]

PSW

1PC

(SP)

PCwPCa16-bit offset

w

DcA

w

BcA

w

DcA

w

BcA

w

0000H; Iw0

w

(A)

w

PC; PC

w

PCa11-bit offset

w

Z N C V VT ST

&&&&

&&&&

v

&&&&

&&&&

v

&&&&

bbbbb b

bbbbb b

bbbbb b

bbbbb b

bbb

bbb

bbb

bbb

&&

&&

&&

&&

bbbbb b

bbbbb b

bbbbb b

bbbbb b

bbbbb b

bbbbb b

& &&&& & &

bbbbb b

bbbbb b

bbbbb b

bbbbb b

bbbbb b

Flags

&&&

&&&

&

&

&

&

00

00

00

00

u

u

u

u

u

u

u

u

u

u

u

bb

bb

bb

bb

b

b

b

b

b

b

b

b

b

b

b

Notes

2

2

3

3

2

3

3,4

3,4

5

5

5

5

15

Page 20

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

Table 3-1B. Instruction Summary

Mnemonic Operands Operation (Note 1)

RET 0 PCw(SP); SP

J (conditional) 1 PCwPCa8-bit offset (if taken)

JC 1 Jump if Ce1

JNC 1 jump if Ce0

JE 1 jump if Ze1

JNE 1 Jump if Ze0

JGE 1 Jump if Ne0

JLT 1 Jump if Ne1

JGT 1 Jump if Ne0 and Ze0

JLE 1 Jump if Ne1orZe1

JH 1 Jump if Ce1 and Ze0

JNH 1 Jump if Ce0orZe1

JV 1 Jump if Ve1

JNV 1 Jump if Ve0

JVT 1 Jump if VTe1; Clear VT

JNVT 1 Jump if VTe0; Clear VT

JST 1 Jump if STe1

JNST 1 Jump if STe0

JBS 3 Jump if Specified Bite1

JBC 3 Jump if Specified Bite0

DJNZ/ 1 D

DJNZW If D

DEC/DECB 1 D

NEG/NEGB 1 D

INC/INCB 1 D

EXT 1 D

EXTB 1 D

NOT/NOTB 1 D

CLR/CLRB 1 D

SHL/SHLB/SHLL 2 Cwmsb-----lsbw0

SHR/SHRB/SHRL 2 0xmsb-----lsbxC

SHRA/SHRAB/SHRAL 2 msbxmsb-----lsbxC

SETC 0 Cw1

CLRC 0 Cw0

b bbbb b b

w

Db1;

i

0 then PCwPCa8-bit offset 10

w

Db1

w

0bD

w

Da1

w

D; Da2wSign (D)

w

D; Da1wSign (D)

w

Logical Not (D)

w

0 1000

w

SPa2

Flags

Z N C V VT ST

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb0b

bbbb0b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

bbbb b b

0

0

b

u

b

u

b

u

bb

bb

bb

bb

b

u

b

&

b

&

&&&&

&&&&

&&&&

&&

00

&&

00

&&

00

&&&&

&&&

&&&

bb1bb b

bb0bb b

Notes

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5,6

5,6

5

2

3

7

7

7

16

Page 21

Table 3-1C. Instruction Summary

数控原理与维修 http://www.agreenleaf.cn

Mnemonic Operands Operation (Note 1)

CLRVT 0 VTw0

RST 0 PC

DI 0 Disable All Interupts (Iw0)

EI 0 Enable All Interupts (Iw1)

NOP 0 PC

SKIP 0 PC

NORML 2 Left shift till msbe1; Dwshift count

TRAP 0 SPwSPb2;

PUSHA 1 SPwSP-2; (SP)

POPA 1 IMASK1/WSRw(SP); SPwSPa2

IDLPD 1 IDLE MODE IF KEYe1;

CMPL 2 D-A

BMOV 2

w

2080H 0 0 0 0 0 0 8

w

PCa1

w

PCa2

(SP)wPC; PCw(2010H)

w

PSW

w

0000H; SP

w

(SP)

PSWw(SP); SPwSPa2

POWERDOWN MODE IF KEYe2;

CHIP RESET OTHERWISE

[

PTRÐHI

UNTIL COUNTe0

IMASK1/WSR; IMASK1w00H

a

]

w

PSW; 0 0 0 0 0 0

w

SP-2;

[

PTRÐLOW

a

]

;

80C196KB USER’S GUIDE

Flags

Z N C V VT ST

bbbb

bbbb b b

bbbb b b

bbbb b b

bbbb b b

&&

bbbb b b

&&&& & &

bbbb b b

&&&&

bbbb b b

bb b

0

0

u

b

b

Notes

7

9

NOTES:

1. If the mnemonic ends in ‘‘B’’ a byte operation is performed, otherwise a word operation is done. Operands D, B, and A

must conform to the alignment rules for the required operand type. D and B are locations in the Register File; A can be

located anywhere in memory.

a

2. D,D

3. D,D

4. Changes a byte to word.

5. Offset is a 2’s complement number.

6. Specified bit is one of the 2048 bits in the register file.

7. The ‘‘L’’ (Long) suffix indicates double-word operation.

8. Initiates a Reset by pulling RESET

2080H.

9. The assembler will not accept this mnemonic.

10. The DJNZW instruction is not guaranteed to work. See Functional Deviations section.

2 are consecutive WORDS in memory; D is DOUBLE-WORD aligned.

a

1 are consecutive BYTES in memory; D is WORD aligned.

low. Software should re-initialize all the necessary registers with code starting at

17

Page 22

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

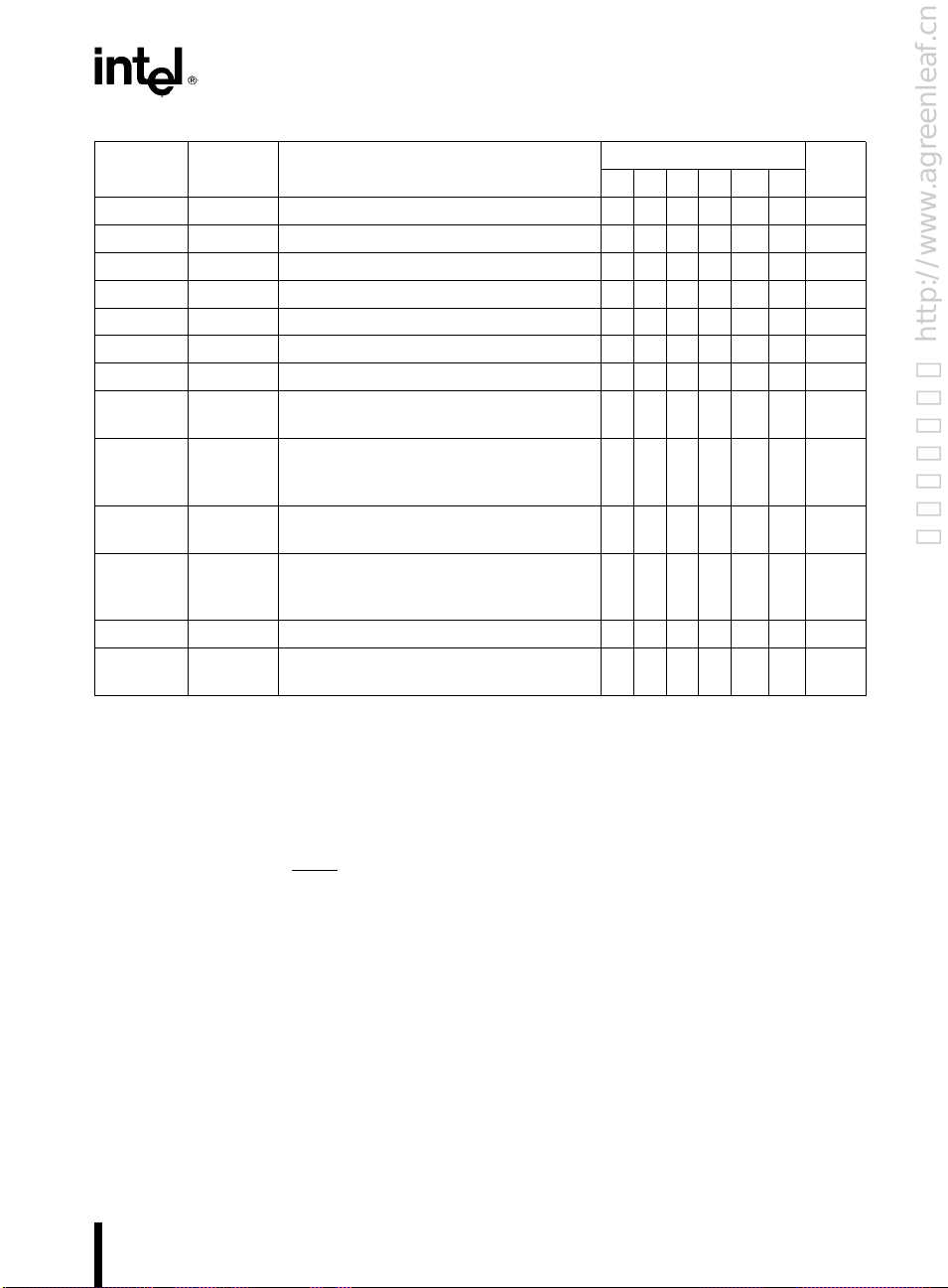

Table 3-2A. Instruction Length (in Bytes)/Opcode

MNEMONIC DIRECT IMMED

NORMAL*

ADD (3-op) 4/44 5/45 4/46 4/46 5/47 6/47

SUB (3-op) 4/48 5/49 4/4A 4/4A 5/4B 6/4B

ADD (2-op) 3/64 4/65 3/66 3/66 4/67 5/67

SUB (2-op) 3/68 4/69 3/6A 3/6A 4/6B 5/6B

ADDC 3/A4 4/A5 3/A6 3/A6 4/A7 5/A7

SUBC 3/A8 4/A9 3/AA 3/AA 4/AB 5/AB

CMP 3/88 4/89 3/AB 3/AB 4/8B 5/8B

ADDB (3-op) 4/54 4/55 4/56 4/56 5/57 6/57

SUBB (3-op) 4/58 4/59 4/5A 4/5A 5/5B 6/5B

ADDB (2-op) 3/74 3/75 3/76 3/76 4/77 5/77

SUBB (2-op) 3/78 3/79 3/7A 3/7A 4/7B 5/7B

ADDCB 3/B4 3/B5 3/B6 3/B6 4/B7 5/B7

SUBCB 3/B8 3/B9 3/BA 3/BA 4/BB 5/BB

CMPB 3/98 3/99 3/9A 3/9A 4/9B 5/9B

MUL (3-op) 5/

(2)

6/

(2)

MULU (3-op) 4/4C 5/4D 4/4E 4/4E 5/4F 6/4F

MUL (2-op) 4/

(2)

5/

(2)

MULU (2-op) 3/6C 4/6D 3/6E 3/6E 4/6F 5/6F

DIV 4/

(2)

5/

(2)

DIVU 3/8C 4/8D 3/8E 3/8E 4/8F 5/8F

MULB (3-op) 5/

(2)

5/

(2)

MULUB (3-op) 4/5C 4/5D 4/5E 4/5E 5/5F 6/5F

MULB (2-op) 4/

(2)

4/

(2)

MULUB (2-op) 3/7C 3/7D 3/7E 3/7E 4/7F 5/7F

DIVB 4/

(2)

4/

(2)

DIVUB 3/9C 3/9D 3/9E 3/9E 4/9F 5/9F

AND (3-op) 4/40 5/41 4/42 4/42 5/43 6/43

AND (2-op) 3/60 4/61 3/62 3/62 4/63 5/63

OR (2-op) 3/80 4/81 3/82 3/82 4/83 5/83

XOR 3/84 4/85 3/86 3/86 4/87 5/87

ANDB (3-op) 4/50 4/51 4/52 4/52 5/53 5/53

ANDB (2-op) 3/70 3/71 3/72 3/72 4/73 4/73

ORB (2-op) 3/90 3/91 3/92 3/92 4/93 5/93

XORB 3/94 3/95 3/96 3/96 4/97 5/97

PUSH 2/C8 3/C9 2/CA 2/CA 3/CB 4/CB

POP 2/CC Ð 2/CE 2/CE 3/CF 4/CF

INDIRECT INDEXED

5/

4/

4/

5/

4/

4/

(1)

(2)

(2)

(2)

(2)

(2)

(2)

A-INC*

(2)

5/

(2)

4/

(2)

4/

(2)

5/

(2)

4/

(2)

4/

(1)

SHORT*

(2)

6/

(2)

5/

(2)

5/

(2)

6/

(2)

5/

(2)

5/

(1)

LONG*

7/

6/

6/

7/

6/

6/

(1)

(2)

(2)

(2)

(2)

(2)

(2)

NOTES:

1. Indirect and indirect

indirect or short indexed. If odd, use indirect or long indexed.

2. The opcodes for signed multiply and divide are the unsigned opcode with an ‘‘FE’’ prefix.

a

share the same opcodes, as do short and long indexed opcodes. If the second byte is even, use

18

Page 23

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

Table 3-2B. Instruction Length (in Bytes)/Opcode

MNEMONIC DIRECT IMMED

LD 3/A0 4/A1 3/A2 3/A2 4/A3 5/A3

LDB 3/B0 3/B1 3/B2 3/B2 4/B3 5/B3

ST 3/C0 Ð 3/C2 3/C2 4/C3 5/C3

STB 3/C4 Ð 3/C6 3/C6 4/C7 5/C7

LDBSE 3/BC 3/BD 3/BE 3/BE 4/BF 5/BF

LBSZE 3/AC 3/AD 3/AE 3/AE 4/AF 5/AF

INDIRECT INDEXED

NORMAL A-INC SHORT LONG

Mnemonic Length/Opcode

PUSHF 1/F2

POPF 1/F3

PUSHA 1/F4

POPA 1/F5

TRAP 1/F7

LCALL 3/EF

SCALL 2/28– 2F

RET 1/F0

LJMP 3/E7

SJMP 2/20 –27

[]

BR

JNST 1/D0

JST 1/D8

JNH 1/D1

JH 1/D9

JGT 1/D2

JLE 1/DA

JNC 1/B3

JC 1/D8

JNVT 1/D4

JVT 1/DC

JNV 1/D5

JV 1/DD

JGE 1/D6

JLT 1/DE

JNE 1/D7

JE 1/DF

JBC 3/30 –37

JBS 3/38–3F

NOTES:

3. The 3 least significant bits of the opcode are concatenated with the 8 bits to form an 11-bit, 2’s complement offset.

4. The DJNZW instruction is not guaranteed to work. See Functional Deviations section.

2/E3

(3)

(3)

Mnemonic Length/Opcode

DJNZ 3/E0

DJNZW 3/E1

NORML 3/0F

SHRL 3/0C

SHLL 3/0D

SHRAL 3/0E

SHR 3/08

SHRB 3/18

SHL 3/09

SHLB 3/19

SHRA 3/0A

SHRAB 3/1A

CLRC 1/F8

SETC 1/F9

DI 1/FA

EI 1/FB

CLRVT 1/FC

NOP 1/FD

RST 1/FF

SKIP 2/00

IDLPD 1/F6

BMOV 3/C1

(4)

19

Page 24

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

Table 3.3A. Instruction Execution State Times

MNEMONIC DIRECT IMMED

INDIRECT INDEXED

(1)

NORMAL* A-INC* SHORT* LONG*

ADD (3-op) 5 6 7/10 8/11 7/10 8/11

SUB (3-op) 5 6 7/10 8/11 7/10 8/11

ADD (2-op) 4 5 6/8 7/9 6/8 7/9

SUB (2-op) 4 5 6/8 7/9 6/8 7/9

ADDC 4 5 6/8 7/9 6/8 7/9

SUBC 4 5 6/8 7/9 6/8 7/9

CMP 4 5 6/8 7/9 6/8 7/9

ADDB (3-op) 5 5 7/10 8/11 7/10 8/11

SUBB (3-op) 5 5 7/10 8/11 7/10 8/11

ADDB (2-op) 4 4 6/8 7/9 6/8 7/9

SUBB (2-op) 4 4 6/8 7/9 6/8 7/9

ADDCB 4 4 6/8 7/9 6/8 7/9

SUBCB 4 4 6/8 7/9 6/8 7/9

CMPB 4 4 6/8 7/9 6/8 7/9

MUL (3-op) 16 17 18/21 19/22 19/22 20/23

MULU (3-op) 14 15 16/19 17/19 17/20 18/21

MUL (2-op) 16 17 18/21 19/22 19/22 20/23

MULU (2-op) 14 15 16/19 17/19 17/20 18/21

DIV 26 27 28/31 29/32 29/32 30/33

DIVU 24 25 26/29 27/30 27/30 28/31

MULB (3-op) 12 12 14/17 13/15 15/18 16/19

MULUB (3-op) 10 10 12/15 12/16 12/16 14/17

MULB (2-op) 12 12 14/17 15/18 15/18 16/19

MULUB (2-op) 10 10 12/15 13/15 12/16 14/17

DIVB 18 18 20/23 21/24 21/24 22/25

DIVUB 16 16 18/21 19/22 19/22 20/23

AND (3-op) 5 6 7/10 8/11 7/10 8/11

AND (2-op) 4 5 6/8 7/9 6/8 7/9

OR (2-op) 4 5 6/8 7/9 6/8 7/9

XOR 4 5 6/8 7/9 6/8 7/9

ANDB (3-op) 5 5 7/10 8/11 7/10 8/11

ANDB (2-op) 4 4 6/8 7/9 6/8 7/9

ORB (2-op) 4 4 6/8 7/9 6/8 7/9

XORB 4 4 6/8 7/9 6/8 7/9

LD, LDB 4, 4 5, 4 5/8 6/8 6/9 7/10

ST, STB 4, 4

b

5/8 6/9 6/9 7/10

LDBSE 4 4 5/8 6/8 6/9 7/10

LDBZE 4 4 5/8 6/8 6/9 7/10

BMOV internal/internal: 6a8 per word

external/internal: 6

external/external: 6

a

11 per word

a

14 per word

PUSH (int stack) 6 7 9/12 10/13 10/13 11/14

POP (int stack) 8

b

10/12 11/13 11/13 12/14

PUSH (ext stack) 8 9 11/14 12/15 12/15 13/16

POP (ext stack) 11

*Times for operands as: SFRs and internal RAM (0 –1FFH)/memory controller (200H –0FFFFH)

NOTE:

1. Execution times for memory controller references may be one to two states higher depending on the number of bytes in

the prefetch queue. Internal stack is 200H– 1FFH and external stack is 200H –0FFFFH.

b

13/15 14/16 14/16 15/17

20

Page 25

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

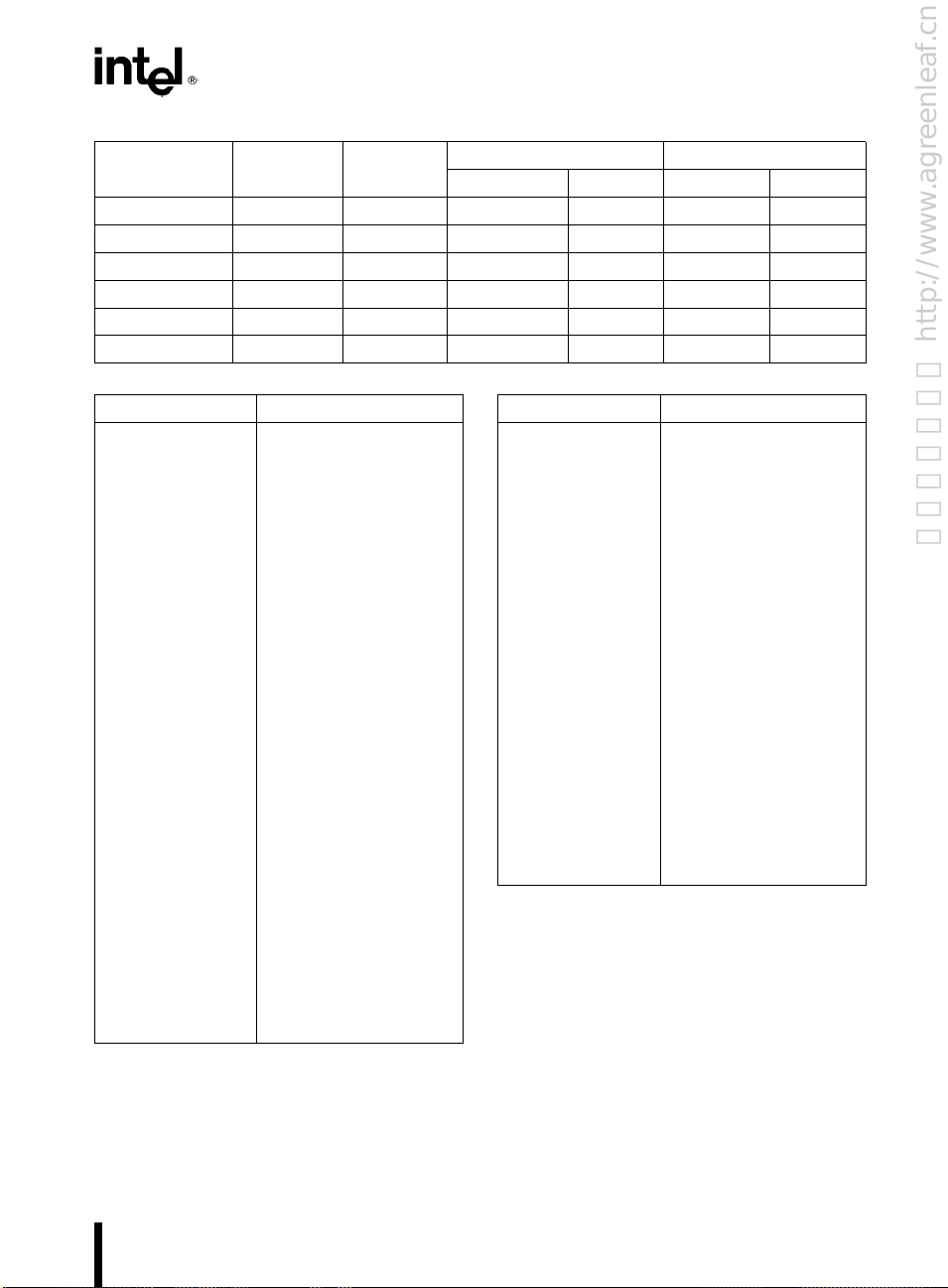

Table 3.3B. Instruction Execution State Times

MNEMONIC MNEMONIC

PUSHF (int stack) 6 PUSHF (ext stack) 8

POPF (int stack) 7 POPF (ext stack) 10

PUSHA (int stack) 12 PUSHA (ext stack) 18

POPA (int stack) 12 POPA (ext stack) 18

TRAP (int stack) 16 TRAP (ext stack) 18

LCALL (int stack) 11 LCALL (ext stack) 13

SCALL (int stack) 11 SCALL (ext stack) 13

RET (int stack) 11 RET (ext stack) 14

CMPL 7 DEC/DECB 3

CLR/CLRB 3 EXT/EXTB 4

NOT/NOTB 3 INC/INCB 3

NEG/NEGB 3

LJMP 7

SJMP 7

BR[indirect

JNST, JST 4/8 jump not taken/jump taken

JNH, JH 4/8 jump not taken/jump taken

JGT, JLE 4/8 jump not taken/jump taken

JNC, JC 4/8 jump not taken/jump taken

JNVT, JVT 4/8 jump not taken/jump taken

JNV, JV 4/8 jump not taken/jump taken

JGE, JLT 4/8 jump not taken/jump taken

JNE, JE 4/8 jump not taken/jump taken

JBC, JBS 5/9 jump not taken/jump taken

DJNZ 5/9 jump not taken/jump taken

DJNZW (Note 1) 5/9 jump not taken/jump taken

NORML 8a1 per shift (9 for 0 shift)

SHRL 7

SHLL 7

SHRAL 7

SHR/SHRB 6

SHL/SHLB 6

SHRA/SHRAB 6a1 per shift (7 for 0 shift)

CLRC 2

SETC 2

DI 2

EI 2

CLRVT 2

NOP 2

RST 15 (includes fetch of configuration byte)

SKIP 3

IDLPD 8/25 (proper key/improper key)

]

7

a

1 per shift (8 for 0 shift)

a

1 per shift (8 for 0 shift)

a

1 per shift (8 for 0 shift)

a

1 per shift (7 for 0 shift)

a

1 per shift (7 for 0 shift)

NOTE:

1. The DJNZW instruction is not guaranteed to work. See Functional Deviations section.

21

Page 26

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

3.5 80C196KB Instruction Set Additions and Differences

For users already familiar with the 8096BH, there are

six instructions added to the standard MCS-96 instruction set to form the 80C196KB instruction set. All of

the former instructions perform the same function, except as indicated in the next section. The new instructions and their descriptions are listed below:

PUSHA Ð PUSHes the PSW, INTÐMASK, IM-

POPA Ð POPs the PSW, INTÐMASK, IMASK1,

IDLPD Ð Sets the part into IDLE or Powerdown

CMPL Ð Compare 2 long direct values

BMOV Ð Block move using 2 auto-incrementing

DJNZW Ð Decrement Jump Not Zero using a Word

INSTRUCTION DIFFERENCES

Instruction times on the 80C196KB are shorter than

those on the 8096 for many instructions. For example a

c

16

14 states. In addition, many zero and one operand instructions and most instructions using external data

take one or two fewer state times.

Indexed and indirect operations relative to the stack

pointer (SP) work differently on the 80C196KB than

on the 8096BH. On the 8096BH, the address is calculated based on the un-updated version of the stack

pointer. The 80C196KB uses the updated version. The

offset for POP[SP]and POP nn[SP]instructions may

need to be changed by a count of 2.

ASK1, and WSR

and WSR

mode

pointers and a counter

counter (Not functional on current stepping.)

16 unsigned multiply has been reduced from 25 to

3.6 Software Standards and Conventions

For a software project of any size it is a good idea to

modularize the program and to establish standards

which control the communication between these modules. The nature of these standards will vary with the

needs of the final application. A common component of

all of these standards, however, must be the mechanism

for passing parameters to procedures and returning results from procedures. In the absence of some overriding consideration which prevents their use, it is suggested that the user conform to the conventions adopted by

the PLM-96 programming language for procedure linkage. It is a very usable standard for both the assembly

language and PLM-96 environment and it offers compatibility between these environments. Another advantage is that it allows the user access to the same floating

point arithmetics library that PLM-96 uses to operate

on REAL variables.

REGISTER UTILIZATION

The MCS-96 architecture provides a 256 byte register

file. Some of these registers are used to control registermapped I/O devices and for other special functions

such as the ZERO register and the stack pointer. The

remaining bytes in the register file, some 230 of them,

are available for allocation by the programmer. If these

registers are to be used effectively, some overall strategy

for their allocation must be adopted. PLM-96 adopts

the simple and effective strategy of allocating the eight

bytes between addresses 1CH and 23H as temporary

storage. The starting address of this region is called

PLMREG. The remaining area in the register file is

treated as a segment of memory which is allocated as

required.

ADDRESSING 32-BIT OPERANDS

These operands are formed from two adjacent 16-bit

words in memory. The least significant word of the

double word is always in lower address, even when the

data is in the stack (which means that the most significant word must be pushed into the stack first). A double word is addressed by the address of its least significant byte. Note that the hardware supports some operations on double words. For these operations the double

word must be in the internal register file and must have

an address which is evenly divisible by four.

SUBROUTINE LINKAGE

Parameters are passed to subroutines in the stack. Parameters are pushed into the stack in the order that

they are encountered in the scanning of the source text.

Eight-bit parameters (BYTES or SHORT-INTEGERS) are pushed into the stack with the high order

byte undefined. Thirty-two bit parameters (LONG-INTEGERS, DOUBLE-WORDS, and REALS) are

pushed onto the stack as two 16-bit values; the most

significant half of the parameter is pushed into the

stack first.

As an example, consider the following PLM-96 procedure:

exampleÐprocedure: PROCEDURE

(param1,param2,param3);

DECLARE param1 BYTE,

param2 DWORD,

param3 WORD;

22

Page 27

80C196KB USER’S GUIDE

数控原理与维修 http://www.agreenleaf.cn

When this procedure is entered at run time the stack

will contain the parameters in the following order:

?????? : param1

high word of param2

low word of param2

param3

return address

Figure 3-5. Stack Image

If a procedure returns a value to the calling code (as

opposed to modifying more global variables) then the

result is returned in the variable PLMREG. PLMREG

is viewed as either an 8-, 16- or 32-bit variable depending on the type of the procedure.

The standard calling convention adopted by PLM-96

has several key features:

a) Procedures can always assume that the eight bytes of

register file memory starting at PLMREG can be

used as temporaries within the body of the procedure.

b) Code which calls a procedure must assume that the

eight bytes of register file memory starting at

PLMREG are modified by the procedure.

c) The Program Status Word (PSWÐsee Section 3.3) is

not saved and restored by procedures so the calling

code must assume that the condition flags (Z, N, V,