Page 1

Intel 186 EB/EC

Evaluation Board

User’s Manual

80C186EC/80C188EC

80L186EC/80L188EC

and

80C186EB/80C188EB

80L186EB/80L188EB

March 1997

Order Number: 272986-001

Page 2

Informa t ion in this do cument is provided in connection with Intel pr od ucts. No license, expre ss or implied, b y e st oppel or oth er -

wise, to any intellec t ual property r i g ht s is granted by t his document. Exc ept as provide d i n In t el’s Terms and Conditions of Sale

for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale

and/or u se o f In tel pro du cts i nc lud in g li abil it y o r war ra nti es r el ati ng t o fi t ness fo r a part ic ular pur pose , m ercha nta bi lit y, or i nfr i ngement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving,

or life sustaining applications.

The product may contain design defects or errors known as errata. Current characterized errata are available on request.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice. Contact your local

Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

*Third-party brands and names are the property of their respective owners.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be ob-

tained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

Copyright © INTEL CORPORATION, 1997

Page 3

CONTENTS

CHAPTER 1

ABOUT THIS MANUAL

1.1 CONTENT OVERVIEW................................................................................................. 1-1

1.2 NOTATION CONVENTIONS......................................................................................... 1-2

1.3 RELATED DOCUMENTS.............................................................................................. 1-3

1.4 ELECTRONIC SUPPORT SYSTEMS........................................................................... 1-4

1.4.1 FaxBack Service .......................................................................................................1-4

1.4.2 World Wide Web .......................................................................................................1-4

1.5 TECHNICAL SUPPORT................................................................................................ 1-5

CHAPTER 2

GETTING STARTED

2.1 SYSTEM REQUIREMENTS.......................................................................................... 2-3

2.2 WHAT’S IN YOUR KIT................................................................................................... 2-3

2.3 VIEWING THE BOARD SCHEMATICS......................................................................... 2-4

2.4 SETTING UP THE EVALUATION BOARD AND THE HOST PC.................................. 2-4

CHAPTER 3

HARDWARE OVERVIEW

3.1 JUMPER SUMMARY..................................................................................................... 3-1

3.2 MICROPROCESSOR.................................................................................................... 3-2

3.2.1 Packaging .................................................................................................................3-2

3.3 MEMORY CONFIGURATION........................................................................................ 3-3

3.3.1 Flash (Program Memory) ..........................................................................................3-5

3.3.1.1 Configuring the Board for Flash Downloading .................................................3-5

3.3.2 SRAM (Static Memory) .............................................................................................3-7

3.4 PROGRAMMABLE LOGIC............................................................................................ 3-7

3.5 POWER SUPPLY.......................................................................................................... 3-8

3.6 SERIAL INTERFACE..................................................................................................... 3-9

3.7 EXPANSION INTERFACE........................................................................................... 3-12

3.8 LCD INTERFACE ................................... ........ ......... ........ ........ ......... ........ ......... ........ .. 3-15

3.8.1 LCD Interface Demo ...............................................................................................3-15

iii

Page 4

CONTENTS

CHAPTER 4

INTRODUCTION TO THE SOFTWARE

4.1 SOFTWARE FEATURES.............................................................................................. 4-1

4.2 RESTRICTIONS............................................................................................................ 4-2

4.3 EMBEDDED CONTROLLER MONITOR (ECM)............................................................ 4-2

4.4 USER INTERFACE........................................................................................................ 4-3

4.4.1 Numeric Input ............................................................................................................4-3

4.4.2 Controlling Lengthy Commands ................................................................................4-3

4.4.3 Aborting from iECM-86 .............................................................................................4-3

4.5 INITIATING AND TERMINATING iECM-86................................................................... 4-3

4.5.1 ECM86 ......................................................................................................................4-3

4.5.2 -COM2, -COM1 .........................................................................................................4-4

4.5.3 -DIAG ........................................................................................................................4-4

4.5.4 -POLL, -SIGNAL ................................................................................. ......... ........ .....4-5

4.5.5 RESET SYSTEM, RES SYSTEM, RESET, RES ......................................................4-5

4.5.6 DOS ..........................................................................................................................4-5

4.5.7 QUIT .........................................................................................................................4-5

4.6 RELATED INFORMATION............................................................................................ 4-6

4.6.1 Reserved Functions ..................................................................................................4-6

4.6.2 Reserved Memory .....................................................................................................4-6

4.6.3 Reserved I/O .............................................................................................................4-6

CHAPTER 5

iECM-86 COMMANDS

5.1 ENTERING COMMANDS.............................................................................................. 5-1

5.2 FILE OPERATIONS....................................................................................................... 5-2

5.2.1 Loading and Saving Object Code .............................................................................5-2

5.2.2 Other File Operations ................................................................................................5-3

5.3 PROGRAM CONTROL................................................................................................. 5-5

5.3.1 Resetting the Target .................................................................................................5-5

5.3.2 Breakpoints ...............................................................................................................5-5

5.3.3 Program Execution ...................................................................................................5-7

5.3.4 Program Stepping .....................................................................................................5-8

5.4 DISPLAYING AND MODIFYING PROGRAM VARIABLES......................................... 5-10

5.4.1 Supported Data Types ............................................................................................5-10

5.4.2 BYTE Commands ...................................................................................................5-11

5.4.3 WORD Commands .................................................................................................5-12

5.4.4 DWORD Commands .......................................................... ......... ............................5-13

5.4.5 STACK Commands .................................................................................................5-14

5.4.6 STRING Commands ...............................................................................................5-15

5.4.7 PORT Commands ...................................................................................................5-15

5.4.8 WPORT Commands ...............................................................................................5-16

5.4.9 Processor Variables ................................................................................................5-17

iv

Page 5

CONTENTS

CHAPTER 6

iRISM-186 COMMANDS

6.1 IRISM VARIABLES........................................................................................................ 6-1

6.1.1 Other Variables .........................................................................................................6-1

6.2 RISM STRUCTURE......................................................... .......................................... .... 6-2

6.3 RECEIVING DATA FROM THE HOST.......................................................................... 6-2

6.4 SENDING DATA TO THE HOST................................................................................... 6-2

6.5 RISM COMMANDS........................ .......................................... ......... ........ ......... ............ 6-2

6.5.1 SET_DATA_FLAG (Code 00H) .......................... ........ ........ ......... ........ ......... ........ .....6-3

6.5.2 TRANSMIT (Code 02H) .............................................................. ........ ......... .............6-3

6.5.3 READ_BYTE (Code 04H) .........................................................................................6-3

6.5.4 READ_WORD (Code 05H) .......................................................................................6-3

6.5.5 READ_DOUBLE (Code 06H) ....................................................................................6-3

6.5.6 WRITE_BYTE (Code 07H) ........................................................................................6-3

6.5.7 WRITE_WORD (Code 08H) ......................................................................................6-3

6.5.8 WRITE_DOUBLE (Code 09H) ..................................................................................6-4

6.5.9 LOAD_ADDRESS (Code 0AH) .................................................................................6-4

6.5.10 READ_PC (Code 10H) .............................................................................................6-4

6.5.11 WRITE_PC (Code 11H) ............................................................................................6-4

6.5.12 START_USER (Code 12H) ......................................................... ........ ......... ........ .....6-4

6.5.13 STOP_USER (code 13H) .........................................................................................6-4

6.5.14 TRAP_ISR ................................................................................................................6-5

6.5.15 REPORT_STATUS (Code 14H) ...............................................................................6-5

6.5.16 MONITOR_ESCAPE (Code 15H) .............................. ........ ......... ........ ......... ........ .....6-5

6.5.17 READ_BPORT (Code 16H) ......................................................................................6-5

6.5.18 WRITE_BPORT (Code 17H) .....................................................................................6-5

6.5.19 READ_WPORT (Code 18H) .....................................................................................6-5

6.5.20 WRITE_WPORT (Code 19H) ....................................................................................6-6

6.5.21 STEP (Code 1AH) .....................................................................................................6-6

6.5.22 READ_REG (Code 1BH) ..........................................................................................6-6

6.5.23 WRITE_REG (Code 1CH) .........................................................................................6-6

6.5.24 Start Up Commands (/ or \) .......................................................................................6-7

APPENDIX A

PARTS LIST

v

Page 6

CONTENTS

FIGURES

2-1 Intel 186 EB Evaluation Board Layout..........................................................................2-1

2-2 Intel 186 EC Evaluation Board Layout .........................................................................2-2

3-1 Physical Memory Map..................................................................................................3-4

3-2 Jumper Assembly for Flash Downloading....................................................................3-6

3-3 E1 Jumper....................................................................................................................3-8

3-4 J2 Power Connector.....................................................................................................3-8

3-5 25-Pin to 9-Pin Adaptor..............................................................................................3-11

3-6 186 EC Peripheral Expansion Connector JP2 (40 pin)..............................................3-12

3-7 186 EB Peripheral Expansion Connector JP2 (24 pin)...............................................3-13

TABLES

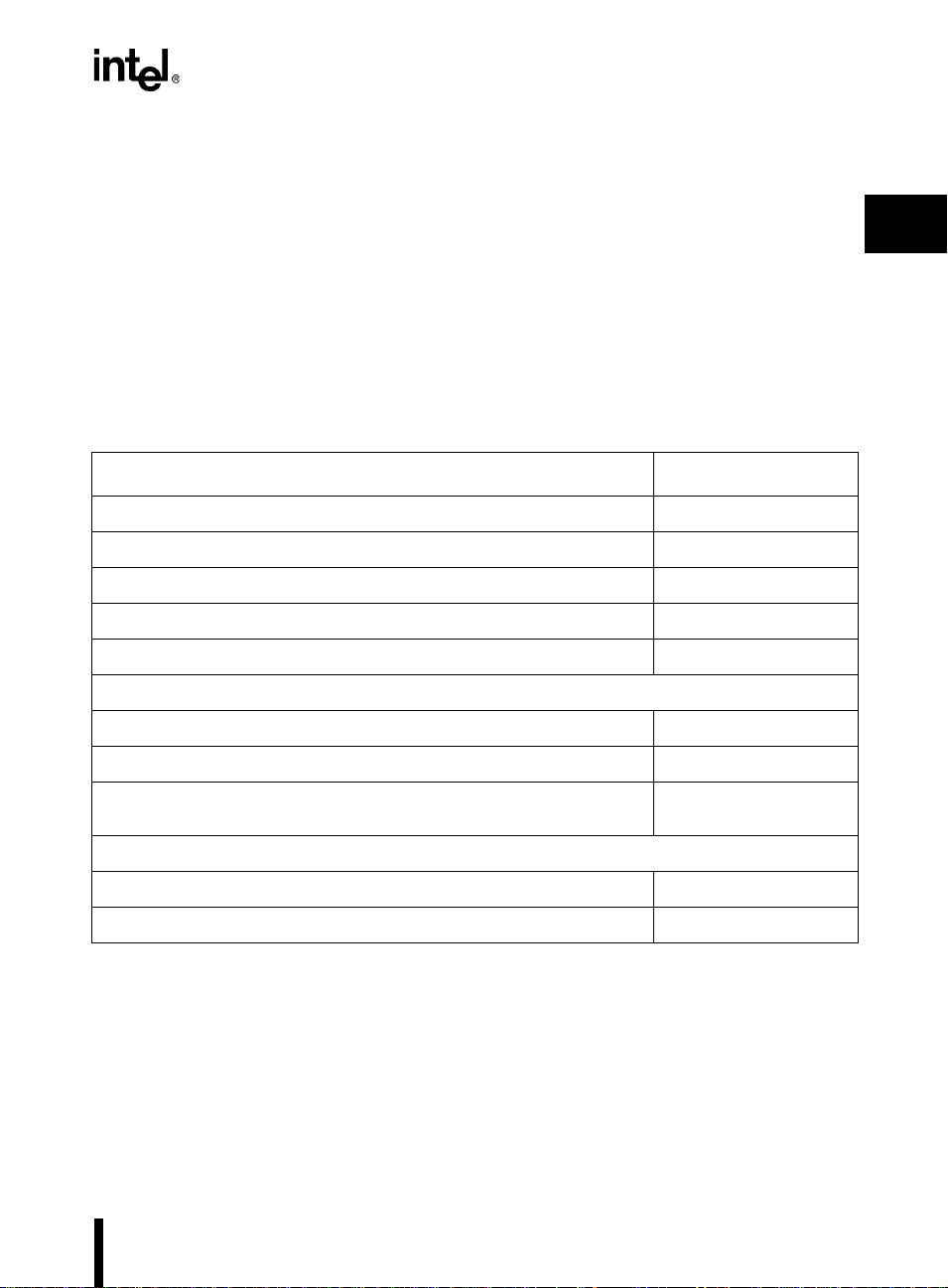

1-1 Customer Support Telephone Numbers.......................................................................1-5

3-1 80x186EB/EC Evaluation Board Jumper Settings........................................................3-1

3-2 Logical Memory Map....................................................................................................3-3

3-3 P1 Host Serial Connector.............................................................................................3-9

3-4 P2 Serial Channel 0 ...................................................................................................3-10

5-1 Supported Data Types...............................................................................................5-10

6-1 iRISM Variables............................................................................................................6-1

6-2 iRISM Registers ...........................................................................................................6-6

A-1 80186 EB Board Manual Parts List.............................................................................A-1

A-2 80186 EC Board Manual Parts List.............................................................................A-4

vi

Page 7

A

About This Manual

1

Page 8

Page 9

CHAPTER 1

ABOUT THIS MANUAL

This manual describes how to set up and use the Intel 186 EB/EC Evaluation Board. The board

is used to evaluate hardware and software performance and provide an “emulation-like” feel

when executing and debugging user-written code. This board operates at either 3.3 volts or 5.0

volts. It supports the following processors:

• 80C186EB/80C188EB

• 80L186EB/80L188EB

• 80C186EC/80C188EC

• 80L186EC/80L188EC.

The 3.3 V, 16 MHz 80L186EB or 80L186EC proce ssor is instal led on th e evalua tion boa rd. This

manual covers both processors.

1.1 CONTENT OVERVIEW

Chapter 1, About This Manual — This chapter contains an overview of this manual.

Chapter 2, Getting Start ed — This chapt er des cribe s the I ntel 186 EC/EB Evaluat ion Boa rd, and

provides setup instructions.

1

Chapter 3, Hardware Overview — This chapter describes the evaluation board hardware, such

as connectors, jumpers, memory configuration, and power supply.

Chapter 4, Introducti on to the Softwa re — This chapter provides an overview of the software

used on the evaluation board and the host computer.

Chapter 5, iECM-86 Commands — This chapter describes the iECM-86 software, which runs

on the host computer.

Chapter 6, iRISM-186 Commands — This chapter describes the iRISM-186 software, which

runs on the evaluation board.

Appendix A, Parts List — This chapter contains a part list for both the EB and EC versions of

the evaluation board.

1-1

Page 10

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

1.2 NOTATION CONVENTIONS

The following notation conventions are used in this manual.

# Pound symbol (#) appended to a signal name indicates that the signal is

active low.

italics Italics identify variables and indicate new terms.

bold sans-serif In text, identifies commands (instructions).

typewriter

font

This font is used for code examples. All characters are equal width; this is

useful for maintaining accurate character spacing.

UPPERCASE In text, signal names are shown in uppercase. When several signals share a

common name, each signal is represented by the signal name followed by a

number; the group is represented by the signal name followed by a variable

(n). In code examples, signal names are shown in the case required by the

software development tool in use.

Designations fo r

hexadecimal a nd

binary numbers

Hexadecimal numbers are represented by a string of hex digits followed by

the letter H. A zero prefix is added to numbers that begin with A through F.

(FF is shown as 0FFH.) For binary numbers, the letter B may be appended

for clar ity.

Units of

mA

milliamps, milliamperes

Measure

A

amps, amperes

NOTE:

Units listed are

frequently used;

other units and

symbols are used

as necessary.

1-2

Kbit, Kbyte

K

Ω

Mbit, Mbyte

KHz, MHz

ms

µs

ns

µF

W

V

kilobits, kilobytes

kilo-ohms

megabits, megabyte s

kilohertz, megahertz

milliseconds

microseconds

nanoseconds

microfarads

watts

volts

Page 11

ABOUT THIS MANUAL

1.3 RELATED DOCUMENTS

You can order Intel product literature from the following Intel literature centers.

1-800-548-4725 U.S. and Canada

708-296-9333 U.S. (from overseas)

44(0)1793-431155 Europe (U.K.)

44(0)1793-421333 Germany

44(0)1793-421777 France

81(0)120-47-88- 32 Japan (fax only)

The following documents may be useful for designing applications using this evaluation board.

Document Name Intel Order #

1

80C186EB/80C188EB Microproces sor User’s Manual

80C186EC/80C 188EC Microprocessor User’s Manual

80C186EB/80C188EB and 80L186EB /80L188EB

80C186EC/80C188EC and 80L186EC/80L188EC

Flash Memory

AP484: Interfacing a Floppy D isk Drive to an 80C186EX Family Process or

AP730: Interfacing the 82C59A-2 to Intel186 Family Processors

AP731: Understanding the In terrupt Control Unit of the

80C186EC/8 0C188EC

80C186EC/80C188EC Hypertext Manual & Datasheet

ApBuilder Interactive Programmi ng Tool Software Pack age 272216

databook 210830

ApBuilder and Hypertext

datasheet 272433

datasheet 272434

Application Notes

270830

272047

272339

272822

272823

272298

1-3

Page 12

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

1.4 ELECTRONIC SUPPORT SYSTEMS

Intel’s FaxBack* service provides up-to-date technical information. Intel also offers a variety of

informatio n on the Worl d Wide Web. These systems are avai labl e 24 hours a day, 7 days a week,

providing technical information whenever you need it.

1.4.1 FaxBack Service

FaxBack is an on- demand publ ishi ng syst em that s ends docu ments to your fax machi ne. You can

get product announcements, change notifications, product literature, device characteristics,

design recommendations, and quality and reliability information.

1-800-525-3019 (US or Canada)

+44-1793-496646 (Eur ope )

+65-256-5350 (Singapore)

+852-2-844-4448 (Hong Kong)

+886-2-514-0815 (Taiwan)

+822-767-2594 (Korea)

+61-2-975-3922 (Australia)

1-503-264-6835 or 1-916-356-3105 (Worldwide)

1.4.2 World Wide Web

Intel offers a variety of information through the World Wide Web (http://www.intel.com/).

1-4

Page 13

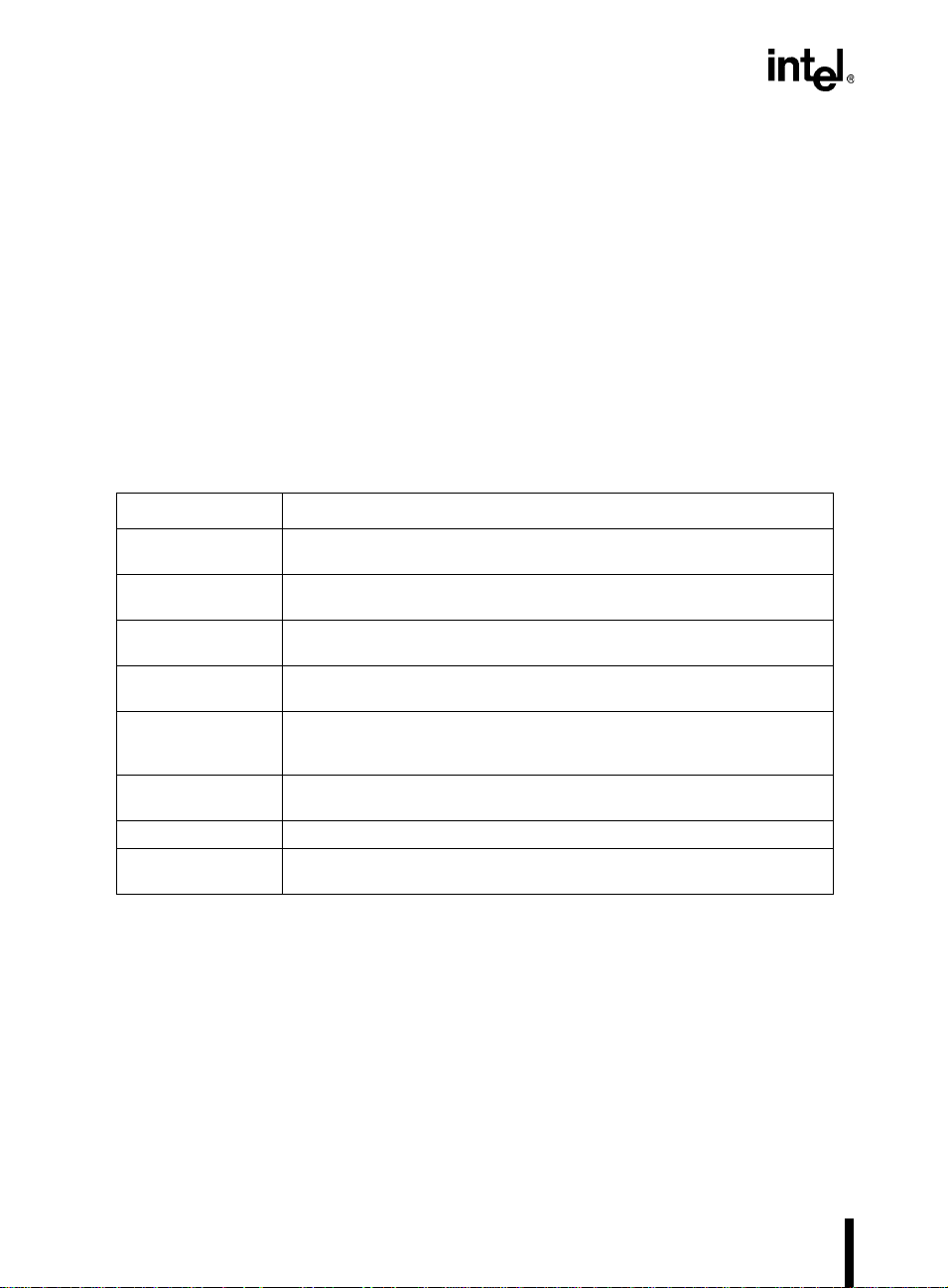

1.5 TECHNICAL SUPPORT

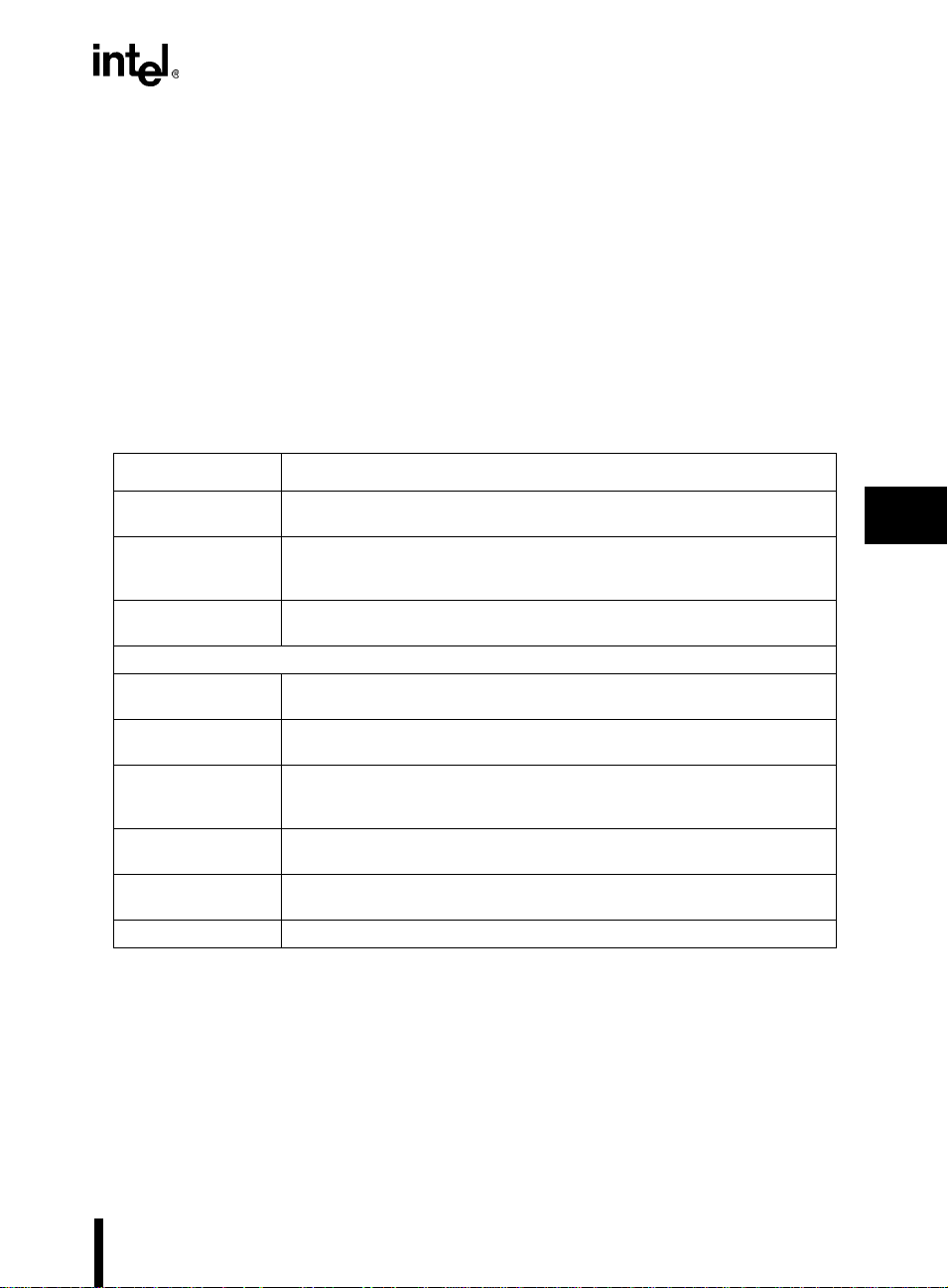

Table 1-1. Customer Support Telephone Numbers

ABOUT THIS MANUAL

Customer Support (US and Canada) 800-628-8686

Australia

National

Sydney

Belgium, Nethe rl ands, and Luxembourg 010-4071-111

Canada Contact local distributor

Finland 358-0-544-644

France 33-1-30-57-72-22

Germany Hardware: 49-89-903-8529

Israel 972-3-548-3232

Italy 39-02-89200950

Japan 0120-1-80387

Sweden 46-8-7340100

008-257-307

61-2-975-3300

61-3-810-2141

Software: 49-89-903-2025

1

1-5

Page 14

Page 15

Getting Started

2

Page 16

Page 17

CHAPTER 2

GETTING STARTED

This chapter des cribes t he Intel 18 6 EC/EB Eval uation Boar d kit, and provi des se tup instru ctions.

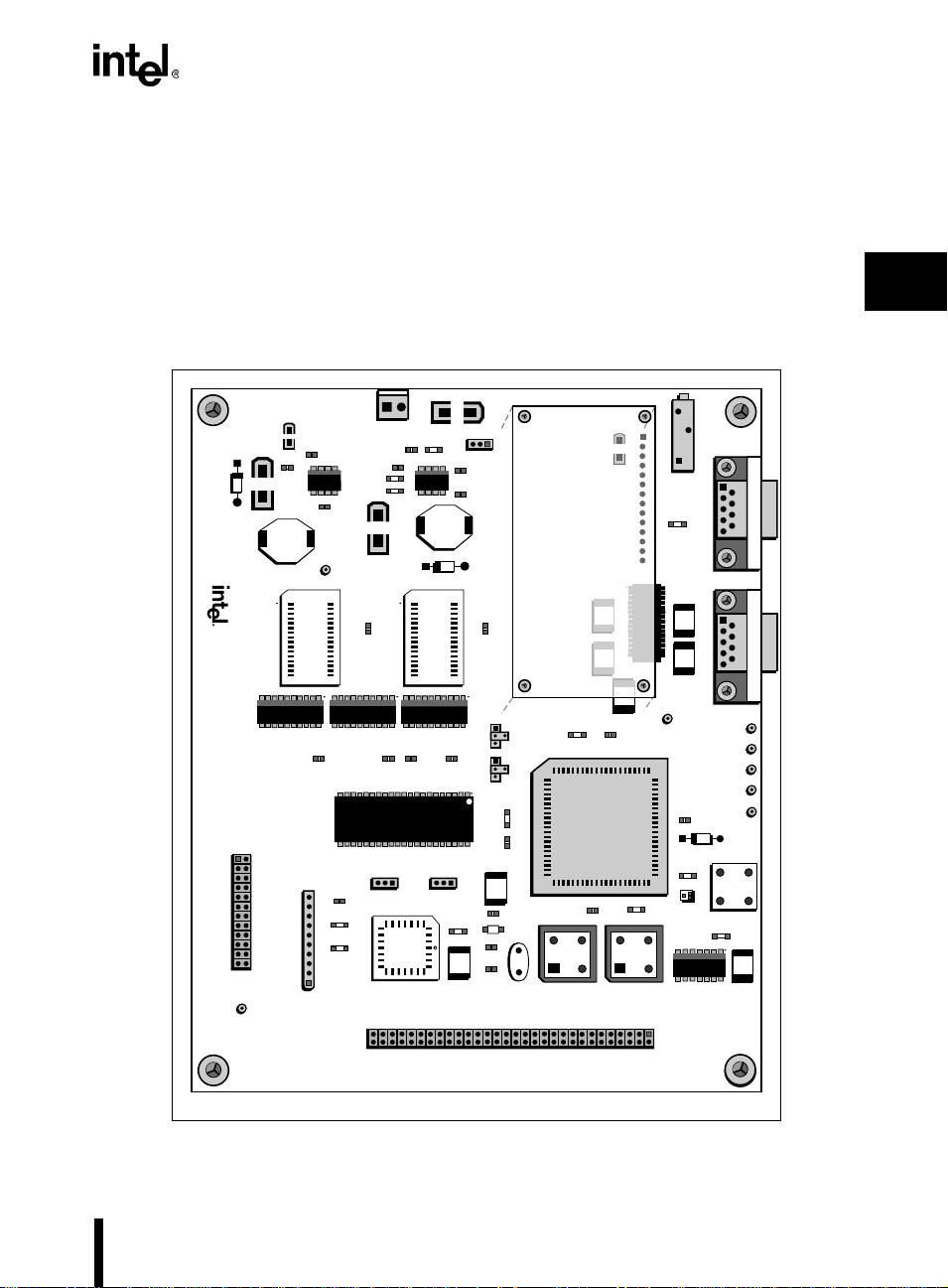

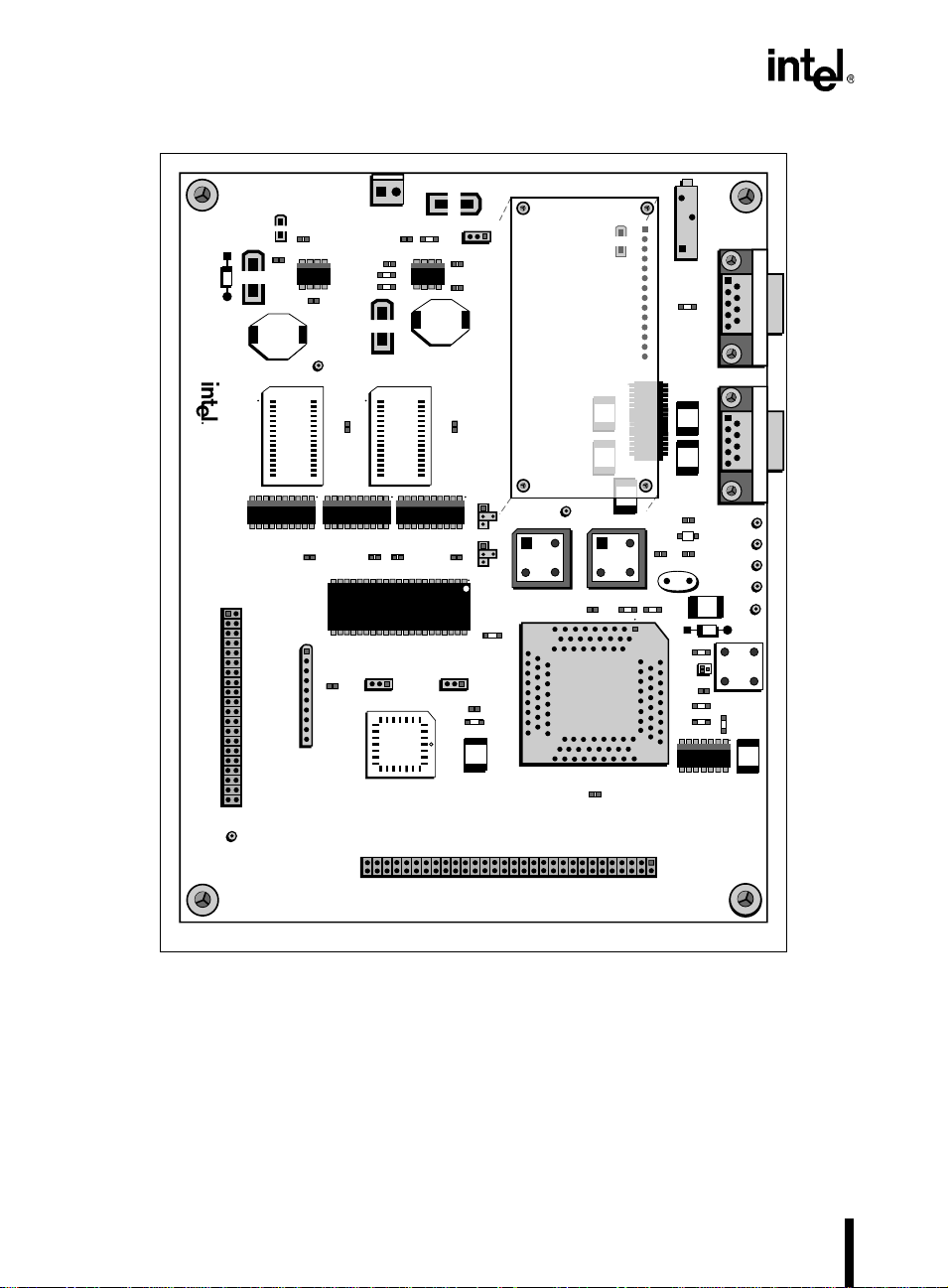

Figure 2-1 shows the 80x186 EB Evaluation Board layout, and Figure 2-2 shows the EC board

layout. Refer to these figu res wh en you are fo llow ing the inst ructio ns in this ch apt er for se tting

up your evaluation board.

J1

R2

P1

R3

P2

C2 C3

DCE ConnectorPC Interface

TP6

GND

R5

V

CC

JP1

V

CC

TP1

TP4 TP3 TP2

TP5

C4

D1

R4

Q1

S1

R1

C1U1

C32

C33

GND

JP2

L3

TP8

C31

U14

V

CC

T0INT1OUT

T1INT0OUT

GNDGND

INT0P2.2

INT1P2.3

INT2BCLK0

INT3P2.6

INT4P2.7

GNDGND

GCS6#+5V

GCS7#+12V

D3

80X186EB EVAL 3V / 5V

V

CC

RP1

GND

C34

C26

TP7

C30

R12

R13

C28

U11

U13

J2

+5V GND

C25

R10

R11

C27

C29

U12

186/188

SELECT

GNDGND

C24

CLKOUTDT-R#

+5VDEN#

C22 R9

C23

E3

ABC

GCS5#BHE#

+12VRESOUT

PWRDN

NMIWR#

LOCK#RD#

U6

C14

FLASH

U10

ALELA19

5V/3V Select

CBA

C20

U7

C21

L2

D2

U8

U9

E4

ABC

R8

C19

READYLA18

HOLDLA17

HLDALA16

GNDGND

C12

E1

C13

PROT

WRT

A B C

A B C

SELECT

C15

C17

C18

AD15LA15

AD14LA14

C5

U2

C8C7

C6

E2 D

E3

U4

D

V

PP

C11R7

C16

L1

U5

Y1

AD13LA13

AD12LA12

AD11LA11

AD10LA10

AD9LA9

AD8LA8

C9

R6

C10

U3

GNDGND

AD7LA7

AD6LA6

AD5LA5

AD4LA4

AD3LA3

AD2LA2

AD1LA1

AD0LA0

2

Figure 2-1. Intel 186 EB Evaluation Board Layout

A5289-01

2-1

Page 18

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

C32

C33

D3

80X186EC EVAL 3V / 5V

C31

L3

GND

C30

C26

TP7

U13

U11

C27

J2

+5V GND

C24

R12

R13

C21 R11

C25

5V/3V Select

U6

U7

C15

CBA

C20

C22

C19

E1

L2

WRT PROT V

C12C11

J1

R2

C8

U2

R3

C2 C3

P1

P2

DCE ConntectorPC Interface

E2 D

A B C

C34

RP1

U12 U8

186/188

SELECT

C29

GNDGND

CLKOUTDT-R#

C23C28

ABC

+5VDEN#

+12VRESOUT

E5

GCS5#BHE#

NMIWR#

LOCK#RD#

ALELA19

U14

JP2

T1OUTT0IN

T0OUTT1IN

V

V

CC

CC

P3.0INT0

P3.1INT1

P3.2INT2

P3.3INT3

P3.4INT4

P3.5INT5

WDTOUT#INT6

GNDINT7

BCLK0INTA#

P2.3GND

RXD1DRQ0

TXD1DRQ1

P2.6DRQ2

CTS1#DRQ3

GNDGND

+5VGCS6#

+12VGCS7#

GND

TP8

C16

FLASH

PWRDN

U10

READYLA18

HOLDLA17

U9

ABC

C18

HLDALA16

A B C

PP

SELECT

E4

GNDGND

AD15LA15

R9

C17

R10

E3

D

AD14LA14

AD13LA13

AD12LA12

U5

AD11LA11

AD10LA10

AD9LA9

GND

AD8LA8

GNDGND

AD7LA7

TP6

U3

AD6LA6

C14

AD5LA5

AD4LA4

C10

AD3LA3

AD2LA2

AD1LA1

AD0LA0

TP1

C4

L1

C9

C5

TP4 TP3 TP2

Y1

TP5

R7R8C13

U4

V

CC

JP1

V

CC

C6

D1

R4

Q1

C7

R5

R6

S1

R1

C1U1

A5288-01

Figure 2-2. Intel 186 EC Evaluation Board Layout

2-2

Page 19

GETTING STARTED

2.1 SYSTEM REQUIREMENTS

• IBM* PC AT, XT or BIOS-compatible computer host system (interfaces via COM1 or

COM2 at 9600 baud).

• 5 V power supply (the connector housing and contact pins are included in the kit).

2.2 WHAT’S IN YOUR KIT

Evaluation Board Your kit includes a board with either a 3.3 volt, 16 MHz

80L186EB or 80L186EC microprocessor installed. Separately

packaged components included with the board are 5 VDC versions of the microprocessor and SRAM for conversion to a

5 VDC evaluation platform.

Monitor Program The Embedded Controller Monitor (ECM) program supports

basic software and hardware evaluation and basic debug facilities

(LOAD, GO, STEP, etc.) on the evaluation board. The ECM consists of two prog rams : RISM -186 ex ecutes in the ev aluat ion boa rd

and ECM-86 executes in an IBM PC or BIOS-compatible computer, called the host PC. These two programs communicate

through an asynchronous serial channel using a binary protocol

defined specifically for this application.

The source co de for the monitor soft ware is pro vid ed on a di sket te

included in your kit; this allows you to update the software for

various operating conditions in your target application.

Contents on Disk In addition to Flash downloading software, a diskette provided in

the kit contains schematics, a pld file for the programmable logic

device used on the board, and a sample assembly file for working

the with L CD display. Compiler software is not included in the

kit.

2

Software Development

Kit

Flash Loading

Utility

Serial Cable A serial cable is provided to connect the evaluation board to the

The kit provides a software development kit, which includes a

software debugger, locator, and sample code.

Users can download application programs to the on-board Flash

memory for execution. The Flash loading uti l it y is co nta in ed on a

diskette, and a separate manual, the CQI Flash Loader User’s

Manual, provides instructions for using this utility.

host PC.

2-3

Page 20

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

2.3 VIEWING THE BOARD SCHEMATICS

The schematics provided on the diskette are in the Adobe* Acrobat .pdf format. You can view

and print the schem atic s using the Acrobat Reader. The Reade r is availa bl e at no char ge from the

Intel World Wide Web site (http://www.intel.com/) or from the Adobe site

(http://www.adobe.com/).

2.4 SETTING UP THE EVALUATION BOARD AND THE HOST PC

This section tells you how to set up the board for use with a host PC. This section assumes you

won’t be using some of the advanced features of the board when you first power it up. For

additional options, such as selecting 80188 evaluation mode, refer to Chapter 3, “Hardware

Overview.”

1. Make sure you are in a static-free environment before removing any components from

their anti-static packaging. The evaluation board is susceptible to electro-static discharge

damage; such damage may cause product failure or unpredictable operation.

2. Inspect the contents of your kit. Make sure that all items are included. Check for damage

that may have oc cur re d during shipmen t. Cont act y our sales repres ent at iv e i f any items are

missing or damaged.

CAUTION: Many of the connectors on the evaluation board provide power through non-

standard pins. Connecting the wrong cable or reversing the cable can damage the

evaluation board and may damage the device being connected. Use extreme

caution when preparing to connect cables to this product.

3. Connect the power supply. The Intel 186 EC/EB Evaluation Board operates from a

5 VDC ± 10% power supply plugged into the J2 power connector (see Figures 2-1

and 2-2). This 5 volt signal is stepped down to 3.3 volts on the board. The connector

housing and contact pins provided in your kit match the power supply to the J2 connector.

To select 5 V, place a jumper on pins B and C of jumpe r E1. To select 3 V, place a jumper

on pins A and B of jumper E1. See Figures 2-1 and 2-2 for jumper locations.

All devices on the board operate at both 3.3 volts and 5.0 volts (except the LCD display,

which is hardwired to 5 volts). This option allows comparison of current consumption

when running code at either voltage. Separately packaged 5 V versions of the 80C186

processor and SRAM must be installed on the board for 5V operation.

2-4

Page 21

GETTING STARTED

4. Apply power to the host PC and the evaluation board.

When power is applied to the board, the message “i186 Ex 3V/5V EV” should appear

across the LCD display. This message indicates board initialization is complete. If the

message does not appear, press the reset button (S1).

Connect one end of the standard 9-pin AT-type serial connector to header P1 on the

evaluation board. Connect the other end to the COM1 port of the host computer. (You can

use COM2 if you need to, but you’ll have to specify COM2 when you run the Monitor

Software.) The PC and board communicate at 9600 baud.

After connection to the PC, the processor may appear to be held in the reset state. The

reason this occurs is that one of the host signals is used to reset the board. This signal may

be active prior to invoking the ECM86 host software on the PC. The PC and board

communicate at 9600 baud.

5. Insert the ECM-86 floppy disk provided with your kit in the floppy drive on the host PC.

You can run the ECM86 program directly from the diskette or copy the contents of the

diskette to your hard drive.

6. At the DOS prompt, change to the floppy disk drive (or to the directory to which you

copied the files in the previous step) and enter this command:

ECM86

After a moment, the PC should display the ECM86 monitor screen.

Comple te information on using the monitor software is located in Chapters 4 and 5.

2

2-5

Page 22

Page 23

Hardware Overview

3

Page 24

Page 25

HARDWARE OVERVIEW

CHAPTER 3

HARDWARE OVERVIEW

The evaluation board comes with a 16 MHz 80L186 EB or EC processor, 512 Kbytes of Flash

(containing the iRISM-186 monitor and a Flas h loa der utility in the boot blo ck) , and 256Kbytes

of SRAM. The expansion connector (JP1) supports up to 1 Mbyte of external memory and

64 K bytes of external I/O. Refer to Figures 2-1 and 2-2 for the exact locations of connectors,

jumpers and headers listed in this chapter.

The board utilizes the high peripheral integration of the 186 product family. The programmable

chip-selects support on-board memory, expansion memory, and the LCD interface. The

timer/counter unit controls timing for LCD display accesses. The serial control unit communicates with the hos t PC throug h the i ECM-86 softwa re and the Fl ash lo ader host softwa re. Fin ally,

the I/O port unit controls on-board power management functions (enable/disable serial drivers

and +12 volts).

Other on-chip peripherals are made available for hardware expansion via the JP1, JP2, and P2

connectors. The following sections describe in detail the specific devices used on the board.

3.1 JUMPER SUMMARY

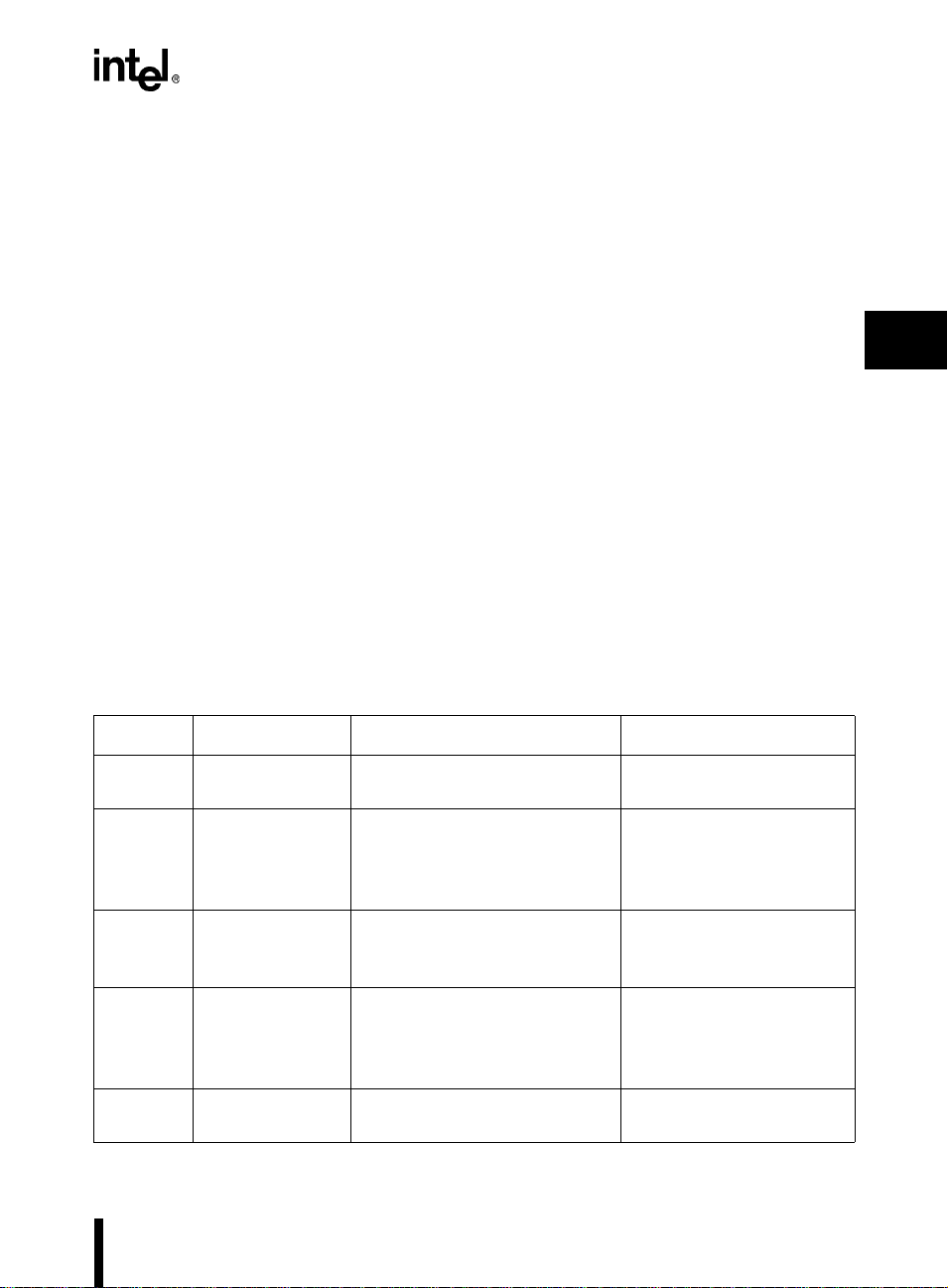

Table 3-1. 80x186EB/EC Evaluation Board Jumper Settings

3

Jumper Name Description Options

E1 5 V/3 V Select Selects voltage (5 V or 3.3 V) that

E2 LA19/WRT PROT Selects options for Flash WP# pin.

E3 V

E4 Flash Powerdo wn

E5 186/ 188 Select Jumper for appropria te processor

†

Default setting

Select Selects 5 V or 12V programming

PP

Select

will be present on V

Includes option to make LA19

available t o Flash pi n 2 f or upg rading

to 8-MBIT component

(PA28F800BV).

voltage, as well as GND to remove

all program and erase capabilities.

Selects options for Flash RP# pin.

For normal operation, SW-RES# is

selected. To un l ock boot block

(regar dl e s s of WP#), 12 V is

selected.

type.

power plane.

CC

A-B = 3.3 V

B-C = 5 V

A-B = Write protect boot block

B-C = Unlock boot block

B-D = Add LA19 for 8- MBIT

Flash

A-B = Total WRT protect

B-C = 12 V program voltage

B-D = 5 V program voltage

A-B = Normal

B-C = Program boot block

override

A-B = 188 processor i nstalled

B-C = 186 processor in stalled

†

†

†

†

†

3-1

Page 26

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

3.2 MICROPROCESSOR

The core of the evaluation board is the 80x186 microprocessor. This processor operates at

3.3 volts up to 16 MHz in this board. Alternatively, the board can be configured to run at 5 volts

up to 33 MHz. To vary the CPU clock speed, an appropriate frequency value oscillator must be

installed at location U3 on the EC board and at location U5 on the EB board. The oscillator

operates at twice the frequency of the installed processor.

The 80x186 processor offers the following features:

• 16-bit data bus

• 1 Mbyte address space

• 2 on-chip UARTs

• 10 programmable chip-selects

• Interrupt control unit

• 3 programmable timer/counters

• Power management unit

• 32-bit watchdog timer (EC only)

• 4 DMA channels (EC only)

The 8-bit bus version of the processor (80C188/80L188) may also be used in this board. To

configure the board to operate with an 8-bit bus, jumper E5 must be in the A–B position. To

configure the board to operate with a 16-bit bus, jumper E5 must be in the B–C position. Many

of the proce ssor’ s on-c hip pe ripher als c an be a ccesse d usin g t he two e xpansi on conne cto rs on the

board (JP1 and JP2).

NOTE

Because host communications use the on-chip serial ports, changing the

operating frequency of the board requires the processor serial ports to be

reconfigured. The RISM monitor source code is provided on a floppy diskette

in your kit and is commented to indicate current register values.

3.2.1 Packaging

The 80x186 EC is packaged in a 100 lead PQFP and so cket and t he 80x186 EB is pac kaged in an

84 lead PLCC package and socket. Adaptors are available from Applied Microsystems Corp.*

and Emulation Technologies, Inc.* to allow for the connection of in-circuit emulators.

3-2

Page 27

HARDWARE OVERVIEW

3.3 MEMORY CONFIGURATION

The memory on the evaluation board can be divided into three types: Flash, SRAM, and

expansion. Flash memory contains the Flash loader utility, located in the boot block boundary,

and the RISM monitor program, beginning at F800:0000. Users can execute their test code from

boot-up using the Flash loader utility. Refer to the CQI Flash Loader Reference Manual for

instructions on programming the Flash memory. SRAM memory is used for the processor

interrupt vector table , stack all ocati on, and RISM da ta vari able s, and as a poss ible de st inati on for

user-writ ten code down loaded on the host i nterf ace. Expan sion me mory can be ac cessed through

the expansion interface, if required.

Table 3-2 shows the log ic al memory map and Figure 3-1 s hows the phys ic al memory ma p of t he

evaluation board.

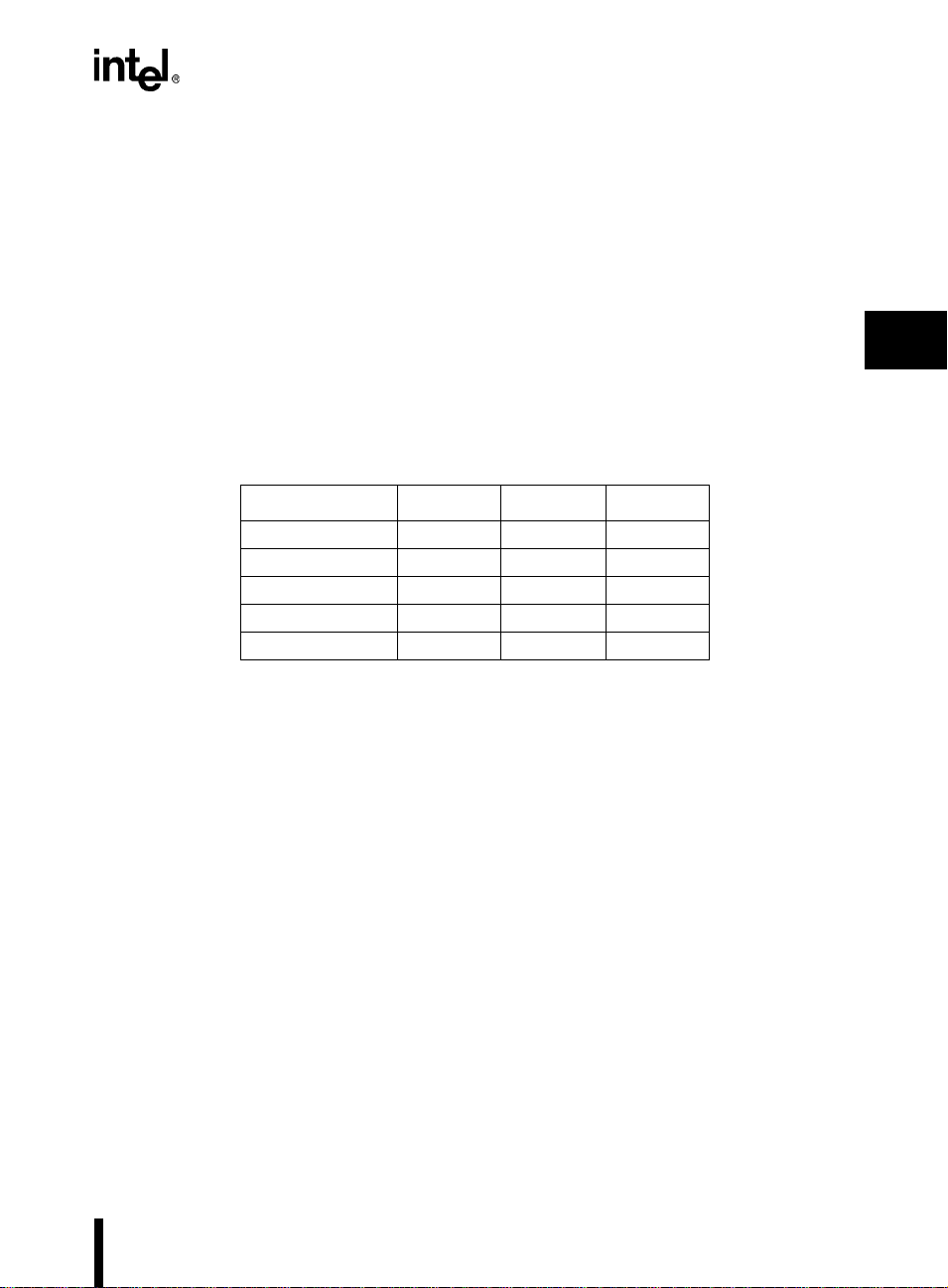

Table 3-2. Logical Memory Map

Memory Area Start (H) Stop (H) Size

SRAM 0000:0000 2000:0000 128 Kbytes

Flash 8000:0000 F000:FFFF 512 Kbytes

Flash Boot Block FC00:0000 F000:FFFF 16 Kbytes

Expansion 4000:0000 8000:000 0 256 Kbytes

LCD (I/O) 0000:0400 0000:0440 64 bytes

3

3-3

Page 28

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

FFFFFH

UCS Flash

512 K

80000H

FFFFFH

Flash Loader Utility* (16K)

FC000H

Control Block

64 K

LCD Control

IO SpaceMemory Space

Peripheral

FFFFH

FF00H

0440H

0400H

Expansion

256 K

Unused

SRAM

128 K

Interru pt Vec t or Table at 00000H to 003FFH ( 1K)

LCS

LCS

GCS5

40000H

20000H

00000H

1Meg

UCS — Upper Chip Select

Start: 80000H Stop: FFFFF (Flash 512 K)

• 3 Wait Stat es

• Active for Memory Bus Cycles

• Bus Ready Not Required

LCS — Lower Chip Select

Start: 0000H Stop: 40000H (SRAM 128 K)

• 2 Wait Stat es

• Stop Address Required

• Active for Memory Bus Cycles

• Bus Ready Ignored

GCS5 — Expansion Memory

Start: 40000H Stop: 80000H (Expansion 256 K)

• Zero Wait Stat es

• Ignore Stop Address

• Active for Memory Bus Cycles

• Bus Ready Requi r ed

GCS7 — Expansion I/O

Start: 400H Stop: 500H

• Zero Wait States

• Ignore Stop Ad dress

• Active for I/O Bus Cycles

• Bus Ready Required

GCS2 — LCD Display I/O

Start: 400H Stop: 440H

• 8 Wait States

• Active for I/O Bus Cycles

• Bus Ready Ignored

* As shipped, RISM is located at F800:0000 and pointed to by the Flash lo ader utility during boot-up.

Figure 3-1. Physical Memory Map

3-4

Page 29

HARDWARE OVERVIEW

3.3.1 Flash (Program Memory)

Flash memory, as configured in the RISM monitor, is mapped to the upper 512 Kbytes of the

1 Mbyt e 80x186 proce ssor ad dress spac e. The board incl udes a singl e 4 Mbit, 32-pin PSOP Flash

device at locati on U9 with 110 ns access time at 3.3 V and 60 ns access time at 5 V. This memory

runs with one wait state at 5 volts/20 MHz and 3.3 volts/16 MHz.

The device data bus can be configured to be either 8 or 16 bits wide (corresponding to the

80x188and the 80x186 processor, respectively). Jumper E5 determines the Flash bus width.

When E5 is in the A–B position, the bus is 8 bits wide; when E5 is in the B–C position, the bus

is 16 bits wide. The configurable bus width allows access to all 512 Kbytes of Flash memory.

If a user app li cat i on r equi re s no nvolatile memory for storage, Flash can be erased and wr it te n by

jumpering E3 for either 5 V or 12 V programming voltage (V

) and using the proper

PP

programming algorithm. The SmartVoltage* Flash device can be programmed using either

voltage. The Flash loader utility is located in the Flash boot block (upper 16 Kbytes, FC000h to

FFFFFh). Writes to this region are prohibited, regardless of the voltage on V

, unless the RP#

PP

input is at +12 vo lt s or ju mp er E2 is s et to un lock the boot block . Jumpe r E4 controls the volt age

on RP#. When E4 i s i n the B–C position, the +1 2 vo lt s uppl y i s connected to RP#. When E4 is in

the A–B position, RP# is connected to the board reset signal.

CAUTION: To access boot block memory, E4 must be in the B–C position and Port Pin 1.1

must be programmed to a logic 0 (enabling +12 volts). Accessing the boot block is

not recommended, as the Flash loader utility code could be corrupted.

3

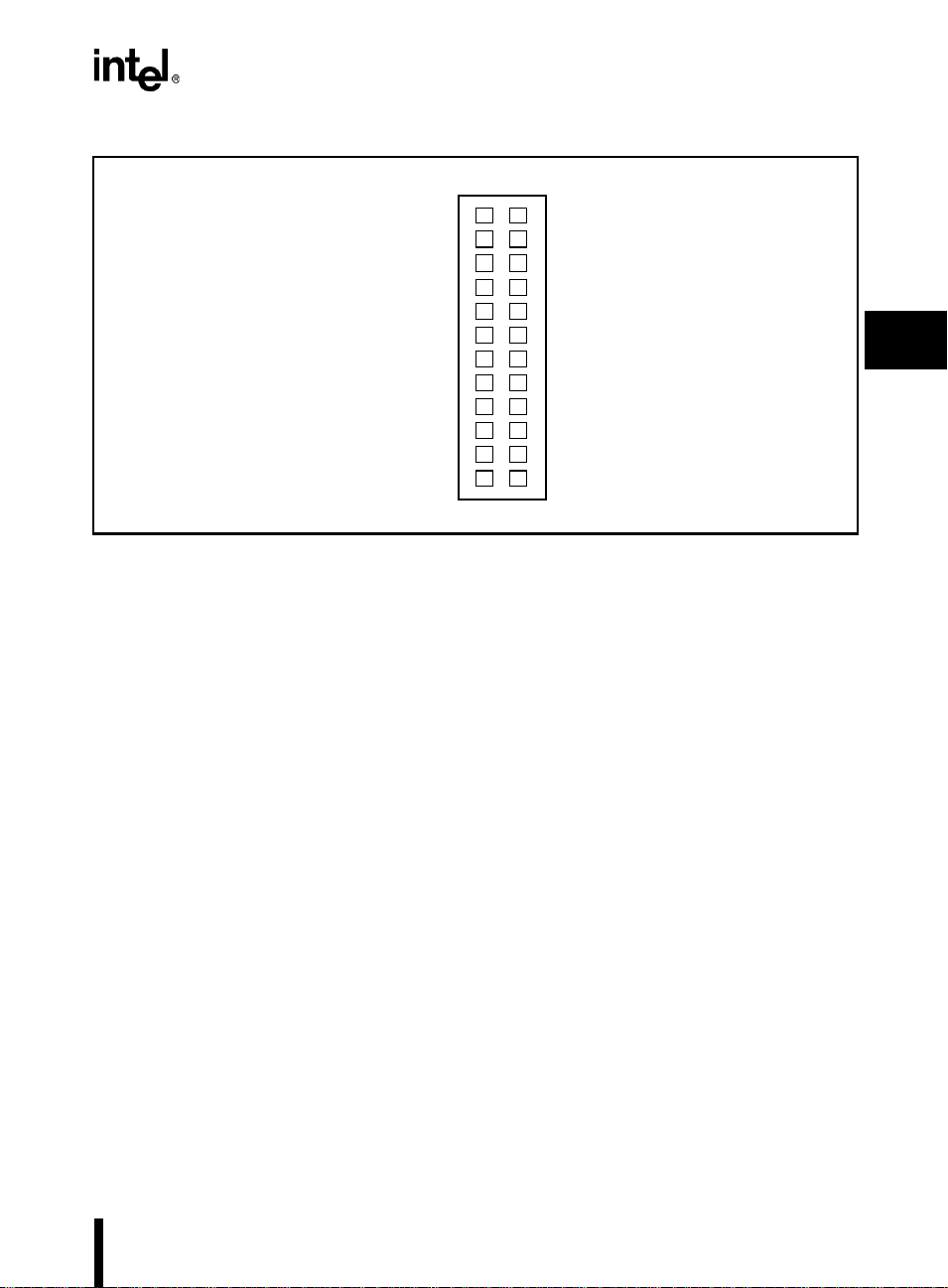

3.3.1.1 Setting Up the Board for Flash Downloading

You can use the Flash utility host program, FLASHLDR.EXE, provided in the kit to download

your application program to the Flash memory. Upon reset or power-up, the Flash loader reads

port pin to determine whether to execute a loaded program, such as RISM, or download new

software to Flash memory.

To set up the board for Flash downloading:

1. Power-off the evaluation board and disconnect the serial cable from the PC.

2. Port pin P2.6 on the secondary header (JP2) controls which programs execute at start-up.

Connect P2.6 to the +5 volt pin with jumper wire and 10 kΩ resistor. Figure 3-2 illustrates

this connection.

CAUTION: A 10 kΩ resistor is required when jumpering from the P2.6 pin to the 5 volt pin; if

this configuration is not used, the processor’s port control hardware could be

damaged.

3-5

Page 30

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

V

CC

Jumper Wire

10K ohm

P2.6

+5V

Jumper Wire

186 EB Connector JP2

V

CC

DRQ2

GCS6#

JP2

T1OUTT0IN

T0OUTT1IN

V

CC

P3.0INT0

P3.1INT1

P3.2INT2

P3.3INT3

P3.4INT4

P3.5INT5

WDTOUT#INT6

GNDINT7

BCLK0INTA#

P2.3GND

RXD1DRQ0

TXD1DRQ1

P2.6

CTS1#DRQ3

GNDGND

+5V

+12VGCS7#

186 EB Connecto r JP2 186 EC Connector JP2

186 EC Connector JP2

V

CC

T0INT1OUT

T1INT0OUT

GNDGND

INT0P2.2

INT1P2.3

INT2BCLK0

INT3

INT4P2.7

GNDGND

GCS6#

GCS7#+12V

Jumper Wire

10K ohm

Jumper Wire

A5420-01

Figure 3-2. Jumper Assembly for Flash Downloading

3. Reconnect the serial cable and power-up the board.

You should notice that the text CQFLASH LOADER now displays on the LED, signaling

that the board is ready for Flash downloading.

When the jumper assembly is installed, the Flash target program waits for commands from the

PC host, allowing you to use the provided Flash loader utility program to download programs to

the Flash.

3-6

Page 31

HARDWARE OVERVIEW

If this text does not display o n the LED, indicat ing a probl em with th e jumper as sembly, the board

boots as if no Flash loader assembly is installed; that is, the Flash target program immediately

starts the loaded user application program (for example, the iRISM monitor software).

You can find complete instructions for using the Flash utility program in the CQI Flash Lo ad er

User Manual included in your kit.

3.3.2 SRAM (Static Memory)

SRAM occupies the lower 128 Kbytes of memory starting at location 00000H. This memory is

used by the processor for interrupt vectors and stack allocation, by the RISM for program

variables, and by the user for downloaded code. The board includes two 1-Mbit, 32-pin SRAMs

with 17 ns access time at 3.3 volts. SRAMs are socketed to allow installation of 5 V SRAMs

(17 ns access time).

To allow insertion of both the 80x186 processor and the 80x188 processor, the memory is

configured such that only 128 Kbytes of the SRAM is accessible, even though 256 Kbytes of

SRAM are installed on the board.

3.4 PROGRAMMABLE LOGIC

All glue logic re quired by t he evaluatio n board is impl emented on a GAL 22 LV10C-15. The PLD

file located on the floppy diskette in your kit includes logic equations for this device. The logic

implemented inclu des the following:

• Inverting the Port Pin signal controlling V

(so VPP is disabled at reset)

PP

• Controlling the 8-bit/16-bit configuration for the Flash device

• Decoding the Enable signal for the LCD display

3

3-7

Page 32

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

3.5 POWER SUPPLY

The power supply connects to J2 on the board schematic. Pin 1 must connect to +5 volts and pin

2 must connect to g rou nd. The sup ply is then re gul ated to 3. 3 vol ts by t he on-b oard ci rc uitry. The

V

for the board is controlled by jumper E1. When E1 is in the A–B position, VCC = 3.3 volts;

CC

when E1 is in the B–C position, V

= 5.0 volts. VCC is converted t o +12 v olts f or opt ional Flash

CC

programming voltage.

E1

A

B

C

A – B

B – C

VCC = 3.3 volts

VCC = 5.0 volts

A2607-01

Figure 3-3. E1 Jumper

The LCD display controller VCC pin connects directly to the 5 volt supply, not the VCC plane,

allowing 5 volt operation only.

21

+5VDC - V

Ground - V

CC

SS

Figure 3-4. J2 Power Connector

The Maxim* MAX750 component at U6 (EC) or U7 (EB) is a current-mode DC-DC converter.

This device takes the 5 volt supply and steps it down to 3.3 volts. This voltage output is always

supplied to provide V

for the processor, memory, and logic when selected at E1.

CC

3-8

Page 33

HARDWARE OVERVIEW

The Maxim MAX734 loc at ed at U11 is al so a cur rent-mode DC-DC conv er ter . T his device steps

up the V

voltage to +12.0 volts. This voltage output is supplied to provide a VPP option for

CC

Flash memory programming. The SHDN# input (pin 1) connects to a port pin (P1.1) on the

processor through an inverter. At reset, SHDN# is driven low to disable the +12 volt signal. The

output remains disabled until Port Pin 1.1 is programmed to a logic 0. When SHDN# is low, the

output (pin 8) is V

minus a diode drop. The evaluation board uses SmartVoltage Flash. To

CC

prevent unintentional writes to Flash, set jumpers E2 and E3 as indicated in Table 3-1.

3.6 SERIAL INTERFACE

Connector P1 c onne ct s t o yo ur PC’s serial por t. P1 i nt erf aces pin-to-p in wit h a st andard nine-pin

RS-232 serial connector. Verify that the cable being used provides all signals required.

Table 3-3. P1 Host Serial Connector

P1 Connector

1234 5

6

78

9

Pin

Nos.

1 (CF) DCD Data Carrier Detect DTR P1-pin 4

2 (BB) RxD Receive Data TxD of MAX561

3 (BA) TxD Transmit Data RxD of MAX561

4 (CD) DTR Data Terminal Ready INIT

5 (AB) SG Signal Ground Digital Ground

6 (CC) DSR Data Set Ready DTR P1-pin4

7 (CA) RTS Request To Send CTS P1-pin8

8 (CB) CTS Clear To Send RTS P1-pin7

9 (CE) RI Ring Indicator Run Indicator

Host RS-232

Signal Name

Connection on

Evaluation Board

Connector P2 is an additional serial port for user applications. Receive, Transmit, and Clear-toSend are connected. Other connector pins are routed to test points on the board.

3

3-9

Page 34

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

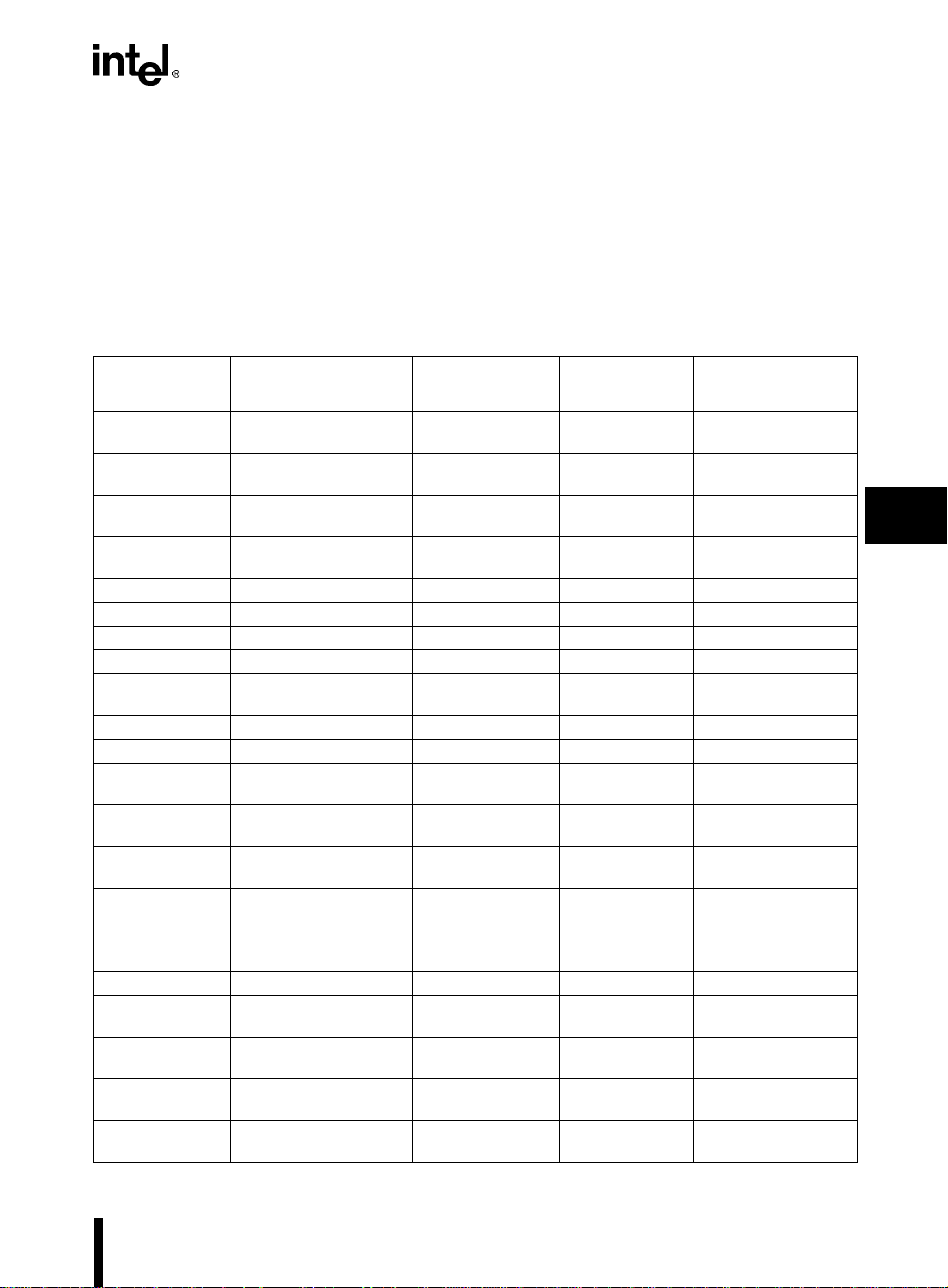

Table 3-4. P2 Serial Channel 0

P2 Connector

1234 5

6

78

9

Pin

Nos.

1 (CF) DCD Data Carrier Detect Test Point 1

2 (BB) RxD Receive Data RxD

3 (BA) TxD Transmit Data TxD

4 (CD) DTR Data Terminal Ready Test Point 4

5 (AB) SG Si gnal Ground Digital Ground

6 (AB) DSR Data Set Ready Test Point 2

7 (CD) RTS Request To Send Test Point 3

8 (BA) CTS Clear To Send CTS

9 (BB) RI R ing Indicator Test Point 5

Host RS-232

Signal Name

Connection on

Eval uation Board

The two serial connectors are connected to the Maxim MAX561, an EIA/TIA-562

Driver/Rece iver. Th is devi ce ope rates from a 3.3 volt V

(or 5 volts, o pti onall y). The E IA/ TIA-

CC

562 standard is a low voltage serial communications protocol. This protocol operates at ±3.7

volts. The 3.3 volt signals from the board are charge-pumped to ±6.6 volt levels internally,

conforming t o t hi s s ta ndard. Signals from the seria l conn ect or s, P 1 and P2, are tr ans la te d t o a 3.3

volt level. Output from this device is recognized by EIA/TIA-232-D receivers, and inputs can

handle EIA/TIA-232-D levels without damaging the device. The MAX561 SHDN pin (pin 25)

connects to port pin 1.0 on the 80x186 processor. When this pin is programmed to a logic 1, the

Maxim device will go into shutdown mode, reducing current consumption to leakage. During

initialization, port pin 1.0 is programmed t o a l ogi c 0 to enable communi ca ti on wi th the host PC.

Serial communications on the evaluation board are controlled by the 80x186 processor on-chip

serial ports. Serial Port 0 on the microprocessor handles PC communications via connector P1.

Serial Port 1 is available for user applications via connector P2. The 80x186 processor supports

synchronous serial communications as well as various modes of asynchronous communications.

The time base for the host interface is a 6.0 MHz oscillator connected to BCLK0, the external

serial clock i nput on the 80 x186 process or. This al lows the use r to change t he process or oper ating

frequency without altering the baud rate.

NOTE

The BCLK0 input must be less than half the processor operating frequency

(which is half the clock input frequency). Operating the processor below

12.288 MHz requires reprogramming the serial control unit on the 80x186

processor. The source code for the RISM monitor is provided on a floppy

diskette included in your kit for this purpose.

Figure 3-5 on page 3-11 illustrates the adaptor cable needed if your PC has a 25-pin serial port

connector.

3-10

Page 35

To Evaluation Board

DCD

1

DSR

6

RXD

2

RTS

7

TXD

3

CTS

8

DTR

4

RI

9

GND

5

P1

Note:

Signal mnemonics are referenced to the host.

HARDWARE OVERVIEW

To Host PC

Shield Ground

TXD

RXD

RTS

CTS

DSR

GND

DTR

DCD

1

14

2

15

3

16

4

17

5

18

6

19

7

20

8

21

9

22

RI

10

23

11

24

12

25

13

3

Figure 3-5. 25-Pin to 9-Pin Adaptor

A2343-02

3-11

Page 36

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

3.7 EXPANSION INTERFACE

There are two expansi on conne ctors on the evalua tion b oard. Ref er to the schemat ics in clude d on

a floppy diskett e in your ki t for repr esentat ion of the co nnector pi nouts. The 60- pin JP1 conn ector

(Figure 3-7) provides latched address pins and the address/data bus signals. This connector also

provides access to all bus-control signals, programmable chip-selects, +3.3 volts, +5 volts, and

+12 volts. The JP2 connector provides access to on-chip peripherals of the 80x186 processor.

This connector allows access to interrupt inputs, timer inputs and outputs, port pins, CLKOUT,

RESOUT, +3.3 volts, +5 volts, and +12 volts. The JP2 connector contains 40 pins for the EC

processors (see Figure 3-6) and 24 pins for the EB processors (see Figure 3-7).

NOTE

3.3 volts is available on the connector only when jumper E1 selects VCC = 3.3

volts; otherwise, these pins are 5 volts. +12 volts is available on the connector

only when Port Pin 1.1 is programmed to a logic 0; otherwise, these pins are

V

minus a diode drop.

CC

..............................

V

SS

T1IN.............................

V

..............................

CC

INT0.............................

INT1.............................

INT2.............................

INT3.............................

INT4.............................

INT5.............................

INT6.............................

INT7.............................

INTA#...........................

V

...............................

SS

DRQ0...........................

DRQ1...........................

DRQ2...........................

DRQ3...........................

V

...............................

SS

GCS6#..........................

GCS7#..........................

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

2 - T1OUT

4 - T0OUT

6 - V

CC

8 - P3.0

10 - P3.1

12 - P3.2

14 - P3.3

16 - P3.4

18 - P3.5

20 - WDTOUT#

22 - V

SS

24 - BCLK0

26 - P2.3

28 - RXD1

30 - TXD1

32 - P2.6

34 - CTS1#

36 - V

SS

38 - +5VDC

40 - +12VDC

Figure 3-6. 186 EC Peripheral Expansion Connector JP2 (40 pin)

3-12

Page 37

HARDWARE OVERVIEW

............

V

CC

T1OUT.......

T0OUT.......

V

.............

SS

P2.2............

P2.3............

BCLK0........

P2.6............

P2.7............

V

.............

SS

+5V.............

+12V...........

1

3

5

7

9

11

13

15

17

19

21

23

2 - V

CC

4 - T0IN

6 - T1IN

8 - V

SS

10 - INT0

12 - INT1

14 - INT2

16 - INT3

18 - INT4

20 - V

SS

22 - GCS6#

24 - GCS7#

Figure 3-7. 186 EB Peripheral Expansion Connector JP2 (24 pin)

3

3-13

Page 38

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

JP1 Memory - I/O Expansion Connector

2x30 Pin Molex* 39-51-6004 or Equivalent

..............................

V

CC

LA0 Output..................

LA1 Output..................

LA2 Output..................

LA3 Output..................

LA4 Output..................

LA5 Output..................

LA6 Output..................

LA7 Output..................

V

..............................

SS

LA8 Output..................

LA9 Output.................

LA10 Output................

LA11 Output................

LA12 Output................

LA13 Output................

LA14 Output................

LA15 Output................

V

...............................

SS

LA16.............................

LA17............................

LA18...........................

LA19...........................

RD#............................

WR#............................

BHE#..........................

RESOUT.....................

DEN#...........................

DT-R#.........................

V

..............................

SS

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

2 - V

CC

4 - D0 Bidirectional

6 - D1 Bidirectional

8 - D2 Bidirectional

10 - D3 Bidirectional

12 - D4 Bidirectional

14 - D5 Bidirectional

16 - D6 Bidirectional

18 - D7 Bidirectional

20 - V

SS

22 - D8 Bidirectional

24 - D9 Bidirectional

26 - D10 Bidirectional

28 - D11 Bidirectional

30 - D12 Bidirectional

32 - D13 Bidirectional

34 - D14 Bidirectional

36 - D15 Bidirectional

38 - V

SS

40 - HLDA

42 - HOLD

44 - READY Input

46 - ALE

48 - LOCK#

50 - NMI

52 - GCS5#

54 - +12 VDC

56 - +5 VDC

58 - CLKOUT

60 - V

SS

3-14

Figure 3-8. CPU Bus Expansion (EB and EC)

Page 39

HARDWARE OVERVIEW

3.8 LCD INTERFACE

The evaluation board includes a 16-character by 1-line LCD display. The display has an 8-bit

interface and is de signed to o perat e at up to 20MHz. The displa y inc lud es a Hitach i* 447 80 LCD

display cont roll er th at tak es car e of funct ions s uch as char acte r inte rp retat ion an d displ ay ref resh.

The display i s write-only. T his i s b eca use the displ ay cont ro ll er operates a t 5 v olt s V

part driving a 3.3-volt bus can damage parts operating at 3.3 volts V

. This means that the

CC

. A 5-volt

CC

BUSY pin of the processor can not be monitored to det er mine when the pr oc essor is rea dy for t he

next command, so a delay loop must be used to allow the display to finish commands.

Signals from the 80x186 processor can be connected directly to the LCD controller inputs,

regardless of V

, because 3.3 volt and 5 volt outputs are compatible with 5 volt TTL level

CC

inputs.

The LCD display is mapped in I/O space at 400H to 440H. All command and data writes to the

display are t o this addre ss. Port pin 1.4 is used to c ontrol whi ch LCD regis ter is acc essed. P1.4= 0

accesses the command register; P1.4 = 1 accesses the data register.

3.8.1 LCD Interface Demo

The diskette provided in your kit includes a file, LCD_DEMO.ASM, that contains source code

you can assemble and load onto the board (using iECM). You can execute the program for a

demonstration of the basic principals of operating the LCD display module. This program prints

a static message to the display. The source code is commented to serve as a tutorial and can be

adapted as needed for other applications and messages. Note that although the LCD module is

capable of displaying standard ASCII (characters 32 through 125) or custom characters, this

demo uses only ASCII characters.

For more infor mat ion re gardin g t he opera tion o f the d is play co ntrol le r, ple ase re fer to th e Hitac hi

LCD Controller/Driver LSI Data Book.

3

3-15

Page 40

Page 41

Introduction to the

Software

4

Page 42

Page 43

CHAPTER 4

INTRODUCTION TO THE SOFTWARE

The Intel 186 EC/ EB Eva luation Board us es an Embedd ed Contr oller M onitor ( ECM) wr itte n for

the 80x186 family of 16-bit microprocessors. This monitor supports basic debug facilities

(LOAD, GO, STEP, etc.) in the user’s target system. The ECM is broken into two independent

programs. One of these (iRISM-186) executes in the evaluation board and the other (iECM-86)

executes in an IBM PC or BIOS-compatibl e c om put er . These two programs communicate via an

asynchronous serial channel using a binary protocol defined specifically for this application.

The partitioning of the ECM into two separate programs supports a number of goals:

• The system is easy to adapt to a new target because the code that runs in the target is very

simple and small.

• The feature set of the user interface is not limited by the resources of the target, since the

user interfa ce is impl em ent ed in the host PC .

• Concurrent operation of the ECM and the target system is easily achieved. This allows you

to interrogate and (carefully) modify the state of the target system while it is running.

This chapter descri bes the us er inter face provided b y the i ECM-86, the interf ace betw een this PCresident software and the target-resident software, and the structure of the software in the target.

The board uses the internal 80x186 EB/EC serial port for host communications.

4

The iECM-86 software was created by Intel to support users of the 80x186 architecture and is

placed in the public domain with no restrictions or warranties of any kind.

4.1 SOFTWARE FEATURES

The iECM-86 software has the following features:

• Sixteen software execution breakpoints

• Concurrent interrogation of target memory and registers

• Supports BYTE, CHARACTER, WORD, STRING, DOUBLE WORD, and REAL variable

types

• Supports LOAD, SAVE, LIST, LOG, and command INCLUDE files

4-1

Page 44

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

4.2 RESTRICTIONS

Two words of the user stack are reserved for use by the iRISM-186 software. Other memory

and/or regi ster s in th e targ et me mory are use d by the iRI SM-186 softwa re. The exac t amo unt and

location of this memory is implementation-dependent.

An asynchronous serial port capable of operation at 9600 baud must be available in the target

system. The RISM described in this document uses the 80x186 EB/EC internal serial port.

The TRAP instruction is reserved.

Breakpoints and program stepping will not operate if the user’s code is in Flash or other

nonchangeable memory.

4.3 EMBEDDED CONTROLLER MONITOR (ECM)

An ECM (Embedded Controller Mon itor) is installe d in your target system to pr ovide basic debug

capability. Capabilities include lo ading object files into system RAM, examin ing and modifying

variables, executing code, and stepping through code. A personal computer acts as the host for

program translation and emulates a video display during user interaction with the ECM. The

ECM developed f or the 80x186 famil y makes the assumpt i on t ha t t he user interface is a person al

computer; no provision is made for interface to a CRT terminal. By making this assumption, it is

possible to re duc e t h e s iz e an d com p lexity of the c ode t hat must be inst alled in the t arget system.

The term coined for this target-resident code is Reduced Instruction Set Monitor (RISM).

The RISM consists of about 2200 bytes of 80x186 code that provides primitive operations.

Software running in the host uses the RISM commands to provide a complete user interface to

the target system. The advantage of this approach is that the ECM can be readily adapted to

different tar g et sys tems and requires only a sma ll par t of t he available targ et mem or y space. The

disadvantage is that the user interface must be provided by a personal computer.

RISM is structured as a short section of initialization code and an interrupt service routine (ISR).

The ISR processes interrupts from the host system. The RISM ISR consists of a short prologue

and a case-jump to one of 20 to 25 command executors. These executors are simple and short;

the flow though the e nti re ISR (i nc luding the prologue) is 15-20 instructi ons. The serial communication occu rs at 96 00 baud, which li mits the frequenc y of the se inter rupts t o 1 KHz. In the worst

case, the board will be slowed by the execution of a fairly short RISM ISR every millisecond

while executing user code. It is possible to operate the board so that no real time is lost to the

iECM-86 unless the user is actively interrogating the target. See “Initiating and Terminating

iECM-86” on page 4-3 and the description of the RISM REPORT_STATUS code (Code 14H)

on page 6-5 for details.

4-2

Page 45

INTRODUCTION TO THE SOFTWARE

4.4 USER INTERFACE

The user interface to the iECM-86 supports commands to initiate and configure the ECM-86,

perform I/O operations involving DOS files, execute user programs, and interrogate variables in

the target sy stem. Inter rogation can be done in a numb er of format s and in most case s can be done

concurrently with user code execution.

4.4.1 Numeric Input

The command parser used by the iECM-86 software requires that numeric inputs always start

with the digits 0-9. Hexadecimal numbers that start with A–F must be preceded by a zero. For

example, enter “0AA55” instead of “AA55.” This requirement is similar to that of ASM86.

4.4.2 Controlling Lengthy Commands

Most of the commands supported by iECM-86 appear to complete without delay. Some

commands (f or exa m ple , d isp laying or fil l ing a large area of memory) t ake an appreciable l en g th

of time to complete. In general, these commands can be aborted by pressing Enter. Those

commands that display a large amount of information can be paused by pressing the spacebar.

After you have checked the data on the screen, you can press the spacebar again to resume the

output.

4

4.4.3 Aborting from iECM-86

Press Ctrl+C to close any open files and return to DOS.

4.5 INITIATING AND TERMINATING iECM-86

This section descri bes t he command s for invoki ng iECM -86 f rom DOS and exit ing ba ck to DOS.

4.5.1 ECM86

This command, entered at t he D OS p rom pt , l oads the iECM-86 software and e xecutes it. Se ver al

options are available with this command. Option strings always start with a hyphen (-) and can

be entered in upper or lower case. The operation of these options is described below. Any or all

of these options can be entered in any order. If the options are contradictory, the actual option

accepted is the last one entered.

4-3

Page 46

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

4.5.2 -COM2, -COM1

These options tell the iECM -86 softwa re which ser ial communic ation port is to be use d. If neith er

option is entered, COM1 is used as a default. If iECM-86 detects valid CTS (Clear to Send) and

DSR (Data Set Ready) signals from the appropriate COM port, it signs on and displays a

command prompt. When the target is stopped, the command prompt is an asterisk (*). When the

target is already running, the prompt is a greater-than sign (>).

4.5.3 -DIAG

If CTS and DSR are not present, iECM-86 displays a warning message. You can choose to

proceed or exit. It is possible, but not likely, that iECM-86 will operate properly even after the

warning. It is more likely that ther e is a prob lem with the serial port or th e cabling that preve nts

proper operation.

If the problem is not obvious, such as a disconnected cable or no power to the target hardware,

use the -DIAG invocation option to help isolate the problem. The -DIAG option puts the iECM86 system in a special mode that allows many tests to be used to find interfacing problems or

target bugs.

The diagnostic mode is intended to support debugging of boards that use iECM-86 software. It

also provides a simple routine to check the communications interface between the host and the

target.

In the board , a seri al por t loo p-back mo de all ows de buggin g the ho st/bo ard inter face. Upon res et,

the board is in the echo mode. Until it receives an ASCII slash (/) or backslash (\), it increments

every character it receives from the host and sends the incremented value back to the host. The

LCD dis plays the word “DIAGNOSTICS” when the board is in echo mode. If a backslash is

received by the RISM, the board leaves echo mode and starts normal operation. When a slash is

received, the board stops echoing incremented received data and starts responding to RISM

commands with the diagnostic flag set.

NOTE

The target hardware has to be reset before using the -DIAG option. When

executing diagnostic routines from Flash, certain commands such as

breakpoints and stepping will not work because they need to modify the code

to work properly.

When the host software is invoked in the diagnostic mode, it prompts you to enter characters on

the keyboard. Thes e charac ters are sen t to the target , and the res ponse from the ta rget i s displayed

on screen. This is a simple confidence check on the serial communication channel. You are told

to enter a slash or backslash to terminate this mode and proceed in either the diagnostic mode or

the normal user’s mode. If the user interface is invoked without the -DIAG option, the software

immediately transmits a reverse-slash, which should put the target in the normal mode.

4-4

Page 47

INTRODUCTION TO THE SOFTWARE

4.5.4 -POLL, -SIGNAL

These two options contr ol how the host software detects whether or not the user’s code is running.

If poll mode is selected, the host periodically polls the target with a REPORT_STATUS

command. This takes no additional hardware, but it forces the target to spend instruction cycles

responding t o the p oll. The si gnal m ode av oids t hi s overh ead, but it requi res t hat t he tar get se t t he

Ring Indicator modem line before it issues a REPORT_STATUS command. If neither option is

selected, the s ig nal mo de i s s elect ed as a default. On the boar d, t he P1.3 pin of 80x186 p roc ess or

is used to generate this running signal. Therefore, the signal mode is recommended. (The

REPORT_STATUS command is described on page 6-5.)

4.5.5 RESET SYSTEM, RES SYSTEM, RESET, RES

This command and its abbreviations reset the entire target hardware system. This command

operates by dropping the DTR modem control line. This comes into the target as DSR. After

dropping DTR, the iECM-86 software waits about 1 second to allow the target to complete its

initiali zation r outines. The iECM -86 warns of this time dela y and th en ignores input fr om the ho st

PC until it e xpi res. Unless spe ci al pr ecautions are taken in the design of a ta rge t system, any da ta

in RAM (including downloaded object code) may be corrupted by the reset. On the board, the

RAM contents should not be affected by a reset.

4

4.5.6 DOS

This command enables you to temporarily leave iECM-86 and return to DOS. Once you have

suspended iECM-86, you may perform other functions in DOS, including using other software

programs such as ASM86, as long as there is sufficient memory to do so.

To re-enter i ECM-86, type exi t at the DOS prompt. i ECM-86 retur ns with all condi tions that were

in effect at the time it was suspended.

4.5.7 QUIT

This command closes any files that iECM-86 has opened and exits to DOS. Note that this

command can b e u sed eve n if the targ et is r unni ng. iECM -8 6 s ets the selec ted COM por t to 9600

baud, 8 bits, no parity and one stop bit. The port is left in this state by iECM-86 when control is

returned to DOS.

4-5

Page 48

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

4.6 RELATED INFORMATION

All unreser ved funct ions of the pr ocessor a re avail able to you, exc ept the Non-Maskab le In terrupt

(NMI), the Breakpoint instruction (INT 3), the Trap Flag (TF), 16 Kbytes of address space, and

128 bytes of I/O space.

4.6.1 Reserved Functions

The Trap Flag and its vector in memory locations 4H–7H are reserved for use by the SSTEP

command and BREAKPOINTS.

The NMI pin and its vector in memory locations 8H–0BH are reserved for use by the host

interface.

The INT 3 instruction and its vector in memory locations 0CH–0FH are reserved for use by the

SSTEP command and BREAKPOINTS.

4.6.2 Reserved Memory

On-board Flash memory, as shipped, is 32 Kbytes from address 0H to 7FFFH.

Addresses 0H–3FFH are the interrupt vectors for the processor.

You must not alter the interrupt vectors from 4H–0FH.

Memory locations 400 H–415H a re reserv ed for us e by the RI SM monitor c ode. You must ensu re

that no locations in this partition are used by code that is to operate with the RISM. The easiest

way of doing this is to generate an ASM-86 module that declares a DATA SEGMENT at 400H

that is 22 bytes long. This module can then be linked into the final program to prevent the linker

from assigning these registers to another module.

Fourteen words of user stack space must be reserved for use by the iRISM-186 software while

the board is processing a host interrupt. The CS:SP register pair is initialized by RISM to

0000H:0800H, providing a total stack size of 501 words before RISM data variables are

overwritten. If this is insufficient for your application, your code should alter the SP to a large

enough value. Normally, you should write your code to begin at address 800H and download it

to Flash memory using iECM-86. You should use any space left beneath your code as data

memory.

4.6.3 Reserved I/O

The I/O space from 400H–47FH is reserved for use by the host interface.

4-6

Page 49

iECM-86 Commands

5

Page 50

Page 51

This chapter defines the iECM-86 software commands.

5.1 ENTERING COMMANDS

The syntax for iECM commands is shown below:

COMMAND

metasymbol

CHAPTER 5

iECM-86 COMMANDS

iECM-86 command definitions use one or more of the following metasymbols:

addr

address iECM-86 is able to interpret the microprocessor’s address space as

either a flat 20-bit array or through segmentation. A location

anywhere within the 1 Mbyte memory range may be specified by its

complete physical address, such as 0F1AC9H.

segment:offset Memory may also be accessed by segments. Valid segment

references are the following (where segment and offset are valid

integers):

CS:offset

DS:offset

ES:offset

SS:offset

When using CS, DS, ES or SS, the full address i s c al cul at ed u si ng t he

actual value of the appropriate target processor segment register.

In addition to the above registers, iECM-86 maintains four userdefinable registers that may be used for segment variables:

CB:offset

DB:offset

EB:offset

SB:offset

5

This faci lity is useful w hen reading f rom assembler listings, wh ich

are typically offset from 0000. These base registers are used, for

example, as a base pointer to a block of memory for debug purposes.

CB could be loaded with the base address of a code module, then

breakpoints could be set using offsets from that base. Using these

internal iECM registers has no effect on the values of the target

processor's registers.

5-1

Page 52

INTEL 186 EB/EC EVALUATION BOARD USER’S MANUAL

bp_number Sixteen breakpoints are available to the user. This number selects

which breakpoint to access.

code_addr The code address may be specified by either segment: offset,

CS:offset, or CB:offset.

count This denotes the number of times a command executes.

filename This is the location (path) and name of the file you want to reference

(e.g., \progdir\program.obj).

value Data to be entered in the current base notation.

5.2 FILE OPERATIONS

iECM-86 uses f il es in the host sy st em to load and sav e o bject code, to ent er pr edef ined strings of

commands, to keep a log of commands that are entered by the user, and to keep a record of an

entire debug session that includes both the characters entered by the user and the responses

generated by i E CM-86 on the host s cr een. The commands th at operate with fi le s are descri bed in

the following sections.

5.2.1 Loading and Saving Object Code

iECM-86 accepts object files that are generated by Intel’s development tools. iECM-86 will not

accept file s that conta in unresolv ed external s or files that contai n re-locat able re cords. These files

must be passed through LINK86 and/or LOC86 to resolve the externals and/or absolutely locate