Page 1

Intel® 80331 I/O Processor

Design Guide

March 2005

Order Number:273823-003

Page 2

Intel® 80331 I/O Processor Design Guide

Contents

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DO CUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUM ES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/ OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING T O FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT.

Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling1-800-548-

4725, or by visiting Intel's website at http://www.intel.com.

AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Connect, CT Media, Dialogic, DM3, EtherExpress,

ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share,

Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel

SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, LANDesk, LanRover, MCS, MMX, MMX

logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your

Command, RemoteExpress, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside,

TokenExpress, Trillium, VoiceBrick, Vtune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United

States and other countries.

The ARM* and ARM Powered logo marks (the ARM marks) are trademarks of ARM, Ltd., and Intel uses these marks under license from ARM, Ltd.î

*Other names and brands may be claimed as the property of ot hers.

Copyright© Intel Corporation 2002

2

Page 3

Intel® 80331 I/O Processor Design Guide

Contents

Contents

1 Introduction..................................................................................................................................11

1.1 About This Document ..................................... ...... ...... ....... ...... ....... ...... ....... .......................11

1.1.1 Terminology and Definitions ..................................................................................12

1.1.2 Other Relevant Documents ...................................................................................14

1.2 About the Intel

2 Package Information ...................................................................................................................17

2.1 Power Plane Layout............................................................................................................21

2.2 Intel

3Terminations................................................................................................................................23

3.1 Analog Filters......................................................................................................................27

3.2 DDR Resistor Compensation..............................................................................................28

3.3 DDR Driver Compensation .................................................................................................29

4 Routing Guidelines......................................................................................................................31

4.1 General Routing Guidelines................................................................................................31

4.2 Crosstalk.............................................................................................................................32

4.3 EMI Considerations ............................................................................................................34

4.4 Power Distribution and Decoupling.....................................................................................34

4.5 Trace Impedance................................................................................................................36

®

80331 I/O Processor Applications.............................................................................22

3.1.1 V

4.4.1 Decoupling.............................................................................................................34

®

80331 I/O Processor.................................................................................15

Pin Requirements......................................................................................27

CCPLL

5 Board Layout Guidelines............................................................................................................37

5.1 Motherboard Stack Up Information.....................................................................................37

5.2 Adapter Card Stackup .......... ...... ....... ...... ....... ...... ...... ....... ...... ....... ...... ....... ...... ....... ..........39

6 PCI-X Layout Guidelines.............................................................................................................41

6.1 Interrupt Routing and IDSEL Lines.....................................................................................41

6.1.1 PCI Arbitration .......................................................................................................42

6.1.2 PCI Resistor Compensation ..................................................................................42

6.2 PCI General Layout Guidelines..........................................................................................43

6.3 PCI-X Topology Layout Guidelines.....................................................................................43

6.4 Intel

®

80331 I/O Processor PCI/X Layout Analysis ............................................................44

6.4.1 PCI Clock Layout Guidelines .................................................................................45

6.4.2 Single-Slot at 133 MHz ..........................................................................................48

6.4.3 Embedded PCI-X 133 MHz ...................................................................................49

6.4.4 Embedded PCI-X 133 MHz Alternate Topology ....................................................50

6.4.5 Combination of PCI-X 133 MHz Slot and Embedded Topology ............................51

6.4.6 Combination PCI-X 133 MHz Slot and Embedded Topology 2 .............................52

6.4.7 PCI-X 100 MHz Slot Topology...............................................................................53

6.4.8 PCI-X 100 MHz Embedded Topology....................................................................54

6.4.9 PCI-X 100 MHz Slot and Embedded Topology......................................................55

6.4.10 PCI-X 100 MHz Slot and Embedded Topology 2...................................................56

6.4.11 PCI-X 66 MHz Slot Topology.................................................................................57

6.4.12 PCI-X 66 MHz Embedded Topology......................................................................58

6.4.13 PCI-X 66 MHz Mixed Mode Topology....................................................................59

3

Page 4

Intel® 80331 I/O Processor Design Guide

Contents

6.4.14 PCI 66 MHz Slot Topology ....................................................................................60

6.4.15 PCI 66 MHz Embedded Topology.........................................................................61

6.4.16 PCI 66 MHz Mixed Mode Topology.......................................................................62

6.4.17 PCI 33 MHz Slot Topology ....................................................................................63

6.4.18 PCI 33 MHz Embedded Mode Topology...............................................................64

6.4.19 PCI 33 MHz Mixed Topology.................................................................................65

7 Memory Controller.......................................................................................................................67

7.1 DDR Bias Voltages.............................................................................................................67

7.2 Intel

®

80331 I/O Processor DDR Overview ........................................................................68

7.3 DDR 333 Signal Integrity Simulation Conditions ................................................................69

7.3.1 DDR 333 Stackup Example...................................................................................70

7.4 DDR Layout Guidelines ......................................................................................................72

7.4.1 Source Synchronous Signal Group .......................................................................72

7.4.1.1 Routing Requirements...........................................................................73

7.4.2 Clock Signal Groups............................. ...... ............................................. ....... ...... .81

7.4.2.1 Control Signals Termination...................................................................85

7.4.3 Embedded Configuration.......................................................................................89

7.4.3.1 DDR 333 Source Synchronous Routine Guidelines ..............................89

7.4.3.2 DDR 333 Embedded Clock Routing Recommendations .......................92

7.4.3.3 DDR 333 Embedded Address/Command/Control Routing Guidelines..96

7.5 DDR II 400 Layout Guidelines..........................................................................................101

7.5.1 Simulation Conditions..........................................................................................102

7.5.2 DDRII-400 Trace Width/Impedance Requirements .............................................103

7.5.3 DIMM Layout Design ...........................................................................................104

7.5.3.1 DDR II 400 DIMM Source Synchronous Routing.................................104

7.5.3.2 DDRII 400 Clock Routing Guidelines...................................................107

7.5.3.3 DDRII 400 Address/Command/Control Routing Guidelines ................108

7.5.4 Embedded Configuration.....................................................................................110

7.5.4.1 DDRII 400 Embedded Source Synchronous Routine Guidelines........110

7.5.4.2 DDRII 400 Embedded Clock Routing Recommendations ...................113

7.5.4.3 DDRII 400 Embedded Address/Command/Control Routing Guidelines....

116

7.6 DDR Signal Termination...................................................................................................120

7.7 DDR Termination Voltage.................................................................................................121

7.8 DDR V

Voltage............................................................................................................121

REF

8 Peripheral Local Bus.................................................................................................................123

8.1 Peripheral Bus Signals .....................................................................................................123

8.1.1 Address/Data Signal Definitions..........................................................................123

8.1.2 Control/Status Signal Definitions.........................................................................123

8.1.3 Bus Width ............................................................................................................124

8.1.4 Flash Memory Support ........................................................................................125

8.1.5 Layout Guidelines for the Peripheral Bus............................................................126

8.2 Topology Layout Guidelines.............................................................................................127

9 Power Delivery...........................................................................................................................131

9.1 Power Sequencing............................................................................................................131

9.2 Power Failure....................................................................................................................132

9.2.1 Theory of Operation.............................................................................................132

9.2.2 Power Failure Sequence .....................................................................................132

9.2.3 Power Delay ........................................................................................................133

4

Page 5

Intel® 80331 I/O Processor Design Guide

Contents

9.3 Battery Backup ................................................................................................................. 134

9.3.1 Non-Battery Backup Circuits................................................................................135

10 Intel® IQ80331 Evaluation Platform Board..............................................................................137

11 JTAG Circuitry for Debug .........................................................................................................139

11.1 Requirements ...................................................................................................................139

11.2 JTAG Signals / Header.....................................................................................................140

11.3 System Requirements ... ............................................. ....... ...... ....... ...... ....... .....................141

11.4 JTAG Hardware Requirements.........................................................................................142

11.4.1 Macraigor Raven and WindRiver Systems visionPROBE / visionICE .................142

11.4.2 ARM Multi-ICE.....................................................................................................142

12 Debug Connectors and Logic Analyzer Connectivity............................................................143

12.1 Probing PCI-X Signals......................................................................................................143

13 References .................................................................................................................................147

13.1 Related Documents ..........................................................................................................147

13.2 Electronic Information................. ....... ...... ....... ............................................. ...... ....... ........148

5

Page 6

Intel® 80331 I/O Processor Design Guide

Contents

Figures

1Intel® 80331 I/O Processor Functional Block Diagram...............................................................16

2Intel

3Intel

4Intel

5Intel

6Intel

7V

8 Intel

®

80331 I/O Processor 829-Ball FCBGA Package Diagram................................................18

®

80331 I/O Processor Preliminary Ballout (Top View) .......................................................19

®

80331 I/O Processor Preliminary Ballout (Bottom View)..................................................20

®

80331 I/O Processor Power Plane Layout........................................................................21

®

80331 I/O Processor PCI-X Adapter Card Block Diagram ...............................................22

Configuration..................................................................................................................27

CCPLL

®

80331 I/O Processor DDRRES Resistor Compensation Circuitry...................................28

9 DDR Driver Compensation Circuitry...........................................................................................29

10 Crosstalk Effects on Trace Distance and Height........................................................................32

11 PCB Ground Layout Around Connectors ...................................................................................33

12 Motherboard Stackup Recommendations ..................................................................................38

13 Adapter Card Stackup .................................. ...... ....... ...... ...... ....... ..............................................40

14 Interrupt and IDSEL Mapping .....................................................................................................41

15 PCI RCOMP ...............................................................................................................................42

16 PCI Clock Distribution and Matching Requirements...................................................................45

17 Single-Slot Point-to-Point Topology.............. ...... ....... ...... ...... ....... ...... ....... .................................48

18 Embedded PCI-X 133 MHz Topology ........................................................................................49

19 Embedded PCI-X 133 MHz Alternate Topology.........................................................................50

20 Embedded PCI-X 133 MHz Topology ........................................................................................51

21 Embedded PCI-X 133 MHz Topology ........................................................................................52

22 Slot PCI-X 100 MHz Slot Routing Topology...............................................................................53

23 Embedded PCI-X 100 MHz Routing Topology...........................................................................54

24 Combination of Slot and Embedded PCI-X 100 MHz Routing Topology....................................55

25 Combination of Slots and Embedded PCI-X 100 MHz Routing Topology..................................56

26 PCI-X 66 MHz Slot Routing Topology ........................................................................................57

27 PCI-X 66 MHz Embedded Routing Topology.............................................................................58

28 PCI-X 66 MHz Mixed Mode Routing Topology...........................................................................59

29 PCI 66 MHz Topology ................................................................................................................60

30 PCI 66 MHz Embedded Topology..............................................................................................61

31 PCI 66 MHz Mixed Topology......................................................................................................62

32 PCI 33 MHz Slot Routing Topology............................................................................................63

33 PCI 33 MHz Embedded Mode Routing Topology.......................................................................64

34 PCI 33 MHz Mixed Mode Routing Topology ..............................................................................65

35 100 ohm Differential Trace .........................................................................................................71

36 Source Synchronous Length Matching.......................................................................................73

37 Data Group Length Matching .....................................................................................................73

38 DIMM DQ/DQS Topology...........................................................................................................79

39 DIMM DQ/DQS Split Termination Topology...............................................................................80

40 DDR 333 Registered DIMM Clock Topology..............................................................................83

41 DDR 333 Unbuffered DIMM Clock Topology..............................................................................84

42 Trace Length Requirements for Source Clocked Routing ..........................................................85

43 DDR 333 DIMM Unbuffered/Registered Address/CMD Topology Lengths................................87

44 Embedded DDR 333 DQ/DQS Topology ...................................................................................91

45 Embedded DDR 333 Buffered Clock Topology..........................................................................92

46 Embedded DDR 333 Unbuffered Clock Topology......................................................................95

47 Embedded DDR 333 Unbuffered ADDR/CMD Topology ...........................................................98

48 Embedded DDR 333 Registered ADDR/CMD Topology..........................................................100

6

Page 7

Intel® 80331 I/O Processor Design Guide

Contents

49 Intel® 80331 I/O Processor DDRII 400 DIMM Source Synchronous Routing..........................104

50 DDR II 400 DIMM DQ Topology...............................................................................................106

51 DDR II 400 DIMM DQS Topology.............................................................................................106

52 DDR II 400 DIMM Clock Topology............................................................................................107

53 DDR II 400 DIMM Address/CMD Topology..............................................................................109

54 DDR II 400 DIMM Address/CMD Split Termination Topology ..................................................109

55 DDR II 400 Embedded DQ Topology .............. ....... ...... ...... ....... ...... ....... ..................................11 1

56 DDR II 400 Embedded DQS Topology.....................................................................................112

57 DDR II 400 Embedded Clock Topology....................................................................................115

58 DDR II 400 Embedded Address/Control Topology...................................................................118

59 DDR II 400 Embedded Address/Control Topology With Split Termination...............................119

60 Routing Termination Resistors (top view).................................................................................120

61 DDR V

Circuit......................................................................................................................121

REF

62 Data Width and Low Order Address Lines ............. ...... ...... .............................................. ...... ..124

63 Four MByte Flash Memory System ..........................................................................................125

64 Peripheral Bus Unlatched Bidirectional Single Load Topology.................................................127

65 Peripheral Bus Latched Bidirectional Single Load Topology....................................................128

66 Peripheral Bus Latched Bidirectional Two Load Topology.......................................................129

67 Power Failure Comparator Circuit ............................................................................................133

68 SCKE Circuit.............................................................................................................................134

69 Intel

70 Intel

®

IQ80331 Evaluation Platform Board CRB Block Diagram..............................................137

®

80331 I/O Processor CRB Form Factor..........................................................................138

71 JTAG Header Pin Out...............................................................................................................140

72 JTAG Signals at Powerup.........................................................................................................141

73 JTAG Signals at Debug Startup................................................................................................141

74 Example Power-Up Circuit for nTRST......................................................................................142

7

Page 8

Intel® 80331 I/O Processor Design Guide

Contents

Tables

1 Terminology and Definitions .......................................................................................................12

2 FC-style, H-PBGA Package Dimensions....................................................................................17

3 Terminations: Pull-up/Pull-down.................................................................................................23

4 Decoupling Recommendations.............. ....... ............................................. ...... ....... ...... ....... .......34

5 Motherboard Stack Up, Stripline and Microstrip.........................................................................37

6 Adapter Card Stack Up, Microstrip and Stripline ........................................................................39

7 PCI-X Slot Guidelines.................................................................................................................43

8 PCI-X Clock Layout Requirements Summary ............................................................................46

9 PCI-X 133 MHz Single Slot Routing Recommendations ............................................................48

10 Embedded PCI-X 133 MHz Routing Recommendations............................................................49

11 Embedded PCI-X 133 MHz Alternate Topology Routing Recommendations.............................50

12 Embedded and Slot PCI-X 133 MHz Routing Recommendations..............................................51

13 Embedded and Slot PCI-X 133 MHz Routing Recommendations..............................................52

14 PCI-X 100 MHz Slot Topology Routing Recommendations .......................................................53

15 PCI-X 100 MHz Embedded Routing Recommendations............................................................54

16 Combination of Slot and Embedded PCI-X 100 MHz Routing Recommendations ....................55

17 Combination of Slot and Embedded PCI-X 100 MHz Routing 2 Recommendations .................56

18 PCI-X 66 MHz Slot Routing Recommendations.........................................................................57

19 PCI-X 66 MHz Embedded Routing Recommendations..............................................................58

20 PCI-X 66 MHz Mixed Mode Routing Recommendations............................................................59

21 PCI 66 MHz Slot Table ...............................................................................................................60

22 PCI 66 MHz Embedded Table....................................................................................................61

23 PCI 66 MHz Mixed Mode Table..................................................................................................62

24 PCI 33 MHz Slot Routing Recommendations.............................................................................63

25 PCI 33 MHz Embedded Routing Recommendations .................................................................64

26 PCI 33 MHz Mixed Mode Routing Recommendations ...............................................................65

27 DDR Bias Voltages.....................................................................................................................67

28 DDR II Bias Voltage....................................................................................................................67

29 Core Speed and Memory Configuration.....................................................................................68

30 Simulated DDR 333 Topologies .................................................................................................69

31 Example Topologies for DDR Trace...........................................................................................71

32 x64 DDR Memory Configuration.................................................................................................72

33 x72 DDR Memory Configuration.................................................................................................72

34 Source Synchronous Termination Requirements.......................................................................73

35 Source Synchronous Routing Recommendations......................................................................74

36 DIMM DQ/DQS Topology Lengths.............................................................................................75

37 Die to Ball Internal Lengths ........................................................................................................75

38 DIMM DQ/DQS Split Termination Topology Lengths .................................................................80

39 DIMM Clocked Signal Group Termination..................................................................................81

40 Clock Signal Group Registered/Unbuffered DIMM Routing Requirements................................82

41 Registered DIMM Clock Topology Lengths................................................................................83

42 DDR 333 Unbuffered DIMM Clock Topology Lengths................................................................84

43 Source Clocked Signal Routing..................................................................................................85

44 Control Signals Routing Guidelines............................................................................................86

45 Control Signal DIMM Topology Lengths.....................................................................................88

46 DDR 333 Embedded Source Synchronous Routing Recommendations....................................89

47 Embedded DDR 333 DQ/DQS Topology Lengths......................................................................91

48 DDR 333 Embedded Registered/Unbuffered Clock Routing Recommendations.......................93

8

Page 9

Intel® 80331 I/O Processor Design Guide

Contents

49 Embedded DDR 333 Buffered Clock Topology Lengths ............................................................94

50 Embedded DDR 333 Unbuffered Clock Topology Lengths........................................................95

51 DDR 333 Embedded Address/Command Routing Recommendations ......................................96

52 Embedded DDR 333 Unbuffered Address/CMD Topology Lengths...........................................98

53 Embedded DDR 333 Registered Address/CMD Topology Lengths...........................................99

54 x64 DDR Memory Configuration...............................................................................................101

55 x72 DDR Memory Configuration...............................................................................................101

56 DDR II Topologies Simulated ...................................................................................................102

57 Example Topology for DDRII Trace Width/Impedance Requirem ent s ... ...... ....... ...... ....... ...... ..103

58 DDRII 400 DIMM Source Synchronous Routing Recommendations........................................105

60 DDR II 400 DIMM DQS Lengths...............................................................................................106

59 DDR II 400 DIMM DQ Lengths.................................................................................................106

61 DDRII 400 DIMM Clock Routing Recommendations................................................................107

62 DDR II 400 DIMM Clock Lengths..............................................................................................107

63 DDRII 400 DIMM Address/Command/Control Routing Recommendation ...............................108

64 DDR II 400 DIMM Address/CMD Lengths ................................................................................109

65 DDRII 400 Embedded Source Synchronous Routing Recommendations................................110

66 DDR II 400 Embedded DQ Lengths ....................... ...... ...... ....... ...... ....... ..................................111

67 DDR II 400 Embedded DQS Lengths.......................................................................................112

68 DDRII 400 Embedded Clock Routing Recommendations ........................................................113

69 DDR II 400 Embedded Clock (PLL) Lengths............................................................................114

70 DDRII 400 Embedded Address/Command/Control Routing Recommendations......................116

71 DDR II 400 Embedded Address/CMD Lengths ........................................................................117

72 Flash Wait State Profile Programming .....................................................................................125

73 Routing Guideline Bidirecti ona l Singl e Load .... ....... ...... ...... ....... ...... ....... ...... ............................12 7

74 Routing Guideline Latched Bidirectional Latch Single Load.....................................................128

75 Routing Guideline Latch Bidirectional Two Loads ....................................................................129

76 Intel

®

80331 I/O Processor Bias Voltages...............................................................................131

77 Four Peaks Customer Reference Board Features ...................................................................138

78 Logic Analyzer Pod 1................................................................................................................143

80 Logic Analyzer Pod 3................................................................................................................144

79 Logic Analyzer Pod 2................................................................................................................144

82 Logic Analyzer Pod 5................................................................................................................145

81 Logic Analyzer Pod 4................................................................................................................145

83 Logic Analyzer Pod 6................................................................................................................146

84 Design References ...................................................................................................................147

85 Intel Related Documentation ....................................................................................................147

86 Electronic Information...............................................................................................................148

9

Page 10

Intel® 80331 I/O Processor Design Guide

Contents

Revision History

TaTa

Date Revision Description

March 2005 003 Updated Figure 27, Figure 33, and Figure 49.

October 2004 002

September 2003 001 Initial Release.

In Chapter 6:

Table 8: added row Preferred Topology: stripline

Table 8: changed Clock Layout Requirements Add-in card

impedance from 60 ohms to 57 ohms.

Changed topology information in Figure 24 and Table 16.

Table 17 Added alternate PCI-X 100MHz Slot and Embedded

Topology Figure 25 and Table 16.

Table 18 Changed Add-in card impedance from 60 ohms +/-

15% to 57 ohms +/- 15%.

In Chapter 7:

DDR 333 Source Synchronous recommendations removed the

requirement for length matching for DQS groups based on

simulations

Removed row in Table 48 “Length Matching Requirements:

between clock groups”. This is required only for unbuffered

clocks and was already mentioned in the previous row.

Table 51: removed row in “Trace Length: 80331 signal Ball to

Series Term ination” because the series termination is no

longer needed.

Table 52: Removed Rout ing Guideline 4 because unbuffered

and registered DIMM’s have the same topology.

Deleted Figure 57 because simulations showed that series

resistors is no longer needed for DDR 333 DIMM control

signals

Table 53: Removed Lengt h Matching within DQS group

recommendation now because length matching will happen

when matching to M_CK.

Changed Embedded DDR 333 DQ/DQS Topology Figure 44

resistor listed as 50 ohms +/- 5% to 51 ohms +/- 5% because

this is a standard value resistor.

In Chapter 9

Removed VCC25/VCC18 from the power up sequence order

and added a note stating that there is no sequence order

requirements for the VCC25 or VCC18 rail.

Other:

Moved the decoupling guidelines from Chapter 3 to Chapter 4.

Removed reference to the Hot Plug controller. This feature is

not part of the 80331 product.

10

Page 11

Intel® 80331 I/O Process or Design Guide

Introduction

Introduction 1

1.1 About This Document

This document provides layout information and guidelines for designing platform or add-in bo ard

applications with the Intel

It is recommended that this document be used as a guideline. Intel recommends employing

best-known design practices with board level simulation, signal integrity testing and validation for

a robust design.

Designers please note that this g uide focu ses upo n sp ecific design cons iderations fo r the 8 0331 and

is not intended to be an all-inclusive list of all good design practices. Use this guide as a starting

point and use empirical data to optimize your particular design.

Intel Corporation assumes no responsibility for any errors which may appear in this document nor

does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice. In

particular, d escri p t ions of f eatu res, t i mings , pack aging , and pin-outs does not imply a commitment

to implement them. In fact, this specification does not imply a commitment by Intel to design,

manufacture, or sell the product described herein.

®

80331 I/O processor (80331), which is ARM* architecture compliant.

11

Page 12

Intel® 80331 I/O Process or Design Guide

Introduction

1.1.1 Terminology and Definitions

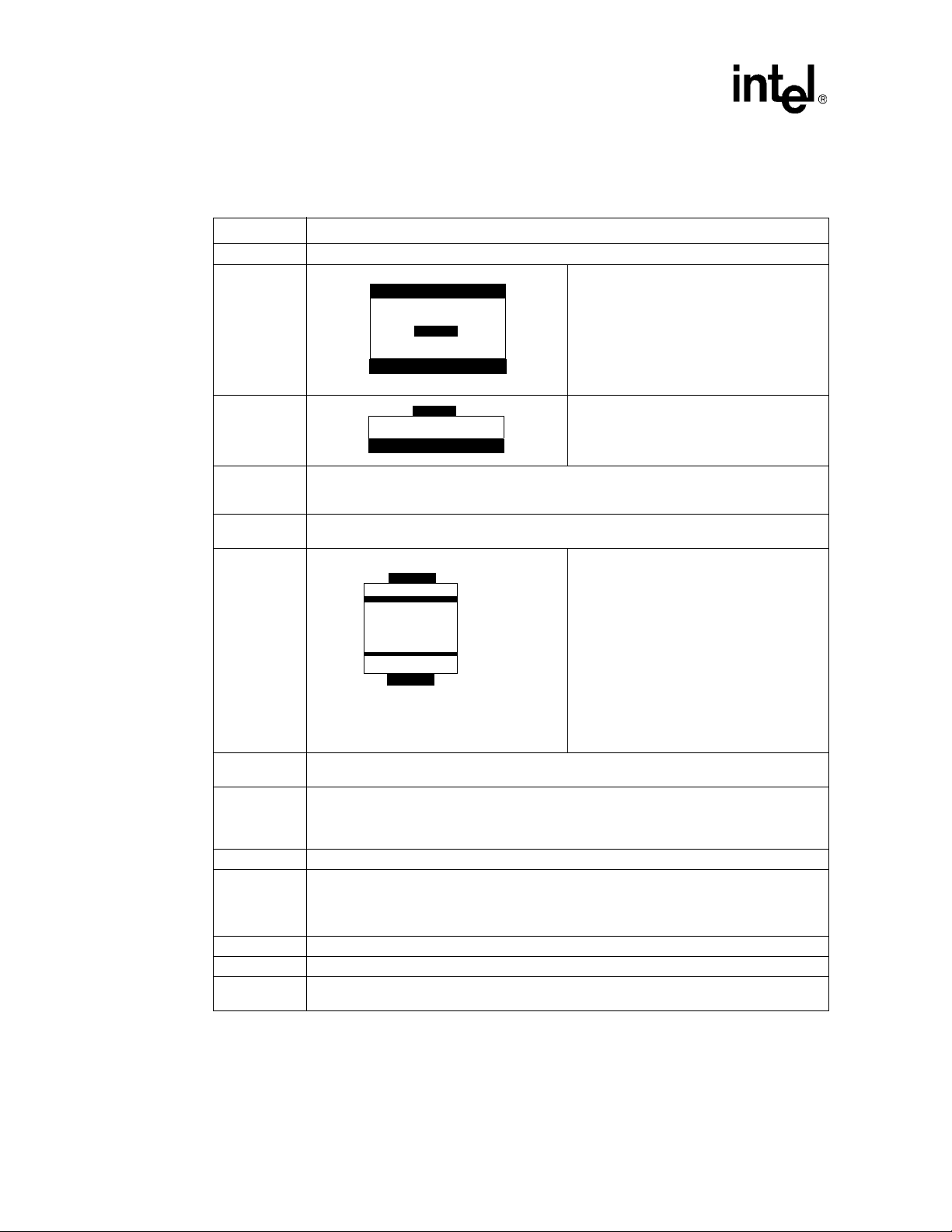

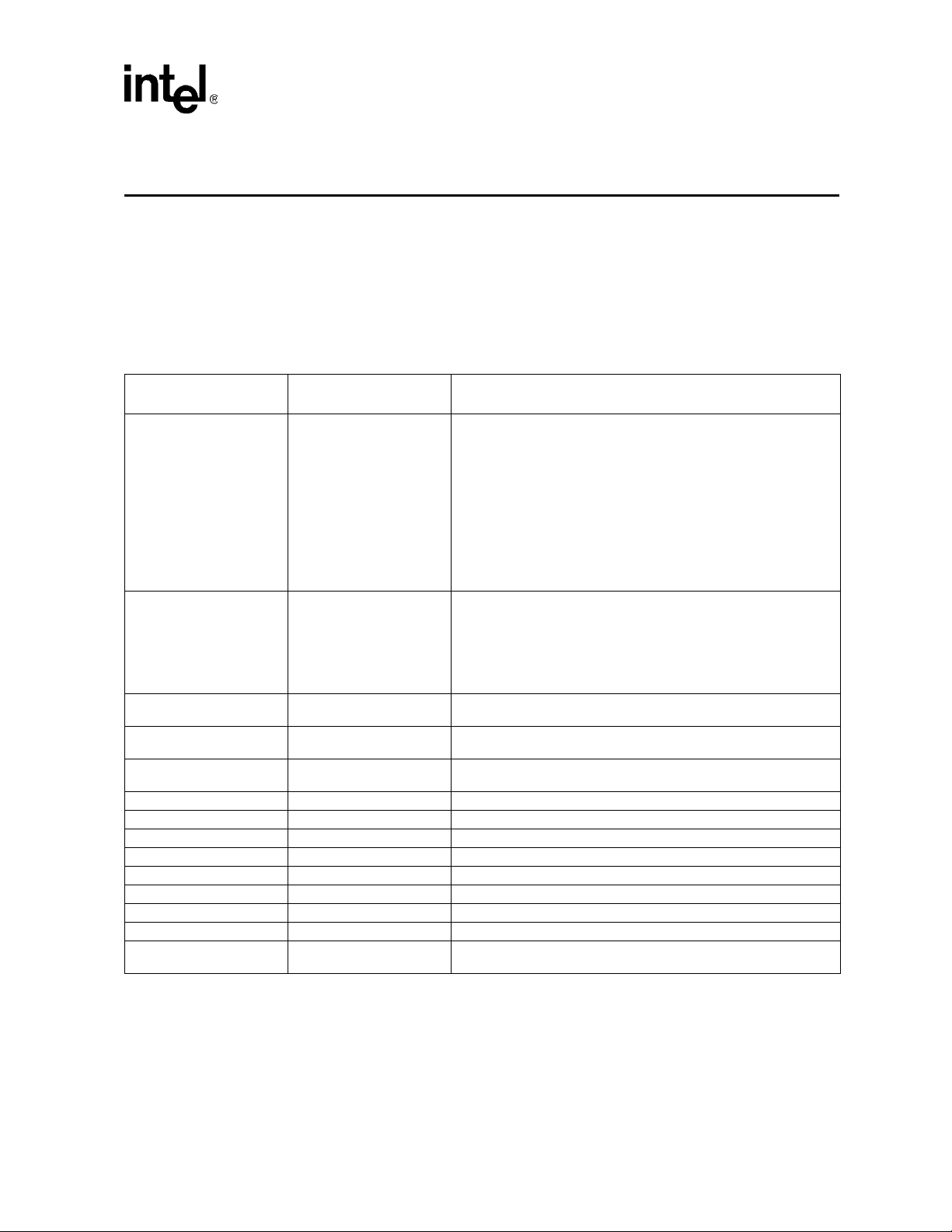

Table 1. Terminology and Definitions (Sheet 1 of 2)

Term Definition

80331 Intel

Stripline

®

80331 I/O processor

Stripline in a PCB is composed of the

conductor inserted in a dielectric with GND

planes to the top and bottom.

NOTE: An easy way to distinguish stripline

from microstrip is that you need to

strip away layers of the board to view

the trace on stripline.

Microstrip

Prepreg

Core

PCB

DDR

DDR II

DIMM Dual Inline Memory Module

Source

Synchronous

DDR

SSTL_2 Series Stub Terminated Logic for 2.5 V

JEDEC Provides standards for the semiconductor industry.

DLL

Material used for the lamination process of manufacturing PCBs. It consists of a layer of

epoxy material that is placed between two cores. This layer melts into epoxy when heated and

forms around adjacent traces.

Material used for the lamination process of manufacturing PCBs. This material is two sided

laminate with copper on each side. The core is an internal layer that is etched.

Layer 1: copper

Prepreg

Layer 2: GND

Core

Layer 3: V

Prepreg

Layer 4: copper

Example of a Four-Layer Stack

Double Data Rate Synchronous DRAM. Data is clocked on both rising and falling edges of the

clock.

DDR II is backward compatible with DDR I. However, it has an increased DDR data rate to

3.2 GBytes/sec with a clock rate of 200 MHz for multiple DIMM configurations. It allows data

rate of 6.4 Gbytes/sec with a clock rate of 400 MHz for a single DIMM point to point

configuration.

• For reads data leaves the DDR or memory controller with a data strobe. The memory

controller delays the data strobe internally to line it up with the data valid window.

• For writes the memory controller places the data strobe in the middle of the data valid

window to ensure that the correct data gets clocked into the DRAM.

Delay Lock Loop - refers to the DDR feature used to provide appropriate strobe delay to clock

in data.

CC

Microstrip in a PCB is composed of the

conductor on the top layer above the dielectric

with a ground plane below

Printed circuit board.

Example manufacturing process consists of

the following steps:

• Consists of alternating layers of core and

prepreg stacked

• The finished PCB is heated and cured.

• The via holes are drilled

• Plating covers holes and outer surfaces

• Etching removes unwanted copper

• Board is tinned, coated with solder mask

and silk screened

12

Page 13

Table 1. Terminology and Definitions (Sheet 2 of 2)

Term Definition

A network that transmits a coupled signal to another network is aggressor network.

Intel® 80331 I/O Process or Design Guide

Introduction

Aggressor

Victim A network that receives a coupled cross-talk signal from anot her net wor k is a victi m network.

Network The trace of a PCB that completes an electrical connection between two or more components.

Stub Branch from a trunk terminating at the pad of an agent.

Intersymbol Interference (ISI). This occurs when a transition that has not been completely

dissipated, interferes with a signal being transmitted down a transmission line. ISI can impact

both the timing and signal integrity. It is dependent on frequency, time delay of the line and the

ISI

CRB Customer Reference Board

PC1600

PC2100

PC2700

PC3200

Downstream At or toward the Primary PCI interface from the Secondary PCI interface

Local memory

DWORD 32-bit data word.

Local bus

Outbound At or toward the PCI interface of the 80331 AT U from the Internal Bus.

Inbound At or toward the Internal Bus of the 80331 from the PCI interface of the ATU.

Local processor Intel XScale

Core processor Intel XScale® core within the 80331.

Flip Chip

Mode

Conversion

ROMB Raid on motherboard

ODT

refection coefficient at the driver and receiver. Examples of ISI patterns that could be used in

testing at the maximum allowable frequencies are the sequences shown below:

JEDEC Names for DDR based on peak data rates.

PC1600= clock of 100 MHz * 2 data words/clock * 8 bytes = 1600 MB/sec

JEDEC Names for DDR based on peak data rates.

PC2100= clock of 133 MHz * 2 data words/clock * 8 bytes = 2128 MB/sec

JEDEC Names for DDR II based on peak data rates.

PC2700= clock of 167 MHz * 2 data words/clock * 8 bytes = 2672 MB/sec

JEDEC Names for DDR II based on peak data rates.

PC3200= clock of 200 MHz * 2 data words/clock * 8 bytes = 3200 MB/sec

Memory subsystem on the Intel XScale

busses.

80331 Internal Bus.

FC-BGA (flip chip-ball grid array) chip packages are designed with core flipped up on the back of

the chip, facing away from the PCB. This allows more efficient cooling of the package.

Mode Conversions are due to imperfections on the interconnect which transform differential

mode voltage to common mode voltage and common mode voltage to differential voltage.

On Die Termination - eliminates the need for termination resistors by placing the termination at

the chip.

Zo

®

core within the 80331.

Zo

Victim Network

Aggressor Network

0101010101010101

0011001100110011

0001110001110001111

®

core DDR SDRAM or Peripheral Bus Interface

Zo

Zo

13

Page 14

Intel® 80331 I/O Process or Design Guide

Introduction

1.1.2 Other Relevant Documents

1. Intel® 80331 I/O Processor Specification Update (273930), Intel Corporation

2. Intel® 80331 I/O Processor Data sheet (273943), Intel Corporation

3. Intel® 80331 I/O Processor Developer’s Manual (273942), Intel Corporation

4. Intel XScale® 80200 Processor based on Intel® Microarchitecture Developer’s Manual

(273411), Intel Corp orati on

5. PCI Local Bus Specification, Revision 2.3 - PCI Special Interest Group

6. PCI-X Specification, Revision 1.0b - PCI Special Interest Group

7. PCI Bus Power Management Interface Specification, Revis ion 1.1 - PCI Special Interest

Group

8. IEEE Standard Test Access Port and Boundary-Scan Architecture (IEEE JTAG-1149.1-1990)

14

Page 15

Intel® 80331 I/O Process or Design Guide

1.2 About the Intel® 80331 I/O Processor

The 80331 is a multi-function device that integrates the Intel XScale® core (ARM* architecture

compliant) with intelligent peripherals and PCI-to-PCI Bridge. The 80331 consolidates the

following into a single system:

• Intel XScale

• PCI-to-PCI Bridge supporting PCI-X interfaces on the Primary and Secondary bus.

• Address Translation Unit (PCI-to-Internal Bus Application Bridge) interfaced to the

Secondary Bus

• High-Performance Memory Controller

• Interrupt Controller with up to 13 external interrupt inputs

• Two Direct Memory Access (DMA) Controllers

• Application Accelerator

• Messaging Unit

• Peripheral Bus Interface Unit

• Performance Monitor

• Tw o I

®

core

2

C Bus Interface Units

Introduction

• Two 16550 compatible UARTs with flow control (four pins)

• Eight General Purpose Input Output (GPIO) ports

It is an integrated processor that addresses the needs of intelligent I/O applications and helps

reduce intelligent I/O system costs.

15

Page 16

Intel® 80331 I/O Process or Design Guide

Introduction

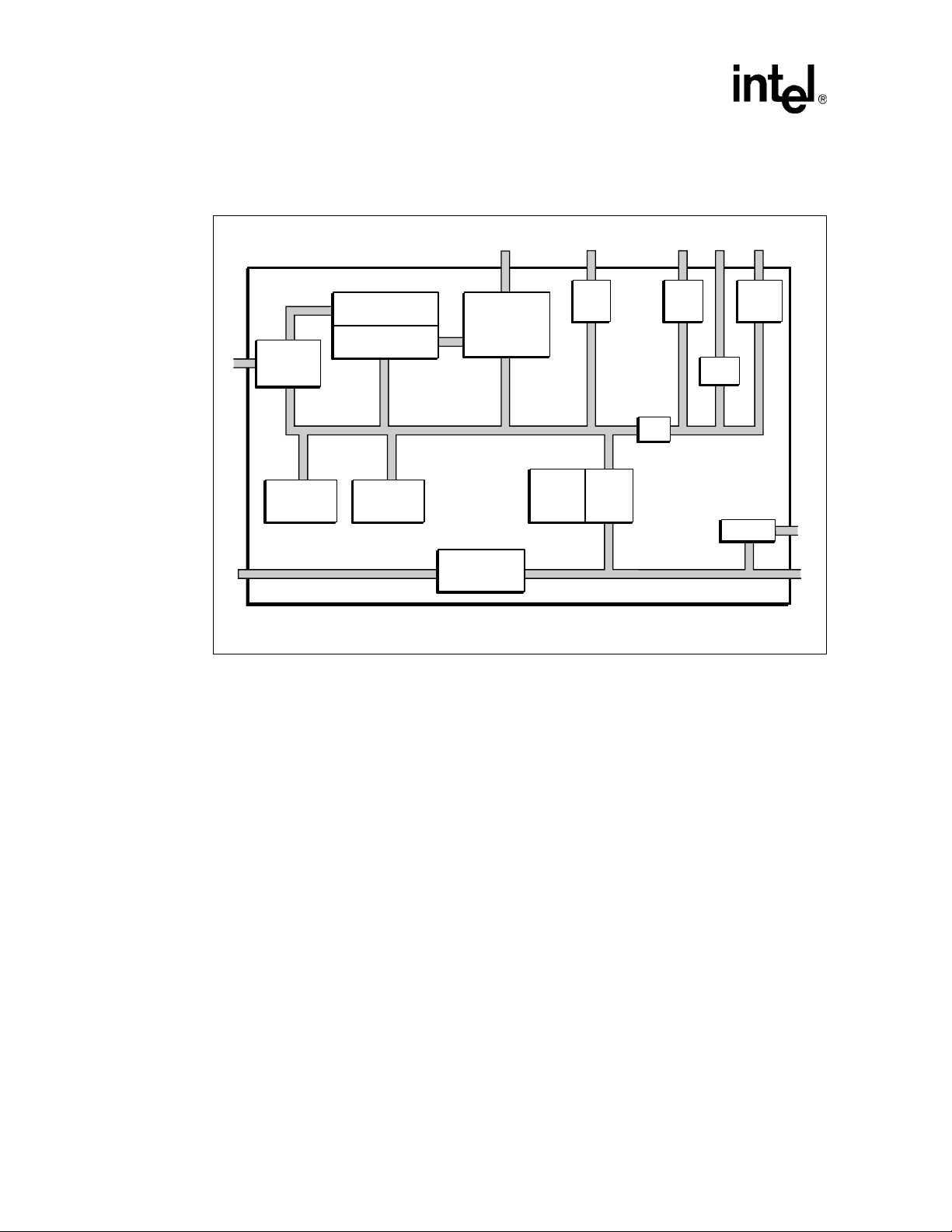

Figure 1 provides a block diagram of the 80331.

Figure 1. Intel® 80331 I/O Processor Functional Block Diagram

Message

Unit

16-bit

PBI

BRG

ATU

Intel® XScale™

Core

Bus Interface

Interrupt

Controller

& Timers

Application

Accelerator

Primary PCI Bus Secondary PCI Bus

Unit

Internal Bus

2 Channel

DMA

Controller

32/64-bit DDR

Interface

Memory

Controller

PCI-to-PCI

Bridge

UART

Units

2 - 1²C

Units

GPIO

Arbiter

B2472-01

16

Page 17

Intel® 80331 I/O Process or Design Guide

Package Information

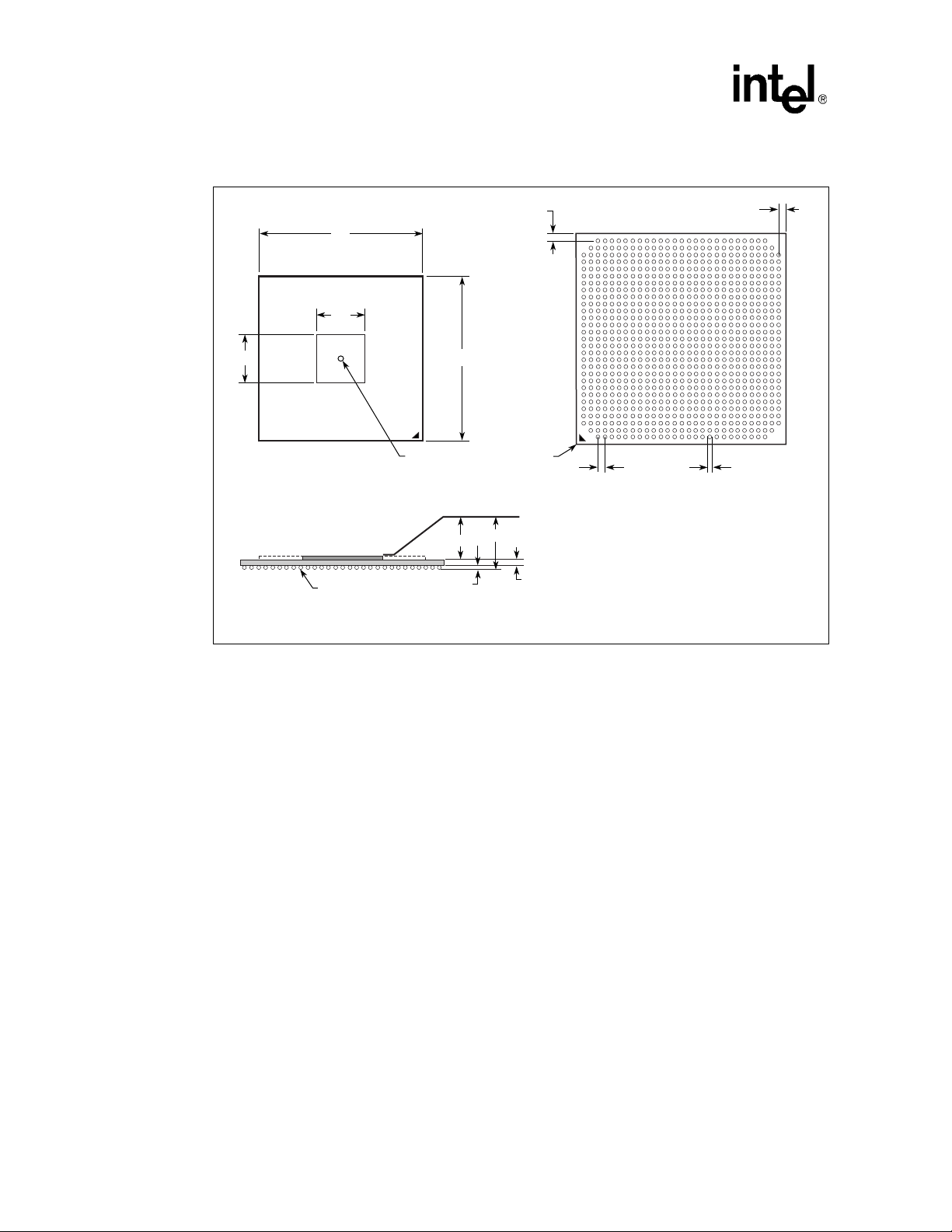

Package Information 2

The 80331 is of fered in a Flip Chip Ball Grid Array (FCBGA) package. This is a fu ll-array package

with 829 ball connections. The mechanical dimensions for this package are provided in the figure

below and

(FCBGA), mapped by pin function. This diagram is helpfu l in placing components around the

80331 for the layout of a PCB. To simplify routing and minimize the number of cross traces, keep

this layout in mind when placi ng compo nents on y our board. Th e signals, by des ign, are located o n

the FCBGA package to simplify signal routing and system implementation.

Table 2. FC-style, H-PBGA Package Dimensions

Table 2. Figure 3 and Figure 4 show the 829 pins of the Flip Chip Ball Grid Array

829-Pin BGA

Symbol Minimum Maximum

A 2.392 2.942

A1 0.50 0.70

A3 0.742 0.872

b 0.61 Ref.

C 1.15 1.37

D 37.45 37.55

E 37.45 37.55

F1 9.88 Ref.

F2 10.16 Ref.

e 1.27 Ref.

S1 0.97 Ref.

S2 0.97 Ref.

NOTE: Measurement in millimeters.

17

Page 18

Intel® 80331 I/O Process or Design Guide

Package Information

Figure 2. Intel® 80331 I/O Processor 829-Ball FCBGA Package Diagram

F2

S1

E

F1

Die

D

Pin #1

Corner

AJ

AH

AG

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

1234

5 6 7 8 9 10111213141516171819 20212223242526272829

e

Top View Bottom View

A

A3

Seating Plane

A1

C

Side View

S2

øb

B1230-03

18

Page 19

Intel® 80331 I/O Process or Design Guide

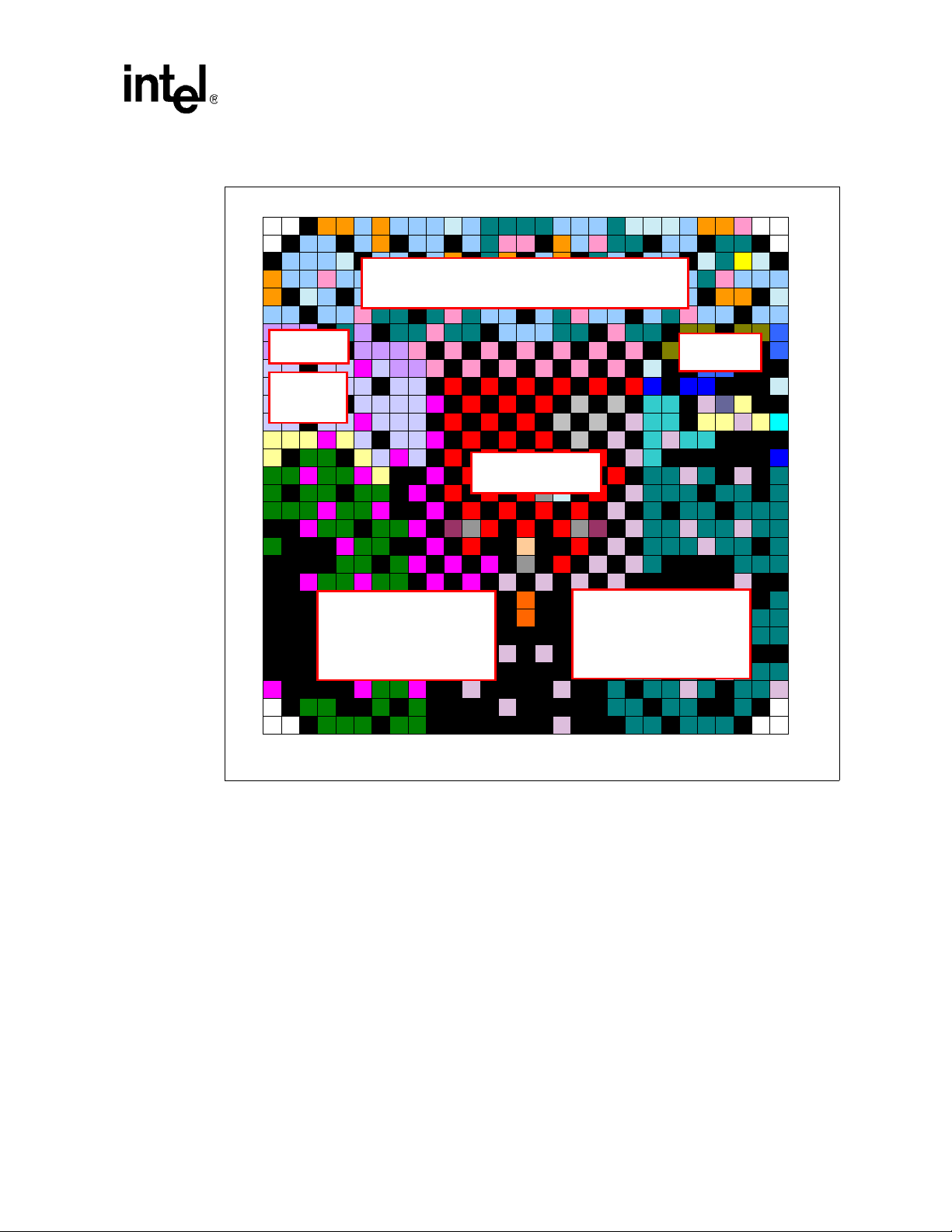

Figure 3. Intel® 80331 I/O Processor Preliminary Ballout (Top View)

Package Information

AJ

AH

AG

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

GPIO

PBI

21

2223242526272829

DDR/DDRII/SDRAM

Secondary

PCI-X Bus

21

2223242526272829

VCC/VSS

JTAG

Primary

PCI-X Bus

1234567891011121314151617181920

AJ

AH

AG

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

1234567891011121314151617181920

B1758-01

19

Page 20

Intel® 80331 I/O Process or Design Guide

Package Information

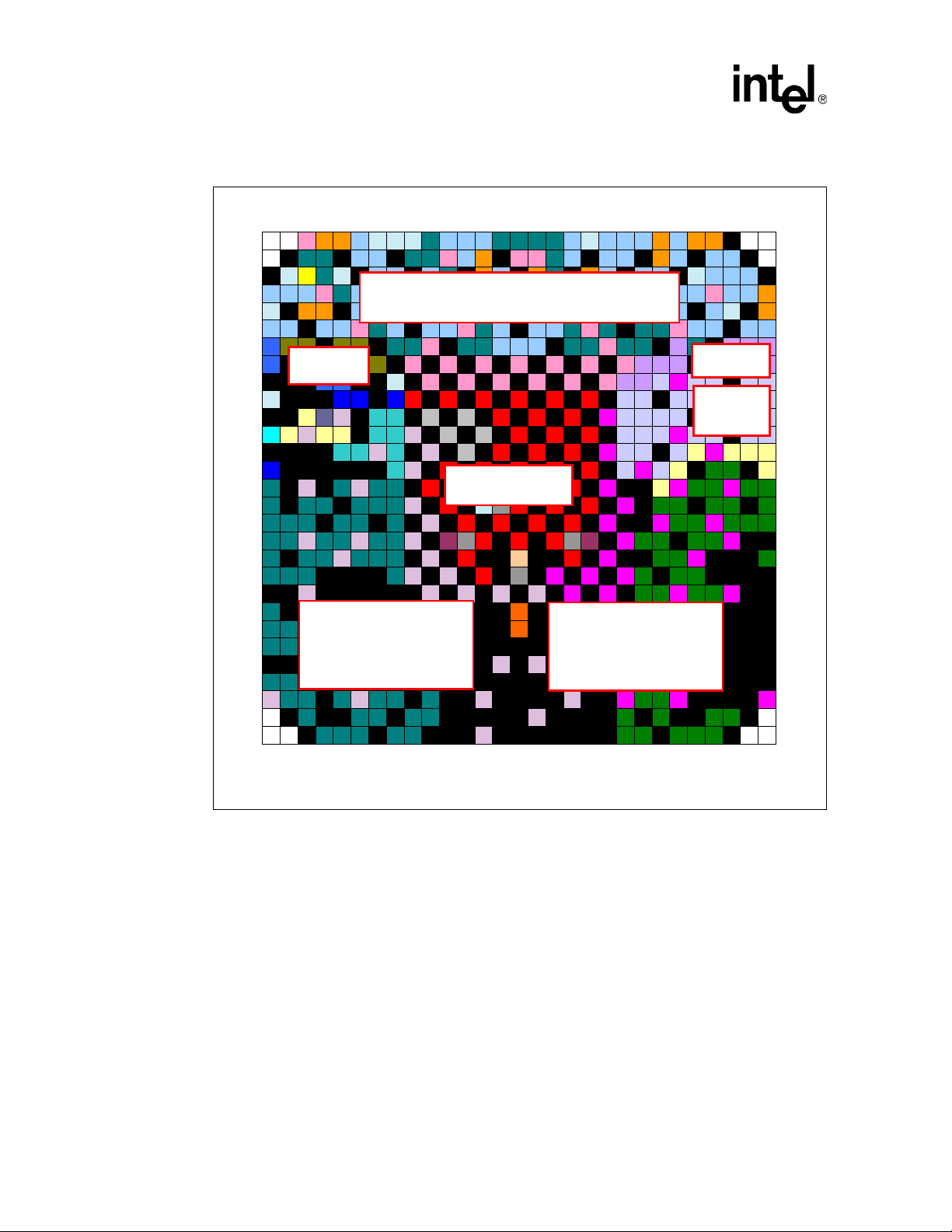

Figure 4. Intel® 80331 I/O Processor Preliminary Ballout (Bottom View)

1 2 3 4 5 6 7 8 9 10111213141516171819202122 23 24 25 26 27 28 29

AJ

AH

AG

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

JTAG

Primary

PCI-X Bus

1 2 3 4 5 6 7 8 9 10111213 141516171819202122 23 24 25 26 27 28 29

DDRII/SDRAM

GPIO

VCC/VSS

Secondary

PCI-X Bus

PBI

AJ

AH

AG

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

B1210-01

20

Page 21

Intel® 80331 I/O Process or Design Guide

1

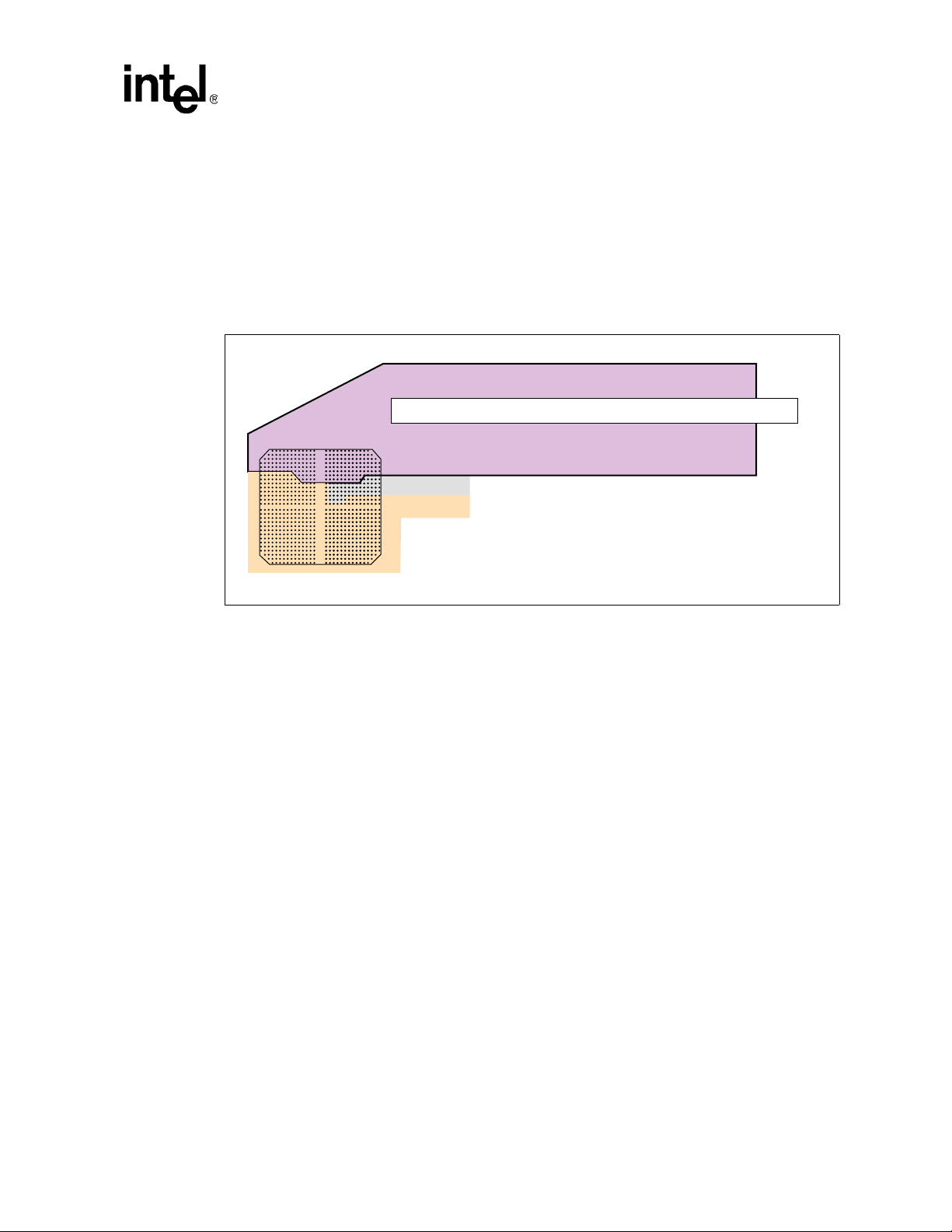

2.1 Power Plane Layout

Figure 5 provides an example of how the 80331 DDR, CPU core and 1.5 V core power planes are

partitioned on the Intel® IQ80331 Evaluation Platform Board (IQ80331).

Note: The voltage for the secondary PCIX bus and primary PCIX bus can be on the same plane.

Figure 5. Intel® 80331 I/O Processor Power Plane Layout

VCC_DDR

Package Information

(Use Top Layer for VTT Plane)

DDR DIMM Connector

VCC_XSCALE

VCC 1.5 V

DDR VDD Regulator

To Regulators

B2529-0

21

Page 22

Intel® 80331 I/O Process or Design Guide

Package Information

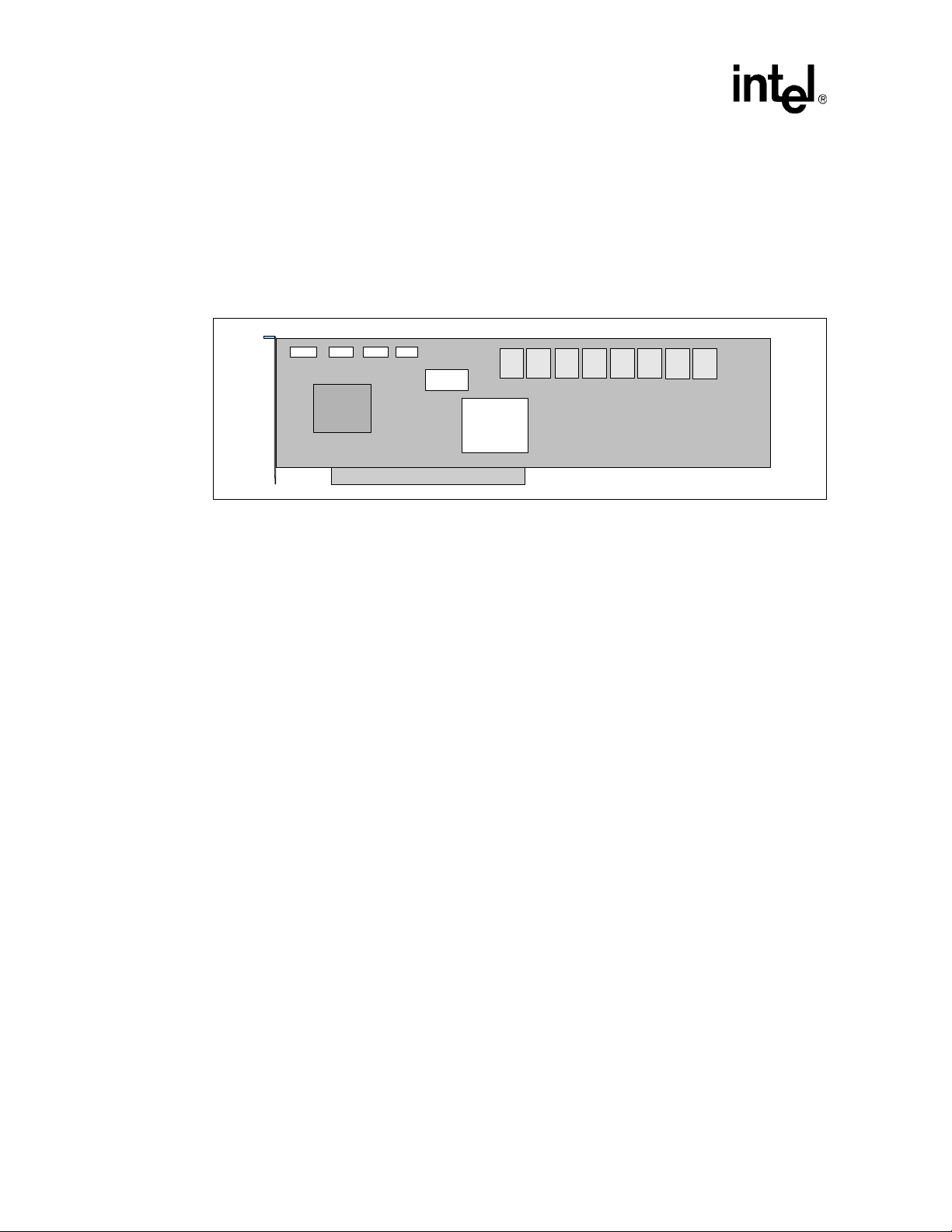

2.2 Intel® 80331 I/O Processor Applications

This section provides a block diagram of a 80331 Serial ATA adapter card application. This entire

SATA RAID card adapter can be implemented with just a few chips using the 80331 integrated

PCI-X bridge and IO processing capability.

Figure 6. Intel® 80331 I/O Processor PCI-X Adapter Card Block Diagram

SATA Connectors

SATA

Controller

4 Channel

Flash

PCI-X Edge

Intel® 80331

I/O Processor

DDR II

22

Page 23

Intel® 80331 I/O Process or Design Guide

Terminations

Terminations 3

This chapter provides the recommended pull-up and pull-down terminations for a 80331 layout.

Table 3 li sts these 80331 termination values. On a motherboard, the PCI Local Bus Specification,

Revision 2.3 requires that the PCI signals provide the termination resistors. Pull-ups on the PCI

signals are not required with PCIODT_EN = 1 (enabled), because they are implemented on the die.

Refer to the

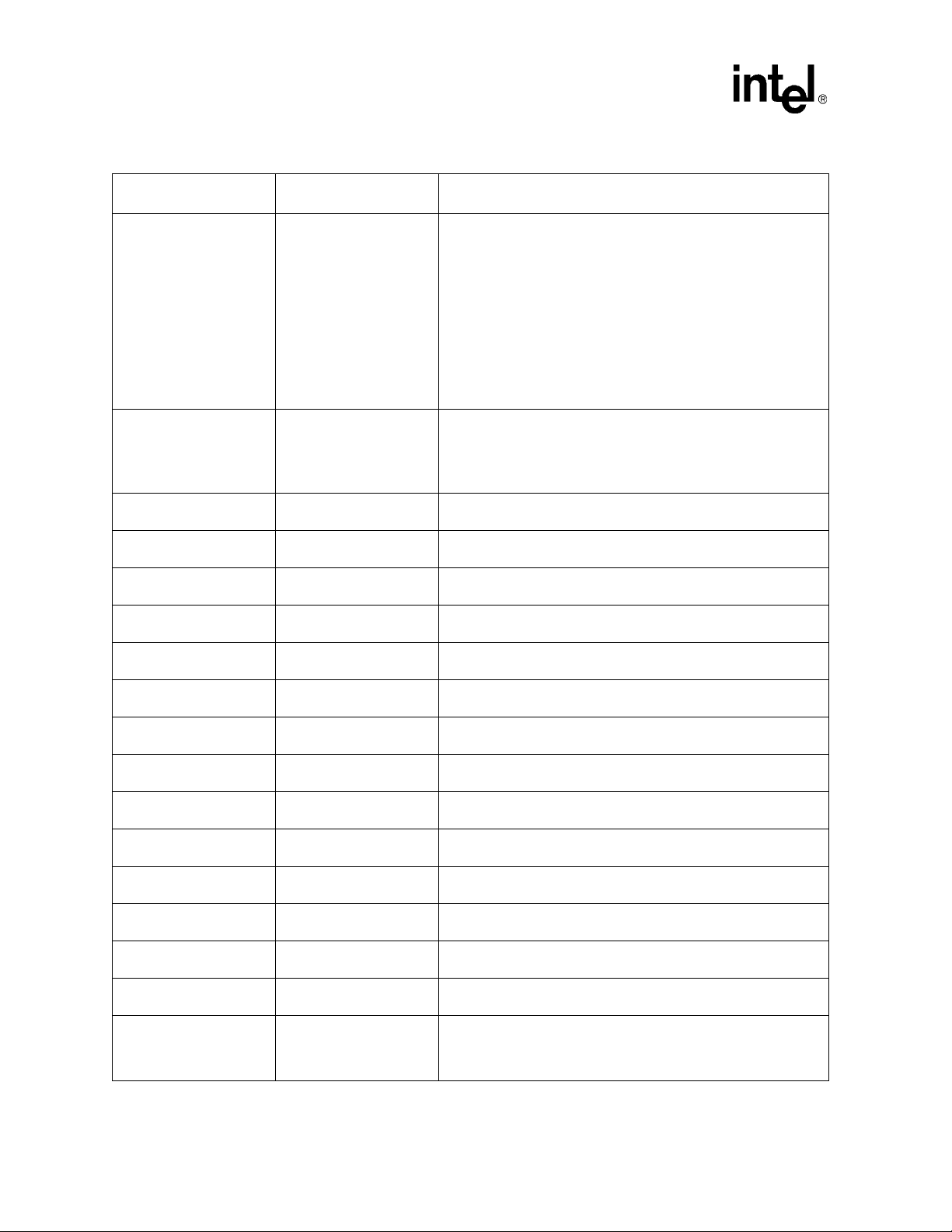

Table 3. Terminations: Pull-up/Pull-down (Sheet 1 of 4)

Signal

PWRDELAY

Table 3 for more information.

Pull-up or Pull-down

Resistor Value (in Ohms)

If battery backup is

implemented:

• 1.5 K pull-up to 3.3 V is

required on

PWRDELAY.

Battery Backup not

implemented:

• This pin can be

permanently pulled low

with a 1.5K pull-down

Comments

NOTES:

• Alternatively tied to P_RST# refer to Section 11.4.2, “ARM

TRST# 1.5K pull-down*

TMS

TDI

TCK

GPIO[0]/U0_RXD 8.2 K pull-up Note : GPIO[7:0] initializes as inputs on assertion of P_RST#.

GPIO[1]/U0_TXD 8.2 K pull-up Note: GPIO[7:0] initializes as inputs on assertion of P_RST#.

GPIO[2]/U0_CTS# 8.2 K pull-up Note : GPIO[7:0] initializes as inputs on assertion of P_RST#.

GPIO[3]/U0_RTS# 8.2 K pull-up N ote: GPIO[7:0] initializes as inputs on assertion of P_RST#.

GPIO[4]/U1_RXD 8.2 K pull-up Note : GPIO[7:0] initializes as inputs on assertion of P_RST#.

GPIO[5]/U1_TXD 8.2 K pull-up Note: GPIO[7:0] initializes as inputs on assertion of P_RST#.

GPIO[6]/U1_CTS# 8.2 K pull-up Note : GPIO[7:0] initializes as inputs on assertion of P_RST#.

GPIO[7]/U1_RTS 8.2 K pull-up Note: GPIO[7:0] initializes as inputs on assertion of P_RST#.

ARB_EN (see comments)

NC when not being used

(has internal pull-up)

NC when not being used

(has internal pull-up)

1.5K pull-down when not

used

Multi-ICE” on page 142 for more information about using with a

ICE.

• When not used this signal is be tied to GND.

• This pin has an internal pull-up.

This signal has been defeatured. Please refer to the Intel® 80331

Specification Update for more information.

23

Page 24

Intel® 80331 I/O Process or Design Guide

Terminations

Table 3. Terminations: Pull-up/Pull-down (Sheet 2 of 4)

Signal

PCIODT_EN

P_32BITPCI#

S_INT[D:A]# . Refer to comments

S_LOCK# Refer to comments

S_SERR# Refer to comments

S_TRDY# Refer to comments

S_PERR# Refer to comments

S_DEVSEL# Refer to comments

S_FRAME# Refer to comments

S_STOP# Refer to comments

S_IRDY# Refer to comments

S_AD[63:32] Refer to comments

S_C/BE[7:4 ] Re fe r to c omments

S_PAR64 Refer to comments

S_REQ64# Re fer to comments

S_ACK64# Refer to comments

S_M66EN Refer to comments

Pull-up or Pull-down

Resistor Value (in Ohms)

1.5 K pull-down when

needed (see comments)

1.5 K pull-down when

needed (see comments)

PCI Bus ODT Enable: is latched on the rising (deasserting) edge of

P_RST#, and determines when the PCI-X interface has On Die

Termination enabled valid on the secondary PCI bus only.

• 0 = ODT disabled on the secondary PCI bus. (Requires pull-down

resistor).

• 1 = ODT enabled on the secondary PCI bus. (Default mode).

This signal controls termination for the following signals:

S_AD[63:32], S_C/BE[7:4]#, S_PAR64, S_REQ64#, S_REQ[3:0]#,

S_ACK64#, S_FRAME#, S_IRDY#, S_DEVSEL#, S_TRDY#,

S_STOP#, S_PERR#, S_LOCK#, S_M66EN, S_SERR# and

XINT[3:0]#

NOTE: This signal is muxed onto signal A[20].

Primary PCI-X Bus Width: By default, identifies 80331 subsystem as

64-bit unless user attaches appropriate pull-down resistor.

0 = 32 bit wide bus. (Requires pull-down resistor).

1 = 64 bit wide bus. (Default mode).

NOTE: Muxed onto signal A[2]

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required when PCI

bus is to operate at 66 MHz. This signal is grounded for 33 MHz

operation.

Comments

24

Page 25

Intel® 80331 I/O Process or Design Guide

Table 3. Terminations: Pull-up/Pull-down (Sheet 3 of 4)

Signal

S_RCOMP 100 ohm +/- 1% to GND

SCLKIN

S_REQ[3:0]# Refer to comments

S_PCIXCAP Refer to comments

PRIVMEM

PRIVDEV 1.5 K pull-down when

P_RCOMP 100 ohm +/- 1% to GND

P_REQ# Refer to comments

P_LOCK# Refer to comments

P_SERR# Refer to comments

P_TRDY# Refer to comments

P_PERR# Refer to comments

P_DEVSEL# Refer to comments

P_FRAME# Refer to comments

P_STOP# Refer to comments

P_IRDY# Refer to comments

P_AD[63:32] Refer to comments

P_C/BE[7:4] Refer to comments

P_PAR64 Refer to comments

P_REQ64# Refer to comments

P_ACK64# Refer to comments

Pull-up or Pull-down

Resistor Value (in Ohms)

Through 33.2ohm resistor

to S_CLKOUT

1.5 K pull-down when

needed (refer to comments)

needed (refer to comments)

• When PCIODT_EN = 1 no external pull-up needed

• When PCIODT_EN = 0, then 8.2 K pull-up is required.

66 MHz PCI: connect pin to GND.

66 MHz PCI-X: use 0.01 µF to GND || 10 K resistor to GND.

100 MHz PCI-X: use 0.01 µF to GND.

133 MHz PCI-X: use 0.01 µF to GND.

Private Memory Enable: PRIVMEM latched at rising (deasserting)

edge of P_RST# and determines when the 80331 operates with

Private Memory Space on the secondary PCI bus of the PCI-to-PCI

Bridge.

0 = Normal addressing mode. Requires pull-down resistor.

1 = Private Addressing enable in PCI-to-PCI Bridge. (Default mode)

Muxed onto signal A[1],

Private Device Enable: PRIVDEV latched at rising (deasserting)

edge of P_RST# and determines when the 80331 operates with

Private Device enabled on the secondary PCI bus of the PCI-to-PCI

Bridge.

0 = All Secondary PCI devices are accessible to Primary PCI

configuration cycles. (Requires pull-down resistor).

1 = Private Devices enabled in PCI-to-PCI Bridge. (Default mode)

Muxed onto signal A[0]

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

Terminations

Comments

1

25

Page 26

Intel® 80331 I/O Process or Design Guide

Terminations

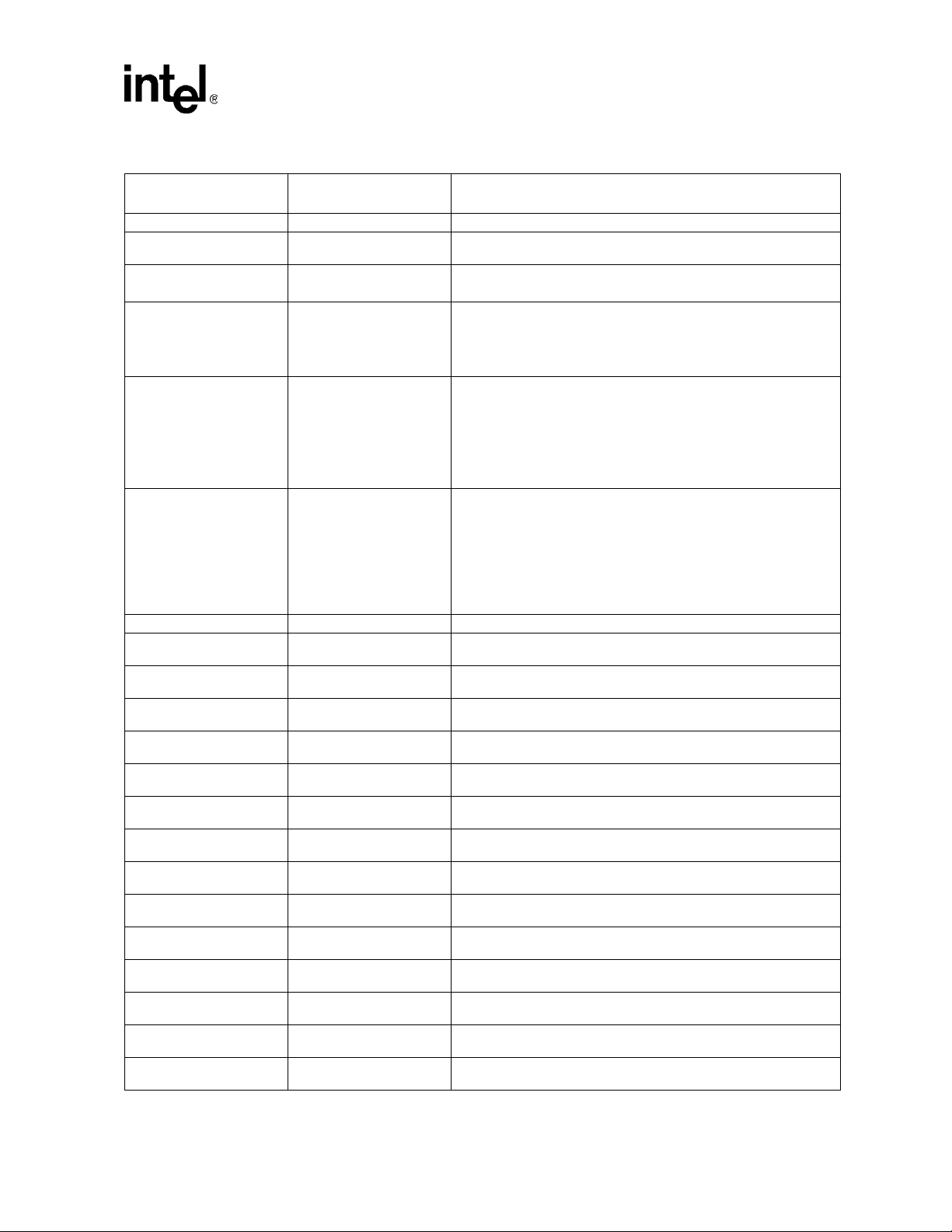

Table 3. Terminations: Pull-up/Pull-down (Sheet 4 of 4)

Signal

P_M66EN Refer to comments

P_REQ# Refer to comments

M_CK[2:0], M_CK[2:0]# Refer to comments For M_CKs and M_CK#s not used leave these pins unconnected.

DQS[8:0]# Refer to Comments When not in DDRII mode these signals are NC’s

DDRRES[2:1]

HPI# 8.2 K pull-up

P_BOOT16#

MEM_TYPE

RETRY

CORE_RST#

BRG_EN

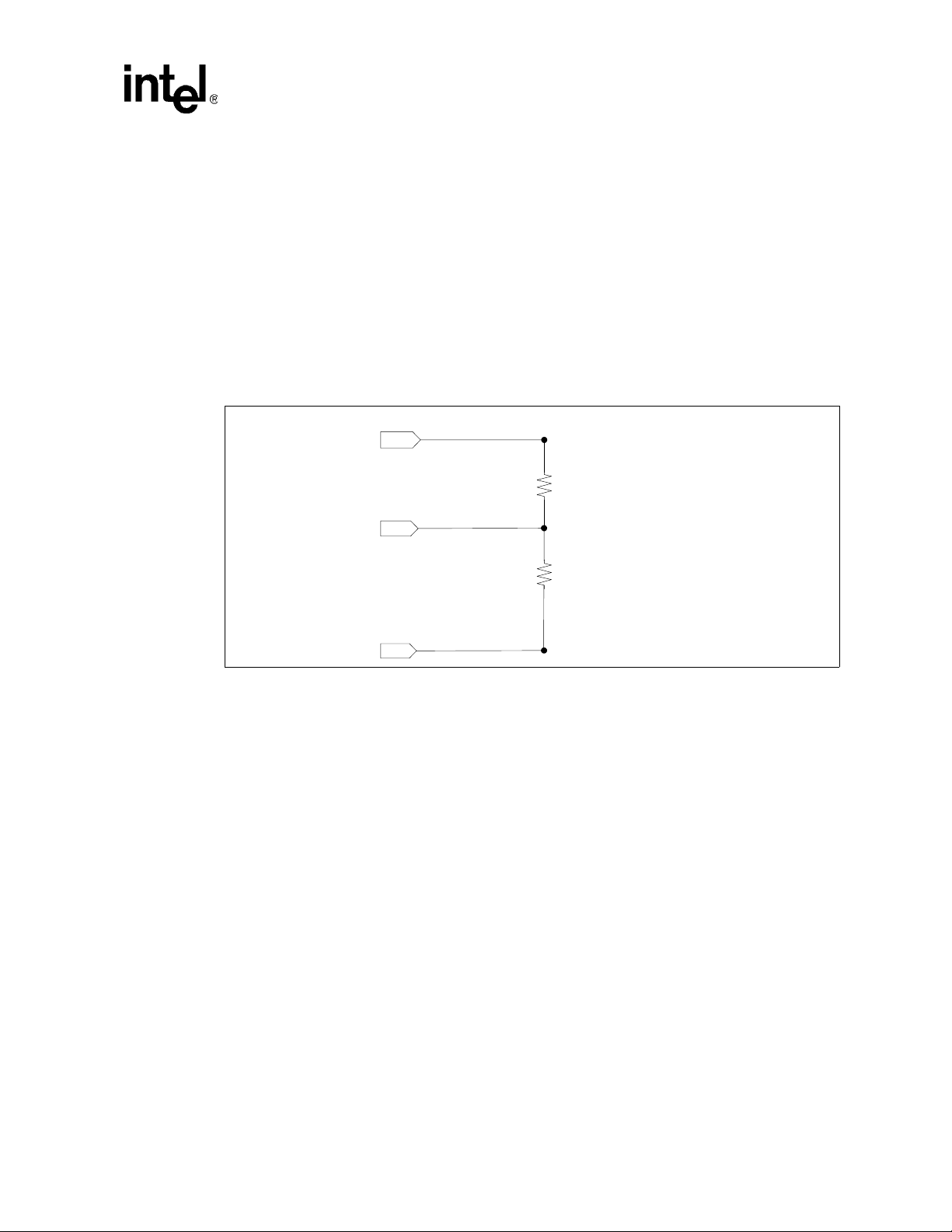

DDRSLWCRES Refer to Figure 9

DDRIMPCRES Refer to Figure 9

ODT[1:0]

Pull-up or Pull-down

Resistor Value (in Ohms)

•Refer to Figure 8 for the

recommended

termination for DDRII

mode.

• When not in DDRII

mode these signals

have a 1.0 K pull-down.

1.5 K pull-down when

needed (refer to comments)

1.5 K pull-down when

needed (refer to comments)

1.5 K pull-down when

needed (refer to comments)

1.5 K pull-down when

needed (refer to comments)

1.5 K pull-down when

needed (refer to comments)

Connect to ODT on DIMM

terminated with 49.9 ohm

resistor to VTT

Comments

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

8.2 K pull-up is required when not already pulled up on the PCI bus.

An add-in card may rely on the motherboard to pull-up this signal.

Bus Width is latched on the rising (asserting) edge of P_RST#, it sets

the default bus width for the PBI Memory Boot window:

• 0 = 16 bits wide (Requires a pull-down resistor.)

• 1 = 8 bits wide (Default mode)

Muxed onto signal AD[4].

Memory Type: MEM_TYPE is latched on the rising (asserting) edge

of P_RST# and it defines the speed of the DDR SDRAM interface.

0 = DDR-II SDRAM at 400 MHz (Required pull-down resistor.)

1 = DDR SDRAM at 333 MHz (Default mode)

Muxed onto signal AD[2]

Configuration Retry Mode: RETRY is lat ched on t he rising (asserting)

edge of P_RST# and determines when PCI interface of the ATU

disables PCI configuration cycles by signaling a retry until the

configuration cycle retry bit is cleared in the PCI configuration and

status register.

0 = Configuration Cycles enabled (Requires pull down resistor.)

1 = Configuration Retry enabled in the ATU and the Configuration.

(Default mode)

Muxed onto signal AD[6]

Core Reset Mode is latched on the rising (asserting) edge of P_RST#

and determines when the Intel

processor reset bit is cleared in PCI configuration and status register.

0 = Hold in reset. (Requires pull-down resistor.)

1 = Do not hold in reset. (Default mode)

Muxed onto signal AD[5]

Bridge Enable: BRG_EN latched at rising (deasserting) edge of

P_RST# and determines when the 80331 operates wi th PCI- to-PCI

Bridge.

0 = Disable Bridge, enable P_CLK input on S_CLKIN input.

(Requires pull-down resistor)

1 = Enabled Bridge. (Default mode)

Muxed onto signal AD[0]

When not used this pin is left as a “no connect”.

®

XScale™ core is held in reset until the

26

Page 27

3.1 Analog Filters

The following section describes filters needed for biasing PLL circuitry.

Intel® 80331 I/O Process or Design Guide

Terminations

3.1.1 V

T o reduce clock skew, the V

package. The lowpass filter, as shown in

timing relationships in system designs. The node con necti ng V

short as possible. The

- V

The following notes list the layout guidelines for this filter.

Figure 7. V

CCPLL

Pin Requirements

balls for the Phase Lock Loop (PLL) circuit are isolated on the

CCPLL

Figure 7 reduces noise induced clock jitter and its effects on

and the capacitor must be as

CCPLL

Figure 7 filter circuit is recommended for each of the Four PLL pairs: V

SSA1, VCCPLL2

- V

SSA2, VCCPLL4

- V

SSA4

and V

CCPLL5

- V

SSA5

pairs.

• 4.7 µH (Inductor)

— L must be magnetically shielded

—ESR: max < 0.4Ω

— rated at 45mA

— An example of this inductor is TDK part number MLZ2012E4R7P.

• 22 µF (Capacitor)

—ESR: max < 0.4Ω

— ESL < 3.0nH

— Place 22 µF capacitor as close as possible to package pin.

• 0.5 ohm 1% (Resistor)

— 1/16W 6.3V

• 0.5 ohm 1% resistor must be placed between V

• Route V

• V

CCPLL

[1-5] and V

CCPLL

[1-5] and V

[1-5] as differential traces.

SSA

[1-5] traces must be ground referenced (No VCC references).

SSA

and L. The resistor rating is 1/16W.

CC

• Maximum total board trace length = 1.2”.

• Minimum trace space to other nets = 30 mils.

• The 1.5 V supply regulator used for the PLL filter must have less than +/- 3% tolerance.

• Note: V

Configuration

CCPLL

SSA1

, V

SSA2, VSSA4 and VSSA5

pins must not be connected to ground.

CCPLL1

1.5 V

0.5 ohms , 1%

Note: Do Not conn ect V SSA pins to g round

Board Trace:

Trace w idth > 25 mils

Trace Spac ing < 10 mils

Trace Length < 600 mils

4.7 uH <25%

22 uF <20%

Board Route

Traces

Breakout Traces

Beneath BGA

Breakout Trace:

Trace w idth > 6 mils

Tra c e S pa c in g < 6 mils

Trace Length < 600 mils

VCCPLL

Intel®

I/O Processor

VSSA

27

Page 28

Intel® 80331 I/O Process or Design Guide

Terminations

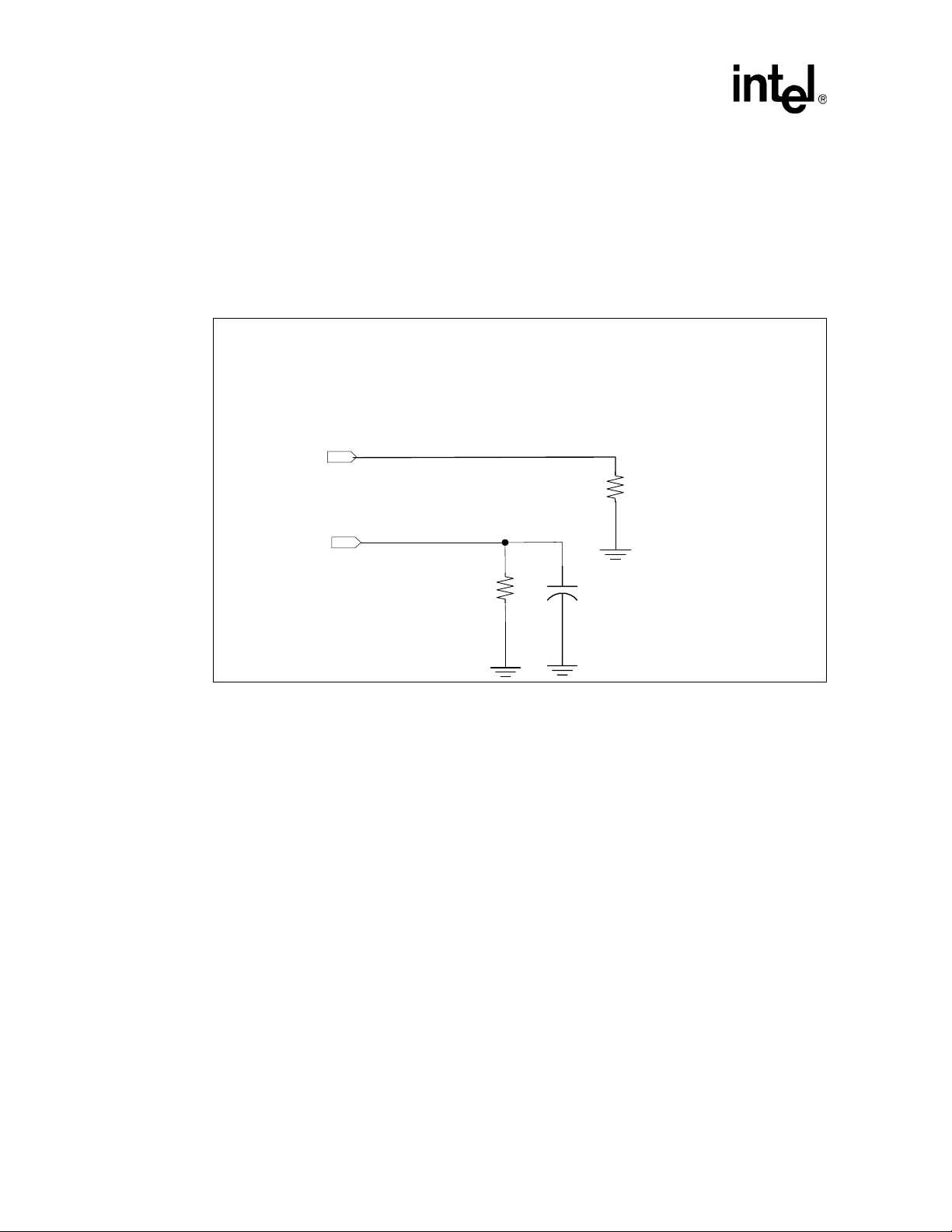

3.2 DDR Resistor Compensation

The Figure 8 provides the 80331 DDR II DDRES circuitry. The DDRRES1 resistor has a tight

toleranc e of 40.2 ohm 0.5%. DDRRES2 is used as compensation for DDR-II OCD. Due to the fact that

OCD is not supported this pin should be pulled to GND with a 1K resistor.

s

Note: when not in DDR II mode these pins must have a 1.0 K pull-down to GND.

Figure 8. Intel® 80331 I/O Processor DDRRES Resistor Compensation Circuitry

DDRRES2

1K ohms

DDRRES1

40.2 ohms

0.5%

0.1uF

28

Page 29

3.3 DDR Driver Compensation

External reference resistors are used to control slew rate and driver impedance. The

DDRIMPCRES (or DDRDRVCRES) resistor directly controls the on-die termination (ODT). The

recommendations are as follows:

• DDRIMPCRES: controls on-die termination, DDR - 385 ohms, DDRII - 285 ohms. Note that

the closest standard 1% resistors are acceptable

• DDRSLWRCRES: controls slew rate and driver impedance, DDR 845 ohms, DDRII

ohms.

825

With these values the ODT is 150/75 ohms for DDRII and 200/100 ohms for DDR.

Figure 9. DDR Driver Compensation Circuitry

DDRIMPCRES

DDRCRES0

Intel® 80331 I/O Process or Design Guide

Terminations

.

385 ohms DDR

285 ohms DDRII

DDRSLWCRES

845 ohms DDR

825 ohms DDRII

29

Page 30

Intel® 80331 I/O Process or Design Guide

Terminations

This Page Intentionally Left Blank

30

Page 31

Intel® 80331 I/O Process or Design Guide

Routing Guidelines

Routing Guidelines 4

This chapter provides some basic ro uting guidel ines for layout and design of a printed circuit board

80331. The high-speed clocking required when designing with the 80331 requires special

using

attention to signal integrity. In fact, it is highly recommended that the board design be simulated to

determine optimum layout for signal integrity. The information in this chapter provides guidelines

to aid the designer with board layout. Several factors influence the signal integrity of a

design. These factors include:

• Power distribution

• Minimizing crosstalk

• Decoupling

• Layout considerations when routing the DDR memory, DDR II memory, and PCI-X bus

interfaces

80331

4.1 General Routing Guidelines

This section details general routing guidelines for designing with 80331. The order in which

signals are routed varies from designer to designer. Some designers prefer to route all clock signals

first, while others pre fer to route al l high -speed b us sig nals fi rst. Ei ther ord er can be u sed, pr ovide d

the guidelines listed here are followed.

31

Page 32

Intel® 80331 I/O Process or Design Guide

Routing Guidelines

4.2 Crosstalk

Crosstalk is caused by capacitive and inductive cou pling between si gnals. Crosstal k is composed of

both backward and forward crosstalk components. Backward crosstalk creates an induced signal on

victim network that propagates in the opposite direction of the aggressor signal. Forward crosstalk

creates a signal that propagates in the same direction as the aggressor signal.

Circuit board analysis software is used to analyze your board layout for crosstalk probl ems. Examples

of 2D analysis tools include Parasitic Parameters from ANSOFT

Crosstalk problems occur when circuit etch lines run in parallel. When board analysis software is not

available, the layout needs to be designed to mai ntain at least the minimum recommended spacing for

bus interfaces.

• A general guideline to use is, that space distance between adjacent signals be a least 3.3 times

the distance from signal trace to the nearest return plane. The coupled noise between adjacent

traces decreases by the square of the distance between the adjacent traces.

• It is also recommended to specify the height of the above reference plane when laying out

traces and provide this parameter to the PCB manufacturer. By moving traces closer to the

nearest reference plane, the coupled noise decreases by the square of the distance to the

reference plane.

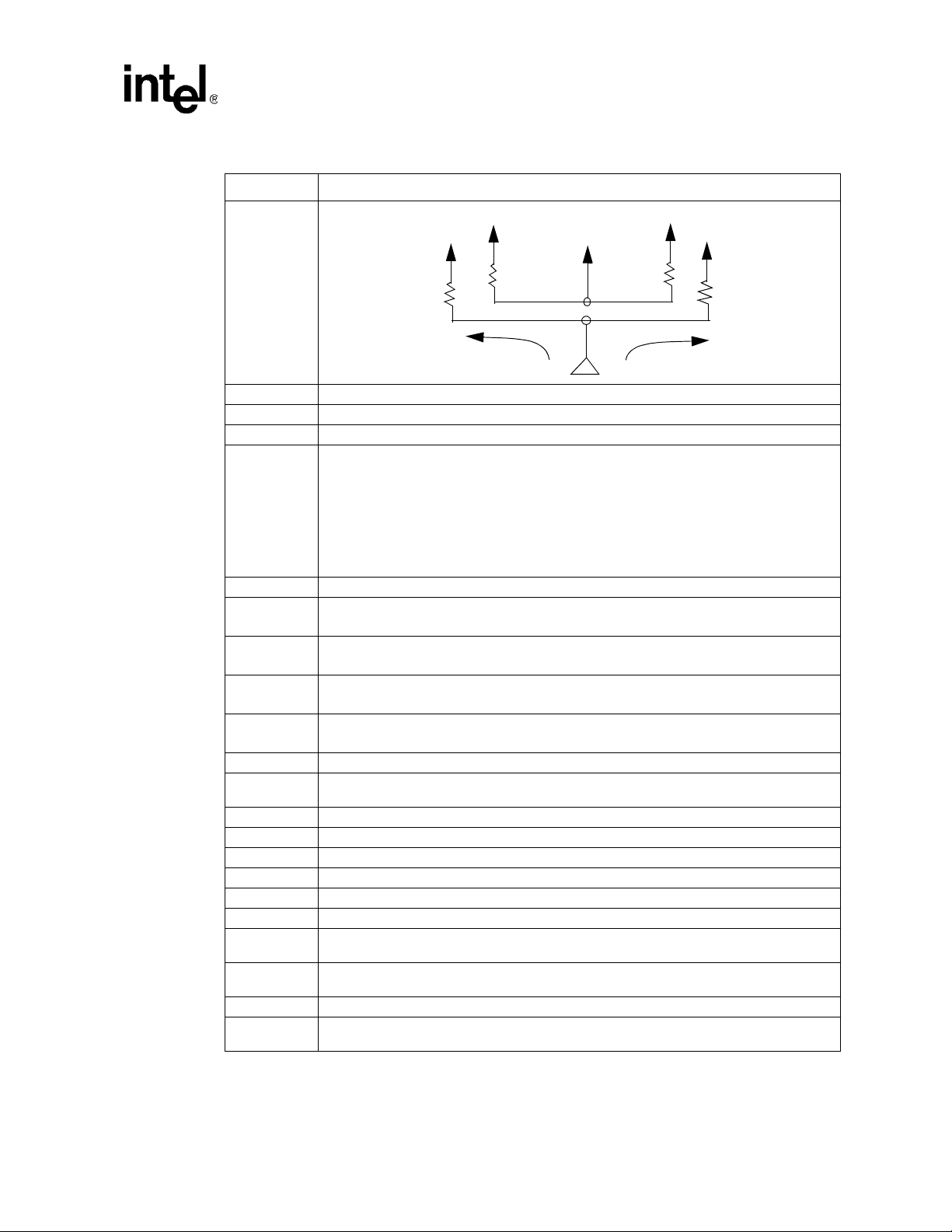

Figure 10. Crosstalk Effects on Trace Distance and Height

P

H

aggressor victim

Reference Plane

• Avoid slots in the ground plane. Slots increases mutual inductance thus increasing crosstalk.

• Throughout the design guide unbroken GND reference planes are recommended. If it is not

possible to route over an unbroken ground plane then an unbroken power plane is acceptable.

If it is necessary to use power plane referencing, it is better to reference the power plane used

by the I/O connector (if applicable). It is also recommended to add decoup ling to the connector

near the pins.

*

and XFS from Quad Design*.

Reduce Crosstalk:

- Maximize P

- Minimize H

A9259-01

• Make sure that ground plane surrounding connector pin fields are not completely cleared out.

When this area is completely cleared out, around the connector pins, all the return current must

flow together around the pin field increasing crosstalk. The preferred method of laying out a

connector in the GND layer is shown in

32

Figure 11B.

Page 33

Figure 11. PCB Ground Layout Around Connectors

Connector

Connector Pins

GND PCB Layer

A. Incorrect method B. Correct method

Intel® 80331 I/O Process or Design Guide

Routing Guidelines

A9260-01

33

Page 34

Intel® 80331 I/O Process or Design Guide

Routing Guidelines

4.3 EMI Considerations

It is highl y recommended that good EMI design practices be followed when designing wit h the

80331.

• To minimize EMI on your PCB a useful technique is to not extend the power planes to the

edge of the board.

• Another technique is to surround the perimeter of your PCB layers with a GND trace. This

helps to shield the PCB with grounds minimizing radiation.

The below link can provide some useful general EMI guidelines considerations:

http://developer.intel.com/design/auto/mcs96/applnots/272673.htm

4.4 Power Distribution and Decoupling

Have ample decoupling to ground, for the power planes, to minimize the effects of the switching

currents. Three types of decoupling are: the bulk, the high-frequency ceramic, and the inter-plane

capacitors.

• Bulk capacitance consist of electrolytic or tantalum capacitors. These capacitors supply large

reservoirs of charge, but they are useful only at lower frequencies due to lead inductance

effects. The bulk capacitors can be located anywhere on the board.

• For fast switching currents, high-frequency low-inductance capacitors are most effective.

Place these capacitors as close to the device being decoupled as possible. This minimizes the

parasitic resistance and inductance associated with board traces and vias.

• Use an inter-plane capacitor between power and ground planes to reduce the effective plane

impedance at high frequencies. The general guideline for placing capacitors is to place

high-frequency ceramic capacitors as close as possible to the module.

4.4.1 D ecoupling

Inadequate high-frequency decoupling results in intermittent and unreliable behavior.

A general guideline recommends that you use the largest easily available capacitor in the lowest

inductance package. The high speed decoupling capacitor should be placed as close to the pin as

possible with short, wide trace.

Table 4 provides the details on the recommended decoupling capacitors for each of the voltage

planes.

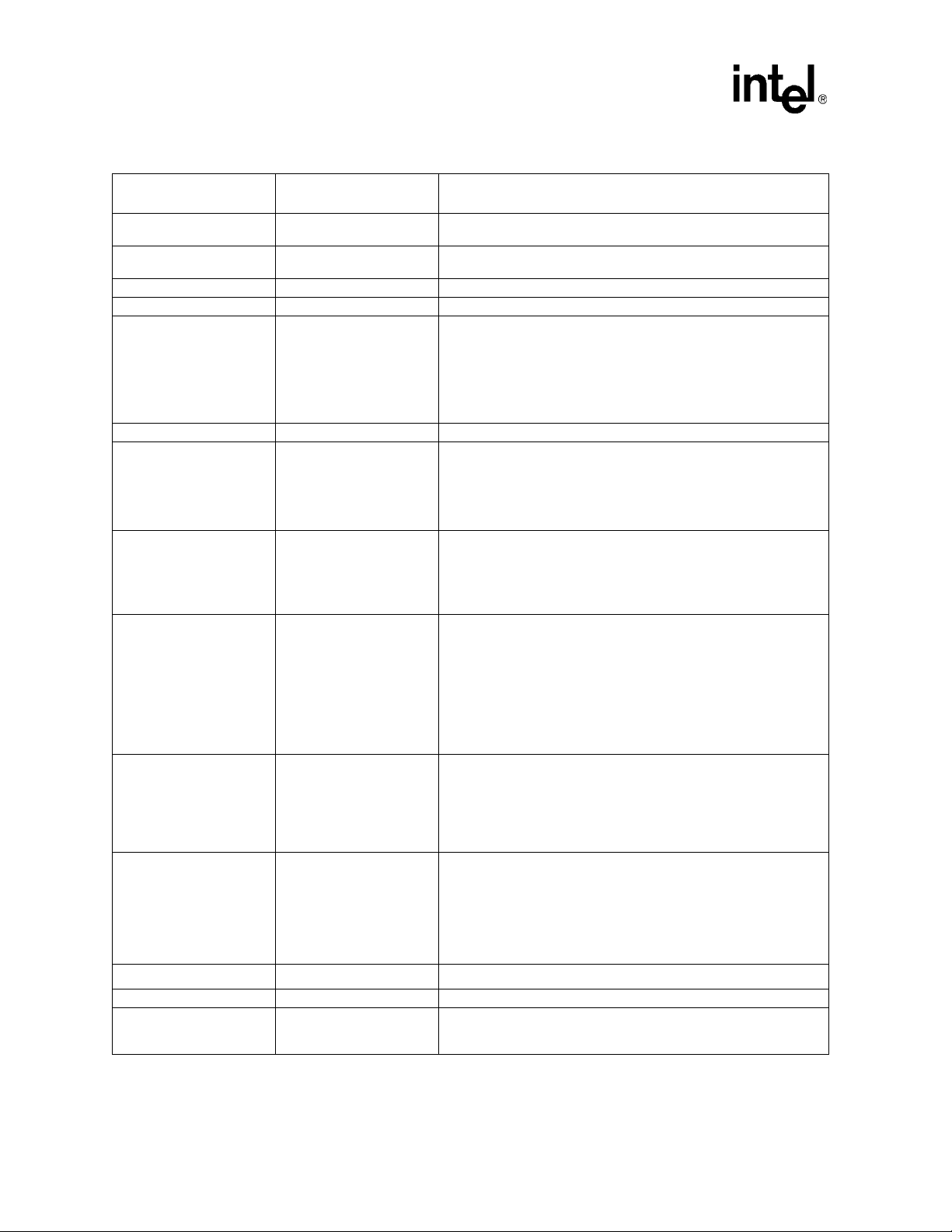

Table 4. Decoupling Recommendations

Volta ge Plan e Voltage Pins Package C (µF)

Number of

Caps

PCI/PCI-X 3.3V VCC33 1210 22 3

PCI/PCI-X 3.3V VCC33 0603 0.1 12

PCI/PCI-X 3.3V VCC33 7343 150 1

DDR/DDRII 2.5/1.8V VCC25/18 0603 0.1 14

34

Page 35

Table 4. Decoupling Recommendations

Intel® 80331 I/O Process or Design Guide

Routing Guidelines

Voltage Plane Voltage Pins Package C (µF)

DDR/DDRII 2.5/1.8V VCC25/18 1210 22 2

DDR/DDRII 2.5/1.8V VCC25/18 7343 150 1

Core 1.5V VCC15 0603 0.1 17

Core 1.5V VCC15 1210 22 2

CPU 1.35V VCC13 0603 0.1 6

CPU 1.35V VCC13 1206 10 1