Fairchild Semiconductor CD4028BCW, CD4028BCN, CD4028BCMX, CD4028BCM Datasheet

October 1987

Revised January 1999

CD4028BC BCD-to-Decimal Decoder

© 1999 Fairchild Semiconductor Corporation DS005959.prf www.fairchildsemi.com

CD4028BC

BCD-to-Decimal Decoder

General Description

The CD4028BC is a BCD-to-decimal or binary-to-octal

decoder consisting of 4 in puts, decoding logic gates, and

10 output buffers. A BCD code applied to the 4 inputs, A, B,

C, and D, results in a high level at the selected 1-of-10 decimal decoded outputs. Similarly, a 3-bit binary code applied

to inputs A, B, and C i s deco ded in octal a t o utputs 0–7. A

high level signal at the D input inhibits octal decoding and

causes outputs 0–7 to go LOW.

All inputs are protected against static discharge damage by

diode clamps to V

DD

and VSS.

Features

■ Wide supply voltage range: 3.0V to 15V

■ High noise immunity: 0.45 V

DD

(typ.)

■ Low power TTL compatibility: fan out of 2 driving 74L

or 1 driving 74LS

■ Low power

■ Glitch free outputs

■ “Positive logic” on inputs and outputs

Applications

• Code conversion

• Address decoding

• Indicator-tube decoder

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram

Pin Assignments for DIP and SOIC

Top View

Order Number Package Number Package Description

CD4028BCM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body

CD4028BCN N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

www.fairchildsemi.com 2

CD4028BC

Truth Table

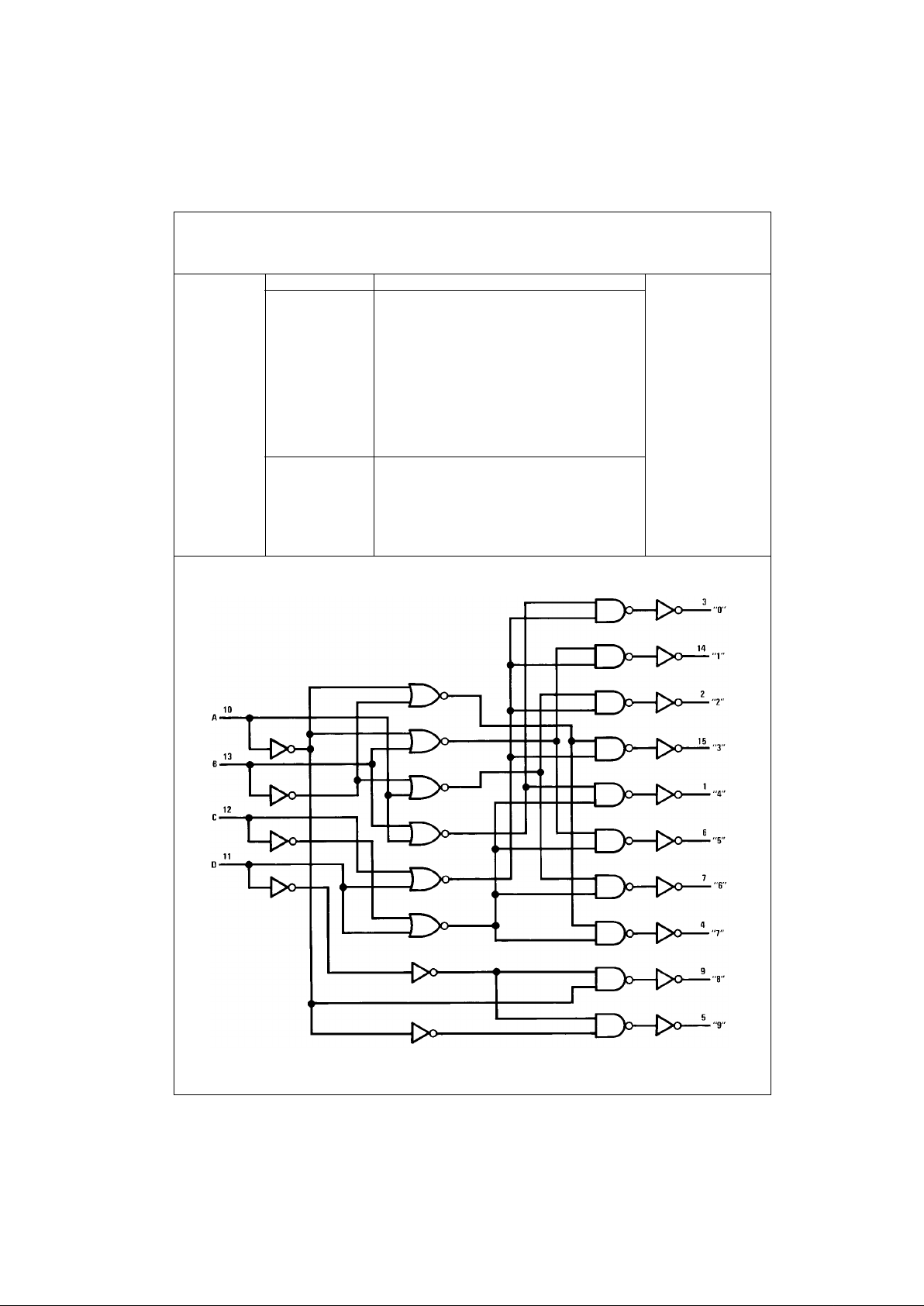

Logic Diagram

DCBA0123456789

00001000000000

00010100000000

00100010000000

00110001000000

01000000100000 BCD States

01010000010000

01100000001000

1 = HIGH Level01110000000100

0 = LOW Level 10000000000010

10010000000001

10100000000010

10110000000001

11000000000010 Extraordinary States

11010000000001

11100000000010

11110000000001

Loading...

Loading...