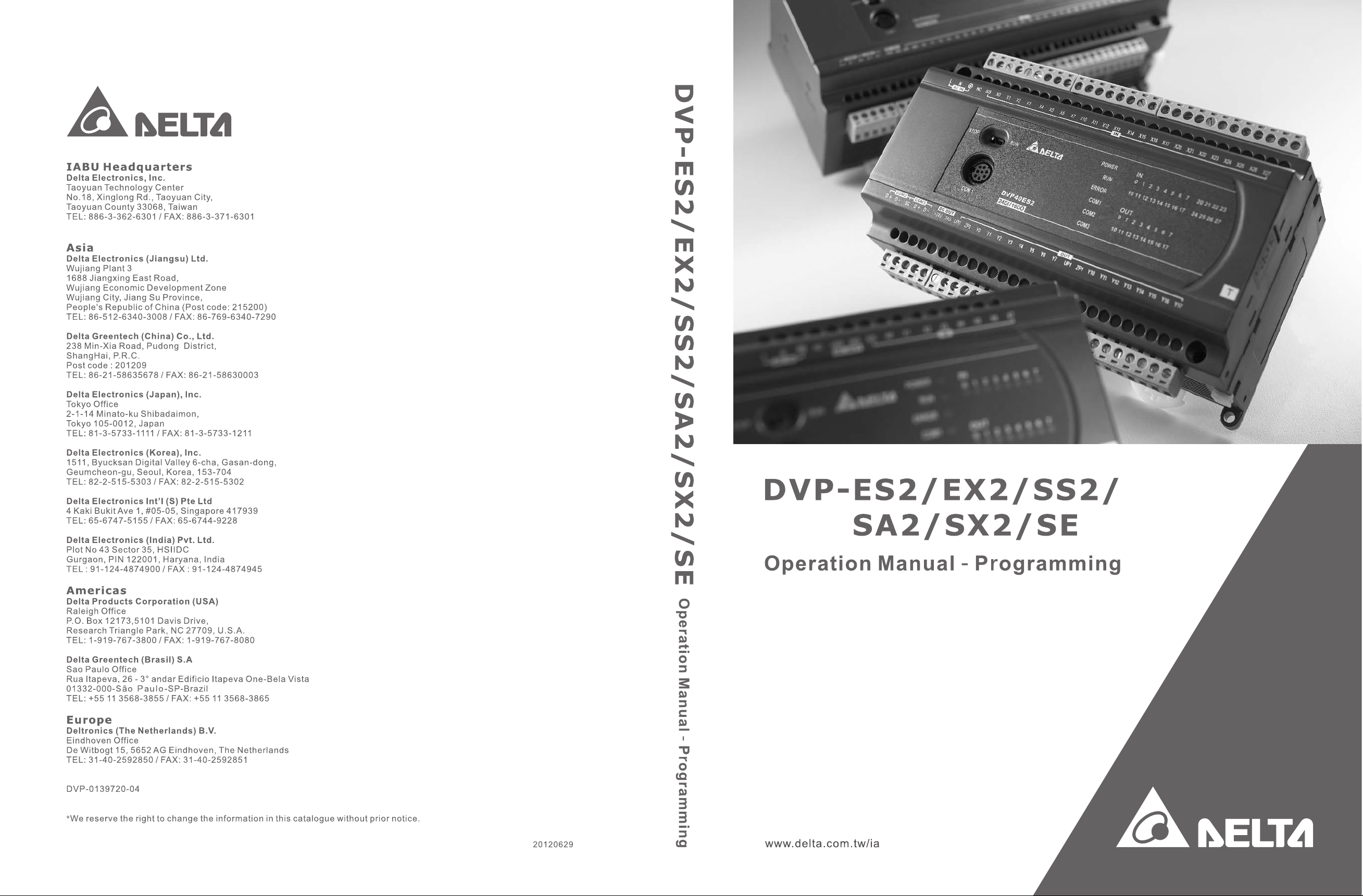

Page 1

Page 2

DVP-ES2/EX2/SS2/SA2/SX2/SE

Operation Manual

Programming

Publication History

Issue Description of Changes Date

First

Edition

Second

Edition

The first edition is issued. 2010/08/04

1. Chapter 2.8 M Relay: Add M1037, M1119, M1182,

M1308, M1346, and M1356, and update the

description of the functions of M1055~M1057and

M1183.

2. Chapter 2.13 Special Data Register: Add D1037,

D1312, D1354, and D1900~D1931, and modify the

attributes of the latched functions of D1062,

D1114, D1115, and D1118.

3. Chapter 2.16 Applications of Special M Relays and

D Registers: Update the description of the

functions of RTCs; add M1037, D1037( Enable SPD

function), M1119( Enable 2-speed ou tput function

of DDRVI instruction) , M1308, D1312( Output

specified pulses or seek Z phase signal when zero

point is achieved) , and M1346( Output clear

signals when ZRN is completed); Easy PLC Link is

changed to PLC Link, and the description is added.

4. Chapter 3.1 Basic Instructions (without API

numbers) and Chapter 3.2 Explanations to Basic

Instructions: Add NP and PN instructions, and add

Chapter 3.7 Numerical List of Instructions (in

alphabetic order)

5. Chapter 3.6 Numerical List of Instructions and

Chapter 3.8 Detailed Instruction Explanation:

Increase explanations of DSPA instruction, and

add floating-point contact type comparison

instructions FLD=, FLD>, FLD<, FLD<>, FLD<=,

FLD>=, FAND=, FAND>, FAND<, FAND<>,

FAND<=, FAND>=, FOR=, FOR>, FOR<, FOR<>,

FOR<=, FOR>=; add the supplementary

description of PLSR instruction and the description

of K11~K19 in DTM instruction mode; update the

description of API166 instruction.

2011/09/15

Page 3

Issue Description of Changes Date

1. SE is added in the title of the manual.

2. Chapter 2.16: The default value in D1062 is K10.

3. API 15 in Chapter 3: The contents about S<D are

deleted in program example 3.

Third

Edition

4. API 148 and API 149 are added in chapter 3.

5. The information related to DVP-SE is added.

6. The information related to DVP32ES-C is added.

7. The descriptions of the models are added in the

contents.

8. Appendix A is added.

2012/05/31

Page 4

DVP-ES2/EX2/SS2/SA2/SX2/SE

Operation Manual

Programming

Contents

1 PLC Concepts

1.1 PLC Scan Method……………………………………………………………………………... 1-2

1.2 Current Flow……………………………………………………………………………………. 1-3

1.3 NO Contact, NC Contact……………………………………………………………………… 1-3

1.4 PLC Registers and Relays………………………………………………………… …………. 1-4

1.5 Ladder Logic Symbols…………………………………………………… …………………… 1-5

1.5.1 Creating a PLC Ladder Program…………………………………………………... 1-6

1.5.2 LD / LDI (Load NO contact / Load NC contact)…………………………………... 1-7

1.5.3 LDP / LDF (Load Rising edge trigger/ Load Falling edge trigger)……………… 1-7

1.5.4 AND / ANI (Connect NO contact in series / Connect NC contact in series)…... 1-7

1.5.5 ANDP / ANDF (Connect Rising edge in series/ Connect Falling edge in

series)…………………………………………………………………………………. 1-7

1.5.6 OR / ORI (Connect NO contact in parallel / Connect NC contact in parallel)…. 1-8

1.5.7 ORP / ORF (Connect Rising edge in parallel/ Connect Falling edge in

parallel)……………………………………………………………………………….. 1-8

1.5.8 ANB (Connect block in series)……………………………………………………... 1-8

1.5.9 ORB (Connect block in parallel)……………………………………………………. 1-8

1.5.10 MPS / MRD / MPP (Branch instructions)………………………………………….. 1-8

1.5.11 STL (Step Ladder Programming)…………………………………………………... 1-9

1.5.12 RET (Return)…………………………………………………………………………. 1-10

1.6 Conversion between Ladder Diagram and Instruction List Mode…………… …………… 1-11

1.7 Fuzzy Syntax…………………………………………………………………………………… 1-12

1.8 Correcting Ladder Diagram…………………………………………………………………… 1-14

1.9 Basic Program Design Examples……………………………………………………………. 1-16

2 Programming Concepts

2.1 ES2/EX2 Memory Map……………………………………………………………………….. 2-2

2.2 SS2 Memory Map…………………………………………………………………………….. 2-5

2.3 SA2 Memory Map…………………………………………………………………………….. 2-8

2.4 SX2 Memory Map…………………………………………………………………………….. 2-11

2.5 Status and Allocation of Latched Memory………………………………………………….. 2-14

2.6 PLC Bits, Nibbles, Bytes, Words, etc……………………………………………………….. 2-15

2.7 Binary, Octal, Decimal, BCD, Hex…………………………………………………………… 2-15

2.8 M Relay………………………………………………………………………………………… 2-17

2.9 S Relay………………………………………………………………………………………… 2-30

2.10 T (Timer) …………… ………………………………………………………………………… 2-30

2.11 C (Counter) …………………………………………………………………………………… 2-31

2.12 High-speed Counters………………………………………………………………………… 2-34

2.13 Special Data Register………………………………………………………………………… 2-39

2.14 E, F Index Registers…………………………………………………………………..……… 2-51

2.15 Nest Level Pointer[N], Pointer[P], Interrupt Pointer [I] …………………..……………….. 2-51

2.16 Applications of Special M Relays and D Registers……………………...………………… 2-55

3 Instruction Set

3.1 Basic Instructions (without API numbers) ………………………..………………………… 3-2

i

Page 5

3.2 Explanations to Basic Instructions…………………………………………………………... 3-3

3.3 Pointers………………………………………………………………………………………… 3-12

3.4 Interrupt Pointers……………………………………………………………………………… 3-12

3.5 Application Programming Instructions……………………………………………………… 3-14

3.6 Numerical List of Instructions (classified according to the function)…………………….. 3-24

3.7 Numerical List of Instructions (in alphabetic order)……………………………………….. 3-33

3.8 Detailed Instruction Explanation…………………………………………………………….. 3-42

4 Communications

4.1 Communication Ports…………………………………………………………………………. 4-2

4.2 Communication Protocol ASCII mode……………………………………………………….. 4-3

4.2.1 ADR (Communication Address) …………………………………………………… 4-3

4.2.2 CMD (Command code) and DATA………………………………………………… 4-3

4.2.3 LRC CHK (checksum) ……………………………………………………………… 4-5

4.3 Communication Protocol RTU mode………………………………………………………… 4-7

4.3.1 Address (Communication Address) ………………………………………………. 4-7

4.3.2 CMD (Command code) and DATA………………………………………………… 4-8

4.3.3 CRC CHK (check sum) …………………………………………………………….. 4-9

4.4 PLC Device Address…………………………………………………………………………... 4-11

4.5 Command Code……………………………………………………………………………….. 4-13

4.5.1 Command Code: 01, Read Status of Contact (Input point X is not included)… 4-13

4.5.2 Command Code: 02, Read Status of Contact (Input point X is included)……... 4-14

4.5.3 Command Code: 03, Read Content of Register (T, C, D)………………………. 4-15

4.5.4 Command Code: 05, Force ON/OFF single contact………………………… ….. 4-16

4.5.5 Command Code: 06, Set content of single register……………………………… 4-17

4.5.6 Command Code: 15, Force ON/OFF multiple contacts…………………………. 4-18

4.5.7 Command Code: 16, Set content of multiple registers………………………….. 4-18

5 Sequential Function Chart

5.1 Step Ladder Instruction [STL], [RET] ………………………………………………………. 5-2

5.2 Sequential Function Chart (SFC) …………………………………………………………… 5-2

5.3 The Operation of STL Program……………………………………………………………… 5-4

5.4 Points to Note for Designing a Step Ladder Program…………………………………….. 5-9

5.5 Types of Sequences………………………………………………………………………….. 5-11

5.6 IST Instruction…………………………………………………………………………………. 5-22

6 Troubleshooting

6.1 Common Problems and Solutions…………………………………………………………... 6-2

6.2 Error code Table (Hex) …………………………………………………………................... 6-4

6.3 Error Detection Devices………………………………………………………….................. 6-6

7 CANopen Function and Operation

7.1 The Introduction of CANopen…………………………………………………………........... 7-2

7.1.1 The Description of the CANopen Functions……………………………………… 7-2

7.1.2 The Input/Output Mapping Areas………………………………………………….. 7-3

7.2 The Installation and the Network Topology…………………………………………………. 7-3

7.2.1 The Dimensions…………………………………………………………................. 7-3

7.2.2 The Profile………………………………………………………….......................... 7-4

7.2.3 The CAN Interface and the Network Topology…………………………………… 7-4

7.3 The CANopen Protocol………………………………………………………….................... 7-8

7.3.1 The Introduction of the CANopen Protocol……………………………………….. 7-8

7.3.2 The CANopen Communication Object………………………… …………………. 7-9

7.3.3 The Predefined Connection Set…………………………………………………… 7-14

ii

Page 6

7.4 Sending SDO, NMT and Reading Emergency Message through the Ladder Diagram... 7-15

7.4.1 Data St ructure of SDO Request Message………………………………………... 7-15

7.4.2 Data Structure of NMT Message…………………………………………………... 7-18

7.4.3 Data Structure of EMERGENCY Request Message…………………………….. 7-19

7.4.4 Example on Sending SDO through the Ladder Diagram……………………….. 7-21

7.5 Indicators and Troubleshooting…………………………………………………………........ 7-23

7.5.1 Description of Indicators…………………………………………………………..... 7-23

7.5.2 CANopen Network Node S tate Display…………………………………………… 7-24

7.6 Application Example…………………………………………………………......................... 7-27

7.7 Object Dictionary………………………………………………………….............................. 7-35

Appendix A

A.1 Installing the USB Driver…………………………………………… ……………................. A-2

iii

Page 7

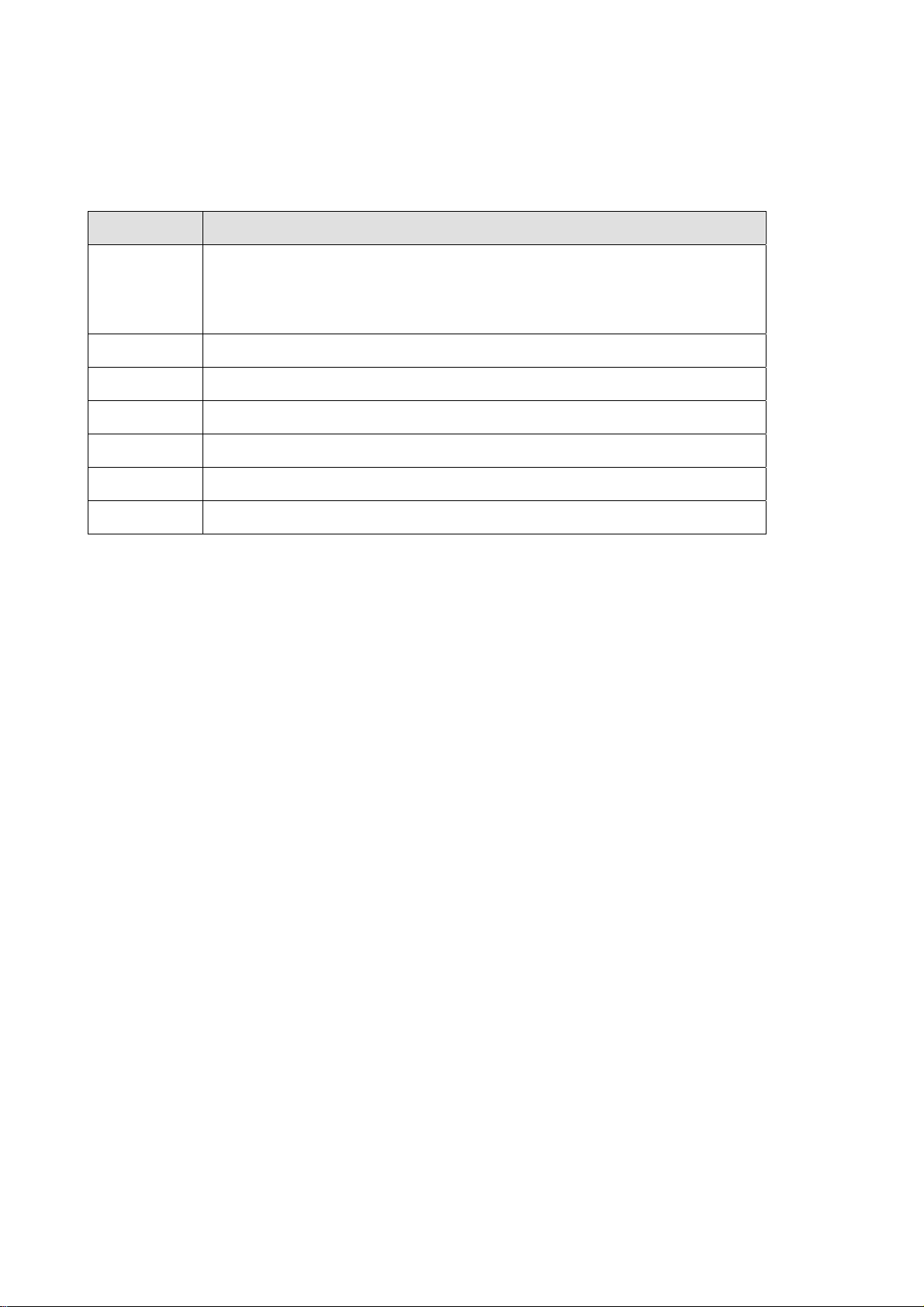

The DVP-ES2 series PLCs, the DVP-ES2-C series PLCs, the DVP-EX2 series

PLCs, the DVP-SS2 series PLCs, the DVP-SA2 series PLCs, the DVP-SX2

series PLCs, and the DVP-SE series PLCs are listed below.

Series Model name

DVP16ES200R, DVP16ES200T, DVP24ES200R, DVP24ES200T,

DVP-ES2

DVP32ES200R, DVP32ES200T, DVP32ES211T, DVP40ES200R,

DVP40ES200T, DVP60ES200R, DVP60ES200T,

DVP32ES200RC, DVP32ES200TC

DVP-ES2-C

DVP-EX2

DVP-SS2

DVP-SA2

DVP-SX2

DVP-SE

DVP32ES200RC, DVP32ES200TC

DVP20EX200R, DVP20EX200T, DVP30EX200R, DVP30EX200T

DVP14SS211R, DVP14SS211T

DVP12SA211R, DVP12SA211T

DVP20SX211R, DVP20SX211S, DVP20SX211T

DVP12SE11R, DVP12SE11T

iv

Page 8

v

Page 9

PLC Concepts

This chapter introduces basic and advanced concepts of ladder logic, which is the mostly

adopted programming language of PLC. Users familiar with the PLC concepts can move to

the next chapter for further programming concepts. However, for users not familiar with the

operating principles of PLC, please refer to this chapter to get a full understanding of PLC

concepts.

Chapter Contents

PLC Scan Method...............................................................................................................1-2

1.1

1.2 Current Flow........................................................................................................................1-3

1.3 NO Contact, NC Contact ....................................................................................................1-3

1.4 PLC Registers and Relays.................................................................................................1-4

1.5 Ladder Logic Symbols.......................................................................................................1-5

1.5.1 Creating a PLC Ladder Program...........................................................................1-6

1.5.2 LD / LDI (Load NO contact / Load NC contact).....................................................1-7

1.5.3 LDP / LDF (Load Rising edge trigger/ Load Falling edge trigger).........................1-7

1.5.4 AND / ANI (Connect NO contact in series / Connect NC contact in series)..........1-7

1.5.5 ANDP / ANDF (Connect Rising edge in series/ Connect Falling edge in series)..1-7

1.5.6 OR / ORI (Connect NO contact in parallel / Connect NC contact in parallel) .......1-8

1.5.7 ORP / ORF (Connect Rising edge in parallel/ Connect Falling edge in parallel)..1-8

1.5.8 ANB (Connect block in series) ..............................................................................1-8

1.5.9 ORB (Connect block in parallel)............................................................................1-8

1.5.10 MPS / MRD / MPP (Branch instructions) ..............................................................1-8

1.5.11 STL (Step Ladder Programming) ..........................................................................1-9

1.5.12 RET (Return) .......................................................................................................1-10

1.6 Conversion between Ladder Diagram and Instruction List Mode...............................1-1 1

1.7 Fuzzy Syntax.....................................................................................................................1-12

1.8 Correcting Ladder Diagram.............................................................................................1-14

1.9 Basic Program Design Examples ...................................................................................1-16

1-1

Page 10

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

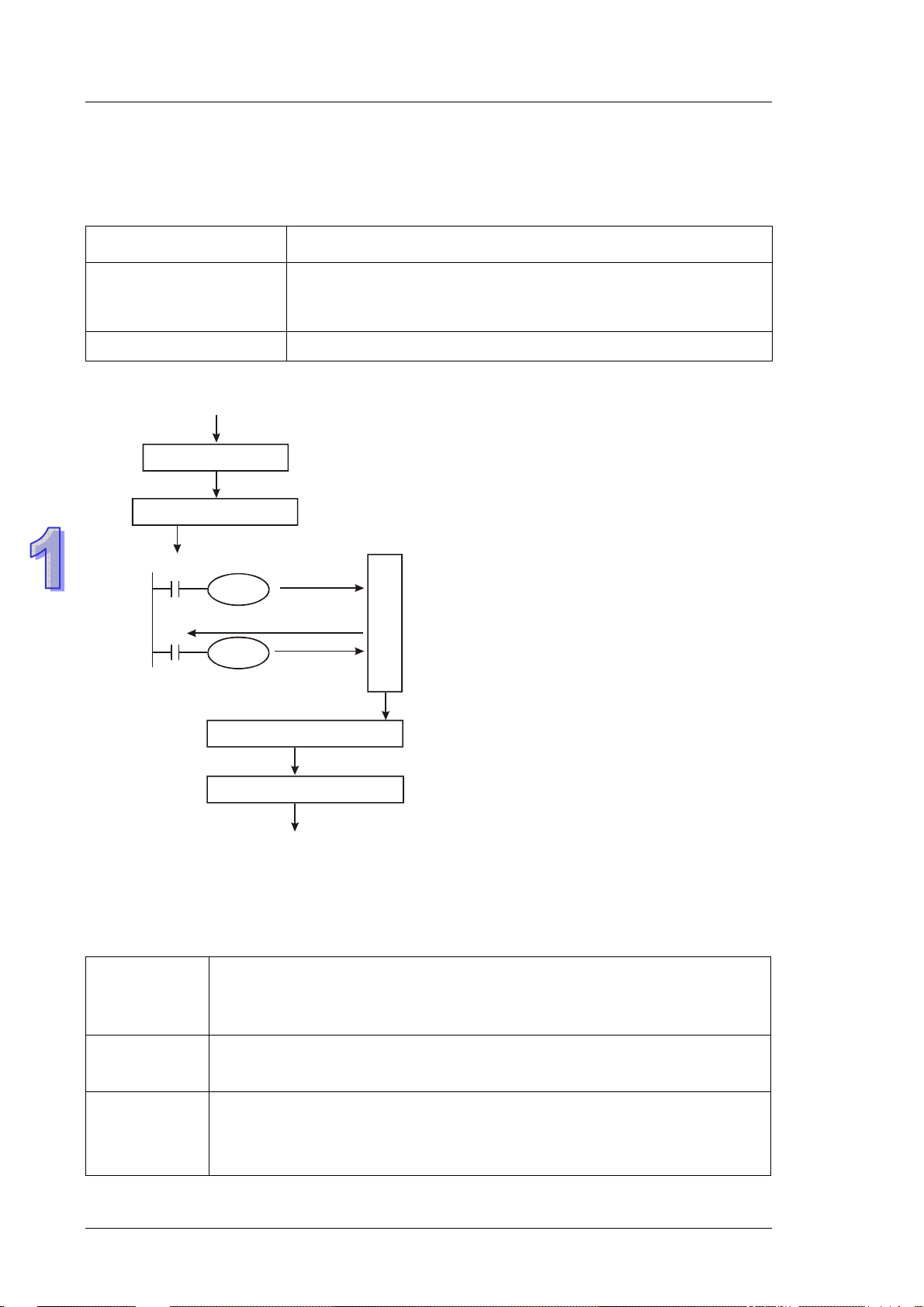

1.1 PLC Scan Method

PLC utilizes a standard scan method when evaluating user program.

Scanning process:

Scan input status

Evaluate user program

Refresh the outputs

Input sig nal

Program

Output

Input X

Input terminal

Store to memory

Input signal memory

Read X0 status from memory

X0

Y0

Read Y0 state from memory

Y0

M0

Output latched memory

Read the physical input status and store the data in internal

memory.

Evaluate the user program with data stored in internal memory.

Program scanning starts from up to down and left to right until

reaching the end of the program.

Write the evaluated data to the physical outputs

Input signal:

PLC reads the ON/OFF status of each input and

stores the status into memory before evaluating

the user program.

Once the external input status is stored into

internal memory, any change at the external

inputs will not be updated until next scan cycle

Writ e Y0 stat e into

Device Memory

starts.

Program:

PLC executes instructions in user program from

top to down and left to right then stores the

Write M0 state into

Output

evaluated data into internal memory. Some of this

memory is latched.

Output:

When END command is reached the program

Output terminal

evaluation is complete. The output memory is

transferred to the external physical outputs.

Output Y

Scan time

The duration of the full scan cycle (read, evaluate, write) is called “scan time.” With more I/O or

longer program, scan time becomes longer.

PLC measures its own scan time and stores the value (0.1ms) in register

Read

scan time

Measure

scan time

D1010, minimum scan time in register D1011, and maximum scan time in

register D1012.

Scan time can also be measured by toggling an output every scan and then

measuring the pulse width on the output being toggled.

Scan time can be calculated by adding the known time required for each

Calculate

scan time

instruction in the user program. For scan time information of individual

instruction please refer to Ch3 in this manual.

1-2

Page 11

1. PLC Concepts

Scan time exception

PLC can process certain items faster than the scan time. Some of these items interrupts and halt

the scan time to process the interrupt subroutine program. A direct I/O refresh instruction REF

allows the PLC to access I/O immediately during user program evaluation instead of waiting until

the next scan cycle.

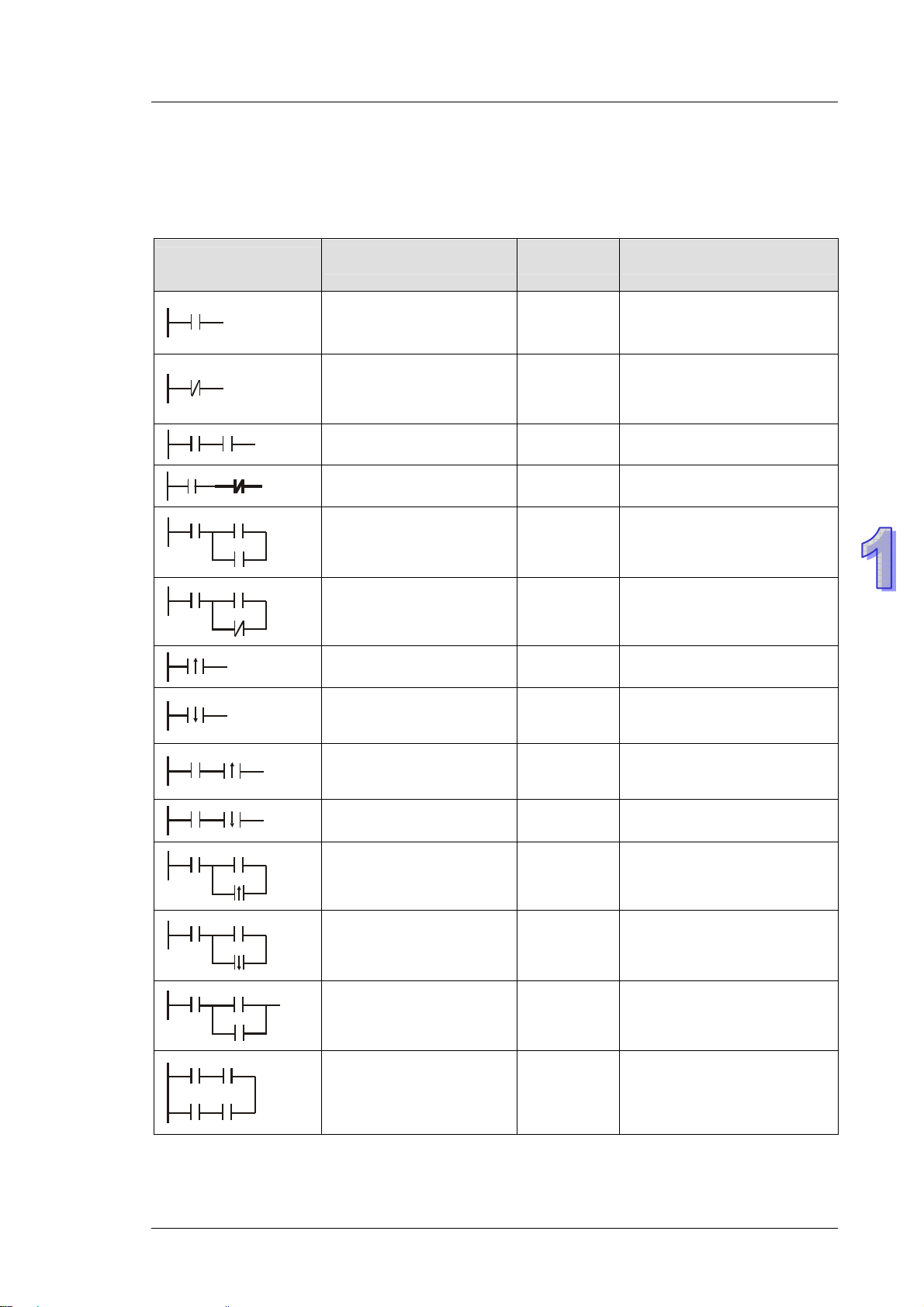

1.2 Current Flow

Ladder logic follows a left to right principle. In the example below, the current flows through paths

started from either X0 or X3.

X0

X1 X2

Y0

Y0

X3

Reverse Current

When a current flows from right to left, which makes a reverse current logic, an error will be

detected when compiling the program. The example below shows the reverse current flow.

X0

X4

X1

X2

Y0

Y0

X3

a

X4 X5

b

X6

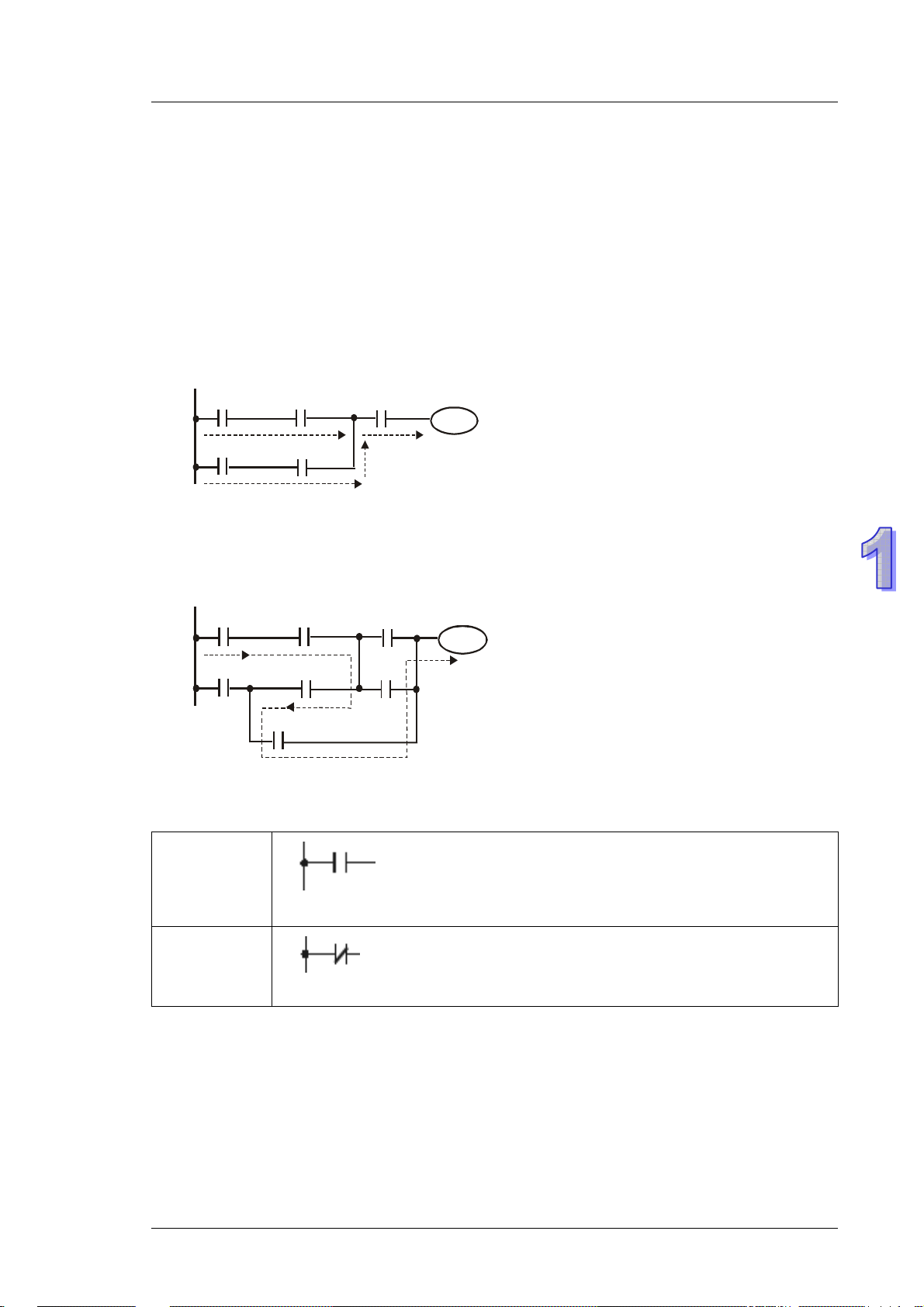

1.3 NO Contact, NC Contact

NO contact

Normally Open Contact, A contact

NC Contact

Normally Closed Contact, B contact

1-3

Page 12

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

1.4 PLC Registers and Relays

Introduction to the basic internal devices in a PLC

Bit memory represents the physical input points and receives external input

X

(Input Relay)

Y

(Output Relay)

M

(Internal Relay)

S

(Step Relay)

signals.

Device indication: Indicated as X and numbered in octal, e.g. X0~X7,

X10~X17…X377

Bit memory represents the physical output points and saves the status to be

refreshed to physical output devices.

Device indication: Indicated as Y and numbered in octal, e.g. Y0~Y7,

Y10~Y17. ..Y377

Bit memory indicates PLC status.

Device indication: Indicated as M and numbered in decimal, e.g. M0, M1,

M2…M4095

Bit memory indicates PLC status in Step Function Control (SFC) mode. If no

STL instruction is applied in program, step point S can be used as an internal

relay M as well as an annunciator.

Device indication: Indicated as S and numbered in decimal, e.g. S0, S1,

S2…S1023

T

(Relay)

(Word)

(Dword)

C

(Counter)

(Relay)

(Word)

(Dword)

D

(Data register)

(Word)

E, F

(Index register)

(Word)

Bit, word or double word memory used for timing

register in it. When its coil is ON and the set time is reached, the associated

contact will be energized. Every timer has its resolution (unit:

1ms/10ms/100ms).

and has coil, contact and

Device indication: Indicated as T and numbered in decimal, e.g. T0, T1,

T2…T255

Bit, word or double word memory used for counting and has coil, contact and

register in it. The counter count once (1 pulse) when the coil goes from OFF to

ON. When the predefined counter value is reached, the associated contact will

be energized. There are 16-bit and 32-bit high-speed counters available for

users.

Device indication: Indicated as C and numbered in decimal, e.g. C0, C1,

C2…C255

Word memory stores values and parameters for data operations. Every

register is able to store a word (16-bit binary value). A double word will occupy

2 consecutive data registers.

Device indication: Indicated as D and numbered in decimal, e.g. D0, D1,

D2…D4999

Word memory used as a modifier to indicate a specified device (word and

double word) by defining an offset. Index registers not used as a m odifier can

be used as general purpose register.

Device indication: indicated as E0 ~ E7 and F0 ~ F7.

1-4

Page 13

1. PLC Concepts

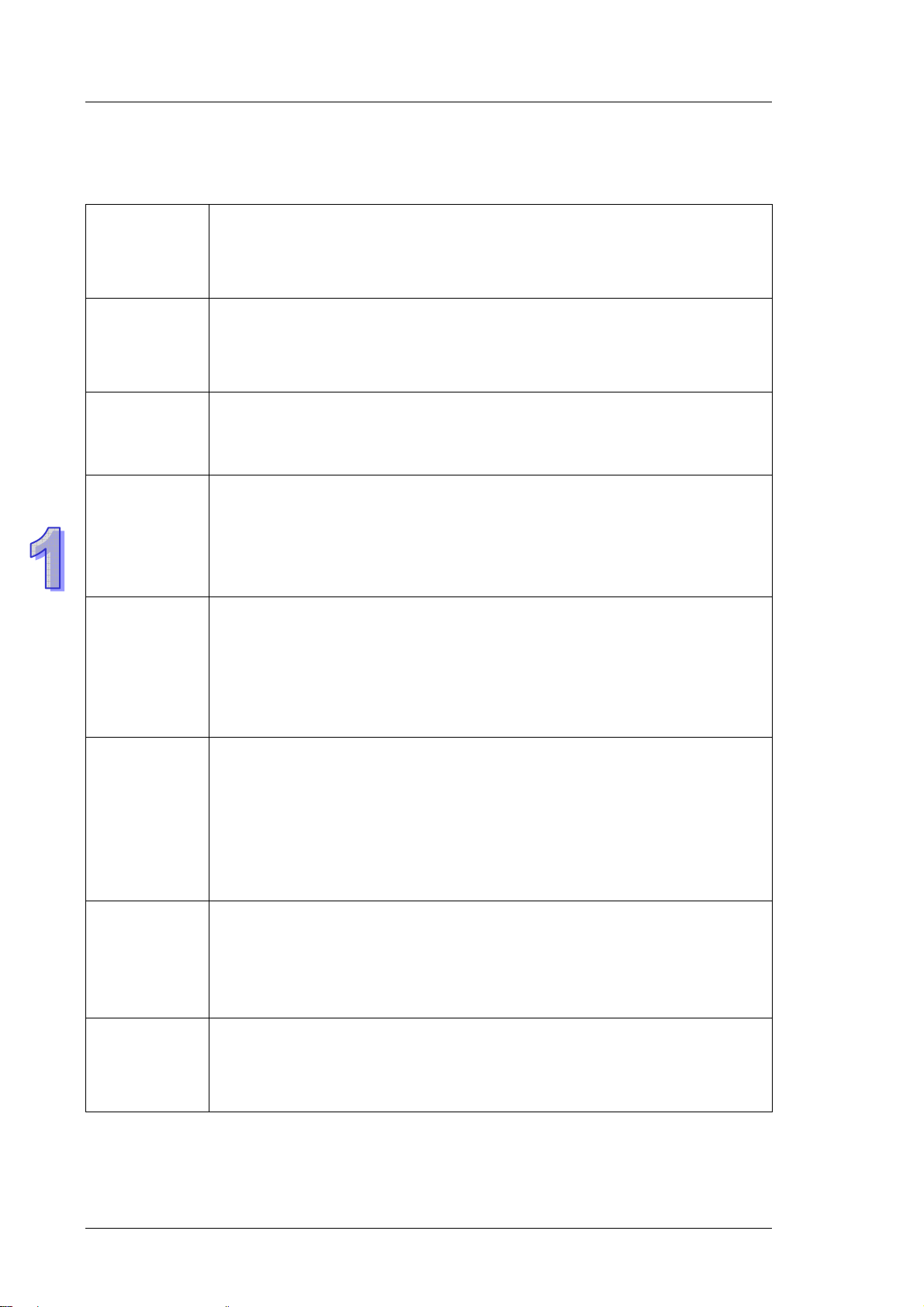

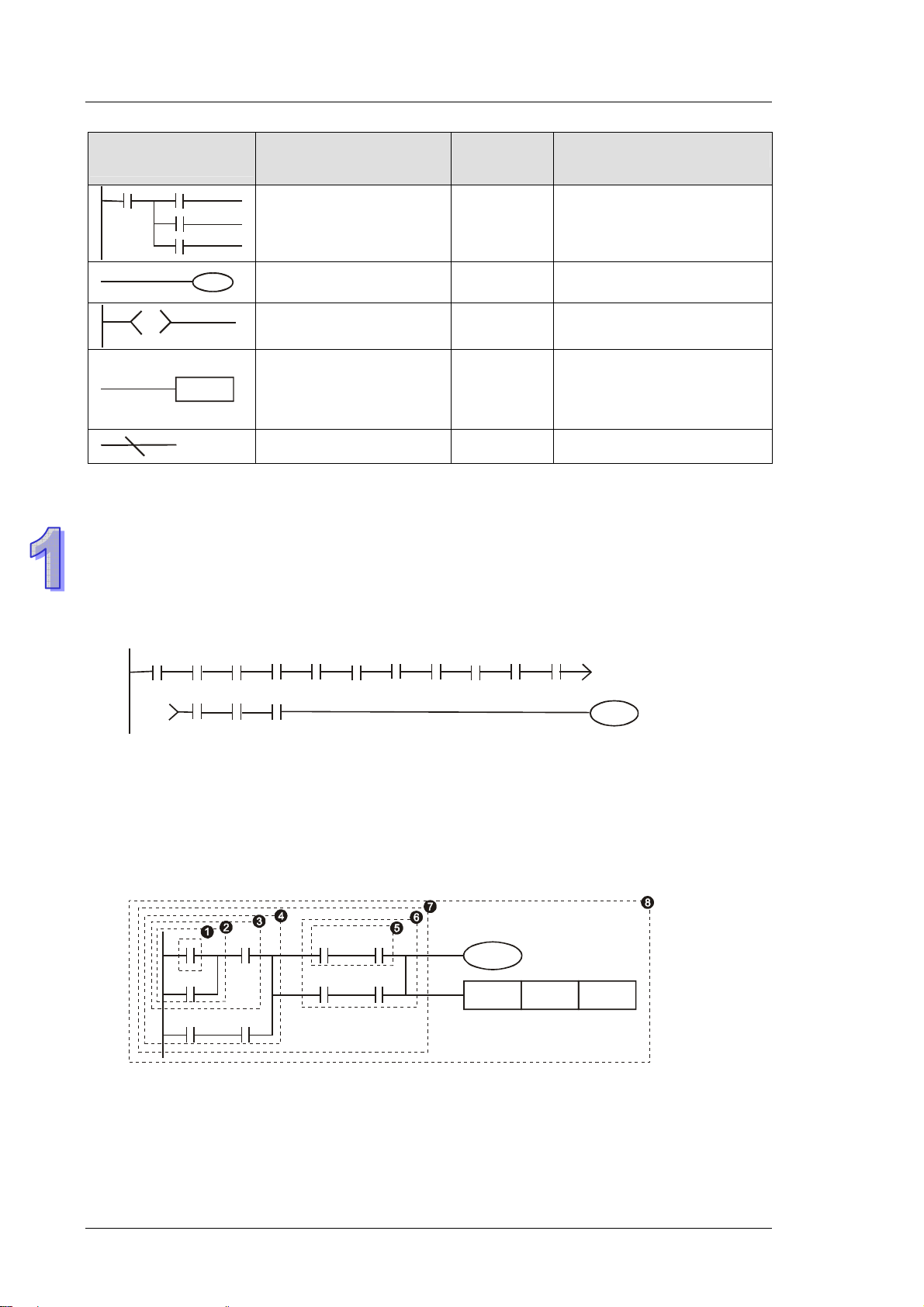

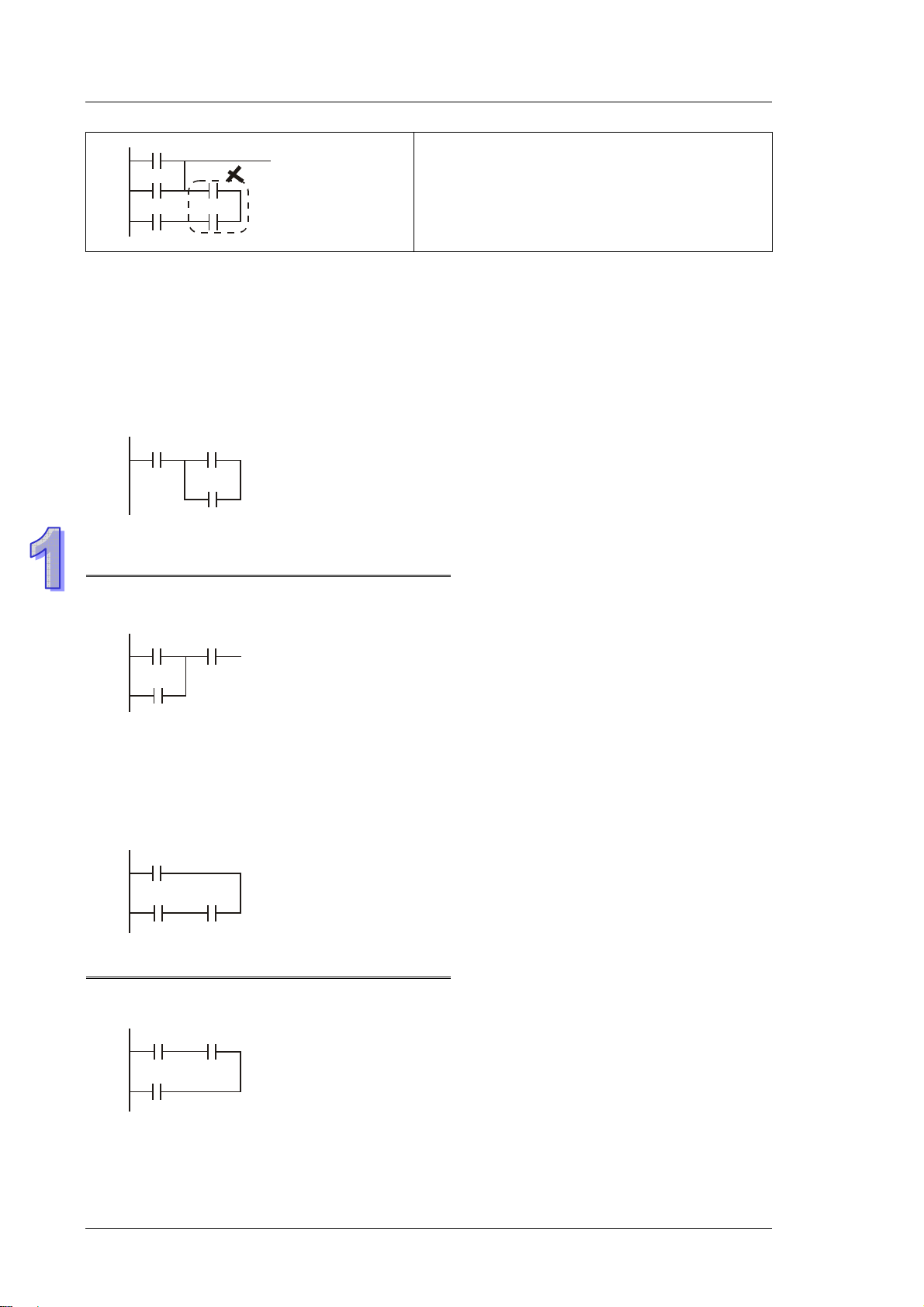

1.5 Ladder Logic Symbols

The following table displays list of WPLSoft symbols their descripti on, command, and memory

registers that are able to use the symbol.

Ladder Diagram

Structure

Explanation Instruction Available Devices

NO (Normally Open)

contact / A contact

NC (Normally Closed)

contact / B contact

NO contact in series

NC contact in series

NO contact in parallel

NC contact in parallel

Rising-edge trigger

switch

LD X, Y, M, S, T, C

LDI X, Y, M, S, T, C

AND X, Y, M, S, T, C

ANI X, Y, M, S, T, C

OR X, Y, M, S, T, C

ORI X, Y, M, S, T, C

LDP X, Y, M, S, T, C

Falling-edge trigger

switch

Rising-edge trigger in

series

Falling-edge trigger in

series

Rising-edge trigger in

parallel

Falling-edge trigger in

parallel

Block in series

LDF X, Y, M, S, T, C

ANDP X, Y, M, S, T, C

ANDF X, Y, M, S, T, C

ORP X, Y, M, S, T, C

ORF X, Y, M, S, T, C

ANB None

Block in parallel

ORB None

1-5

Page 14

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

Ladder Diagram

Structure

Explanation Instruction Available Devices

MPS

S

Multiple output branches

Output coil

Step ladder

MRD

None

MPP

OUT Y, M, S

STL S

Basic / Application

instruction

Inverse logic

-

INV None

Basic instructions and API

instructions. Please refer to

chapter 3 Instruction Set

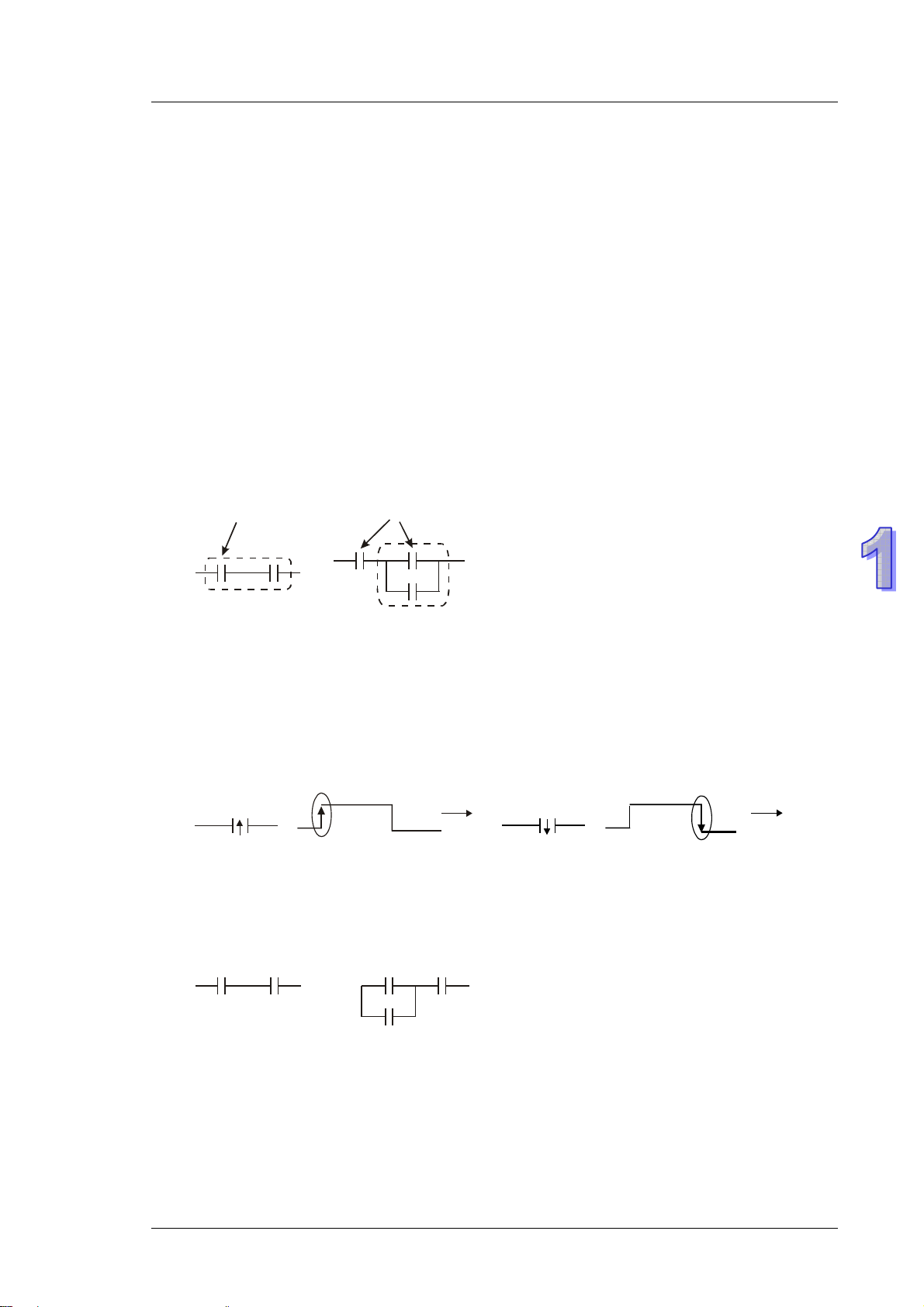

1.5.1 Creating a PLC Ladder Program

The editing of the program should start from the left side bus line to the right side bus line, and from

up to down. However, the right side bus line is omitted when editing in WPLSoft. A single row can

have maximum 11 contacts on it. If more than 11 contacts are connected, a continuous symbol “0”

will be generated automatically and the 12th contact will be placed at the start of next row. The

same input points can be used repeatedly. See the figure below:

X1 X2

X0

X12 X13

X11

0

X4 X5 X6 X7

X3

X10

C0

C1

0

Y1

When evaluating the user program, PLC scan starts from left to right and proceeds to next row

down until the PLC reaches END instruction. Output coils and basic / application instructions

belong to the output process and are placed at the right of ladder diagram. The sample program

below explains the execution order of a ladder diagram. The numbers in the black circles indicate

the execution order.

1-6

X0 X1 Y1 X4

Y1

M0

X3

M1

T0

M3

TMR T0 K10

Page 15

Execution order of the sample program:

1 LD X0

2 OR M0

3 AND X1

4 LD X3

AND M1

ORB

5 LD Y1

AND X4

6 LD T0

AND M3

ORB

7 ANB

8 OUT Y1

TMR T0 K10

1.5.2 LD / LDI (Load NO contact / Load NC contact)

LD or LDI starts a row or block

LD instruction LD instruction

1. PLC Concepts

AND block OR bl oc k

1.5.3 LDP / LDF (Load Rising edge trigger/ Load Falling edge trigger)

Similar to LD instruction, LDP and LDF instructions only act at the rising edge or falling edge when

the contact is ON, as shown in the figure below.

X0

Rising-edge

OFF

ON

OFF

Time

X0

OFF

Falling-edge

ON

OFF

Time

1.5.4 AND / ANI (Connect NO contact in series / Connect NC contact in series)

AND (ANI) instruction connects a NO (NC) contact in series with another device or block.

AND instruction AND instruction

1.5.5 ANDP / ANDF (Connect Rising edge in series/ Connect Falling edge in series)

Similar to AND instruction, ANDP (ANDF) instruction connects rising (falling) edge triggers in series

with another device or block.

1-7

Page 16

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

1.5.6 OR / ORI (Connect NO contact in parallel / Connect NC contact in parallel)

OR (ORI) instruction connects a NO (NC) in parallel with another device or block.

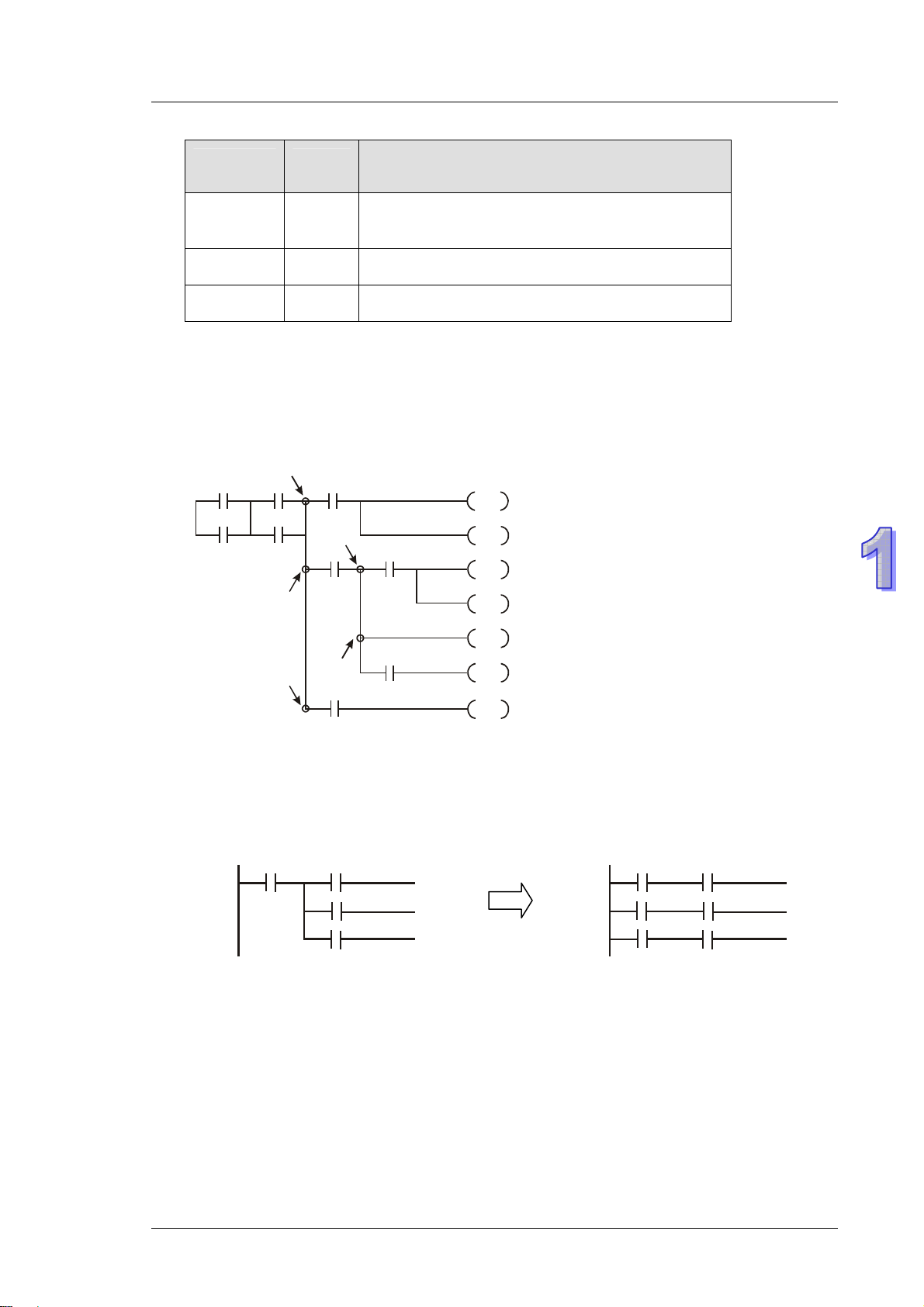

OR instruction OR instruction OR instruction

1.5.7 ORP / ORF (Connect Rising edge in parallel/ Connect Falling edge in parallel)

Similar to OR instruction, ORP (ORF) instruction connects rising (falling) edge triggers in parallel

with another device or block

1.5.8 ANB (Connect block in series)

ANB instruction connects a block in series with another block

ANB command

1.5.9 ORB (Connect block in parallel)

ORB instruction connects a block in parallel with another block

ORB instruction

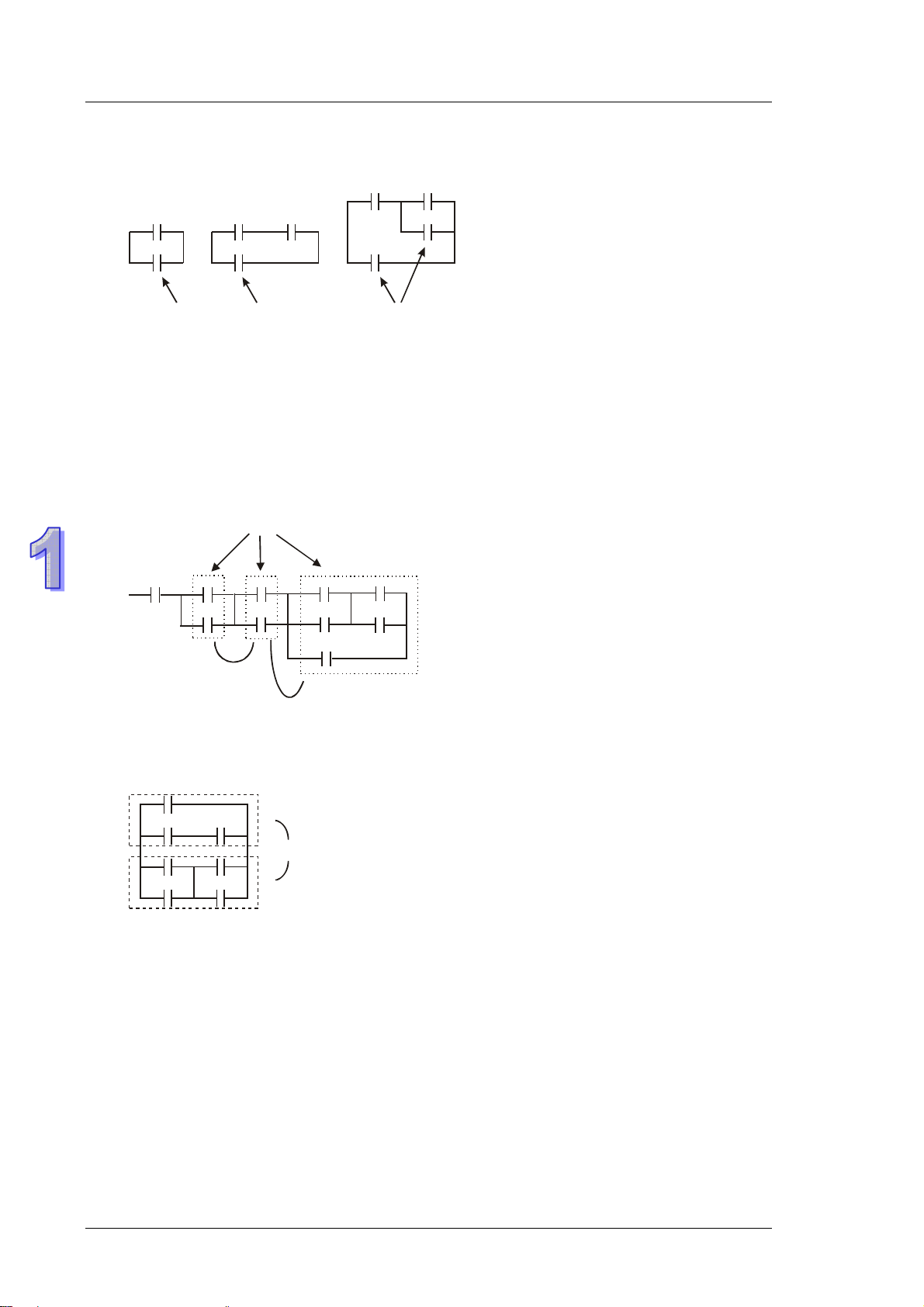

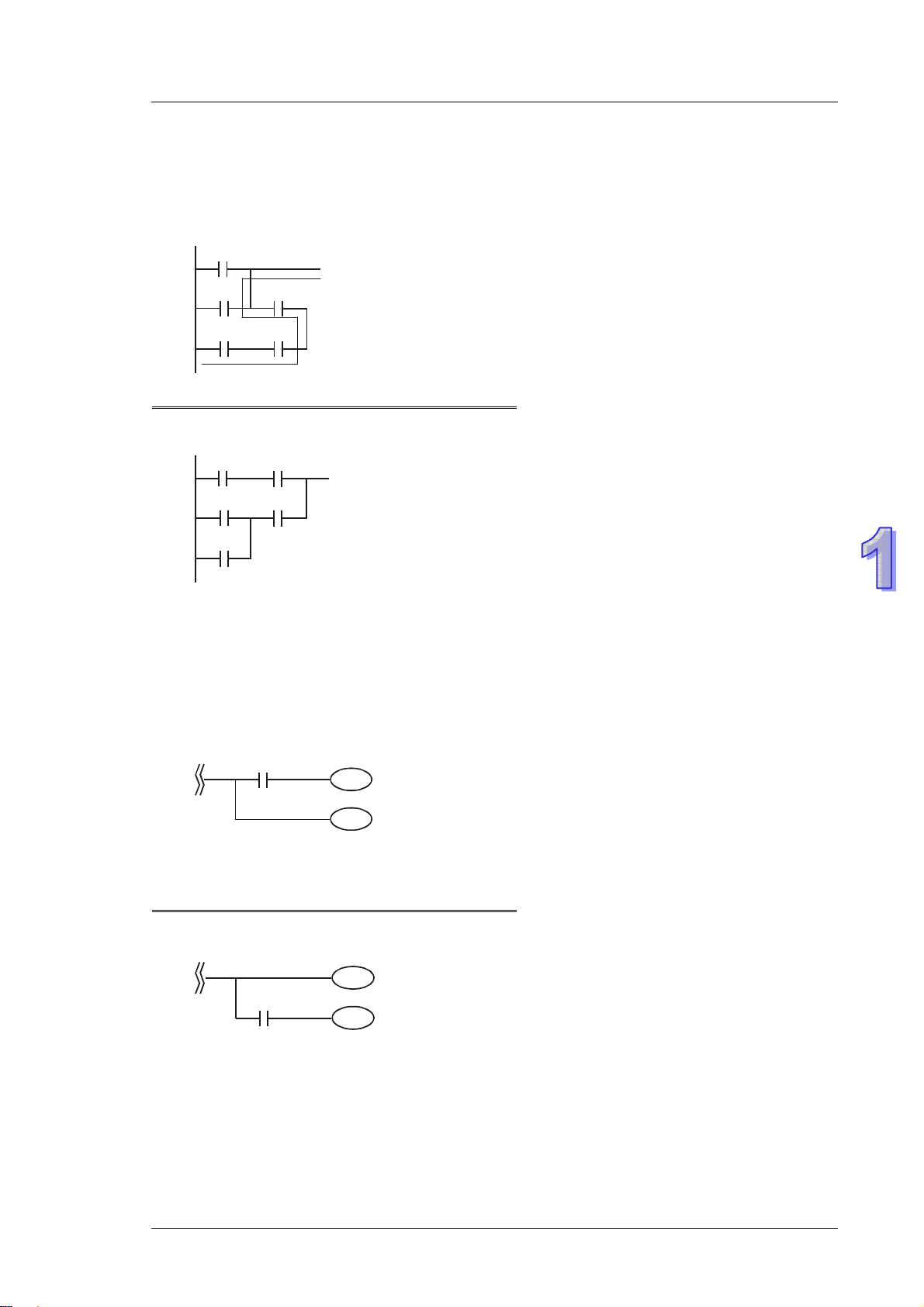

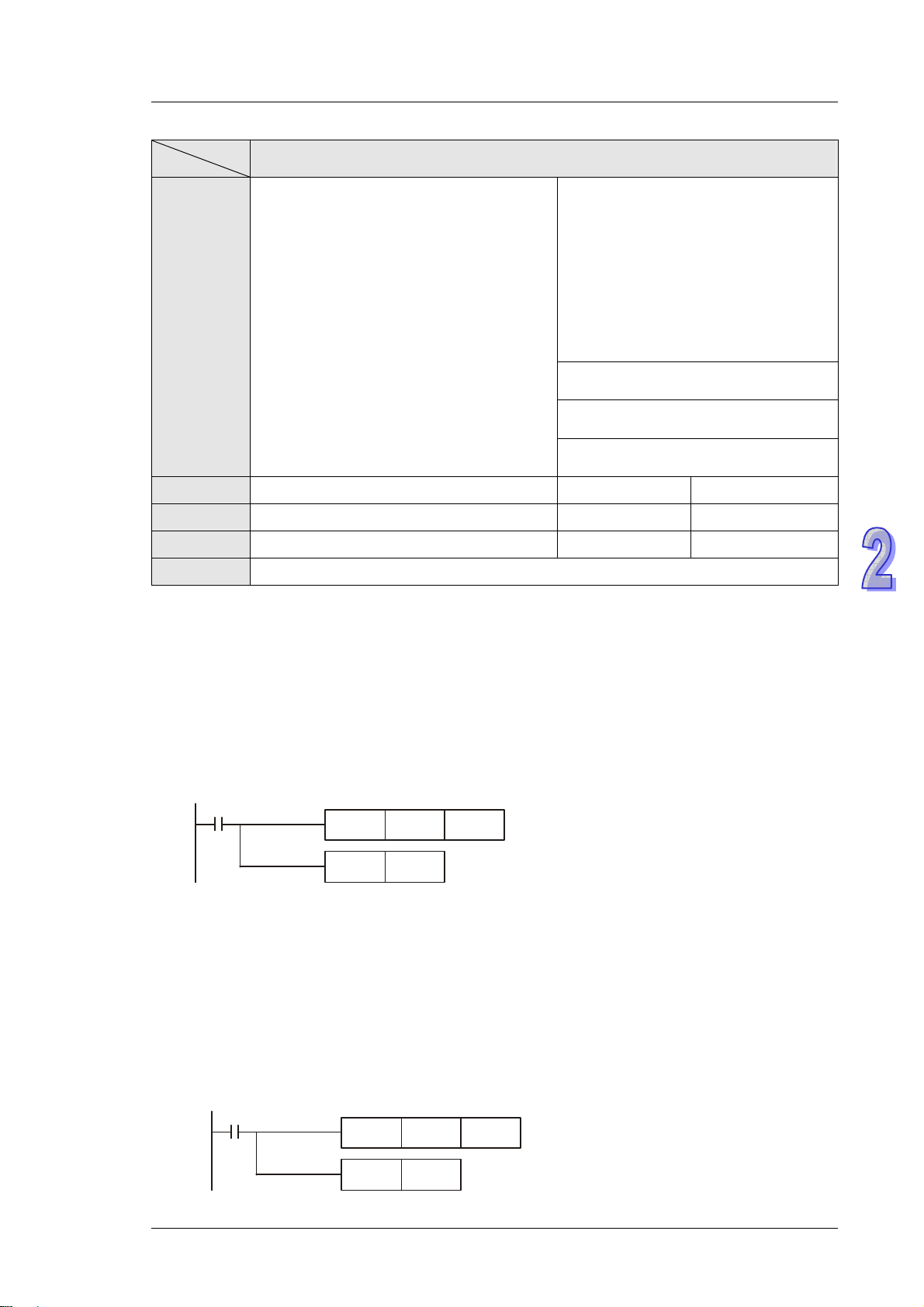

1.5.10 MPS / MRD / MPP (Branch instructions)

These instructions provide a method to create multiplexed output branches based on current result

stored by MPS instruction.

1-8

Page 17

1. PLC Concepts

Branch

instruction

Branch

Symbol

Description

Start of branches. Stores current result of

MPS

┬

program evaluation. Max. 8 MPS-MPP pairs can

be applied

MRD

MPP

├

└

Reads the stored current result from previous

MPS

End of branches. Pops (reads then resets) the

stored result in previous MPS

Note: When compiling ladder diagram with WPLSoft, MPS, MRD and MPP could be automatically

added to the compiled results in instruction format. However, sometimes the branch instructions

are ignored by WPLSoft if not necessary. Users programming in instruction format can enter branch

instructions as required.

Connection points of MPS, MRD and MPP:

MPS

MPS

MRD

MPP

MPP

Note: Ladder diagram editor in ISPSoft does not support MPS, MRD and MPP instructions. To

achieve the same results as branch instructions, users have to connect all branches to the left

hand bus bar.

WPLSoft

ISPSoft

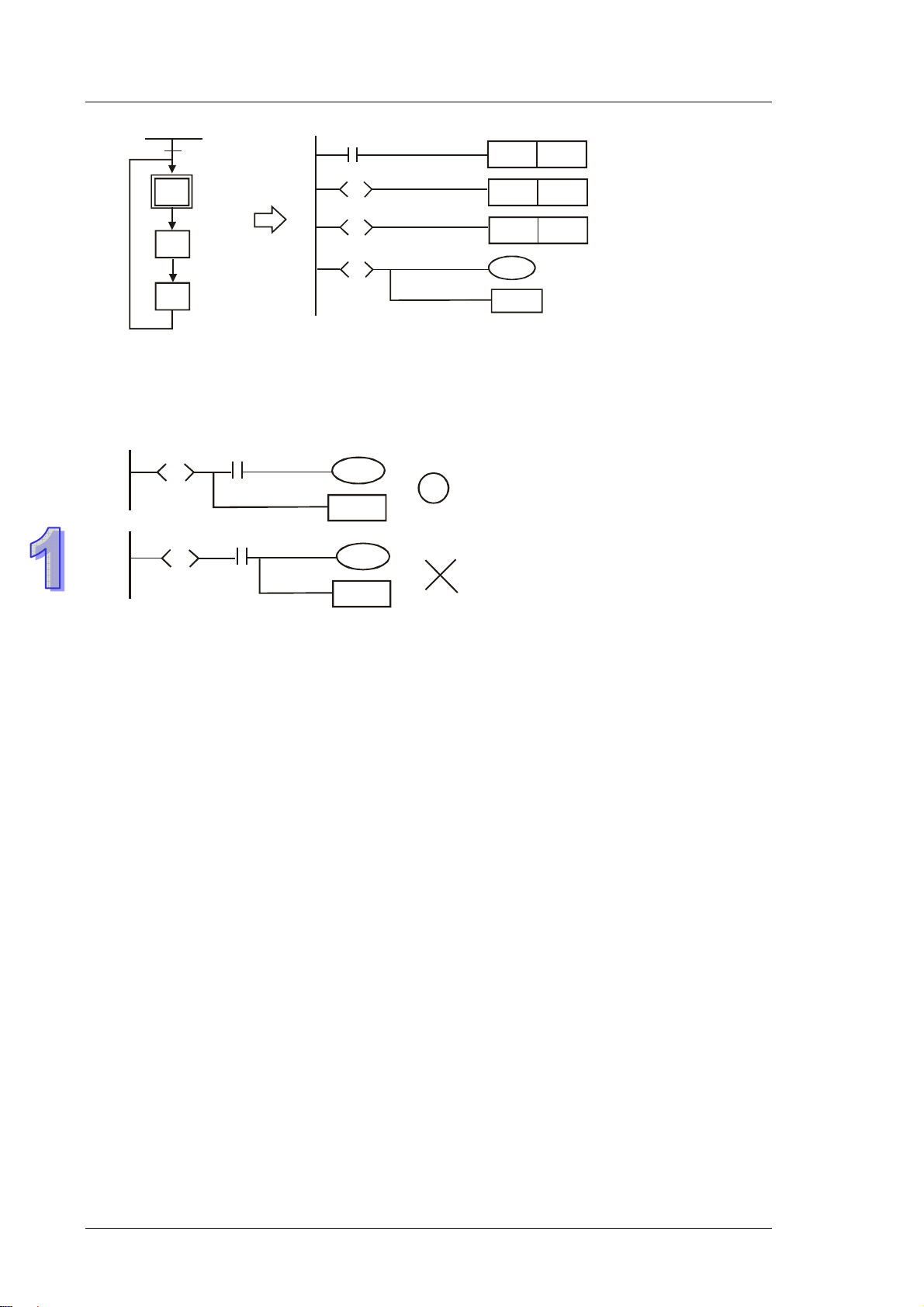

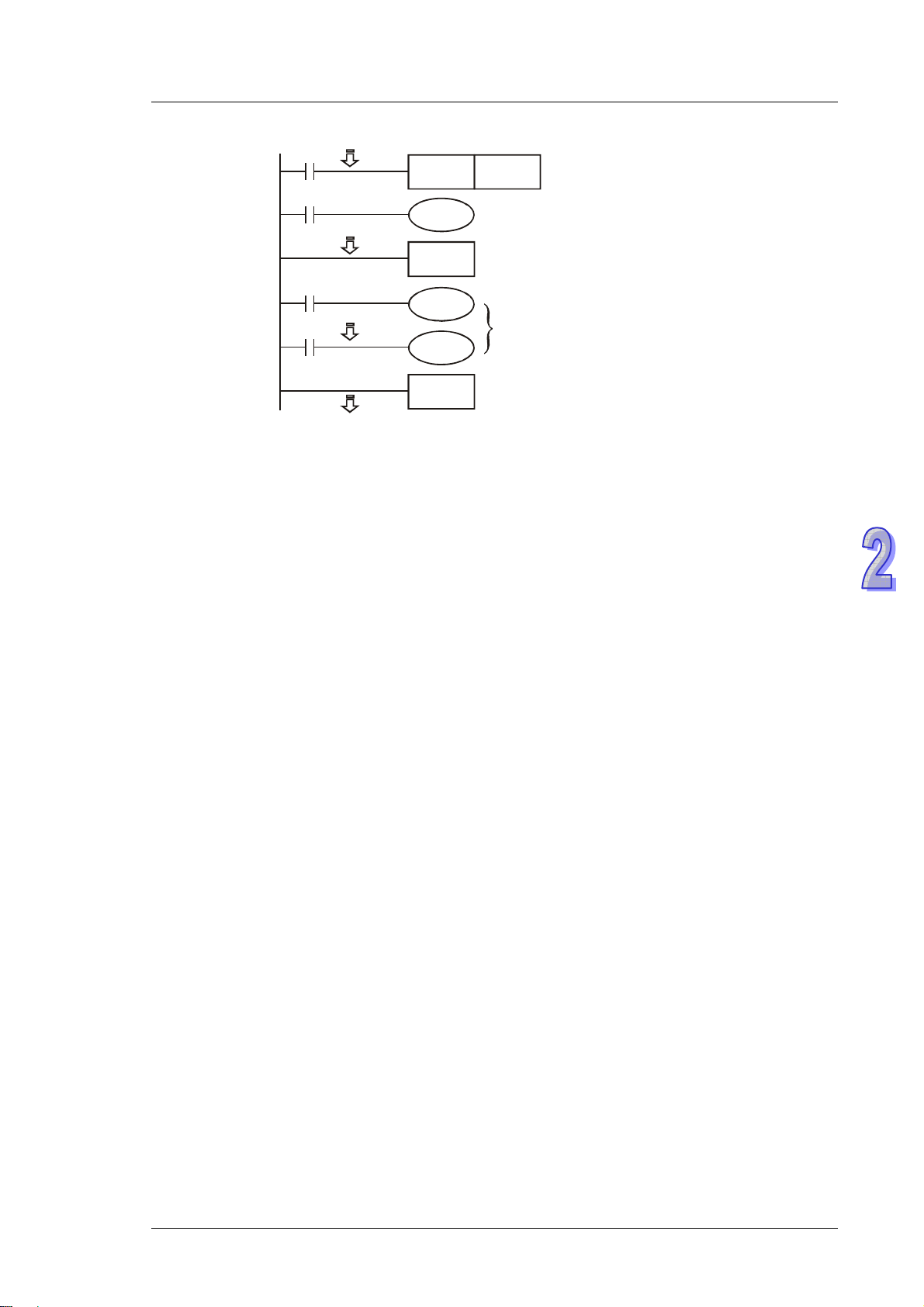

1.5.11 STL (Step Ladder Programming)

STL programming uses step points, e.g. S0 S21, S22, which allow users to program in a clearer

and understandable way as drawing a flow chart. The program will proceed to next step only if the

previous step is completed, therefore it forms a sequential control process similar to SFC

(Sequential Function Chart) mode. The STL sequence can be converted into a PLC ladder diagram

which is called “step ladder diagram” as below.

1-9

Page 18

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

M1002

S0

S21

M1002

initial

pulse

S0

S

S21

S

S22

S

SET

SET

SET

e

S0

S0

S21

S22

S22

RET

1.5.12 RET (Return)

RET instruction has to be placed at the end of sequential control process to indicate the com pletion

of STL flow.

S20

e

S

RET

S20

e

S

RET

Note: Always connect RET instruction immediately after the last step point indicated as the above

diagram otherwise program error may occur.

1-10

Page 19

1. PLC Concepts

Y

Y

Y

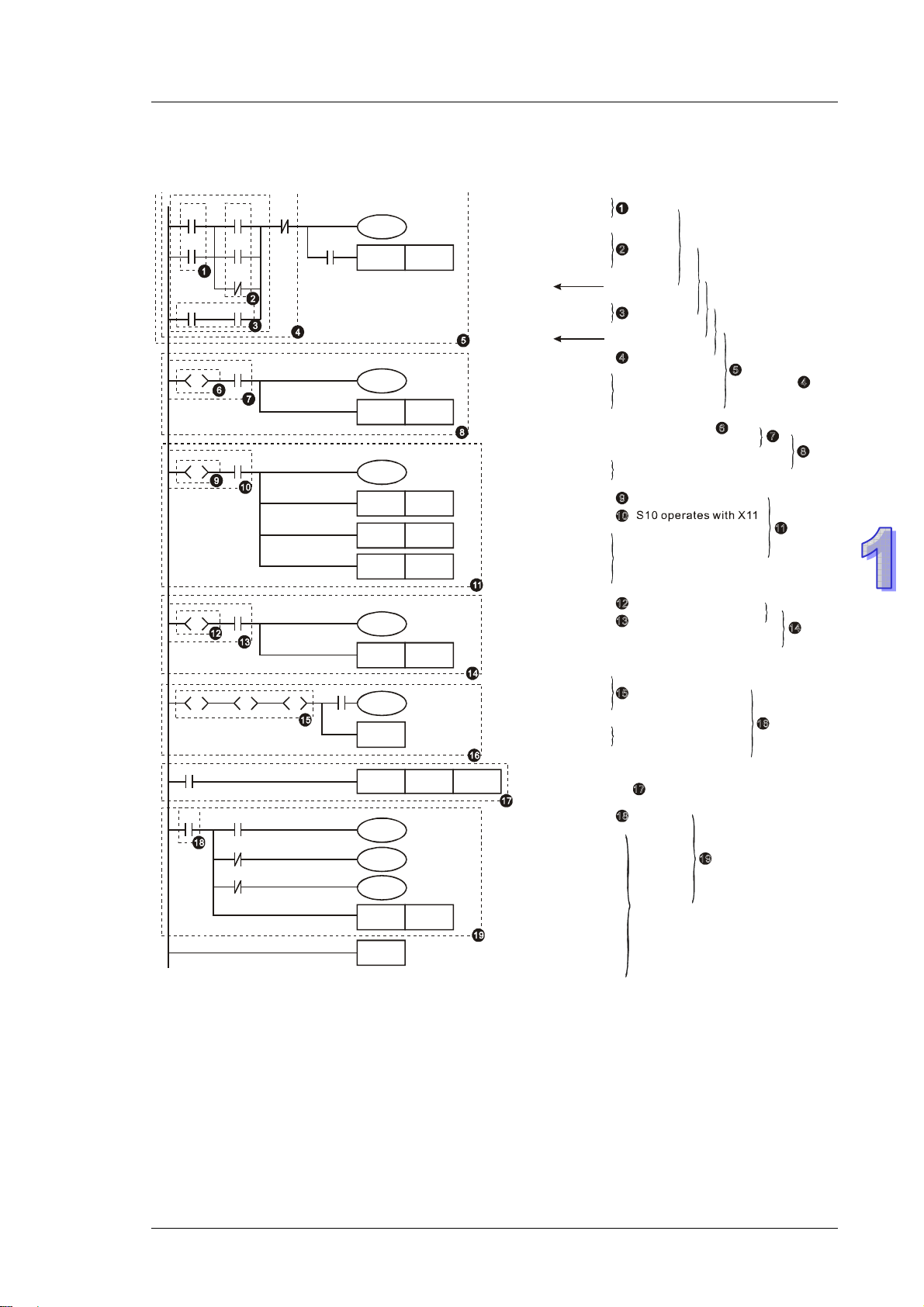

1.6 Conversion between Ladder Diagram and Instruction List Mode

Ladder Diagram

X0 X2 X1

X1

M0

M1

Y0

M2

S0

X10

S

S10

X11

S

S11

X12

S

S20

X0

C0

S12SS13

S

X1

X1

M2

Instruction

LD X0

Y0

C0

SET S0

OR X1

LD X2

OR M0

ORI M1

ANB

LD M2

AND Y0

ORB

AN I X1

10

OUT Y0

AND C0

SET S10

SET S0

STL S0

LD X10

11

SET S11

OUT Y10

SET S1 0

STL S10

LD X11

SET S12

OUT Y11

SET S11

SET S13

SET S1 2

SET S1 3

STL S11

12

LD X12

OUT Y12

SET S20

SET S2 0

STL S20

X13

S

S0

RET

STL S12

STL S13

LD X13

OUT S0

RET

CNT

C0

LD X0

K10

CNT C0 K10

LD C0

M0

M1

M2

RST C0

END

MPS

AND X1

OUT M0

MRD

AN I X1

OUT M1

MPP

AN I M2

OUT M2

RST C0

END

OR

block

OR

block

Block in series

AND

block

Block in parallel

ANI

Multiple

output s

Start of step ladder

S0 status operates with X10

Output Y10 and

transfer of step point

Read S10 status

Output Y1 1 and

transfer of step points

Read S11 status

S11 operates with X12

Output Y12 and

transfer of step points

Convergence of

multip le status

Read X13 status and

transfer of step point

Retur n

Read C0

Multi ple

output s

End of program

The output

continues

based on

status of

End of step

ladder

1-11

Page 20

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

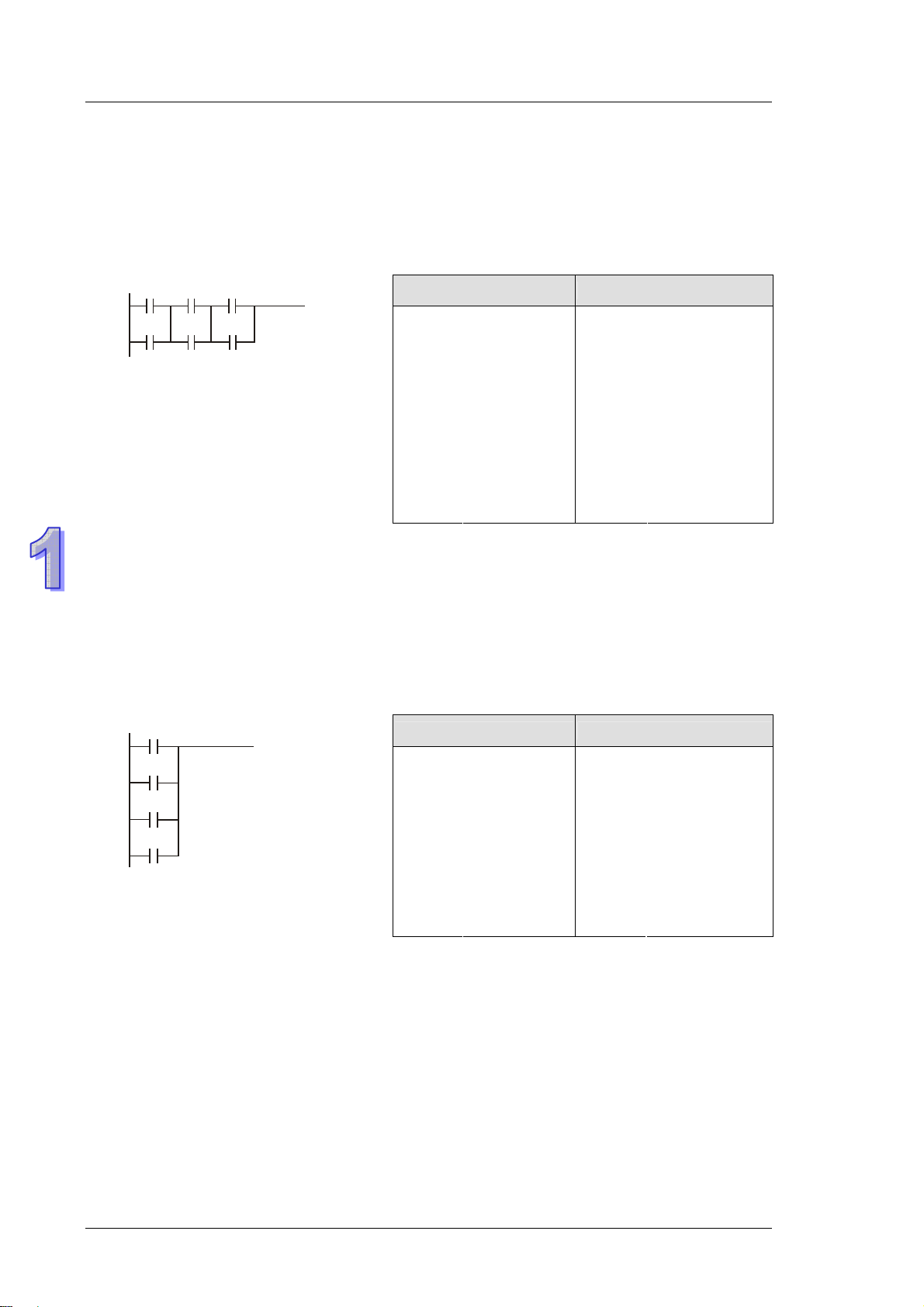

1.7 Fuzzy Syntax

Generally, the ladder diagram programming is conducted according to the “up to down and left to

right” principle. However, some programming methods not following this principle still perform the

same control results. Here are some examples explaining this kind of “fuzzy syntax.”

Example 1:

X0 X2 X4

X5X3X1

Better method OK method

LD X0 LD X0

OR X1 OR X1

LD X2 LD X2

OR X3 OR X3

ANB LD X4

LD X4 OR X5

OR X5 ANB

ANB ANB

The two instruction programs can be converted into the same ladder diagram. The difference

between Better and OK method is the ANB operation conducted by MPU. ANB instruction cannot

be used continuously for more than 8 times. If more than 8 ANB instructions are used continuously,

program error will occur. Therefore, apply ANB instruction after a block is made is the better

method to prevent the possible errors. In addition, it’s also the more logical and clearer

programming method for general users.

Example 2:

X0

Good method Bad method

X1

LD X0 LD X0

OR X1 LD X1

X2

X3

OR X2 LD X2

OR X3 LD X3

ORB

ORB

ORB

The difference between Good and Bad method is very clear. With longer program code, the

required MPU operation memory increases in the Bad method. To sum up, following the general

principle and applying good / better method when editing programs prevents possible errors and

improves program execution speed as well.

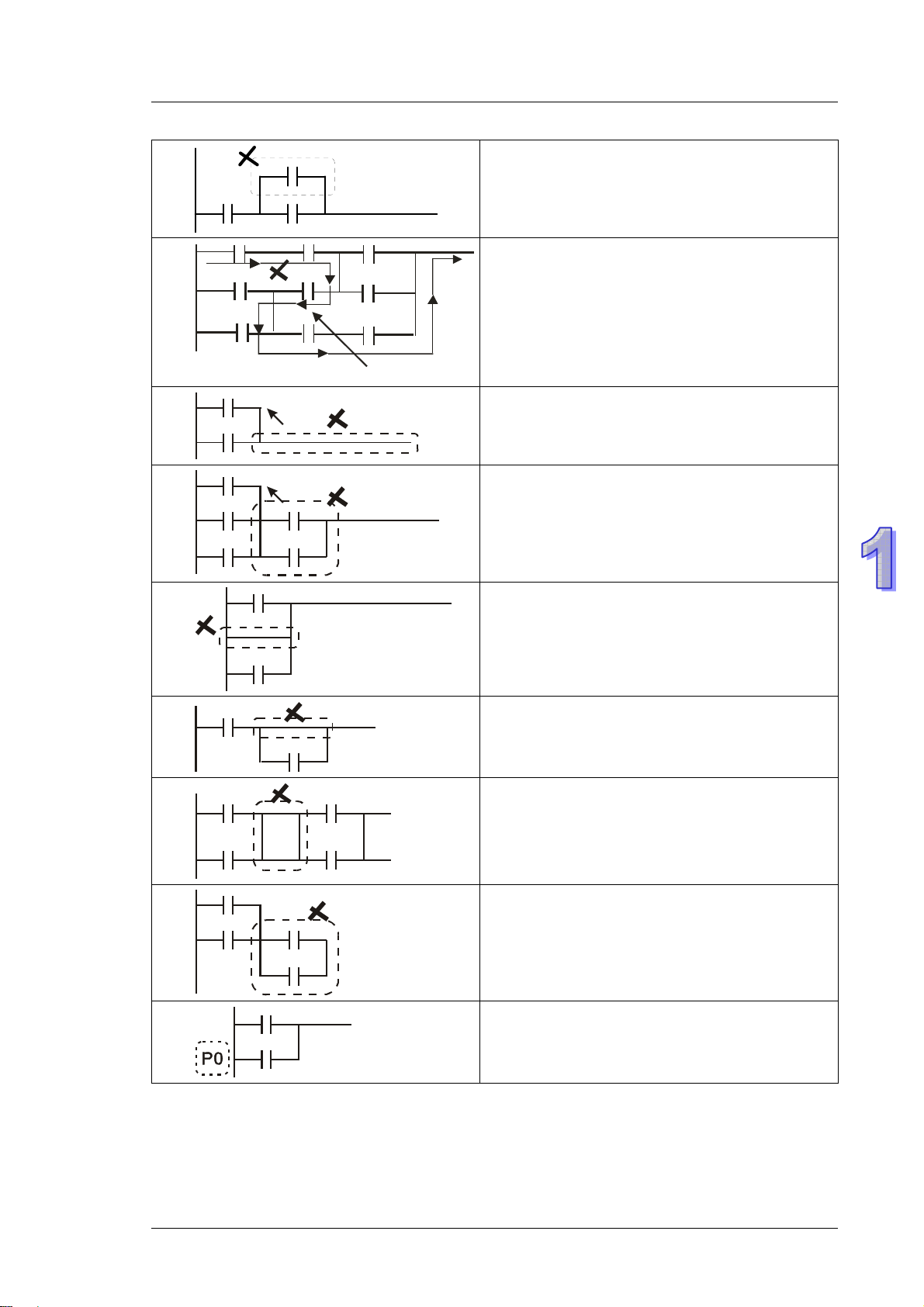

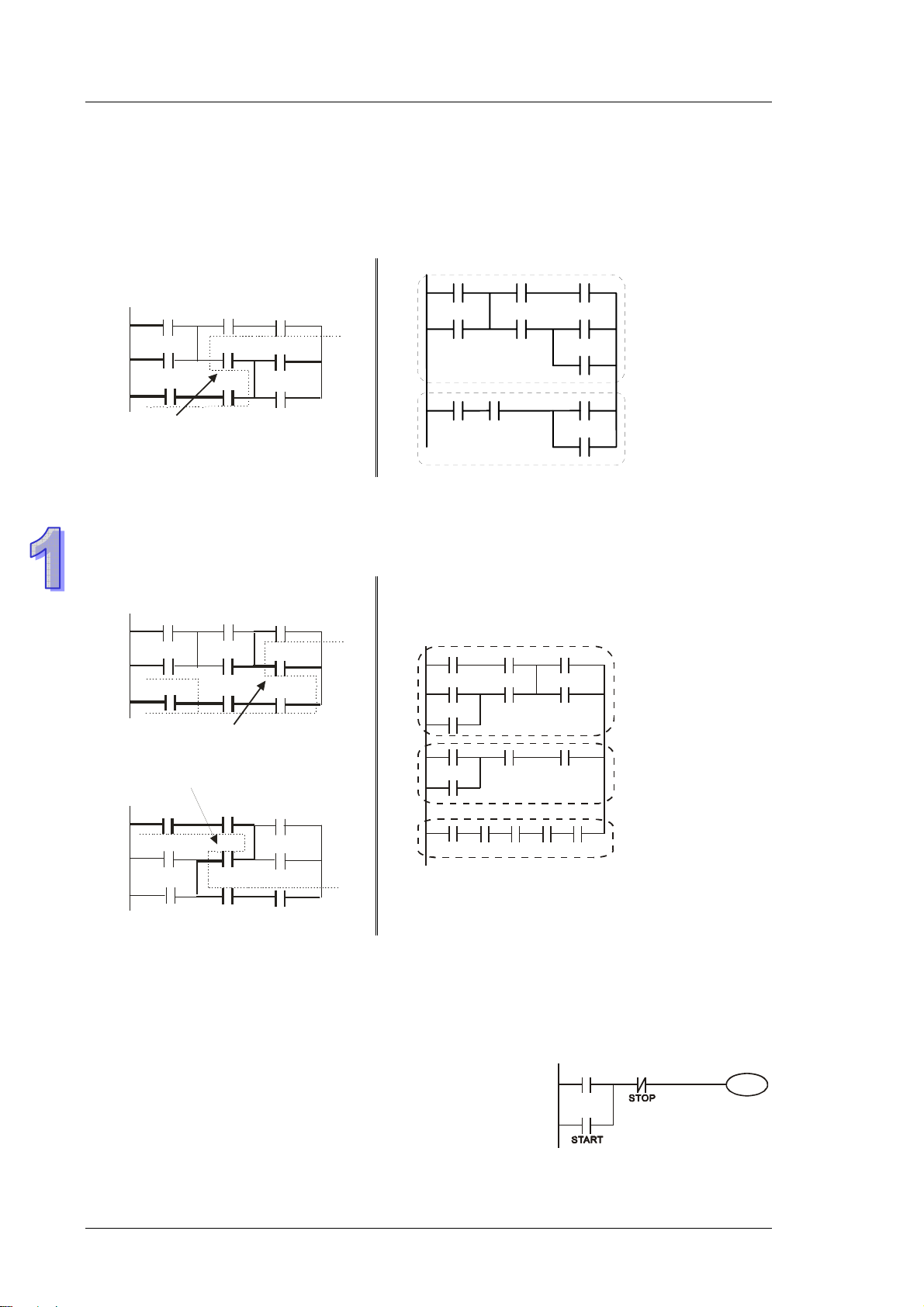

Common Programming Errors

PLC processes the diagram program from up to down and left to right. When editing ladder

diagram users should adopt this principle as well otherwise an error would be detected by WPLSoft

when compiling user program. Common program errors are listed below:

1-12

Page 21

Reverse cur rent

1. PLC Concepts

OR operation upward is not allowed.

“Reverse current” exists.

Output should be connected on top of the

circuit..

Block combination should be made on top of the

circuit..

Parallel connection with empty device is not

allowed..

Parallel connection with empty device is not

allowed.

No device in the middle block.

Devices and blocks in series should be

horizontally aligned

Label P0 should be at the first row of the

complete network.

1-13

Page 22

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

“Reverse current” exists

1.8 Correcting Ladder Diagram

Example 1:

Connect the block to the front for omitting ANB instruction because simplified program improves

processing speed

X0 X1

Instruction List

X2

LD X0

LD X1

OR X2

ANB

Ø

X0X1

X2

Example 2:

When a device is to be connected to a block, connect the device to upper row for omitting ORB

instruction

T0

X1

X2

Instruction List

LD X1

OR X2

AND X0

Instruction List

LD T0

LD X1

AND X2

ORB

1-14

X1

T0

X2

Ø

Instruction List

LD X1

AND X2

OR T0

Page 23

1. PLC Concepts

Example 3:

“Reverse current” existed in diagram (a) is not allowed for PLC processing principle.

X0

Instruction List

LD X0

X1

X3

X2

X4

OR X1

AND X2

LD X3

(a)

AND X4

ORB

Ø

X3

X1

X4

X2

Instruction List

LD X3

AND X4

X0

(b)

LD X1

OR X0

AND X2

ORB

Example 4:

For multiple outputs, connect the output without additional input devices to the top of the circuit for

omitting MPS and MPP instructions.

X0

Y1

Y0

Instruction List

MPS

AND X0

OUT Y1

MPP

OUT Y0

Ø

Y0

X0

Y1

Instruction List

OUT Y0

AND X0

OUT Y1

1-15

Page 24

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

Example 5:

Correct the circuit of reverse current. The pointed reverse current loops are modified on the right.

X0 X1 X2

X0

X3

X6

reverse current

X4

X1

X7

X2

X5

X10

LOOP1

Ö

X3 X4 X5

X6 X7 X5

X10

X10

LOOP1

Example 6:

Correct the circuit of reverse current. The pointed reverse current loops are modified on the ri ght.

X0

X3

X6

X1

X4

X7

reverse current

X2

X5

X10

LOOP1

X0 X1 X2

X3 X4 X5

X6

X3 X7 X10

Ö

Reverse current

X0

X3

X6

X1

X4

X7

X2

X5

X10

LOOP2

X6

X0 X1 X7 X10

X4

LOOP1

LOOP

2

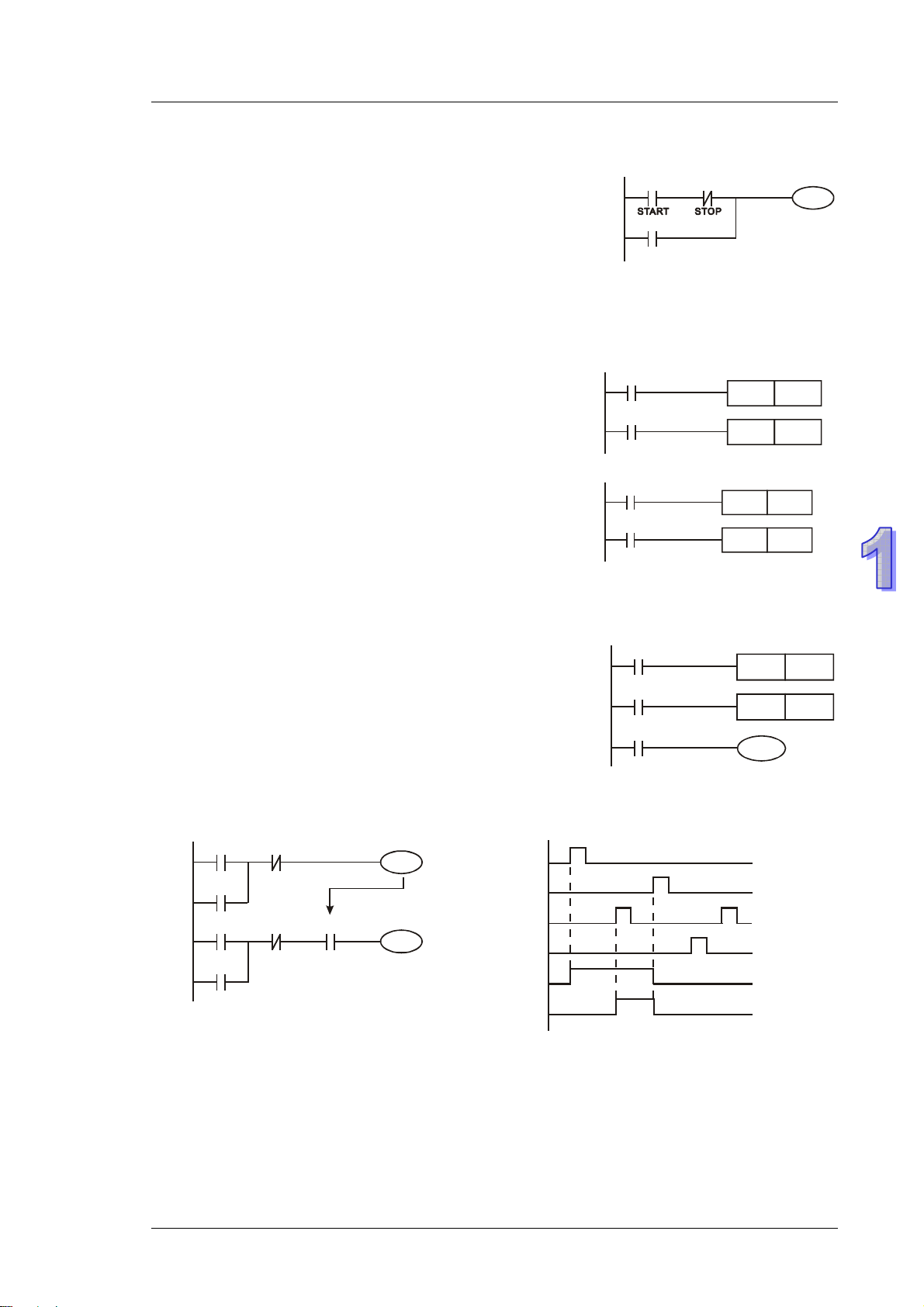

1.9 Basic Program Design Examples

Example 1 - Stop First latched circuit

When X1 (START) = ON and X2 (STOP) = OFF, Y1 will be ON.

If X2 is turned on, Y1 will be OFF. This is a Stop First circuit

because STOP button has the control pri ority than START

1-16

Y1

X1

X2

Y1

Page 25

Example 2 - Start First latched circuit

When X1 (START) = ON and X2 (STOP) = OFF, Y1 will be ON

and latched. If X2 is turned ON, Y1 remains ON. This is a Start

First circuit because START button has the control priority than

STOP

Example 3 - Latched circuit of SET and RST

The diagram opposite are latched circuits consist of RST and

SET instructions.

In PLC processing principle, the instruction close to the end of

the program determines the final output status of Y1. Therefore,

if both X1 and X2 are ON, RST which is lower than SET forms a

Stop First circuit while SET which is lower than RST forms a

Start First circuit.

Example 4 - Power down latched circuit

The auxiliary relay M512 is a latched relay. Once X1 is ON, Y1

retains its status before power down and resumes after power

up.

X1

Y1

Stop first

X1

X2

Start first

X2

X1

X1

X2

M512

1. PLC Concepts

X2

Y1

SET

RST

Y1

Y1

RST

SET

Y1

Y1

M512

SET

RST M 5 12

Y1

Example 5 - Conditional Control

X1

Y1

X2

Y2

X3

X4

Y1

Y1

Y2

X1

X3

X2

X4

Y1

Y2

Because NO contact Y1 is connected to the circuit of Y2 output, Y1 becomes one of the conditions

for enabling Y2, i.e. for turning on Y2, Y1 has to be ON

1-17

Page 26

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

Example 6- Interlock control

X1

Y1

X3

Y2

Y1

X1

X3

X2

X2

Y2

X4

Y1

Y2

X4

Y1

Y2

NC contact Y1 is connected to Y2 output circuit and NC contact Y2 is connected Y1 output circuit.

If Y1 is ON, Y2 will definitely be OFF and vice versa. This forms an Interlock circuit which prevents

both outputs to be ON at the same time. Even if both X1 and X2 are ON, in this case only Y1 will

be enabled.

Example 7 - Sequential Control

X1

Y1

X3

Y2

Y1

Connect NC contact Y2 to Y1 output circuit and

NO contact Y1 to Y2 output circuit. Y1 becomes

one of the conditions to turn on Y2. In addition, Y1

X2

Y2

X4

Y1

Y2

will be OFF when Y2 is ON, which forms an

sequential control process.

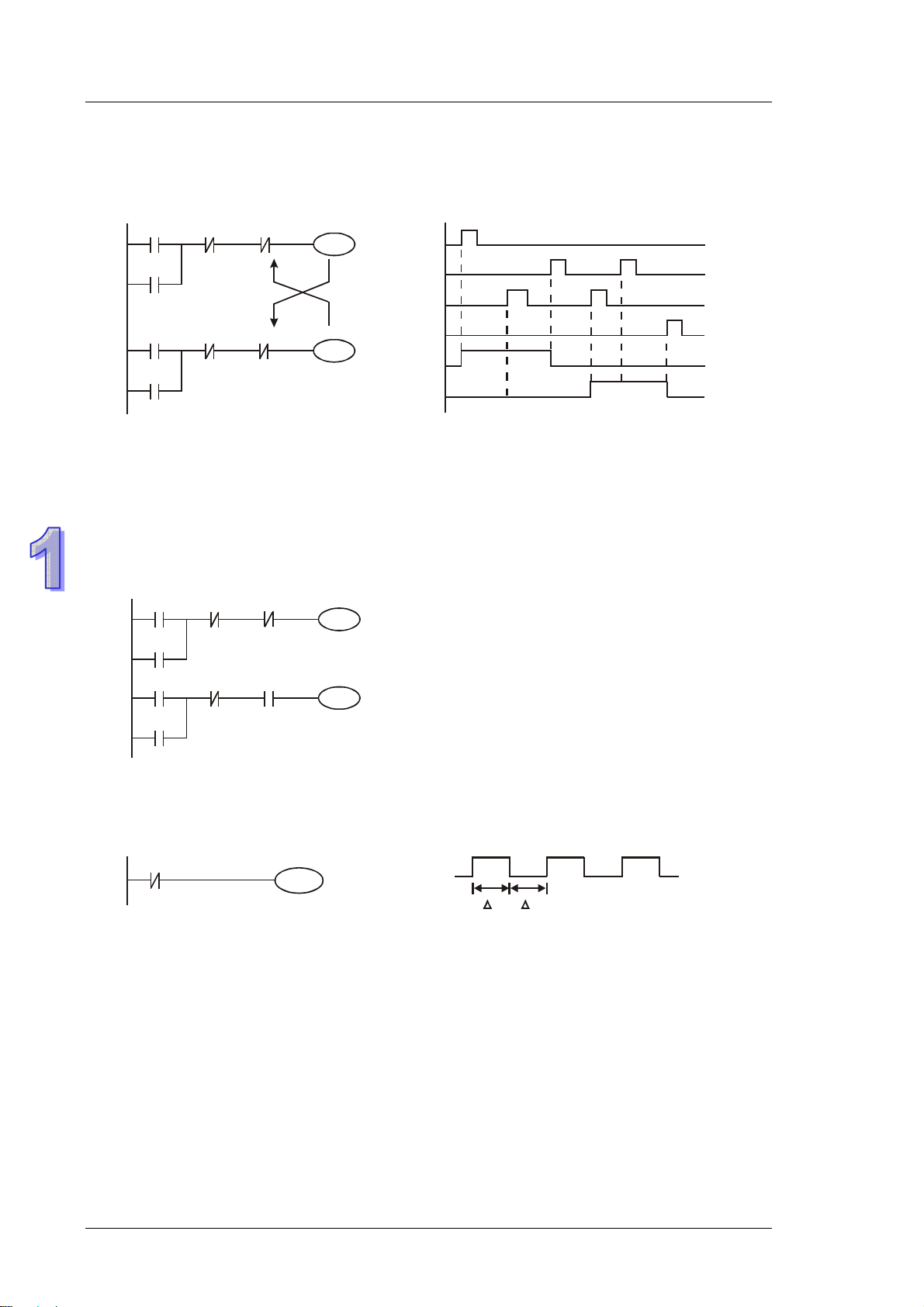

Example 8 - Oscillating Circuit

An oscillating circuit with cycle ΔT+ΔT

Y1

Y1

Y1

T T

In the first scan, Y1 turns on. In the second scan, Y1 turns off due to the reversed state of contact

Y1. Y1 output status changes in every scan and forms an oscillating circuit with output cycleΔ

T(ON)+ΔT(OFF)

1-18

Page 27

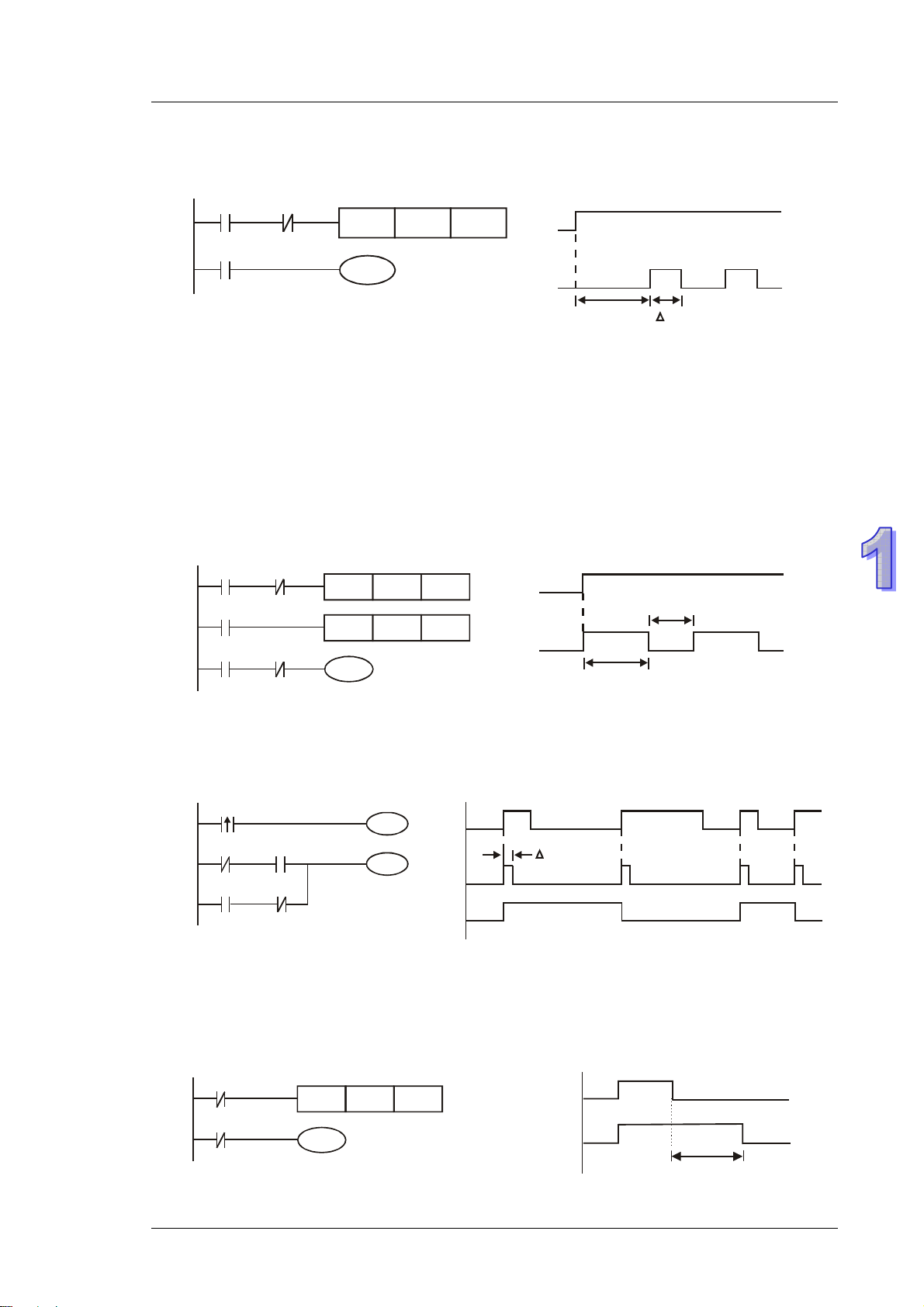

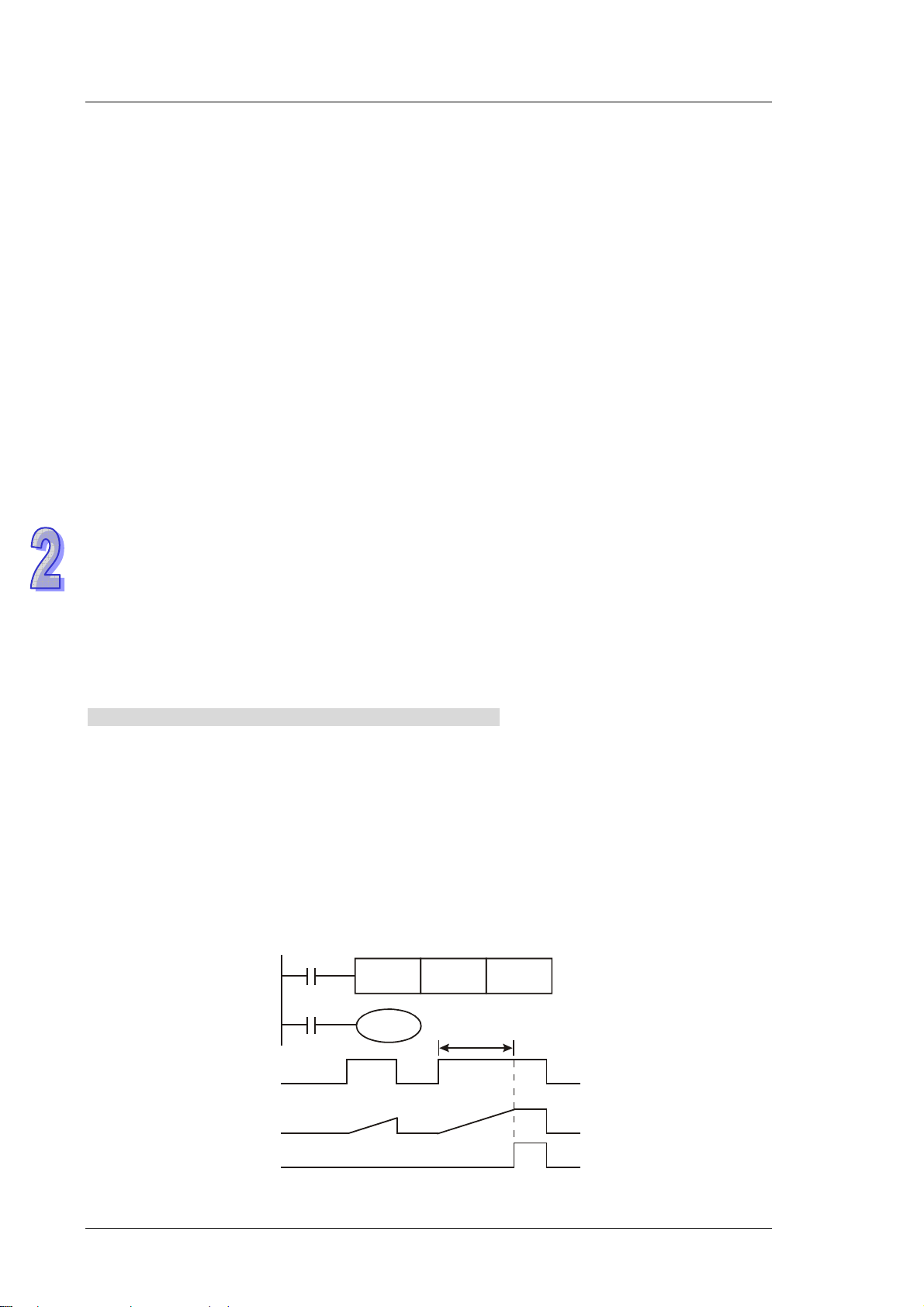

Example 9 – Oscillating Circuit with Timer

An oscillating circuit with cycle nT+ΔT

1. PLC Concepts

X0

Y1

TMR

T0

Kn

X0

T0

Y1

Y1

TTn

When X0 = ON, T0 starts timing (nT). Once the set time is reached, contact T0 = ON to enable

Y1(ΔT). In next scan, Timer T0 is reset due to the reversed status of contact Y1. Therefore contact

T0 is reset and Y1 = OFF. In next scan, T0 starts timing again. The process forms an oscillating

circuit with output cycle nT+ΔT.

Example 10 - Flashing Circuit

The ladder diagram uses two timers to form an oscillating circuit which enables a flashing indicator

or a buzzing alarm. n1 and n2 refer to the set values in T1 and T2 and T refers to timer resolution.

X0

T1

X0 T1

T2

TMR

Y1

T1

Kn1

T2TMR Kn2

X0

Tn2

Y1

T

n1

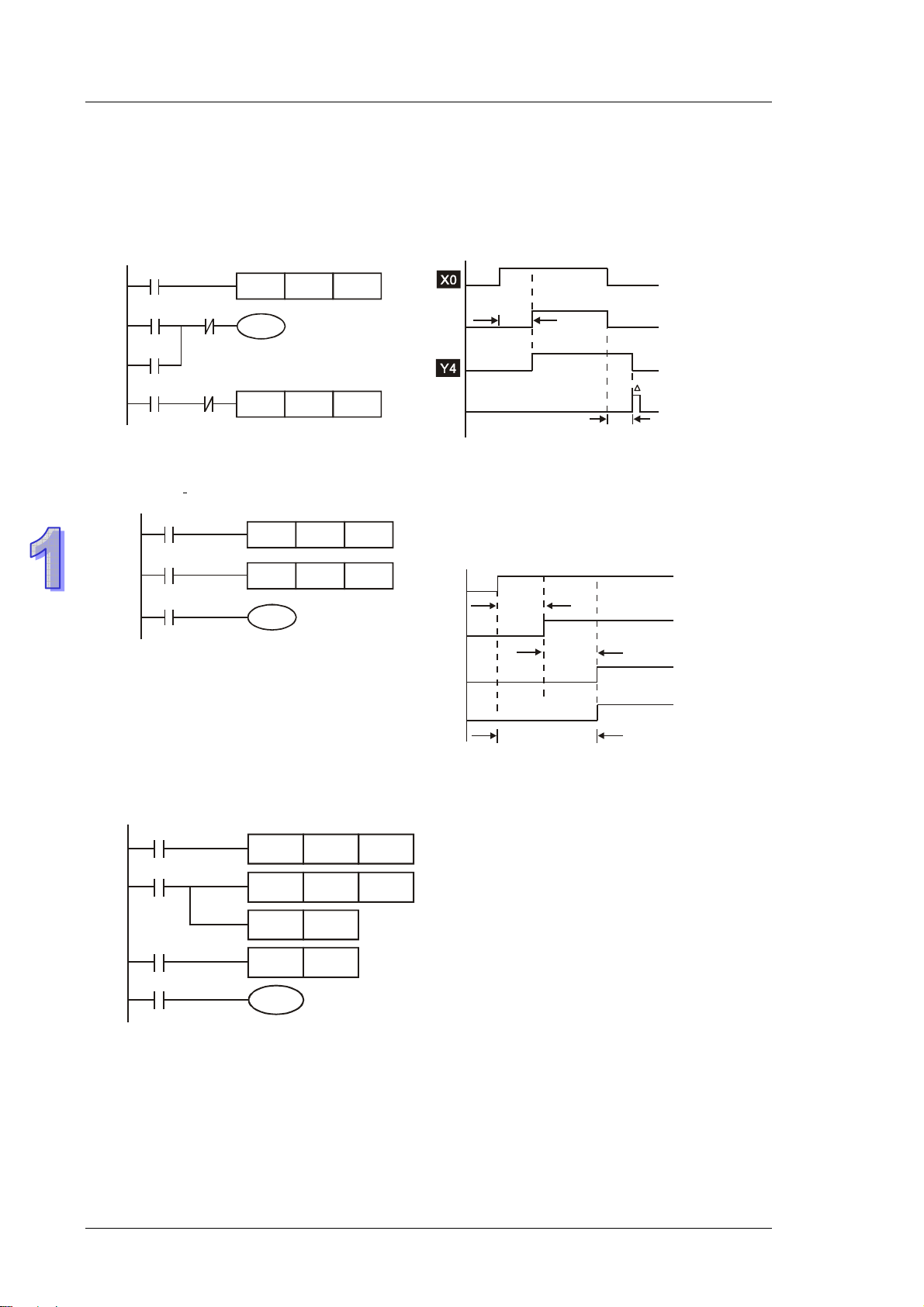

Example 11 - Trigger Circuit

In this diagram, rising-edge contact X0 generates trigger pulses to control two actions executing

interchangeably.

X0

X0

T

M0

Y1

M0

M0

M0

Y1

Y1

Y1

Example 12 - Delay OFF Circuit

If X0 = ON, timer T10 is not energized but coil Y1 is ON. When X0 is OFF, T10 is activated. After

100 seconds (K1000 × 0.1 sec = 100 sec), NC contact T10 is ON to turn off Y1. Turn-off action is

delayed for 100 seconds by this delay OFF circuit.

X0

T10

TMR

Y1

T10

K1000

X0

Y1

Timer Resolution: 0.1 sec

100 seconds

1-19

Page 28

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

Example 13 - Output delay circuit

The output delay circuit is composed of two timers executing delay actions. No matter input X0 is

ON or OFF, output Y4 will be delayed.

X0

T5

K50

5 secs

T5

T5

Y4

TMR

T6

Y4

Y4

X0

TMR

T6

K30

Example 14 -

Timing extension circuit

X0

TMR

T11

T12

T11

T12TMR Kn2

Y1

.

Kn1

The total delay time: (n1+n2)* T. T refers to the

timer resolution.

Timer = T11, T12

Timer resolution: T

Example 15 – Counting Range Extension Circuit

X13

The counting range of a 16-bit counter is 0 ~

32,767. The opposite circuit uses two counters to

increase the counting range as n1*n2. When

value in counter C6 reaches n2, The pulses

counted from X13 will be n1*n2.

C5

X14

C6

CNT

RST

Y1

C5

Kn1

C6CNT Kn 2

C5RST

C6

T6

X0

T11

T12

Y1

n1*

T

(n1+n2)*

n2*

T

3 secs

T

T

1-20

Page 29

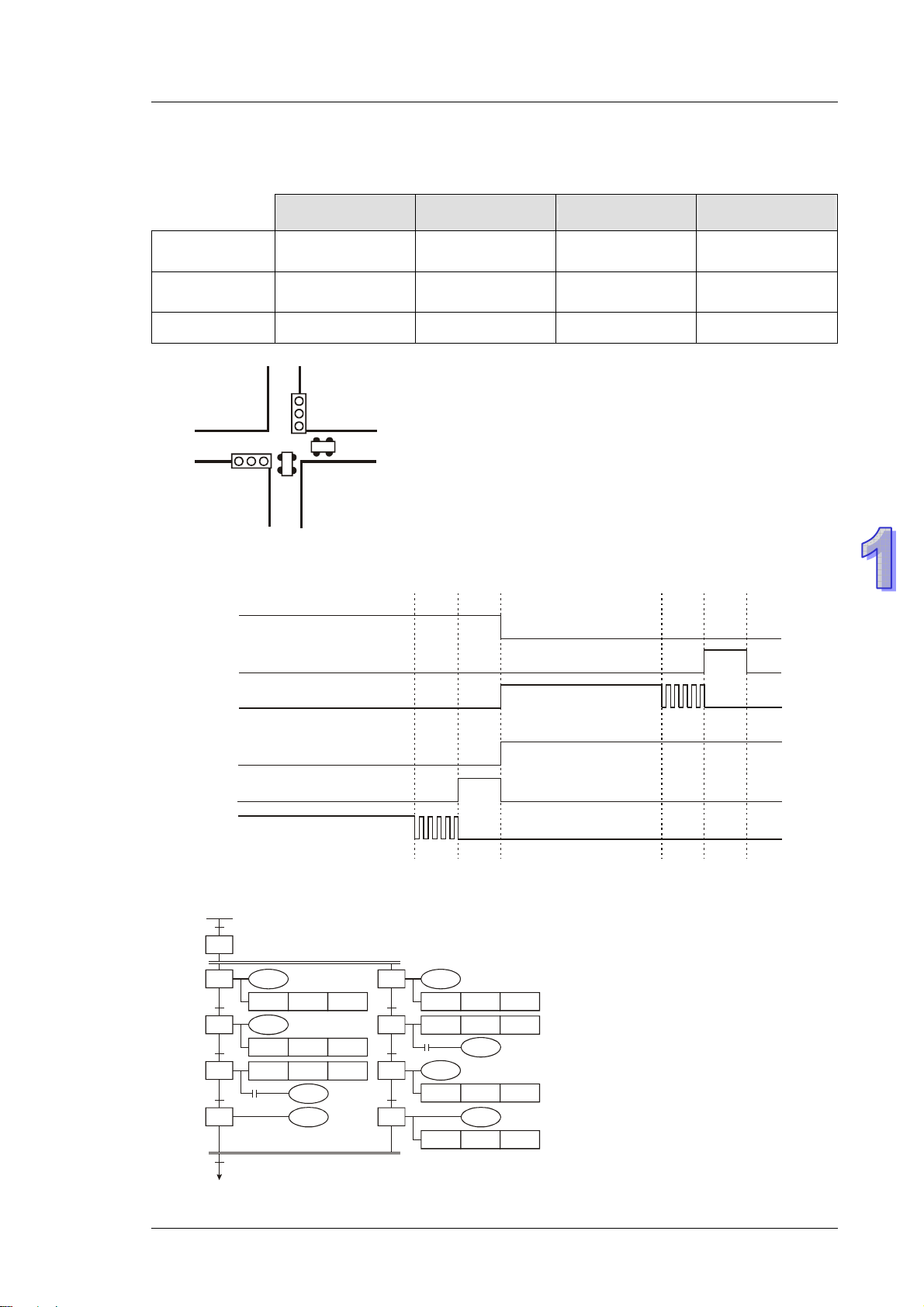

Example 16 - Traffic light control (Step Ladder Logic)

Traffic light control

1. PLC Concepts

Red light Yellow light Green light

Green light

blinking

Vertical light Y0 Y1 Y2 Y2

Horizontal light Y20 Y21 Y22 Y22

Light Time 35 Sec 5 Sec 25 Sec 5 Sec

Vertical

Light

Horizontal

Light

Timing Diagram:

Vertical

Light

Red

Y0

Y1

Yellow

Green

Y2

Horizontal

Light

Red

Y20

Yellow

Y21

Green

Y22

SFC Figure:

M1002

S0

S20

T0

S21

T1

S22

T2

S23

T13

S0

25 Sec

Y0

TMR T0 K350

Y2

TMR T1 K250

TMR T2 K50

M1013

Y2

Y1

T10

T11

T12

S30

S31

S32

S33

5 Sec

5 Sec

Y22

TMR T10 K250

TMR T11 K50

M1013

Y22

Y21

TMR T12 K50

Y20

TMR T13 K350

25 Sec

5 Se c5 Sec

1-21

Page 30

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

2

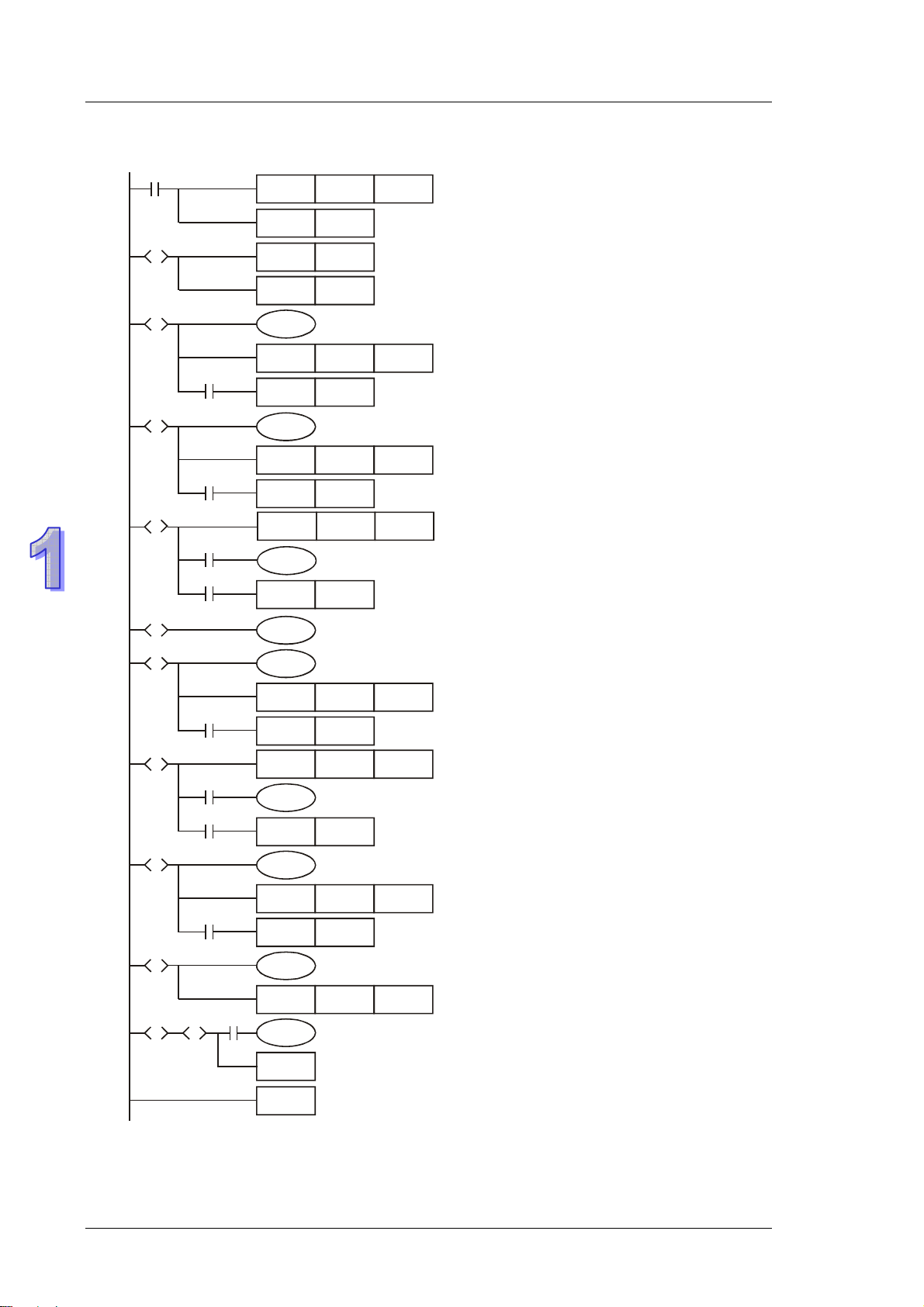

Ladder Diagram:

M100

S0

S

S20

S

S21

S

S22

S

S23

S

S30

S

T0

T1

M1013

T2

ZRST S0 S127

SET S0

SET S20

SET S30

Y0

TMR T0

K350

SET S21

Y2

TMR T1

K250

SET S22

TMR T2

K50

Y2

SET S23

Y1

Y22

S31

S

M1013

S32

S

S33

S

S23SS33

S

T10

T11

T12

TMR T10

SET S31

TMR T11

Y22

SET S32

Y21

TMR T12

SET S33

Y20

TMR T13 K350

T13

S0

RET

END

K250

K50

K50

1-22

Page 31

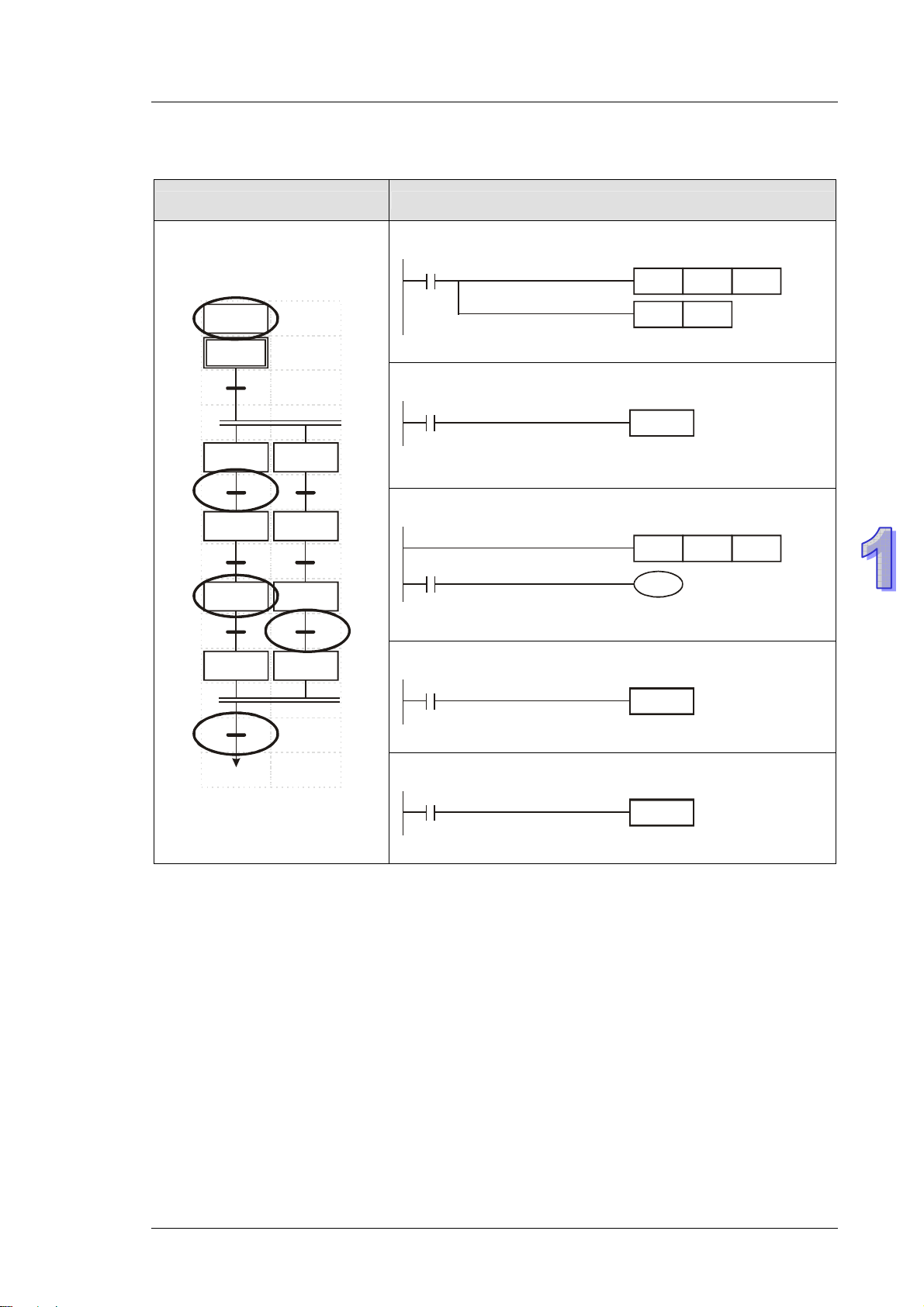

WPLSoft programming (SFC mode)

SFC logic Internal Ladder Logic

LAD-0

1. PLC Concepts

M1002

S0ZRST S127

LAD-0

S0

0

S20

1

S21

2

S22

3

S23

4

S30

S31

S32

S33

SET

S0

Transfer con dition 1

T0

TRANS*

5

6

S22

T2TMR K50

M1013

Y2

7

Transfer con dition 4

T13

T13

T13

T13

T13

T13

T13

TRANS*

TRANS*

TRANS*

TRANS*

TRANS*

TRANS*

TRANS*

S0

T12

T12

T12

T12

T12

T12

T12

TRANS*

TRANS*

TRANS*

TRANS*

TRANS*

TRANS*

TRANS*

Transfer con dition 7

1-23

Page 32

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

MEMO

1-24

Page 33

Programming Concepts

DVP-ES2/EX2/SS/SA2/SX2/SE is a programmable logic controller spanning an I/O range of

10–256 I/O points (SS2/SA2/SX2/SE: 512 points). PLC can control a wide variety of devices

to solve your automation needs. PLC monitors inputs and modifies outputs as controlled

by the user program. User program provides features such as boolean logic, counting,

timing, complex math operations, and communications to other communicating products.

Chapter Contents

2.1 ES2/EX2 Memory Map.............................................................................................................. 2-2

2.2 SS2 Memory Map...................................................................................................................... 2-5

2.3 SA2 Memory Map...................................................................................................................... 2-8

2.4 SX2 Memory Map.................................................................................................................... 2-11

2.5 Status and Allocation of Latched Memory........................................................................... 2-14

2.6 PLC Bits, Nibbles, Bytes, Words, etc ...................................................................................2-15

2.7 Binary, Octal, Decimal, BCD, Hex ......................................................................................... 2-15

2.8 M Relay ....................................................................................................................................2-17

2.9 S Relay.....................................................................................................................................2-30

2.10 T (Timer) .................................................................................................................................. 2-30

2.11 C (Counter).............................................................................................................................. 2-31

2.12 High-speed Counters ............................................................................................................. 2-34

2.13 Special Data Register............................................................................................................. 2-39

2.14 E, F Index Registers ............................................................................................................... 2-51

2.15 Nest Level Pointer[N], Pointer[P], Interrupt Pointer [I] .......................................................2-51

2.16 Applications of Special M Relays and D Registers.............................................................2-55

2-1

Page 34

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

A

2.1 ES2/EX2 Memory Map

Specifications

Control Method Stored program, cyclic scan system

I/O Processing Method

Batch processing method (when END instruction is

executed)

Execution Speed LD instructions – 0.54μs, MOV instructions – 3.4μs

Program language Instruction List + Ladder + SFC

Program Capacity 15872 steps

Bit

Contacts

X External inputs

Y External outputs

X0~X377, octal number system, 256

points max, (*4)

Y0~Y377, octal number system, 256

points max, (*4)

Total

256+16 I/O

M0~M511, 512 points, (*1)

General

M768~M999, 232 points, (*1)

M2000~M2047, 48 points, (*1)

M

uxiliary

relay

Latched

Special

M512~M767, 256 points, (*2)

M2048~M4095, 2048 points, (*2)

M1000~M1999, 1000 points, some

are latched

Total

4096 points

T0~T126, 127 points, (*1)

100ms

(M1028=ON,

T64~T126:

10ms)

T Timer

10ms

(M1038=ON,

T200~T245: 1ms)

T128~T183, 56 points, (*1)

T184~T199 for Subroutines, 16

points, (*1)

T250~T255(accumulative),

6 points (*1)

T200~T239, 40 points, (*1)

T240~T245(accumulative),

Total

256 points

6 points, (*1)

T127, 1 points, (*1)

1ms

T246~T249(accumulative), 4 points,

(*1)

C

Counter

16-bit count up

C0~C111, 112 points, (*1)

C128~C199,72 points, (*1)

C112~C127,16 points, (*2)

Total

232 points

C200~C223, 24 points, (*1)

C224~C231, 8 points, (*2)

2-2

32-bit count

up/down

Page 35

Specifications

C235~C242, 1 phase 1 input, 8

points, (*2)

C232~C234, 2 phase 2 input, 3

points, (*2)

C243~C244, 1 phase 1 input, 2

points, (*2)

C245~C250, 1 phase 2 input, 6

points, (*2)

32bit

highspeed

count

up/down

Software

Hard-

ware

C251~C254 2 phase 2 input, 4

points, (*2)

Initial step point S0~S9, 10 points, (*2)

2. Programming Concepts

Total

23 points

Word

Register

S10~S19, 10 points (use with IST

instruction), (*2)

S

Step

point

Zero point return

Latched S20~S127, 1 08 points, (*2)

General S128~S911, 784 points, (*1)

Alarm S912~S1023, 112 points, (*2)

T Current value T0~T255, 256 words

C0~C199, 16-bit counter, 200 words

C Current value

C200~C254, 32-bit counter, 55 words

D0~D407, 408 words, (*1)

General

D600~D999, 400 words, (*1)

D3920~D9999, 6080 words, (*1)

D408~D599, 192 words, (*2)

D2000~D3919, 1920 words, (*2)

D1000~D1999, 1000 words, some

are latched

D9900~D9999,100 words , (*1),

(*5)

Data

D

register

Latched

Special

For Special

mudules

Total 1024

points

Total

10000 points

Pointer

Index E0~E7, F0~F7, 16 words, (*1)

N Master control loop N0~N7, 8 points

P Pointer P0~P255, 256 points

I Interrupt

Service

External interrupt

I000/I001(X0), I100/I101(X1), I200/I201(X2),

I300/I301(X3), I400/I401(X4), I500/I501(X5),

I600/I601(X6), I700/I701(X7), 8 points (01: risingedge trigger

, 00: falling-edge trigger )

2-3

Page 36

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

Specifications

Timer interrupt

High-speed

counter interrupt

Communication

interrupt

I602~I699, I702~I799, 2 points (T imer resolution =

1ms)

I010, I020, I030, I040, I050, I060, I070, I080,8

points

I140(COM1), I150(COM2), I160(COM3), 3 points,

(*3)

K-32,768 ~ K32,767 (16-bit operation),

K Decimal K-2,147,483,648 ~ K2,147,483,647 (32-bit

Constant

H Hexadecimal

operation)

H0000 ~ HFFFF (16-bit operation),

H00000000 ~HFFFFFFFF (32-bit operation)

COM1: built-in RS-232 ((Master/Slave)

Serial ports

COM2: built-in RS-485 (Master/Slave)

COM3: built-in RS-485 (Master/Slave)

COM1 is typically the programming port.

Real Time Clock Year, Month, Day, Week, Hours, Minutes, Seconds

Special I/O Modules Up to 8 special I/O modules can be connected

Notes:

1. Non-latched area cannot be modified

2. Latched area cannot be modified

3. COM1: built-in RS232 port. COM2: built-in RS485 port. COM3: built-in RS485 port.

4. When input points(X) are expanded to 256 points, only 16 output points(Y) are applicable. Also,

when ouput points(Y) are expanded to 256 points, only 16 input points(X) are applicable.

5. This area is applicable only when the ES2/EX2 MPU is connected with special I/O modules.

Every special I/O module occupies 10 points.

2-4

Page 37

2. Programming Concepts

A

2.2 SS2 Memory Map

Specifications

Control Method Stored program, cyclic scan system

I/O Processing Method

Batch processing method (when END instruction is

executed)

Execution Speed LD instructions – 0.54μs, MOV instructions – 3.4μs

Program language Instruction List + Ladder + SFC

Program Capacity 7920 steps

Bit

Contacts

X External inputs

Y External outputs

X0~X377, octal number system, 256

points max.

Y0~Y377, octal number system, 256

points max.

Total

480+14

I/O(*4)

M0~M511, 512 points, (*1)

General

M768~M999, 232 points, (*1)

M2000~M2047, 48 points, (*1)

M

uxiliary

relay

Latched

Special

M512~M767, 256 points, (*2)

M2048~M4095, 2048 points, (*2)

M1000~M1999, 1000 points, some

are latched

Total

4096 points

T0~T126, 127 points, (*1)

100ms

(M1028=ON,

T64~T126:

10ms)

T Timer

10ms

(M1038=ON,

T200~T245: 1ms)

T128~T183, 56 points, (*1)

T184~T199 for Subroutines, 16

points, (*1)

T250~T255(accumulative),

6 points (*1)

T200~T239, 40 points, (*1)

T240~T245(accumulative),

Total

256 points

6 points, (*1)

T127, 1 points, (*1)

1ms

T246~T249(accumulative), 4 points,

(*1)

C

Counter

16-bit count up

C0~C111, 112 points, (*1)

C128~C199, 72 points, (*1)

C112~C127, 16 points, (*2)

Total

233 points

32-bit count

up/down

C200~C223, 24 points, (*1)

C224~C232, 9 points, (*2)

2-5

Page 38

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

Specifications

C235~C242, 1 phase 1 input, 8

points, (*2)

C233~C234, 2 phase 2 input, 2

points, (*2)

C243~C244, 1 phase 1 input, 2

points, (*2)

C245~C250, 1 phase 2 input, 6

points, (*2)

32bit

highspeed

count

up/down

Software

Hard-

ware

C251~C254 2 phase 2 input, 4

points, (*2)

Initial step point S0~S9, 10 points, (*2)

Total

22 points

Word

Register

S10~S19, 10 points (use with IST

instruction), (*2)

S

Step

point

Zero point return

Latched S20~S127, 1 08 points, (*2)

General S128~S911, 784 points, (*1)

Alarm S912~S1023, 112 points, (*2)

T Current value T0~T255, 256 words

C0~C199, 16-bit counter, 200 words

C Current value

C200~C254, 32-bit counter, 55 words

D0~D407, 408 words, (*1)

General

D600~D999, 400 words, (*1)

D3920~D4999, 1080 words, (*1)

D

Data

register

Latched

Special

D408~D599, 192 words, (*2)

D2000~D3919, 1920 words, (*2)

D1000~D1999, 1000 words, some

are latched

Total 1024

points

Total

5016 points

Pointer

2-6

Index E0~E7, F0~F7, 16 words, (*1)

N Master control loop N0~N7, 8 points

P Pointer P0~P255, 256 points

I Interrupt

Service

External interrupt

Timer interrupt

I000/I001(X0), I100/I101(X1), I200/I201(X2),

I300/I301(X3), I400/I401(X4), I500/I501(X5),

I600/I601(X6), I700/I701(X7), 8 points (01: risingedge trigger

, 00: falling-edge trigger )

I602~I699, I702~I799, 2 points (T imer resolution =

1ms)

Page 39

Specifications

2. Programming Concepts

High-speed

counter interrupt

Communication

interrupt

I010, I020, I030, I040, I050, I060, I070, I080, 8

points

I140(COM1), I150(COM2), 2 points, (*3)

K-32,768 ~ K32,767 (16-bit operation),

K Decimal K-2,147,483,648 ~ K2,147,483,647 (32-bit

Constant

H Hexadecimal

operation)

H0000 ~ HFFFF (16-bit operation),

H00000000 ~HFFFFFFFF (32-bit operation)

COM1: built-in RS-232 ((Master/Slave)

Serial ports COM2: built-in RS-485 (Master/Slave)

COM1 is typically the programming port.

Real Time Clock Year, Month, Day, Week, Hours, Minutes, Seconds

Special I/O Modules Up to 8 special I/O modules can be connected

Notes:

1. Non-latched area cannot be modified

2. Latched area cannot be modified

3. COM1: built-in RS232 port. COM2: built-in RS485 port.

4. SS2 MPU occupies 16 input points (X0~X17) and 16 output points (Y0~Y17).

2-7

Page 40

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

A

2.3 SA2 Memory Map

Specifications

Control Method Stored program, cyclic scan system

I/O Processing Method

Batch processing method (when END instruction is

executed)

Execution Speed LD instructions – 0.54μs, MOV instructions – 3.4μs

Program language Instruction List + Ladder + SFC

Program Capacity 15872 steps

Bit

Contacts

X External inputs

Y External outputs

X0~X377, octal number system, 256

points max.

Y0~Y377, octal number system, 256

points max.

Total

480+14

I/O(*4)

M0~M511, 512 points, (*1)

General

M768~M999, 232 points, (*1)

M2000~M2047, 48 points, (*1)

M

uxiliary

relay

Latched

Special

M512~M767, 256 points, (*2)

M2048~M4095, 2048 points, (*2)

M1000~M1999, 1000 points, some

are latched

Total

4096 points

T0~T126, 127 points, (*1)

100ms

(M1028=ON,

T64~T126:

10ms)

T Timer

10ms

(M1038=ON,

T200~T245: 1ms)

T128~T183, 56 points, (*1)

T184~T199 for Subroutines, 16

points, (*1)

T250~T255(accumulative),

6 points (*1)

T200~T239, 40 points, (*1)

T240~T245(accumulative),

Total

256 points

6 points, (*1)

T127, 1 points, (*1)

1ms

T246~T249(accumulative), 4 points,

(*1)

C

Counter

16-bit count up

C0~C111, 112 points, (*1)

C128~C199, 72 points, (*1)

C112~C127, 16 points, (*2)

Total

233 points

C200~C223, 24 points, (*1)

C224~C232, 9 points, (*2)

C235~C242, 1 phase 1 input, 8

points, (*2)

Total

22 points

2-8

32-bit count

up/down

32bit Softhigh- ware

Page 41

Specifications

2. Programming Concepts

speed

count

up/down

C233~C234, 2 phase 2 input, 2

points, (*2)

C243~C244, 1 phase 1 input, 2

points, (*2)

Hard-

ware

C245~C250, 1 phase 2 input, 6

points, (*2)

C251~C254 2 phase 2 input, 4

points, (*2)

Initial step point S0~S9, 10 points, (*2)

S10~S19, 10 points (use with IST

instruction), (*2)

S

Step

point

Zero point return

Latched S20~S127, 1 08 points, (*2)

General S128~S911, 784 points, (*1)

Alarm S912~S1023, 112 points, (*2)

T Current value T0~T255, 256 words

C0~C199, 16-bit counter, 200 words

C Current value

C200~C254, 32-bit counter, 55 words

Total 1024

points

Word

Register

Pointer

D0~D407, 408 words, (*1)

General

D600~D999, 400 words, (*1)

D3920~D9999, 6080 words, (*1)

Data

D

register

Latched

Special

D408~D599, 192 words, (*2)

D2000~D3919, 1920 words, (*2)

D1000~D1999, 1000 words, some

are latched

Index E0~E7, F0~F7, 16 words, (*1)

N Master control loop N0~N7, 8 points

P Pointer P0~P255, 256 points

I Interrupt

Service

External interrupt

Timer interrupt

I000/I001(X0), I100/I101(X1), I200/I201(X2),

I300/I301(X3), I400/I401(X4), I500/I501(X5),

I600/I601(X6), I700/I701(X7), 8 points (01: rising-

edge trigger

, 00: falling-edge trigger )

I602~I699, I702~I799, 2 points (T imer resolution =

1ms)

Total

10000 points

2-9

Page 42

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

Specifications

High-speed

counter interrupt

Communication

interrupt

I010, I020, I030, I040, I050, I060, I070, I080, 8

points

I140(COM1), I150(COM2), I160(COM3), 3 points,

(*3)

K-32,768 ~ K32,767 (16-bit operation),

K Decimal K-2,147,483,648 ~ K2,147,483,647 (32-bit

Constant

H Hexadecimal

operation)

H0000 ~ HFFFF (16-bit operation),

H00000000 ~HFFFFFFFF (32-bit operation)

COM1: built-in RS-232 ((Master/Slave)

Serial ports

COM2: built-in RS-485 (Master/Slave)

COM3: built-in RS-485 (Master/Slave)

COM1 is typically the programming port.

Real Time Clock Year, Month, Day, Week, Hours, Minutes, Seconds

Special I/O Modules Up to 8 special I/O modules can be connected

Notes:

1. Non-latched area cannot be modified

2. Latched area cannot be modified

3. COM1: built-in RS232 port. COM2: built-in RS485 port. COM3: built-in RS-485 port

4. SA2 MPU occupies 16 input points (X0~X17) and 16 output points (Y0~Y17).

2-10

Page 43

2. Programming Concepts

A

2.4 SX2 Memory Map

Specifications

Control Method Stored program, cyclic scan system

I/O Processing Method

Batch processing method (when END instruction is

executed)

Execution Speed LD instructions – 0.54μs, MOV instructions – 3.4μs

Program language Instruction List + Ladder + SFC

Program Capacity 15872 steps

Bit

Contacts

X External inputs

Y External outputs

X0~X377, octal number system, 256

points max.

Y0~Y377, octal number system, 256

points max.

Total

480+14

I/O(*4)

M0~M511, 512 points, (*1)

General

M768~M999, 232 points, (*1)

M2000~M2047, 48 points, (*1)

M

uxiliary

relay

Latched

Special

M512~M767, 256 points, (*2)

M2048~M4095, 2048 points, (*2)

M1000~M1999, 1000 points, some

are latched

Total

4096 points

T0~T126, 127 points, (*1)

100ms

(M1028=ON,

T64~T126:

10ms)

T Timer

10ms

(M1038=ON,

T200~T245: 1ms)

T128~T183, 56 points, (*1)

T184~T199 for Subroutines, 16

points, (*1)

T250~T255(accumulative),

6 points (*1)

T200~T239, 40 points, (*1)

T240~T245(accumulative),

Total

256 points

6 points, (*1)

T127, 1 points, (*1)

1ms

T246~T249(accumulative), 4 points,

(*1)

C

Counter

16-bit count up

C0~C111, 112 points, (*1)

C128~C199, 72 points, (*1)

C112~C127, 16 points, (*2)

Total

232 points

32-bit count

up/down

32bit Softhigh- ware

C200~C223, 24 points, (*1)

C224~C231, 8 points, (*2)

C235~C242, 1 phase 1 input, 8

points, (*2)

Total

23 points

2-11

Page 44

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

Specifications

speed

count

up/down

C232~C234, 2 phase 2 input, 2

points, (*2)

C243~C244, 1 phase 1 input, 2

points, (*2)

Hard-

ware

C245~C250, 1 phase 2 input, 6

points, (*2)

C251~C254 2 phase 2 input, 4

points, (*2)

Initial step point S0~S9, 10 points, (*2)

S10~S19, 10 points (use with IST

instruction), (*2)

S

Step

point

Zero point return

Latched S20~S127, 1 08 points, (*2)

General S128~S911, 784 points, (*1)

Alarm S912~S1023, 112 points, (*2)

T Current value T0~T255, 256 words

C0~C199, 16-bit counter, 200 words

C Current value

C200~C254, 32-bit counter, 55 words

Total 1024

points

Word

Register

Pointer

D0~D407, 408 words, (*1)

General

D600~D999, 400 words, (*1)

D3920~D9999, 6080 words, (*1)

D

Data

register

Latched

Special

D408~D599, 192 words, (*2)

D2000~D3919, 1920 words, (*2)

D1000~D1999, 1000 words, some

are latched

Index E0~E7, F0~F7, 16 words, (*1)

N Master control loop N0~N7, 8 points

P Pointer P0~P255, 256 points

I Interrupt

Service

External interrupt

Timer interrupt

I000/I001(X0), I100/I101(X1), I200/I201(X2),

I300/I301(X3), I400/I401(X4), I500/I501(X5),

I600/I601(X6), I700/I701(X7), 8 points (01: risingedge trigger

, 00: falling-edge trigger )

I602~I699, I702~I799, 2 points (T imer resolution =

1ms)

Total

10000 points

2-12

Page 45

Specifications

2. Programming Concepts

High-speed

counter interrupt

Communication

interrupt

I010, I020, I030, I040, I050, I060, I070, I080, 8

points

I140(COM1), I150(COM2), 2 points, (*3)

K-32,768 ~ K32,767 (16-bit operation),

K Decimal K-2,147,483,648 ~ K2,147,483,647 (32-bit

Constant

H Hexadecimal

operation)

H0000 ~ HFFFF (16-bit operation),

H00000000 ~HFFFFFFFF (32-bit operation)

COM1: built-in RS-232 ((Master/Slave)

Serial ports

COM2: built-in RS-485 (Master/Slave)

COM3: built-in USB port (Slave)

COM1 is typically the programming port.

Real Time Clock Year, Month, Day, Week, Hours, Minutes, Seconds

Right side: Up to 8 special I/O modules can be

Special I/O Modules

connected

Left side: Up to 8 high-speed I/O modules can be

connected

Notes:

1. Non-latched area cannot be modified

2. Latched area cannot be modified

3. COM1: built-in RS232 port. COM2: built-in RS485 port.

4. SX2 MPU occupies 16 input points (X0~X17) and 16 output points (Y0~Y17).

2-13

Page 46

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

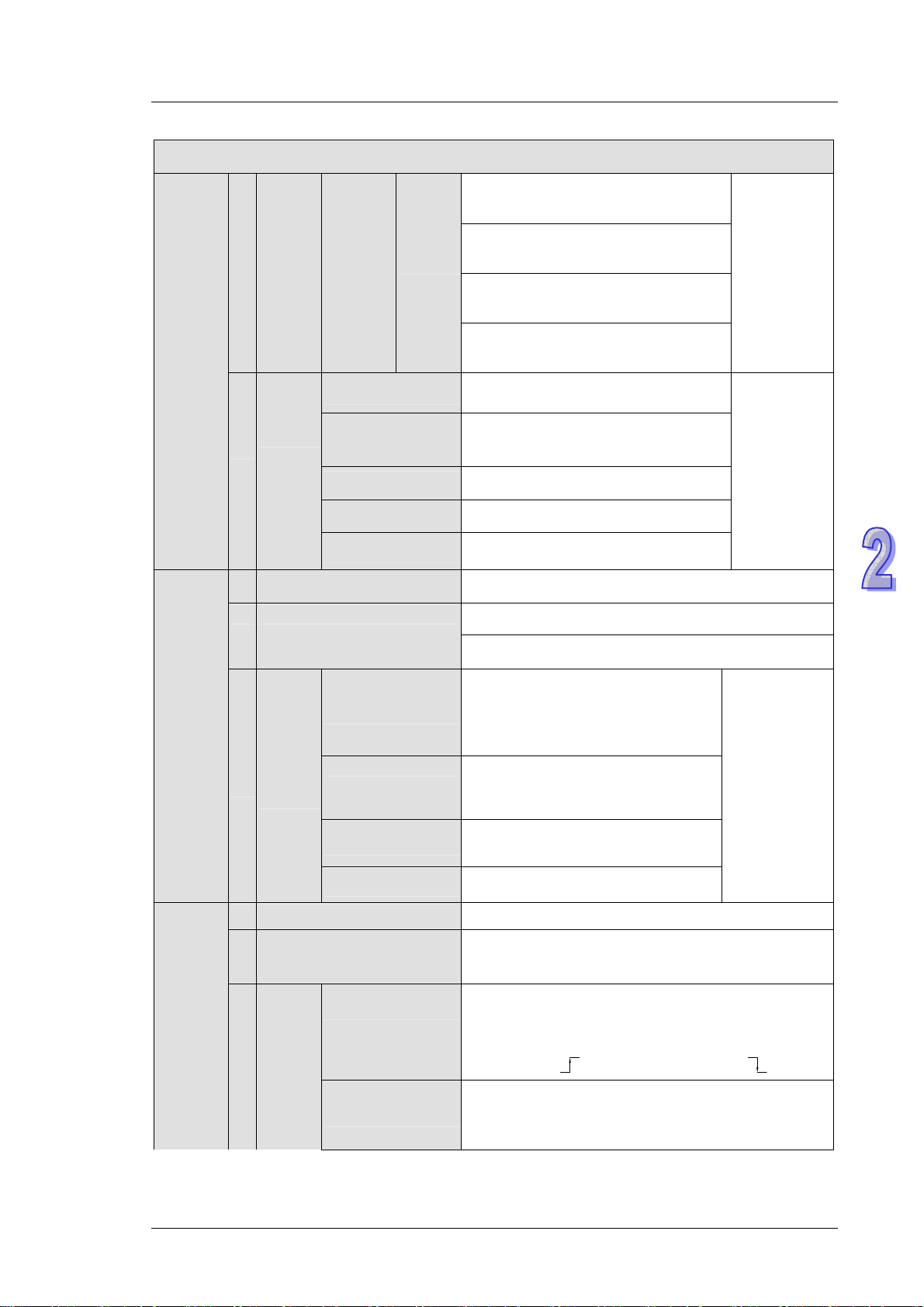

2.5 Status and Allocation of Latched Memory

Clear all

Memory

type

Nonlatched

Latched Unchanged Unchanged Clear 0

Special M,

Special D,

Index

Register

Power

OFF=>ON

Clear Unchanged Clear Unchanged 0

Initial Unchanged Unchanged

STOP=>RUN

RUN=>STOP

When

M1033=OFF, clear

When M1033=ON,

No change

non-latched Factory

area setting

(M1031=ON)

Clear all

latched area

(M1032=ON)

Initial

setting

General Latched Special auxiliary relay

M

Auxiliary relay

M0~M511

M768~M999

M2000~M2047

Not latched Latched

M512~M999

M2048~M4095

M1000~M1999

Some are latched and

can’t be changed.

T

Timer

C

Counter

S

Step relay

D

Register

100 ms 100 ms 1 ms 10 ms 10ms 1 ms 100 ms

T0 ~T126 T250~T

T128~T183

M1028=1,T64~

T126:10ms

non-latched non-latched Accumulative non-latched

16-bit count up 32-bit count up/down

C0~C111

C128~C199

Non-latched Latched Non-latched Latched Latched

Initial Zero return Latched General Step alarm

S0~S9 S10~S19 S20~S127 S128~S911 S912~S1023

General Latched Special register For AIO

D0~D407

D600~D999

D3920~D9899

Non-latched Latched

T184~T199 T127 T200~T239 T240~T245 T246~T249

For

subroutine

C112~C127 C200~C223 C224~C231 C232~C254

Latched Non-latched Latched

D408~D599 D9900~D999

D2000~D3919

M1038=1,T200~T245:

1ms

D1000~D1999

Some are latched, and

can’t be changed

32-bit high-speed

count up/down

Non-latched

255

-

9

2-14

Page 47

2. Programming Concepts

2.6 PLC Bits, Nibbles, Bytes, Words, etc

For different control purposes, there are five types of values inside DVP-PLC for executin g the

operations.

Numeric Description

Bit

Nibble

Bit is the basic unit of a binary number system. Range is 0 or 1

Consists of 4 consecutive bits, e.g. b3~b0. Range 0 ~ 9 in Decimal or 0~F in

Hex

Byte

Word

Consists of 2 consecutive nibbles, e.g. b7~b0. Range 00 ~ FF in Hex

Consists of 2 consecutive bytes, e.g. b15~b0. Range 0000 ~ FFFF in Hex

Consists of 2 consecutive words, e.g. b31~b1. Range 00000000 - FFFFFFFF

Double Word

in Hex

Bit, nibble, byte, word, and double word in a binary system:

DW

W1

BY3 BY2 BY1 BY0

2.7 Binary, Octal, Decimal, BCD, Hex

W0

Double Word

Word

Byte

NB0NB1NB2NB3NB4NB5NB6NB7

Nibble

Bit

For fulllfilling different kinds of internal manipulation, DVP-PLC appies 5 foramts of number systems.

Each number system has its specific purpose and function describ ed as below.

1. Binary Number, (BIN)

PLC internally calculates, operates, and stores the value in Binary format.

2. Octal Number, (OCT)

The external I/O points of DVP-PLC are numbered in octal format.

e.g.

External inputs: X0~X7, X10~X17, …, X377. (No. of device)

External outputs: Y0~Y7, Y10~Y17, …, Y377. (No. of device)

3. Decimal Number, (DEC)

DVP-PLC appies decimal operation in situations below:

z Set value for timers and counters, e.g. TMR C0 K50. (K value)

z No. of S, M, T, C, D, E, F, P, I devices, e.g. M10, T30. (No. of device)

z For use of operand in API instru ctions, e.g. MOV K123 D0. (K value)

2-15

Page 48

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

z Constant K:

Decimal value in PLC operation is attached with an “K”, e.g. K100 indicates the value 100 in

Decimal format.

Exception:

When constant K is used with bit devices X, Y, M, S, the value specifed after K indicates

the groups of 4-bit unit, which forms a digit(4-bit), byte(8 bit), word(16bit), or double

word(32-bit) data, e.g. K2Y10, K4M100, representing Y10 ~ Y17 and M100~M1 15.

4. BCD (Binary Coded Decimal)

BCD format takes 1 digit or 4 bits to indicate a Decimal value, so that data of consecutive 16

bits indicates a 4-digit decimal value. Used mainly for reading values from DIP switches or

sending data to 7-segement displays

5. Hexadecimal Number, HEX

DVP-PLC appies Hexadecimal operation in situations below:

z For use of operand in API instru ctions, e.g. MOV H1A2B D0。(H value)

z Constant H:

Hexadecimal value in PLC operation is attached with an “H”, e.g. H100 indicates the value

100 in Hex format.

Reference Table:

Binary Octal Decimal (K) BCD Hexadecimal (H)

(BIN) (OCT) (DEC) (Binary Code Decimal) (HEX)

For PLC

internal

operation

No. of X, Y

relay

Costant K, No. of

registers M, S, T, C,

D, E, F, P, I devices

For DIP Switch and 7segment display

Constant H

0000 0 0 0000 0

0001 1 1 0001 1

0010 2 2 0010 2

0011 3 3 0011 3

0100 4 4 0100 4

0101 5 5 0101 5

0110 6 6 0110 6

0111 7 7 0111 7

1000 10 8 1000 8

1001 11 9 1001 9

1010 12 10 0000 A

1011 13 11 0001 B

1100 14 12 0010 C

2-16

Page 49

2. Programming Concepts

Binary Octal Decimal (K) BCD Hexadecimal (H)

(BIN) (OCT) (DEC) (Binary Code Decimal) (HEX)

For PLC

internal

operation

No. of X, Y

relay

Costant K, No. of

registers M, S, T, C,

D, E, F, P, I devices

For DIP Switch and 7segment display

Constant H

1101 15 13 0011 D

1110 16 14 0100 E

1111 17 15 0101 F

10000 20 16 0110 10

10001 21 17 0111 11

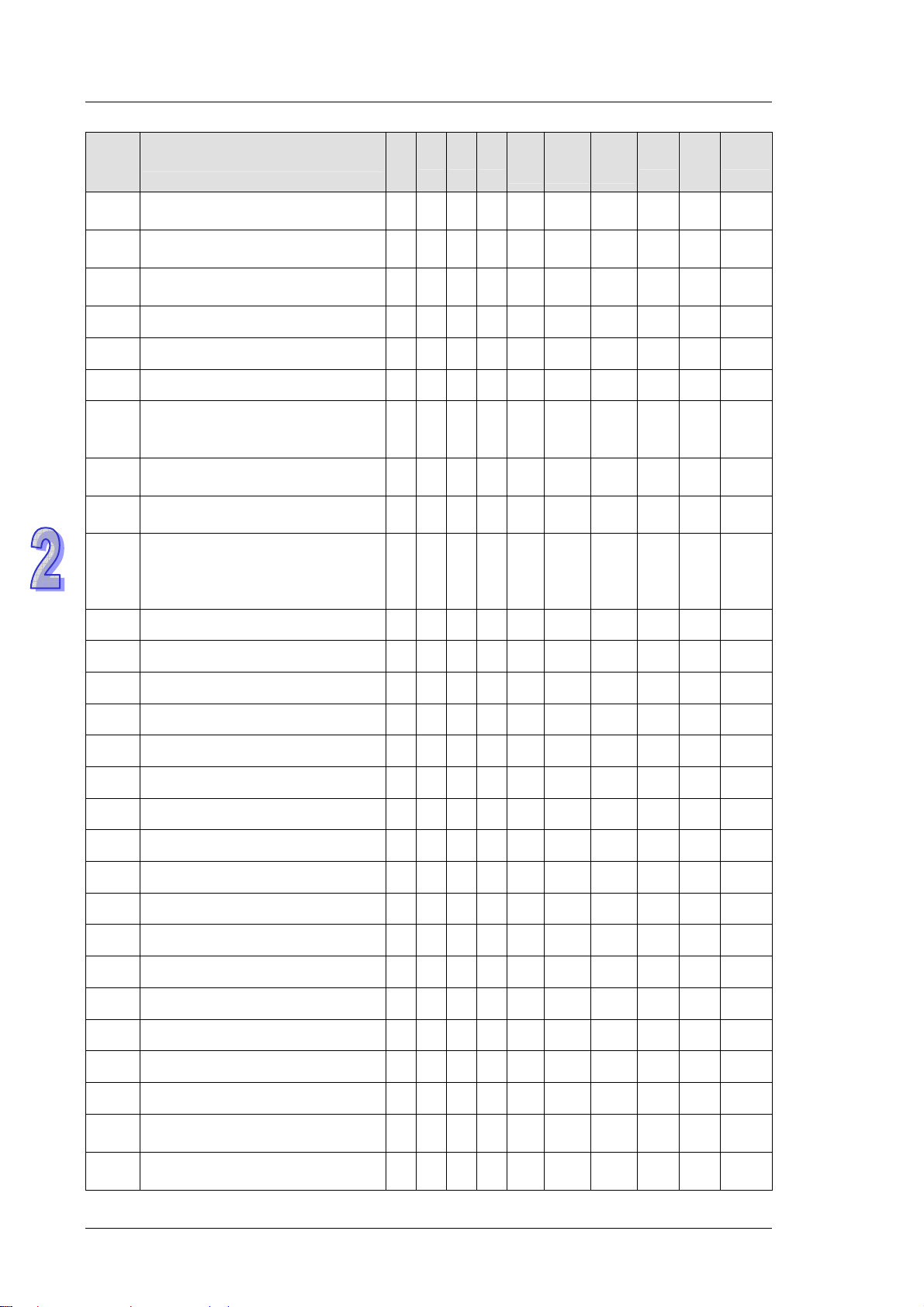

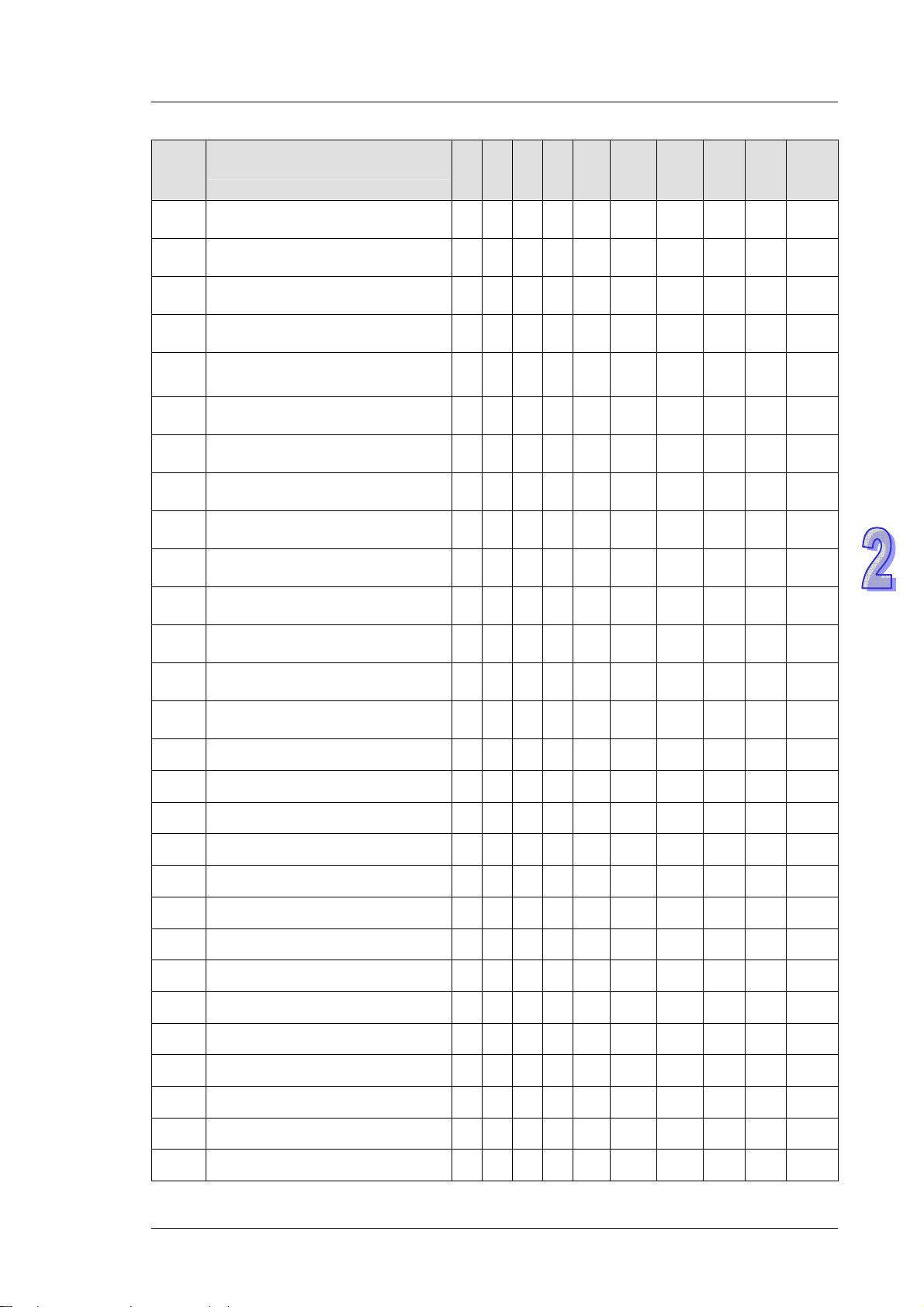

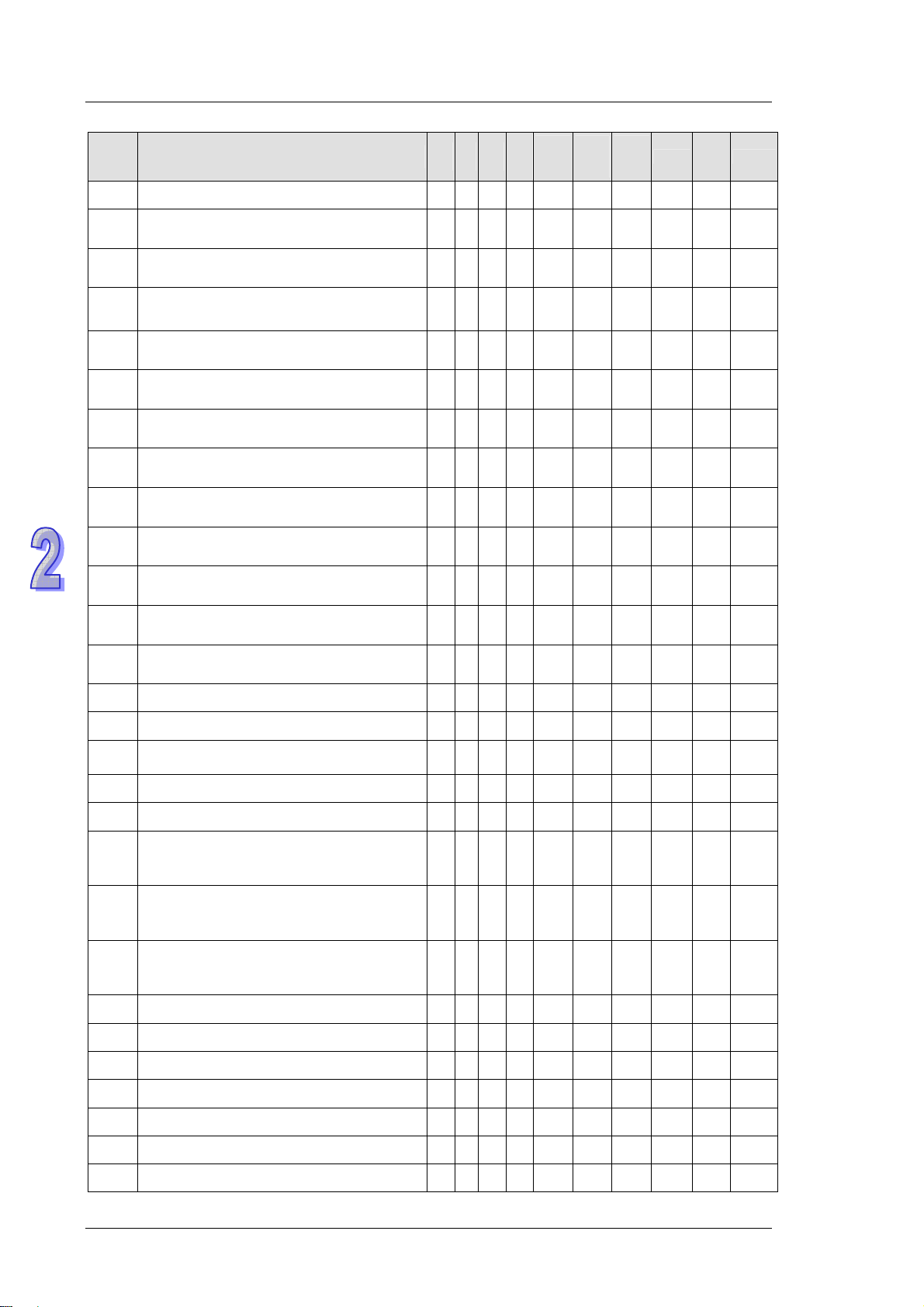

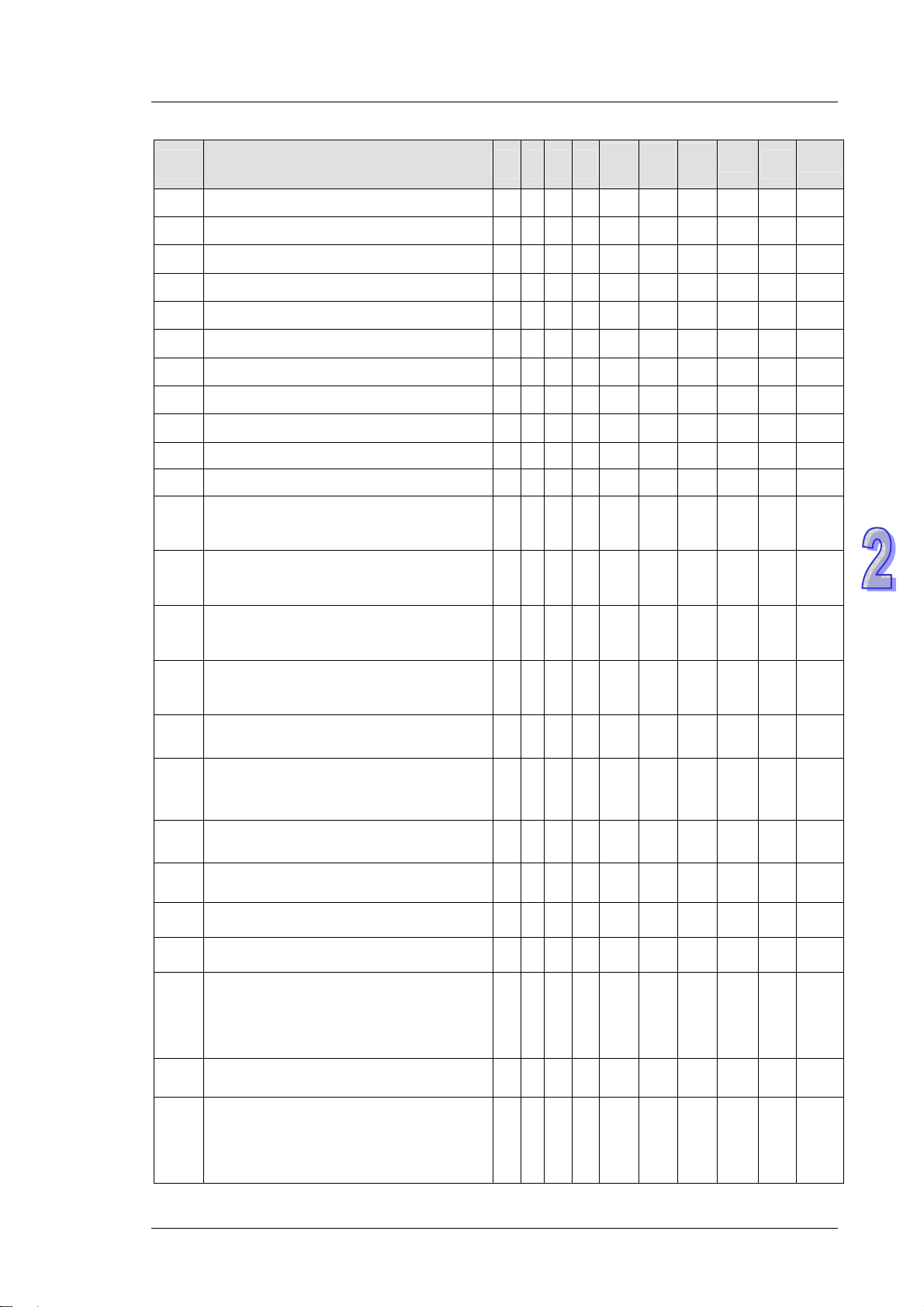

2.8 M Relay

The types and functions of special auxiliary relays (special M) are listed in the table below. Care

should be taken that some devices of the same No. may bear different meanings in different series

MPUs. Special M and special D marked with “*” will be further illustrated in 2.13. Columns marked

with “R” refers to “read only”, “R/W” refers to “read and write”, “-“ refers to the status remains

unchanged and “#” refers to that system will set it up according to the status of the PLC.

OFF

Special

M

Function

ES2

SS2 SA2 SX2

EX2

Ø

ON

STOP

RUN

Ø

RUN

Ø

STOP

Attrib.

Latch

-ed

Default

M1000* OFF ON OFF R NO OFF

M1001* ON OFF ON R NO ON

M1002*

M1003*

M1004* ON when syntax errors occur OFF OFF - R NO OFF

M1008* OFF OFF - R NO OFF

M1009

M1011* 10ms clock pulse, 5ms ON/5ms OFF OFF - - R NO OFF

M1012*

M1013* 1s clock pulse, 0.5s ON / 0.5s OFF OFF - - R NO OFF

M1014* 1 min clock pulse, 30s ON / 30s OFF OFF - - R NO OFF

M1015* Enable high-speed timer OFF - - R/W NO OFF

M1016* OFF - - R/W NO OFF

Monitor normally open contact

Monitor normally closed contact

Enable single positive pulse at the

moment when RUN is activate (Normally

OFF)

Enable single negative pulse at the

moment when RUN is activate (Normally

ON)

Watchdog timer (ON: PLC WDT time out)

Indicate LV signal due to 24VDC

insufficiency

100ms clock pulse, 50ms ON / 50ms

OFF

Indicate Year display mode of RTC.

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

OFF ON OFF R NO OFF

ON OFF ON R NO ON

OFF - - R NO OFF

OFF - - R NO OFF

M1017* OFF - - R/W NO OFF

M1018 Flag for Radian/Degree, ON for degree OFF - - R/W NO OFF

±30 seconds correction on real time clock

○ ○ ○ ○

○ ○ ○ ○

2-17

Page 50

DVP-ES2/EX2/SS2/SA2/SX2/SE Operation Manual - Programming

OFF

Special

M

Function

ES2

SS2 SA2 SX2

EX2

Ø

ON

STOP

Ø

RUN

STOP

RUN

Ø

Attrib.

Latch

-ed

Default

M1020 Zero flag

M1021 Borrow flag

M1022 Carry flag

M1024 COM1 monitor request

M1025*

M1026 RAMP mode selection

M1027 PR output mode selection (8/16 bytes)

M1028

M1029*

M1030*

M1031* Clear all non-latched memory

M1032* Clear all latched memory

M1033* Output state latched at STOP

M1034* Disable all Y outputs

Indicate incorrect request for

communication

Switch T64~T126 timer resulotion

(10ms/100ms). ON =10ms

CH0 (Y0, Y1) pulse output execution

completed.

Pulse output Y1 execution completed

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

OFF - - R NO OFF

OFF - - R NO OFF

OFF - - R NO OFF

OFF - - R/W NO OFF

OFF - - R NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R NO OFF

OFF - - R NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

M1035*

M1037*

M1038

M1039* Fix scan time

M1040 Disable step transition

M1041 Step transition start

M1042 Enable pulse operation

M1043 Zero return completed

M1044 Zero point condition

M1045 Disable “all output reset” function

M1046 Indicate STL status

M1047 Enable STL monitoring

M1048 Indicate alarm status

M1049 Enable alarm monitoring

Enable X7 input point as RUN/STOP

switch

Enable 8-sets SPD function (Has to be

used with D1037)

Switch T200~T255 timer resulotion

(10ms/1ms). ON = 1ms

○ ○ ○ ○

╳ ╳ ○○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

- - - R/W YES OFF

OFF OFF OFF R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - OFF R/W NO OFF

OFF - - R/W NO OFF

OFF - OFF R/W NO OFF

OFF - OFF R/W NO OFF

OFF - - R/W NO OFF

OFF - - R NO OFF

OFF - - R/W NO OFF

OFF - - R NO OFF

OFF - - R/W NO OFF

M1050 Disable interruption I000 / I001

M1051 Disable interruption I100 / I101

2-18

○ ○ ○ ○

○ ○ ○ ○

OFF - - R/W NO OFF

OFF - - R/W NO OFF

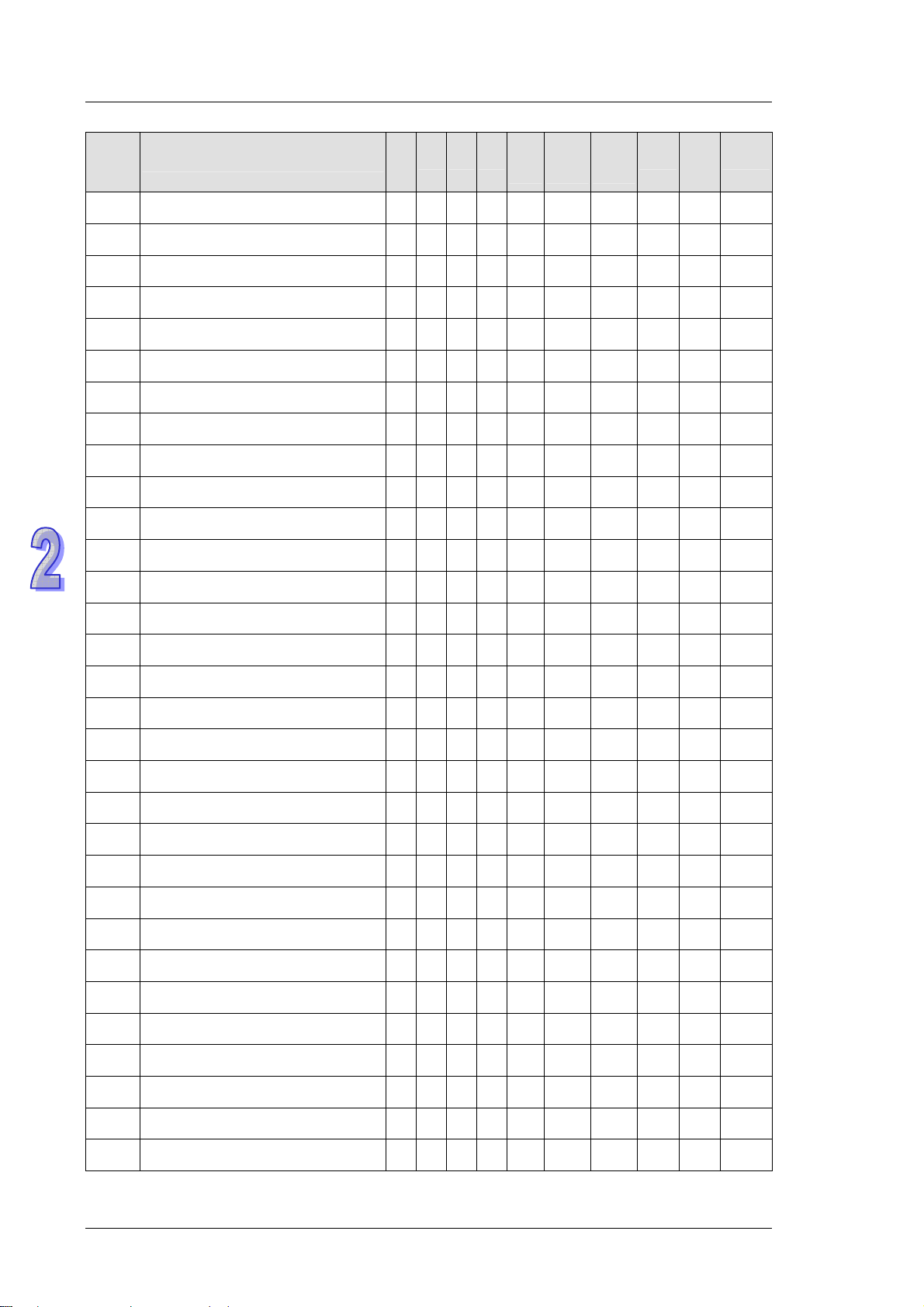

Page 51

Special

M

Function

ES2

SS2 SA2 SX2

EX2

OFF

Ø

ON

2. Programming Concepts

STOP

RUN

Ø

RUN

Ø

STOP

Attrib.

Latch

-ed

Default

M1052 Disable interruption I200 / I201

M1053 Disable interruption I300 / I301

M1054 Disable interruption I400 / I401

M1055 Disable interruption I500 / I501

M1056 Disable interruption I600~I699

M1057 Disable interruption I700~I799

M1058 COM3 monitor request

M1059

M1060 System error message 1

M1061 System error message 2

M1062 System error message 3

M1063 System error message 4

M1064 Incorrect use of operands

M1065 Syntax error

M1066 Loop error

Disable high-speed counter interruptions

I010~I080

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ╳ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

○ ○ ○ ○

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R/W NO OFF

OFF - - R NO OFF

OFF - - R NO OFF

OFF - - R NO OFF

OFF - - R NO OFF

OFF OFF - R NO OFF

OFF OFF - R NO OFF

OFF OFF - R NO OFF

M1067* Program execution error

M1068* Execution error locked (D1068)

M1070

M1071

M1072 PLC status (RUN/STOP), ON = RUN

M1075

M1078

M1079

M1080 COM2 monitor request

M1081

M1083*

M1084*

M1085

Switching clock pulse of Y1 for PWM

instruction (ON: 100us; OFF: 1ms)

Switching clock pulse of Y3 for PWM

instruction (ON: 100us; OFF: 1ms)

Error occurring when write in Flash ROM

Y0/CH0(Y0, Y1) pulse output pause

(immediate)

Y1 pulse output pause (immediate)

Changing conversion mode for FLT

instruction

Selecting X6 pulse-width detecting mode.

M1083 = ON, detecting pulse-width when

X6 = ON; M1083 = OFF, detecting pulsewidth when X6 = OFF.

Enabling X6 Pulse width detecting

function. (has to be used with M1183 and

D1023)