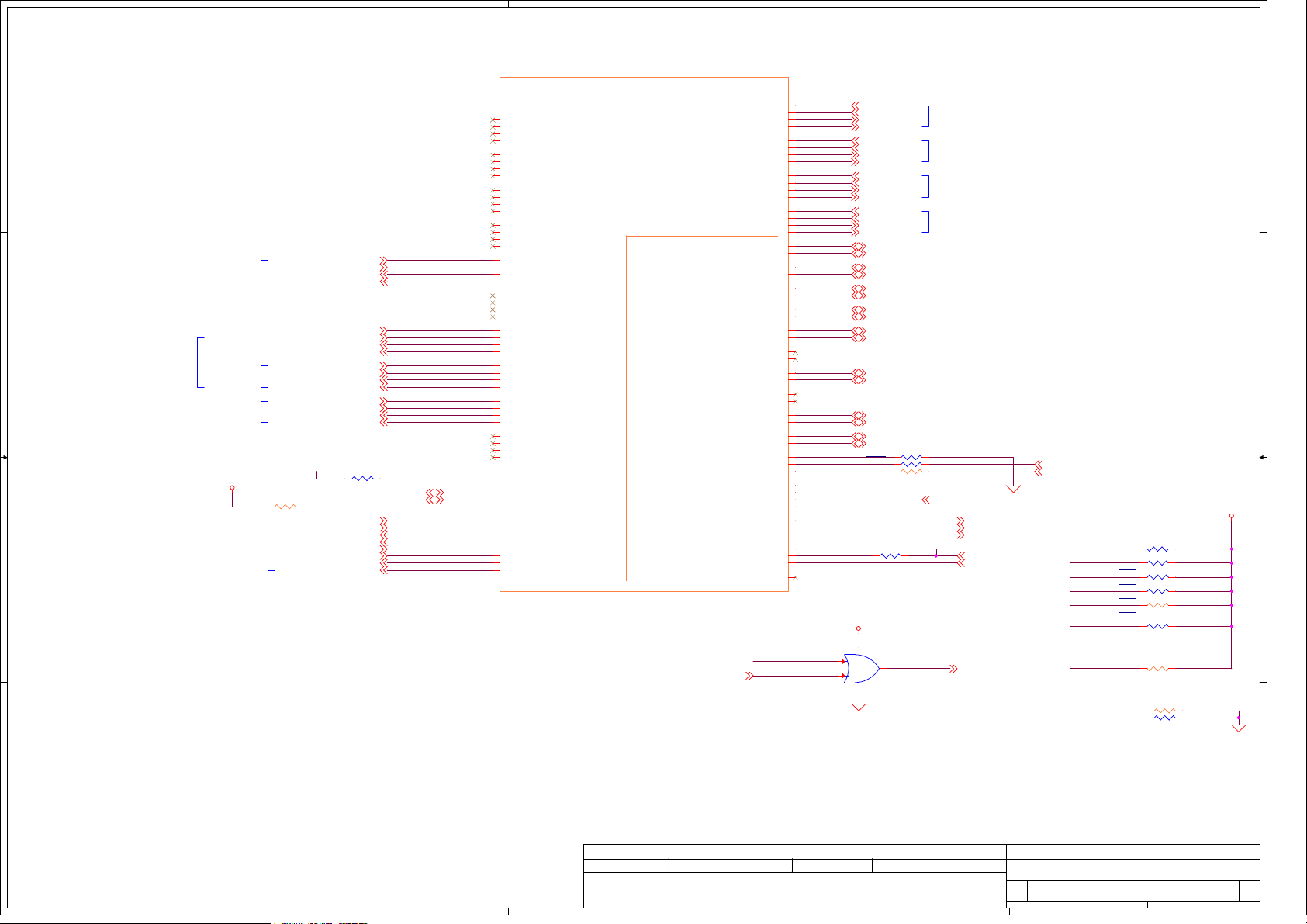

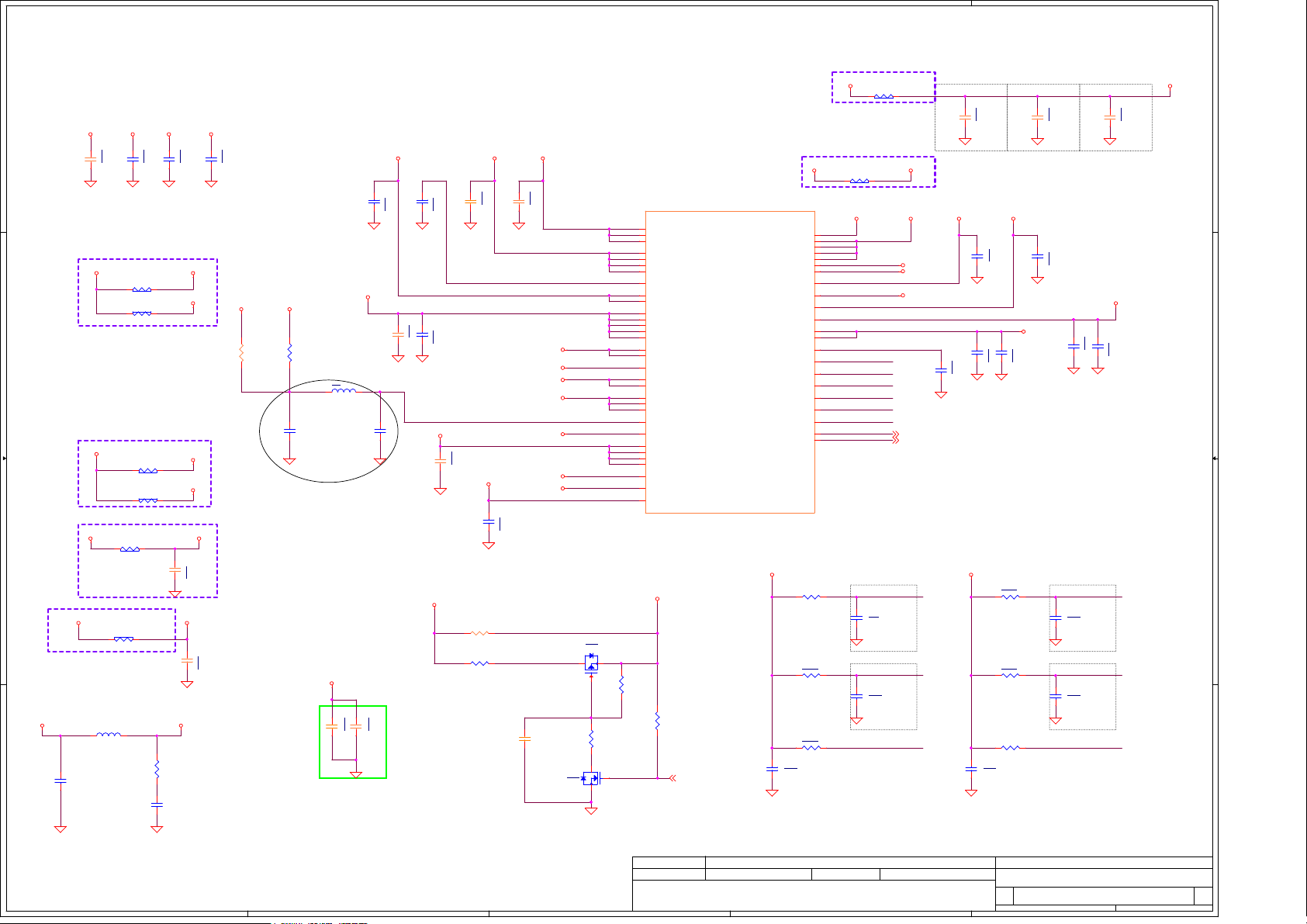

Dell LATITUDE 5290 boardview

A

B

C

D

E

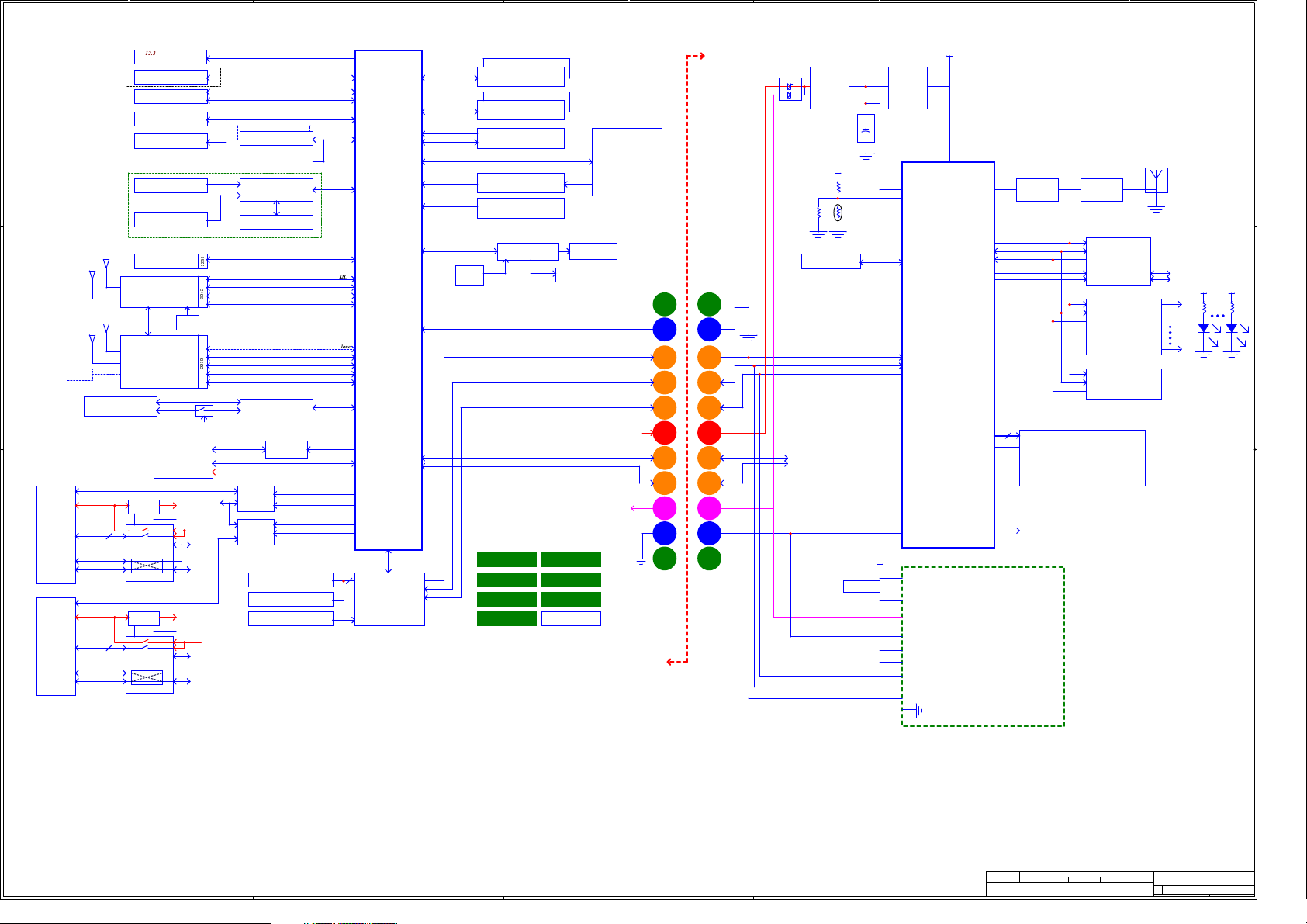

MODEL NAME : LA-F371P non-AR

PCB NO : DAA000EC010

BOM P/N : 431A8C31L01

1 1

Dell/Compal Confidential

2 2

Schematic Document

Pebble Creek MLK (Kabylake R/U)

3 3

2017-11-03

Rev: 1.0

ZZZ

MB_PCB

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2015/10/22 2013/10/28

2015/10/22 2013/10/28

2015/10/22 2013/10/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P01-Cover Page

P01-Cover Page

P01-Cover Page

Document Number Re v

Document Number Re v

Document Number Re v

LA-F371P

LA-F371P

LA-F371P

E

1 65Tuesday, November 07, 2017

1 65Tuesday, November 07, 2017

1 65Tuesday, November 07, 2017

1.0

1.0

1.0

A

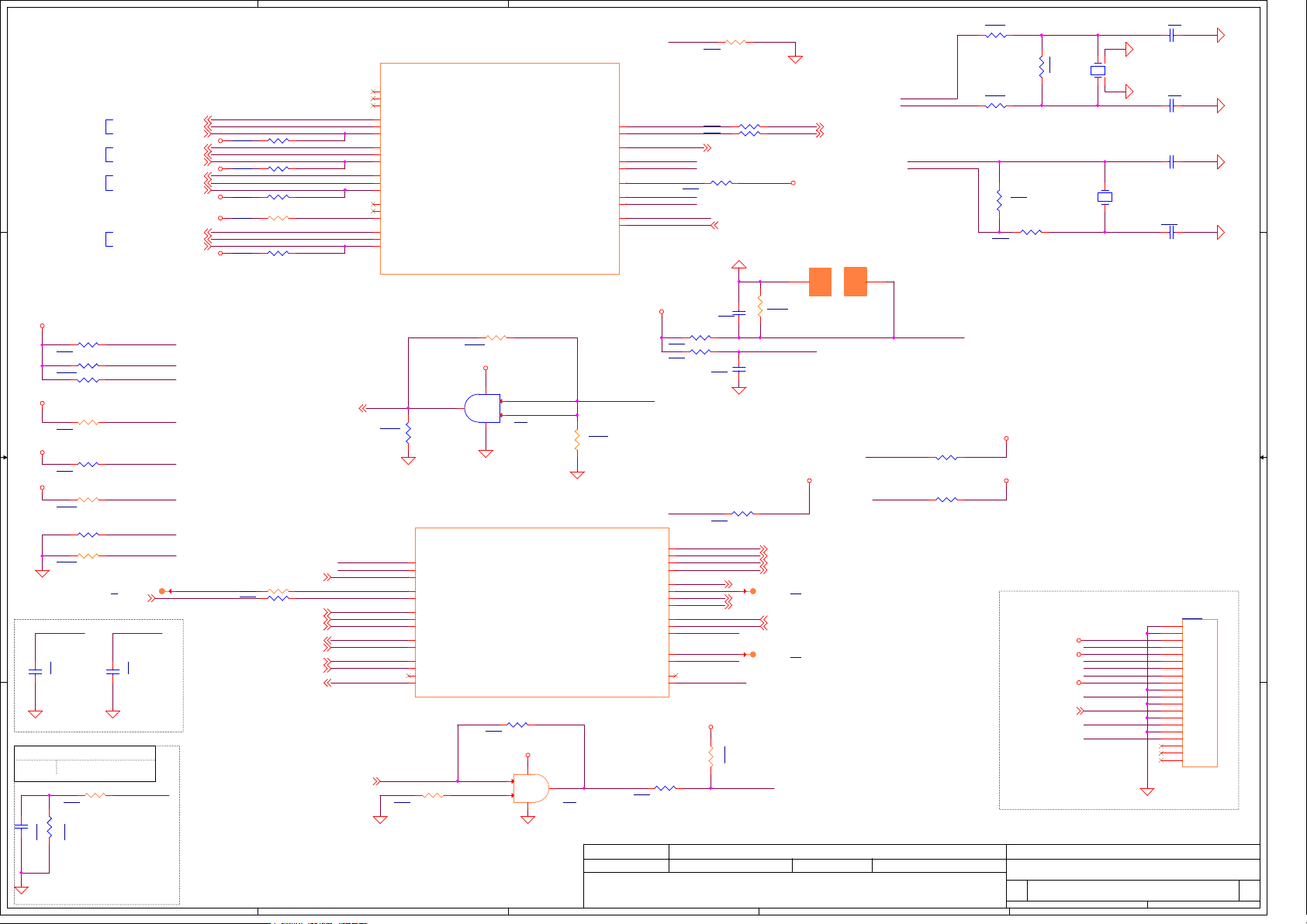

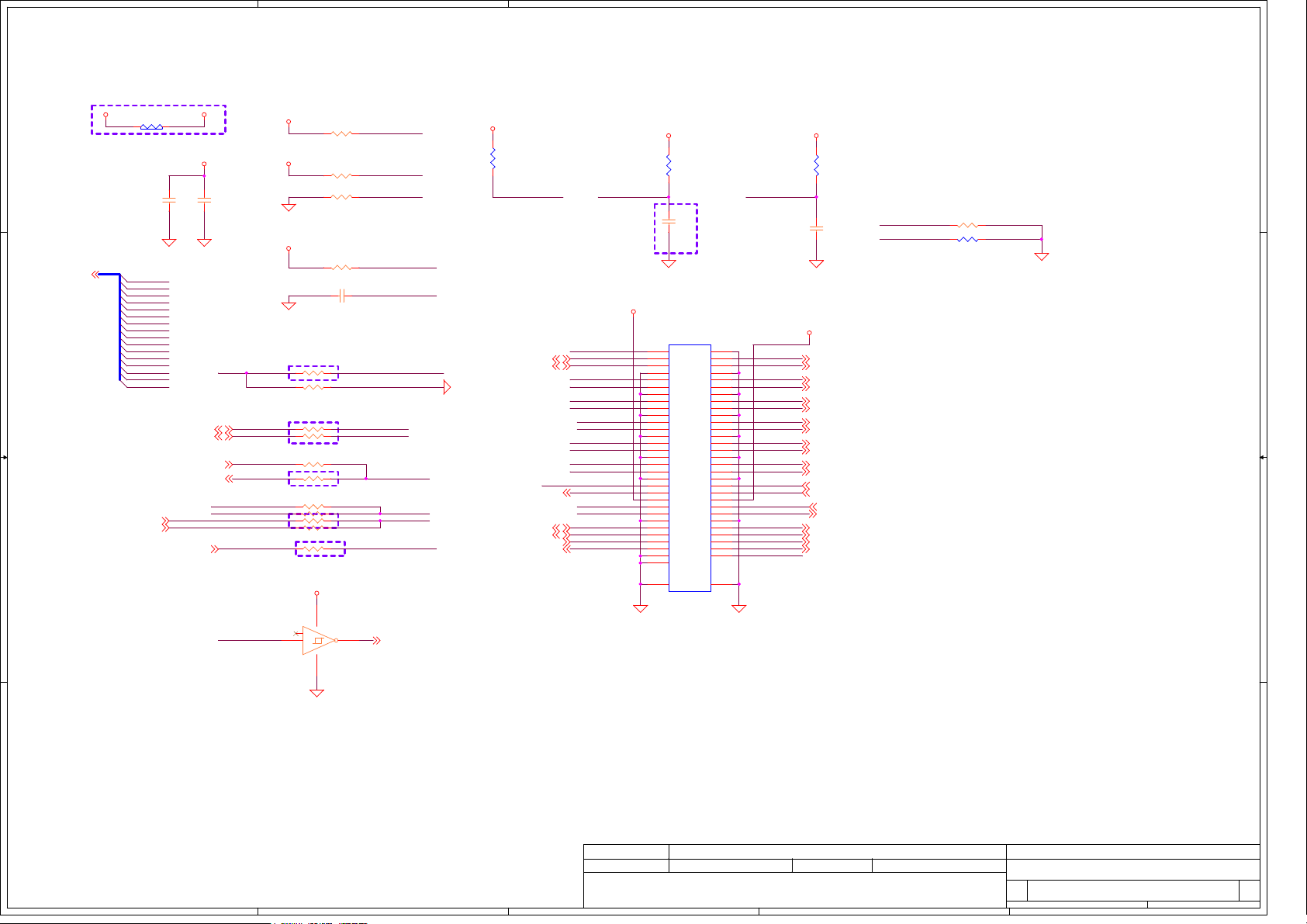

12.3" 3:2

Samsung W UXGA+

ALS

AMS-TAOS TSL2591

Touch Cntrl

1 1

Wacom G12T-W9015

Gyro + Accelerometer

ST LSM6DS3TR

E-Compass

ST LIS2MDLTR

p.22

p.31

p.22

p.31

p.31

on WF camera module

SPI ROM 16M (Main)

SPI ROM 4M(2nd)

NPCT750JB AYX

p.23

p.25

uSIM

p.26

p.24

CHRG_IN

From EC

5V_ALW

CHRG_IN

From EC

5V_ALW

0

8

2

2

2

4

0

3

0

3

2

2

GPIO

(BIOS C ontrolled)

p.38

to EC

to EC

to PCH

to PCH

SPI

USB3.0

RealTek

RTS5242 PCIe to SD

5V@1.5A

Parade

MUX

PS8743A

Parade

MUX

PS8743A

USH Control Vault

Broadcom 58102

Module : DWRFID1603

RDIF/NFC

Antenn a

BC1.2

TI TPS254 4

p.37

p.37

SAR Proximity Sensor

Smtech SX9310

Hall Sensor (On USH board )

TCS40DPR

Kickstand Open /Close detection

(mechanical switch)

Finger Print Reader

NB 2023-S

Smart Card Reader

NXP TDA803 4HN

on IO board

SSD M.2 2280

Slot 3-Key-M

WWAN 4G LTE

M.2 3042 Slot 2-Key-B

Hardware Crypto Accelerator

Module : EM7455

LTE Coex

2 2

RFFEM

uSD Connector

WLAN / BT 4.1

M.2 2230 Slot 1-Key-A

3x3(UI)

WiGig (UI)

Module :

8265NGW/QCNFA 344A

18265NGW

SD4.0/SDXC

SD_WP

p.27

USB3.0 TypeA

BC1.2

with Power Share

TI TPS254 4

USB3.0 / DP x 2lanes or DP x 4 lanes

VBUS

Port-A

CC 2

USB Type-C

ALT mode

with PD

3 3

USB (Top)

USB (Bottom)

p.39

MOSFET

VBUS PP_5V0

CC

TI-ACE 65 982-DC

I2C

p.35

USB3.0 / DP x 2lanes or DP x 4 lanes

Port-B

USB Type-C

ALT mode

with PD

VBUS

CC 2

USB (Top)

USB (Bottom)

p.39

MOSFET

VBUS PP_5V0

CC

TI-ACE 65 982-DC

I2C to EC

p.36

eDP x2 lanes

p.7

p.31

USB 2.0

IOB conn p.43

PCIe x 2lanes

GNSS I2C

PCIe x 2lanes

USB 3.0 / SSIC

USB 2.0

PCIe x 1lane

PCIe x 1lane

USB2.0

eLBS

CLINK

PCIe x 1lane

p.27

USB2.0

USB2.0

p.38

USB3.0

DP1.2 x 4lanes

USB3.0

USB3.0

DP1.2 x 4lanes

p.31

p.31

p.42 p.30

B

eDP

I2C

ISH

Channel A

I2C

I2C

SPI SPI#2

I2C

SPI

I2C (iSH)

SPI#1

Channel B

CSI-2#2

I2C

I2C

CSI-02#0

USB#7

USB2.0 #5

KabyLake U

EC

MEC5105

ESPI

HDA

GPIO

USB2#2

I2C_CLK

I2C_DAT

I2C_INT

I2C 3

PCIe#7,8

I2C (iSH)

PCIe#11/PCIe #12

USB3 # 2 / SSIC

USB2 # 4

PCIe#5

PCIe#6

USB2#7

UART

CLINK

PCIe#9

USB2#9

UART

USB3#3

DDI#2

USB3.0 #1

USB3.0 #4

DDI#1

TABLET

Memory Bus

Memory Bus

MIPI CSI-2 x 2lanes

I2C

I2C

MIPI CSI-2 x 2lanes

D+/D-

4x DMIC

3DMIC on M/B

1DMIC on WFCAM

Dock_Dete ct

Channel A - 4GB

LPDDR3 1866/2133

32Gb x 32 QDP

Channel B - 4GB

LPDDR3 1866/2133

32Gb x 32 QDP

5MP FFC

5BF501 T2/OV5 670

8MP RFC

5BA802T2/OV8 858

Face IR Module

LiteOn 5SF106N2B

HDA

1.5V

p.28

EC JTAG

SPI Programmer

USB PD Debug

DCI Debug

Channel A - 4GB

Channel B - 4GB

Audio Codec

ALC325 3-VA3-C G

p.19

p.20

p.33

SKYCAM PMIC

TPS68470YFFR_DBSG A56

I2C

p.33

p.43

Universal

Headset Jack

p.28 p.29

2x

Speaker

p.29

XDP DEbug

ESPI Debug

APS Debug

Coin Cell

I2C_INT

CHRG_IN

5V/2A

C

3.3V LDO

VSW_3V3

p.34

SPI ROM 2MB

GND

GND

DET_L

DET_L

I2C1

I2C1

CLK

CLK

I2C1

I2C1

DAT

DAT

I2C1

I2C1

INT

INT

5V

5V

D+

D-

12V

DET_R

GND

D+

D-

12V

DET_R

GND

USB 2.0 D+

USB 2.0 D-

D

Boost

TPS61 200

A/D

A/D

SPI

SPI

I2C_CLK

I2C_DAT

I2C_INT

HEAD_DET # GPIO

VR_OUT

VCC_EC

VSW_3V3

VCC

CSR1021

TX/RX

I2C_CLK

I2C_DAT

I2C_INT

GPIO

GPIO

KSO/KSI

GPIO

Pi-Matching i-pex conn

PTP_MODE #

PTP_SL P#

Keyboard Matrix

BT ON/OFF ButtonGPIO

I2C_CLK

I2C_DAT

I2C_INT

PTP_MODE #

EN

CLK

DAT

INT

I/O Expander

TI TCA6416

I2C_CLK

I2C_DAT

I2C_INT

E

USB_D-

Charge/Low _BAT#

KB_LED_PW M

KB_BL_D ET#

MASK_LE D#

MUTE_LE D#

BT_LED#

Accelermeter

ST LNG2DMTR

USB 2.0 D+USB_D+

USB 2.0 D-

5V 5V

WCFW_EN

+VCC_EC

WC_OUT

POGO_DET _R#

WC_DISC

CHG_DICS(NC)

I2C#1_INT

I2C#1_D AT

I2C#1_C LK

WC PRU Board

GND

Keyboard

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

D

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2015/10/22 2013/10/28

2015/10/22 2013/10/28

2015/10/22 2013/10/28

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

P02-Block Diagram

P02-Block Diagram

P02-Block Diagram

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-F371P

LA-F371P

LA-F371P

Date: Sheet of

Date: Sheet o f

Date: Sheet o f

E

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

2 65Tuesday, November 07, 2 017

2 65Tuesday, November 07, 2 017

2 65Tuesday, November 07, 2 017

1.0

1.0

1.0

A

B

C

D

E

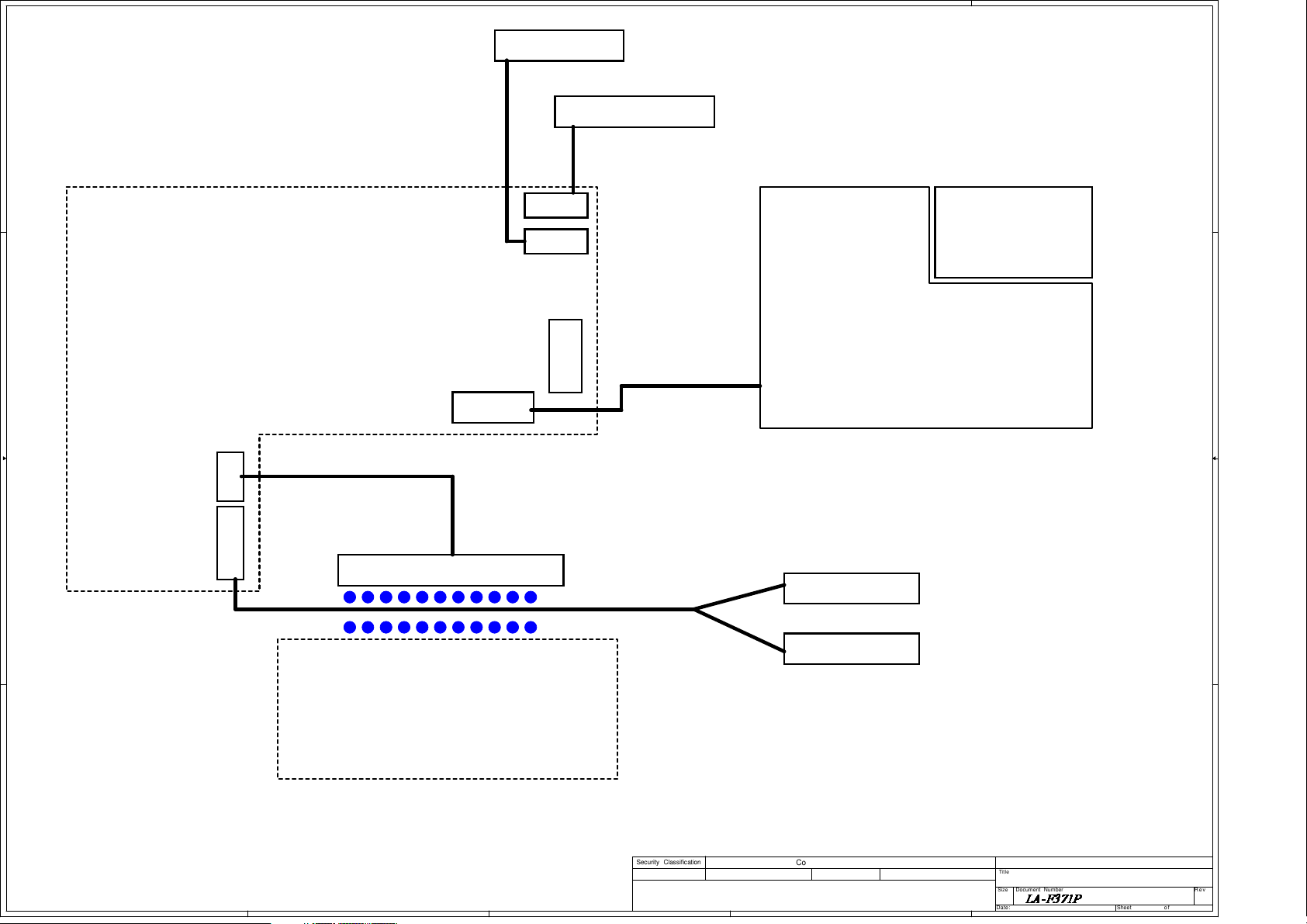

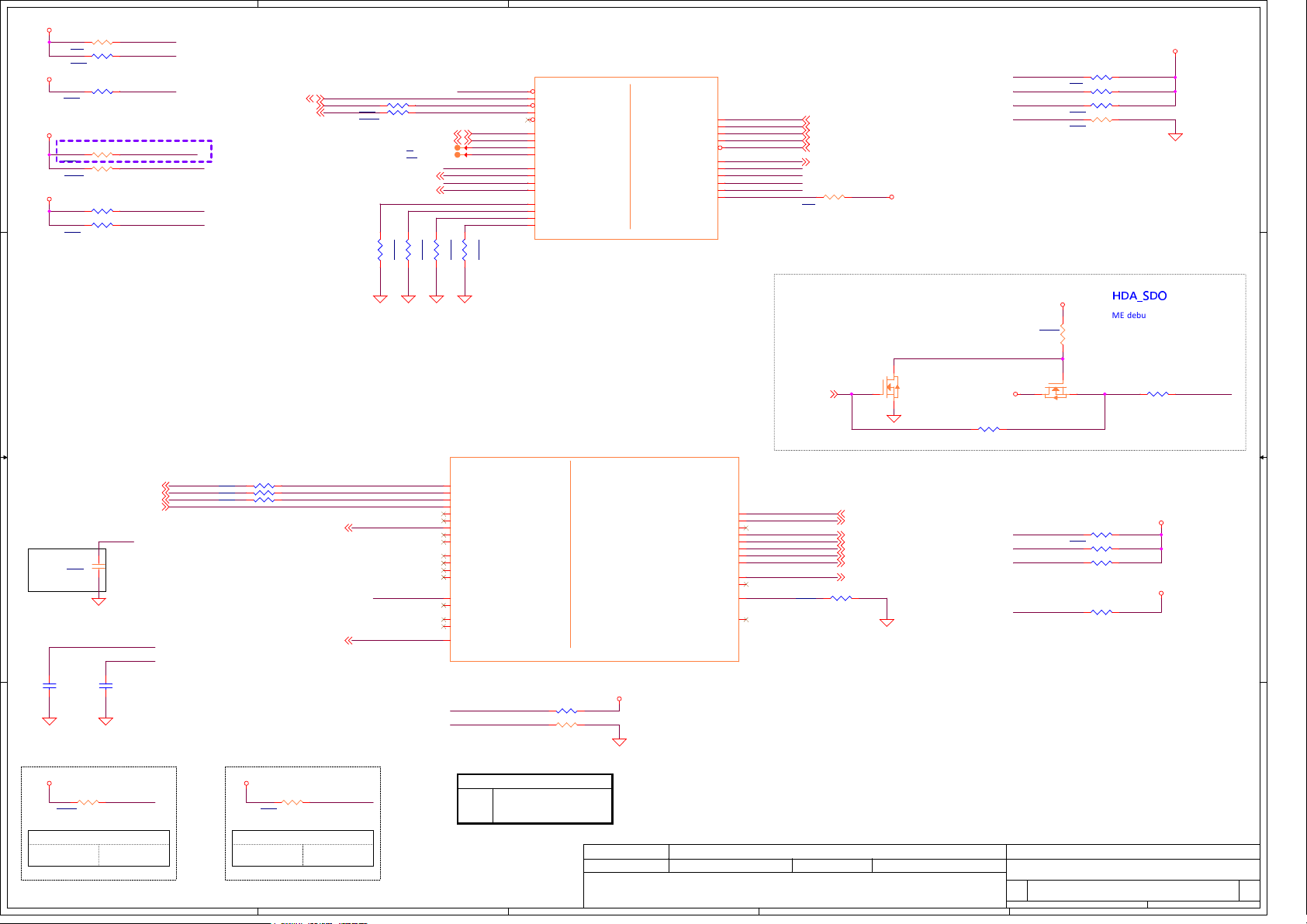

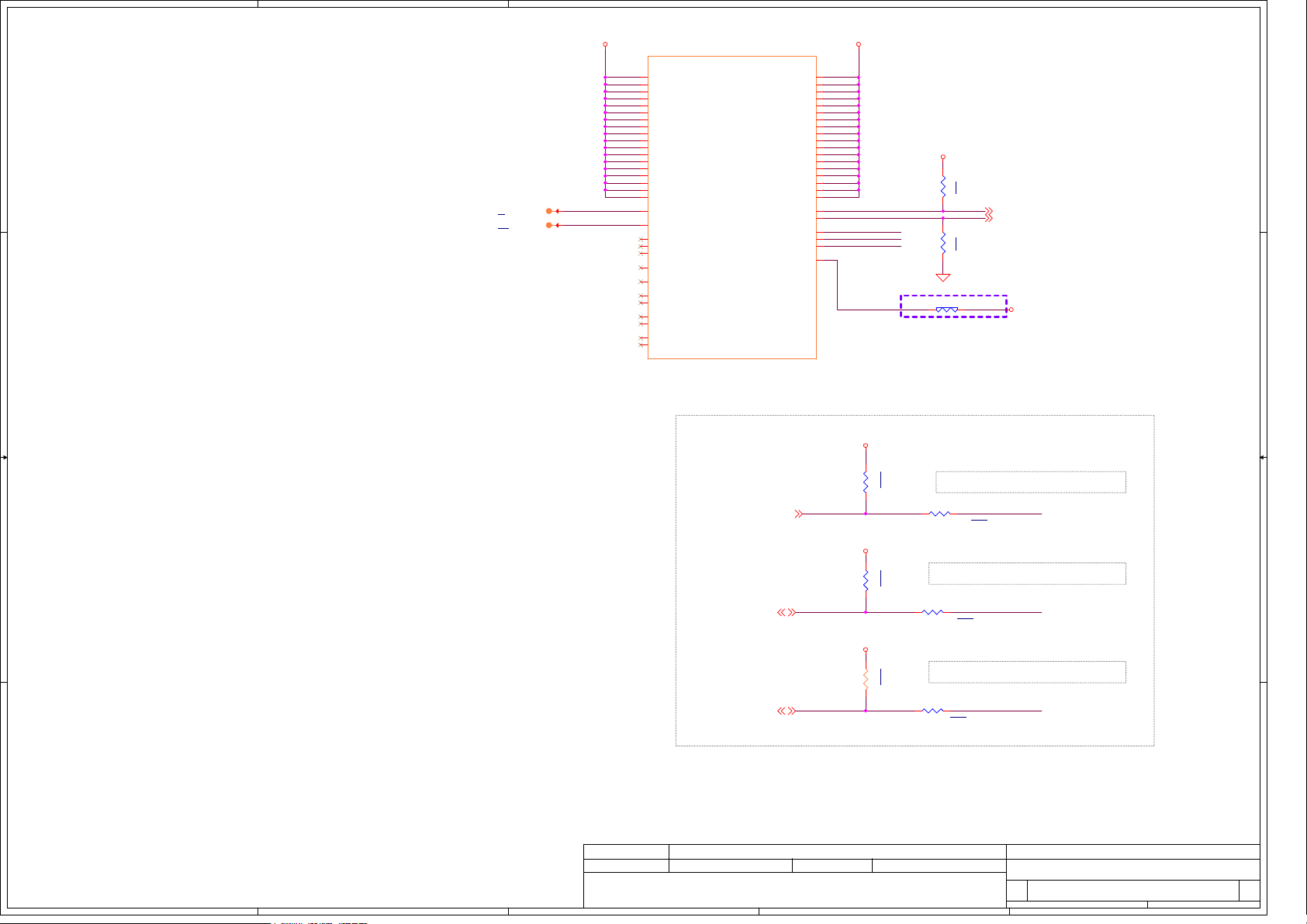

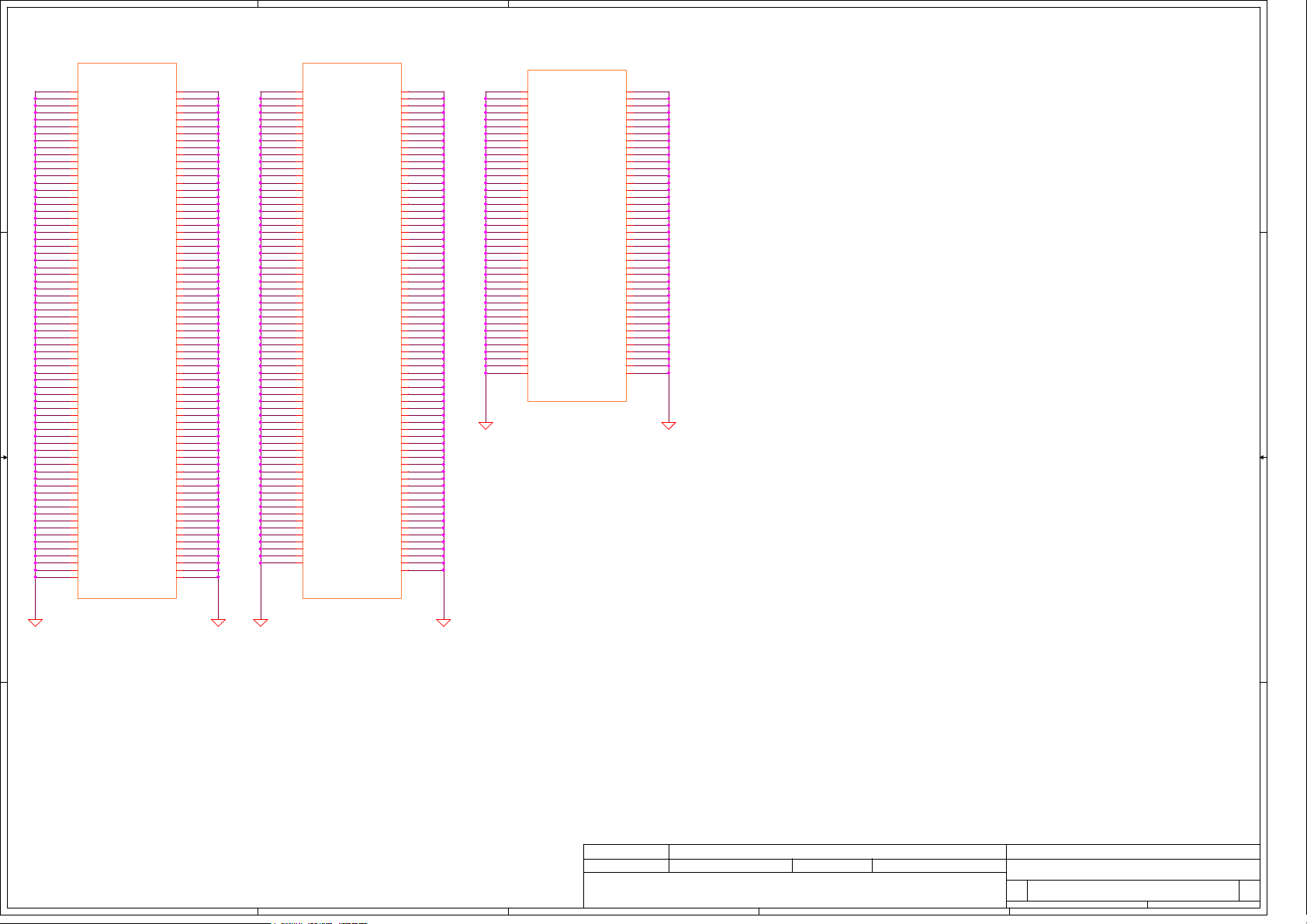

Rear Camera + 4th DMIC

BTB FPC 34 pin

1 1

Front Camera + ALS sensor+ LED

BTB FPC 30 pin

JUFC 1

p.33

PWR_BUTTON Board

JWFC1

p.33

LS-F371P

IOB

M/B

2 2

LA-F371P

JIOB2 eDP+iTou ch

p.43

JIOB1

p.43

BTB FPC 30pin

p.47

BATT_CON N

LS-F371P

IOB Cable

BTB FPC 40pin

3 3

p.22

Dock Board LS-F372P

(K/B + Bluetooth + Wireless Charge)

eDP+itouch Y-Cable

Coaxial cable 50P

iTouch

14pin

LCD Panel

Base Board

LS-D893P

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2015/10/22 2013/10/28

2015/10/22 2013/10/28

2015/10/22 2013/10/28

40pin

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

P03-DaughterB block diagram

P03-DaughterB block diagram

P03-DaughterB block diagram

Document Number Re v

Document Number Re v

Document Number Re v

LA-F371P

LA-F371P

LA-F371P

LA-F371P

LA-F371P

LA-F371P

LA-F371PLA-F371P

LA-F371PLA-F371P

LA-F371PLA-F371P

E

3 65Tuesday, November 07, 2017

3 65Tuesday, November 07, 2017

3 65Tuesday, November 07, 2017

1.0

1.0

1.0

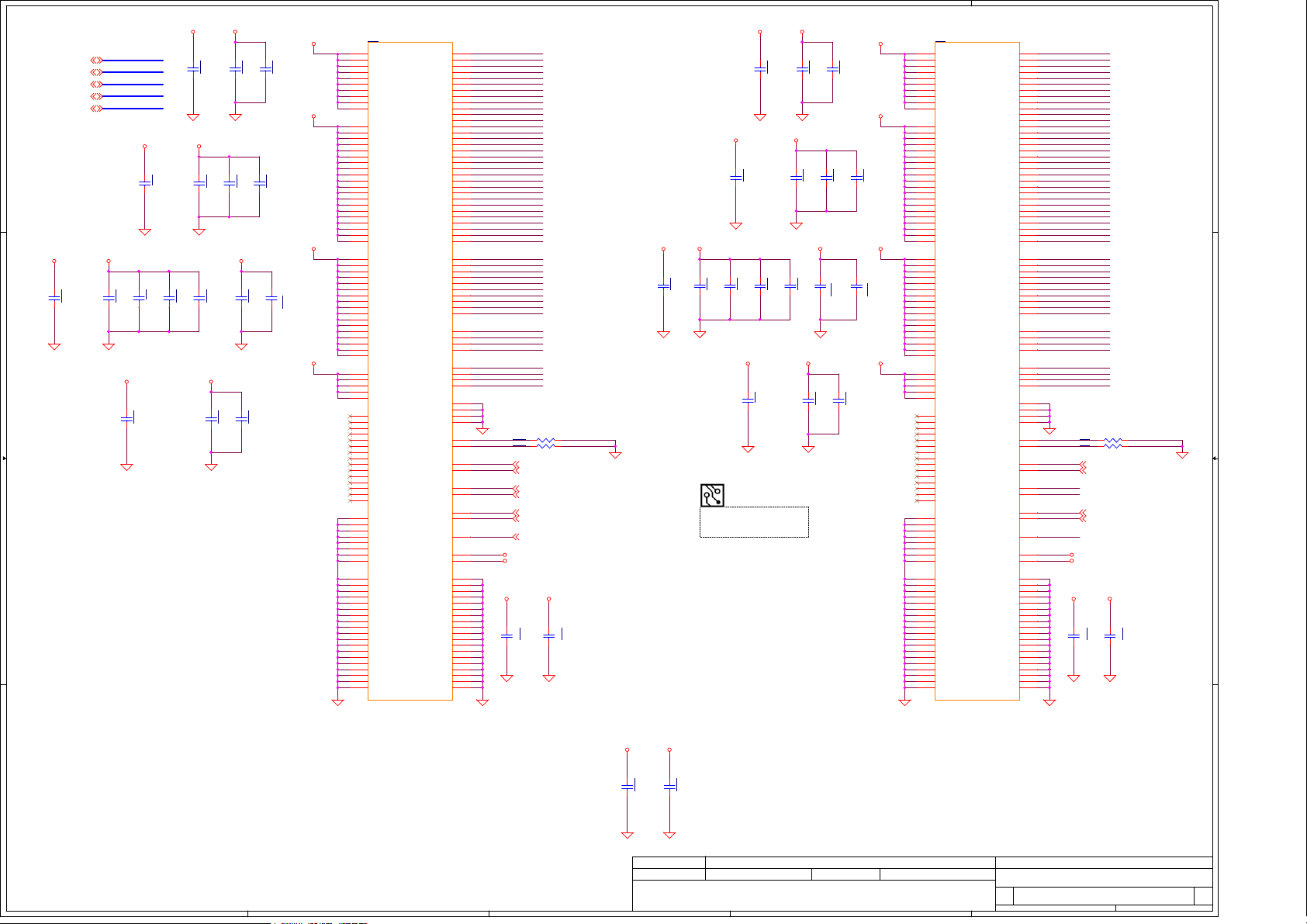

A

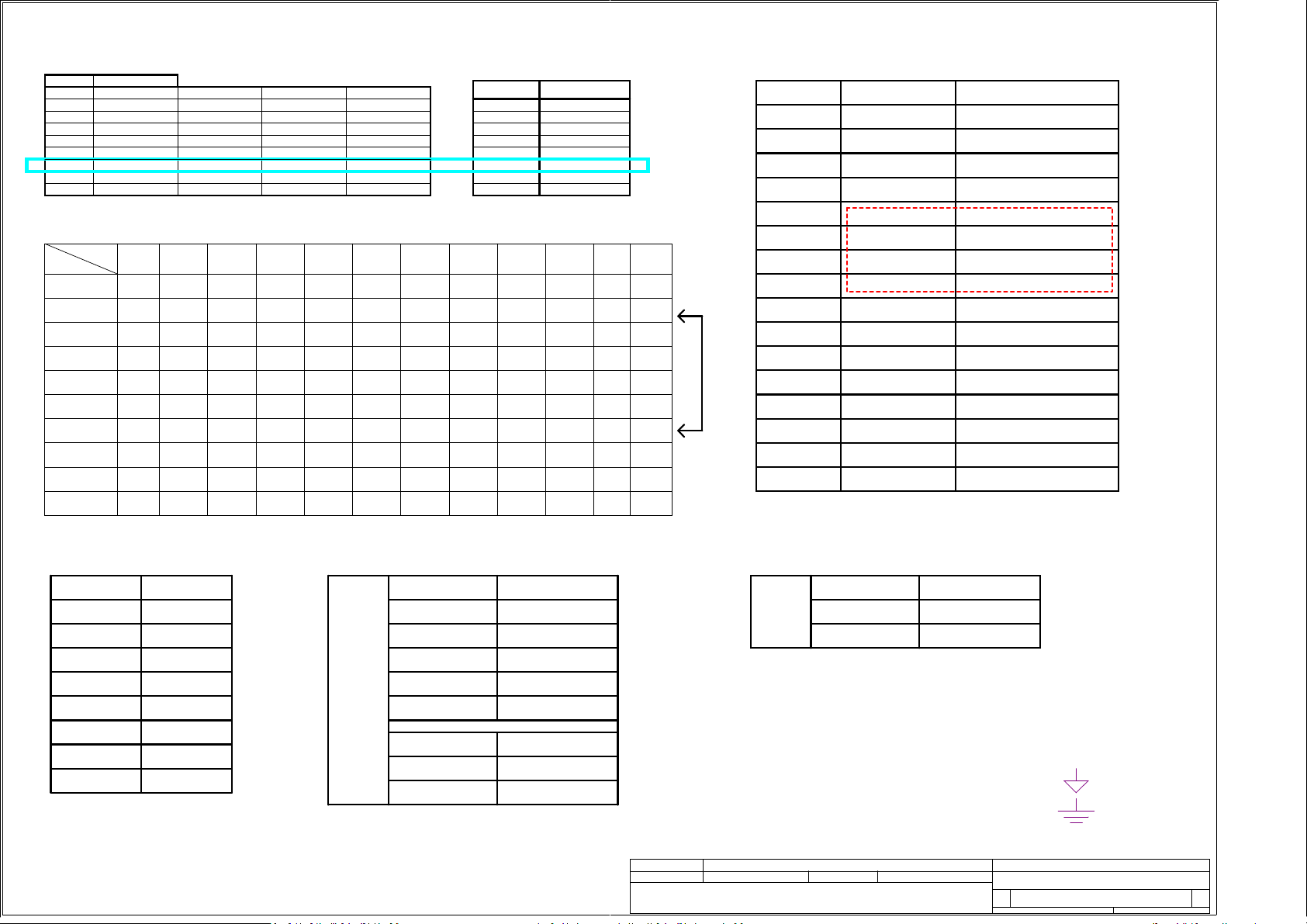

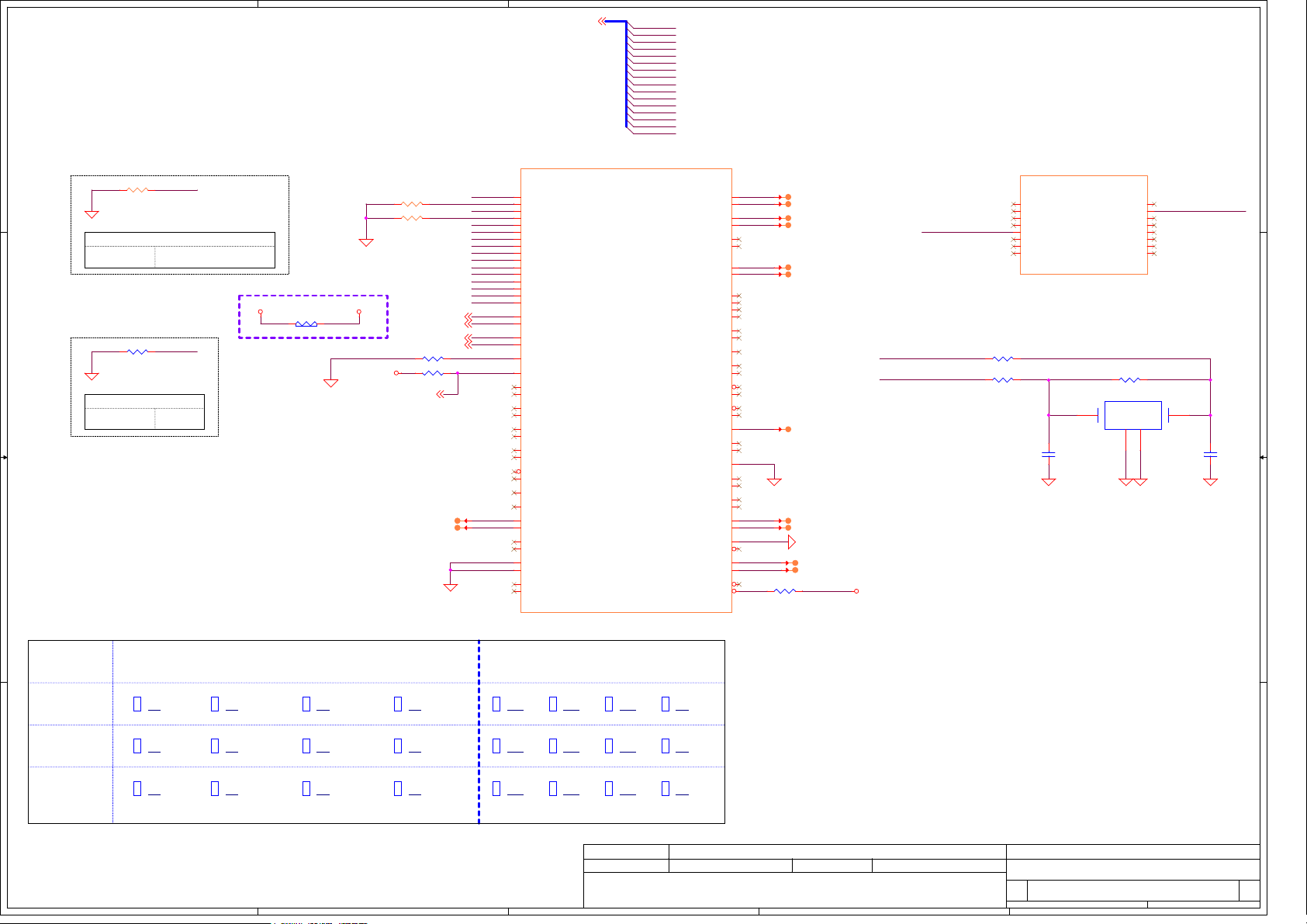

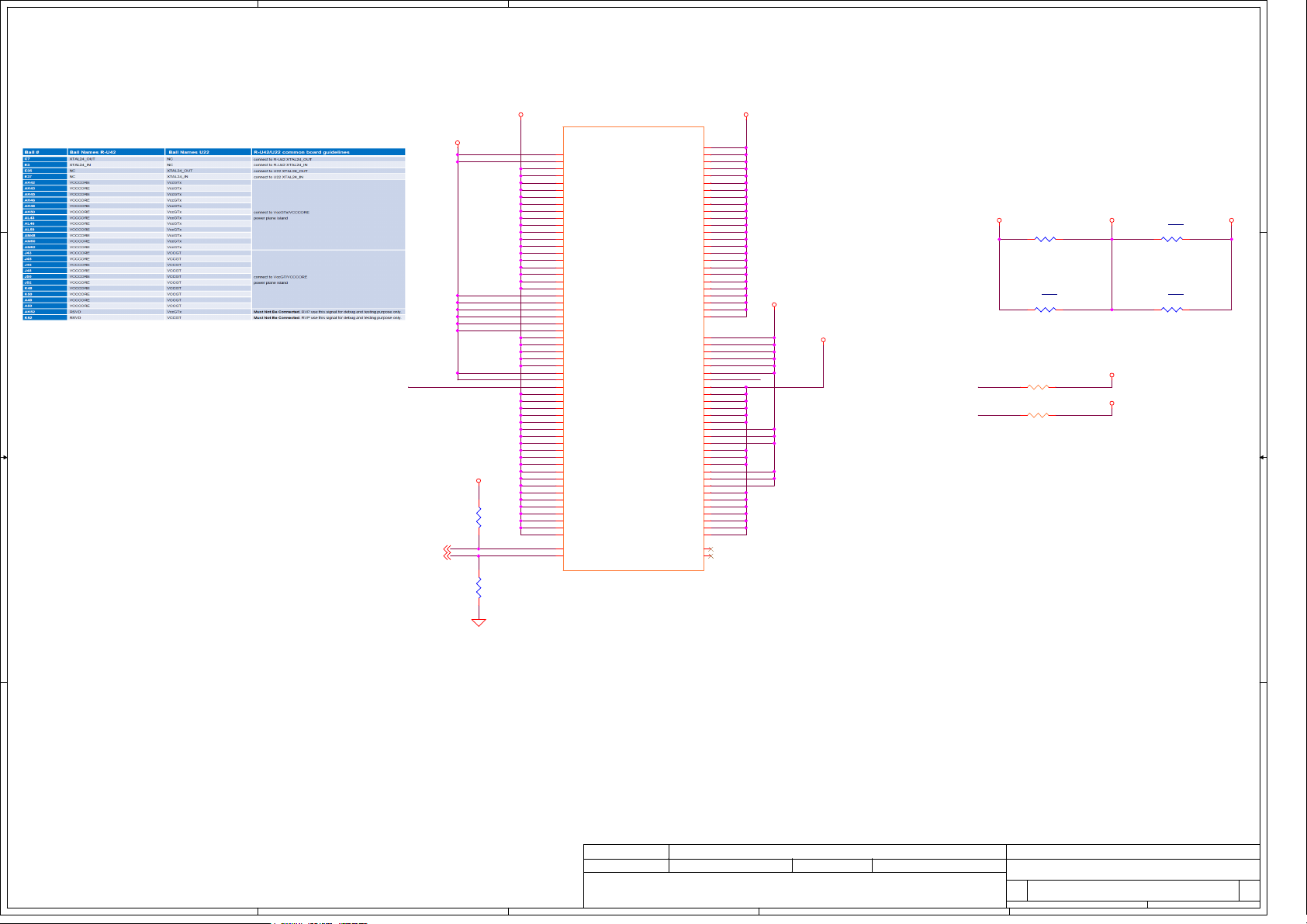

Board ID Table

3.3V +/- 5%Vcc

0

1

2

3

4

5

6

7

RBoard ID

240K +/- 5% 4700p

130K +/- 5%

62K +/- 5%

33K +/- 5%

8.2K +/- 5%

4.3K +/- 5%

2K +/- 5%

NC

4700p

4700p

4700p

4700p

4700p

4700p

C

REV

Pre-EVT1

EVT1

DVT1

DVT2

PVT

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

0.2

0.3

0.4

1.0

SMBUS Control Table

SOURCE

No use

1 1

PCH_SML0CLK

PCH_SML0DATA

PCH_SML1CLK

PCH_SML1DATA

SMBCLK

SMBDATA

EC_SMB00_CLK

EC_SMB00_DAT

EC_SMB01_CLK

EC_SMB01_DAT

EC_SMB02_CLK

EC_SMB02_DAT

EC_SMB03_CLK

EC_SMB03_DAT

EC_SMB04_CLK

EC_SMB04_DAT

EC_SMB05_CLK

EC_SMB05_DAT

EC_SMB10_CLK

EC_SMB10_DAT

PCH

PCH

PCH

MEC5105

MEC5105

MEC5105

MEC5105

MEC5105

MEC5105

MEC5105

Base

V

BATT

V

Charger

V

XDP

V

USH

V

PD

Control ler

Trinit y

Dock

P-Sensor

MUX

V V

V V

V

V

IMVP

IO

EXpendor

Link

V

V

USB 3.0Board ID Table

Flexible I/O

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Interface DESTINATION

USB 3.0 #1

USB 3.0 #2/SSIC

USB 3.0 #3

USB 3.0 #4

PCI-E#1 / USB 3.0#5

PCI-E#2 / USB 3.0#6

PCI-E #3

PCI-E #4

PCI-E #5

USB Type-C Port-A

NGFF (WWAN)

USB 3.0 Type-A

USB Type-C Port-B

Reserved for AR

Reserved for AR

Reserved for AR

Reserved for AR

NGFF (WLAN)

PCI-E #6

PCI-E #7

PCI-E #8 /SATA #1

PCI-E #9

NGFF (SSD)

NGFF (SSD) #7/#8 2lane PCI-E

Card Reader

PCI-E #10

PCI-E #11

NGFF (WWAN/2nd SSD)

PCI-E #12 NGFF (WWAN/2nd SSD)

Port Mapping USB 2.0

DESTINATIONUSB 2.0 PORT#

1

2

3

4

5

7

Type-C Port-A

Dock

Type-C Port-B NGFF (WWAN)

WWAN

IR CAM

WLAN

USB Type-A9

USH10

CLK

CLK

DESTINATIONDIFFERENTIAL

CLKOUT_PCIE0

CLKOUT_PCIE1

NGFF (WLAN)

CLKOUT_PCIE2

CLKOUT_PCIE3

SSD

CLKOUT_PCIE5 Card Reader

FLEX CLOCKS DESTINATION

CLKOUT_LPC_0

CLKOUT_LPC_1

ESPI

ESPI

Displayport

DDI PORT# DESTINATION

DDI

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

2015/10/22 2013/10/28

2015/10/22 2013/10/28

2015/10/22 2013/10/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

1

2

Deciphered Date

Deciphered Date

Deciphered Date

USB Type-C Port-B

USB Type-C Port-A

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

Symbol Note :

: means de-pop

@

: means Digital Ground

: means Analog Ground

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

P04-Notes List

P04-Notes List

P04-Notes List

Document Number Re v

Document Number Re v

Document Number Re v

LA-F371P

LA-F371P

LA-F371P

4 65Tuesday, November 07, 2017

4 65Tuesday, November 07, 2017

4 65Tuesday, November 07, 2017

1.0

1.0

1.0

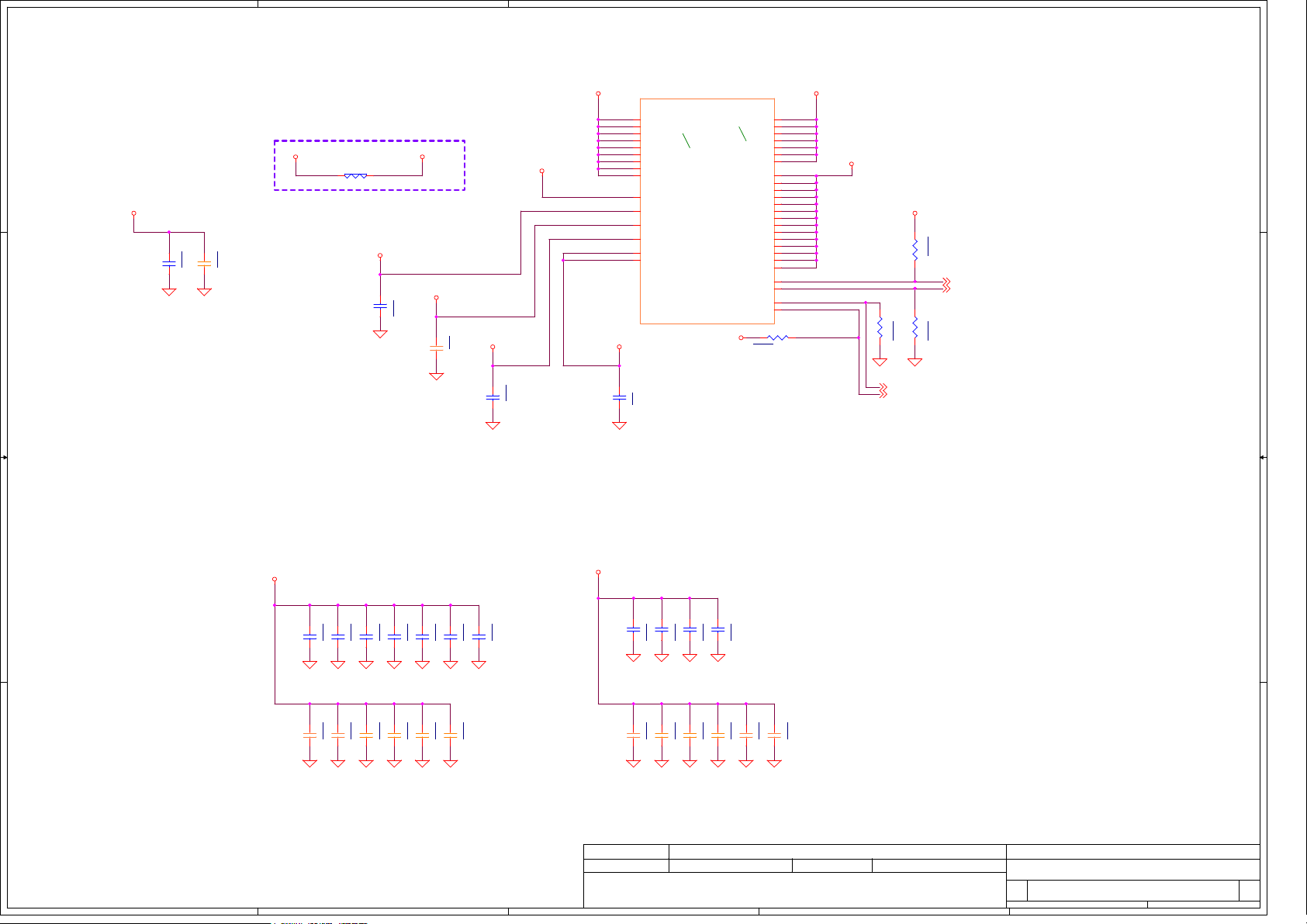

5

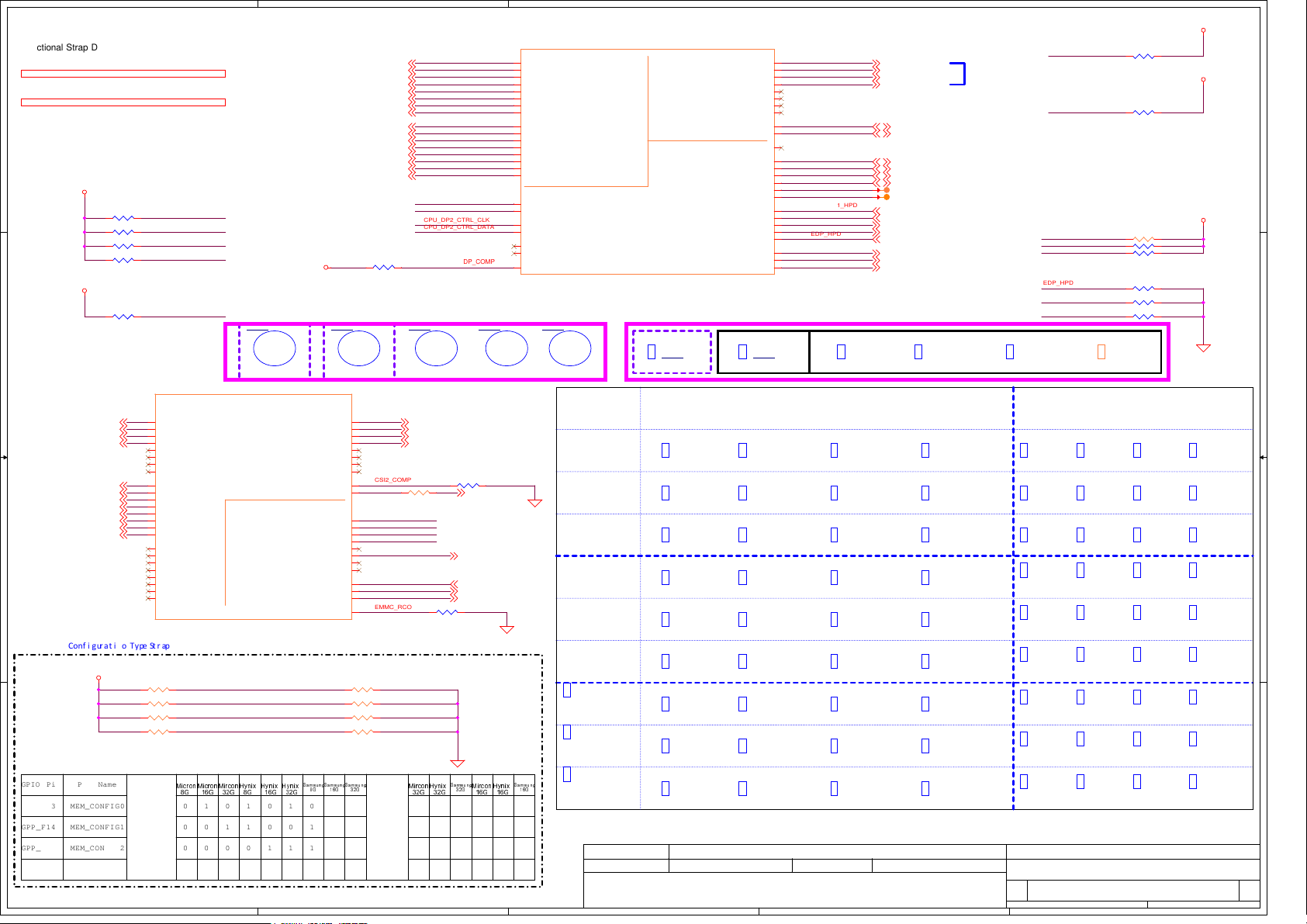

Functional Strap Definitions

GPP_E19 (Internal Pull Down): DDPB_CTRLDATA

0 = Port B is not detected.

1 = Port B is detected.

GPP_E21 (Internal Pull Down): DDPC_CTRLDATA

0 = Port C is not detected.

1 = Port C is detected.

D D

Type-C PortB

Type-C PortA

+3VS

CPU_DP2_CTRL_CLK

RC43 2.2K_0402_5%

RC45 2.2K_0402_5%

RC178 2.2K_0402_5%

RC179 2.2K_0402_5%

+3V_PRIM

RC199

C C

UFCAM_CSI2_DN033

UFCAM_CSI2_DP033

UFCAM_CSI2_DN133

UFCAM_CSI2_DP133

WFCAM_CSI2_DN433

WFCAM_CSI2_DP433

WFCAM_CSI2_DN533

WFCAM_CSI2_DP533

WFCAM_CSI2_DN633

WFCAM_CSI2_DP633

WFCAM_CSI2_DN733

WFCAM_CSI2_DP733

B B

DDR Memory Conf i gura t i no Type Str ap pin

+1.8VA

GPIO Pin

A A

GPP_ F1 3

GPP_ F1 4

GPP_ F1 5

GPP_ F1 6 MEM_C ONF IG 3

Pin Name

MEM_C ON FI G0

MEM_C ON FI G1

MEM_C ON FI G2

12

CPU_DP2_CTRL_DATA

12

CPU_DP1_CTRL_CLK

12

CPU_DP1_CTRL_DATA

12

1 2

@

@

@

MEDIACARD_IRQ#

10K_0402_5%

UCPU1I

@

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL-U_BGA1356

RH17

RH15 10K_0402_5%

RH12 10K_0402_5%

RH9 10K_0 402_5%

12

12

12

12

Micron

8G

10K_0402_5%@

0

1866 Mb ps

000

0 0 0 0 0 0 0

5

SKL_U LT

Micron

Mircon

16G

32G

0 1

1

0 1

0

+1.0VS_VCCIO

PVT-010

Add R3 CPN CPU

UCPU1

SR3L9@

R3 R3

SA0000AWS2L

i5 vpro R

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

MEM_CONFIG0

MEM_CONFIG1

MEM_CONFIG2

MEM_CONFIG3

Hynix

Hynix

Hynix

32G

16G

8G

01

0

1

0

0 11

CAD Note:Trace width=20 mils, Isolat i on Spaci ng=25 mil,

Max length=100 mils.

PVT-010

Add R3 CPN CPU

UCPU1

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

EMMC_RCOMP

9 OF 20

RH18

RH16 10K_0402_5%

@

RH13 10K_0402_5%

@

RH10 10K_0402_5%

@

Samsun g

Samsun g

16G

8G

1

0

1

1

1

1

0

4

DDI1_P2_TXN037

DDI1_P2_TXP037

DDI1_P2_TXN137

DDI1_P2_TXP137

DDI1_P2_TXN237

DDI1_P2_TXP237

DDI1_P2_TXN337

DDI1_P2_TXP337

PCH_DDI2_N03 7

PCH_DDI2_P037

PCH_DDI2_N13 7

PCH_DDI2_P137

PCH_DDI2_N23 7

PCH_DDI2_P237

PCH_DDI2_N33 7

PCH_DDI2_P337

CPU_DP1_CTRL_CLK

CPU_DP1_CTRL_DATA

CPU_DP2_CTRL_CLK

CPU_DP2_CTRL_DATA

1 2

RC108 24.9_0402_1%

COMPENSATION PU FOR eDP

4+2 CPU Option

UCPU1

SR3LB@

SA0000AWB3L

i5 Nvpro R

C37

D37

C32

D32

C29

D29

B26

A26

E13

@

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

Samsun g

32G

0

0

2133 Mb ps

0

1

CSI2_COMP

RC197

MEM_CONFIG0

MEM_CONFIG1

MEM_CONFIG2

MEM_CONFIG3

GNSS_OFF#

USH_DET#

GNSS_IRQ

WWAN_PWR_OFF#

EMMC_RCOMP

12

10K_0402_5%@

12

12

12

4

QNEG@

SA0000AWB1L

i5 Nvpro R

UFCAM_CSI2_CLKN0 33

UFCAM_CSI2_CLKP0 33

WFCAM_CSI2_CLKN1 33

WFCAM_CSI2_CLKP133

RC114

1 2

1 2

0_0402_5%

1 2

RC66 200_0402_1%

Samsun g

Mircon

Hynix

32G

32G

32G

1

0

0

111

0

0

1

1 1

E55

F55

E58

F58

F53

G53

F56

G56

C50

D50

C52

D52

A50

B50

D51

C51

L13

L12

N7

N8

N11

EDP_COMP

GNSS_OFF# 25

USH_DET# 41,43

GNSS_IRQ 25

WWAN_PWR_OFF# 25

N12

E52

UCPU1

QNBE@

SA0000AWR0L

i7 vpro R

100_0402_1%

MEDIACARD_IRQ# 27

Mircon

Hynix

16G

16G

1 0

0

0 0

0

1 1

1 1 1

3

UCPU1A

@

DDI1_TXN[0]

DDI1_TXP[0]

DDI1_TXN[1]

DDI1_TXP[1]

DDI1_TXN[2]

DDI1_TXP[2]

DDI1_TXN[3]

DDI1_TXP[3]

DDI2_TXN[0]

DDI2_TXP[0]

DDI2_TXN[1]

DDI2_TXP[1]

DDI2_TXN[2]

DDI2_TXP[2]

DDI2_TXN[3]

DDI2_TXP[3]

GPP_E18/DDPB_CTRLCLK

GPP_E19/DDPB_CTRLDATA

GPP_E20/DDPC_CTRLCLK

GPP_E21/DDPC_CTRLDATA

GPP_E22/DDPD_CTRLCLK

GPP_E23/DDPD_CTRLDATA

EDP_RCOMP

SKL-U_BGA1356

SKL-U

DDI

DISPLAY SIDEBANDS

EDP

1 OF 20

SKL-U Ballout Rev0.71 & INTEL symbol Rev1.0

PVT-010

Add R3 CPN CPU

R3

SR3JY@

UCPU1

i3 NVPro

SA0000B2Y1L

DRAM Option (R1) , R3 check P08

Micron 8G/1866

MICRON_8G@

UD1

MT52L256M32D1PF-107WT

SA00009XU0L

Micron 16G/1866

MICRON_16G@

UD1

MT52L512M32D2PF-107WT

SA00009U70L

Micron 32G/1866

MICRON_32G@

UD1

MT52L1G32D4PG-107WT

SA00009XV0L

Hynix 8G/1866

HYNIX_8G@

UD1

H9CCNNN8GTMLAR-NUD FBGA

SA00008G64L

Hynix 16G/1866

HYNIX_16G@

UD1

H9CCNNNBJTMLAR-NU D FBGA

SA00008FJ4L

Hynix 32G/1866

HYNIX_32G@

UD1

H9CCNNNCLTMLAR-NU D FBGA

SA0000AEN0L

Samsung 8G/1866

SAMSUNG_8G@

UD1

K4E8E324EB-EGCF FBGA178P

SA00009XY0L

Samsung 16G/1866

SAMSUNG_16G@

UD1

K4E6E304EB-EGCF FBGA17

SA00008QV2L

Samsung 32G/1866

SAMSUNG_32G@

UD1

4EBE304EB-EGCF FBGA178

SA00008X10L

Issued Date

Issued Date

Issued Date

3

Samsun g

16G

1

1

UCPU1

QNEE@

SA0000AWS0L

i5 vpro R

X76

X7669231L05

X7669231L07

X7669231L09

X7669231L06

X7669231L08

X7669231L10

X76_8G@

X768G

X76

X7669231L01

X7669231L01

X76_16G@

X7616G

X76

X7669231L02

X7669231L02

X76_32G@

X7632G

X76

X7669231L03

X7669231L03

Security Cl assification

Security Cl assification

Security Cl assification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

C47

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

CPU_DP1_HPD

CPU_DP2_HPD

I2C0_IRQ_TS

WLAN_RST#

EDP_HPD

eDP_TXN_P0 22

eDP_TXP_P0 22

eDP_TXN_P1 22

eDP_TXP_P1 22

eDP_AUXN 22

eDP_AUXP 22

PCH_DDI1_AUXN 36,37

PCH_DDI1_AUXP 36,37

PCH_DDI2_AUXN 35,37

PCH_DDI2_AUXP 35,37

@

PAD~D

@

PAD~D

CPU_DP1_HPD 30,36,37

CPU_DP2_HPD 30,35,37

I2C0_IRQ_TS 22

WLAN_RST# 24

EDP_HPD 22

PANEL_BKLEN 22

EDP_BIA_PWM 22

PCH_ENVDD 22

2+2 CPU Option

QNB1@

UCPU1

i3 NVPro

SA0000B2Y0L

MICRON_8G@

UD2

MT52L256M32D1PF-107W T

SA00009XU0L

MICRON_16G@

UD2

MT52L512M32D2PF-107W T

SA00009U70L

MICRON_32G@

UD2

MT52L1G32D4PG-107WT

SA00009XV0L

HYNIX_8G@

UD2

H9CCNNN8GTMLAR-NUD FBGA

SA00008G64L

HYNIX_16G@

UD2

H9CCNNNBJTMLAR-NU D FBGA

SA00008FJ4L

HYNIX_32G@

UD2

H9CCNNNCLTMLAR-NU D FBGA

SA0000AEN0L

SAMSUNG_8G@

UD2

K4E8E324EB-EGCF FBGA178P

SA00009XY0L

SAMSUNG_16G@

UD2

K4E6E304EB-EGCF FBGA17

SA00008QV2L

SAMSUNG_32G@

UD2

4EBE304EB-EGCF FBGA178

SA00008X10L

Compal Secret Data

Compal Secret Data

2015/10/22 2013/10/28

2015/10/22 2013/10/28

2015/10/22 2013/10/28

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SR343@

UCPU1

i3 NVPro

SA0000A387L

MICRON_8G@

UD3

MT52L256M32D1PF-107WT

SA00009XU0L

MICRON_16G@

UD3

MT52L512M32D2PF-107WT

SA00009U70L

MICRON_32G@

UD3

MT52L1G32D4PG-107WT

SA00009XV0L

HYNIX_8G@

UD3

H9CCNNN8GTMLAR-NUD FBGA

SA00008G64L

HYNIX_16G@

UD3

H9CCNNNBJTMLAR-NU D FBGA

SA00008FJ4L

HYNIX_32G@

UD3

H9CCNNNCLTMLAR-NU D FBGA

SA0000AEN0L

SAMSUNG_8G@

UD3

K4E8E324EB-EGCF FBGA178P

SA00009XY0L

SAMSUNG_16G@

UD3

K4E6E304EB-EGCF FBGA17

SA00008QV2L

SAMSUNG_32G@

UD3

4EBE304EB-EGCF FBGA178

SA00008X10L

2

2Lane eDP

T6

T5

SR342@

UCPU1

i5 NVPro

SA0000A377L

MICRON_8G@

UD4

MT52L256M32D1PF-107WT

SA00009XU0L

MICRON_16G@

UD4

MT52L512M32D2PF-107WT

SA00009U70L

MICRON_32G@

UD4

MT52L1G32D4PG-107WT

SA00009XV0L

HYNIX_8G@

UD4

H9CCNNN8GTMLAR-NUD FBGA

SA00008G64L

HYNIX_16G@

UD4

H9CCNNNBJTMLAR-NU D FBGA

SA00008FJ4L

HYNIX_32G@

UD4

H9CCNNNCLTMLAR-NU D FBGA

SA0000AEN0L

SAMSUNG_8G@

UD4

K4E8E324EB-EGCF FBGA178P

SA00009XY0L

SAMSUNG_16G@

UD4

K4E6E304EB-EGCF FBGA17

SA00008QV2L

SAMSUNG_32G@

UD4

4EBE304EB-EGCF FBGA178

SA00008X10L

1

+3VS

I2C0_IRQ_TS

WLAN_RST#

GNSS_IRQ

USH_DET#

GNSS_OFF#

EDP_HPD

CPU_DP1_HPD

CPU_DP2_HPD

SR340@

UCPU1

i5 Vpro

SA0000ADO2L

DRAM Config Option

(Resistor pop location)

MEM_CONFIG0

X76_M8G@

RH18

10K_0402_5%

SD028100280

X76_M16G@

RH17

10K_0402_5%

SD028100280

X76_M32G@

RH18

10K_0402_5%

SD028100280

X76_H8G@

RH17

10K_0402_5%

SD028100280

X76_H16G@

RH18

10K_0402_5%

SD028100280

X76_H32G@

RH17

10K_0402_5%

SD028100280

X76_S8G@

RH18

10K_0402_5%

SD028100280

X76_S16G@

RH17

10K_0402_5%

SD028100280

X76_S32G@

RH18

10K_0402_5%

SD028100280

RC194 100K_0201_5%

RH505

RH8 10K_0201_5%

@

RH7 100K_0201_5%

RH5

RC126 100K_0402_5%

RC124 100K_0402_5%

RC46 100K_0402_5%

@SR33Z@

UCPU1

i7 VPro

SA0000ADP2L

MEM_CONFIG1 MEM_CONFIG2 MEM_CONFIG3

X76_M8G@

RH16

10K_0402_5%

SD028100280

X76_M16G@

RH16

10K_0402_5%

SD028100280

X76_M32G@

RH15

10K_0402_5%

SD028100280

X76_H8G@

RH15

10K_0402_5%

SD028100280

X76_H16G@

RH16

10K_0402_5%

SD028100280

X76_H32G@

RH16

10K_0402_5%

SD028100280

X76_S8G@

RH15

10K_0402_5%

SD028100280

X76_S16G@

RH15

10K_0402_5%

SD028100280

X76_S32G@

RH16

10K_0402_5%

SD028100280

1 2

1 2

1 2

1 2

X76_M8G@

RH13

10K_0402_5%

SD028100280

X76_M16G@

RH13

10K_0402_5%

SD028100280

X76_M32G@

RH13

10K_0402_5%

SD028100280

X76_H8G@

RH13

10K_0402_5%

SD028100280

X76_H16G@

RH12

10K_0402_5%

SD028100280

X76_H32G@

RH12

10K_0402_5%

SD028100280

X76_S8G@

RH12

10K_0402_5%

SD028100280

X76_S16G@

RH12

10K_0402_5%

SD028100280

X76_S32G@

RH13

10K_0402_5%

SD028100280

12

10K_0201_5%

10K_0201_5%

12

12

12

+1.8VA

+3VS

X76_M8G@

RH10

10K_0402_5%

SD028100280

X76_M16G@

RH10

10K_0402_5%

SD028100280

X76_M32G@

RH10

10K_0402_5%

SD028100280

X76_H8G@

RH10

10K_0402_5%

SD028100280

X76_H16G@

RH10

10K_0402_5%

SD028100280

X76_H32G@

RH10

10K_0402_5%

SD028100280

X76_S8G@

RH10

10K_0402_5%

SD028100280

X76_S16G@

RH10

10K_0402_5%

SD028100280

X76_S32G@

RH9

10K_0402_5%

SD028100280

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P05-MCP(1/14)DDI,EDP,CSI2,EMMC

P05-MCP(1/14)DDI,EDP,CSI2,EMMC

P05-MCP(1/14)DDI,EDP,CSI2,EMMC

LA-F371P

LA-F371P

LA-F371P

1

5 65Tuesday, November 07, 2017

5 65Tuesday, November 07, 2017

5 65Tuesday, November 07, 2017

1.0

1.0

1.0

5

4

3

2

1

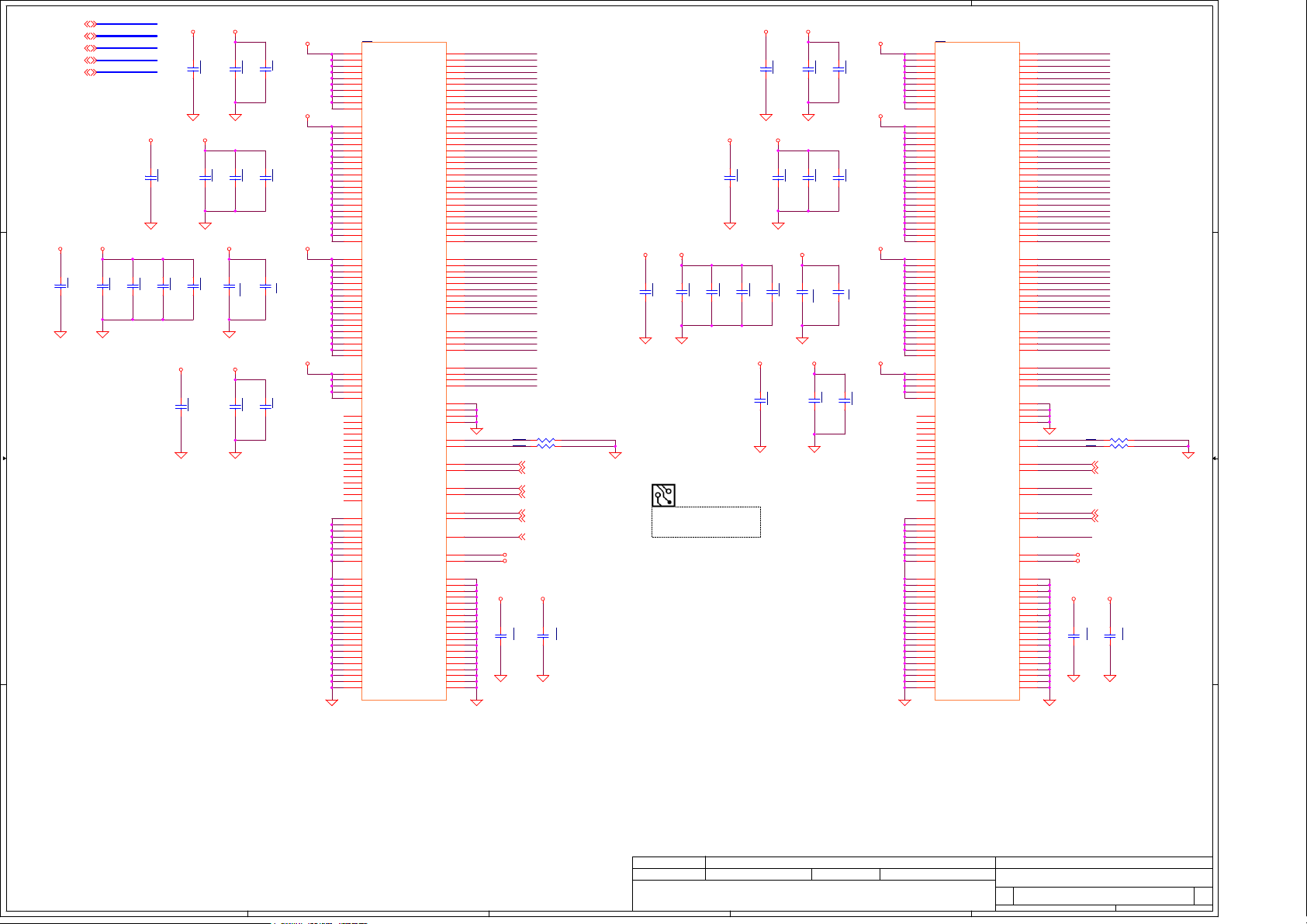

LPDDR3, Ballout for side by side(Non-Interleave)

DDR_A_DQS#[0..7]19

DDR_A_DQS[0..7]19

DDR_A_D[0..63]19

DDR_A_CA1_[0..9]19,21

DDR_A_CA2_[0..9]19,21

D D

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

C C

B B

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

UCPU1B

@

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

DDR_B_DQS#[0..7]20

DDR_B_DQS[0..7]20

DDR_B_D[0..63]20

DDR_B_CA1_[0..9]20,21

DDR_B_CA2_[0..9]20,21

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

DDR0_ODT[1]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

2 OF 20

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CKE2

DDR_A_CKE3

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_VTT_CNTL

DDR_A_CLK#0 19,21

DDR_A_CLK0 19,21

DDR_A_CLK#1 19,21

DDR_A_CLK1 19,21

DDR_A_CKE0 19,21

DDR_A_CKE1 19,21

DDR_A_CKE2 19,21

DDR_A_CKE3 19,21

DDR_A_CS#0 19,21

DDR_A_CS#1 19,21

DDR_A_ODT0 19,21

DDR_A_CA1_0 19,21

DDR_A_CA1_1 19,21

DDR_A_CA1_2 19,21

DDR_A_CA1_3 19,21

DDR_A_CA1_4 19,21

DDR_A_CA1_5 19,21

DDR_A_CA1_6 19,21

DDR_A_CA1_7 19,21

DDR_A_CA1_8 19,21

DDR_A_CA1_9 19,21

DDR_A_CA2_0 19,21

DDR_A_CA2_1 19,21

DDR_A_CA2_2 19,21

DDR_A_CA2_3 19,21

DDR_A_CA2_4 19,21

DDR_A_CA2_5 19,21

DDR_A_CA2_6 19,21

DDR_A_CA2_7 19,21

DDR_A_CA2_8 19,21

DDR_A_CA2_9 19,21

DDR_A_DQS#0 19

DDR_A_DQS0 19

DDR_A_DQS#1 19

DDR_A_DQS1 19

DDR_A_DQS#4 19

DDR_A_DQS4 19

DDR_A_DQS#5 19

DDR_A_DQS5 19

DDR_B_DQS#0 20

DDR_B_DQS0 20

DDR_B_DQS#1 20

DDR_B_DQS1 20

DDR_B_DQS#4 20

DDR_B_DQS4 20

DDR_B_DQS#5 20

DDR_B_DQS5 20

+V_DDR_REF_CA 21

+V_DDR_REFA_R 21

+V_DDR_REFB_R 21

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UCPU1C

@

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

3 OF 20

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK0

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CKE2

DDR_B_CKE3

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK#0 20,21

DDR_B_CLK#1 20,21

DDR_B_CLK0 20,21

DDR_B_CLK1 20,21

DDR_B_CKE0 20,21

DDR_B_CKE1 20,21

DDR_B_CKE2 20,21

DDR_B_CKE3 20,21

DDR_B_CS#0 20,21

DDR_B_CS#1 20,21

DDR_B_ODT0 20,21

DDR_B_CA1_0 20,21

DDR_B_CA1_1 20,21

DDR_B_CA1_2 20,21

DDR_B_CA1_3 20,21

DDR_B_CA1_4 20,21

DDR_B_CA1_5 20,21

DDR_B_CA1_6 20,21

DDR_B_CA1_7 20,21

DDR_B_CA1_8 20,21

DDR_B_CA1_9 20,21

DDR_B_CA2_0 20,21

DDR_B_CA2_1 20,21

DDR_B_CA2_2 20,21

DDR_B_CA2_3 20,21

DDR_B_CA2_4 20,21

DDR_B_CA2_5 20,21

DDR_B_CA2_6 20,21

DDR_B_CA2_7 20,21

DDR_B_CA2_8 20,21

DDR_B_CA2_9 20,21

DDR_A_DQS#2 19

DDR_A_DQS2 19

DDR_A_DQS#3 19

DDR_A_DQS3 19

DDR_A_DQS#6 19

DDR_A_DQS6 19

DDR_A_DQS#7 19

DDR_A_DQS7 19

DDR_B_DQS#2 20

DDR_B_DQS2 20

DDR_B_DQS#3 20

DDR_B_DQS3 20

DDR_B_DQS#6 20

DDR_B_DQS6 20

DDR_B_DQS#7 20

DDR_B_DQS7 20

@

T36

PAD~D

+1.2V_DDR

NC

A

GND

VCC

UC1

5

4

Y

1

CC15

0.1U_0402_10V7K

2

Security Cl assification

Security Cl assification

Security Cl assification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+3VS

12

R32

100K_0402_5%

SM_PG_CTRL 53

Compal Secret Data

Compal Secret Data

2015/10/22 2013/10/28

2015/10/22 2013/10/28

2015/10/22 2013/10/28

3

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

LPDDR3 COMPENSATION SIGNALS

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CAD Note:

Trace width=12~15 mil, Spacing=20 mils

Max trace length= 500 mil

1 2

RC164 200_0402_1%

RC166 80.6_0402_1%

1 2

RC165 162_0402_1%

1 2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P06-MCP(2/14)LPDDR3

P06-MCP(2/14)LPDDR3

P06-MCP(2/14)LPDDR3

LA-F371P

LA-F371P

LA-F371P

1

6 65Tuesday, November 07, 2017

6 65Tuesday, November 07, 2017

6 65Tuesday, November 07, 2017

1.0

1.0

1.0

DDR_VTT_CNTL

1

2

3

74AUP1G07GW_TSSOP5

Use SA00005U600

A A

5

4

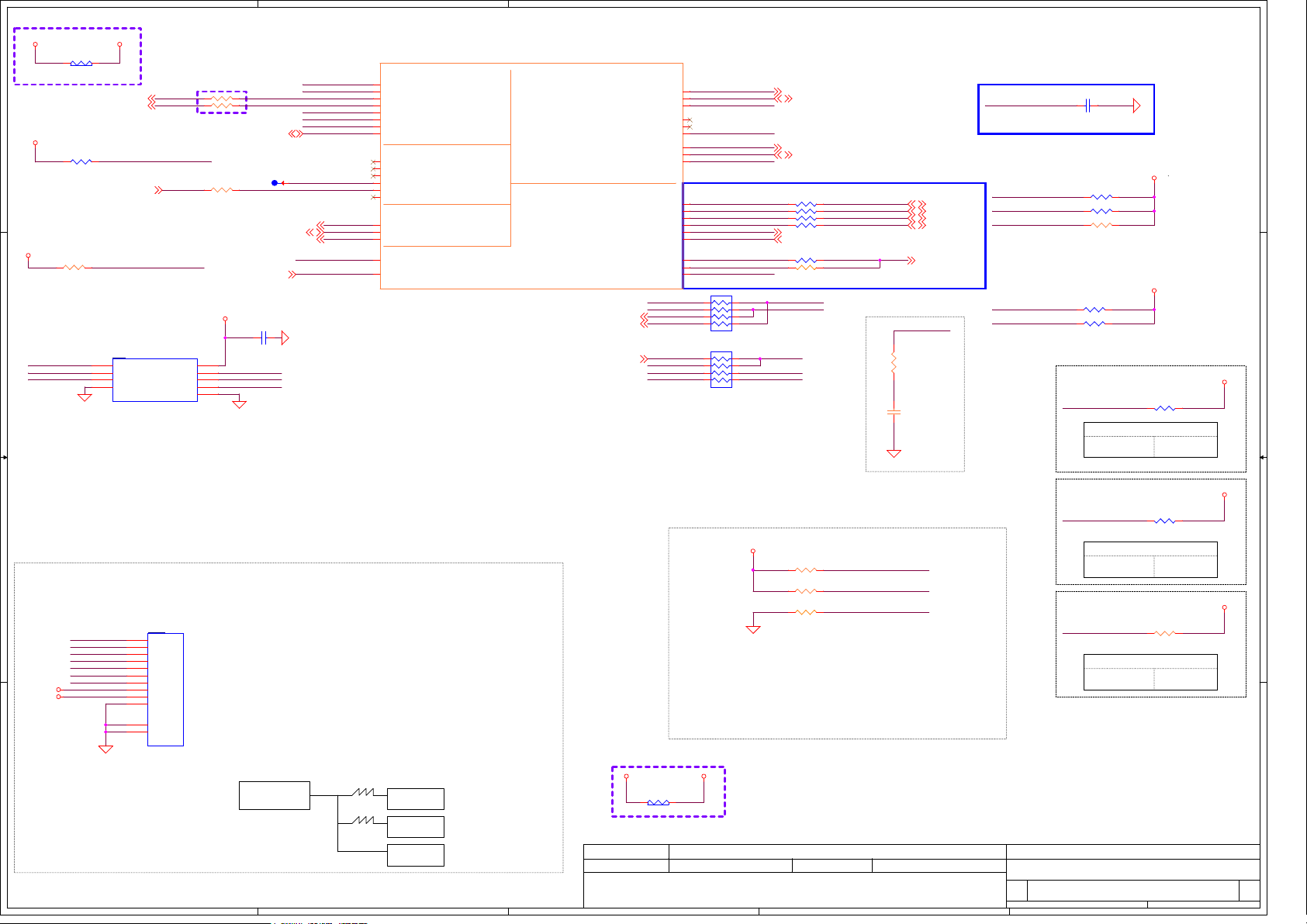

PCH_SPI_DO_XDP13

PCH_SPI_DO2_XDP13

+1.8V_ESPI

TPM_PIRQ#8,31

5

ESPI_ALERT#

SIO_RCIN#

PVT-048

De-pop debug XDP related compoments

RC67 1K_0402_5%@XDP@ 1 2

RC69 1K_0402_5%@XDP@

1 2

RC198

@

1 2

PCH_SPI_CS2#31

TC1

0_0201_5%

ESPI_ALERT#30

CL_CLK24

CL_DATA24

CL_RST#24

SPI_MOSI= SPI_IO0

SPI_MISO= SPI_IO1

PCH EDS R0.7 p.235~236

PCH_SPI_CLK

PCH_SPI_SO

PCH_SPI_SI

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_CS0#

PCH_SPI_CS1#

SIO_RCIN#

ESPI_ALERT#

PVT-023

Change 0 ohm to short pad

+1.8VA

R513

1 2

@

0_0201_5%

D D

+1.8V_ESPI

1 2

RC83 10K_0402_5%

+1.8V_PGPP

@

1 2

RC73 10K_0402_5%

+3.3V_SPI

CC90

C C

PCH_SPI_CS0#

SPI_SO_VROM1

SPI_IO2_VROM1

128Mb Flash ROM

UH1

1

CS#

2

HOLD#_RESET#

DO

3

WP#

4

GND

ThemalPad

W25Q128JVEIQ_WSON8_8X6

VCC

8

7

6

CLK

5

DI

9

1 2

0.1U_0402_25V6

SPI_IO3_VROM1

SPI_CLK_VROM1

SPI_SI_VROM1

AW3

AW2

AU4

AU3

AU2

AU1

AW13

AY11

AV2

AV3

M2

M3

J4

V1

V2

M1

G3

G2

G1

4

UCPU1E

@

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356

SKL-U

SMBUS, SMLINK

LPC

GPP_A14/SUS_STAT#/ESPI_RESET#

3

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

5 OF 20

SPI_SI_VROM1

PCH_SPI_CLK_TPM31

PCH_SPI_SI_TPM31

PCH_SPI_SO_TPM31

SPI_CLK_VROM1

SPI_SO_VROM1

SPI_IO2_VROM1

SPI_IO3_VROM1

DDR_XDP_SMBCLK

R7

DDR_XDP_SMBDAT

R8

PCH_SMB_ALERT#

R10

R9

W2

GPP_C5

W1

SML1_SMBCLK

W3

SML1_SMBDAT

V3

GPP_B23

AM7

AY13

BA13

BB13

AY12

BA12

BA11

PCI_CLK_LPC0

AW9

PCI_CLK_LPC1

AY9

AW11

CLKRUN#

RP2

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

RP3

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

RFQ-034

change LPC to ESPI mode

ESPI_IO0_R

ESPI_IO1_R

ESPI_IO2_R

ESPI_IO3_R

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

DDR_XDP_SMBCLK 13

DDR_XDP_SMBDAT 13

SML1_SMBCLK 30

SML1_SMBDAT 30

RC383 15_0402_5%1 2

RC384 15_0402_5%

1 2

RC385 15_0402_5%

1 2

RC386 15_0402_5%

1 2

ESPI_CS# 30,43

ESPI_RESET# 30

RC71 15_0402_5%

1 2

1 2

RC70 22_0402_5%@

PCH_SPI_SI

PCH_SPI_CLK

2

SPI_CLK_VROM1

33_0402_5%

RC169@

1 2

33P_0402_50V8J

CC91@

1 2

ESPI_IO0 30,43

ESPI_IO1 30,43

ESPI_IO2 30,43

ESPI_IO3 30,43

ESPI_CLK 30,43

ESPI_CLK

Reserve for RF

DDR_XDP_SMBDAT

DDR_XDP_SMBCLK

CLKRUN#

SML1_SMBCLK

SML1_SMBDAT

1

12

EMC@12P_0402_50V8J

CC78

12

RN12.2K_0402_5%

12

RN22.2K_0402_5%

12

@

RC828.2K_0402_5%

+3V_PRIM

1 2

RC55 1K_0402_5%

1 2

RC51 1K_0402_5%

change RC49 to 2.2k

PCH_SMB_ALERT#

RC49 2.2K_0402_5%

TLS C ONFIDENTIALITY

HIGH

LOW(DEFAULT)

+3VS

1 2

ENABLE

DISAB LE

+3V_PRIM

+3V_PRIM

GPP_C5

+3V_PRIM

RH19 1K_0402_ 5%~D

1 2

B B

SPI debug conn

PCH_SPI_CS1#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_IO2

+3.3V_SPI

+3V_PRIM

A A

PCH_SPI_IO3

JSPI2

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

GND1

12

GND2

ACES_50521-01041-P01

CONN@

PCH SPI

PVT-023

Change 0 ohm to short pad

RC170

@

9/5 MOW

Opt i on 1: I mpl e ment a 1 k Oh m pull - down r esi st or on t he si gnal and de- popul at e

the

required 1 kOhm pull-up resistor(MOW WW5).

In this case, customers must ensure that the SPI

f l ash devi ce on t he pl a t fo r m has HOLD f unct i onal i t y di sabl ed by default.

Note that the pull down resistor on SPI0_IO3 is only needed for SKL U/Y plat f or ms

with ES and SKL S/H plat f or ms wi t h pre-ES 1/ ES1 s a mpl es( MO W W W9).

+3.3V_SPI+3V_PRIM

12

@

RH20 1K_0402_ 5%~D

1 2

@

RH21 1K_0402_ 5%~D

1 2

@

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_IO3

EC interface

HIGH

LOW(DEFAULT)

GPP_B23

EXI BOOT STALL BYPASS

HIGH

LOW(DEFAULT)

1 2

RC58 4.7K_0201_5%

ESPI

LPC

+3V_PRIM

1 2

RC64 150K_0201_1%@

ENABLE

DISAB LE

0_0402_1%

TPM

Security Cl assification

Security Cl assification

JSPI

5

4

Security Cl assification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2015/10/22 2013/10/28

2015/10/22 2013/10/28

2015/10/22 2013/10/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P07-MCP(3/14)SPI,SMB,LPC

P07-MCP(3/14)SPI,SMB,LPC

P07-MCP(3/14)SPI,SMB,LPC

LA-F371P

LA-F371P

LA-F371P

1

7 65Tuesday, November 07, 2017

7 65Tuesday, November 07, 2017

7 65Tuesday, November 07, 2017

1.0

1.0

1.0

5

+3VS

HOST_SD_WP#

1 2

RC56

10K_0402_5%

UART2_TXD

1 2

D D

C C

RH3 49.9K_0201_1%

RH4 49.9K_0201_1%

RC190 49.9K_0402_1%

RC191 49.9K_0402_1%

+3V_PRIM

RC180

RC181

RC396

@

RC149

+3VS_TS

RC48 4.7K_0402_5%

RC50 4.7K_0402_5%

+3V_PRIM

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

RC63 2.2K_0201_5%@

UART2_RXD

UART2_RTS#

UART2_CTS#

TPM_PIRQ#7,31

10K_0201_5%

10K_0201_5%

100K_0201_5%

10K_0402_5%

I2C1_SDA_TS

I2C1_SCK_TS

NRB_BIT

RC196

1 2

EDP_CAB_DET#

WWAN_RST#

PCH_3.3V_TS_EN

SIO_EXT_SCI#

RC398

RC399

@

1 2

@

1 2

0_0201_5%

0_0201_5%

0_0201_5%

UART2_RTS#

I2C1_SDA_TS

I2C1_SCK_TS

SKYCAM_I2C_DATA

SKYCAM_I2C_CLK

UF_I2C_DATA

UF_I2C_CLK

SKYCAM_I2C_DATA34

SKYCAM_I2C_CLK34

NO REBOOT STRAP

HIGH

B B

LOW(DEFAULT)

Weak IPD

+3V_PRIM

12

RC65

@

2.2K_0201_5%

GPP_B22

No REBOOT

REBOOT ENABLE

ACCEL_INT1#

ACCEL_INT2#

KICKSTD_SW_DET#_PCH

ALS_I2C1_ALERT#_PCH

BOOT BIOS Destination(Bit 6)

HIGH

LOW(DEFAULT)

Internal PD 20K

A A

LPC

SPI

TS_ID0 TS_ID0_M

RB751S40T1G_SOD523-2

PCB footprint

RB520SM-30 T2R_EMD2 -2

5

12

D112

DII-DMN65D8LW-7

4

EDP_CAB_DET#22

PCH_3.3V_TS_EN44

DEBUG_UART0_TX30

HOST_SD_WP#27

UART2_RXD43

UART2_TXD43

UART2_RTS#43

UART2_CTS#43

TS_RST#22

I2C1_SDA_TS22

I2C1_SCK_TS22

UF_I2C_DATA33

UF_I2C_CLK33

33P_0402_50V8J

33P_0402_50V8J

12

12

CC98@EMC@

12

D107

RB751S40T1G_SOD523-2

RB751S40T1G_SOD523-2

RB751S40T1G_SOD523-2

RB751S40T1G_SOD523-2

+3VS_TS +3VS_TS

1 3

D

Q351

2

G

12

D108

12

D109

12

D110

RC393

100K_0201_5%

S

4

EDP_CAB_DET#

TPM_PIRQ#_R

NRB_BIT

SIO_EXT_SCI#

GPP_B22

WWAN_RST#

HOST_SD_WP#

UART2_RXD

UART2_TXD

UART2_RTS#

UART2_CTS#

TS_RST#

GPP_C17

I2C1_SDA_TS

I2C1_SCK_TS

SKYCAM_I2C_DATA

SKYCAM_I2C_CLK

UF_I2C_DATA

UF_I2C_CLK

33P_0201_50V8J

@EMC@

1

2

CC13

CC99@EMC@

PCB footprint

RB520SM-30 T2R_EMD2 -2

PCB footprint

RB520SM-30 T2R_EMD2 -2

PCB footprint

RB520SM-30 T2R_EMD2 -2

PCB footprint

RB520SM-30 T2R_EMD2 -2

12

UCPU1F

@

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKL-U_BGA1356

33P_0201_50V8J

@EMC@

1

2

CC7

TS_ID0_D 22

33P_0201_50V8J

1

2

33P_0201_50V8J

@EMC@

1

2

CC11

ACCEL_INT1#_D 31

ACCEL_INT2#_D 31

KICKSTD_SW_DET# 30,42

ALS_I2C1_ALERT# 33

3

LPSS ISH

X76

@EMC@

X7669231L56

CC8

X7669231L52

X7669231L54

X7669231L51

X7669231L53

X7669231L55

X76_8G_R3@

X768G3

X76

X7669231L57

X7669231L57

X76_16G_R3@

X7616G3

X76

X7669231L58

X7669231L58

X76_32G_R3@

X7632G3

X76

X7669231L59

X7669231L59

SKL-U

GPP F group

1.8V only

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SD A

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP F group

1.8V only

DRAM Option (R3)

Micron 8G/1866

MICRON_8G_R3@

UD1

MT52L256M32D1PF-107WT

SA00009XU1L

Micron 16G/1866

MICRON_16G_R3@

UD1

MT52L512M32D2PF-107WT

SA00009U71L

Micron 32G/1866

MICRON_32G_R3@

UD1

MT52L1G32D4PG-107WT

SA00009XV1L

Hynix 8G/1866

HYNIX_8G_R3@

UD1

H9CCNNN8GTMLAR-NUD FBGA

SA00008G65L

Hynix 16G/1866

HYNIX_16G_R3@

UD1

H9CCNNNBJTMLAR-NU D FBGA

SA00008FJ5L

Hynix 32G/1866

HYNIX_32G_R3@

UD1

H9CCNNNCLTMLAR-NU D FBGA

SA0000AEN1L

Samsung 8G/1866

SAMSUNG_8G_R3@

UD1

K4E8E324EB-EGCF FBGA178P

SA00009XY1L

Samsung 16G/1866

SAMSUNG_16G_R3@

UD1

K4E6E304EB-EGCF FBGA17

SA00008QV3L

Samsung 32G/1866

SAMSUNG_32G_R3@

UD1

4EBE304EB-EGCF FBGA178

SA00008X11L

Security Cl assification

Security Cl assification

Security Cl assification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2015/10/22 2013/10/28

2015/10/22 2013/10/28

2015/10/22 2013/10/28

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D15/ISH_UART0_RTS#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

MT52L256M32D1PF-107W T

MT52L512M32D2PF-107W T

MT52L1G32D4PG-107WT

H9CCNNN8GTMLAR-NUD FBGA

H9CCNNNBJTMLAR-NU D FBGA

H9CCNNNCLTMLAR-NU D FBGA

K4E8E324EB-EGCF FBGA178P

K4E6E304EB-EGCF FBGA17

4EBE304EB-EGCF FBGA178

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

MICRON_8G_R3@

UD2

SA00009XU1L

MICRON_16G_R3@

UD2

SA00009U71L

MICRON_32G_R3@

UD2

SA00009XV1L

HYNIX_8G_R3@

UD2

SA00008G65L

HYNIX_16G_R3@

UD2

SA00008FJ5L

HYNIX_32G_R3@

UD2

SA0000AEN1L

SAMSUNG_8G_R3@

UD2

SA00009XY1L

SAMSUNG_16G_R3@

UD2

SA00008QV3L

SAMSUNG_32G_R3@

UD2

SA00008X11L

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

6 OF 20

MT52L256M32D1PF-107WT

MT52L512M32D2PF-107WT

MT52L1G32D4PG-107WT

H9CCNNN8GTMLAR-NUD FBGA

H9CCNNNBJTMLAR-NU D FBGA

H9CCNNNCLTMLAR-NU D FBGA

K4E8E324EB-EGCF FBGA178P

K4E6E304EB-EGCF FBGA17

4EBE304EB-EGCF FBGA178

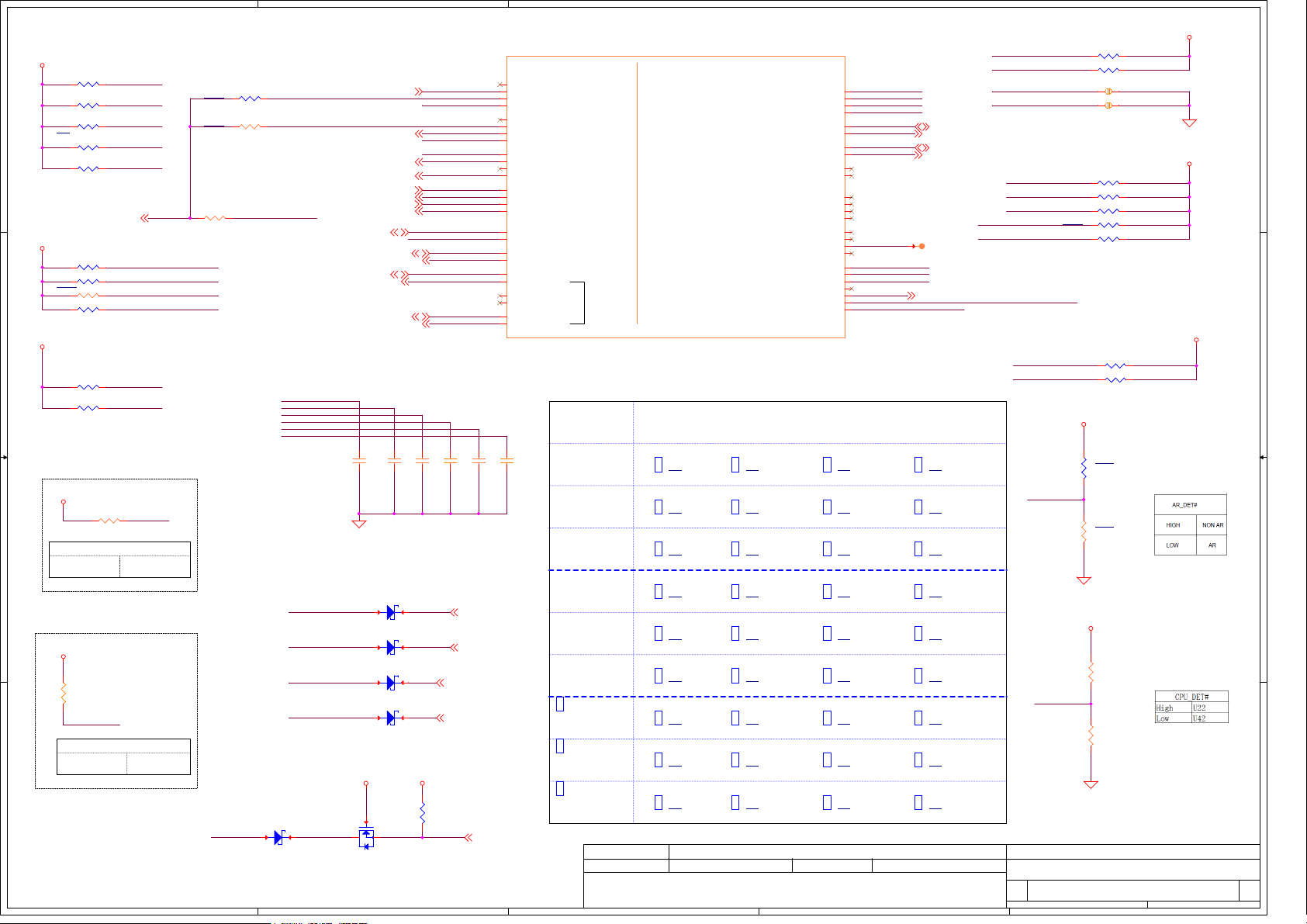

DDR_CHB_EN

P2

DDR_CHA_EN

P3

AR_DET#

P4

CPU_DET#

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

MICRON_8G_R3@

UD3

SA00009XU1L

MICRON_16G_R3@

UD3

SA00009U71L

MICRON_32G_R3@

UD3

SA00009XV1L

HYNIX_8G_R3@

UD3

SA00008G65L

HYNIX_16G_R3@

UD3

SA00008FJ5L

HYNIX_32G_R3@

UD3

SA0000AEN1L

SAMSUNG_8G_R3@

UD3

SA00009XY1L

SAMSUNG_16G_R3@

UD3

SA00008QV3L

SAMSUNG_32G_R3@

UD3

SA00008X11L

2

ISH_I2C0_SDA 31

ISH_I2C0_SCL 31

ALS_I2C1_SDA 33

ALS_I2C1_SCL 33

ACCEL_INT1#

ACCEL_INT2#

TS_ID0

ALS_I2C1_ALERT#_PCH

PAD~D

3.3V_CAM_EN 34

MICRON_8G_R3@

UD4

MT52L256M32D1PF-107WT

SA00009XU1L

MICRON_16G_R3@

UD4

MT52L512M32D2PF-107WT

SA00009U71L

MICRON_32G_R3@

UD4

MT52L1G32D4PG-107WT

SA00009XV1L

HYNIX_8G_R3@

UD4

H9CCNNN8GTMLAR-NUD FBGA

SA00008G65L

HYNIX_16G_R3@

UD4

H9CCNNNBJTMLAR-NU D FBGA

SA00008FJ5L

HYNIX_32G_R3@

UD4

H9CCNNNCLTMLAR-NU D FBGA

SA0000AEN1L

SAMSUNG_8G_R3@

UD4

K4E8E324EB-EGCF FBGA178P

SA00009XY1L

SAMSUNG_16G_R3@

UD4

K4E6E304EB-EGCF FBGA17

SA00008QV3L

SAMSUNG_32G_R3@

UD4

4EBE304EB-EGCF FBGA178

SA00008X11L

2

KICKSTD_SW_DET#_PCH

ALS_I2C1_ALERT#_PCH

@

T15

KICKSTD_SW_DET#_PCH

1

+3VS

DDR_CHA_EN

DDR_CHB_EN

DDR_CHA_EN

DDR_CHB_EN

ACCEL_INT1#

ACCEL_INT2#

TS_ID0

TS_RST#

GPP_C17

RH30 100K_0402_5%~D

1 2

RH29 100K_0402_5%~D

1 2

RH31 SHORT PADS

1 2

@

RH28 SHORT PADS

1 2

@

RC182

1 2

RC183

1 2

RC192 100K_0201_5%

1 2

RC391 220K_0201_5%

1 2

RC392 100K_0201_5%1 2

RC205

1 2

RC206

1 2

+3V_PRIM

12

R5771

10K_0201_5%

AR_DET#

12

R5772

@

10K_0201_5%

+3V_PRIM

12

@U22@

R5775

10K_0201_5%

CPU_DET#

12

@U42@

R5776

10K_0201_5%

+1.8V_PGPP

10K_0201_5%

10K_0201_5%

+3V_PRIM

10K_0201_5%

10K_0201_5%

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P08-MCP(4/14)GSPI,I2C,UART,ISH

P08-MCP(4/14)GSPI,I2C,UART,ISH

P08-MCP(4/14)GSPI,I2C,UART,ISH

LA-F371P

LA-F371P

LA-F371P

1

8 65Tuesday, November 07, 2017

8 65Tuesday, November 07, 2017

8 65Tuesday, November 07, 2017

1.0

1.0

1.0

5

4

3

2

1

UCPU1H

@

PCIE/US B3/SATA

H13

D D

PCIE_PRX_WLANTX_N524

1 2

PCIE_PRX_WLANTX_P524

PCIE_PTX_WLANRX_N524

PCIE_PTX_WLANRX_P524

PCIE_PRX_SSDTX_N723

PCIE_PRX_SSDTX_P723

PCIE_PTX_SSDRX_N723

PCIE_PTX_SSDRX_P723

SATA_PRX_SSDTX_N823

SATA_PRX_SSDTX_P823

SATA_PTX_SSDRX_N823

SATA_PTX_SSDRX_P823

PCIE_PRX_CARDTX_N927

PCIE_PRX_CARDTX_P927

PCIE_PTX_CARDRX_N927

PCIE_PTX_CARDRX_P927

1 2

RC113 100_0402_1%

CPU_XDP_PRDY#13

CPU_XDP_PREQ#13

PCIE_PRX_WWANTX_N1125

PCIE_PRX_WWANTX_P1125

PCIE_PTX_WWANRX_N1125

PCIE_PTX_WWANRX_P1125

PCIE_PRX_WWANTX_N1225

PCIE_PRX_WWANTX_P1225

PCIE_PTX_WWANRX_N1225

PCIE_PTX_WWANRX_P1225

PCIE_RCOMPN

PCIE_RCOMPP

WLAN

PCIe Gen2 x 1

C C

PCIe SSD

SATA SSD

Cardreade r

PCIe Gen2 x 1

+1.8V_PGPP

@

RC72 10K_0402_5%

M.2 2242

WWAN 2nd

SSD SATA/PCIe 2 Lane ony 4/14

B B

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL-U_BGA1356

SKL-U

SSIC / USB3

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB2

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

SIO_SLP_S0#10,31,45,56,57

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5