Cirrus Logic CS493302-IL, CS493302-CL, CS493292-CL, CS493264-IL, CS493002-CL Datasheet

...

CS49300 Family DSP

Multi-Standard Audio Decoder Family

Features

zCS4930X: DVD Audio Sub-family

—PES Layer decode for A/V sync

—DVD Audio Pack Layer Support

—Meridian Lossless Packing Specification (MLP)™

—Dolby Digital™, Dolby Pro Logic II™

—MPEG-2, Advanced Audio Coding Algorithm (AAC)

—MPEG Multichannel

—DTS Digital Surround™, DTS-ES Extended Surround™

zCS4931X: Broadcast Sub-family

—PES Layer decode for A/V sync

—Dolby Digital

—MPEG-2, Advanced Audio Coding Algorithm (AAC)

—MPEG-1 (Layers 1, 2, 3) Stereo

—MPEG-2 (Layers 2, 3) Stereo

zCS4932X: AVR Sub-family

—Dolby Digital, Dolby Pro Logic II

—DTS & DTS-ES decoding with integrated DTS tables

—Cirrus Original Surround 5.1 PCM Enhancement

—MPEG-2, Advanced Audio Coding Algorithm (AAC)

—MPEG Multichannel

—MP3 (MPEG-1, Layer 3)

zCS49330: General Purpose Audio DSP

—THX® Surround EX™ and THX® Ultra2 Cinema

—General Purpose AVR and Broadcast Audio Decoder (MPEG Multichannel, MPEG Stereo, MP3, C.O.S.)

—Car Audio

zFeatures are a super-set of the CS4923/4/5/6/7/8/9

—8 channel output, including dual zone output capability

—Dynamic Channel Remapability

—Supports up to 192 kHz Fs @ 24-bit throughput

—Increased memory/MIPs

—SRAM Interface for increased delay and buffer capability

—Dual-Precision Bass Manager

—Enhance your system functionality via firmware upgrades through the Crystal WareTM Software Licensing Program

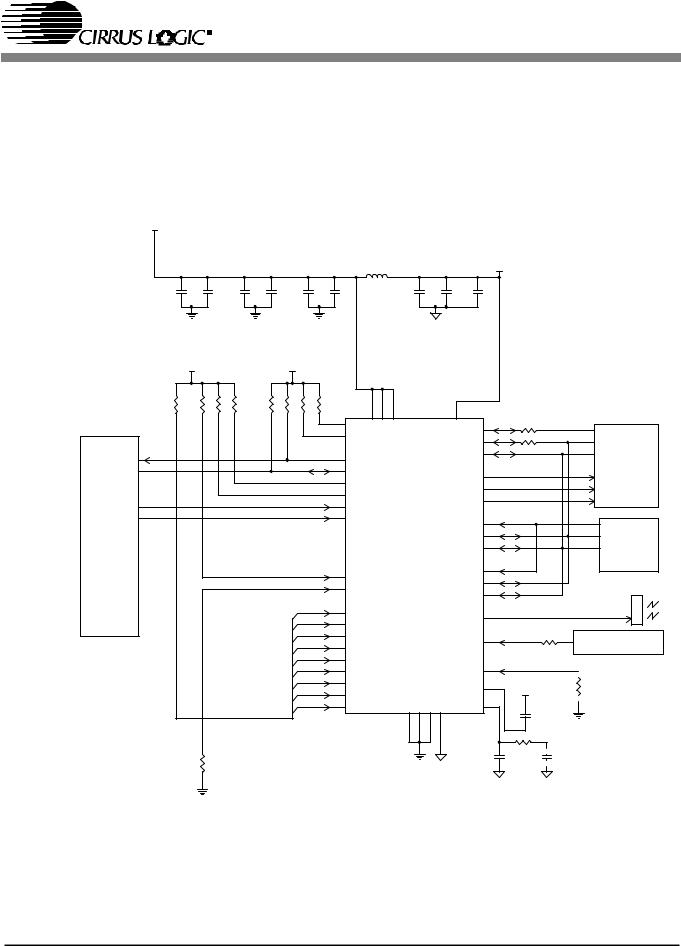

Description

The CS493XX is a family of multichannel audio decoders intended to supersede the CS4923/4/5/6/7/8/9 family as the leader of audio decoding in both the DVD, broadcast and receiver markets. The family will be split into parts tailored for each of these distinct market segments.

For the DVD market, parts will be offered which support Meridian Lossless Packing (MLP), Dolby Digital, Dolby Pro Logic II, MPEG Multichannel, DTS Digital Surround, DTS-ES, AAC, and subsets thereof. For the receiver market, parts will be offered which support Dolby Digital, Dolby Pro Logic II, MPEG Multichannel, DTS Digital Surround, DTS-ES, AAC, and various virtualizers and PCM enhancement algorithms such as HDCD®, DTS Neo:6TM, LOGIC7®, and SRS Circle Surround II®. For the broadcast market, parts will be offered which support Dolby Digital, AAC, MPEG-1, Layers 1,2 and 3, MPEG-2, Layers 2 and 3.

Under the Crystal brand, Cirrus Logic is the only single supplier of high-performance 24-bit multi-standard audio DSP decoders, DSP firmware, and high-resolution data converters. This combination of DSPs, system firmware, and data converters simplify rapid creation of world-class high-fidelity digital audio products for the Internet age.

Ordering Information: See page 85

|

APPLICATION |

CORE DECODER FUNCTIONALITY |

CS49300 |

DVD Audio |

MLP, AC-3, AAC, DTS, MPEG 5.1, MP3, etc. |

|

|

|

CS49310 |

Broadcast |

AAC, AC-3, MPEG Stereo, MP3, etc. |

|

|

|

CS49311 |

Broadcast |

AAC, MPEG Stereo, MP3, etc. |

|

|

|

CS49312 |

Broadcast |

AC-3, MPEG Stereo, MP3, etc. |

|

|

|

CS49325 |

AVR |

AC-3, COS, MPEG 5.1, MP3, etc. |

|

|

|

CS49326 |

AVR |

AC-3, DTS, COS, MPEG 5.1, MP3, etc. |

|

|

|

CS49329 |

AVR |

AC-3, AAC, DTS, MPEG 5.1, MP3, etc. |

|

|

|

CS49330 |

Car Audio DSP |

Car Audio Code |

|

|

|

CS49330 |

General Purpose |

MPEG 5.1, MPEG Stereo, MP3, C.O.S., etc |

|

|

|

CS49330 |

Post-Processor |

DPP, THX Surround EX, THX Ultra2 Cinema |

|

|

|

|

RD, |

WR, |

SCDIO, |

|

|

|

|

|

|

|

DATA7:0, |

|

R/W, |

DS, |

SCDOUT, |

|

|

|

|

|

|

RESET |

EMAD7:0, |

CS |

EMOE, |

EMWR, |

PSEL, |

A0, |

A1, |

ABOOT, |

EXTMEM, |

|

|

GPIO7:0 |

GPIO11 GPIO10 GPIO9 SCCLK SCDIN |

INTREQ |

GPIO8 |

|

||||||

CMPDAT, |

|

|

|

|

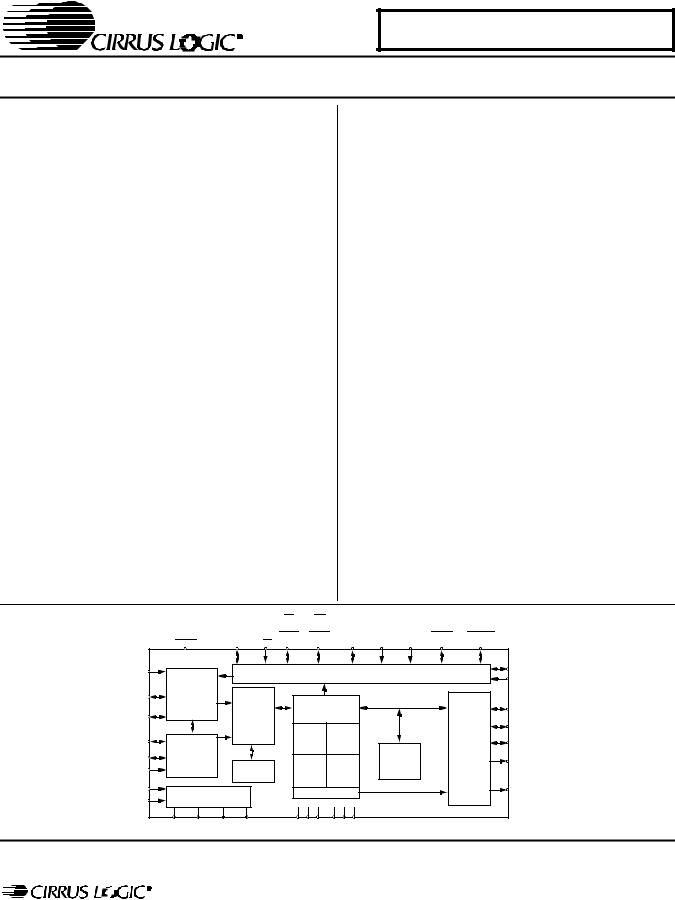

Parallel or Serial Host Interface |

|

|

DD |

|||

SDATAN2 |

Compressed |

|

|

|

|

|

DC |

||||

CMPCLK, |

Data Input |

|

|

|

|

|

|

|

|

|

|

Interface |

Framer |

|

|

|

|

|

|

|

|

||

SCLKN2 |

|

Shifter |

|

24-Bit |

|

|

|

|

MCLK |

||

CMPREQ, |

|

|

|

DSP Processing |

|

|

|

|

|||

|

Input |

|

|

|

|

|

|

||||

LRCLKN2 |

|

|

|

|

|

|

|

|

|

SCLK |

|

|

|

Buffer |

|

RAM |

RAM |

|

|

|

|

||

SCLKN1, |

|

|

|

|

|

|

|

||||

Digital |

Controller |

Program |

Data |

|

|

|

Output |

LRCLK |

|||

STCCLK2 |

Audio |

|

|

Memory Memory |

|

RAM |

Formatter |

|

|||

LRCLKN1 |

|

|

|

|

|

|

AUDATA[2.0] |

||||

Input |

RAM Input |

ROM |

ROM |

Output |

|

|

|||||

SDATAN1 |

Interface |

|

|

|

|||||||

Program |

Data |

|

Buffer |

|

|

|

|||||

|

|

Buffer |

Memory Memory |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

XMT958/AUDATA3 |

|||

CLKIN |

PLL |

|

|

|

STC |

|

|

|

|

||

CLKSEL |

|

|

|

|

|

|

|

|

|||

Clock Manager |

|

|

|

|

|

|

|

|

|

||

|

FILT2 FILT1 |

VA AGND |

|

DGND[3:1] |

VD[3:1] |

|

|

|

|

|

|

|

|

Preliminary Product Information |

This document contains information for a new product. |

|

||||||||

|

|

Cirrus Logic reserves the right to modify this product without notice. |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Copyright Cirrus Logic, Inc. 2002 |

MAR ‘02 |

|

|

|

|

|

|

|

|

|

|

|

|||

P.O. Box 17847, Austin, Texas 78760 |

||||||||||||

(All Rights Reserved) |

DS339PP4 |

|||||||||||

(512) 445 7222 FAX: (512) 445 7581 |

||||||||||||

|

1 |

|||||||||||

http://www.cirrus.com |

|

|||||||||||

CS49300 Family DSP

TABLE OF CONTENTS |

|

|

1. CHARACTERISTICS AND SPECIFICATIONS ................................................................. |

6 |

|

1.1 |

Absolute Maximum Ratings ........................................................................................ |

6 |

1.2 |

Recommended Operating Conditions ......................................................................... |

6 |

1.3 |

Digital D.C. Characteristics ......................................................................................... |

6 |

1.4 |

Power Supply Characteristics ..................................................................................... |

6 |

1.5 |

Switching Characteristics — RESET ........................................................................ |

7 |

1.6 |

Switching Characteristics — CLKIN ............................................................................ |

7 |

1.7 |

Switching Characteristics — Intel® Host Mode ........................................................... |

8 |

1.8 |

Switching Characteristics — Motorola® Host Mode .................................................. |

10 |

1.9 |

Switching Characteristics — SPI Control Port .......................................................... |

12 |

1.10 Switching Characteristics — I2C® Control Port ....................................................... |

14 |

|

1.11 Switching Characteristics — Digital Audio Input ..................................................... |

16 |

|

1.12 Switching Characteristics — CMPDAT, CMPCLK .................................................. |

18 |

|

1.13 Switching Characteristics — Parallel Data Input ..................................................... |

18 |

|

1.14 Switching Characteristics — Digital Audio Output ................................................... |

19 |

|

2. FAMILY OVERVIEW ....................................................................................................... |

21 |

|

2.1 |

Multichannel Decoder Family of Parts ...................................................................... |

21 |

3. TYPICAL CONNECTION DIAGRAMS ........................................................................... |

24 |

|

3.1 |

Multiplexed Pins ........................................................................................................ |

24 |

3.2 |

Termination Requirements ........................................................................................ |

25 |

3.3 |

Phase Locked Loop Filter ......................................................................................... |

25 |

4. POWER ........................................................................................................................... |

25 |

|

4.1 |

Decoupling ................................................................................................................ |

25 |

4.2 |

Analog Power Conditioning ....................................................................................... |

25 |

Contacting Cirrus Logic Support

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts

Dolby Digital, AC-3, Dolby Pro Logic, Dolby Pro Logic II, Dolby Surround, Surround EX, Virtual Dolby Digital, MLP and the “AAC” logo are trademarks and the “Dolby Digital” logo, “Dolby Digital with Pro Logic II” logo, “Dolby” and the double-”D” symbol are registered trademarks of Dolby Laboratories Licensing Corporation. DTS, DTS Digital Surround, DTS-ES Extended Surround, DTS Neo:6, and DTS Virtual 5.1 are trademarks and the “DTS”, “DTS-ES”, “DTS Virtual 5.1” logos are registered trademarks of the Digital Theater Systems Corporation. The “MPEG Logo” is a registered trademark of Philips Electronics N.V. Home THX Cinema and THX are registered trademarks of Lucasfilm Ltd. Surround EX is a jointly developed technology of THX and Dolby Labs, Inc. AAC (Advanced Audio Coding) is an “MPEG-2-standard-based” digital audio compression algorithm (offering up 5.1 discrete decoded channels for this implementation) collaboratively developed by AT&T, the Fraunhofer Institute, Dolby Laboratories, and the Sony Corporation. In regards to the MP3 capable functionality of the CS49300 Family DSP (via downloading of mp3_493xxx_vv.ld and mp3e_493xxx_vv.ld application codes) the following statements are applicable: “Supply of this product conveys a license for personal, private and non-commercial use. MPEG Layer-3 audio decoding technology licensed from Fraunhofer IIS and THOMSON Multimedia.” MLP and Meridian Lossless Packing are registered trademarks of Meridian Audio Ltd. Harman VMAx is a registered trademark of Harman International. The LOGIC7 logo and LOGIC7 are registered trademarks of Lexicon. SRS Circle Surround, and SRS TruSurround are trademarks of SRS Labs, Inc. The HDCD logo, HDCD, High Definition Compatible Digital and Pacific Microsonics are either registered trademarks or trademarks of Pacific Microsonics, Inc. in the United States and/or other countries. HDCD technology provided under license from Pacific Microsonics, Inc. This product’s software is covered by one or more of the following in the United States: 5,479,168; 5,638,074; 5,640,161; 5,872,531; 5,808,574; 5,838,274; 5,854,600; 5,864,311; and in Australia: 669114; with other patents pending. Intel is a registered trademark of Intel Corporation. Motorola is a registered trademark of Motorola, Inc. I2C is a registered trademark of Philips Semiconductor. Purchase of I2C Components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys a license under the Philips I2C Patent Rights to use those components in a standard I2C system. The “Cirrus Logic Logo” is a registered trademark of Cirrus Logic, Inc. All other names are trademarks, registered trademarks, or service marks of their respective companies.

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided “AS IS” without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic web site or disk may be printed for use by the user. However, no part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

2 |

DS339PP4 |

|

|

|

|

|

|

|

|

|

|

CS49300 Family DSP |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.3 |

Ground ...................................................................................................................... |

|

32 |

||||||||

4.4 |

Pads ......................................................................................................................... |

|

32 |

||||||||

5. CLOCKING ..................................................................................................................... |

|

32 |

|||||||||

6. CONTROL ...................................................................................................................... |

|

32 |

|||||||||

6.1 |

Serial Communication .............................................................................................. |

33 |

|||||||||

|

6.1.1 SPI Communication ...................................................................................... |

33 |

|||||||||

|

6.1.2 I2C Communication ...................................................................................... |

35 |

|||||||||

|

6.1.3 INTREQ Behavior: A Special Case .............................................................. |

39 |

|||||||||

6.2 |

Parallel Host Communication ................................................................................... |

41 |

|||||||||

|

6.2.1 Intel Parallel Host Communication Mode ..................................................... |

43 |

|||||||||

|

6.2.2 Motorola Parallel Host Communication Mode .............................................. |

45 |

|||||||||

|

6.2.3 Procedures for Parallel Host Mode Communication .................................... |

46 |

|||||||||

7. EXTERNAL MEMORY .................................................................................................... |

48 |

||||||||||

7.1 |

Non-Paged Memory ................................................................................................. |

49 |

|||||||||

7.2 |

Paged Memory ........................................................................................................ |

49 |

|||||||||

8. BOOT PROCEDURE & RESET ..................................................................................... |

52 |

||||||||||

8.1 |

Host Boot .................................................................................................................. |

52 |

|||||||||

|

8.1.1 Serial Download Sequence .......................................................................... |

52 |

|||||||||

|

8.1.2 Parallel Download Sequence ....................................................................... |

55 |

|||||||||

8.2 |

Autoboot |

................................................................................................................... |

56 |

||||||||

|

8.2.1 Autoboot INTREQ Behavior ......................................................................... |

57 |

|||||||||

8.3 |

Decreasing Autoboot Times Using GFABT Codes (Fast Autoboot) ......................... |

59 |

|||||||||

|

8.3.1 Design Considerations when using GFABT Codes ...................................... |

61 |

|||||||||

8.4 |

Internal Boot ............................................................................................................. |

61 |

|||||||||

8.5 |

Application Failure Boot Message ............................................................................ |

61 |

|||||||||

8.6 |

Resetting the CS493XX ............................................................................................ |

61 |

|||||||||

8.7 |

External Memory Examples ...................................................................................... |

63 |

|||||||||

|

8.7.1 Non-Paged Autoboot Memory ...................................................................... |

63 |

|||||||||

|

8.7.2 32 Kilobyte Paged Autoboot Memory ........................................................... |

64 |

|||||||||

8.8 |

CDB49300-MEMA.0 ................................................................................................. |

65 |

|||||||||

9. HARDWARE CONFIGURATION ................................................................................... |

67 |

||||||||||

10.DIGITAL INPUT & OUTPUT ........................................................................................... |

67 |

||||||||||

10.1 Digital Audio Formats .............................................................................................. |

67 |

||||||||||

|

10.1.1 I2S .............................................................................................................. |

67 |

|||||||||

|

10.1.2 Left Justified ............................................................................................... |

67 |

|||||||||

|

10.1.3 Multichannel ............................................................................................... |

67 |

|||||||||

10.2 Digital Audio Input Port ........................................................................................... |

68 |

||||||||||

10.3 Compressed Data Input Port ................................................................................... |

69 |

||||||||||

10.4 Byte Wide Digital Audio Data Input ......................................................................... |

69 |

||||||||||

|

10.4.1 Parallel Delivery with Parallel Control ........................................................ |

69 |

|||||||||

|

10.4.2 Parallel Delivery with Serial Control ........................................................... |

70 |

|||||||||

10.5 Digital Audio Output Port ......................................................................................... |

70 |

||||||||||

|

10.5.1 IEC60958 Output ........................................................................................ |

71 |

|||||||||

11.HARDWARE CONFIGURATION ................................................................................... |

72 |

||||||||||

11.1 Address Checking ................................................................................................... |

72 |

||||||||||

11.2 Input Data Hardware Configuration ........................................................................ |

72 |

||||||||||

|

11.2.1 |

Input Configuration Considerations ......................................................... |

75 |

||||||||

11.3 Output Data Hardware Configuration ...................................................................... |

76 |

||||||||||

|

11.3.1 |

Output Configuration Considerations ........................................................ |

78 |

||||||||

11.4 Creating Hardware Configuration Messages .......................................................... |

78 |

||||||||||

DS339PP4 |

3 |

CS49300 Family DSP

12.PIN DESCRIPTIONS ....................................................................................................... |

80 |

13.ORDERING INFORMATION............................................................................................ |

85 |

14.PACKAGE DIMENSIONS ............................................................................................... |

85 |

LIST OF FIGURES |

|

Figure 1. RESET Timing ..................................................................................................................... |

7 |

Figure 2. CLKIN with CLKSEL = VSS = PLL Enable .......................................................................... |

7 |

Figure 3. Intel® Parallel Host Mode Read Cycle ................................................................................. |

9 |

Figure 4. Intel® Parallel Host Mode Write Cycle ................................................................................. |

9 |

Figure 5. Motorola® Parallel Host Mode Read Cycle ........................................................................ |

11 |

Figure 6. Motorola® Parallel Host Mode Write Cycle ........................................................................ |

11 |

Figure 7. SPI Control Port Timing ..................................................................................................... |

13 |

Figure 8. I2C® Control Port Timing ................................................................................................... |

15 |

Figure 9. Digital Audio Input Data, Master and Slave Clock Timing ................................................. |

17 |

Figure 10. Serial Compressed Data Timing ...................................................................................... |

18 |

Figure 11. Parallel Data Timing (when not in a parallel control mode) ............................................. |

18 |

Figure 12. Digital Audio Output Data, Input and Output Clock Timing ............................................. |

20 |

Figure 13. I2C® Control ..................................................................................................................... |

26 |

Figure 14. I2C® Control with External Memory ................................................................................. |

27 |

Figure 15. SPI Control ...................................................................................................................... |

28 |

Figure 16. SPI Control with External Memory ................................................................................... |

29 |

Figure 17. Intel® Parallel Control Mode ............................................................................................ |

30 |

Figure 18. Motorola® Parallel Control Mode ..................................................................................... |

31 |

Figure 19. SPI Write Flow Diagram .................................................................................................. |

33 |

Figure 20. SPI Read Flow Diagram .................................................................................................. |

34 |

Figure 21. SPI Timing ....................................................................................................................... |

36 |

Figure 22. I2C® Write Flow Diagram ................................................................................................ |

37 |

Figure 23. I2C® Read Flow Diagram ................................................................................................ |

38 |

Figure 24. I2C® Timing ..................................................................................................................... |

40 |

Figure 24. Intel Mode, One-Byte Write Flow Diagram ...................................................................... |

44 |

Figure 25. Intel Mode, One-Byte Read Flow Diagram ...................................................................... |

44 |

Figure 26. Motorola Mode, One-Byte Write Flow Diagram ............................................................... |

45 |

Figure 27. Motorola Mode, One-Byte Read Flow Diagram ............................................................... |

46 |

Figure 28. Typical Parallel Host Mode Control Write Sequence Flow Diagram ............................... |

47 |

Figure 29. Typical Parallel Host Mode Control Read Sequence Flow Diagram ............................... |

48 |

Figure 30. External Memory Interface .............................................................................................. |

51 |

Figure 31. External Memory Read (16-bit address) ......................................................................... |

51 |

Figure 32. External Memory Write (16-bit address) .......................................................................... |

51 |

Figure 33. Typical Serial Boot and Download Procedure ................................................................. |

53 |

Figure 34. Typical Parallel Boot and Download Procedure .............................................................. |

54 |

Figure 35. Autoboot Timing Diagram ................................................................................................ |

56 |

Figure 37. Autoboot INTREQ Behavior ............................................................................................ |

57 |

Figure 36. Autoboot Sequence ......................................................................................................... |

58 |

4 |

DS339PP4 |

CS49300 Family DSP |

|

Figure 38. Fast Autoboot Sequence Using GFABT Codes ............................................................... |

60 |

Figure 39. Performing a Reset .......................................................................................................... |

62 |

Figure 40. Non-Paged Memory ......................................................................................................... |

64 |

Figure 41. Example Contents of a Paged 32 Kilobytes External Memory (Total 256 Kilobytes) ....... |

64 |

Figure 42. CDB49300-MEMA.0 Daughter Card for the CDB4923/30-REV-A.0 ................................ |

66 |

Figure 43. I2S Format ........................................................................................................................ |

68 |

Figure 44. Left Justified Format (Rising Edge Valid SCLK) ............................................................... |

68 |

Figure 45. Multichannel Format ......................................................................................................... |

68 |

LIST OF TABLES |

|

Table 1. PLL Filter Component Values .............................................................................................. |

25 |

Table 2. Host Modes.......................................................................................................................... |

32 |

Table 3. SPI Communication Signals................................................................................................. |

33 |

Table 4. I2C® Communication Signals ............................................................................................. |

35 |

Table 5. Parallel Input/Output Registers ............................................................................................ |

42 |

Table 6. Intel Mode Communication Signals...................................................................................... |

43 |

Table 7. Motorola Mode Communication Signals .............................................................................. |

45 |

Table 8. Memory Interface Pins ......................................................................................................... |

49 |

Table 9. Boot Write Messages........................................................................................................... |

52 |

Table 10. Boot Read Messages......................................................................................................... |

52 |

Table 11. Reduced Autoboot Times using GFABT8.LD, GFABT6.LD, and GFABT4.LD |

|

on a CS493264-CL Rev. G DSP........................................................................................................ |

59 |

Table 12. Memory Requirements for Example 5.1, 6.1 and 7.1 Channel Systems ........................... |

63 |

Table 13. Digital Audio Input Port ...................................................................................................... |

68 |

Table 14. Compressed Data Input Port.............................................................................................. |

69 |

Table 15. Digital Audio Output Port.................................................................................................... |

70 |

Table 16. MCLK/SCLK Master Mode Ratios...................................................................................... |

71 |

Table 17. Output Channel Mapping ................................................................................................... |

71 |

Table 18. Input Data Type Configuration |

|

(Input Parameter A)............................................................................................................................ |

73 |

Table 19. Input Data Format Configuration |

|

(Input Parameter B)............................................................................................................................ |

73 |

Table 20. Input SCLK Polarity Configuration |

|

(Input Parameter C) ........................................................................................................................... |

75 |

Table 21. Input FIFO Setup Configuration |

|

(Input Parameter D) ........................................................................................................................... |

75 |

Table 22. Output Clock Configuration |

|

(Parameter A)..................................................................................................................................... |

76 |

Table 23. Output Data Format Configuration |

|

(Parameter B)..................................................................................................................................... |

76 |

Table 24. Output MCLK Configuration |

|

(Parameter C) .................................................................................................................................... |

77 |

Table 25. Output SCLK Configuration |

|

(Parameter D) .................................................................................................................................... |

77 |

Table 26. Output SCLK Polarity Configuration |

|

(Parameter E)..................................................................................................................................... |

77 |

Table 27. Example Values to be Sent to CS493XX After Download or Soft Reset ........................... |

79 |

DS339PP4 |

5 |

CS49300 Family DSP

1.CHARACTERISTICS AND SPECIFICATIONS

1.1. Absolute Maximum Ratings

(AGND, DGND = 0 V; all voltages with respect to 0 V)

Parameter |

|

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

|

DC power supplies: |

Positive digital |

VD |

–0.3 |

2.75 |

V |

|

Positive analog |

VA |

–0.3 |

2.75 |

V |

|

||VA| – |VD|| |

|

- |

0.3 |

V |

|

|

|

|

|

|

Input current, any pin except supplies |

|

Iin |

- |

± 10 |

mA |

Digital input voltage |

|

VIND |

–0.3 |

3.63 |

V |

Storage temperature |

|

Tstg |

–65 |

150 |

°C |

CAUTION: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

1.2. Recommended Operating Conditions

(AGND, DGND = 0 V; all voltages with respect to 0 V)

Parameter |

|

Symbol |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

DC power supplies: |

Positive digital |

VD |

2.37 |

2.5 |

2.63 |

V |

|

Positive analog |

VA |

2.37 |

2.5 |

2.63 |

V |

|

||VA| – |VD|| |

|

- |

- |

0.3 |

V |

|

|

|

|

|

|

|

Ambient operating temperature |

|

TA |

0 |

- |

70 |

°C |

1.3. Digital D.C. Characteristics

(TA = 25 °C; VA, VD[3:1] = 2.5 V ± 5%; measurements performed under static conditions.)

Parameter |

Symbol |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

High-level input voltage |

VIH |

2.0 |

- |

- |

V |

Low-level input voltage |

VIL |

- |

- |

0.8 |

V |

High-level output voltage at IO = –2.0 mA |

VOH |

VD × 0.9 |

- |

- |

V |

Low-level output voltage at IO = 2.0 mA |

VOL |

- |

- |

VD × 0.11 |

V |

Input leakage current |

Iin |

- |

- |

1.0 |

µA |

1.4. Power Supply Characteristics

(TA = 25 °C; VA, VD[3:1] = 2.5 V ± 5%; measurements performed under operating conditions)

|

Parameter |

Symbol |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

Power supply current: |

Digital operating: VD[3:1] |

|

- |

200 |

310 |

mA |

|

Analog operating: VA |

|

- |

1.7 |

4 |

mA |

|

|

|

|

|

|

|

6 |

DS339PP4 |

CS49300 Family DSP

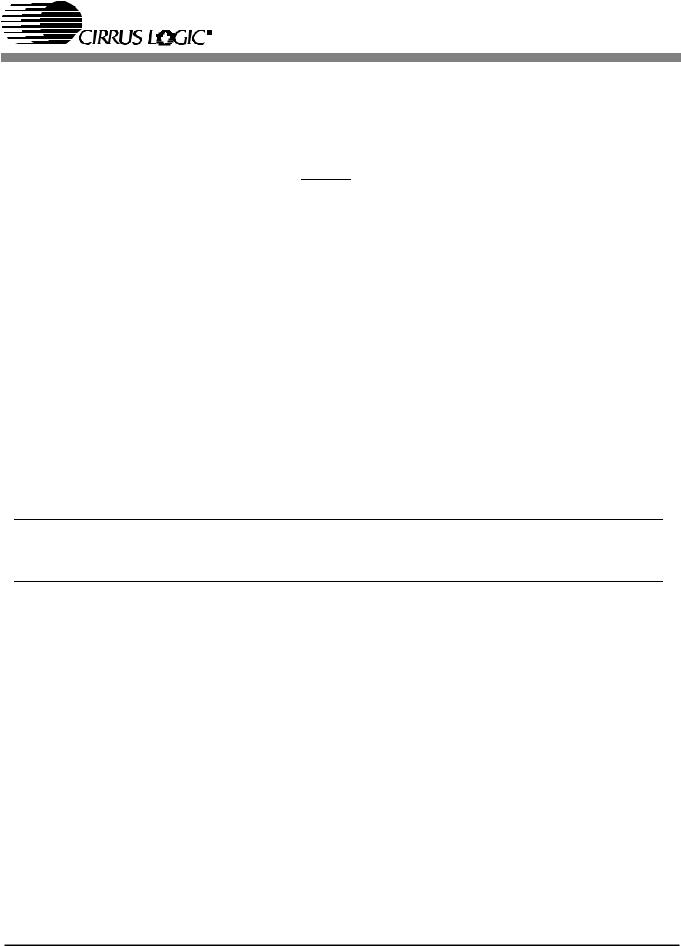

1.5. Switching Characteristics — RESET

(TA = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF)

|

|

|

Parameter |

|

Symbol |

Min |

Max |

Unit |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

minimum pulse width low (-CL) |

(Note 1) |

Trstl |

100 |

- |

s |

||||||

|

RESET |

|

||||||||||||

|

|

|

minimum pulse width low (-IL) |

(Note 1) |

Trstl |

530 |

- |

s |

||||||

|

RESET |

|||||||||||||

|

All bidirectional pins high-Z after |

|

|

|

low |

(Note 2) |

Trst2z |

- |

50 |

ns |

||||

|

RESET |

|||||||||||||

|

Configuration bits setup before |

|

|

|

high |

|

Trstsu |

50 |

- |

ns |

||||

|

RESET |

|

||||||||||||

|

Configuration bits hold after |

|

|

|

high |

|

Trsthld |

15 |

- |

ns |

||||

|

RESET |

|

||||||||||||

Notes: 1. The minimum RESET pulse listed above is valid only when using the recommended pull-up/pull-down resistors on the RD, WR, PSEL and ABOOT mode pins. For Rev. D and older parts, pull-up/pull-down resistors may be 4.7 k or 3.3 k. For Rev. E and newer parts, pull-up/pull-down resistors must be 3.3 k.

2. This specification is characterized but not production tested.

RESET |

|

RD, W R, |

|

PSEL, ABOOT |

|

All Bidirectional |

|

Pins |

Trstsu Trsthld |

Trst2z

Trstl

Figure 1. RESET Timing

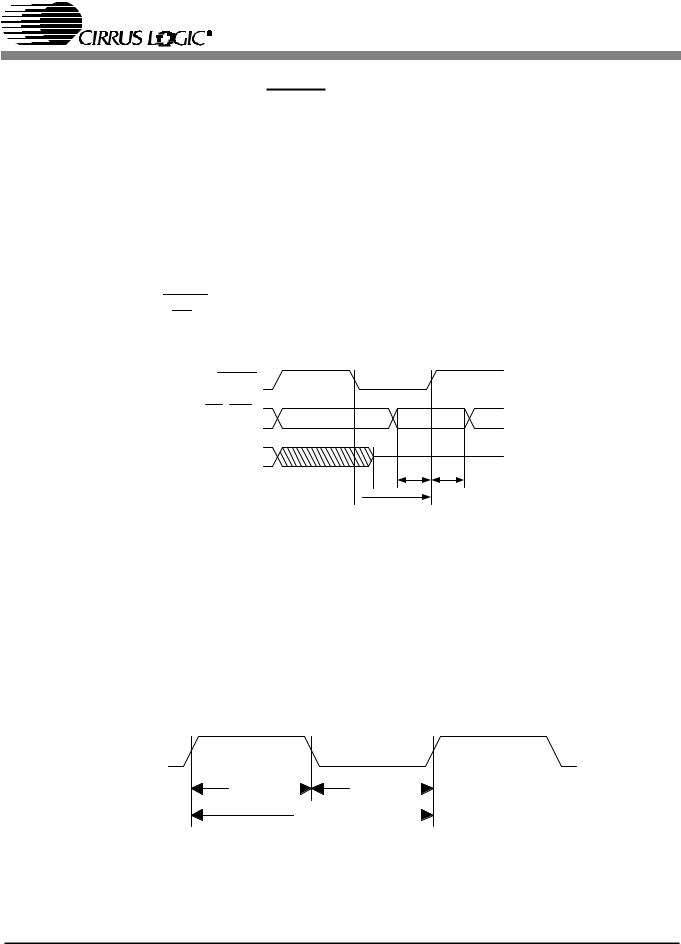

1.6. Switching Characteristics — CLKIN

(TA = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF)

Parameter |

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

CLKIN period for internal DSP clock mode |

Tclki |

35 |

3800 |

ns |

CLKIN high time for internal DSP clock mode |

Tclkih |

18 |

|

ns |

CLKIN low time for internal DSP clock mode |

Tclkil |

18 |

|

ns |

CLKIN

Tclkih |

|

|

Tclkil |

|

Tclki |

|

|||

|

|

|

||

|

|

|

||

Figure 2. CLKIN with CLKSEL = VSS = PLL Enable

DS339PP4 |

7 |

CS49300 Family DSP

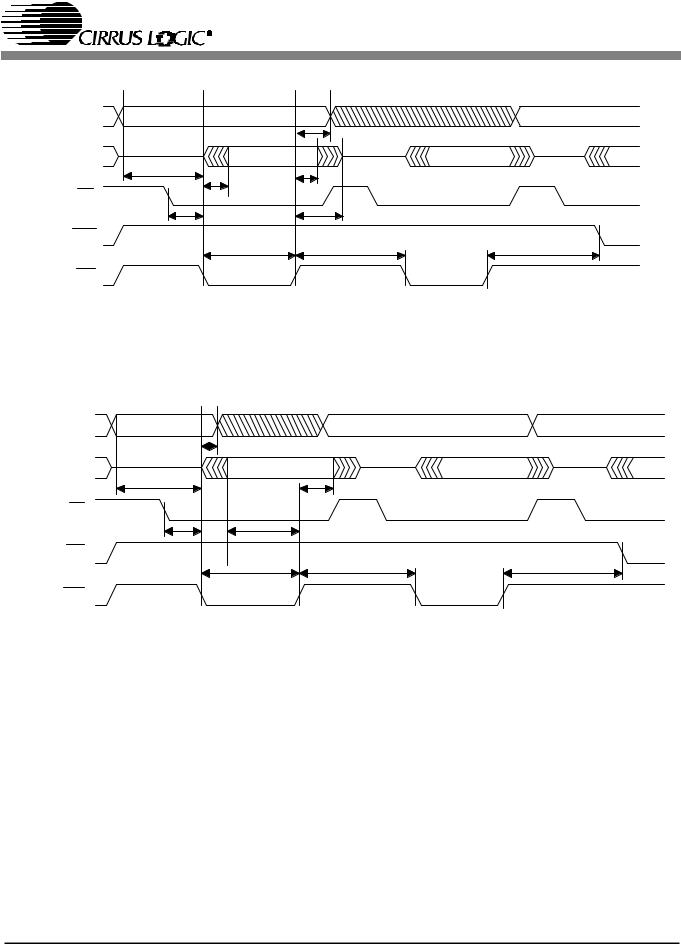

1.7. Switching Characteristics — Intel® Host Mode

(TA = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

|

|

Symbol |

Min |

Max |

Unit |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Address setup before |

|

|

|

|

|

|

|

|

and |

|

|

low or |

|

|

|

|

and |

|

|

|

low |

Tias |

5 |

- |

ns |

||||||||||||||||||||||||||||||||||||||||||||

|

CS |

|

|

RD |

CS |

|

WR |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Address hold time after |

|

|

|

|

|

|

|

|

|

|

|

and |

|

|

|

|

low or |

|

|

|

|

and |

|

|

|

low |

Tiah |

5 |

- |

ns |

|||||||||||||||||||||||||||||||||||||||

|

CS |

|

|

RD |

|

CS |

WR |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Delay between |

|

|

|

|

|

|

|

|

then |

|

|

|

|

|

|

|

|

|

|

low or |

|

|

|

|

then |

|

|

|

|

low |

|

|

|

Ticdr |

0 |

∞ |

ns |

||||||||||||||||||||||||||||||||

|

RD |

|

|

CS |

|

CS |

|

RD |

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data valid after |

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

low |

(Note 3) |

Tidd |

- |

21 |

ns |

||||||||||||||||||||||||||||||||||||||||||||||

|

CS |

|

RD |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

and |

|

|

|

|

low for read |

(Note 1) |

Tirpw |

DCLKP + 10 |

- |

ns |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

CS |

|

RD |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data hold time after |

|

|

|

|

|

|

|

or |

|

|

|

|

|

|

|

|

|

high |

|

|

|

Tidhr |

5 |

- |

ns |

||||||||||||||||||||||||||||||||||||||||||||

|

CS |

RD |

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data high-Z after |

|

|

|

|

|

|

|

|

|

|

or |

|

|

|

|

|

|

|

|

|

high |

(Note 2) |

Tidis |

- |

22 |

ns |

|||||||||||||||||||||||||||||||||||||||||||

|

CS |

|

|

RD |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

or |

|

|

|

high to |

|

|

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

low for next read |

(Note 1) |

Tird |

2*DCLKP + 10 |

- |

ns |

||||||||||||||||||||||||||||||||||||||

|

CS |

|

RD |

|

CS |

|

RD |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

or |

|

|

|

high to |

|

|

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

|

|

low for next write |

(Note 1) |

Tirdtw |

2*DCLKP + 10 |

- |

ns |

||||||||||||||||||||||||||||||||||||

|

CS |

RD |

|

CS |

|

WR |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Delay between |

|

|

|

|

|

|

|

|

then |

|

|

|

|

|

|

|

|

|

low or |

|

|

then |

|

|

|

low |

|

|

|

Ticdw |

0 |

∞ |

ns |

||||||||||||||||||||||||||||||||||||

|

WR |

CS |

CS |

WR |

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data setup before |

|

|

|

|

|

|

|

|

|

or |

|

|

|

|

|

|

|

|

|

|

high |

|

|

|

Tidsu |

20 |

- |

ns |

|||||||||||||||||||||||||||||||||||||||||

|

CS |

|

WR |

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

and |

|

|

|

|

low for write |

(Note 1) |

Tiwpw |

DCLKP + 10 |

- |

ns |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

CS |

WR |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data hold after |

|

|

|

|

|

|

or |

|

|

|

|

|

|

|

|

high |

|

|

|

Tidhw |

5 |

- |

ns |

||||||||||||||||||||||||||||||||||||||||||||||

|

CS |

WR |

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

or |

|

|

|

high to |

|

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

|

low for next read |

(Note 1) |

Tiwtrd |

2*DCLKP + 10 |

- |

ns |

|||||||||||||||||||||||||||||||||||||||

|

CS |

WR |

CS |

RD |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

or |

|

|

|

high to |

|

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

|

low for next write |

(Note 1) |

Tiwd |

2*DCLKP + 10 |

- |

ns |

||||||||||||||||||||||||||||||||||||||

|

CS |

WR |

CS |

WR |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLKP, in nanoseconds. DCLKP = 1/DCLK. The DSP clock can be defined as follows:

External CLKIN Mode:

DCLK == CLKIN/4 before and during boot

DCLK == CLKIN after boot

Internal Clock Mode:

DCLK == 10MHz before and during boot, i.e. DCLKP == 100ns

DCLK == 65 MHz after boot, i.e. DCLKP == 15.4ns

It should be noted that DCLK for the internal clock mode is application specific. The application code users guide should be checked to confirm DCLK for the particular application.

2.This specification is characterized but not production tested. A 470 ohm pull-up resistor was used for characterization to minimize the effects of external bus capacitance.

3.See Tidd from Intel Host Mode in Table 6 on page 43

8 |

DS339PP4 |

CS49300 Family DSP

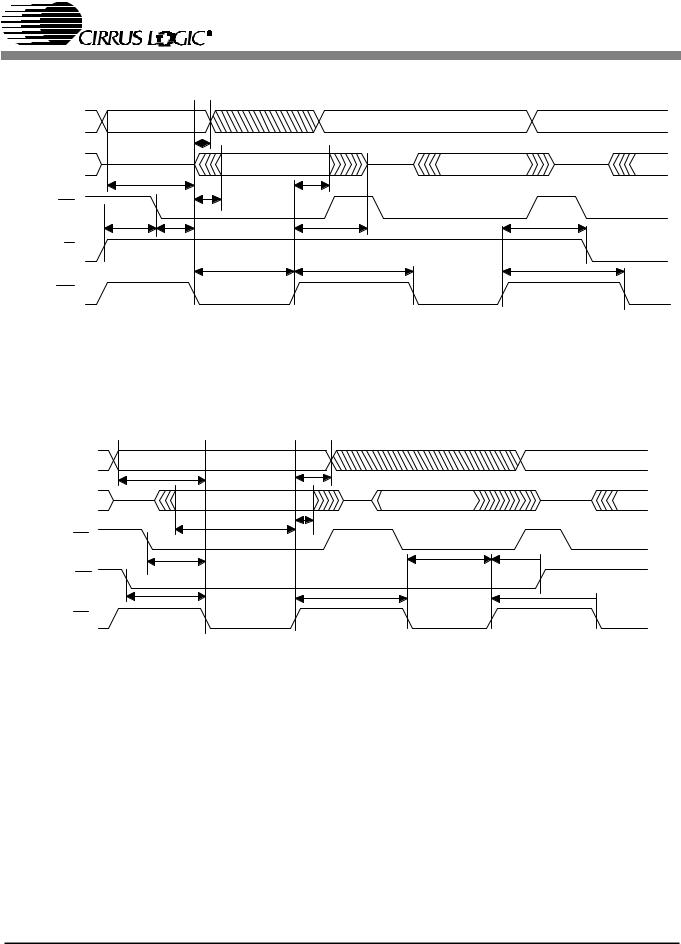

A1:0 |

|

|

Tia h |

DA TA7:0 |

|

Tias |

|

Tidhr |

|

Tidd |

|

CS |

|

Ticdr |

Tidis |

W R |

|

Tirpw |

Tird |

RD |

|

Figure 3. Intel® Parallel Host Mode Read Cycle

A1:0 |

|

Tiah |

|

DATA7:0 |

|

Tias |

Tidhw |

|

|

CS |

|

Ticdw |

Tidsu |

RD |

Tiw d |

Tiw p w |

|

W R |

|

Figure 4. Intel® Parallel Host Mode Write Cycle

Tirdtw

Tiw trd

DS339PP4 |

9 |

CS49300 Family DSP

1.8. Switching Characteristics — Motorola® Host Mode

(TA = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

Min |

Max |

Unit |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Address setup before |

|

|

|

|

|

|

|

|

|

and |

|

|

|

low |

|

Tmas |

5 |

- |

ns |

|||||||||||||||||||||||||||||||||||||||||||||||||

|

CS |

|

|

DS |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Address hold time after |

|

|

|

|

|

|

|

|

|

|

|

|

and |

|

|

|

low |

|

Tmah |

5 |

- |

ns |

||||||||||||||||||||||||||||||||||||||||||||||

|

CS |

|

|

|

DS |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Delay between |

|

|

|

|

|

|

|

|

then |

|

|

|

|

|

|

|

|

|

|

low or |

|

|

then |

|

low |

|

Tmcdr |

0 |

∞ |

ns |

||||||||||||||||||||||||||||||||||||||

|

DS |

|

|

CS |

CS |

DS |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data valid after |

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Tmdd |

- |

21 |

ns |

|||||||||||||||||||||||||

|

CS |

RD |

|

low with R/W |

high |

(Note 3) |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

and |

|

|

|

low for read |

(Note 1) |

Tmrpw |

DCLKP + 10 |

- |

ns |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

CS |

|

DS |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data hold time after |

|

|

|

|

|

|

|

|

|

or |

|

|

|

|

|

|

|

|

|

|

|

high after read |

|

Tmdhr |

5 |

- |

ns |

|||||||||||||||||||||||||||||||||||||||||

|

CS |

DS |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data high-Z after |

|

|

|

|

|

|

|

|

|

|

or |

|

|

|

|

|

|

|

|

|

|

high low after read |

(Note 2) |

Tmdis |

- |

22 |

ns |

|||||||||||||||||||||||||||||||||||||||||

|

CS |

DS |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

or |

|

|

|

high to |

|

|

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

|

low for next read |

(Note 1) |

Tmrd |

2*DCLKP + 10 |

- |

ns |

|||||||||||||||||||||||||||||||||||

|

CS |

|

DS |

CS |

DS |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

or |

|

|

|

high to |

|

|

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

|

low for next write |

(Note 1) |

Tmrdtw |

2*DCLKP + 10 |

- |

ns |

|||||||||||||||||||||||||||||||||||

|

CS |

DS |

CS |

DS |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Delay between |

|

|

|

|

|

|

|

then |

|

|

|

|

|

|

|

|

|

|

low or |

|

|

then |

|

low |

|

Tmcdw |

0 |

∞ |

ns |

|||||||||||||||||||||||||||||||||||||||

|

DS |

CS |

CS |

DS |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data setup before |

|

|

|

|

|

|

|

|

|

|

|

or |

|

|

|

|

|

|

|

|

|

|

|

high |

|

Tmdsu |

20 |

- |

ns |

|||||||||||||||||||||||||||||||||||||||

|

CS |

|

DS |

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

and |

|

|

|

low for write |

(Note 1) |

Tmwpw |

DCLKP + 10 |

- |

ns |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

CS |

DS |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

setup before |

|

|

|

|

|

|

|

|

|

|

|

|

AND |

|

|

|

|

|

|

|

|

low |

|

Tmrwsu |

5 |

- |

ns |

||||||||||||||||||||||||||||||||||||

|

R/W |

|

CS |

|

DS |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

hold time after |

|

|

|

|

|

|

|

|

|

or |

|

|

|

|

|

|

|

|

|

high |

|

Tmrwhld |

5 |

- |

ns |

||||||||||||||||||||||||||||||||||||||

|

R/W |

CS |

DS |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Data hold after |

|

|

|

|

|

|

or |

|

|

|

|

|

|

|

|

|

high |

|

Tmdhw |

5 |

- |

ns |

||||||||||||||||||||||||||||||||||||||||||||||

|

CS |

DS |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

or |

|

|

|

high to |

|

|

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

high for next read |

Tmwtrd |

2*DCLKP + 10 |

- |

ns |

||||||||||||||||||||||||

|

CS |

DS |

CS |

DS |

low with R/W |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(Note 1) |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

or |

|

|

|

high to |

|

|

|

|

|

|

|

|

|

and |

|

|

|

|

|

|

|

|

|

low for next write |

(Note 1) |

Tmwd |

2*DCLKP + 10 |

- |

ns |

|||||||||||||||||||||||||||||||||||||

|

CS |

DS |

CS |

DS |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLKP, in nanoseconds. DCLKP = 1/DCLK. The DSP clock can be defined as follows:

External CLKIN Mode:

DCLK == CLKIN/4 before and during boot

DCLK == CLKIN after boot

Internal Clock Mode:

DCLK == 10MHz before and during boot, i.e. DCLKP == 100ns

DCLK == 65 MHz after boot, i.e. DCLKP == 15.4ns

It should be noted that DCLK for the internal clock mode is application specific. The application code users guide should be checked to confirm DCLK for the particular application.

2.This specification is characterized but not production tested. A 470 ohm pull-up resistor was used for characterization to minimize the effects of external bus capacitance.

3.See Tmdd from Motorola Host Mode in Table 7 on page 45

10 |

DS339PP4 |

CS49300 Family DSP

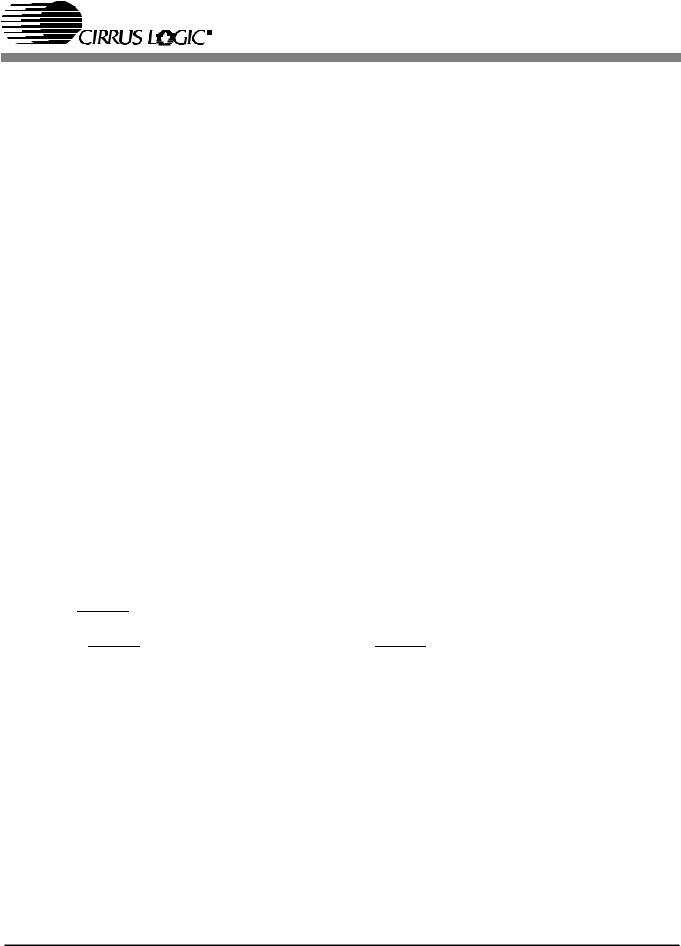

A1:0 |

|

|

|

|

|

Tm ah |

|

DATA7:0 |

Tm as |

|

|

|

Tm dhr |

|

|

|

|

|

|

CS |

Tm rw su |

Tm dd |

|

|

|

||

|

Tm cdr |

Tm dis |

|

|

|

||

R/W |

|

Tm rpw |

Tm rd |

|

|

||

DS |

|

|

|

Tm rw hld |

Tm rdtw |

Figure 5. Motorola® Parallel Host Mode Read Cycle

A 1 |

:0 |

|

|

Tm as |

Tm ah |

D A T A 7 |

:0 |

|

|

Tm d su |

Tm dhw |

C S |

|

|

|

Tm cdw |

Tm w pw |

R /W |

|

|

|

Tm rw su |

Tm w d |

D S |

|

|

Tm rw h ld

Tm rw h ld

Tm w trd

Tm w trd

Figure 6. Motorola® Parallel Host Mode Write Cycle

DS339PP4 |

11 |

CS49300 Family DSP

1.9. Switching Characteristics — SPI Control Port

(TA = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF)

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

Min |

Max |

Units |

||

|

|

|

|

|

|

|

|||||||||||||

|

SCCLK clock frequency |

(Note 1) |

fsck |

- |

2000 |

kHz |

|||||||||||||

|

|

falling to SCCLK rising |

|

tcss |

20 |

- |

ns |

||||||||||||

|

CS |

|

|||||||||||||||||

|

Rise time of SCCLK line |

(Note 7) |

tr |

- |

50 |

ns |

|||||||||||||

|

Fall time of SCCLK lines |

(Note 7) |

tf |

- |

50 |

ns |

|||||||||||||

|

SCCLK low time |

|

tscl |

150 |

- |

ns |

|||||||||||||

|

SCCLK high time |

|

tsch |

150 |

- |

ns |

|||||||||||||

|

Setup time SCDIN to SCCLK rising |

|

tcdisu |

50 |

- |

ns |

|||||||||||||

|

Hold time SCCLK rising to SCDIN |

(Note 2) |

tcdih |

50 |

- |

ns |

|||||||||||||

|

Transition time from SCCLK to SCDOUT valid |

(Note 3) |

tscdov |

- |

40 |

ns |

|||||||||||||

|

Time from SCCLK rising to |

|

|

|

|

rising |

(Note 4) |

tscrh |

- |

200 |

ns |

||||||||

|

INTREQ |

||||||||||||||||||

|

Rise time for |

|

|

|

|

|

|

|

|

|

|

|

(Note 4) |

trr |

- |

(Note 6) |

ns |

||

|

INTREQ |

|

|

|

|

|

|

||||||||||||

|

Hold time for |

|

|

|

from SCCLK rising |

(Note 5, 7) |

tscrl |

0 |

- |

ns |

|||||||||

|

INTREQ |

||||||||||||||||||

|

Time from SCCLK falling to |

|

|

rising |

|

tsccsh |

20 |

- |

ns |

||||||||||

|

CS |

|

|||||||||||||||||

|

High time between active |

|

|

|

|

|

|

|

tcsht |

200 |

- |

ns |

|||||||

|

CS |

|

|

||||||||||||||||

|

Time from |

|

|

|

rising to SCDOUT high-Z |

(Note 7) |

tcscdo |

|

20 |

ns |

|||||||||

|

CS |

|

|||||||||||||||||

Notes: 1. The specification fsck indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port may be limited by the software. The relevant application code user’s manual should be consulted for the software speed limitations.

2.Data must be held for sufficient time to bridge the 50 ns transition time of SCCLK.

3.SCDOUT should not be sampled during this time period.

4.INTREQ goes high only if there is no data to be read from the DSP at the rising edge of SCCLK for the second-to-last bit of the last byte of data during a read operation as shown.

5.If INTREQ goes high as indicated in (Note 4), then INTREQ is guaranteed to remain high until the next rising edge of SCCLK. If there is more data to be read at this time, INTREQ goes active low again. Treat this condition as a new read transaction. Raise chip select to end the current read transaction and then drop it, followed by the 7-bit address and the R/W bit (set to 1 for a read) to start a new read transaction.

6.With a 4.7k Ohm pull-up resistor this value is typically 215ns. As this pin is open drain adjusting the pull up value will affect the rise time.

7.This time is by design and not tested.

12 |

DS339PP4 |

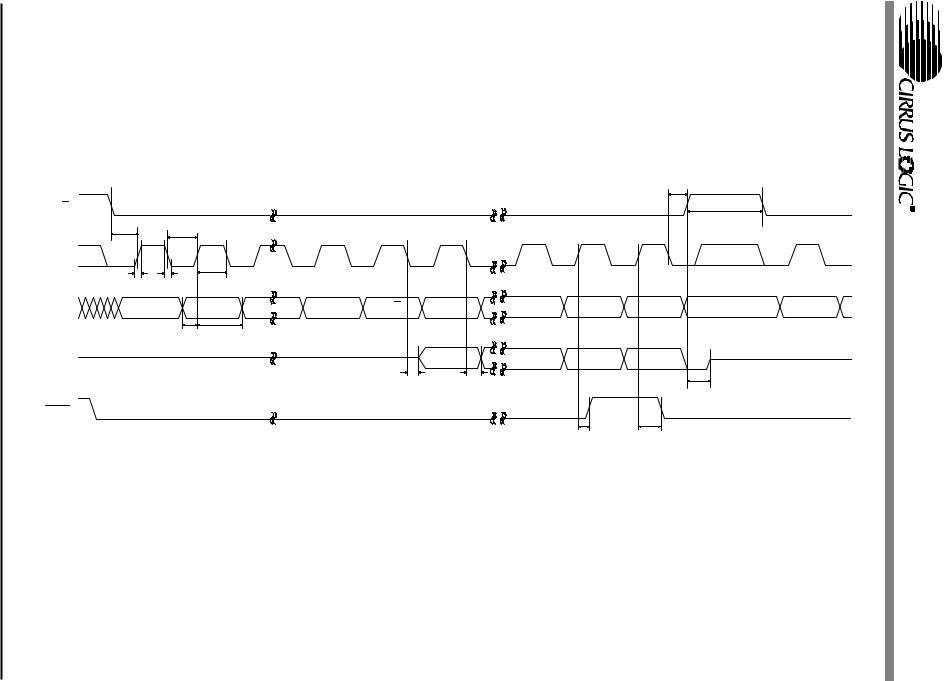

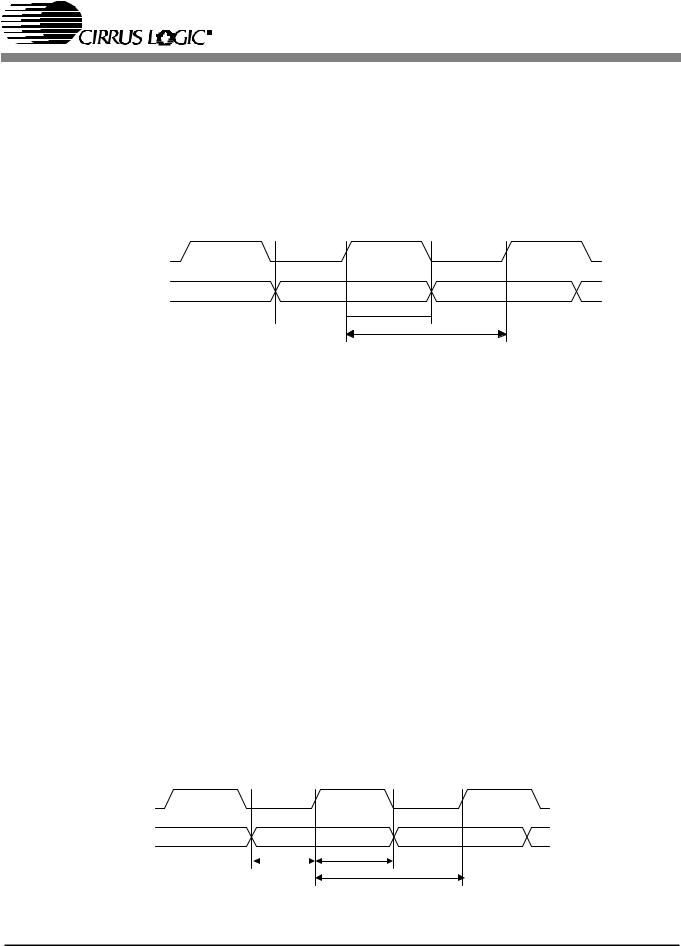

DS339PP4

C S

S C C L K

S C D IN

S C D O U T

IN T R E Q

13

|

|

|

|

|

|

|

|

|

ts c c s h |

tc s s |

ts c l |

|

|

|

|

|

|

|

tc s h t |

0 |

1 |

2 |

6 |

7 |

0 |

5 |

6 |

7 |

|

tr |

ts c h |

|

|

|

|

|

|

|

|

tf |

|

|

|

|

|

|

|

|

|

A 6 |

A 5 |

|

A 0 |

R /W |

M S B |

|

|

L S B |

A 6 |

|

t c d is u t c d ih |

|

|

|

|

|

|

|

|

|

|

|

|

|

M S B |

|

|

L S B |

tri-s ta te |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ts c d o v |

|

ts c d o v |

|

|

tc s c d o |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ts c rh |

ts c rl |

|

Figure 7. SPI Control Port Timing

DSP Family CS49300

CS49300 Family DSP

1.10. Switching Characteristics — I2C® Control Port

(TA = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF)

|

|

|

|

|

Parameter |

|

Symbol |

Min |

Max |

Units |

|

|

|

|

|

|

|

||||||

SCCLK clock frequency |

(Note 1) |

fscl |

|

400 |

kHz |

||||||

Bus free time between transmissions |

|

tbuf |

4.7 |

|

s |

||||||

Start-condition hold time (prior to first clock pulse) |

|

thdst |

4.0 |

|

s |

||||||

Clock low time |

|

tlow |

1.2 |

|

s |

||||||

Clock high time |

|

thigh |

1.0 |

|

s |

||||||

SCDIO setup time to SCCLK rising |

|

tsud |

250 |

|

ns |

||||||

SCDIO hold time from SCCLK falling |

(Note 2) |

thdd |

0 |

|

s |

||||||

Rise time of SCCLK |

(Note 3), (Note 7) |

tr |

|

50 |

ns |

||||||

Fall time of SCCLK |

(Note 7) |

tf |

|

300 |

ns |

||||||

Time from SCCLK falling to CS493XX ACK |

|

tsca |

|

40 |

ns |

||||||

Time from SCCLK falling to SCDIO valid during read operation |

tscsdv |

|

40 |

ns |

|||||||

Time from SCCLK rising to |

|

rising |

(Note 4) |

tscrh |

|

200 |

ns |

||||

INTREQ |

|

||||||||||

Hold time for |

|

|

from SCCLK rising |

(Note 5) |

tscrl |

0 |

|

ns |

|||

INTREQ |

|

||||||||||

Rise time for |

|

|

|

|

|

|

(Note 6) |

trr |

|

** |

ns |

INTREQ |

|

|

|||||||||

Setup time for stop condition |

|

tsusp |

4.7 |

|

s |

||||||

Notes:. 1. The specification fscl indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port may be limited by the software. The relevant application code user’s manual should be consulted for the software speed limitations.

2.Data must be held for sufficient time to bridge the 300-ns transition time of SCCLK. This hold time is by design and not tested.

3.This rise time is shorter than that recommended by the I2C specifications. For more information, see Section 6.1, “Serial Communication” on page 33.

4.INTREQ goes high only if there is no data to be read from the DSP at the rising edge of SCCLK for the last data bit of the last byte of data during a read operation as shown.

5.If INTREQ goes high as indicated in Note 8, then INTREQ is guaranteed to remain high until the next rising edge of SCCLK. If there is more data to be read at this time, INTREQ goes active low again. Treat this condition as a new read transaction. Send a new start condition followed by the 7-bit address and the R/W bit (set to 1 for a read). This time is by design and is not tested.

6.With a 4.7k Ohm pull-up resistor this value is typically 215ns. As this pin is open drain adjusting the pull up value will affect the rise time.

7.This time is by design and not tested.

14 |

DS339PP4 |

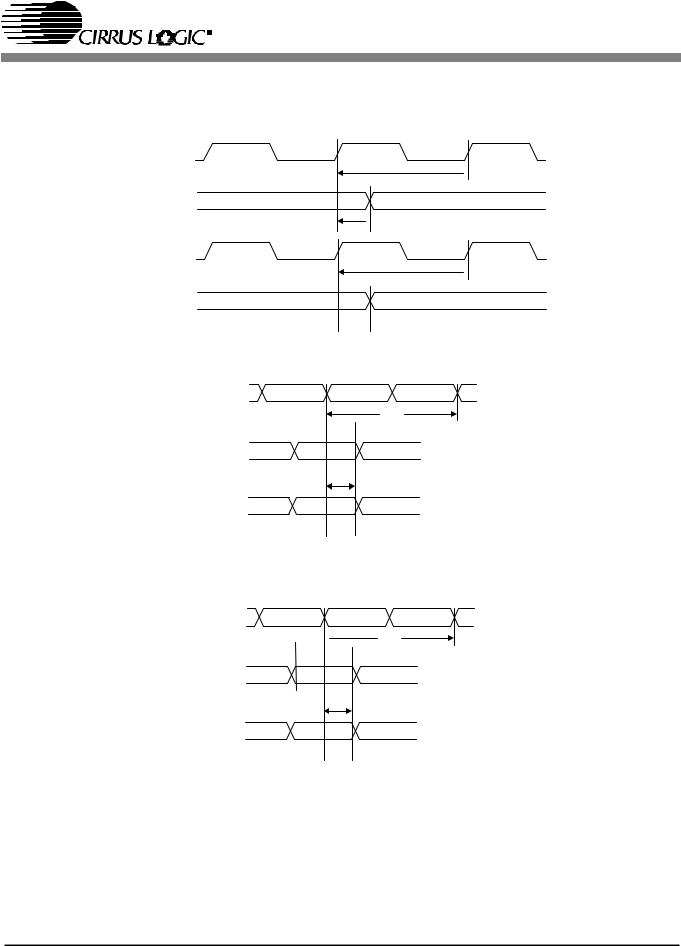

CS49300 Family DSP

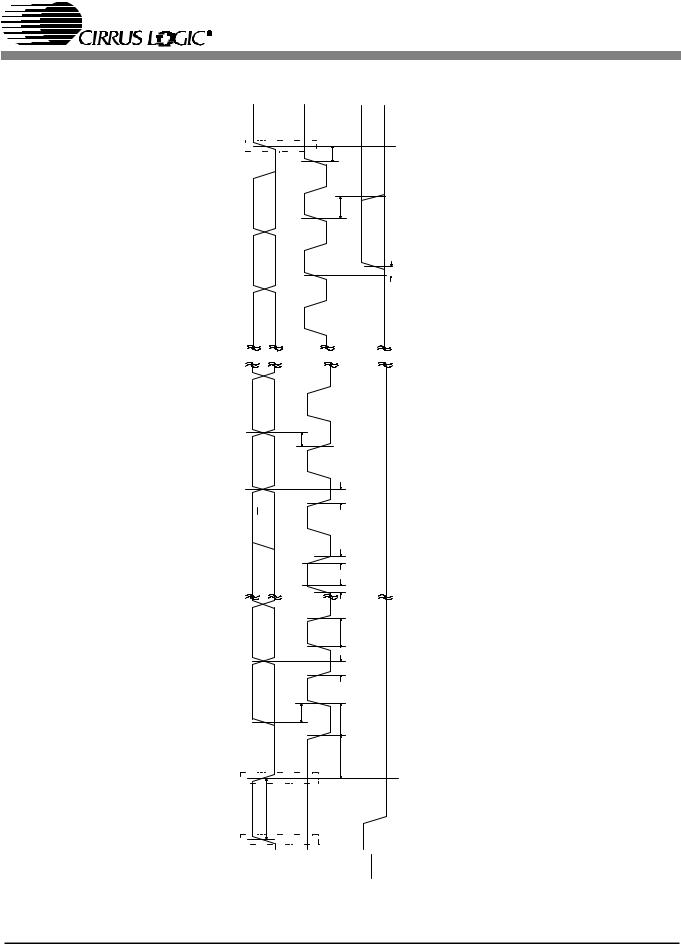

stop |

|

susp |

|

|

t |

ACK |

8 |

scrl |

|

|

t |

LSB |

7 |

scrh |

|

|

t |

|

MSB |

|

0 |

|

|

ACK |

scsdv |

|

|

|

t |

8 |

|

|

|

|

|

|

sca |

|

R/W |

|

|

t |

|

|

7 |

|

|

|

|

|

|

f |

|

|

|

|

t |

|

A0 |

|

6 |

|

|

|

|

|

r |

|

|

|

|

t |

|

A5 |

|

1 |

high |

|

|

t |

||

|

|

|

|

hdd |

|

|

|

|

t |

|

A6 |

sud |

0 |

|

|

|

|

low |

|

|

|

t |

|

|

|

|

|

|

t |

|

|

|

|

hdst |

start |

|

|

|

t |

|

|

|

|

|

|

|

buf |

|

|

|

|

t |

|

|

stop |

SCDIO |

|

SCCLK |

INTREQ |

Figure 8. I2C® Control Port Timing

DS339PP4 |

15 |

CS49300 Family DSP

1.11. Switching Characteristics — Digital Audio Input

(TA = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF)

Parameter |

|

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

|

SCLKN1(2) period for both Master and Slave mode |

(Note 1) |

Tsclki |

40 |

- |

ns |

SCLKN1(2) duty cycle for Master and Slave mode |

(Note 1) |

|

45 |

55 |

% |

|

|

|

|

|

|

Master Mode |

(Note 1, 2) |

|

|

|

|

|

|

|

|

|

|

LRCLKN1(2) delay after SCLKN1(2) transition |

(Note 3) |

Tlrds |

- |

10 |

ns |

SDATAN1(2) setup to SCLKN1(2) transition |

(Note 4) |

Tsdsum |

10 |

- |

ns |

SDATAN1(2) hold time after SCLKN1(2) transition |

(Note 4) |

Tsdhm |

5 |

- |

ns |

Slave Mode |

(Note 5) |

|

|

|

|

|

|

|

|

|

|

Time from active edge of SCLKN1(2) to LRCLKN1(2) transition |

Tstlr |

10 |

- |

ns |

|

Time from LRCLKN1(2) transition to SCLKN1(2) active edge |

|

Tlrts |

10 |

- |

ns |

SDATAN1(2) setup to SCLKN1(2) transition |

(Note 4) |

Tsdsus |

5 |

- |

ns |

SDATAN1(2) hold time after SCLKN1(2) transition |

(Note 4) |

Tsdhs |

5 |

- |

ns |

Notes: 1. Master mode timing specifications are characterized, not production tested.

2.Master mode is defined as the CS493XX driving LRCLKN1(2) and SCLKN1(2). Master or Slave mode can be programmed.

3.This timing parameter is defined from the non-active edge of SCLKN1(2). The active edge of SCLKN1(2) is the point at which the data is valid.

4.This timing parameter is defined from the active edge of SCLKN1(2). The active edge of SCLKN1(2) is the point at which the data is valid.

5.Slave mode is defined as SCLKN1(2) and LRCLKN1(2) being driven by an external source.

16 |

DS339PP4 |

CS49300 Family DSP

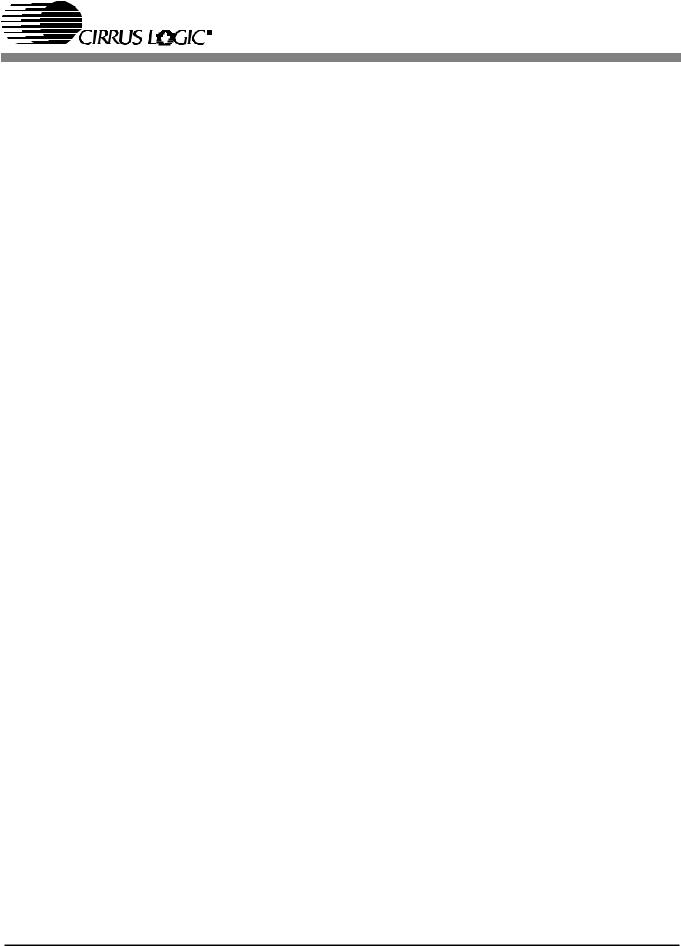

M ASTER M O DE

S C LK N 1

S C LK N 2

Tlrds |

Tsclki |

|

LR C LK N 1

LR C LK N 2

Tsdsum Tsdhm

S D A TA N 1

S D A TA N 2

SLAVE M O DE

S C LK N 1

S C LK N 2

Tsclki

Tlrts

Tstlr

Tstlr

LR C LK N 1

LR C LK N 2

Tsdsus Tsdhs

S D A TA N 1

S D A TA N 2

Figure 9. Digital Audio Input Data, Master and Slave Clock Timing

DS339PP4 |

17 |

CS49300 Family DSP

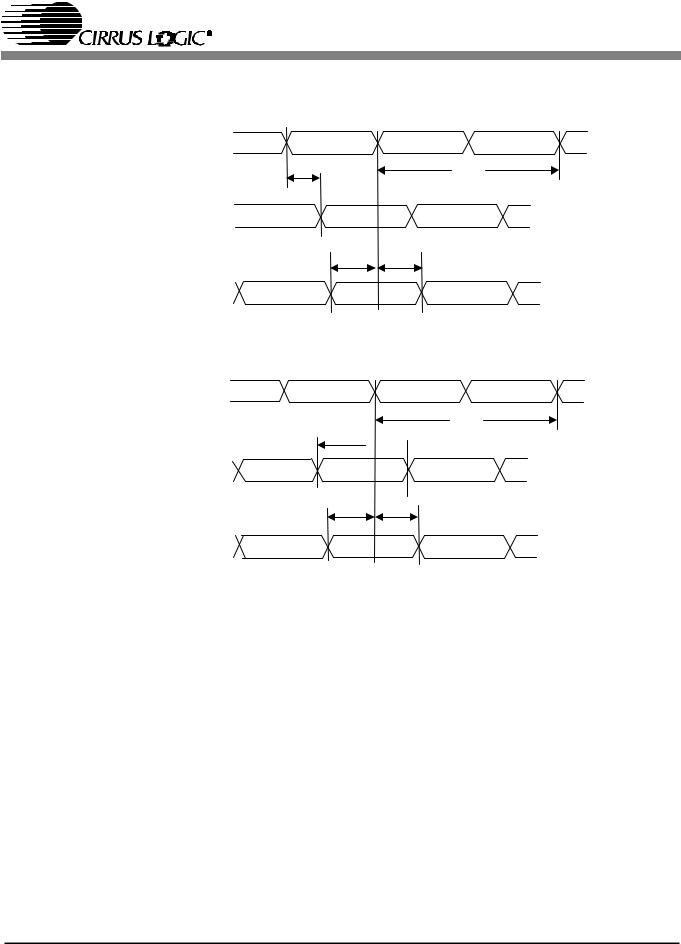

1.12. Switching Characteristics — CMPDAT, CMPCLK

(TA = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, CL = 20 pF)

Parameter |

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

Serial compressed data clock CMPCLK period |

Tcmpclk |

- |

27 |

MHz |

CMPDAT setup before CMPCLK high |

Tcmpsu |

5 |

- |

ns |

CMPDAT hold after CMPCLK high |

Tcmphld |

3 |

- |

ns |

CMPCLK

CMPDAT

Tcm ps u

Tcm p hld

Tcm p hld

Tcm p clk

Figure 10. Serial Compressed Data Timing