Cirrus Logic CS4207 User Manual

CS4207

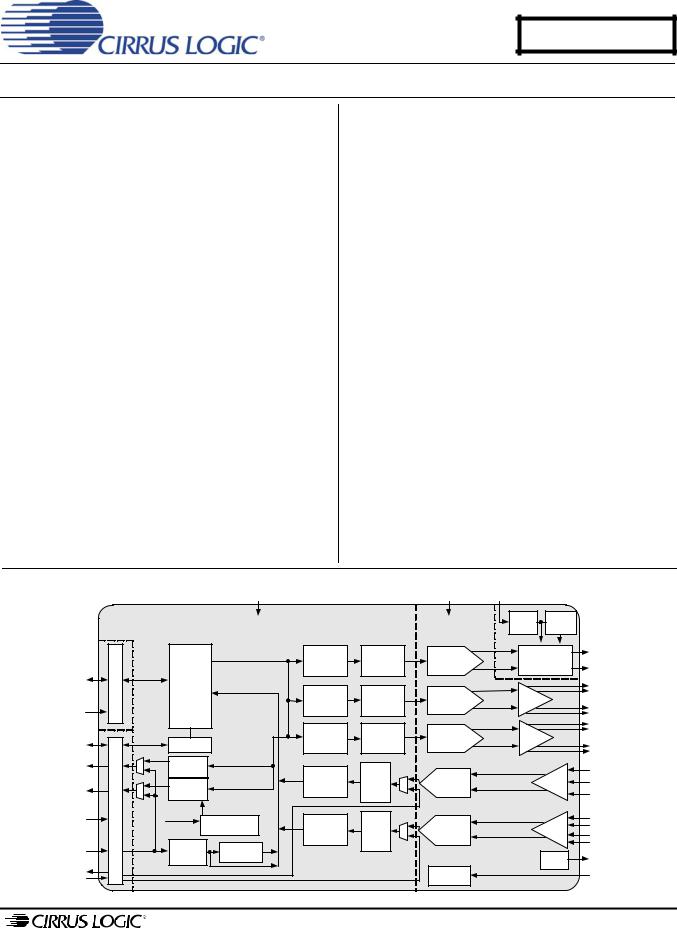

Low-power, 4-in / 6-out HD Audio Codec with Headphone Amp

DIGITAL to ANALOG FEATURES

DAC1 (Headphone)

–101 dB Dynamic Range (A-wtd)

–-89 dB THD+N

Headphone Amplifier - GND Centered

–Integrated Negative-voltage Regulator

–No DC-blocking Capacitor Required

–50 mW Power/Channel into 16

DAC2 & DAC3 (Line Outs)

–110 dB Dynamic Range (A-wtd)

–-94 dB THD+N

–Differential Balanced or Single-ended

Each DAC Supports 32 kHz to 192 kHz Sample Rates Independently.

Digital Volume Control

–+6.0 dB to -57.5 dB in 0.5 dB Steps

–Zero Cross and/or Soft Ramp Transitions

Independent Support of D0 and D3 Power States for Each DAC

Fast D3 to D0 Transition

–Audio Playback in Less Than 50 ms

ANALOG to DIGITAL FEATURES

ADC1 & ADC2

–105 dB Dynamic Range (A-wtd)

–-88 dB THD+N

–Differential Balanced or Single-ended Inputs

–Analog Programmable Gain Amplifier (PGA) ±12 dB, 1.0 dB Steps, with Zero Cross Transitions and Mute

MIC Inputs

–Pre-amplifier with Selectable 0 dB, +10 dB, +20 dB, and +30 dB Gain Settings

–Programmable, Low-noise MIC Bias Level

Each ADC Supports 8 kHz to 96 kHz Sample Rates Independently

Additional Digital Attenuation Control

–-13.0 dB to -51.0 dB in 1.0 dB steps

–Zero Cross and/or Soft Ramp Transitions

Digital Interface for Two Dual Digital Mic Inputs

Independent Support of D0 and D3 Power States for Each ADC

VD |

VA, VA_REF |

VA_HP |

(1.5 V to 1.8 V) |

(3.3 V to 5.0 V) |

(3.3 V to 5.0 V) |

|

|

|

|

|

|

|

Chrg |

|

|

|

|

|

|

|

|

|

Pump |

|

|

|

|

|

|

|

|

|

Buck |

|

|

|

|

|

|

|

SRC & |

|

+VHP |

-VHP |

|

|

Translator |

|

|

Vol/Mute |

2-Chnl |

|

|

Left HP Out |

|

Bus |

Interface |

SRC & |

Line |

|

- Left Line Out |

||||

2-Chnl |

|

||||||||

|

|

|

|

Multibit |

DAC1 |

|

|

Right HP Out |

|

HD Audio |

|

HD |

|

|

Modulator |

|

|

||

|

|

|

|

|

|

|

+ |

||

|

Audio |

|

|

|

|

|

|

||

(1.5 V to 3.3 V) |

Level |

|

|

Modulator |

|

|

|

||

|

|

Vol/Mute |

|

|

|

- Right Line Out |

|||

VL_HD |

|

|

|

Multibit |

DAC2 |

Out |

|

+ |

|

|

|

|

|

|

|

||||

|

|

|

|

|

SRC & |

2-Chnl |

Line |

|

+Left Line Out |

|

|

|

|

Vol/Mute |

Multibit |

|

- |

||

GPIO |

|

GPIO |

|

DAC3 |

Out |

|

+ |

||

|

|

|

Modulator |

|

|||||

|

|

SPDIF |

|

|

|

|

|

- Right Line Out |

|

S/PDIF OUT 2 |

|

|

|

|

|

|

|

+ |

|

|

TX 2 |

|

Vol/Boost/ |

Digital |

2-Chnl |

|

|

||

|

Translator |

SPDIF |

|

Filter & |

PGA |

- Line/Mic In L |

|||

|

|

Mute |

ADC1 |

Line/Mic In R |

|||||

VL_IF |

|

SRC |

|

|

|||||

Fs |

|

|

|

|

|

+ |

|||

S/PDIF OUT 1 |

|

TX 1 |

|

|

|

|

|

+ |

|

|

|

HD Bus |

128Fs Clock |

|

|

|

|

|

|

(3.3 V) |

Level |

|

Vol/Boost/ |

Digital |

2-Chnl |

|

|

- Mic/Line In L |

|

|

Multiplier |

PGA |

|||||||

|

|

Mute |

SRC |

ADC2 |

+Mic/Line In R |

||||

|

|

|

|

Filter & |

|

|

|||

S/PDIF IN |

|

SPDIF |

SPDIF |

|

|

|

MIC |

|

- |

|

RX |

RX SRC |

|

|

|

|

Mic Bias |

||

|

|

|

|

|

|

||||

D-Mic Clock |

|

|

|

|

|

Jack |

Bias |

|

|

|

|

|

|

|

|

|

SENSE_A |

||

D-Mic In |

|

|

|

|

|

Sense |

|

|

|

|

|

|

|

|

|

|

|

||

|

Copyright Cirrus Logic, Inc. 2012 |

AUG '12 |

http://www.cirrus.com |

(All Rights Reserved) |

DS880F4 |

|

CS4207

Digital Audio Interface Receiver

Complete EIAJ CP1201, IEC 60958, S/PDIF Compatible Receiver

32 kHz to 192 kHz Sample Rate Range

Automatic Detection of Compressed Audio Streams

Integrated Sample Rate Converter

–128 dB Dynamic Range

–-120 dB THD+N

–Supports Sample Rates up to 192 kHz

–1:1 Input/Output Sample Rate Ratios

Digital Audio Interface Transmitters

Two Independent EIAJ CP1201, IEC-60958, S/PDIF Compatible Transmitters

32 kHz to 192 kHz Sample Rate Range

System Features

Very Low D3 Power Dissipation of <7 mW

–Jack Detect Active in D3

–HDA BITCLK Not Required for D3 State

Jack Detect Does Not Require HDA Bus BITCLK

All Configuration Settings are Preserved in D3 State

Pop/Click Suppression in State Transitions

Detects Wake Event and Generates Power State Change Request when HDA Bus Controller is in D3

Variable Power Supplies

–1.5 V to 1.8 V Digital Core Voltage

–3.3 V to 5.0 V Analog Core Voltage

–3.3 V to 5.0 V Headphone Drivers

–1.5 V to 3.3 V HD Bus Interface Logic

–3.3 V Interface Logic levels for GPIO, S/PDIF, and Digital Mic

Individual Power-down Managed

–ADCs, DACs, PGAs, Headphone Driver, S/PDIF Receiver, and Transmitters

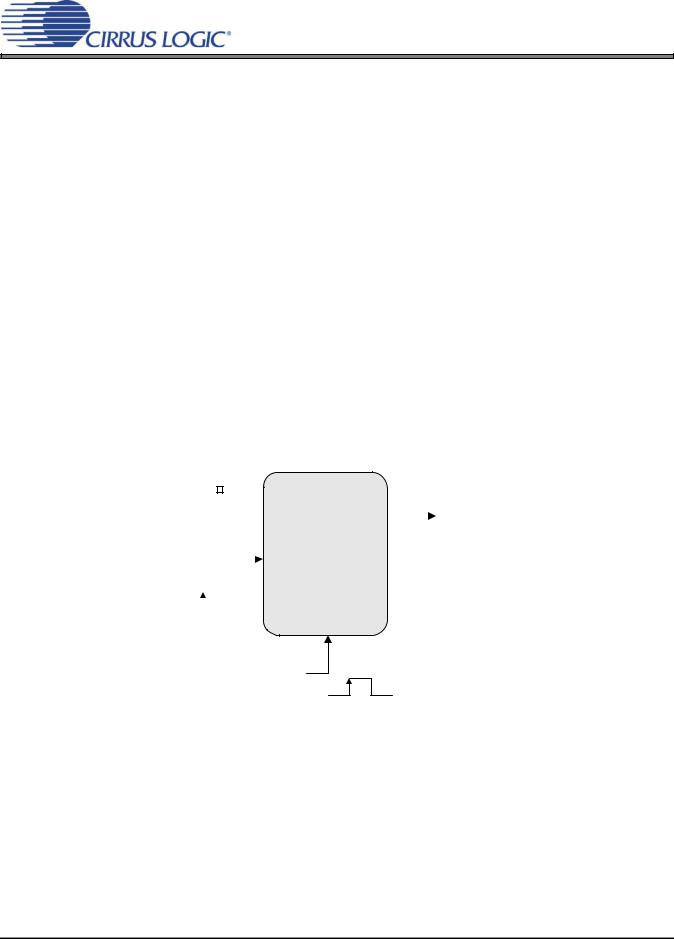

General Description

The CS4207 is a highly integrated multi-channel lowpower HD Audio Codec featuring 192 kHz DACs, 96 kHz ADCs, 192 kHz S/PDIF Transmitters and Receiver, Microphone pre-amp and bias voltage, and a ground centered Headphone driver. Based on multi-bit, delta-sigma modulation, it allows infinite sample rate adjustment between 32 kHz and 192 kHz.

The ADC input path allows control of a number of features. The microphone input path includes a selectable programmable-gain pre-amplifier stage and a low-noise MIC bias voltage supply. A PGA is available for line and microphone inputs and provides analog gain with soft ramp and zero cross transitions. The ADC also features an additional digital volume attenuator with soft ramp transitions.

The stereo headphone amplifier is powered from a separate internally generated positive supply, with an integrated charge pump providing a negative supply. This allows a ground-centered analog output with a wide signal swing and eliminates external DC-blocking capacitors.

The integrated digital audio interface receiver and transmitters utilize a 24-bit, high-performance, monolithic CMOS stereo asynchronous sample rate converter to clock align the PCM samples to/from the S/PDIF interfaces. Auto detection of non-PCM encoded data disables the sample rate conversion to preserve bit accuracy of the data.

In addition to its many features, the CS4207 operates from a low-voltage analog and digital core, making this part ideal for portable systems that require low power consumption in a minimal amount of space.

The CS4207 is available in a 48-pin WQFN package in both Automotive (-40°C to +105°C) and Commercial (-40°C to +85°C) grades. The CS4207 Customer Demonstration board is also available for device evaluation and implementation suggestions. Please refer to “Ordering Information” on p 147 for complete ordering information.

2 |

DS880F4 |

|

|

CS4207 |

TABLE OF CONTENTS |

|

|

1. PIN DESCRIPTIONS .............................................................................................................................. |

8 |

|

1.1 |

CS4207 48-pin QFN Pinout: ............................................................................................................ |

8 |

1.2 |

Digital I/O Pin Characteristics ........................................................................................................ |

10 |

2. TYPICAL CONNECTION DIAGRAMS ................................................................................................. |

11 |

|

3. CHARACTERISTICS AND SPECIFICATIONS .................................................................................... |

13 |

|

RECOMMENDED OPERATING CONDITIONS .................................................................................. |

13 |

|

ABSOLUTE MAXIMUM RATINGS ...................................................................................................... |

13 |

|

ANALOG INPUT CHARACTERISTICS (COMMERCIAL - CNZ) ......................................................... |

14 |

|

ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) ......................................................... |

15 |

|

ADC DIGITAL FILTER CHARACTERISTICS ...................................................................................... |

16 |

|

ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL - CNZ) ..................................................... |

17 |

|

ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) ..................................................... |

19 |

|

COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE ............................. |

21 |

|

DC ELECTRICAL CHARACTERISTICS .............................................................................................. |

21 |

|

DIGITAL MICROPHONE INTERFACE CHARACTERISTICS ............................................................. |

22 |

|

DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS .................................................... |

23 |

|

HD AUDIO BUS SPECIFICATIONS & CHARACTERISTICS .............................................................. |

23 |

|

S/PDIF TRANSMITTER/RECEIVER SPECIFICATIONS & CHARACTERISTICS .............................. |

23 |

|

POWER CONSUMPTION ................................................................................................................... |

24 |

|

4. CODEC RESET AND INITIALIZATION .............................................................................................. |

25 |

|

4.1 |

Link Reset ...................................................................................................................................... |

25 |

4.2 |

Function Group Reset .................................................................................................................... |

25 |

4.3 |

Codec Initialization ......................................................................................................................... |

25 |

4.4 |

D3 Lower Power State Support ..................................................................................................... |

26 |

4.5 |

Extended Power States Supported (EPSS) ................................................................................... |

26 |

4.6 |

Power State Settings Reset (PS-SettingsReset) ........................................................................... |

28 |

4.7 |

Register Settings Across Resets ................................................................................................... |

29 |

5. PRESENCE DETECTION ..................................................................................................................... |

31 |

|

5.1 |

Jack Detection Circuit .................................................................................................................... |

31 |

|

5.1.1 Presence Detection and Unsolicited Response .................................................................... |

31 |

|

5.1.2 S/PDIF Receiver Presence Detect ........................................................................................ |

32 |

6. HD AUDIO CODEC SUPPORTED VERBS AND RESPONSES ......................................................... |

33 |

|

6.1 |

Software Programming Model ....................................................................................................... |

33 |

|

6.1.1 Node ID Summary ................................................................................................................. |

34 |

|

6.1.2 Pin Configuration Register Defaults ...................................................................................... |

35 |

6.2 |

Root Node (Node ID = 00h) ........................................................................................................... |

36 |

|

6.2.1 Vendor and Device ID ........................................................................................................... |

36 |

|

6.2.2 Revision ID ............................................................................................................................ |

36 |

|

6.2.3 Subordinate Node Count ....................................................................................................... |

36 |

6.3 |

Audio Function Group (Node ID = 01h) ......................................................................................... |

37 |

|

6.3.1 Subordinate Node Count ....................................................................................................... |

37 |

|

6.3.2 Function Group Type ............................................................................................................. |

37 |

|

6.3.3 Audio Function Group Capabilities ........................................................................................ |

37 |

|

6.3.4 Supported PCM Size, Rates ............................................................................................... |

.. 38 |

|

6.3.5 Supported Stream Formats ................................................................................................... |

39 |

|

6.3.6 Supported Power States ....................................................................................................... |

39 |

|

6.3.7 GPIO Capabilities .................................................................................................................. |

40 |

|

6.3.8 Power States ......................................................................................................................... |

41 |

|

6.3.9 GPIO Data ............................................................................................................................. |

42 |

|

6.3.10 GPIO Enable Mask .............................................................................................................. |

43 |

|

6.3.11 GPIO Direction .................................................................................................................... |

43 |

|

6.3.12 GPIO Sticky Mask ............................................................................................................... |

43 |

DS880F4 |

|

3 |

|

CS4207 |

|

6.3.13 Implementation Identification ............................................................................................... |

|

44 |

6.3.14 Function Reset .................................................................................................................... |

|

44 |

6.4 DAC1, DAC2, DAC3 Output Converter Widgets (Node ID = 02h, 03h, 04h) ................................. |

|

45 |

6.4.1 Audio Widget Capabilities ..................................................................................................... |

|

45 |

6.4.2 Supported PCM Size, Rates ................................................................................................. |

|

46 |

6.4.3 Supported Stream Formats ................................................................................................... |

|

46 |

6.4.4 Supported Power States ....................................................................................................... |

|

47 |

6.4.5 Output Amplifier Capabilities ................................................................................................. |

|

47 |

6.4.6 Power States ......................................................................................................................... |

|

48 |

6.4.7 Converter Stream, Channel ................................................................................................... |

|

49 |

6.4.8 Converter Format .................................................................................................................. |

|

49 |

6.4.9 Amplifier Gain/Mute ............................................................................................................... |

|

51 |

6.5 ADC1, ADC2 Input Converter Widgets (Node ID = 05h, 06h) ....................................................... |

|

53 |

6.5.1 Audio Widget Capabilities ..................................................................................................... |

|

53 |

6.5.2 Supported PCM Size, Rates ................................................................................................. |

|

54 |

6.5.3 Supported Stream Formats ................................................................................................... |

|

54 |

6.5.4 Input Amplifier Capabilities .................................................................................................... |

|

55 |

6.5.5 Connection List Length .......................................................................................................... |

|

55 |

6.5.6 Supported Power States ....................................................................................................... |

|

56 |

6.5.7 ADC1 Connection List Entry .................................................................................................. |

|

56 |

6.5.8 ADC1 Connection Select Control .......................................................................................... |

|

56 |

6.5.9 ADC2 Connection List Entry .................................................................................................. |

|

57 |

6.5.10 ADC2 Connection Select Control ........................................................................................ |

|

57 |

6.5.11 Power States ....................................................................................................................... |

|

58 |

6.5.12 Converter Stream, Channel ................................................................................................. |

|

59 |

6.5.13 Converter Format ................................................................................................................ |

|

59 |

6.5.14 Amplifier Gain/Mute ............................................................................................................. |

|

61 |

6.6 S/PDIF Receiver Input Converter Widget (Node ID = 07h) ........................................................... |

|

63 |

6.6.1 Audio Widget Capabilities ..................................................................................................... |

|

63 |

6.6.2 Supported PCM Size, Rates ................................................................................................. |

|

64 |

6.6.3 Supported Stream Formats ................................................................................................... |

|

64 |

6.6.4 Connection List Length .......................................................................................................... |

|

65 |

6.6.5 Supported Power States ....................................................................................................... |

|

65 |

6.6.6 Connection List Entry ............................................................................................................ |

|

65 |

6.6.7 Power States ......................................................................................................................... |

|

66 |

6.6.8 Converter Stream, Channel ................................................................................................... |

|

67 |

6.6.9 Converter Format .................................................................................................................. |

|

67 |

6.6.10 Digital Converter Control ..................................................................................................... |

|

69 |

6.7 S/PDIF Transmitter 1, S/PDIF Transmitter 2 Output Converter Widgets (Node ID = 08h, 14h) .... |

70 |

|

6.7.1 Audio Widget Capabilities ..................................................................................................... |

|

70 |

6.7.2 Supported PCM Size, Rates ................................................................................................. |

|

71 |

6.7.3 Supported Stream Formats ................................................................................................... |

|

72 |

6.7.4 Supported Power States ....................................................................................................... |

|

72 |

6.7.5 Power States ......................................................................................................................... |

|

72 |

6.7.6 Converter Stream, Channel ................................................................................................... |

|

74 |

6.7.7 Converter Format .................................................................................................................. |

|

74 |

6.7.8 Digital Converter Control ....................................................................................................... |

|

76 |

6.8 Headphone Pin Widget (Node ID = 09h) ....................................................................................... |

|

78 |

6.8.1 Audio Widget Capabilities .................................................................................................. |

... |

78 |

6.8.2 Pin Capabilities ...................................................................................................................... |

|

78 |

6.8.3 Connection List Length .......................................................................................................... |

|

79 |

6.8.4 Supported Power States ....................................................................................................... |

|

79 |

6.8.5 Connection List Entry ............................................................................................................ |

|

80 |

6.8.6 Power States ......................................................................................................................... |

|

80 |

4 |

DS880F4 |

|

|

CS4207 |

6.8.7 Pin Widget Control ................................................................................................................ |

81 |

6.8.8 Unsolicited Response Control ............................................................................................... |

82 |

6.8.9 Pin Sense .............................................................................................................................. |

83 |

6.8.10 Configuration Default ........................................................................................................... |

83 |

6.9 Line Out 1 Pin Widget (Node ID = 0Ah) ......................................................................................... |

85 |

6.9.1 Audio Widget Capabilities ..................................................................................................... |

85 |

6.9.2 Pin Capabilities ...................................................................................................................... |

86 |

6.9.3 Connection List Length .......................................................................................................... |

86 |

6.9.4 Supported Power States ....................................................................................................... |

87 |

6.9.5 Connection List Entry ............................................................................................................ |

87 |

6.9.6 Power States ......................................................................................................................... |

87 |

6.9.7 Pin Widget Control ................................................................................................................ |

88 |

6.9.8 Unsolicited Response Control ............................................................................................... |

89 |

6.9.9 Pin Sense .............................................................................................................................. |

90 |

6.9.10 EAPD/BTL Enable ............................................................................................................... |

90 |

6.9.11 Configuration Default ........................................................................................................... |

91 |

6.10 Line Out 2 Pin Widget (Node ID = 0Bh) ....................................................................................... |

92 |

6.10.1 Audio Widget Capabilities ................................................................................................... |

92 |

6.10.2 Pin Capabilities .................................................................................................................... |

93 |

6.10.3 Connection List Length ........................................................................................................ |

93 |

6.10.4 Connection List Entry .......................................................................................................... |

94 |

6.10.5 Pin Widget Control .............................................................................................................. |

94 |

6.10.6 EAPD/BTL Enable ............................................................................................................... |

95 |

6.10.7 Configuration Default ........................................................................................................... |

96 |

6.11 Line In 1/Mic In 2, Mic In 1/Line In 2 Pin Widgets (Node ID = 0Ch, 0Dh) .................................... |

97 |

6.11.1 Audio Widget Capabilities ................................................................................................... |

97 |

6.11.2 Line In 1/Mic In 2 Pin Capabilities ....................................................................................... |

97 |

6.11.3 Mic In 1/Line In 2 Pin Capabilities ....................................................................................... |

98 |

6.11.4 Input Amplifier Capabilities .................................................................................................. |

99 |

6.11.5 Supported Power States ..................................................................................................... |

99 |

6.11.6 Power States ....................................................................................................................... |

99 |

6.11.7 Line In 1/Mic In 2 Pin Widget Control ................................................................................ |

101 |

6.11.8 Mic In 1/Line In 2 Pin Widget Control ................................................................................ |

101 |

6.11.9 Unsolicited Response Control ........................................................................................... |

102 |

6.11.10 Pin Sense ........................................................................................................................ |

103 |

6.11.11 Mic In 1/Line In 2 EAPD/BTL Enable .............................................................................. |

104 |

6.11.12 Line In 1/Mic In 2 Configuration Default .......................................................................... |

104 |

6.11.13 Mic In 1/Line In 2 Configuration Default .......................................................................... |

105 |

6.11.14 Amplifier Gain/Mute ......................................................................................................... |

106 |

6.12 Digital Mic In 1, Digital Mic In 2 Pin Widgets (Node ID = 0Eh, 12h) ........................................... |

108 |

6.12.1 Audio Widget Capabilities ................................................................................................. |

108 |

6.12.2 Pin Capabilities .................................................................................................................. |

109 |

6.12.3 Input Amplifier Capabilities ................................................................................................ |

109 |

6.12.4 Pin Widget Control ............................................................................................................ |

110 |

6.12.5 Digital Mic In 1 Configuration Default ................................................................................ |

110 |

6.12.6 Digital Mic In 2 Configuration Default ................................................................................ |

111 |

6.12.7 Amplifier Gain/Mute ........................................................................................................... |

112 |

6.13 S/PDIF Receiver Input Pin Widget (Node ID = 0Fh) .................................................................. |

114 |

6.13.1 Audio Widget Capabilities ................................................................................................. |

114 |

6.13.2 Pin Capabilities .................................................................................................................. |

115 |

6.13.3 Supported Power States ................................................................................................... |

115 |

6.13.4 Power States ..................................................................................................................... |

116 |

6.13.5 Pin Widget Control ............................................................................................................ |

117 |

6.13.6 Unsolicited Response Control ........................................................................................... |

117 |

DS880F4 |

5 |

|

CS4207 |

6.13.7 Pin Sense .......................................................................................................................... |

118 |

6.13.8 Configuration Default ......................................................................................................... |

119 |

6.14 S/PDIF Transmitter 1, S/PDIF Transmitter 2 Output Pin Widgets (Node ID = 10h, 15h) |

........... 120 |

6.14.1 Audio Widget Capabilities ................................................................................................. |

120 |

6.14.2 Pin Capabilities .................................................................................................................. |

121 |

6.14.3 Connection List Length ...................................................................................................... |

121 |

6.14.4 S/PDIF Transmitter 1 Connection List Entry ..................................................................... |

122 |

6.14.5 S/PDIF Transmitter 2 Connection List Entry ..................................................................... |

122 |

6.14.6 Pin Widget Control ............................................................................................................ |

123 |

6.14.7 S/PDIF Transmitter 1 Configuration Default ...................................................................... |

124 |

6.14.8 S/PDIF Transmitter 2 Configuration Default ...................................................................... |

125 |

6.15 Vendor Processing Widget (Node ID = 11h) .............................................................................. |

126 |

6.15.1 Audio Widget Capabilities ................................................................................................. |

126 |

6.15.2 Processing Capabilities ..................................................................................................... |

126 |

6.15.3 Processing State ............................................................................................................... |

127 |

6.15.4 Coefficient Index ................................................................................................................ |

127 |

6.15.5 Processing Coefficient ....................................................................................................... |

128 |

6.15.6 Coefficient Registers ......................................................................................................... |

128 |

6.15.6.1 S/PDIF RX/TX Interface Status (CIR = 0000h) ...................................................... |

129 |

6.15.6.2 S/PDIF RX/TX Interface Control (CIR = 0001h) .................................................... |

130 |

6.15.6.3 ADC Configuration (CIR = 0002h) ......................................................................... |

131 |

6.15.6.4 DAC Configuration (CIR = 0003h) ......................................................................... |

134 |

6.15.6.5 Beep Configuration (CIR = 0004h) ........................................................................ |

135 |

6.16 Beep Generator Widget (Node ID = 13h) .................................................................................. |

136 |

6.16.1 Audio Widget Capabilities ................................................................................................. |

136 |

6.16.2 Beep Generation Control ................................................................................................... |

137 |

7. APPLICATIONS ................................................................................................................................. |

138 |

7.1 HD Audio Interface ....................................................................................................................... |

138 |

7.1.1 Multi-Channel Streams ........................................................................................................ |

138 |

7.2 Analog Inputs ............................................................................................................................... |

139 |

7.3 Analog Outputs ............................................................................................................................ |

142 |

7.3.1 Output Filter ......................................................................................................................... |

142 |

7.3.2 Analog Supply Removal ...................................................................................................... |

142 |

7.4 Digital Mic Inputs .......................................................................................................................... |

142 |

7.5 S/PDIF Input and Outputs ............................................................................................................ |

143 |

7.5.1 S/PDIF Receiver SRC ......................................................................................................... |

143 |

8. PCB LAYOUT CONSIDERATIONS ................................................................................................... |

144 |

8.1 Power Supply, Grounding ............................................................................................................ |

144 |

8.2 QFN Thermal Pad ........................................................................................................................ |

144 |

9. PARAMETER DEFINITIONS .............................................................................................................. |

145 |

10. QFN PACKAGE DIMENSIONS ........................................................................................................ |

146 |

THERMAL CHARACTERISTICS ....................................................................................................... |

146 |

11. ORDERING INFORMATION ............................................................................................................ |

147 |

12. REFERENCES .................................................................................................................................. |

147 |

13. REVISION HISTORY ........................................................................................................................ |

148 |

6 |

DS880F4 |

|

CS4207 |

LIST OF FIGURES |

|

Figure 1.Typical Connection Diagram - Desktop System ......................................................................... |

11 |

Figure 2.Typical Connection Diagram - Portable System ......................................................................... |

12 |

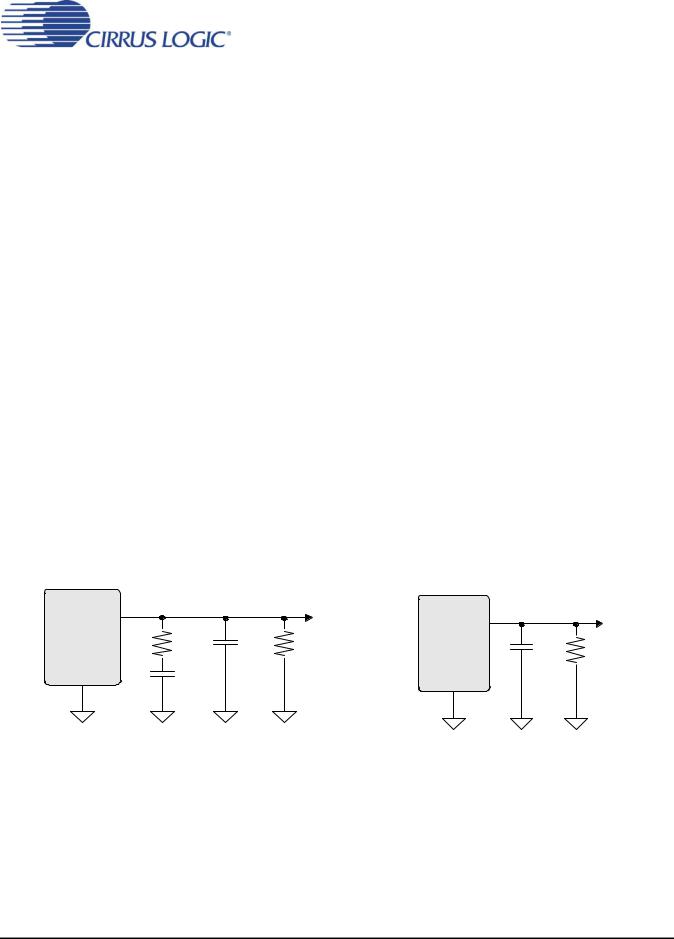

Figure 3.Output Test Load, Headphone Out ............................................................................................. |

18 |

Figure 4.Output Test Load, Line Out ......................................................................................................... |

18 |

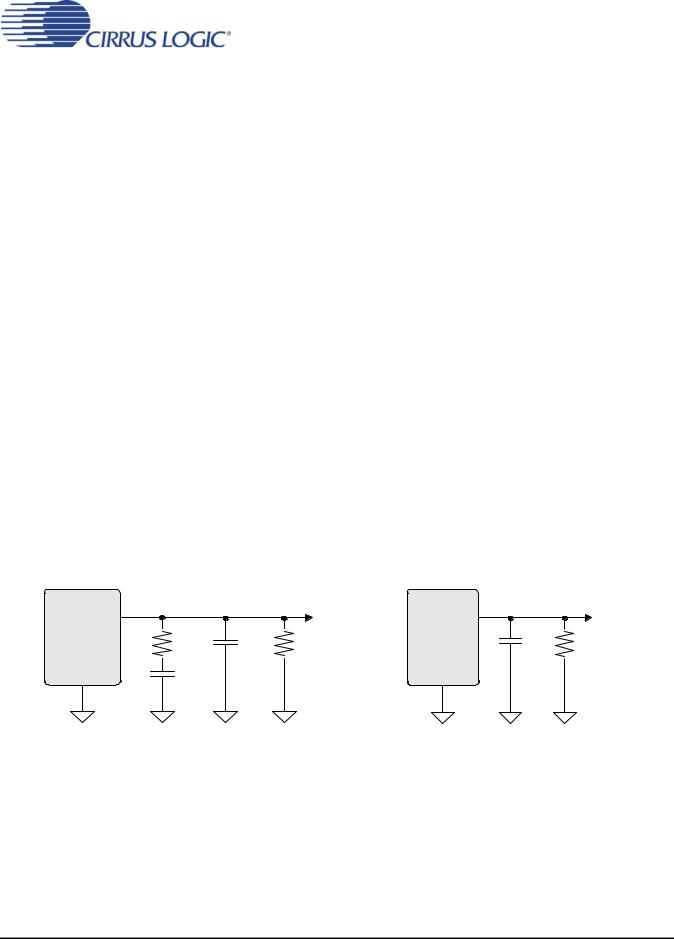

Figure 5.Output Test Load, Headphone Out ............................................................................................. |

20 |

Figure 6.Output Test Load, Line Out ......................................................................................................... |

20 |

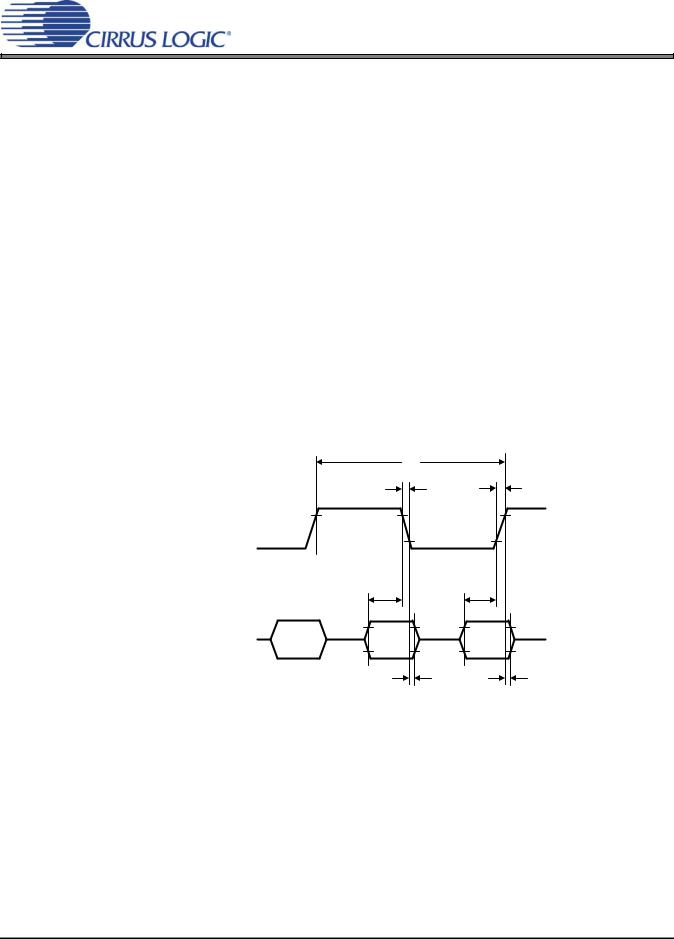

Figure 7.Digital MIC Interface Timing ........................................................................................................ |

22 |

Figure 8.PS-SettingsReset Behavior ........................................................................................................ |

28 |

Figure 9.Jack Presence Detect Circuit ...................................................................................................... |

31 |

Figure 10.Software Programming Model .................................................................................................. |

33 |

Figure 11.Single-Ended Input Filter ........................................................................................................ |

139 |

Figure 12.Pseudo-Differential Input Filter ............................................................................................... |

140 |

Figure 13.Differential Input Filter ............................................................................................................. |

141 |

Figure 14.Differential to Single-Ended Output Filter ............................................................................... |

142 |

Figure 15.Passive Single-Ended Output Filter ........................................................................................ |

142 |

LIST OF TABLES |

|

Table 1. Register Settings Across Reset Conditions ................................................................................ |

29 |

Table 2. Device Node ID Summary ........................................................................................................... |

34 |

Table 3. Pin Configuration Register Defaults ............................................................................................ |

35 |

Table 4. Stream Format Examples ......................................................................................................... |

138 |

Table 5. Line In 1/Mic In 2 Input Topology Register Settings .................................................................. |

139 |

Table 6. Mic In 1/Line In 2 Input Topology Register Settings .................................................................. |

139 |

DS880F4 |

7 |

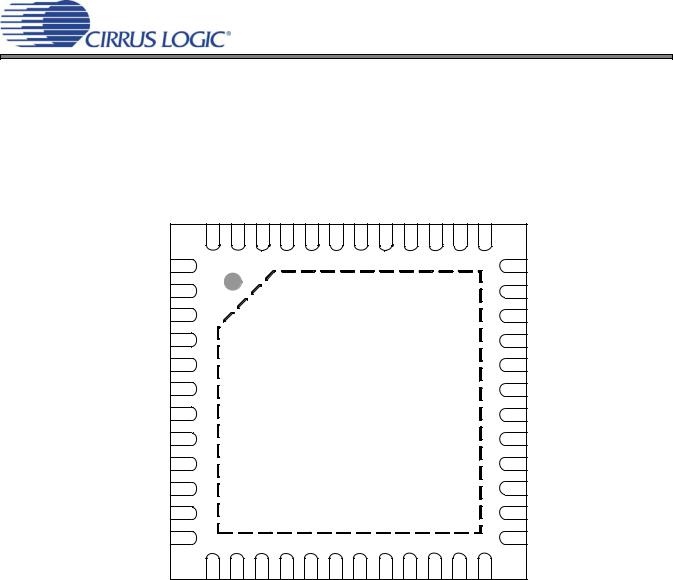

CS4207

1. PIN DESCRIPTIONS

1.1 CS4207 48-pin QFN Pinout: |

|

|

|

|

|

|

|

|

|

|

||||

|

|

SPDIF OUT1 |

SPDIF IN |

VA HP |

FLYP |

VHP FILT+ |

FLYC |

FLYN |

VHP FILT- |

HPOUT R |

HPREF |

HPOUT L |

LINEOUT R1- |

|

|

|

48 |

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 |

39 |

38 |

37 |

|

VL_IF |

1 |

|

|

|

|

|

|

|

|

|

|

|

36 |

LINEOUT_R1+ |

GPIO0/DMIC_SDA1 |

2 |

|

|

|

|

|

|

|

|

|

|

|

35 |

LINEOUT_L1+ |

VL_HD |

3 |

|

|

|

|

|

|

|

|

|

|

|

34 |

LINEOUT_L1- |

DMIC_SCL |

4 |

|

|

|

|

|

|

|

|

|

|

|

33 |

LINEOUT_R2- |

SDO |

5 |

|

|

|

|

|

|

|

|

|

|

|

32 |

LINEOUT_R2+ |

BITCLK |

6 |

|

|

|

|

|

Thermal Pad |

|

|

|

31 |

LINEOUT_L2+ |

||

DGND |

|

|

|

|

|

|

|

|

|

|

LINEOUT_L2- |

|||

7 |

|

|

|

|

|

HPGND |

|

|

|

|

30 |

|||

SDI |

8 |

|

|

|

|

|

|

|

|

|

|

|

29 |

VBIAS (DAC) |

VD |

9 |

|

|

|

|

|

|

|

|

|

|

|

28 |

VCOM |

SYNC |

10 |

|

|

|

|

|

|

|

|

|

|

|

27 |

VREF+ (ADC) |

RESET# |

11 |

|

|

|

Top-Down (Through Package) View |

|

|

26 |

AGND |

|||||

|

|

|

|

|

|

48-Pin QFN Package |

|

|

|

|

VA |

|||

GPIO1/DMIC_SDA2 |

12 |

HPREF |

|

|

|

|

|

|

|

|

|

|

25 |

|

/SPDIF_OUT2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

|

|

|

|

13 |

|

|||||||||||

|

|

SENSE A |

GPIO2 |

GPIO3 |

MICBIAS |

MICIN L- |

MICIN L+ |

MICIN R+ |

MICIN R- |

LINEIN L+ |

LINEIN C- |

LINEIN R+ |

VA REF |

|

Pin Name |

QFN |

Pin Description |

|

|

VL_IF |

1 |

Digital Interface Signal Level (Input) - Digital supply for the GPIO, S/PDIF and Digital Mic inter- |

|

|

faces. Refer to the Recommended Operating Conditions for appropriate voltages. |

||||

|

|

|||

|

|

|

||

GPIO0/ |

2 |

General Purpose I/O (Input/Output) - General purpose input or output line, or |

|

|

DMIC_SDA1 |

Digital Mic Data Input (Input) - The first data input line from a digital microphone. |

|||

|

||||

VL_HD |

3 |

Digital Interface Signal Level (Input) - Digital supply for the HD Audio interface. Refer to the |

|

|

Recommended Operating Conditions for appropriate voltages. |

||||

|

|

|||

DMIC_SCL |

4 |

Digital Mic Clock (Output) - The high speed clock output to the digital microphone. |

|

|

SDO |

5 |

Serial Data Input (Input) - Serial data input stream from the HD Audio Bus. |

|

|

|

|

|

||

BITCLK |

6 |

Bit Clock (Input) - 24 MHz bit clock from the HD Audio Bus. |

|

|

DGND |

7 |

Digital Ground (Input) - Ground reference for the internal digital section. |

|

|

SDI |

8 |

Serial Data Output (Input/Output) - Serial data output stream to the HD Audio Bus. |

|

|

|

|

|

||

VD |

9 |

Digital Power (Input) - Positive power for the internal digital section. |

|

|

SYNC |

10 |

Sync Clock (Input) - 48 kHz sync clock from the HD Audio Bus. |

|

|

|

|

|

|

|

8 |

|

DS880F4 |

||

|

|

|

CS4207 |

|

|

|

|

|

|

|

|

|

|

|

|

Pin Name |

QFN |

Pin Description |

|

|

|

|

|

|

|

RESET# |

11 |

Reset (Input) - The device enters a low power mode when this pin is driven low. |

|

|

|

|

|

|

|

GPIO1/ |

|

General Purpose I/O (Input/Output) - General purpose input or output line, or |

|

|

DMIC_SDA2/ |

12 |

Digital Mic Data Input (Input) - The second data input line from a digital microphone, or |

|

|

SPDIF_OUT2 |

|

S/PDIF Output (Output) - Output from internal S/PDIF Transmitter. |

|

|

SENSE_A |

13 |

Jack Sense Pin (Input/Output) - Jack sense detect. |

|

|

|

|

|

|

|

GPIO2 |

14 |

General Purpose I/O (Input/Output) - General purpose input or output lines. |

|

|

|

|

|

|

|

GPIO3 |

15 |

General Purpose I/O (Input/Output) - General purpose input or output lines. |

|

|

MICBIAS |

16 |

Microphone Bias (Output) - Provides a low noise bias supply for an external microphone. Elec- |

|

|

trical characteristics are specified in the DC Electrical Characteristics table. |

|||

|

|

|

||

|

|

|

|

|

|

MICIN_L- |

17 |

Microphone Input Left/Right (Input) - The full-scale level is specified in the ADC Analog Char- |

|

|

MICIN_L+ |

18 |

||

|

MICIN_R+ |

19 |

acteristics specification table. |

|

|

MICIN_R- |

20 |

|

|

|

|

|

|

|

|

LINEIN_L+ |

21 |

Analog Input (Input) - The full-scale level is specified in the ADC Analog Characteristics specifi- |

|

|

LINEIN_C- |

22 |

||

|

cation table. |

|||

|

LINEIN_R+ |

23 |

||

|

|

|

||

|

|

|

|

|

|

VA_REF |

24 |

Analog Power (Input) - Positive power for the internal analog section. VA_REF is the return pin |

|

|

VA |

25 |

for the VBIAS cap. |

|

|

|

|

|

|

|

AGND |

26 |

Analog Ground (Input) - Ground reference for the internal analog section. |

|

|

VREF+ |

27 |

Positive Voltage Reference (Output) - Positive reference voltage for the internal ADCs. |

|

|

|

|

|

|

|

VCOM |

28 |

Quiescent Voltage (Output) - Filter connection for internal quiescent voltage. |

|

|

|

|

|

|

|

VBIAS |

29 |

Positive Voltage Reference (Output) - Positive reference voltage for the internal DACs. |

|

|

LINEOUT_L2- |

30 |

|

|

|

LINEOUT_L2+ |

31 |

|

|

|

LINEOUT_R2+ |

32 |

Analog Audio Output (Output) - The full-scale output level is specified in the DAC Analog Char- |

|

|

LINEOUT_R2- |

33 |

||

|

LINEOUT_L1- |

34 |

acteristics specification table |

|

|

LINEOUT_L1+ |

35 |

|

|

|

LINEOUT_R1+ |

36 |

|

|

|

LINEOUT_R137 |

|

|

|

|

|

|

|

|

|

HPOUT_L |

38 |

Analog Headphone Output (Output) - The full-scale output level is specified in the DAC Analog |

|

|

HPOUT_R |

40 |

Characteristics specification table. |

|

|

|

|

|

|

|

HPREF |

39 |

Pseudo Diff. Headphone Reference (Input) - Ground reference for the headphone amplifiers. |

|

|

|

|

|

|

|

VHP_FILT- |

41 |

Inverting Charge Pump Filter Connection (Output) - Power supply from the inverting charge |

|

|

pump that provides the negative rail for the headphone amplifier. |

|||

|

|

|

||

|

|

|

|

|

|

FLYN |

42 |

Charge Pump Cap Negative Node (Output) - Negative node for the inverting charge pump’s fly- |

|

|

ing capacitor. |

|||

|

|

|

||

|

FLYC |

43 |

Charge Pump Cap Common Node (Output) - Common positive node for the step-down and |

|

|

inverting charge pumps’ flying capacitor. |

|||

|

|

|

||

|

|

|

|

|

|

VHP_FILT+ |

44 |

Non-Inverting Charge Pump Filter Connection (Output) - Power supply from the step-down |

|

|

charge pump that provides the positive rail for the headphone amplifier. |

|||

|

|

|

||

|

|

|

|

|

|

FLYP |

45 |

Charge Pump Cap Positive Node (Output) - Positive node for the step-down charge pump’s fly- |

|

|

ing capacitor. |

|||

|

|

|

||

|

VA_HP |

46 |

Analog Power For Headphone (Input) - Positive power for the internal analog headphone sec- |

|

|

tion. |

|||

|

|

|

||

|

|

|

|

|

|

SPDIF_IN |

47 |

S/PDIF Input (Input) - Input to internal S/PDIF Receiver. |

|

|

SPDIF_OUT1 |

48 |

S/PDIF Output (Output) - Output from internal S/PDIF Transmitter. |

|

|

HPGND |

TP |

HP Ground (Input) - Ground reference for the internal headphone section. See “QFN Thermal |

|

|

Pad” on page 144 for more information. |

|||

|

|

|

||

|

|

|

|

|

DS880F4 |

|

9 |

|

|

CS4207

1.2Digital I/O Pin Characteristics

Input and output levels and associated power supply voltage are shown in the table below. Logic levels should not exceed the corresponding power supply voltage.

Power |

Pin Name |

I/O |

Driver |

Receiver |

|

Supply |

SW/(HW) |

||||

|

|

|

|||

|

RESET# |

Input |

- |

1.5 V - 3.3 V |

|

|

SDO |

Input |

- |

1.5 V - 3.3 V |

|

VL_HD |

BITCLK |

Input |

- |

1.5 V - 3.3 V |

|

|

SDI (Note 1) |

Input/Output |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

|

|

SYNC |

Input |

- |

1.5 V - 3.3 V |

|

VA |

SENSE_A |

Input |

- |

3.3 V - 5.0 V |

|

|

GPIO1/ |

Input/Output |

3.3 V |

3.3 V |

|

|

DMIC_SDA2 |

||||

|

|

|

|

||

|

GPIO2 |

Input/Output |

3.3 V |

3.3 V |

|

|

GPIO3 |

Input/Output |

3.3 V |

3.3 V |

|

VL_IF |

SPDIF_IN |

Input |

- |

3.3 V |

|

|

SPDIF_OUT |

Output |

3.3 V |

- |

|

|

GPIO0/ |

Input/Output |

3.3 V |

3.3 V |

|

|

DMIC_SDA1 |

||||

|

|

|

|

||

|

DMIC_SCL |

Output |

3.3 V |

- |

Notes:

1. SDI output functionality also requires the VA and VL_IF rails to be at nominal levels.

10 |

DS880F4 |

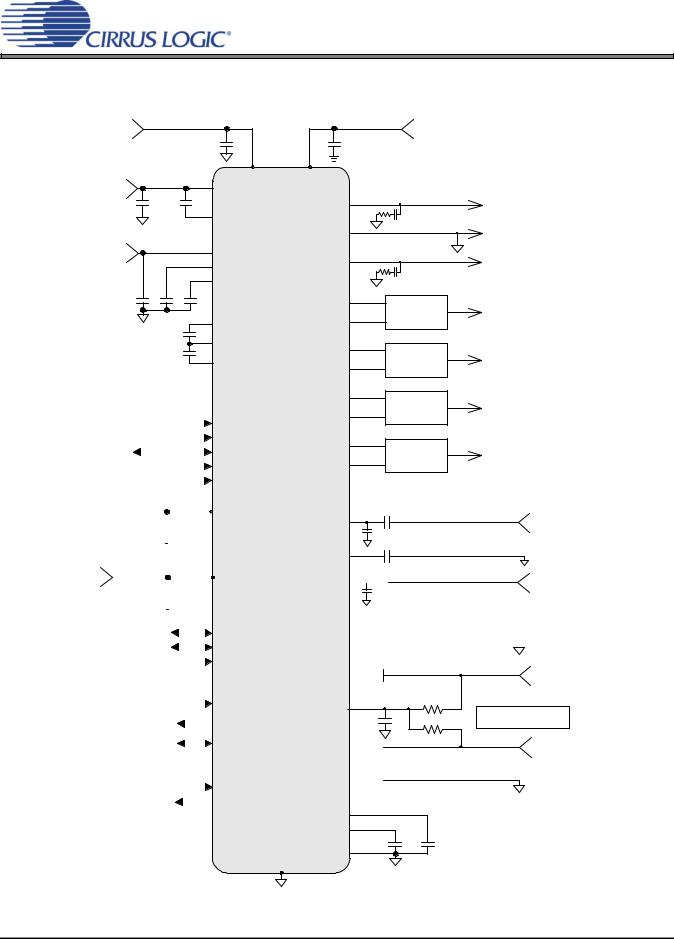

CS4207

2. TYPICAL CONNECTION DIAGRAMS

+5.0 V |

|

0.1 µF |

0.1 µF |

|

|

+1.8 V |

|

|

|

|

|

|

|

|

|

||

|

|

|

VA |

VD |

|

|

|

|

+5.0 V |

0.1 µF |

+ |

VA_REF |

|

|

|

|

|

|

10 µF |

|

|

|

|

Left Headphone |

||

|

|

|

|

HPOUT_L |

33 |

|

|

|

|

|

|

VBIAS |

0.1 µF |

|

|||

|

|

|

|

|

||||

+5.0 V |

|

|

CS4207 HPREF |

|

|

|

Headphone Ground |

|

|

|

VA_HP |

HPOUT_R |

|

|

|

Right Headphone |

|

|

|

|

VHP_FILT+ |

|

|

|

||

|

|

|

|

33 |

0.1 µF |

|

||

|

|

|

VHP_FILT- |

|

|

|||

|

** |

** |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

0.1 µF 10 µF |

10 µF |

LINEOUT_L1+ |

|

|

Differential to |

‡ |

|

|

|

|

|

|

|

|||

|

|

|

|

LINEOUT_L1- |

|

|

Single-Ended |

+Left Line Output 1 |

|

** 2.2 µF |

FLYP |

|

|

Output Filter |

|

||

|

|

|

|

|

|

|

||

|

** 2.2 µF |

FLYC |

LINEOUT_R1+ |

|

|

Differential to |

‡ |

|

|

|

|

|

|||||

|

|

|

FLYN |

LINEOUT_R1- |

|

|

Single-Ended |

+Right Line Output 1 |

|

** Use low ESR |

|

|

Output Filter |

|

|||

ceramic capacitors.

|

|

|

|

|

|

|

|

|

|

|

LINEOUT_L2+ |

|

|

|

|

|

|

|

|

|

|

BITCLK |

LINEOUT_L2- |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

HD Audio |

|

|

|

|

|

|

|

|

SYNC |

LINEOUT_R2+ |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

SDI |

|||

Bus |

|

|

|

|

|

|

|

|

LINEOUT_R2- |

||

|

|

|

|

|

|

|

|

SDO |

|||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

RESET# |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+1.5 V to +3.3 V |

|

|

|

|

VL_HD |

|

||||

|

|

|

|

|

|

|

|

|

|

LINEIN_L+ |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

0.1 µF |

||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

LINEIN_C- |

|

|

|

|

|

|

|

|

|

|

|

|

+3.3 V |

|

|

|

|

|

|

|

|

VL_IF |

|||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

0.1 µF |

||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

GPIO2 |

|

GPIO2 |

|

|

|

|

|||||||

|

||||||||||||

|

GPIO3 |

|

|

|

|

GPIO3 |

||||||

|

||||||||||||

|

*** SENSE_A |

|

|

|

|

|

SENSE_A |

|||||

|

|

|

|

|||||||||

|

S/PDIF RX |

|

|

|

|

|

|

SPDIF_IN |

||||

|

|

|

|

|||||||||

|

S/PDIF TX 1 |

|

|

|

|

SPDIF_OUT1 |

||||||

|

|

|

||||||||||

D-Mic In 2 / S/PDIF TX 2 |

|

|

|

|

DMIC_SDA2/ |

|||||||

|

|

|

|

SPDIF_OUT2 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D-Mic In 1 |

|

|

|

|

|

DMIC_SDA1 |

|||||

|

|

|

|

|||||||||

|

D-Mic Clk |

|

|

|

|

DMIC_SCL |

||||||

|

|

|

|

|

||||||||

*** See Figure 9. |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

HP_GND(Thermal |

LINEIN_R+

MICIN_L-

MICIN_L+

MICBIAS

MICIN_R+

MICIN_R-

VCOM

VREF+

AGND

Pad)

Differential to |

‡ |

|

Single-Ended |

+Left Line Output 2 |

|

Output Filter |

|

|

Differential to |

‡ |

|

Single-Ended |

+Right Line Output 2 |

|

Output Filter |

|

|

* Capacitors must be C0G or equivalent |

||

1 µF |

|

Left Analog Input |

* |

|

|

|

|

|

1800 pF |

|

|

1 µF |

|

|

1 µF |

|

Right Analog Input |

* |

|

|

|

|

|

1800 pF |

|

|

1 µF |

|

|

|

|

Differential Mic Left |

1 µF |

|

|

|

|

Microphone Bias |

|

RL |

The value of RL is dictated by |

0.47 µF |

|

the microphone cartridge. |

|

RL |

|

|

|

Differential Mic Right |

1 µF |

|

|

1 µF |

|

|

|

|

‡ Input and Output |

1 µF |

10 µF |

filters are optional. |

Figure 1. Typical Connection Diagram - Desktop System

DS880F4 |

11 |

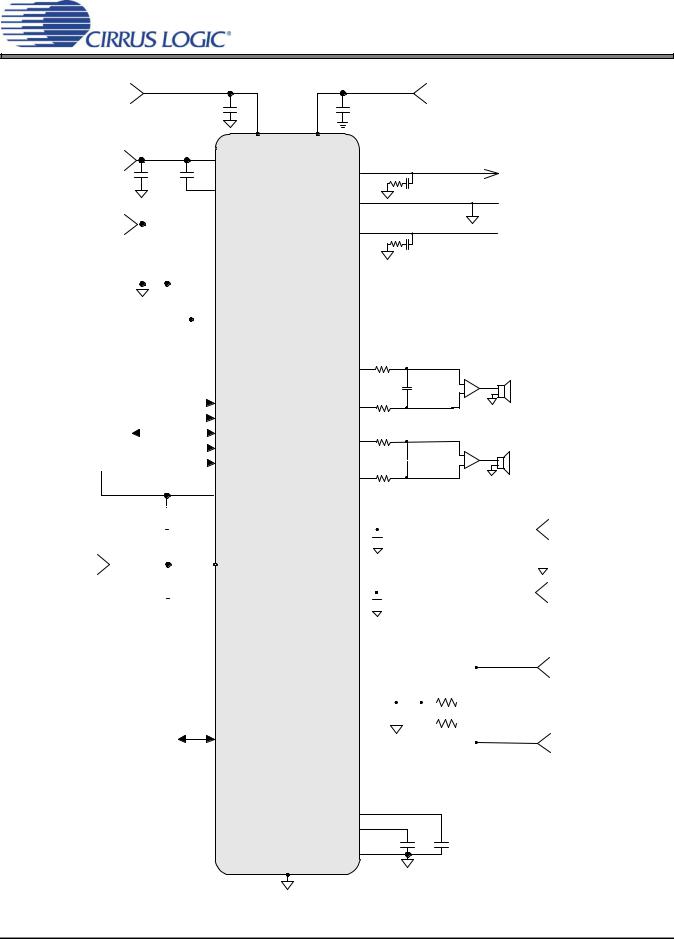

CS4207

+3.3 V |

+1.8 V |

0.1 µF |

0.1 µF |

VA VD

+3.3 V |

+ |

VA_REF |

0.1 µF |

10 µF |

|

|

|

HPOUT_L |

|

|

VBIAS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS4207 HPREF |

|

+3.3 V |

|

|

|

|

|

|

|

|

|

|

|

VA_HP |

HPOUT_R |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VHP_FILT+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.1 µF |

** |

|

** |

|

|

|

|

|

|

|

VHP_FILT- |

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||||

10 µF |

|

10 µF |

|

|

|

LINEOUT_L1+ |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FLYP |

LINEOUT_L1- |

|

|

|

|

|

** 2.2 µF |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

FLYC |

LINEOUT_R1+ |

|||||

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

** 2.2 µF |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

FLYN |

LINEOUT_R1- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

* *Use low ESR |

|

|||||||||||||

|

ceramic capacitors. |

LINEOUT_L2+ |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BITCLK |

LINEOUT_L2- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SYNC |

|

HD Audio |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDI |

|

|

Bus |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LINEOUT_R2+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDO |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET# |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LINEOUT_R2-

+1.5 V to +3.3 V

VL_HD

VL_HD

33 |

Left Headphone |

0.1 µF |

Headphone Ground

Headphone Ground

Right Headphone

Right Headphone

33 |

0.1 µF |

560 |

|

* |

2200 pF |

560 |

Speaker Driver |

560

*2200 pF

*2200 pF

560 Speaker Driver

|

|

|

|

|

|

|

0.1 µF |

|

|

* Capacitors must be C0G or equivalent |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

LINEIN_L+ |

|

|

|

|

|

|

1 µF |

|

|

Left Analog Input |

|

|

|

|

|

|

|

|

|

|

|

|

* |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1800 pF |

|

|

|

||

+3.3 V |

|

|

|

|

|

|

|

VL_IF |

LINEIN_C- |

|

|

|

|

|

|

1 µF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

0.1 µF |

LINEIN_R+ |

|

|

|

|

|

|

|

1 µF |

|

|

Right Analog Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

* |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1800 pF |

|

|

|

|||

GPIO2

GPIO2

GPIO2

GPIO3

GPIO3

GPIO3

*** SENSE_A  SENSE_A

SENSE_A

S/PDIF RX  SPDIF_IN

SPDIF_IN

S/PDIF TX 1 SPDIF_OUT1

SPDIF_OUT1

D-Mic In 2 / S/PDIF TX 2 DMIC_SDA2/ SPDIF_OUT2

D-Mic In 1  DMIC_SDA1

DMIC_SDA1

D-Mic Clk  DMIC_SCL

DMIC_SCL

MICIN_L- |

|

|

|

|

|

|

|

|||||||||

MICIN_L+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

Left Mic In |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 µF |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Microphone Bias |

|

MICBIAS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

RL |

|

|

The value of RL is dictated by |

|

|||

|

|

0.47 µF |

|

|

|

|

|

|

|

|

the microphone cartridge. |

|

||||

MICIN_R+ |

|

|

|

|

|

|

|

|

|

|

|

RL |

|

|

Right Mic In |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||||||

1 µF

MICIN_R-

|

VCOM |

*** See Figure 9. |

VREF+ |

|

1 µF 10 µF |

|

AGND |

|

HP_GND(Thermal Pad) |

|

Figure 2. Typical Connection Diagram - Portable System |

12 |

DS880F4 |

CS4207

3. CHARACTERISTICS AND SPECIFICATIONS

RECOMMENDED OPERATING CONDITIONS

(AGND=DGND=0 V, all voltages with respect to ground.) |

|

|

|

|

|

|

|

|

|

|

|

|

Units |

Parameters |

|

Symbol |

|

Min |

Max |

|

DC Power Supply (Note 1) |

|

|

|

|

|

|

Analog Core |

|

VA |

2.97 |

5.25 |

V |

|

DAC Reference |

|

VA_REF |

2.97 |

5.25 |

V |

|

Headphone Amplifier |

|

VA_HP |

2.97 |

5.25 |

V |

|

Digital Core |

|

VD |

1.42 |

1.89 |

V |

|

HD Audio Bus Interface |

|

VL_HD |

1.42 |

3.47 |

V |

|

GPIO, S/PDIF and Digital Mic Interface |

|

VL_IF |

2.97 |

3.47 |

V |

|

Ambient Temperature |

Commercial - CNZ |

TA |

-40 |

+85 |

C |

|

|

Automotive - DNZ |

-40 |

+105 |

C |

|

|

ABSOLUTE MAXIMUM RATINGS

(AGND = DGND = 0 V; all voltages with respect to ground.)

Parameters |

Symbol |

Min |

Max |

Units |

|

DC Power Supply |

Analog Core |

VA |

-0.3 |

5.5 |

V |

|

DAC Reference |

VA_REF |

-0.3 |

5.5 |

V |

|

Headphone Amplifier |

VA_HP |

-0.3 |

5.5 |

V |

|

Digital Core |

VD |

-0.3 |

3.0 |

V |

|

HD Audio Interface |

VL_HD |

-0.3 |

4.0 |

V |

GPIO, S/PDIF and Digital Mic Interface |

VL_IF |

-0.3 |

4.0 |

V |

|

Input Current |

(Note 2) |

Iin |

- |

±10 |

mA |

Analog Input Voltage |

(Note 3) |

VIN |

AGND-0.7 |

VA+0.7 |

V |

Digital Input Voltage |

(Note 3) HD Audio Interface |

VIND |

-0.3 |

VL_HD+0.4 |

V |

GPIO, S/PDIF and Digital Mic Interface |

|

-0.3 |

VL_IF+0.4 |

V |

|

Ambient Operating Temperature |

(power applied) |

TA |

-55 |

+115 |

°C |

Storage Temperature |

|

Tstg |

-65 |

+150 |

°C |

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

Notes:

1.The device will operate properly over the full range of the analog, digital and interface supplies.

2.Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause SCR latch-up.

3.The maximum over/under voltage is limited by the input current.

DS880F4 |

13 |

CS4207

ANALOG INPUT CHARACTERISTICS (COMMERCIAL - CNZ)

(Test Conditions (unless otherwise specified): Input sine wave (relative to digital full-scale): 1 kHz through passive input filter; VA_HP = VA; VL_HD = VL_IF = 3.3; VD = 1.8 V; TA = +25 C; Measurement Bandwidth is 10 Hz to

20 kHz unless otherwise specified. Sample Frequency = 48 kHz)

|

|

VA, VA_REF = 5.0 V |