Page 1

R

CTK-650

(with price)

ELECTRONIC KEYBOARD

CTK-650

Page 2

CONTENTS

SPECIFICATIONS ....................................................................................................1

BLOCK DIAGRAM ...................................................................................................2

CIRCUIT DESCRIPTION

CPU (HD6433298A16P : H8/329) .....................................................................3

DIGITAL SIGNAL PROCESSOR, LSI-S (HG51A115A01FD) ..........................4

KEY TOUCH LSI (HG52E35P) ..........................................................................5

POWER AMPLIFIER (LA4598) .........................................................................6

BUTTON MATRIX .............................................................................................

KEY MATRIX .....................................................................................................8

WIRING DIAGRAM ...................................................................................................

IC LEAD IDENTIFICATION AND INTERNAL CIRCUIT ..........................................10

PCB VIEW AND MAJOR WAVEFORMS .................................................................

SCHEMATIC DIAGRAM ...........................................................................................

PARTS LIST .............................................................................................................15

EXPLODED VIEW ....................................................................................................19

7

9

12

13

Page 3

SPECIFICATION

Number of keys: 61

Polyphony: 32-note(max.)

Preset tones: 128

Magical preset: BREAK BEAT 16 MELODYCOMP 8

SHADOW DRUM 4 FREE SESSION 32

TONE STACK 40 KEY SPLIT 12

HYPERACTIVE 16

Auto-accompaniment: Rhythm patterns 128

Tempo Adjustable(40 - 255)

Chords Three system: CASIO CHORD, FINGERD,

FULL-RANGE CHORD

Other Variation pattern, fill-in pattern, intro/ending pattern for each

rhythm.

Song memory: song:one

System:Real-time recording

Memory capacity:Up to 1,300 notes

Registration memory: 4 setups

Sound control pads: Phrases 10

Drums 10

SE/Percussion 10

Controller 2

Digital effects: REVERB 1, REVERB 2, REVERB 3, CHORUS, TREMOLO, PHASE

SHIFTER, ORGAN SP, ENHANCER, FLANGER, EQLOUNDNESS

DEMO tunes: 3 tunes

Other functions: Transpose (F# ~ C ~ F : half-note)

Tuning adjustable A4 = 440KHz 50 cents increments

Volume control (Main /Accompaniment)

Speakers: 12cm diameter X 2 (Output:2W+2W)

I/O terminals: Power supply 9V DC jack

Headphones Stereo mini jack

Output impedance:100 ohm

Output voltage:4.5V(RMS. max)

Assignable jack Standard jack

MIDI IN, OUT

Power supply: 3-way AC/DC power sources;

Batteries Six D-size

Battry life Approximately 5 hours on R20P(SUM-1)

AC Required optional AD-5 AC adaptor

Car battery Required optional CA-5 car adaptor

Auto power off: Approximately 6 minutes after the last operation

Power consumption: 7.7W

Dimensions: 942 X 367 X 135 mm(HWD)

31 7/16" X 14 1/2" X 4 3/8" inches(HWD)

Weight: 5.2kg(11.7lbs) excluding batteries

Accessory: Score stand

— 1 —

Page 4

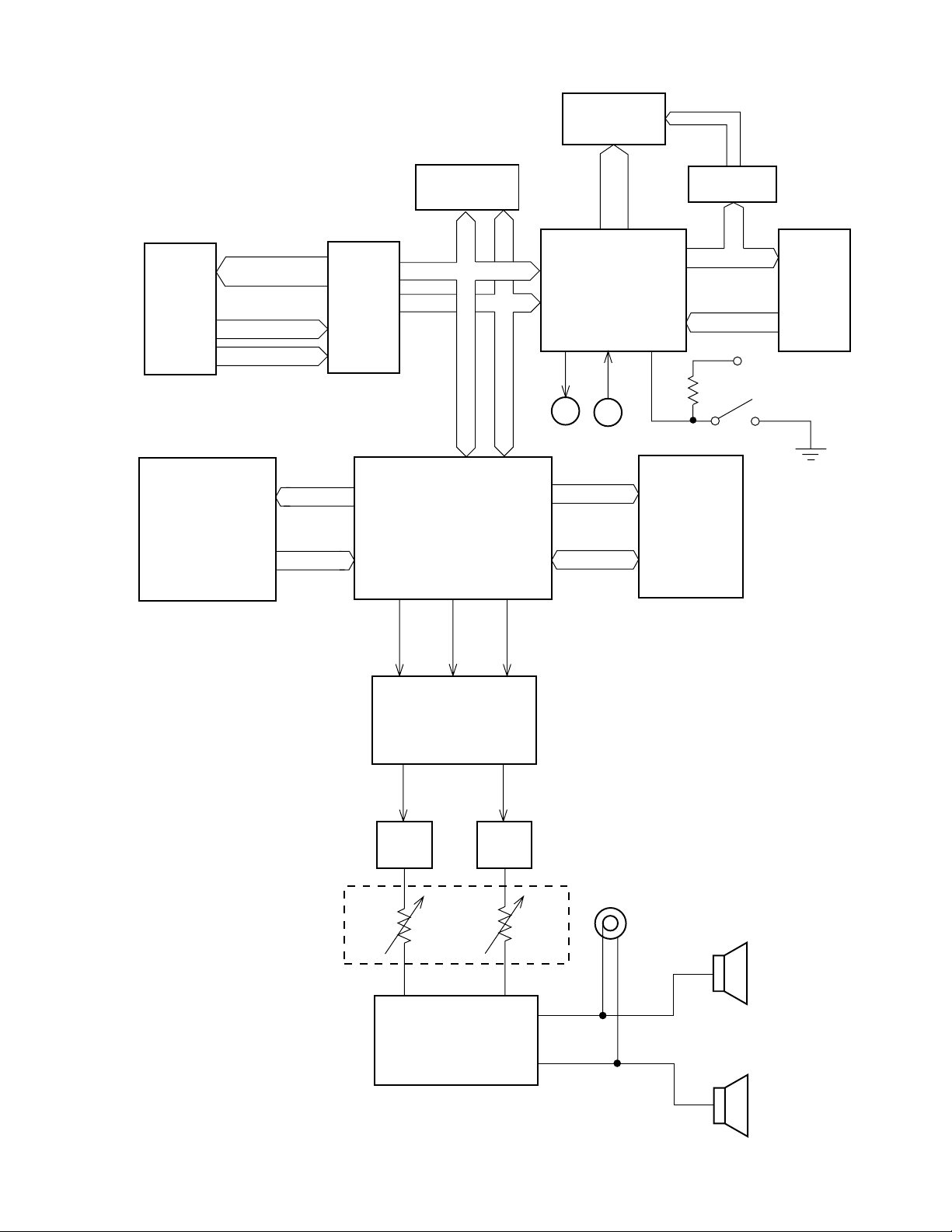

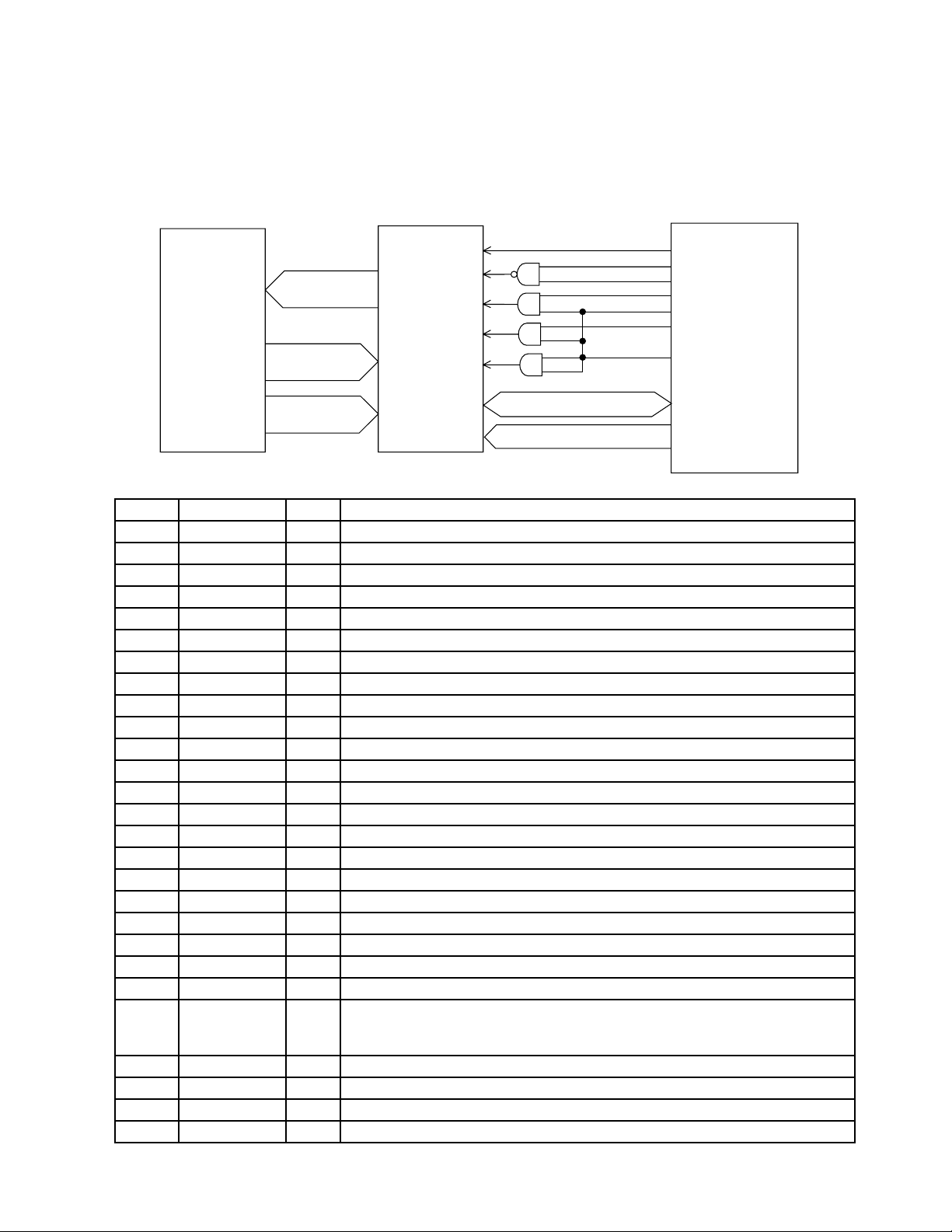

BLOCK DIAGRAM

7-Segment

LED

LO0~LO4

KC0~KC7

Keyboard

SI0~SI7

FI0~FI7

ROM(16M)

TC5316200CP-C079

Key Touch

LSI

HG52E35P

RA0~RA19

RD0~RD15

RAM-1(64K)

MN4464-08L-1

D0~D7

Address Bus

LSI-S

HG51A115A01FD

La

~Lp

CPU

HD6433298A16P

(H8/329)

MIDI

INOUT

EA0~EA12

ED0~ED7

RAM-2(64K)

MN4464-08L-2

LED driver

BA612

KO0~4

KO0~KO5

Buttons

KI1~KI7

VDD

100K

Power Switch

WCK1 SLOP BCK

D/A Converter

µPD6376CX

Filter

Main

Volume

Power Amplifier

LA4598

Filter

Output

Speakers

— 2 —

Page 5

CIRCUIT DESCRIPTION

CPU(HD6433298A16P : H8/329)

The 16-bit CPU contains a 32K-byte ROM, a 1K-byte RAM, an 8-bit A/D converter, timers and I/O ports. The

CPU accesses to the DSP, Key Touch LSI, RAM, buttons and LEDs. But the CPU directly receives MIDI and

pedal signals.

Pin No. Terminal In/Out Function

1 P40/IRQ2 In KO signal data.

2 P41/IRQ1 In Timing signal for KO signal.

3 P42/IRQ0 In APO signal output.

4 P43/-RD Out Read signal outpt.

5 P44/-WR Out Write signal output.

7 P46/PHI Ou t System clock output.

8 P47/-WAIT In Wait signal input

9 P50/Txd Out MIDI signal output.

10 P51/Rxd In MII signal input.

11 P52/SCK Out Reset signal output.

1 2 -RESET In Reset signal input.

13 -NMI In Power on signal input.(Low active)

1 4 Vcc In +5V source.

1 5 -STBY In Standby signal input. Connected to +5V.

1 6 Vss In Ground(0V) source.

17,18 XTAL,EXTAL In/Out 20MHz clock pulse input/output. Connected to crystal.

19,20 MD1,MD0 In Selection for system.

MD1 MD0 MODE

0 1 MODE-1 : Internal ROM mode

1 0 MODE-2 : Non internal ROM mode

1 1 MODE-3 : Single chip mode

21 AVss In Analog ground source.

22 P70/AN0 In Connected to ground.

23~29 P71/AN0~P77/AN7 In KI signal input.

30 AVcc In +5V source.

31~38 P60/FTCI~P67/TMO1 Out Control signal for 7-segment LED.

3 9 Vcc In +5V source.

41~56 P26/A14~P10/A0 Out Address bus.

4 8 Vss In Ground(0V) source.

57~64 P30/D0~P37/D7 In/Out Data bus.

— 3 —

Page 6

DIGITAL SIGNAL PROCESSOR, LSI-S (HG51A115A01FD)

The LSI-S is a 16-bit DSP(Digital Signal Processor) and accessable to 16M-bit sound source ROM and to 64Kbit RAM. The DSP can read data of 32 polyphonic note from the ROM and provides two 16-bit serial dat with

timing signals to each channel's D/A converter.

Pin No. Terminal In/Out Function

1~7 D7~D0 I/O Data bus.

11 GND7 In Ground(0V) source.

12 CK16 Out 16.384MHz clock pulse output.

13 VCC6 In +5V source

14 CK0 In Clock pulse input. Connected to terinal CK16.

16 VCC1 In +5V source.

17 GND1 In Ground(0V) source.

18,19 XTI, XTO In/Out 16.384MHz clock pulse input/output. Connected to crystal.

21 CCSB I Chip select signal input.

22~25 CA0~CA3 In Address bus.

26 CE0 In Connected to ground.(ROM interface ontrol terminal)

27 CWRB In Write enable signal.

28 CRDB In Read enebla signal.

33 RESB In Reset sna iput

34 TESB In Connected to +5V.

40~49

52~57

50 VCC2 In +5V source.

51 GND2 In Ground(0V) source.

59 RA22 Out Chip enable signal output for ROM.

62~73

75~82

74 GND5 In Ground(0V) source.

84 VCC3 In +5V source.

85 GND3 In Ground source.

86 WOK1 Out Ward clock for DAC.

88 SOLP Out 16-bit serial data for L-channel DAC.

89 BOK Out Bit clock for DAC.

93 VCC5 In +5V source.

95,97

99~105

107,109

110,112

96 EWEB Out Write enable signal for RAM.

106 EOEB Out Read enable signal for RAM.

108 VCC7 In +5V source.

111 ECEB Out Chip eneble signal for RAM.

118 VCC4 In +5V source.

119 GND4 In Ground(0V) source.

123~130 ED0~ED7 In/Out Data bus for RAM.

131 GND6 In Connected to Ground.

132 SSI In Connected to Ground.

133 SBCK In Connected to Ground.

134 SWCK In Connected to Ground.

RD0~RD15 In Data bus for sound source ROM.

RA0~RA19 Out Address bus for sound source ROM.

EA0~EA12 Out Address bus for RAM.

— 4 —

Page 7

KEY TOUCH LSI(HG52E35P)

By counting the time between the first key input signal FI and the second SI from the keyboard unit, the key

touch LSI detects key velocity of 256-step. Then the LSI sends the CPU note numbers and their velocities.

Key Touch LSI

HG52E35P

RESB

CCSB

KC0~KC7

Keyboard

FI0~FI9

SI0~SI9

CWRB

CRDB

CKI

P30/D0~P37/D7

P12/A2~P10/A0

D0~D7

A0~A2

Pin No. Terminal In/Out Function

1 REQB Out Interrupt request. Not used.

2, 3 FI10,SI10 In Connected to +5V.

4 VCC In +5V source.

5 CRDB In Read enable signal.

6 CWRB I n Write enable signal.

7 CCBB In Chip select signal.

8 T In Test terminal. Connected to +5V.

9 STYB In Standby terminal. Connected to +5V.

10 RESB In Reset signal.

1 1 W In Test terminal. Connected to +5V.

12 CKI In External clock input.

1 3 TMD In Test terminal. Connected to ground.

1 4 TST In Test terminal. Connected to ground.

1 5 CKO Ou t External clock output. Not used.

1 6 GND In Ground(0V) source.

1 7 XIN In Clock pulse input. Connected to ground.

18 XOUT O ut Clock pulse output. Not used.

1 9 TRES In Test terminal. Connected to ground.

20~28 CD0~CD7 In/Out Data bus.

2 4 GND In Ground(0V) source.

29~31 CA0~CA2 Out Address bus.

3 2 VCC In +5V source.

33~4333~43

53~5553~55

57~6357~63

FI0~FI9FI0~FI9

SI0~SI9SI0~SI9

In Key input signal.

4 0 VCC In +5V source.

44~53 KC0~KC7 Out Key scan signal.

48,56 GND In Ground(0V) source.

5 4 VCC In +5V source.

CPU

HD6433298A16P

P52/SCK

A12

A14

P44/-WR

P42/IRQ0

P43/-RD

P46/PHI

CD0~CD7

CA0~CA2

— 5 —

Page 8

POWER AMPLIFIER(LA4598)

LA4598 is 2-channel power amplifier with standby switch.

Pin No. Terminal In/Out Function

1 Power GND In Ground(0V) source.

2 Ch1 B.S. - Terminal for bootstrap capacitor.

3 Ch1 OUT O u t Channel 1 output.

4 VCC In +9V source.

5 Ch1 N.F. In Negative feedback input.

6 Ch1 IN In Channel 1 input.

7 D.C. - Terminal for decoupling capacitor.

8 Pre GND In Ground(0V) source.

9 Standby In Control signal input. 0V:OFF / +9V:ON

10 Ch2 IN In Channel 2 input.

1 1 Ch2 N.F. In Negative feedback input.

1 2 Ch2 OUT Ou t Channel 2 output.

1 3 Ch2 B.S. - Terminal for bootstrap capacitor.

1 4 NC - Not used.

INTERNAL BLOCK DIAGRAM

D.C.

6

5

8

7

10

11

Input

AMP.

Bias circuit

Ch1 IN

Ch1 NF

Pre GND

Ch2 IN

CH2 NF

Input

AMP.

Pre-drive

AMP.

Pre-drive

AMP.

Power

AMP.

TSD protector

Stand by

Power

AMP.

2

CH2 BS

3

CH1 OUT

POWER GND

1

4

VCC

9

STAND BY

CH2 OUT

12

13

CH2 BS

— 6 —

Page 9

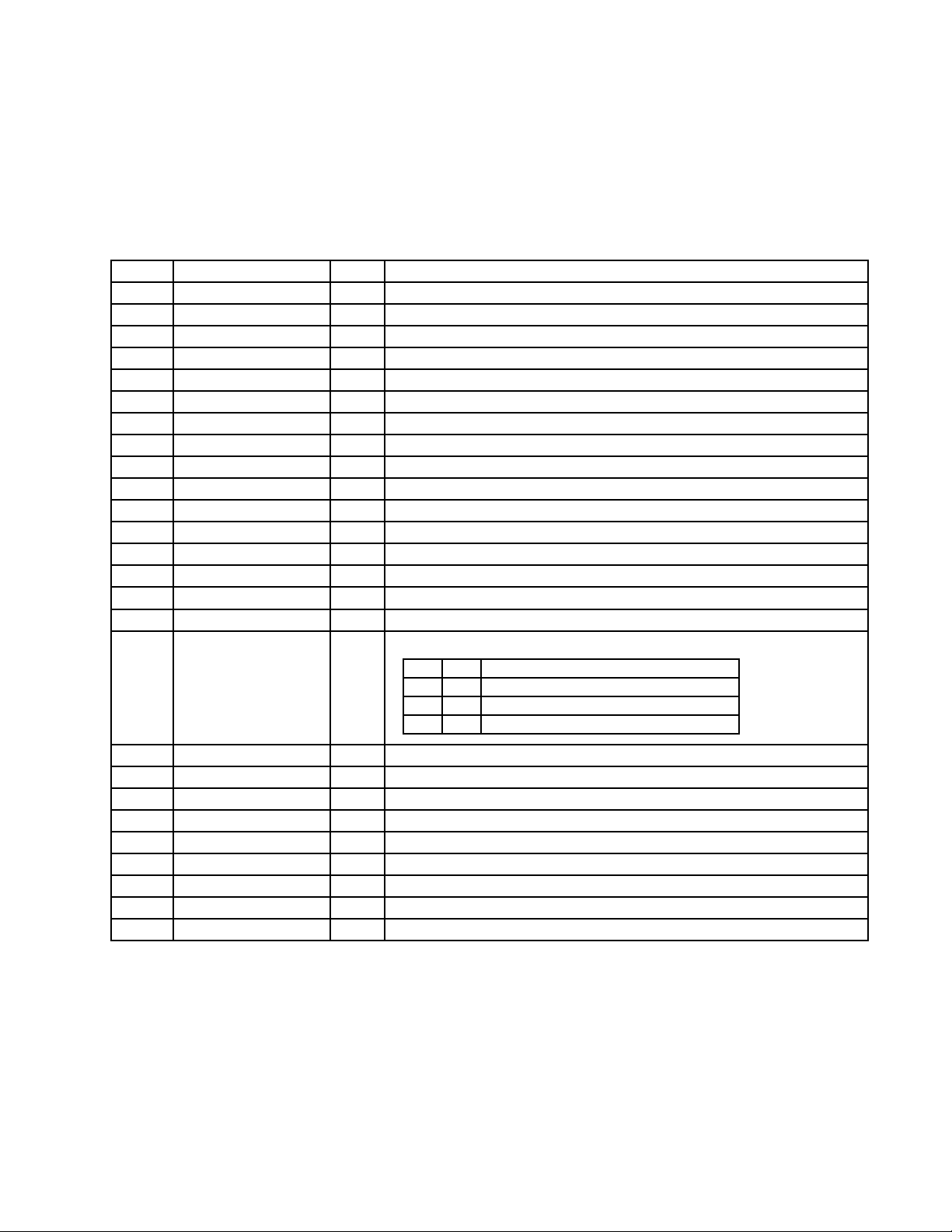

BUTTON MATRIX

KI1 KI2 KI3 KI4 KI5 KI6 KI7

KO0 3 0 2 1 SONG NO.

REGIST-

KO1 SPLIT DEMO LAYER

RATION

MEMORY

KO2 + 9 TONE 7 8 RHYTHM

KO3 VARIATION-A INTRO VARIATION-B

TEMPO

DOWN

KO4 6 – MIDI 5 4

ACCOMP

VOLUME

MAGICAL

PRESET

TEMPO

UP

TOUCHCOVE

ON/OFF

END/

SYNCHRO

MULTI

EFFECTOR

START/STOP

TRANSPOSE

TUNE

KO5 B CHORD D A C

Nomenclature of Keys

C#2

C2 D2E2F2

F#2D#2

G2

A2 B2 C3 D3

C#3A#2G#2

F#3 G#3

D#3

E3

F3 G3 A3 B3 C4 D4 E4 F4 G4 A4 B4 C5 D5 E5 F5 G5 A5 B5

A#3 C#4 D#4

F#4 G#4

A#4

C#5

D#5

F#5 G#5

A#5

C#6

C6

G#6F#6D#6

A#6

B6A6G6F6E6D6

C7

— 7 —

Page 10

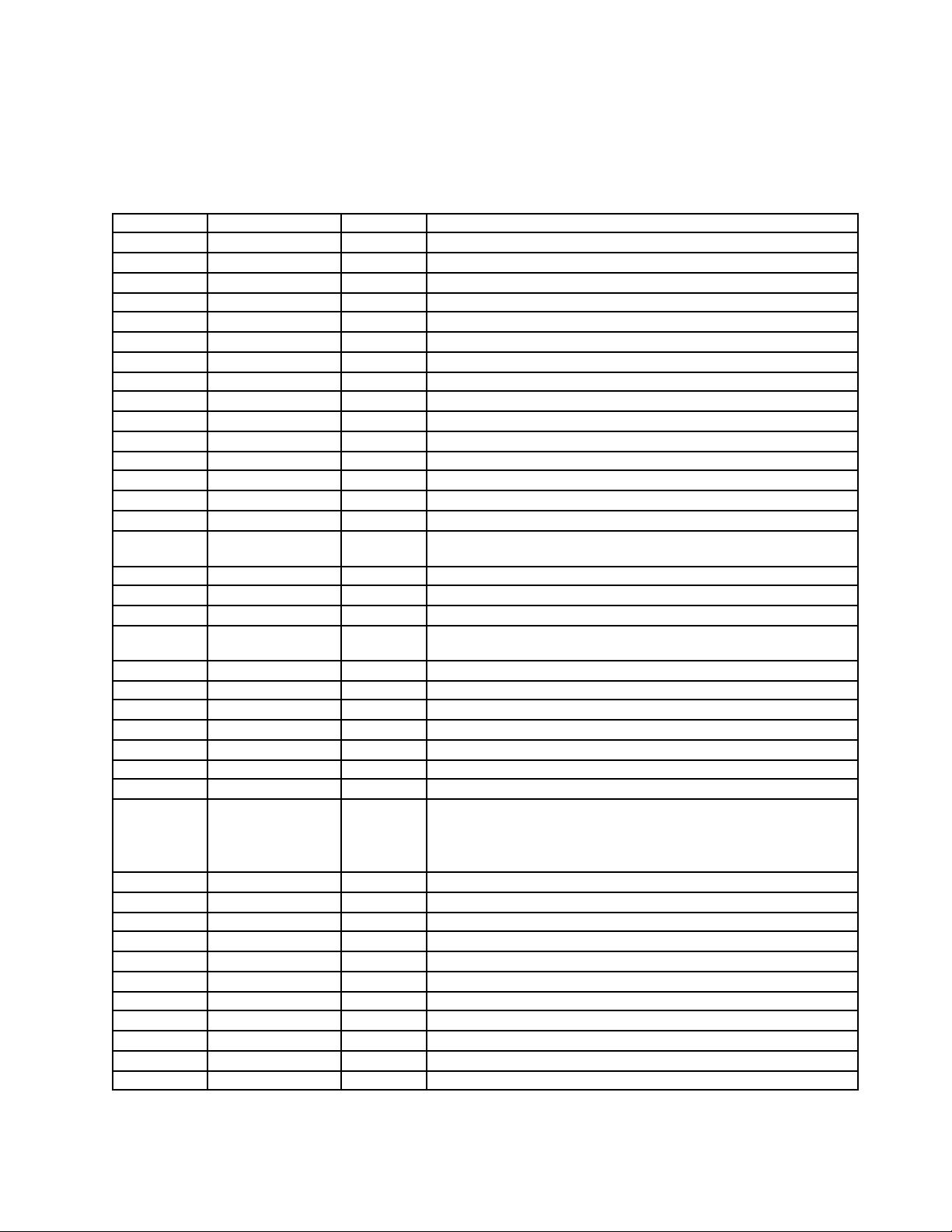

KEY MATRIX

KC0 KC1 KC2 KC3 KC4 KC5 KC6 KC7

FI0 C2 1 C#2 1 D2 1 D#2 1 E2 1 F2 1 F#2 1 G2 1

SI0 C2 2 C#2 2 D2 2 D#2 2 E2 2 F2 2 F#2 2 G2 2

FI1 G#2 1 A2 1 A#2 1 B2 1 C3 1 C#3 1 D3 1 D#3 1

SI1 G#2 2 A2 2 A#2 2 B2 2 C3 2 C#3 2 D3 2 D#3 2

FI2 E3 1 F3 1 F#3 1 G3 1 G#3 1 A3 1 A#3 1 B3 1

SI2 E3 2 F3 2 F#3 2 G3 2 G#3 2 A3 2 A#3 2 B3 2

FI3 C4 1 C#4 1 D4 1 D#4 1 E4 1 F4 1 F#4 1 G4 1

SI3 C4 2 C#4 2 D4 2 D#4 2 E4 2 F4 2 F#4 2 G4 2

FI4 G#4 1 A4 1 A#4 1 B4 1 C5 1 C#5 1 D5 1 D#5 1

SI4 G#4 2 A4 2 A#4 2 B4 2 C5 2 C#5 2 D5 2 D#5 2

FI5 E5 1 F5 1 F#5 1 G5 1 G#5 1 A5 1 A#5 1 B5 1

SI5 E5 2 F5 2 F#5 2 G5 2 G#5 2 A5 2 A#5 2 B5 2

FI6 C6 1 C#6 1 D6 1 D#6 1 E6 1 F6 1 F#6 1 G6 1

SI6 C6 2 C#6 2 D6 2 D#6 2 E6 2 F6 2 F#6 2 G6 2

FI7 G#6 1 A6 1 A#6 1 B6 1 C7 1

SI7 G#6 2 A6 2 A#6 2 B6 2 C7 2

Note:Each key has two contacts, the first contact

Key

Second contact 2

1 and second contact .

First contact 1

2

FI

KC

SI

— 8 —

Page 11

WIRING DIAGRAM

M616T-KY1M

1

FI1

1

DC JACK

PHONES/OUTPUT

SUSTAIN

JA CONNECTOR

FI2

SI0

FI0

SI1

JA-CONNECTOR

SI2

SI3

FI3

KC0

KC1

KC2

KC3

KC4

KC5

17

KC6

17

KC7

M5711-MA1M

MIDI IN

MIDI OUT

JC-CONNECTOR JD-CONNECTOR

112

112

M616T-KY2M

117

KC0

117

JB-CONNECTOR

KC1

KC4

KC3

KC2

JB-CONNECTOR

KC5

FI4

SI4

KC6

KC7

BATT.-

SI5

SI6

BATT.+

SI7

FI5

FI6

FI7

LSP

PG

RSP

PG

LG

POWER

PWLD

KO5

KO4

KO3

KO2

1

JC-CONNECTOR

KO1

KO0

KI1

KI2

12

1

KI3

M5711-CN1M

KI7

KI6

KI5

KI7

La

Lb

KI4

KI6

KI5

KI4

JD-CONNECTOR

Lc

Ld

Le

Lp

Lf

Lg

BATTERY

COMPARTMENT

12

— 9 —

Page 12

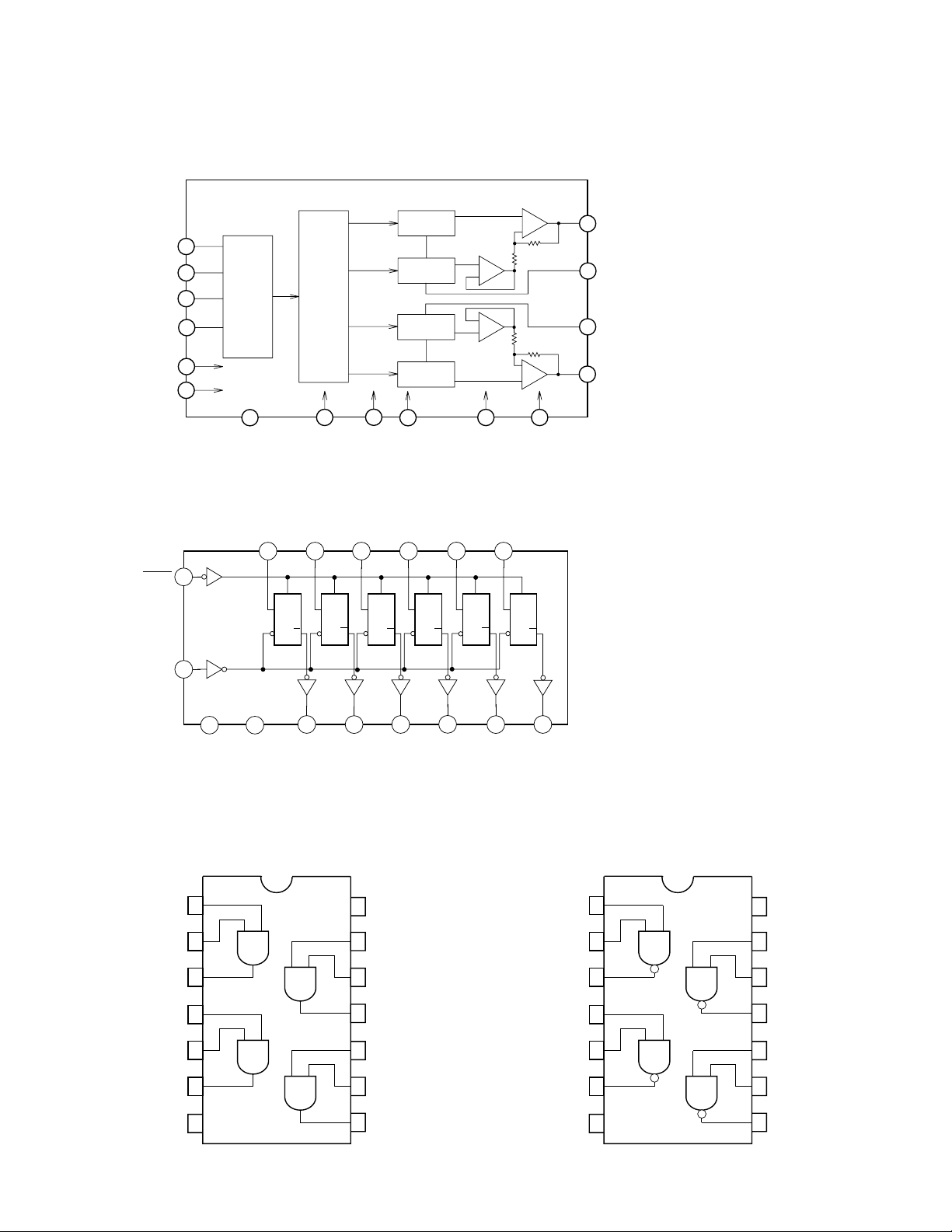

IC LEAD IDENTIFICATION AND INTERNAL CIRCUIT

UPD6376CX (D/A converter)

MAIN DAC

13

LRCK

54

A.GND

SUB DAC

SUB DAC

MAIN DAC

712

8

A.VDD

LRSEL/RSI

SI/LSI

CLK

4/8 fs SEL

D.GND

14

15

TIMING

16

GENERATOR

SHIFT REGISTER

LATCH

1

2

3

N.C.

D.VDD

TC74HC174AP (HEX D-TYPE FLIP FLOP WITH CLEAR )

CLEAR

CLOCK

D0 D1

1

R

D

Q

CK

9

43

D

CK

R

D2 D3

6

D

Q

CK

D

CK

D4

13

R

Q

11

R

Q

D

CK

D5

14

R

R

D

Q

CK

Q

11

10

6

9

L.OUT

L.REF

R.REF

R.OUT

16

VDD GND

8

Q0

2

5

Q1 Q2 Q3 Q4 Q5

10

7

12

15

TC74HC08AP (QUAD 2-INPUT AND GATE) TC74HC00AP (QUAD 2-INPUT NAND GATE)

1A

1B

1Y 3

2A

2B

2Y

GND

1

2

4

5

6

7

14

VCC

13 4B

4A

12

4Y

11

10 3B

3A

9

8

3Y

GND

1A 1

1B

1Y 3

2A

2B

2Y

14

VCC

2

4

5

6

7

13 4B

12

4A

4Y

11

10 3B

3A

9

8

3Y

— 10 —

Page 13

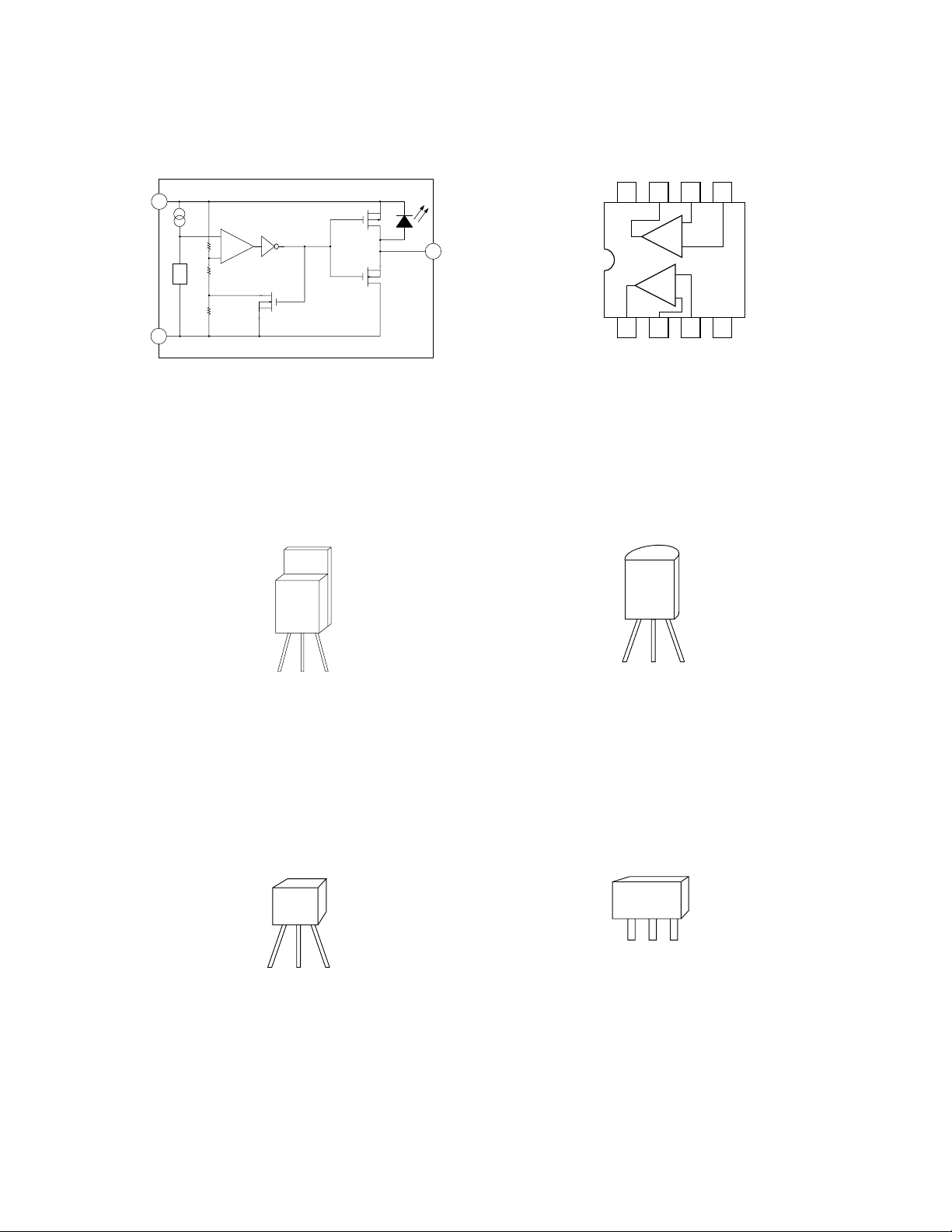

VDD

+

-

+

-

12

34

5

67

8

VCC

GND

VSS

S-8053ANO

2

1

OUT

3

M5218APR

S-81350HG

2SB1274

S-8053ANO

BCE

1

3

2

2SC1740

DTA114TS

2SA933

E

CB

2SB1240

2SD1858

E C B

— 11 —

Page 14

PCB VIEW & MAJOR WAVEFORMS

14

15

2 53 6

18

19

1

7

4

16

17

9

8

10 11 12 13

— 12 —

Page 15

SCHEMATIC DIAGRAM M5711-MA1M

14

15

16

17

18

19

9

8

2 5

3 6

4 7

1

— 13 —

10 11 12 13

Page 16

SCHEMATIC DIAGRAM M5711-CN1M

— 14 —

Page 17

PARTS LIST

CTK-650

Notes: 1. Prices and specifications are subject to change with-

out prior notice.

2. As for spare parts order and supply, refer to the

"GUIDEBOOK for Spare parts Supply", published

separately.

3. The numbers in item column correspond to the same

numbers in drawing.

Page 18

FOB Japan

N Item Code No. Parts Name Specification Q M N.R.Yen R *

Unit Price

PCB ass'y M5711-MA1M

2011 3325 LSI UPD6376CX 1 1 230 A C

2011 5194 LSI HG52E35P 1 1 600 A F

2011 5201 LSI HG51A115A01FD 1 1 2,820 A T

N 2011 6797 LSI LC3564Q-85.10 2 1 280 A C

N 2011 6944 LSI TC5316200CP-C079 1 1 1,230 A N

N 2011 7021 LSI HD6433298A16P 1 1 880 A J

N 2105 2114 IC, Regulator S-81350HG 1 5 65 A B

2105 2219 MOS IC S-8053ANO 1 5 60 A B

N 2105 2912 C-MOS HD74HC08P 1 10 28 A A

2105 3045 C-MOS HD74HC174P 1 5 49 A A

N 2105 3136 C-MOS HD74HC00P 1 10 28 A A

2114 1421 IC, Photo-coupler PC900V 1 1 210 A C

2114 1799 IC, Monolithic M5218APR 1 1 38 A A

2114 2891 IC, Monolithic LA4598 1 1 140 A B

N 2251 0665 Transistor 2SB1240R.S-TV6-T 1 20 26 A A

N 2251 0672 Transistor 2SB1548-P.CS 1 10 44 A A

2252 0889 Transistor 2SA1267Y,GR-AT-T 1 20 8 A A

2252 0896 Transistor 2SC1740S-R,S-TP-T 4 20 8 A A

N 2253 0581 Transistor 2SD1858R.S-TV6-T 1 20 24 A A

N 2259 1883 Digital transistor DTA114TS-TP-T 8 20 10 A A

2310 7996 Zener diode RD4.7ESB2-T1-T 1 20 12 A A

2360 0098 Zener diode RD5.1ESB2-T1-T 1 20 14 A A

N 2360 2233 Zener diode RD5.1JSB1-T1-T 1 20 8 A A

2390 0371 Diode DSK10B-BT-T 1 20 11 B A

2390 1316 Diode SB10-04A3-BT-T 1 20 28 B A

2390 1344 Diode 1SS133T-77-T 3 20 3 C A

N 2390 1995 Diode RB441Q-T77-T 1 20 16 B A

N 2590 1519 Crystal oscillator HC-49U16384 1 1 100 A B

N 2590 1526 Ceramic oscillator EFO-EN2005C4 1 5 62 A B

2606 1141 Carbon film resistor R-20-1K-J-T23-T 13 20 2 C A

2606 1148 Carbon film resistor R-20-220-J-T23-T 3 20 2 C A

2606 1155 Carbon film resistor R-20-330-J-T23-T 3 20 2 C A

2606 1162 Carbon film resistor R-20-10-J-T23-T 3 20 2 C A

2606 1169 Carbon film resistor R-20-100-J-T23-T 40 20 2 C A

2606 1176 Carbon film resistor R-20-100K-J-T23-T 10 20 2 C A

2606 1183 Carbon film resistor R-20-10K-J-T23-T 4 20 2 C A

2606 1197 Carbon film resistor R-20-22-J-T23-T 1 20 2 C A

2606 1204 Carbon film resistor R-20-3.3-J-T23-T 2 20 2 C A

2606 1218 Carbon film resistor R-20-56-J-T23-T 2 20 2 C A

2606 1232 Carbon film resistor R-20-82-J-T23-T 2 20 2 C A

2606 1253 Carbon film resistor R-20-4.7K-J-T23-T 4 20 2 C A

2606 1274 Carbon film resistor R-20-1.5K-J-T23-T 1 20 2 C A

2606 1288 Carbon film resistor R-20-2.2K-J-T23-T 1 20 2 C A

2606 1302 Carbon film resistor R-20-270-J-T23-T 1 20 2 C A

2606 1309 Carbon film resistor R-20-470-J-T23-T 35 20 2 C A

2606 1316 Carbon film resistor R-20-47K-J-T23-T 3 20 2 C A

2606 1323 Carbon film resistor R-20-56K-J-T23-T 22 20 2 C A

2606 1337 Carbon film resistor R-20-1M-J-T23-T 1 20 2 C A

2606 1372 Carbon film resistor R-20-33K-J-T23-T 11 20 2 C A

2606 1386 Carbon film resistor R-20-15K-J-T23-T 4 20 2 C A

2606 1435 Carbon film resistor R-20-560-J-T23-T 1 20 2 C A

2606 1442 Carbon film resistor R-20-18K-J-T23-T 2 20 2 C A

N 2606 1526 Carbon film resistor R-20-150-J-T23-T 3 20 2 C A

N 2606 1708 Carbon film resistor R-20-47-J-T23-T 3 20 2 C A

Notes: N – New parts

M – Minimum order/supply quantity

R – Rank

— 15 —

Page 19

FOB Japan

N Item Code No. Parts Name Specification Q M N.R.Yen R *

Unit Price

2765 1344 Slide volume EWA-MJCC25B23 1 1 110 A B

2801 7910 Electrolytic capacitor 16RE3-470-T2-T 3 10 27 C A

2805 2341 Electrolytic capacitor 10RE2-1000-S1 2 10 45 C A

2805 3061 Electrolytic capacitor 6.3RE2-220-T2-T 2 10 26 C A

2805 3134 Electrolytic capacitor 10RE2-22-T2-T 11 20 14 C A

2805 3142 Electrolytic capacitor 16RE2-10-T2-T 1 20 14 C A

2807 1023 Electrolytic capacitor 50RE2-1-T2-T 2 20 15 C A

2807 1040 Electrolytic capacitor 6.3RE2-470-T2-T 1 10 27 C A

2807 1091 Electrolytic capacitor 6.3RE2-100-T2-T 8 20 18 C A

2807 1112 Electrolytic capacitor 10RE2-100-T2-T 2 20 12 C A

2813 1197 Semiconductive capacitor DD404SR103K16-T 3 20 6 C A

2813 1218 Semiconductive capacitor DD404SR222K16-T 2 20 15 C A

2813 1722 Semiconductive capacitor DD407SR104K16-T 22 20 9 C A

2813 2128 Semiconductive capacitor DD405SR473K16-T 2 20 7 C A

2813 2254 Semiconductive capacitor DD405SR333K16-T 2 20 6 C A

2813 2429 Semiconductive capacitor DD404SR183K16-T 2 20 5 C A

N 2813 3353 Semiconductive capacitor DD404SR123K16-T 2 20 5 C A

2818 0365 Ceramic capacitor RT-HE50TKYB102K-T 1 20 3 C A

2818 0446 Ceramic capacitor RT-HE40TKYB101K-T 15 20 4 C A

2818 2465 Ceramic capacitor RT-HE40TKCH040D-T 2 10 8 C A

2818 3275 Ceramic capacitor RT-HE40TKCH220J-T 2 20 5 C A

2830 6436 Mylar capacitor AMZV-473K50-T 2 10 9 C A

2845 0168 Module capacitor CNB8X101K 1 5 58 C B

2845 0175 Module capacitor CNB7X101K 1 10 44 C A

2845 0182 Module capacitor CNB6X101K 1 10 43 C A

2845 3934 Three polarity capacitor DS310-92D223S-T 7 10 18 C A

3035 0266 Ferrite beads BL02RN2-R62T4-T 12 10 13 C A

3501 4816 DIN jack YKF51-5051 1 1 110 B B

3501 7049 DC jack HEC2305-01-330 1 10 29 A A

3612 0711 Miniature jack YKB21-5101 1 5 90 B B

3612 0789 Jack YKB21-5010 1 5 60 B B

3841 0539 Inductor ELE-V100KR-T 11 20 26 C A

N 4317 4221 Blank PCB M5711-MA1M M111758A-1 1 1 680 C G

N 6922 3740 PCB ass'y M5711-MA1M M111774*1 1 9,570 B CC

PCB ass'y M5711-CN1M

N 2114 3318 IC, Monolithic BA612 1 5 98 A B

2370 0343 LED LN28RPX-(TT) 9 20 16 C A

2370 0952 LED LB-603VP1 1 1 240 C C

N 2370 0959 LED LN882RPX-(TT) 2 20 27 C A

2390 1344 Diode 1SS133T-77-T 37 20 3 C A

N JC 3719 4235 Ribbon cable M711C DF5H12120-MM 2 10 33 C A

N 4317 4231 Blank PCB M5711-CN1M M111759A-1 1 1 280 C C

N 6922 3760 PCB ass'y M5711-CN1M M111775*1 1 1 1,280 C N

PCB ass'y M616T-KY1M

2301 0101 Diode 1S2473-T-77-T 64 20 8 C A

N JA 3719 4242 Ribbon cable M711A DF5H16220-MM 1 5 68 C B

4317 4151 Blank PCB M616T-KY1M M111748A-1 1 1 240 C C

N 6922 3900 PCB ass'y M616T-KY1M M111750*2 1 1 710 C H

PCB ass'y M616T-KY2M

2301 0101 Diode 1S2473-T-77-T 58 20 8 C A

N JB 3719 4249 Ribbon cable M711B DF5H17310-MM 1 5 93 C B

4317 4161 Blank PCB M616T-KY2M M111749A-1 1 1 190 C C

6909 6240 Sponge 35X200 M42674-2 1 20 25 C A

N 6922 3910 PCB ass'y M616T-KY2M M111751*2 1 1 860 C I

Notes: N – New parts

M – Minimum order/supply quantity

R – Rank

— 16 —

Page 20

FOB Japan

N Item Code No. Parts Name Specification Q M N.R.Yen R *

Unit Price

Mechanical Parts

N 1 6922 3800 Display window 711 M312128-1 1 5 93 C B

2 6921 5040 Slide volume knob 601 M311860-1 1 10 13 B A

N 3 6922 3820 Panel 711 M111744-1 1 1 890 C J

N 4a 6922 3830 Rubber button 711A M312122-1 1 10 31 B A

N 4b 6922 3840 Rubber button 711B M312123-1 1 10 32 B A

N 5 6922 3850 Rubber button 711C M312124-1 1 1 110 B B

N 6 6922 3860 Rubber button 711F M211727-1 1 1 130 B B

N 7 6922 3870 Rubber button 711D M312125-1 1 5 72 B B

8 6922 2660 Rubber button 710C M312088-1 1 1 97 B B

N 9 6922 3880 Rubber button 711D M312125-2 1 5 73 B B

N 10 6922 3890 Rubber button 711E M312126-1 1 5 73 B B

11 6922 2680 Rubber button 710D M312082-2 1 10 29 B A

12 3831 0357 Speaker 1221AF 2 1 1,000 B K

13 6922 2840 LT White key set CEGB M111723-1 5 1 100 A B

14 6922 2850 LT White key set DFA M111724-1 4 1 100 A B

15 6922 2860 LT White key set DFAS M111725-1 1 1 100 A B

16 6922 2740 LT Black key set10P M111726-1 2 1 120 A B

17 6922 2750 LT Black key set 5P M111726-2 1 5 86 A B

18 6922 2760 Key contact rubber LT-CB M211704-1 4 5 89 A B

19 6922 2770 Key contact rubber LT-CS M211705-1 1 5 91 A B

N 20 6922 3923 Case ass'y M111732C*2 1 1 1,300 C N

N 21 6918 1634 Battery cover sub ass'y M311164D*1 1 1 200 B C

22 6922 2631 Bottom plate 710 M211706A-1 1 1 360 C D

20-1 6902 6140 Battery spring 90 M41226-1 1 10 27 B A

20-2 6903 2150 Battery spring B M41330-1 1 10 18 B A

20-3 6922 2810 Lower stopper 710 M412287-1 1 1 98 C B

20-4 6922 2820 Upper stopper 710 M412286-1 1 1 75 C B

20-5 6922 4480 Key damper 710 M412324-1 1 1 55 C B

6920 8691 Music stand 590 M311760A-1 1 1 130 B B

Screws

23 0009 2680 Screw 4 x 8 15 50 2 C A

24 0009 2682 Screw 2.6 x 8 43 50 2 C A

25 0009 4588 Screw 2.6 x 18 21 50 2 C A

26 0009 6417 Screw 4 x 10 32 50 2 C A

Notes: N – New parts

M – Minimum order/supply quantity

R – Rank

— 17 —

Page 21

EXPLODED VIEW

— 19 —

Page 22

MA0200941A

Loading...

Loading...