Page 1

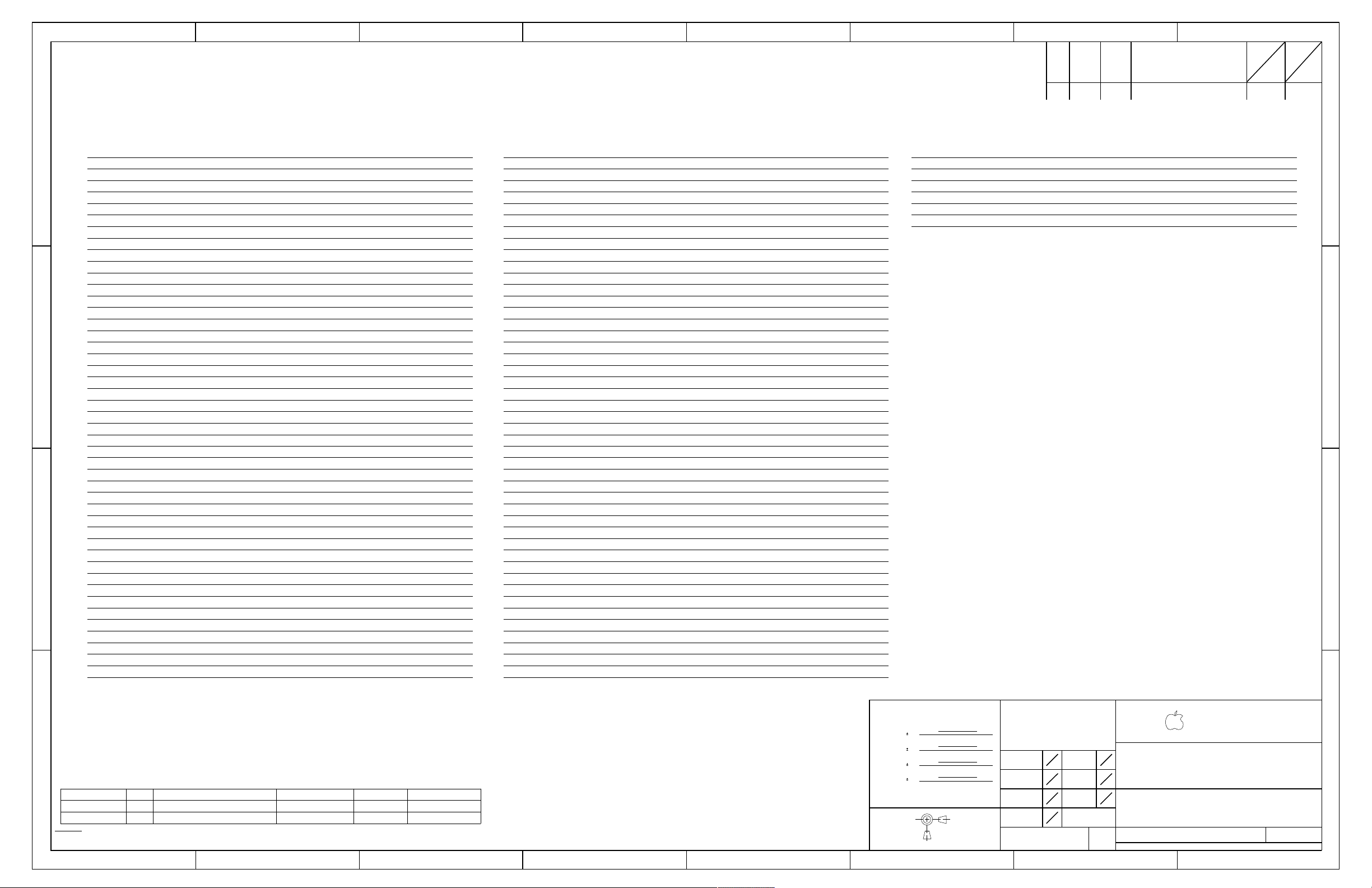

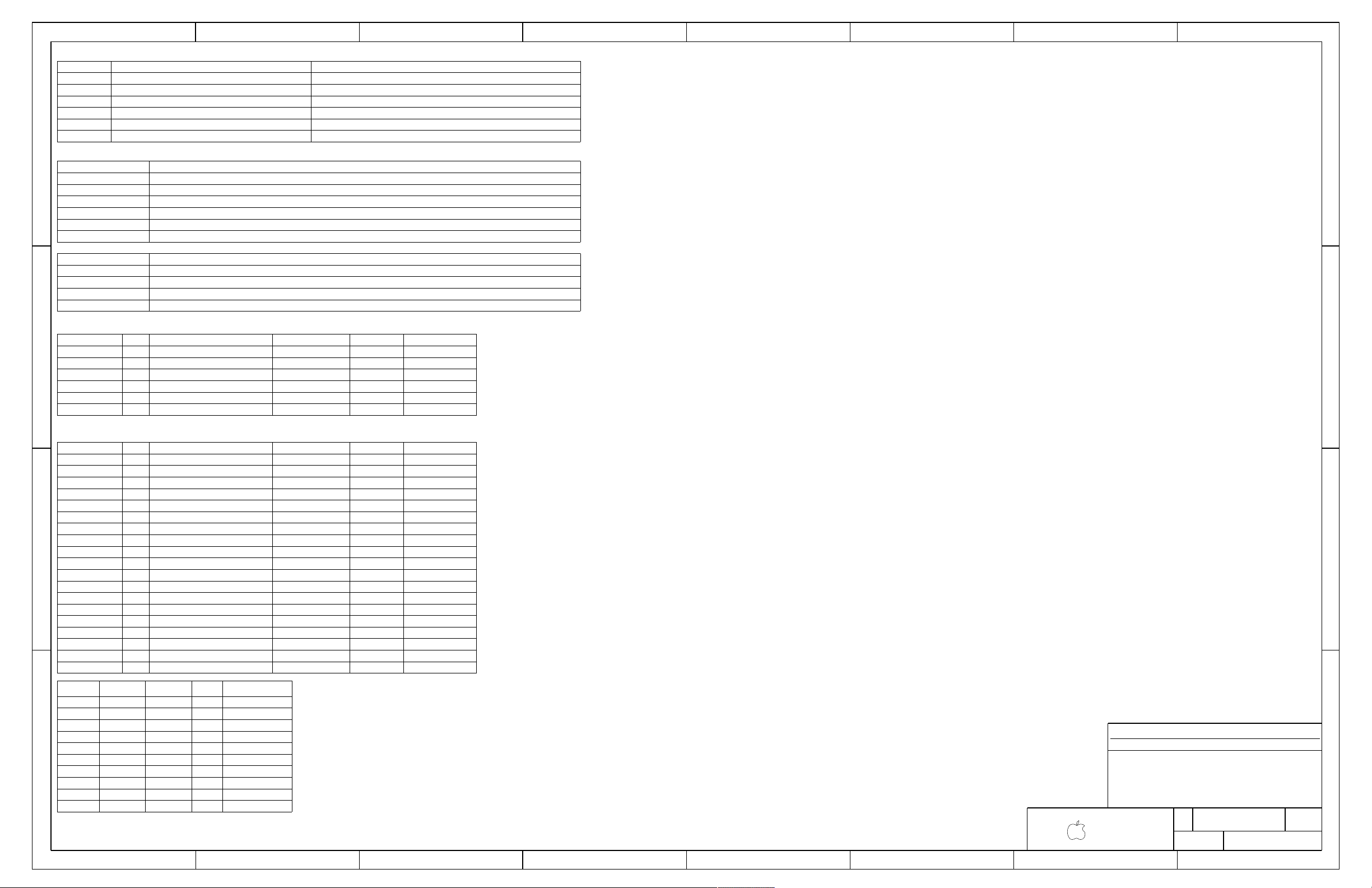

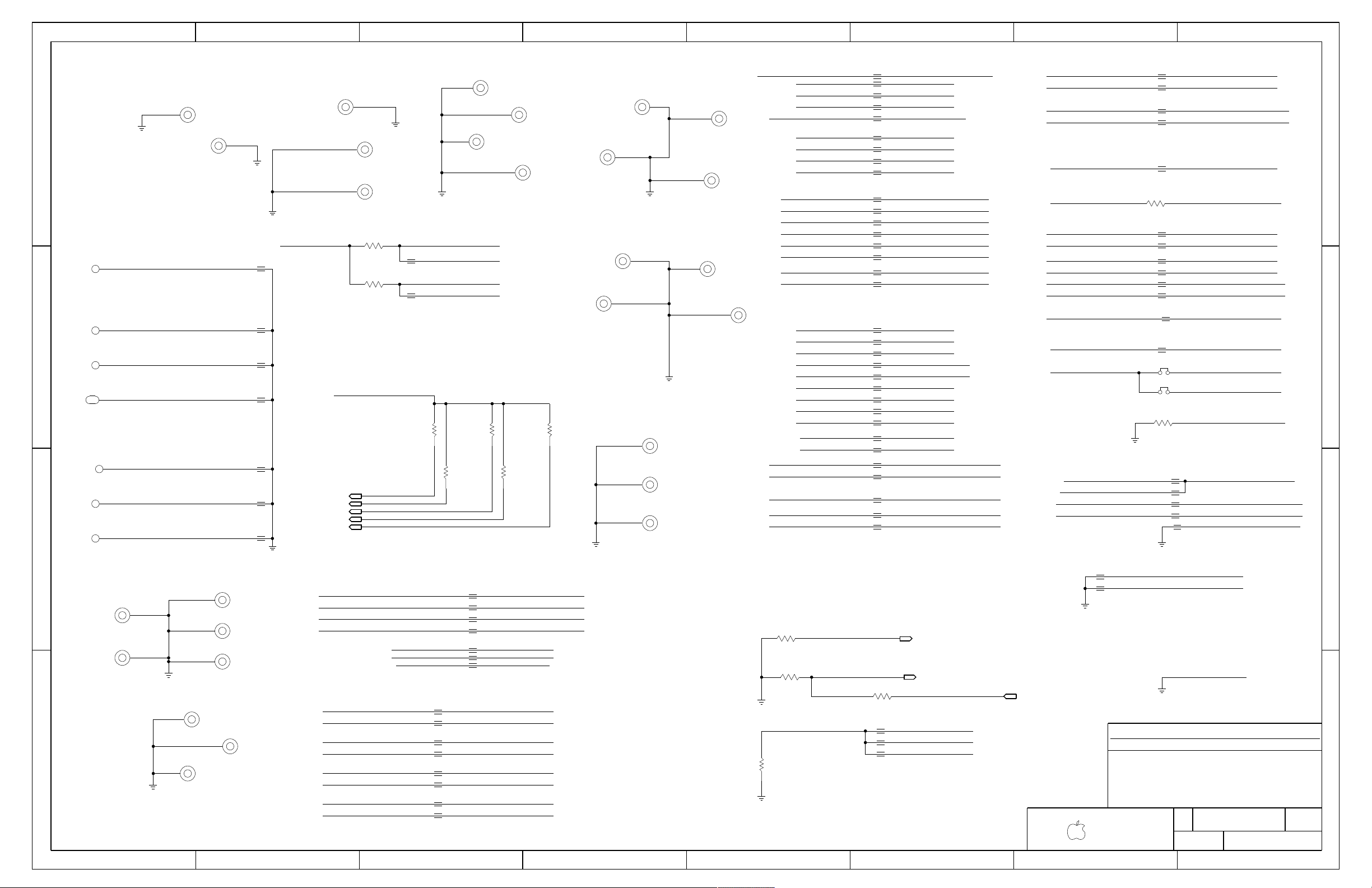

DRAWING

DESCRI PTION

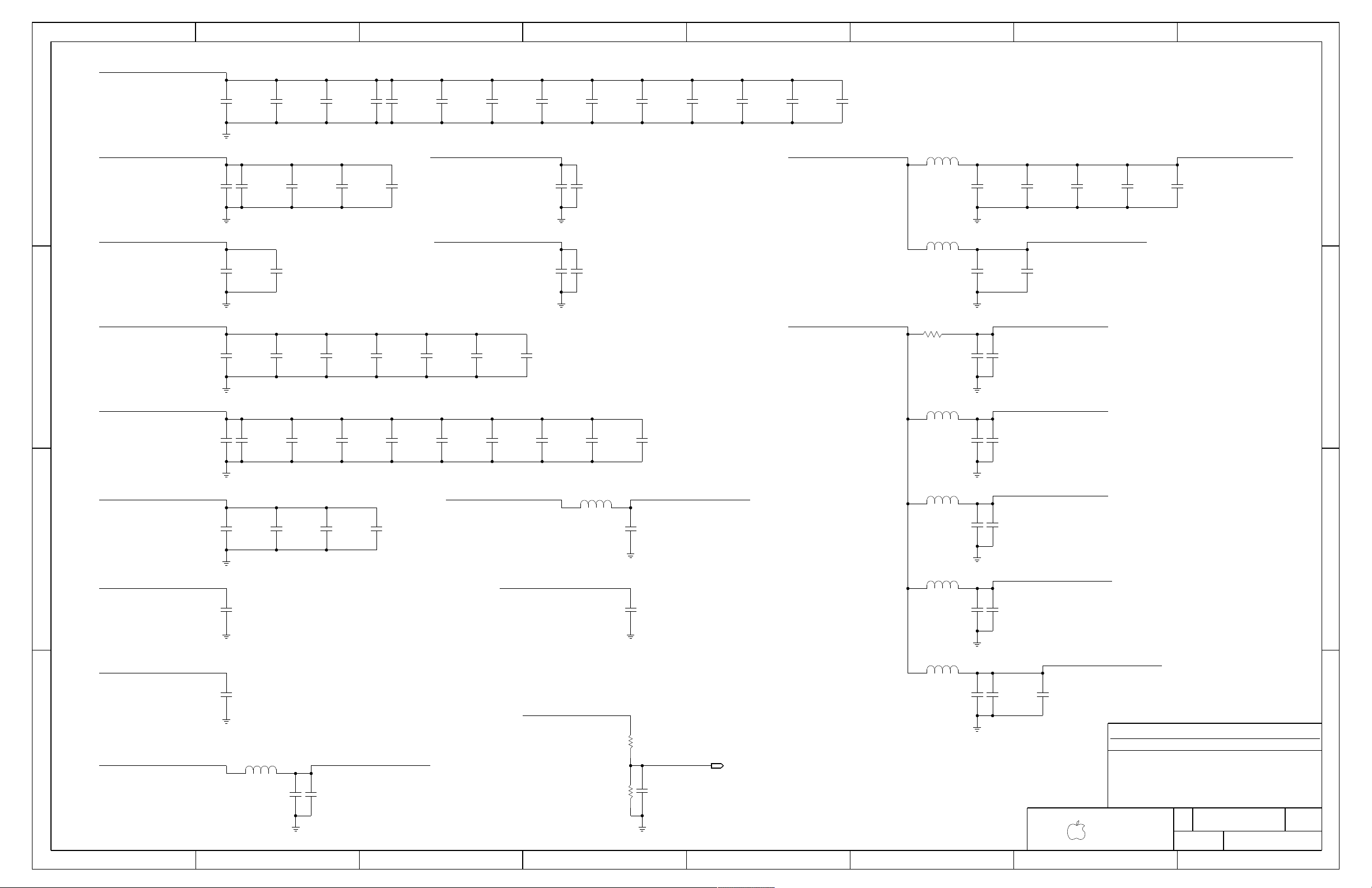

REFERE NCE DE S

BOM OP TION

QTY

PART N UMBER

CRITIC AL

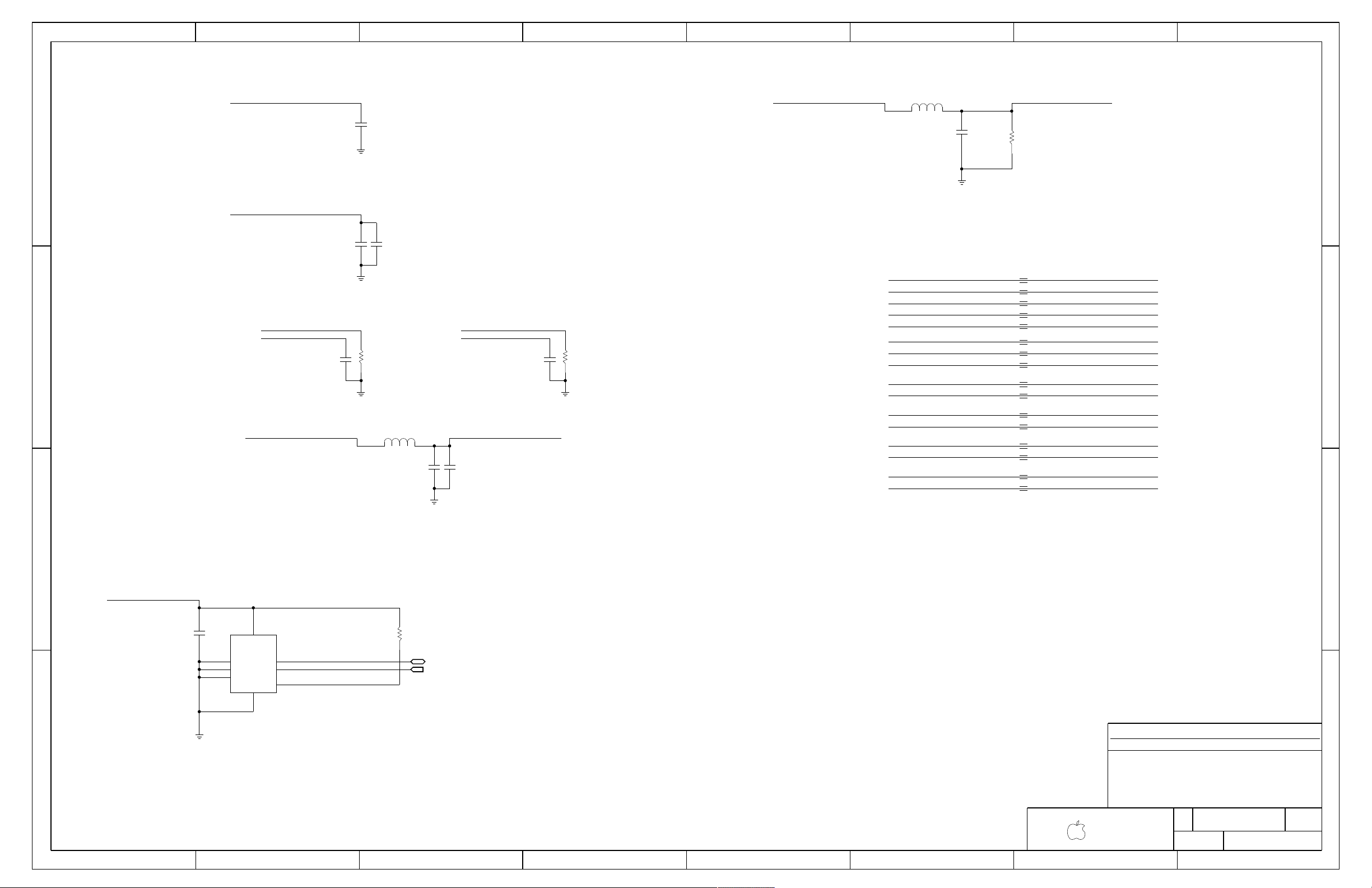

APPLE INC.

6

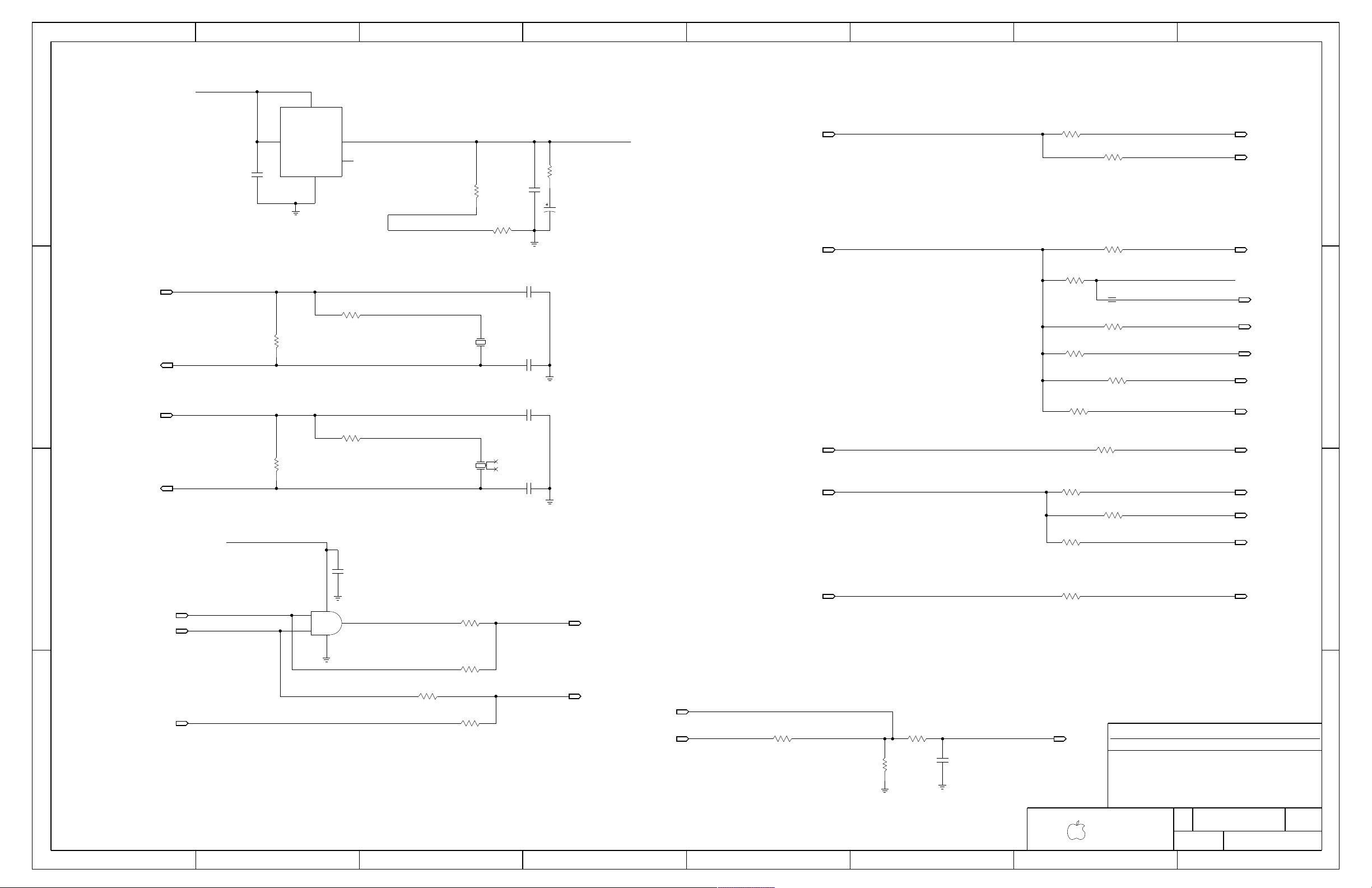

DESIGNER

DESCRI PTION O F CHAN GE

REV.

A

D

C

B

A

D

C

B

8 7

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

TITLE

DRAWING N UMBER

SHT

OF

METRIC

DRAFTER

ENG APPD

QA APPD

RELEASE

DESIGN CK

MFG APPD

SCALE

NONE

MATERIAL/ FINISH

NOTED AS

APPLICABL E

SIZE

D

THIRD ANG LE PROJECT ION

DIMENSION S ARE IN M ILLIMETER S

XX

X.XX

X.XXX

DO NOT SC ALE DRAWIN G

REV

ZONE

ECN

CK

APPD

DATE

ENG

APPD

DATE

1. ALL RESIST ANCE V ALUES A RE IN OHMS, 0 .1 WAT T +/- 5 %.

2. ALL CAPACI TANCE VALUES ARE IN MICROF ARADS.

3. ALL CRYSTA LS & O SCILLAT OR VAL UES ARE IN HE RTZ.

ANGLES

Schematic / PCB #'s

08/18/2008

SCHEM,MBP 15"MLB

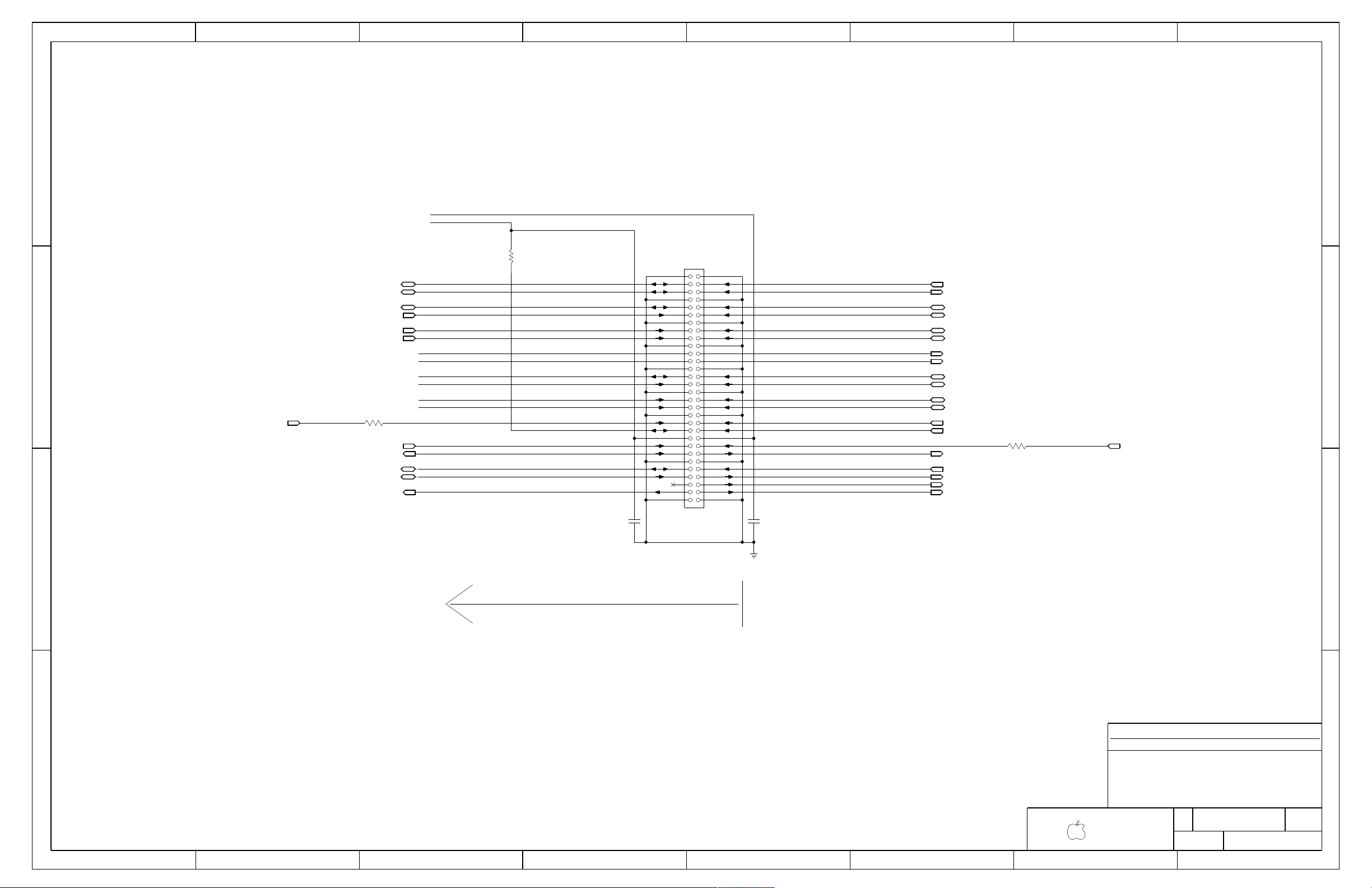

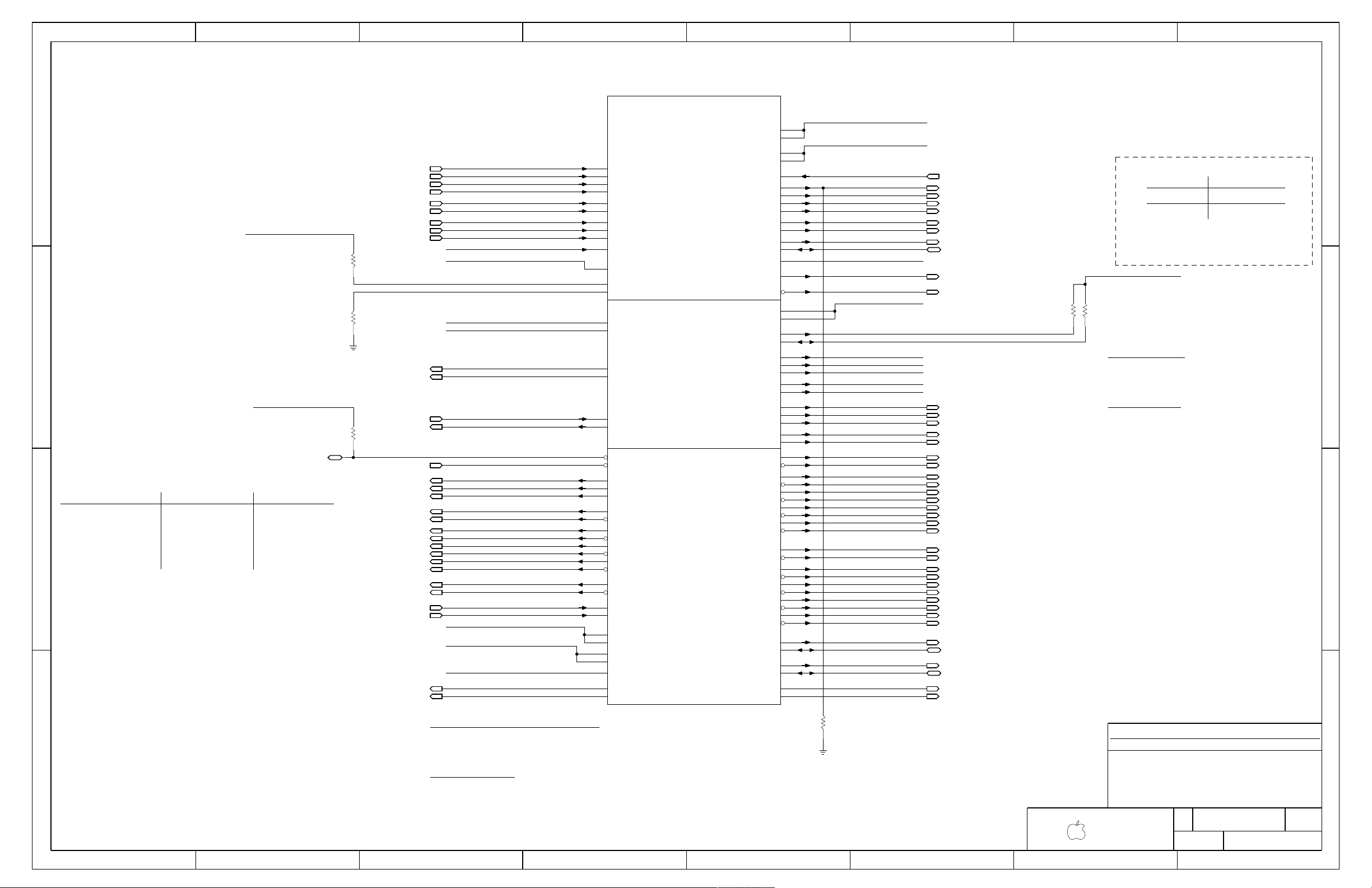

M98 SMBus Connections

45

DDR

07/22/20 08

52

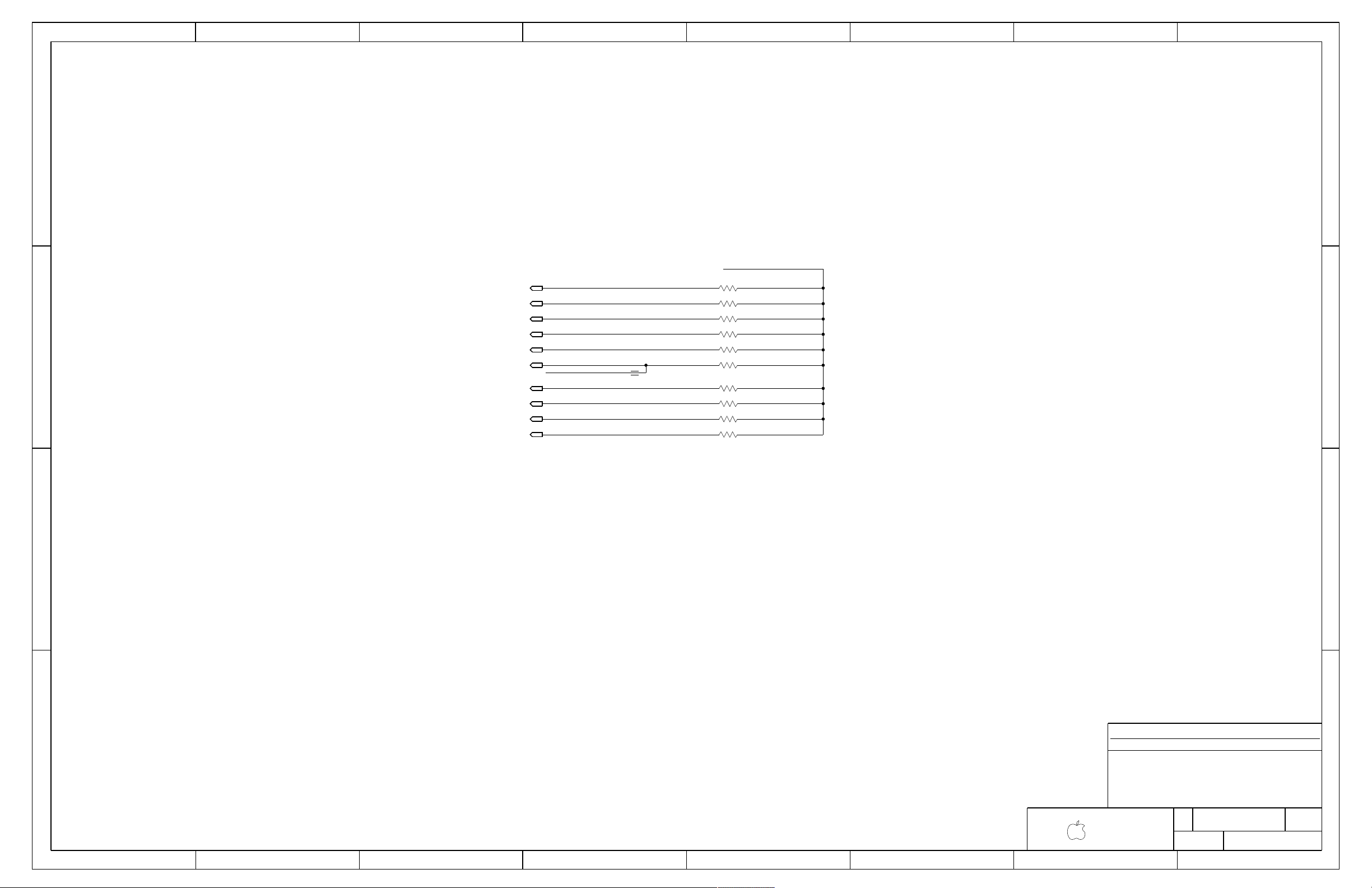

LPC+SPI Debug Connector

44

CHANG_M9 8_MLB

07/01/20 08

51

SMC Support

43

AMASON_M 98_MLB

06/18/20 08

50

SMC

42

T18_MLB

06/18/20 08

49

Front Flex Support

41

CHANG_M9 8_MLB

07/01/20 08

48

External USB Connectors

40

AMASON_M 98_MLB

07/02/20 08

46

SATA Connectors

39

CHANG_M9 8_MLB

07/01/20 08

45

FireWire Ports

38

SENSOR

08/14/20 08

43

FireWire Port Power

37

SENSOR

08/14/20 08

42

FireWire LLC/PHY (FW643)

36

SENSOR

08/14/20 08

41

Ethernet Connector

35

SUMA_M98 _MLB

07/01/20 08

39

Ethernet & AirPort Support

34

SUMA_M98 _MLB

07/01/20 08

38

Ethernet PHY (RTL8211CL)

33

SUMA_M98 _MLB

07/01/20 08

37

ExpressCard Connector

32

YITE_M98 _MLB

07/02/20 08

35

Right Clutch Connector

31

YITE_M98 _MLB

07/02/20 08

34

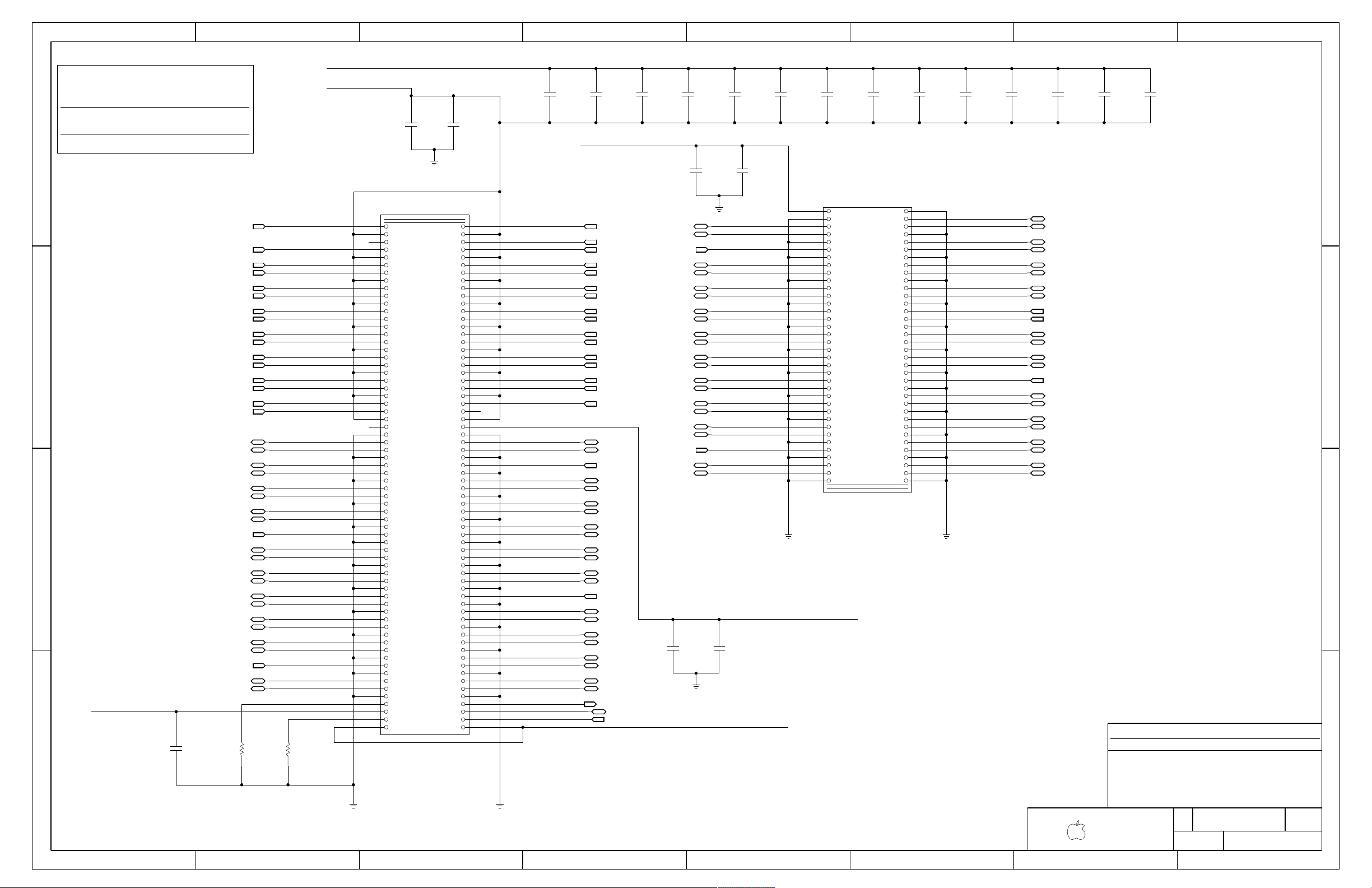

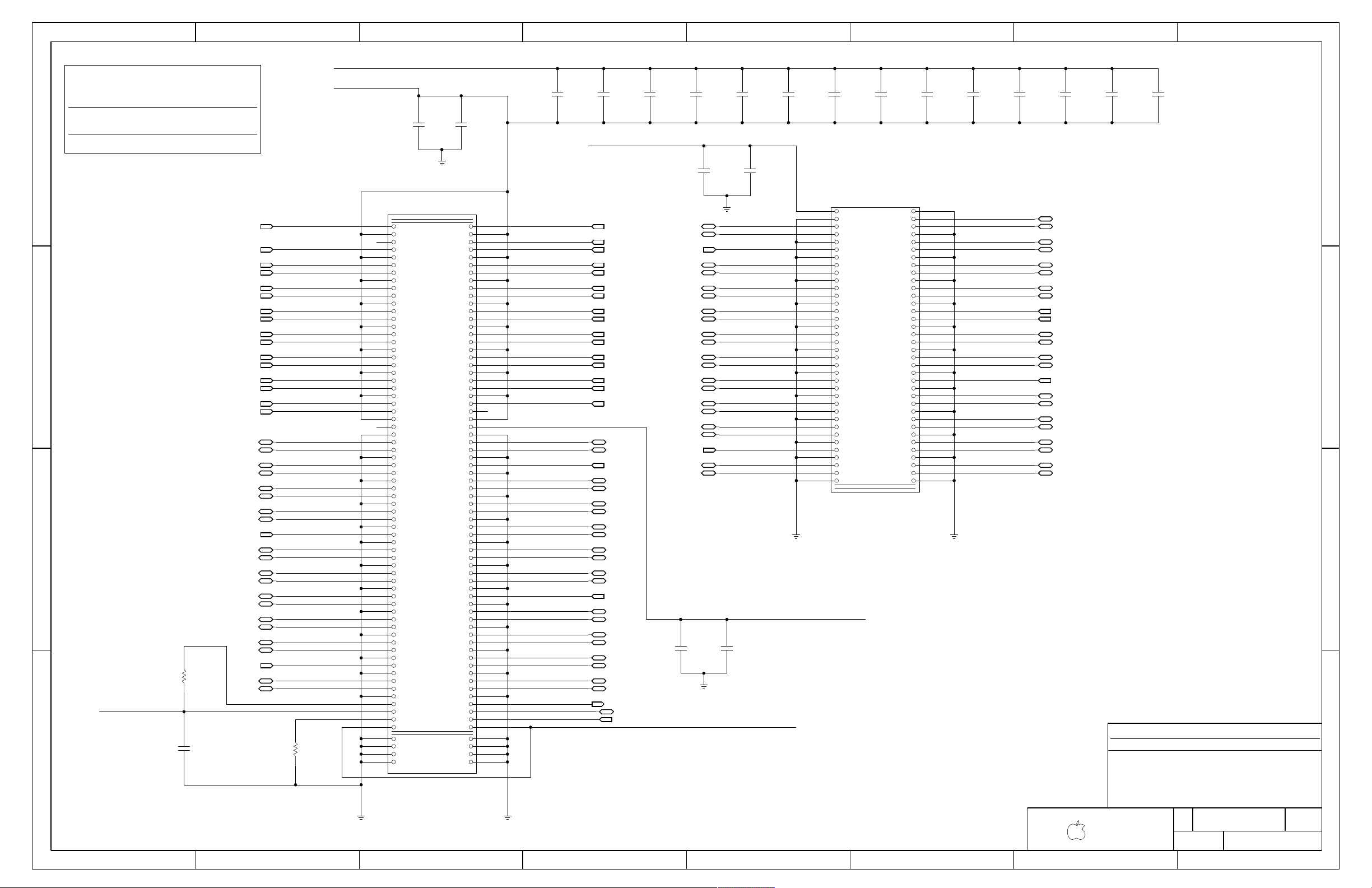

DDR3 Support

30

T18_MLB

06/18/20 08

33

DDR3 SO-DIMM Connector B

29

DDR

07/22/20 08

32

DDR3 SO-DIMM Connector A

28

DDR

07/22/20 08

31

FSB/DDR3/FRAMEBUF Vref Margining

27

DDR

07/22/20 08

29

SB Misc

26

T18_MLB

12/17/20 07

28

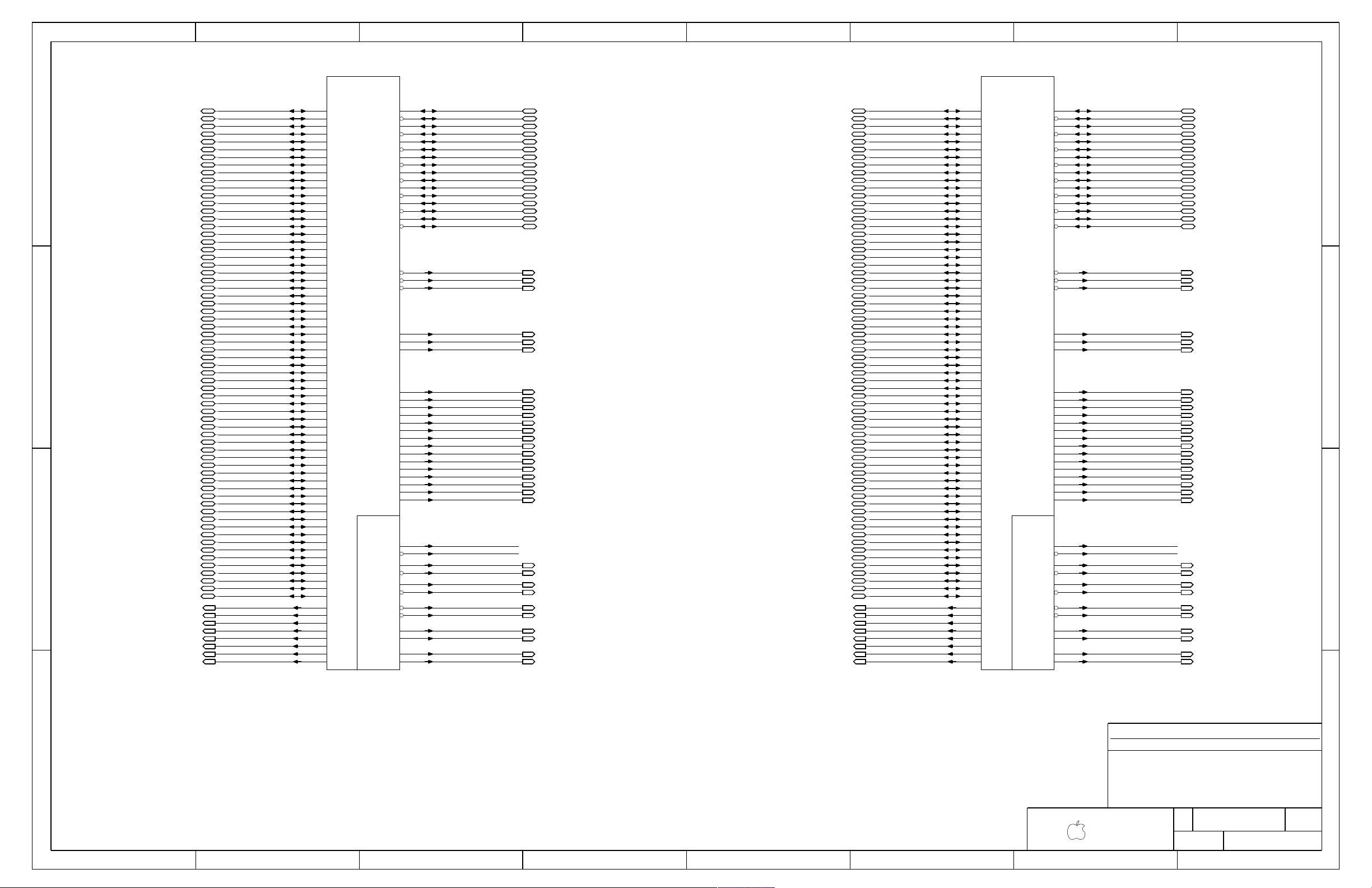

MCP Graphics Support

25

AMASON_M 98_MLB

06/18/20 08

26

MCP Standard Decoupling

24

T18_MLB

06/18/20 08

25

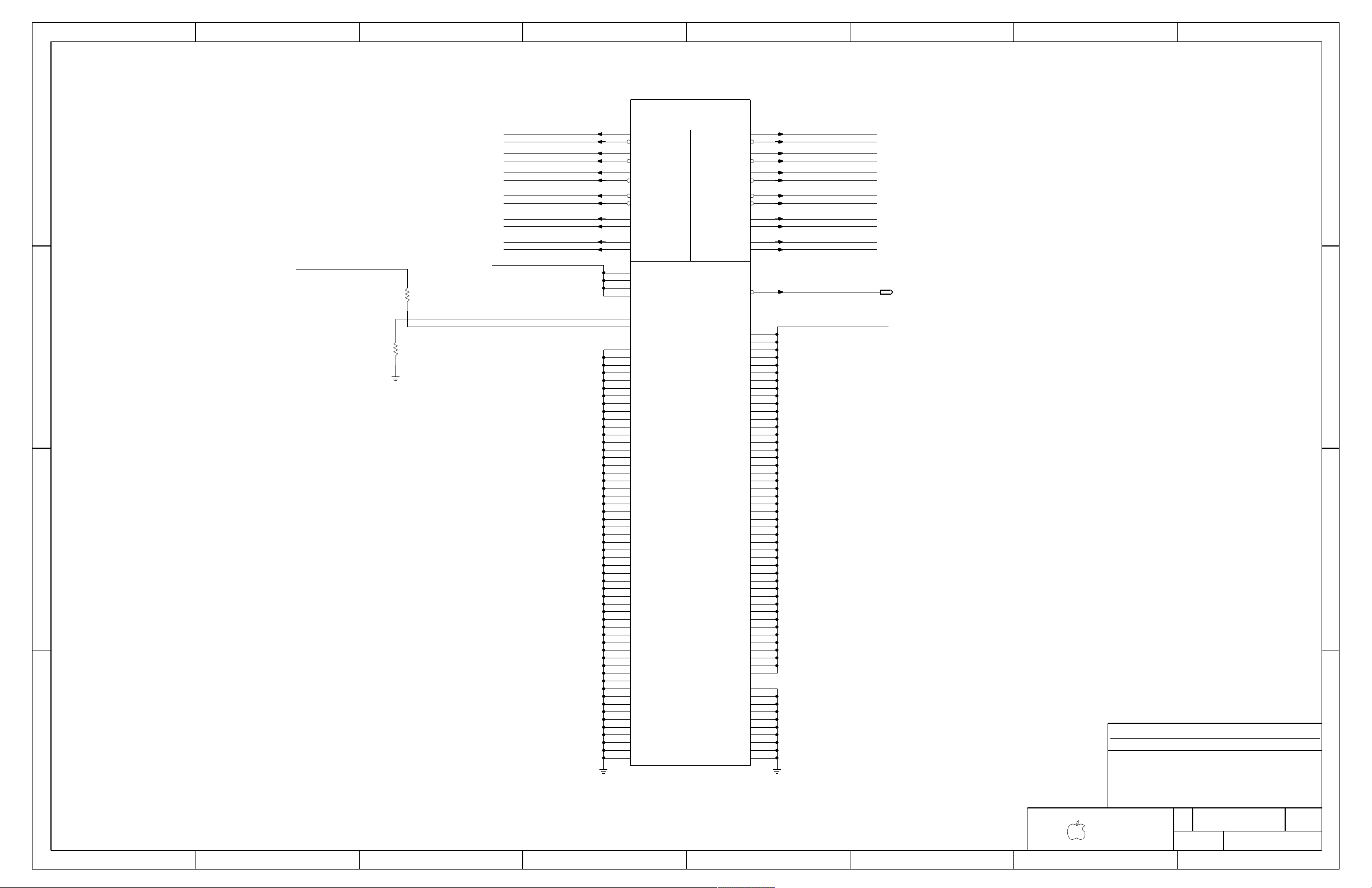

MCP79 A01 Silicon Support

23

T18_MLB

03/31/20 08

24

MCP Power & Ground

22

T18_MLB

06/18/20 08

22

MCP HDA & MISC

21

T18_MLB

06/18/20 08

21

MCP SATA & USB

20

T18_MLB

06/18/20 08

20

MCP PCI & LPC

19

T18_MLB

06/18/20 08

19

MCP Ethernet & Graphics

18

T18_MLB

06/18/20 08

18

MCP PCIe Interfaces

17

T18_MLB

06/18/20 08

17

MCP Memory Misc

16

T18_MLB

06/18/20 08

16

MCP Memory Interface

15

T18_MLB

06/18/20 08

15

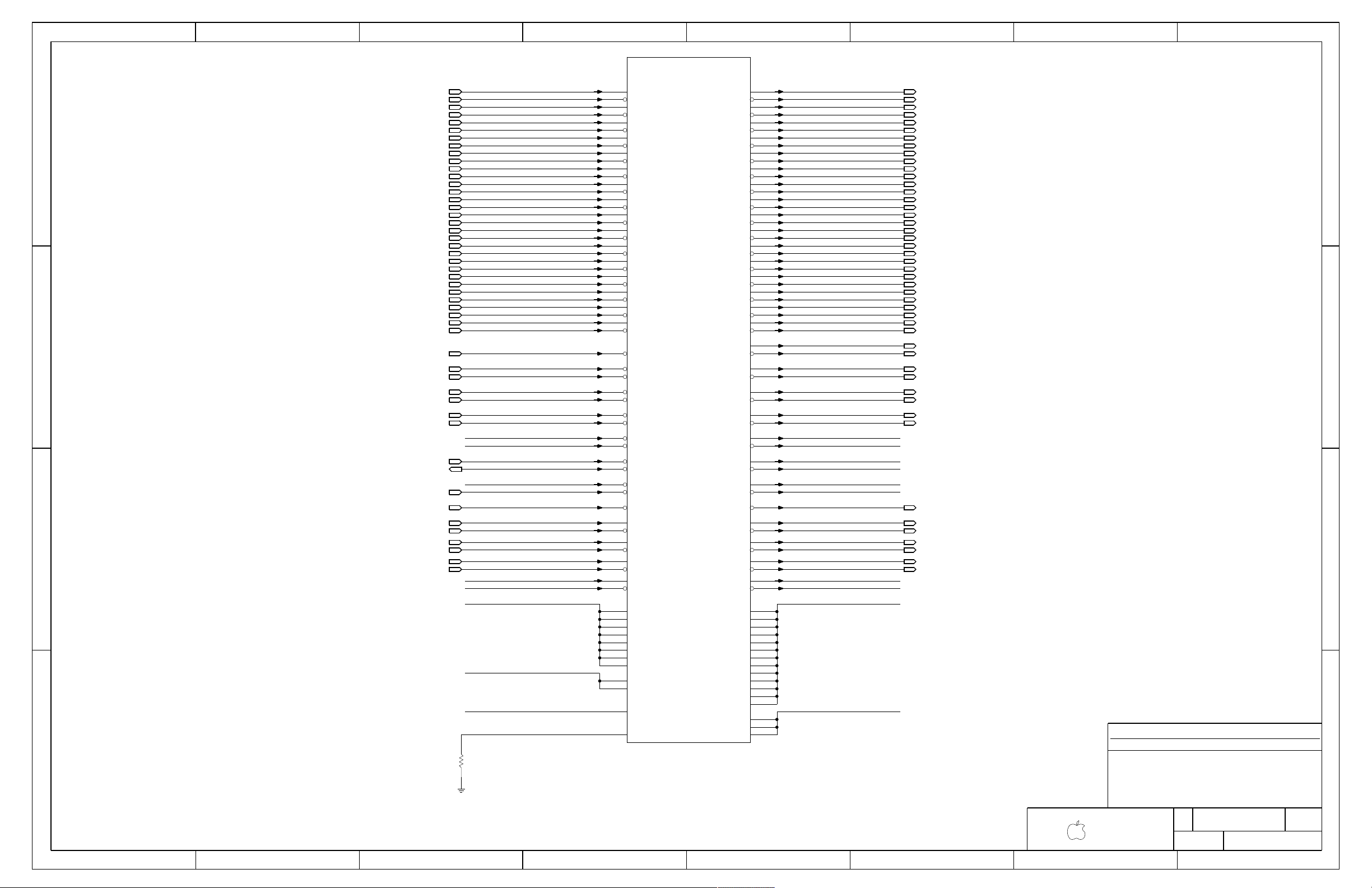

MCP CPU Interface

14

T18_MLB

06/18/20 08

14

eXtended Debug Port(MiniXDP)

13

M99_MLB

01/08/20 08

13

CPU Decoupling & VID

12

M87_MLB

10/17/20 07

12

CPU Power & Ground

11

M87_MLB

10/17/20 07

11

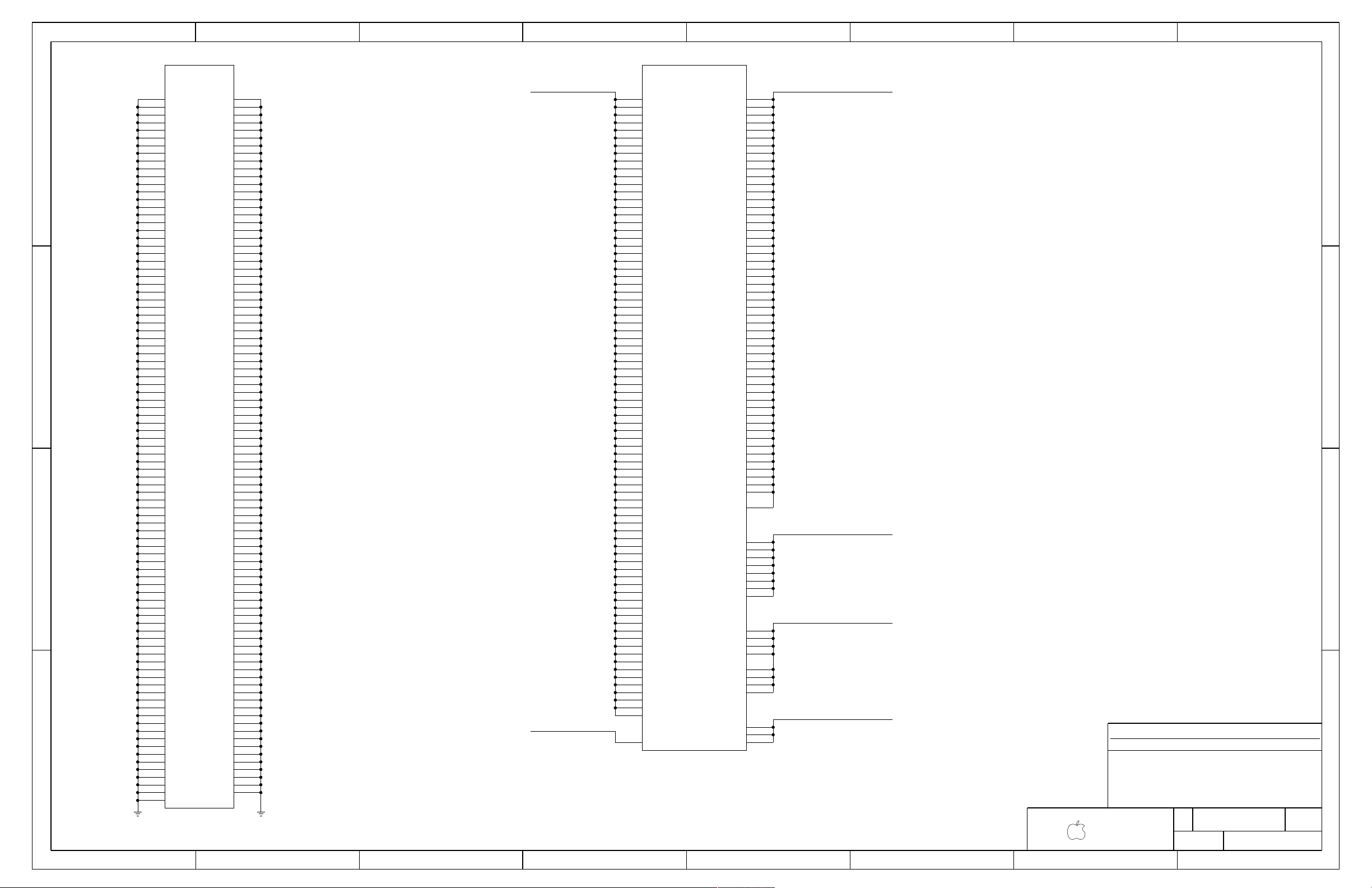

CPU FSB

10

M87_MLB

10/17/20 07

10

Signal Aliases

9

(MASTER)

(MASTER)

9

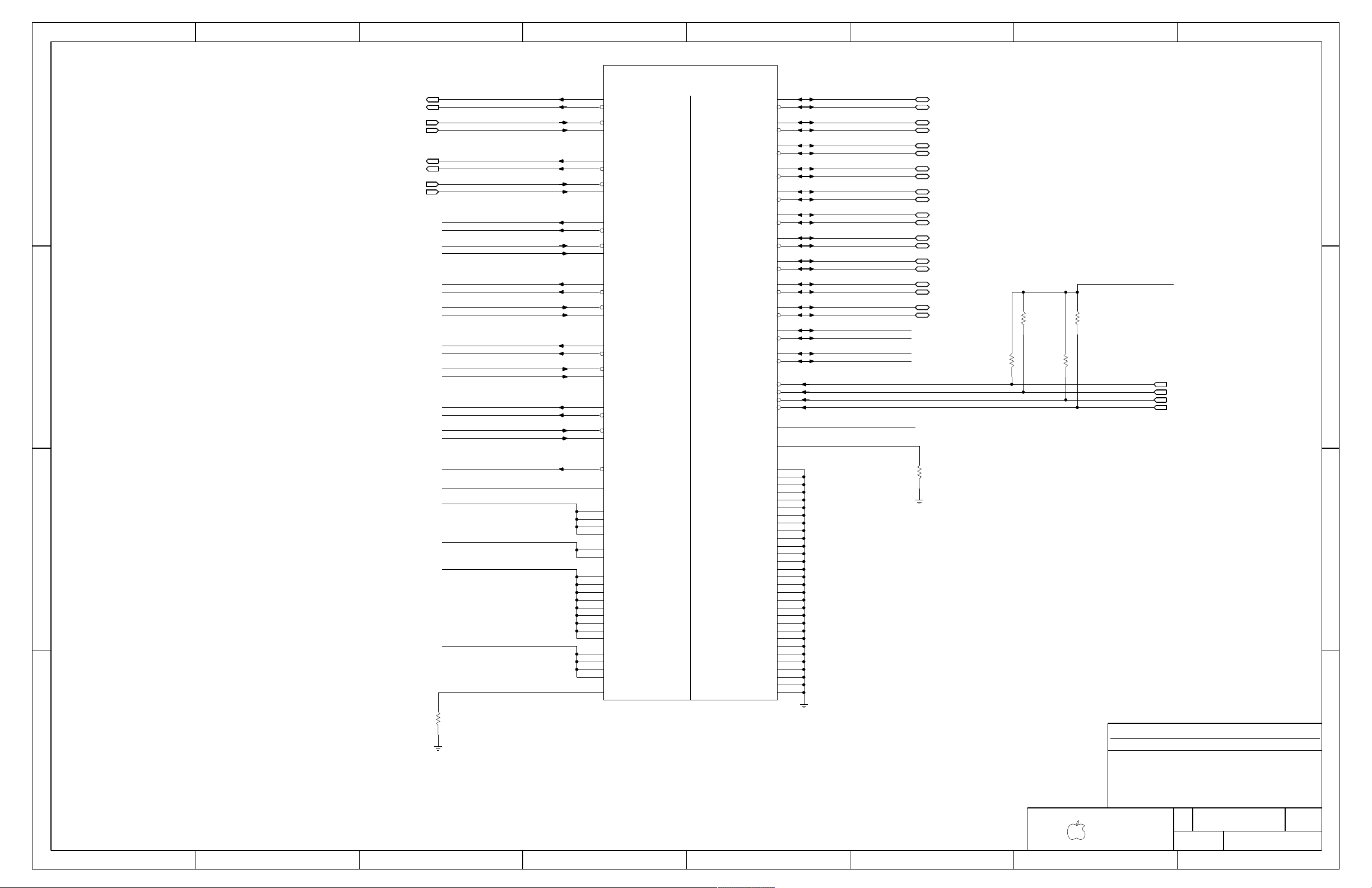

Power Aliases

8

(MASTER)

(MASTER)

8

Functional / ICT Test

7

N/A

N/A7

JTAG Scan Chain

6

DDR

07/22/20 08

6

BOM Configuration

5

N/A

N/A5

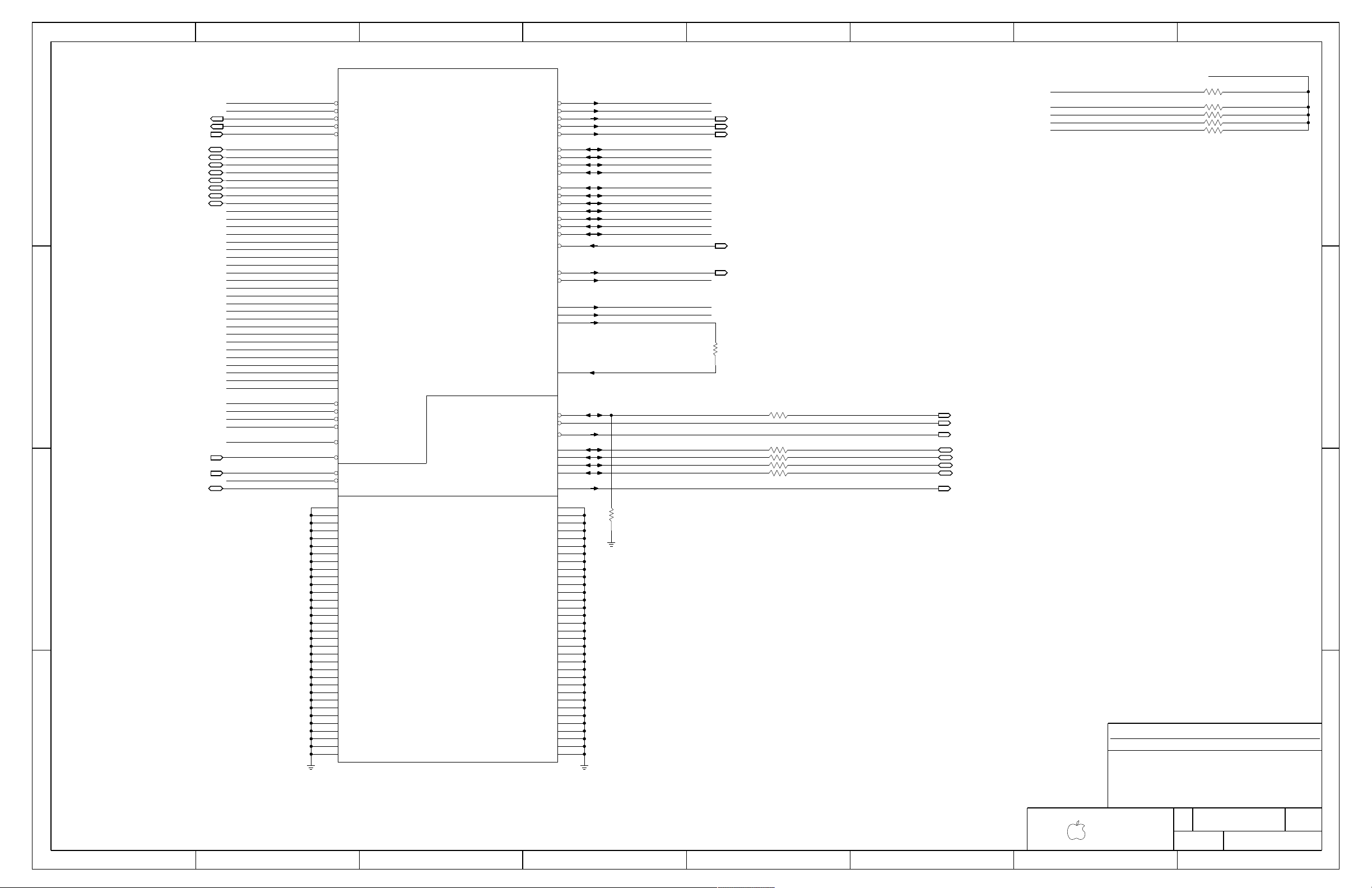

Power Block Diagram

4

N/A

N/A4

Power Block Diagram

3

T18_MLB

12/12/20 07

3

System Block Diagram

2

T18_MLB

12/12/20 07

2

MUXGFX

02/18/20 08

90

103

MCP Constraints 2

MUXGFX

02/18/20 08

89

102

MCP Constraints 1

MUXGFX

02/18/20 08

88

101

Memory Constraints

MUXGFX

02/18/20 08

87

100

CPU/FSB Constraints

MUXGFX

02/01/20 08

86

99

Misc Power Supplies

YITE_M98 _MLB

07/02/20 08

85

98

LCD Backlight Support

YITE_M98 _MLB

07/02/20 08

84

97

LCD BACKLIGHT DRIVER

MUXGFX

07/10/20 08

83

96

Graphics MUX (GMUX)

MUXGFX

07/10/20 08

82

95

1.1V / 1V8 FB Power Supply

MUXGFX

07/10/20 08

81

94

DisplayPort Connector

MUXGFX

07/10/20 08

80

93

Muxed Graphics Support

MUXGFX

02/25/20 08

79

90

LVDS Display Connector

M87_MLB

10/17/20 07

78

89

GPU (G84M) Core Supply

MUXGFX

07/10/20 08

77

88

NV G96 Video Interfaces

MUXGFX

07/09/20 08

76

87

G96 GPIOs & Straps

MUXGFX

07/10/20 08

75

86

NV G96 GPIO/MIO/Misc

MUXGFX

07/10/20 08

74

85

GDDR3 Frame Buffer B (Top)

MUXGFX

07/10/20 08

73

84

GDDR3 Frame Buffer A (Top)

MUXGFX

07/10/20 08

72

82

NV G96 Frame Buffer I/F

MUXGFX

07/10/20 08

71

81

NV G96 Core/FB Power

MUXGFX

07/10/20 08

70

80

NV G96 PCI-E

PWRSQNC

05/12/20 08

69

79

Power FETs

PWRSQNC

05/12/20 08

68

78

Power Control

M99_MLB

12/14/20 07

67

77

Misc Power Supplies

M99_MLB

12/14/20 07

66

76

CPU VTT Power Supply

M99_MLB

01/08/20 08

65

75

1.05V / MCP Core Regulator

M99_MLB

12/13/20 07

64

73

1.5V DDR3 Supply

M99_MLB

01/09/20 08

63

72

5V / 3.3V Power Supply

M87_MLB

10/17/20 07

62

71

IMVP6 CPU VCore Regulator

M99_MLB

12/10/20 07

61

70

PBus Supply & Battery Charger

T18_MLB

12/06/20 07

60

69

DC-In & Battery Connectors

AUDIO

07/09/20 08

59

68

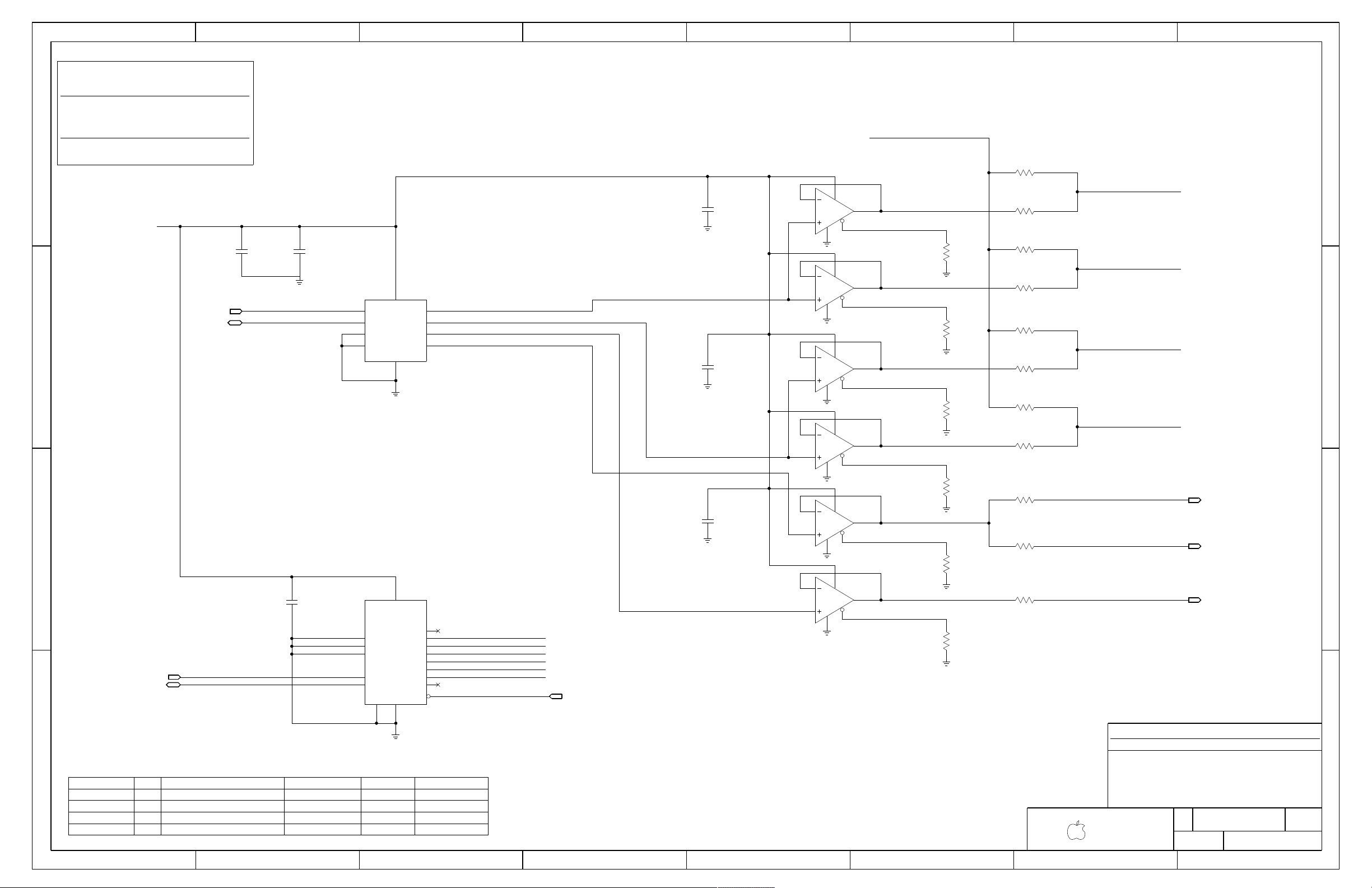

AUDIO: JACK TRANSLATORS

AUDIO

07/09/20 08

58

67

AUDIO: JACKS

AUDIO

07/09/20 08

57

66

AUDIO:SPEAKER AMP

AUDIO

07/09/20 08

56

65

AUDIO: HEADPHONE AMP

AUDIO

07/09/20 08

55

63

AUDIO: LINE IN

AUDIO

07/09/20 08

54

62

AUDIO:CODEC

CHANG_M9 8_MLB

07/01/20 08

53

61

SPI ROM

SENSOR

08/14/20 08

52

59

Sudden Motion Sensor (SMS)

PWRSQNC

05/12/20 08

51

58

WELLSPRING 2

AMASON_M 98_MLB

06/18/20 08

50

57

WELLSPRING 1

M87_MLB

10/17/20 07

49

56

Fan Connectors

SENSOR

08/14/20 08

48

55

Thermal Sensors

SENSOR

08/14/20 08

47

54

Current Sensing

96

109

PCB Rule Definitions

M99_MLB

01/22/20 08

95

108

Project Specific Constraints

MUXGFX

02/21/20 08

94

107

GPU (G96) Constraints

MUXGFX

02/18/20 08

93

106

SMC Constraints

MUXGFX

02/18/20 08

92

105

FireWire Constraints

MUXGFX

02/18/20 08

SENSOR

08/14/20 08

46

53

Current & Voltage Sensing

CRITIC AL051-75 46

1

SCH

SCHEM, FIBBO, M98

Contents Sync

Date

(.csa)

Page

Table of Contents

1

N/A

N/A1

TITLE=ML B

ABBREV=D RAWING

91

104

Ethernet Constraints

MUXGFX

02/18/20 08

Contents Sync

(.csa)

Date

Page

CRITIC AL820-23 30

1

PCBF,F IBBO,M 98

PCB

Contents

(.csa)

Sync

Date

Page

A.0.0

SCHEM,MBP 15MLB

?

1

? ?

? ?

96

051-7546

LAST_MODI FIED=Mon Aug 18 01 :48:34 20 08

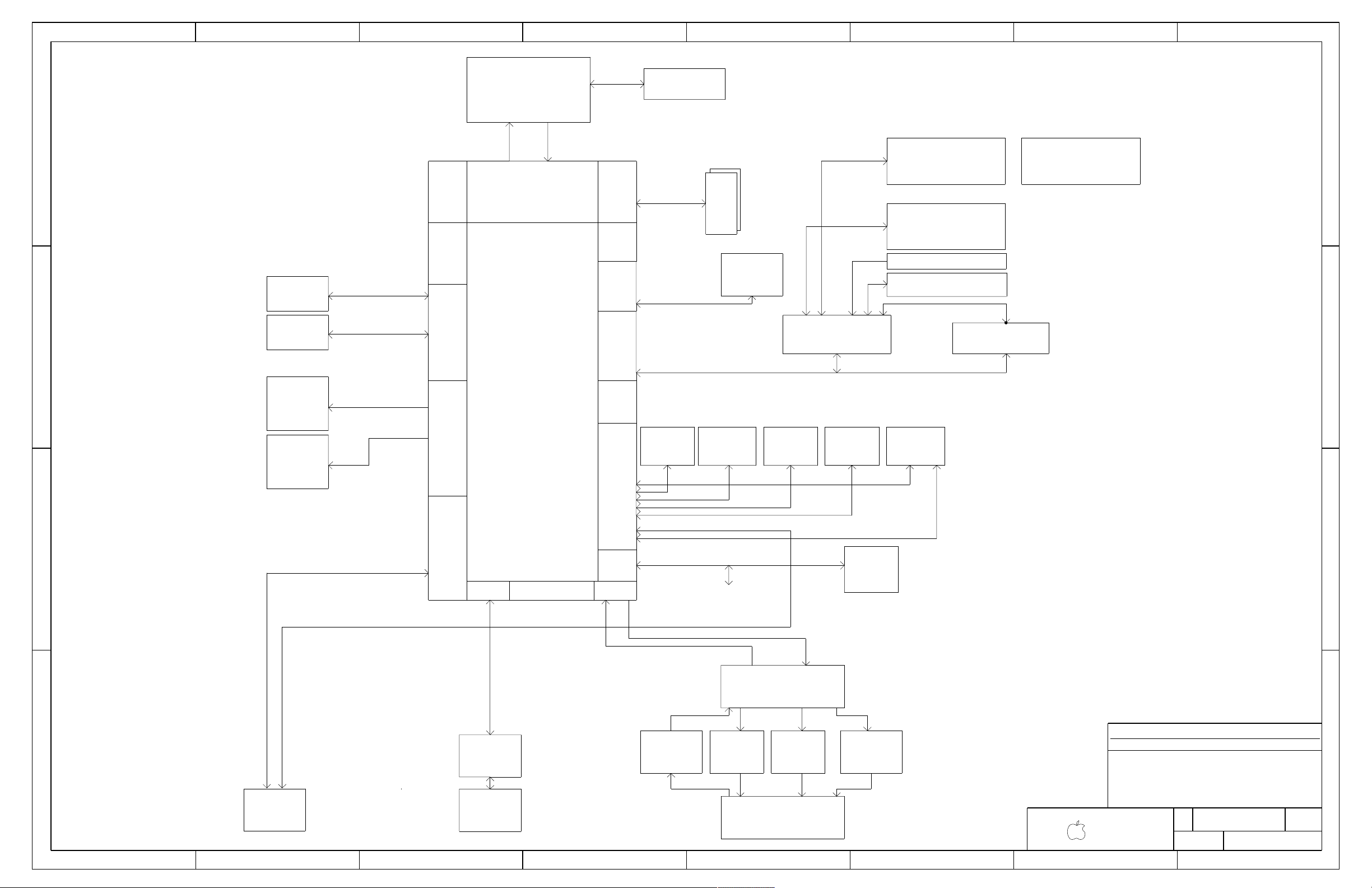

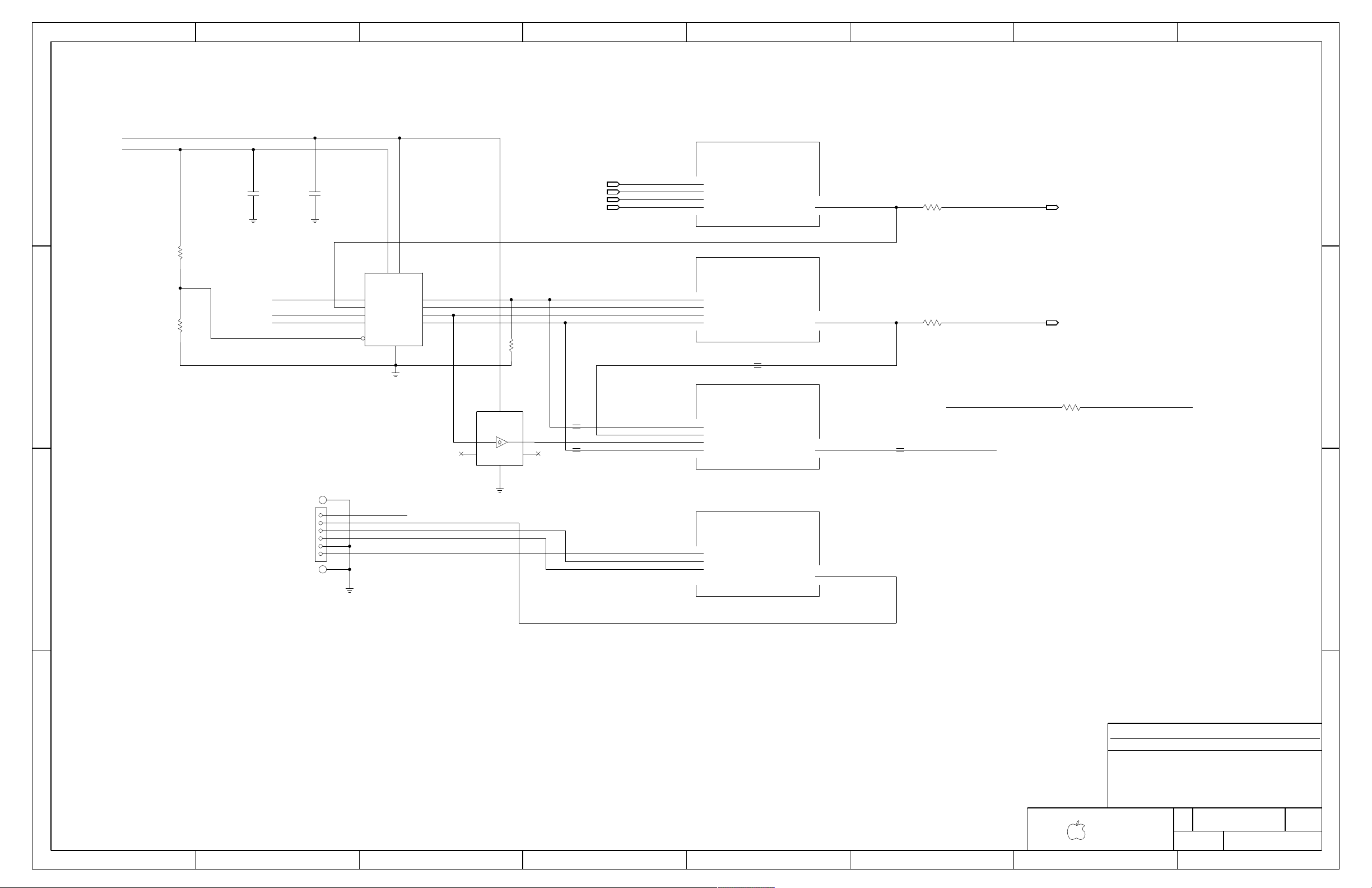

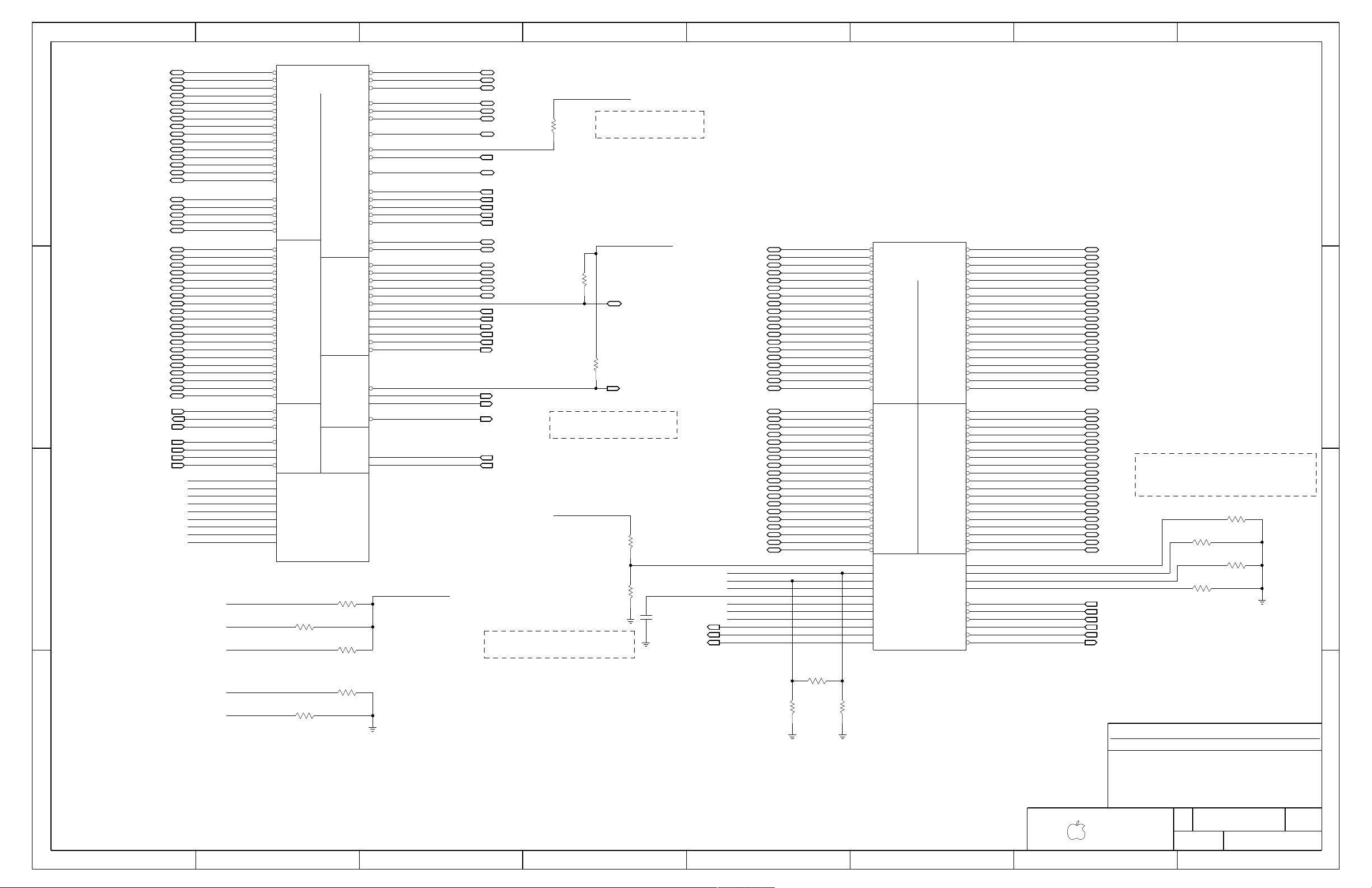

Page 2

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

DRAWING N UMBER

SHT

OF

SIZE

D

J9400

DISPLA Y PORT

J9000

CONN

LVDS

PG 71

CONN

PG 71

Conn

J4520

PG 17

(UP TO 1 2 DEVICE S)

4

TMDS OUT

Line O ut

2

CTRL

IR

J4710

CLK

SATA

(UP TO F OUR PORT S)

Conns

J6800,6801 ,6802,6803

PG 41

MCP79

PG 19

PCI

PG 19

LPC

3 8 9

PG 40

SATA

U6301 U6500U6400

PG 59

PG 56PG 55

HEADPH ONE

Audio

Audio

Codec

FSB

64-Bit

2 UDIMMs

XDP CONN

POWER SUPPLY

PG 28

J3400 U3900

PG 33

Conn

88E111 6

PG 31

GB

E-NET

Amp

Speake r

Amps

PG 54

PG 53

U6200

J4720

PG 57

J4710

U4900

J6950

PG 12

U1000

U1300

J4510

U6600,6605 ,6610,6620

PG 40

J4700

PG 40

HD

E-NET

ODD

Conn

SYNTH

PG 39

U6100

J3900,4635 ,4655

EXTERNAL

USB

PG 40

KEYBOARD

TRACKPAD/

USB

PG 45

POWER SENSE

J5650,5600 ,5610,5611, 5660,5720,5 730,5750

PG 48,49

J4900

DC/BATT

PENRYN

2.X OR 3.X GH Z

INTEL CPU

SPI

PG 20

PG 18

MEMORY

MAIN

800/1067 /1333 MHz

DDR2-800 MHZ

DDR3-106 7/1333MH Z

J2900

DIMM

PG 25,26

SPI

TEMP SENSOR

FAN CONN AND CONTROL

J5100

PG 43

Ser

FanADC

SMC

B,0

Prt

BSB

PWR

Misc

PG 14

Port80,serial

LPC Conn

GPIOs

SATA

1.05V/3GHZ .

1.05V/3GHZ .

RGB OUT

PG 38

PG 38

PG 13

FSB INTE RFACE

PG 24

SMB

PG 20

PG 20

HDA

NVIDIA

PG 41

CAMERA

Connecto rs

PG 44

CONN

SMB

DIMM's

10 5 6 7

Bluetooth

PG 52

Boot ROM

U1400

DVI OUT

PCI-E

PG 16

UP TO 20 LANES3

PG 17

LVDS OUT

DP OUT

HDMI OUT

RGMII

PG 18

AirPort

Mini PCI-E

U3700

Line I n

Amp Amp

PG 60

PG 9

System Block Diagram

SYNC_DA TE=12/ 12/2007

A.0.0

2 96

051-7546

SYNC_MA STER=T 18_MLB

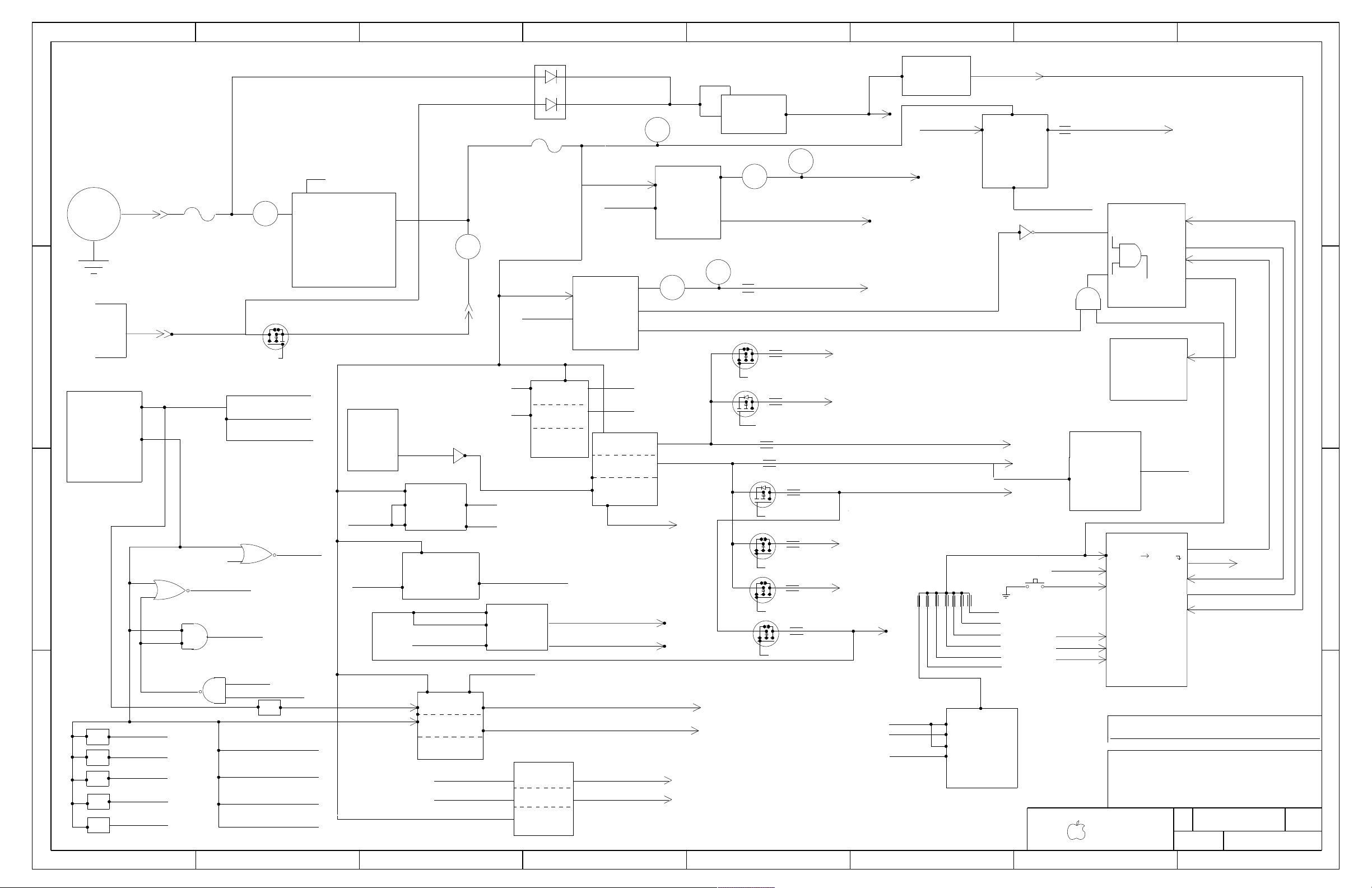

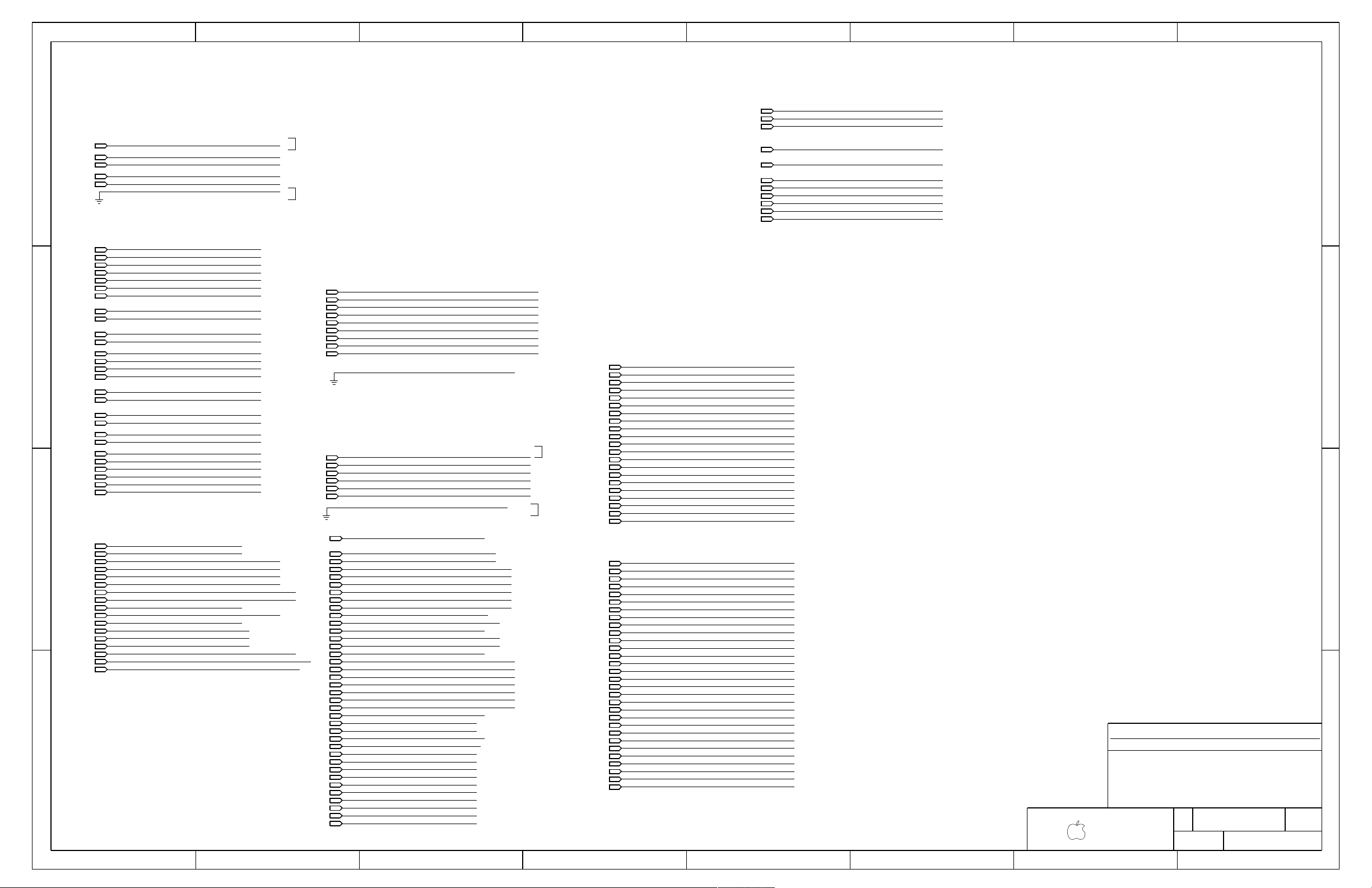

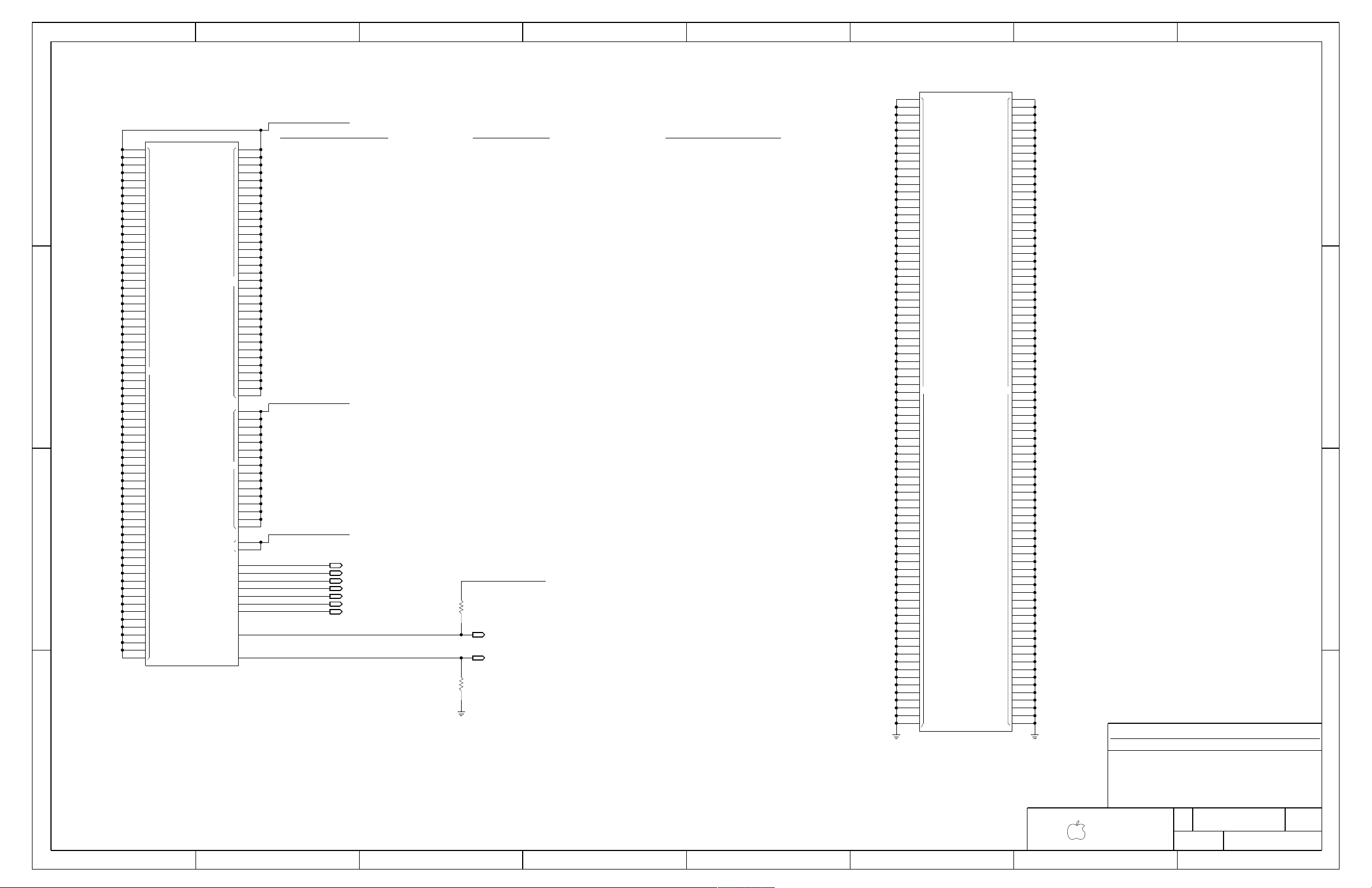

Page 3

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

DRAWING N UMBER

SHT

OF

SIZE

D

PP3V3_S 0GPU_F ET

P3V3S0_ SS

(PAGE 42)

S0PGOOD_PWROK

P1V5S0_PGOOD

P3V3S3_ SS

(18A MAX CURRENT)

GPUVCORE_IOUT

RSMRST_ IN(P13 )

IMVP_VR _ON

PLT_RST *

PWR_BUT TON(P9 0)

PM_PWRB TN_L

SMC_ONO FF_L

RSMRST_ PWRGD

MCP_PS_PWRGD

PWROK

CPUPWRG D(GPIO 49)

PLT_RST_L

CK_PWRG D

VR_PWRGD_CLKEN

VRMPWRG D

PP5V_S0 _FET

(25A MAX CURRENT)

(5A MAX CURRENT)

PM_SLP_S3_DELAY_L

SMC_ADAPTER_EN

PPVBAT_G3H_CHGR_R

CHGR_BGATE

J6950

BATT_POS_F

6A FUSE

DCIN(16.5V)

U7000

ISL6258A

BATTERY CHARGER

PBUS SUPPLY/

(PAGE 60)

PM_SLP_ S5_L

PM_SLP_ S4_L

PM_SLP_ S3_L

U4900

SLP_S3_ L(P93)

SLP_S4_ L(P94)

SLP_S5_ L(P95)

SMC_RESET_L

PM_RSMRST_L

99ms DLY

RSMRST_ OUT(P1 5)

PWRGD(P1 2)

IMVP_VR _ON(P1 6)

PP1V05_ S5_MCP

(PAGE 68)

LTC2900

P1V8S0_PGOOD

CPUVTTS0_PGOOD

MCPCORES0_PGOOD

P5VRIGHT_PGOOD

P1V05S0_PGOOD

P5VS0_SS

Q7900

PP5V_S3 _FET

P5VS3_SS

Q7910

PP3V3_S 3_FET

PP3V3_S 0_FET

P3V3GPU _SS

P3V3_EN ET_FET

P3V3ENE T_EN_L

(12A MA X CURR ENT)

PPDDR_S 3_REG

PPVTT_S 0_DDR_ LDO

PP5V_RT_REG

MCPCPCORE_S0_REG

(PAGE 65)

ISL6236

U7500

1.1V

MCP_CORE

P1V05S0_EN

MCPCORES0_EN

MCPCORES0_EN

CPUVTTS0_EN

MCPDDR_EN

P1V8S0_EN

P5VRIGHT_EN

P5VS0_EN

PM_SLP_S3_L

Q3800

WOL_EN

PM_ENET _EN_L

DDRVTT_EN

DDRREG_EN

U7300

(PAGE 63)

TPS51116

0.9V

1.8V

PPVIN_S0_DDRREG_LDO

P1V2ENET_EN

ENETAVDD_EN

PP1V2_E NET_RE G

PP1V9_E NET_RE G

(PAGE 33)

U3850

LTC3407

GOSHAW K6P

PPVOUT _S0_LC DBKLT

Q7930

Q7970

P5V3V3_ S5_PGOOD

P5V_RT _PGOOD

PP5V_R T_REG

PP3V3_S 5_REG

(5.5A M AX CUR RENT)

PP5V_S5 _REG

(8A MAX CURRE NT)

(PAGE 66)

U7750

ISL8009

CPUVTTS0_PGOOD

PPCPUVTT_S0_REG

CPUVTTS0_EN

PGOOD

(PAG 66)

U7600

TPS51117

VOUT

PP3V42_G3H_REG

(PAGE 59)

U6990

LT3470

3.425V G3HOT

GPU VCORE

U8900

ISL6263B

ISL9504B

CPU VCORE

(PAGE 62)

U7201

TPS51125

3.3V

5V

(PAGE 82)

U9500

TPS511 24

1.8V(R /H)

1.103V (L/H)

VIN

U7400

SC417

(PAGE 64)

(PAGE 84)

U9701

V4

PP1V8_GPU_REG

VOUT1

RST*

U7870

V1

V2

V3

V4

PP1V5_S0_REG

PP3V3_S0

PP5V_S0

VIN

VOUT2

CPUVCORE_IOUT

PPVCORE_CPU_S0

VOUT2

VLDOIN

P3V3S5_EN

(R/H)

VOUT1

EN1

P1V1GPU_EN

PPBUS_G3H

U5400

PP1V1_S0GPU_REG

(PAGE 61)

Q7920

PM_ENET_EN_L

(S0)

P3V3S0_EN

DELAY

Q3805

SMC

LIO_DCIN_ISENSE

Q7055

VOUT1

VIN

EN0

VREG3

ENL

VIN

EN2

VIN

IN

SMC_RESET_L

ENABLE

U5000

RN5VD30A-F

VIN

(L/H)

ADAPTER

VOUT

P1V8FB_EN

VIN

VR_ON

VOUT

A

VIN

U2830

VOUT2

PGOOD1,2

VOUT2

U2850

CPU

U1000

SMC

PWRBTN#

PLTRST*

PWRGOOD

(PAGE 10,11)

RESET*

EN/PSV

S3

RUN1

ENA

EN2

VOUT1

VOUT1

RUN2

S5

VR_PWRGOOD_DELAY

RC

DELAY

RC

DELAY

RC

RC

DELAY

RC

DELAY

RC

MCP79

RSMRST*

U1400

(PAGE 14~22)

U1400

3S2P

A

P60

P5V_RT_EN

PBUSB_VSENSE

Q5315

ENABLES

A

AC

PM_GPUVCORE_EN

SMC PWRGD

IMVP_VR_ON_R

(PAGE 78)

PGOOD

U5498

SMC_GPU_VSENSE

VOUT

D6905

VOUT

U4900

VIN

BKLT_EN

(PAGE 14~22)

SLP_S3#(G17)

SLP_S5#(H17)

Q3810

VOUT

VIN

(S0)

(S0)

MCP79

(S0)

PBUSVSENS_EN

U7859

SMC_PM_G2_EN

(S5)

PGOOD

Q3801

WOW_EN

PM_ENET_EN

PM_WLAN_EN_L

P17(BTN_OUT)

(PAGE 42)

U5705

PPVCORE_GPU_REG

V

A

LIO_S3_EN

P5VS3_EN

P3V3S3_EN

(9 TO 12.6V)

U5715

8A FUSE

D6905

PPVBAT_G3H_CHGR_REG

SMC_BATT_ISENSE

EN_PSV

GPUVCORE_PGOOD

SMC_CPU_VSENSE

V

VR_PWRGD_CLKEN_L

VIN

U7100

PGOOD

RST*

ALL_SYS_PWRGD

VOUT2

EN1

DELAY

PPBUS_G3H

V

PPVIN_G3H_P3V42G3H

PP3V3_S 5

PP5V_S3

(S5)

CHGR_EN

1.05V

EN_PSV

(PAGE 43)

CPU_PWRGD

(6A MAX CURRENT)

M98 POWER SYSTEM ARCHITECTURE

SYNC_MA STER=T 18_MLB

051-7546

96

A.0.0

SYNC_DA TE=12/ 12/2007

3

Power Block Diagram

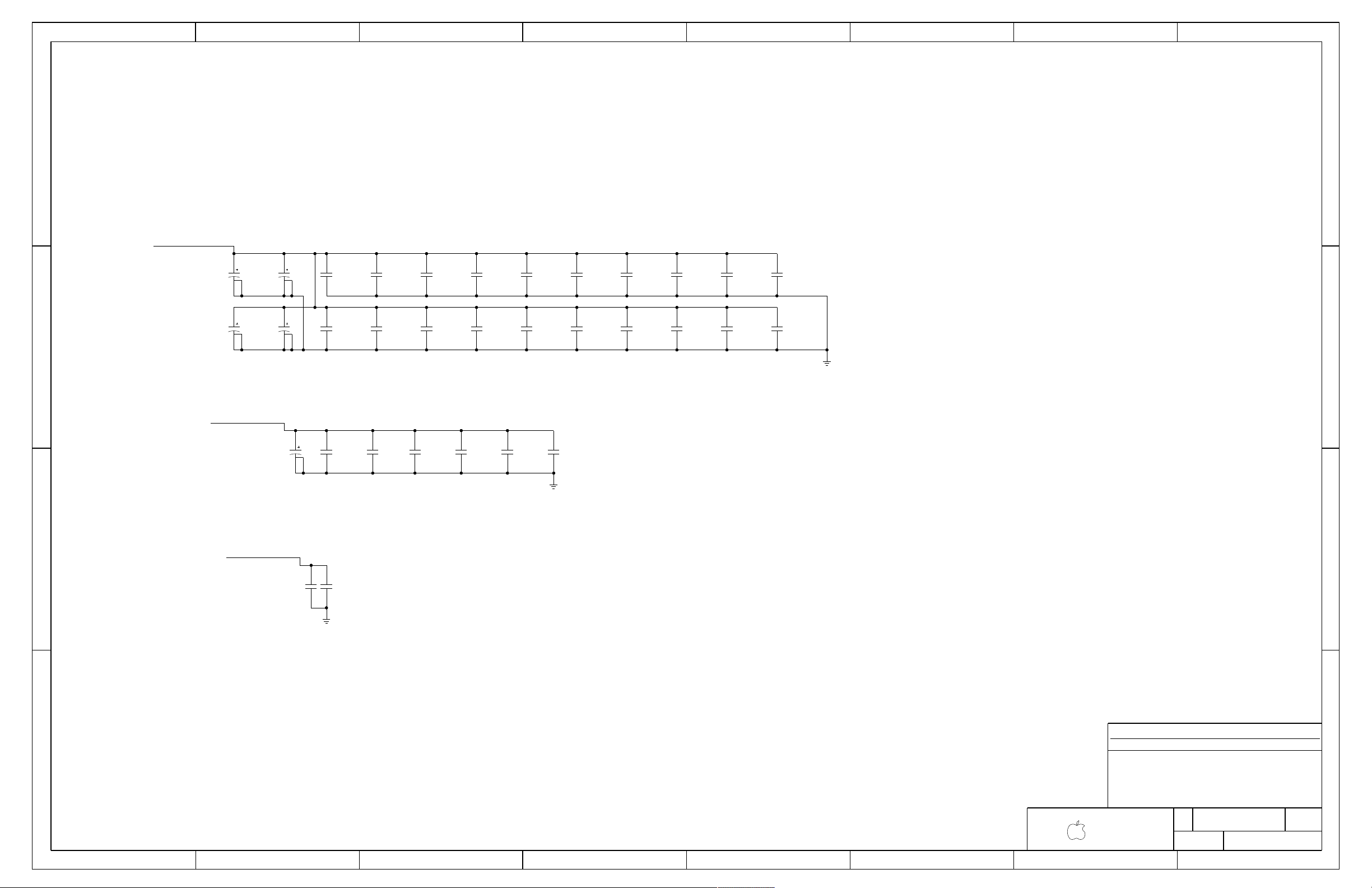

Page 4

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

DRAWING N UMBER

SHT

OF

SIZE

D

SYNC_MA STER=N /A

SYNC_DA TE=N/A

4 96

A.0.0

051-7546

Power Block Diagram

www.laptop-schematics.com

Page 5

BOM OP TIONS

BOM GR OUP

DESCRI PTION

REFERE NCE DE S

BOM OP TION

QTY

PART N UMBER

CRITIC AL

PART NUMB ER

ALTERNATE FOR

PART NUMB ER

BOM OPTIO N

REF DES

COMMENTS:

DESCRI PTION

REFERE NCE DE S

BOM OP TION

QTY

PART N UMBER

CRITIC AL

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

DRAWING N UMBER

SHT

OF

SIZE

D

BOM OP TIONS

BOM GR OUP

BOM OP TIONS

BOM NA ME

BOM NU MBER

BOM Variants

Bar Code Labels / EEE #'s

Module Parts

M98 BOM Groups

M98_CO MMON

ALTERN ATE,CO MMON,M9 8_COMM ON1,M9 8_COMM ON2,M98 _COMMO N3,M98 _DEBUG ,M98_P ROGPART S

M98_DE BUG

M98_PR OGPART S

M98_CO MMON3

630-95 86

M98_COM MON,EEE_ 2NJ,CPU_ 2_8GHZ,F B_512_Q IMONDA

PCBA,2 .8GHZ, 512QIM_ VRAM,M 98

630-93 35

M98_COM MON,EEE_ 0ZB,CPU_ 2_4GHZ,F B_256_H YNIX

PCBA,2 .4GHZ, 256HYN_ VRAM,M 98

630-93 34

M98_COM MON,EEE_ 0ZA,CPU_ 2_4GHZ,F B_256_S AMSUNG

PCBA,2 .4GHZ, 256SAM_ VRAM,M 98

CRITIC AL826-4393

1

EEE_2N H

LBL,P/N LABEL,P CB,28MM X 6 MM

[EEE:2 NH]

BOM Configuration

5 96

051-7546

SYNC_MA STER=N /A

SYNC_DA TE=N/A

A.0.0

U4900

SMC_PRO G

341S22 89

1

CRITIC AL

IC,SMC, DEVELOPM ENT,M98

CRITIC AL

MCP_B0 1

U1400

338S06 00

1

IC,GMCP,M CP79-B01, 35x35MM,B GA1437

CRITIC AL1CPU_2_ 5GHZ

337S36 40

IC,PDC,SL3B X,PRQ,2.53G, 35W,1066,C0 ,6M,BGA

U1000

[EEE:0 ZD]

1

EEE_0Z D

CRITIC AL826-4393

LBL,P/N LABEL,P CB,28MM X 6 MM

1

CRITIC AL826-4393

EEE_0Z B

[EEE:0 ZB]

LBL,P/N LABEL,P CB,28MM X 6 MM

U4800

1

341S23 84

IR,ENCORE II, CY7C 63803-LQX C

CRITIC AL

CRITIC AL

1

338S05 54

IC,GPU, 55nm,NV G96-GS, BGA969, LF

U8000

M98_COM MON,EEE_ 0ZD,CPU_ 2_5GHZ,F B_512_Q IMONDA

630-93 37

PCBA,2 .5GHZ, 512QIM_ VRAM,M 98

VRAM4, VRAM_2 56_HYNI X

FB_256_ HYNIX

CRITIC AL

1

LBL,P/N LABEL,P CB,28MM X 6 MM

826-43 93

EEE_2N J

[EEE:2 NJ]

CRITIC AL

[EEE:0 ZC]

826-43 93

EEE_0Z C

1

LBL,P/N LABEL,P CB,28MM X 6 MM

CRITIC AL

1

338S05 63

U4900

SMC_BLA NK

IC,SMC, HS8/2117 ,9MMX9M M,TLP

U8770

HDCP_YE S

341S22 72

1

IC,HDCP R OM,NVG96, 8 PIN SO IC,LF,HF

CRITIC AL

CRITIC AL1CPU_2_ 4GHZ

337S36 39

IC,PDC,SLB4 N,PRQ,2.4G,2 5W,1066,M0, 3M,BGA

U1000

630-93 36

M98_COM MON,EEE_ 0ZC,CPU_ 2_5GHZ,F B_512_S AMSUNG

PCBA,2 .5GHZ, 512SAM_ VRAM,M 98

FB_512_ QIMONDA

VRAM4, VRAM_5 12_QIMO NDA

CRITIC AL

1

U3700

338S05 70

IC,RTL821 1CL,GIGE TRANSCEIV ER,48P TQ FP

CRITIC AL

1

U4100

338S05 23

IC,FW643-06 ,1394B PHY/O HCI LINK/PC I-E,12

338S06 35

IC,GMCP,M CP79-B02, 35x35MM,B GA1437

CRITIC AL

1

U1400

MCP_B0 2

BOOTROM _PROG

U6100

1

IC,EFI ROM,DEVE LOPMENT ,M98

341S23 66 CRITIC AL

CRITIC AL

1

U6100

BOOTROM _BLANK

335S03 84

IC,32MBIT 8-PIN SPI SERIAL F LASH,SOIC8

IC,SGRAM, GDDR3,16M x32,800MH Z,136 FBG A

U8400,U84 50,U8500,U 8550

VRAM_25 6_SAMSUN G

333S04 82 CRITIC AL

4

IC,SGRAM, GDDR3,32M x32,900MH Z,136 FBG A

VRAM_51 2_QIMOND A

CRITIC AL

4

333S04 72

U8400,U84 50,U8500,U 8550

341S23 83

IC,PSOC +W/USB, 56PIN,M LF,M98

CRITIC AL

1

U5701

TPAD_PR OG

138S0603

ALL

138S0602

Murata alt to Samsung

U8400,U84 50,U8500,U 8550

IC,SGRAM, GDDR3,32M x32,900MH Z,136 FBG A

VRAM_51 2_SAMSUN G

CRITIC AL333S0481

4

U8400,U84 50,U8500,U 8550

333S04 83

IC,SGRAM, GDDR3,16M x32,900MH Z,136 FBG A

4

CRITIC AL

VRAM_25 6_HYNIX

337S36 41

CPU_2_ 8GHZU1000

CRITIC AL

1

IC,PDC,SLB4 3,PRQ,2.8G,3 5W,1066,C0, 6M,BGA

ALL

353S1294

LMV2011,OPAMP. GBW

353S1681

ALL

514-0608

FOXLINK RCVR A LT TO FOXCONN

514-0613

ALL

157S0055

Delta alt to T DK Magnetics

157S0058

ALL

514-0607514-0612

FOXLINK XCVR A LT TO FOXCONN

152S0796

ALL

152S0915

Maglayers alt to Cyntec IND

ALL

341S2366341S2367

Macronix alt t o SST

353S1466

ALL

INTERSIL ALT T O INTERSIL

353S2312

ALL

152S0876 152S0867

Maglayer alt t o Delta

ALL

152S0276 152S0683

Maglayers alt to Dale/Vishay

CRITIC AL

LBL,P/N LABEL,P CB,28MM X 6 MM

1

826-43 93

EEE_0Z A

[EEE:0 ZA]

VRAM4, VRAM_5 12_SAMS UNG

FB_512_ SAMSUNG

630-95 85

M98_COM MON,EEE_ 2NH,CPU_ 2_8GHZ,F B_512_S AMSUNG

PCBA,2 .8GHZ, 512SAM_ VRAM,M 98

M98_CO MMON1

ONEWIR E_PU,I SL6258A ,MEMRE SET_HW ,MEMRE SET_MCP ,MCP_B 02,MCP _PROD, MCPSEQ _SMC

M98_CO MMON2

BKLT_P LL_NOT ,BMON_E NG,MIK EY,BOO T_MODE _USER,G PUVID_ 1P00V, MUXGFX

VRAM4, VRAM_2 56_SAMS UNG

FB_256_ SAMSUNG

DPMUX_ EN_S0, DP_ESD, EG_PWR SEQ_HW ,DP_CA _DET_EG _PLD,M CP_CS1 _NO

GMUX_P ROG,BO OTROM_P ROG,SM C_PROG ,TPAD_ PROG

SMC_DE BUG_YE S,XDP,L PCPLUS ,VREFM RGN

www.laptop-schematics.com

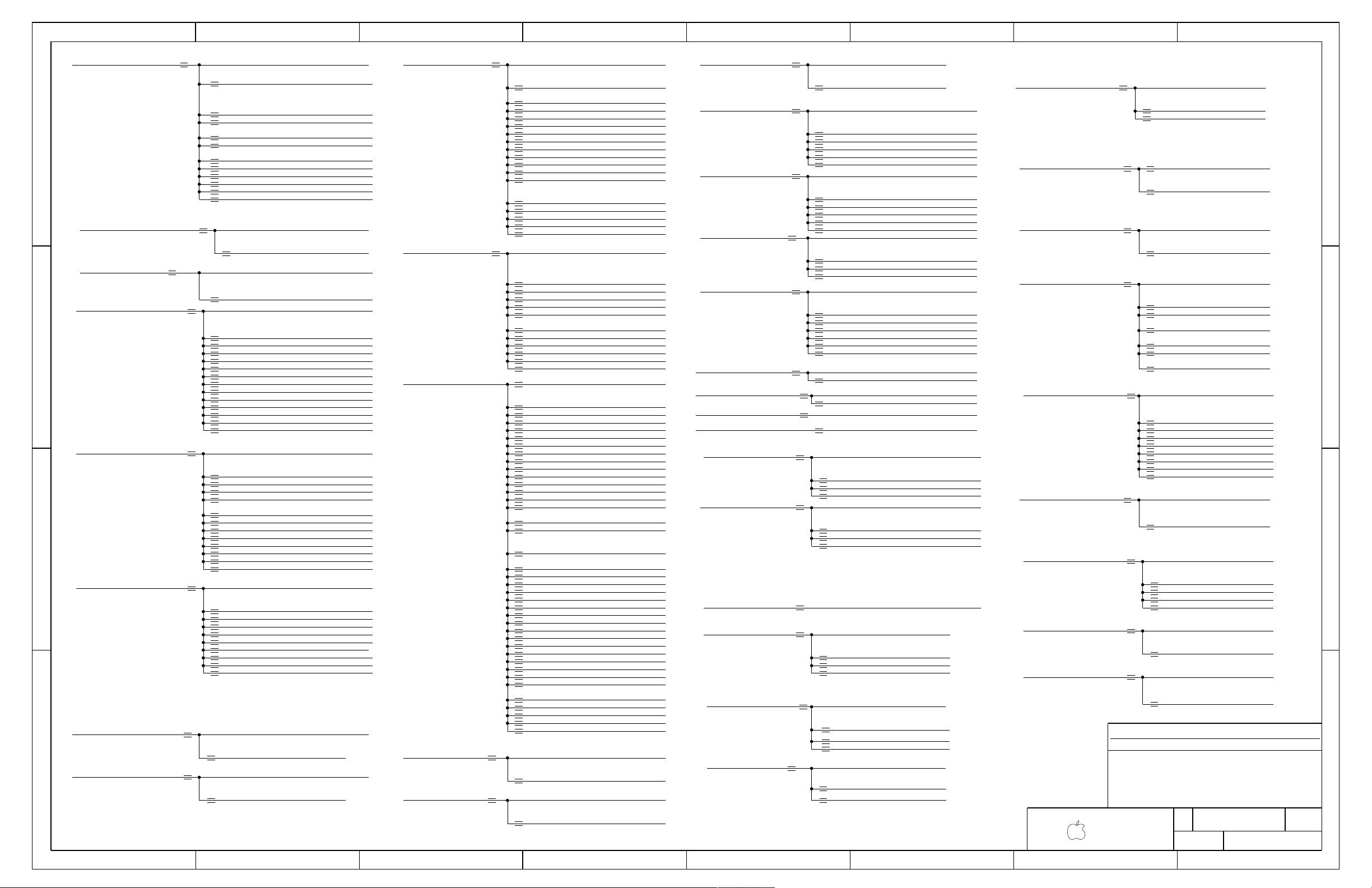

Page 6

IN

B1

OE*

VCCB

B2

B3

B4

GND

A4

A3

A2

A1

VCCA

OUT

GND

VCC

NCNC

YA

NC NC

IN

IN

IN

OUT

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

DRAWING N UMBER

SHT

OF

SIZE

D

TDO

1.05V TO 3.3V LEVEL TRANSLATOR (M98: ON ICT FIXTURE)

From XDP connector

or via level translator

GPU

U9200

GMUX

U8000

MCP

U1400

From XDP connector

U1000

CPU

To XDP connector

and/or level translator

XDP connector

XDP connector

TMS

TCK

TDI

GMUX CPLD Programming Port

6

10 13 87

NLSV4T244

UQFN

JTAG_ALLD EV

CERM

10V

402

20%

0.1UF

JTAG_AL LDEV

20%

10V

CERM

402

JTAG_AL LDEV

0.1UF

JTAG_AL LDEV

5%

10K

1/16W

MF-LF

402

0

1/16W

5%

MF-LF

402

NOSTUFF

13

CRITIC AL

1909782

M-RT-SM

402

MF-LF

1/16W

5%

0

XDP

PLACEM ENT_NO TE=Plac e near pin U 1000.A B3

0

1/16W

MF-LF

5%

402

XDP

PLACEM ENT_NO TE=Plac e near pin U 1400.F 19

74LVC1G 07

SOT886

PLACEM ENT_NO TE=Plac e clos e to U 0600

5%

MF-LF

1/16W

10K

NOSTUFF

402

PLACEM ENT_NO TE=Plac e clos e to U 8000

10K

5%

1/16W

MF-LF

402

6

10 13 87

10 13 87

6

10 13 87

13

051-7546

A.0.0

966

SYNC_MAS TER=DDR

SYNC_DAT E=07/22/ 2008

JTAG Scan Chain

=PP1V05_ S0_CPU

MAKE_BASE= TRUE

JTAG_M CP_TRS T_L

XDP_TC K

XDP_TD O

JTAG_G MUX_TC K

GPU_JT AG_TRS T_L

GPU_JT AG_TMS

=PP3V3_S 0_XDP

JTAG_M CP_TDI

JTAG_G MUX_TM S

GPU_JT AG_TCK

GPU_JT AG_TDO

MAKE_BASE= TRUE

TP_GPU _JTAG_ TDO

JTAG_M CP_TDO_ CONN

GPU_JT AG_TMS

=PP3V3 _GPU_V DD33

XDP_TR ST_L

XDP_TM S

XDP_TC K

XDP_TD I

XDP_TD O_CONN

MAKE_BASE= TRUE

JTAG_M CP_TDO

GPU_JT AG_TDI

XDP_TM S

XDP_TR ST_L

=PP3V3_S 0_XDP

JTAG_L VL_TRA NS_EN_L

JTAG_G MUX_TD O

JTAG_M CP_TMS

MAKE_BASE= TRUE

JTAG_M CP_TCK

JTAG_G MUX_TD I

U0600

2

3

4

5

10

9

8

7

6

12

1

11

C0601

1

2

C0602

1

2

R0601

1

2

R0602

1

2

J0600

7

8

1

2

3

4

5

6

R0603

1 2

R0604

1 2

U0601

2

3

1

5

6

4

R0605

1 2

R0606

1

2

62 13 12

87

87

87

11

13

13

23

76

13

13

13

23

10

21

10

87

75

8

21

83

75 75

10

10

8

83

21

21

83

8

13

6

10

83

75

6

6

13

9

75

75

6 8

21

75

6

6

6

9

13

13

9

Page 7

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

DRAWING N UMBER

SHT

OF

SIZE

D

FUNC_T EST

5 TPs

SATA ODD Connectors

KEYBOARD CONN

Speaker Connectors

FUNC_T EST

Fan Connectors

IPD_FLEX_CONN

LVDS Connectors

POWER RAILS

6 TPs

5 TPs

FUNC_T EST

CPU FSB NO_TESTs

NO_TEST

ICT Test Points

FUNC_T EST

3 TPs

per Fa n

4 TPs

Functional Test Points

per Fa n

FUNC_T EST

EXCARD Connector

I557

I558

I559

I560

I561

I562

I563

I564

I565

I566

I567

I568

I569

I570

I571

I572

I573

I574

I575

I576

I577

I578

I579

I580

I581

I582

I583

I584

I585

I586

I587

I588

I589

I590

I591

I592

I593

I594

I595

I596

I597

I598

I600

I602

I603

I604

I605

I606

I607

I608

I609

I610

I611

I612

I613

I614

I615

I616

I617

I618

I619

I620

I621

I622

I623

I624

I625

I626

I627

I636

I637

I638

I639

I640

I641

I642

I643

I644

I645

I646

I647

I648

I649

I650

I651

I652

I653

I654

I655

I656

I657

I709

I710

I711

I712

I713

I714

I715

I716

I717

I718

I719

I720

I721

I722

I723

I724

I725

I726

I727

I728

I729

I730

I731

I732

I733

I734

I735

I736

I737

I739

I740

I741

I742

I743

I744

I745

I746

I747

I748

I749

I750

I751

I752

I753

I754

I755

I756

I757

I758

I759

I760

I761

I762

I763

I764

I765

7 96

A.0.0

051-7546

Functional / ICT Test

SYNC_MA STER=N /A

SYNC_DA TE=N/A

PP3V3_ S5_AVRE F_SMC

TRUE

PP3V3_S3_LDO

TRUE

PP1V8_ S0GPU_ ISNS_R

TRUE

PP0V9R0 V75_S0_D DRVTT

TRUE

TRUE

PPCPUFS B_ISNS_R

PPCPUVTT _S0

TRUE

PP1V2R1 V05_S5

TRUE

TRUE

PP1V05_S 0_REG

TRUE

PP1V8_S 0

PP1V2_ S0

TRUE

PP2V5_ S0

TRUE

PP3V3_ S0

TRUE

PP3V3_ S3

TRUE

PP3V3_ S5

TRUE

TRUE

PP5V_S 0

TRUE

PP5V_S 3

TRUE

PP3V42 _G3H

TRUE

PPBUS_ CPU_IM VP_ISNS

PPBUS_ G3H

TRUE

PM_SLP_ S3_L

TRUE

TRUE

SATA_O DD_D2R _C_P

TRUE

SATA_O DD_D2R _C_N

TRUE

SATA_O DD_R2D _N

TRUE

SATA_O DD_R2D _P

PCIE_C LK100M _EXCARD _CONN_ N

TRUE

FSB_DI NV_L<3 ..0>

TRUE

FSB_DS TB_L_N <3..0>

TRUE

FSB_HI T_L

TRUE

FSB_DS TB_L_P <3..0>

TRUE

FSB_HI TM_L

TRUE

TRUE

FSB_LO CK_L

FSB_D_ L<63.. 0>

TRUE

TRUE

LED_RETU RN_5

PCIE_E XCARD_ D2R_P

TRUE

TRUE

PP1V8_ S0GPU_ ISNS

TRUE

LED_RETU RN_4

LED_RETU RN_3

TRUE

TRUE

=PP5V_ S0_FAN _LT

EXCARD _CLKRE Q_CONN_ L

TRUE

TRUE

SPKRCO NN_S_N _OUT

SPKRCO NN_R_P _OUT

TRUE

EXCARD _CPUSB _L

TRUE

TRUE

EXCARD _CPPE_ L

PLT_RE SET_SW ITCH_L

TRUE

PP1V5_ S0_EXC ARD_SWI TCH

TRUE

TRUE

PCIE_E XCARD_ R2D_N

TRUE

BI_MIC _LO

FAN_LT _TACH

TRUE

TRUE

LVDS_CON N_A_DATA _N<0>

LVDS_CON N_A_CLK_ F_N

TRUE

TRUE

LVDS_CON N_B_DATA _P<0>

TRUE

LVDS_CON N_A_CLK_ F_P

LVDS_CON N_A_DATA _N<2>

TRUE

LVDS_CON N_A_DATA _P<1>

TRUE

LVDS_CON N_A_DATA _N<1>

TRUE

TRUE

LVDS_CON N_B_CLK_ F_N

LVDS_CON N_B_DATA _N<1>

TRUE

TRUE

FAN_RT _TACH

FSB_AD S_L

TRUE

FSB_AD STB_L< 1..0>

TRUE

FSB_A_ L<31.. 3>

TRUE

LED_RETU RN_2

TRUE

TRUE

LED_RETU RN_1

TRUE

LVDS_CON N_A_DATA _P<0>

LVDS_DDC _DATA

TRUE

TRUE

LVDS_CON N_B_DATA _P<1>

LVDS_CON N_A_DATA _P<2>

TRUE

TRUE

FAN_LT _PWM

TRUE

LVDS_CON N_B_DATA _N<0>

TRUE

LVDS_CON N_B_CLK_ F_P

TRUE

LVDS_CON N_B_DATA _N<2>

LVDS_CON N_B_DATA _P<2>

TRUE

PCIE_C LK100M _EXCARD _CONN_ P

TRUE

TRUE

LED_RETU RN_6

FAN_RT _PWM

TRUE

TRUE

SMC_ODD _DETECT

TRUE

SPKRCO NN_R_N _OUT

TRUE

BI_MIC _HI

SPKRCO NN_L_P _OUT

TRUE

TRUE

WS_KBD6

TRUE

WS_KBD8

TRUE

WS_KBD9

TRUE

WS_KBD11

TRUE

WS_KBD12

TRUE

WS_KBD13

TRUE

WS_KBD14

WS_KBD15_CAP

TRUE

TRUE

WS_KBD16_NUM

TRUE

WS_KBD20

WS_KBD21

TRUE

TRUE

WS_KBD22

TRUE

WS_KBD23

WS_KBD_ONOFF_L

TRUE

PSOC_SCLK

TRUE

Z2_RESET

TRUE

TRUE

Z2_KEY_ACT_L

Z2_HOST_INTN

TRUE

Z2_BOOST_EN

TRUE

WS_KBD2

TRUE

SMBUS_SMC_A_S3_SCL

TRUE

TRUE

SPKRCO NN_L_N _OUT

TRUE

WS_KBD17

PP1V8R1V 5_S0_FET

TRUE

TRUE

WS_LEFT_OPTION_KBD

TRUE

WS_CONTROL_KBD

TRUE

TPAD_GND_F

KBDLED_ANODE

TRUE

WS_LEFT_SHIFT_KBD

TRUE

TRUE

WS_KBD19

TRUE

WS_KBD5

TRUE

WS_KBD7

WS_KBD10

TRUE

WS_KBD18

TRUE

TRUE

PPVCOR E_S0_C PU

TRUE

PPMCPDDR _ISNS

PP3V3_ S0GPU

TRUE

PPDCIN _G3H

TRUE

PPVOUT _S0_LC DBKLT

TRUE

PPVCOR E_GPU

TRUE

PPVTTD DR_S3

TRUE

PP1V8_ GPUIFPX

TRUE

PCIE_E XCARD_ D2R_N

TRUE

USB2_E XCARD_ CONN_P

TRUE

USB2_E XCARD_ CONN_N

TRUE

PCIE_E XCARD_ R2D_P

TRUE

SMBUS_SMC_A_S3_SDA

TRUE

BI_MIC _SHIEL D

TRUE

PSOC_MOSI

TRUE

PSOC_F_CS_L

TRUE

Z2_BOOT_CFG1

TRUE

PP3V42_G3H

TRUE

SPKRCO NN_S_P _OUT

TRUE

LVDS_DDC _CLK

TRUE

BKL_SYN C

TRUE

PP3V3_SW _LCD

TRUE

=PP3V3_S 0_DDC_LC D

TRUE

FSB_RE Q_L<4. .0>

TRUE

TRUE

WS_KBD1

TRUE

WS_KBD4

WS_KBD3

TRUE

TRUE

PP1V0_ FW

PP1V1_S0 GPU_REG

TRUE

TRUE

PP1V8R1V 5_S3

TRUE

PP1V2R 1V05_E NET

PPVP_F W

TRUE

TRUE

PP3V3_ ENET_P HY

PSOC_MISO

TRUE

TRUE

Z2_CLKIN

TRUE

Z2_SCLK

TRUE

Z2_MISO

TRUE

Z2_MOSI

TRUE

Z2_DEBUG3

TRUE

Z2_CS_L

TPAD_GND_F

TRUE

PP18V5_S3

TRUE

TRUE

PICKB_L

TRUE

PP5V_SW _ODD

TRUE

PP3V3_ S0_EXC ARD_SWI TCH

TRUE

PP3V3_ S3_EXC ARD_SWI TCH

SMBUS_MC P_0_DATA

TRUE

SMBUS_MC P_0_CLK

TRUE

TRUE

PPVCOR E_S0_MC P

PPVCOR E_S0_MC P_REG

TRUE

TRUE

GND

GND

TRUE

TRUE

GND

83 81 68 44 42

90

90

43

37

87

87

87

87

87

87

87

89

95

95

95

94

94

94

94

94

94

87

87

87

94

94

94

94

94

94

95

95

95

89

95

43

95

79

87

45

45

43

95

95

8

46

34

89

89

89

89

95

14

14

14

14

14

14

14

84

32

84

84

49

58

58

89

59

80

94

80

94

80

80

80

94

80

14

14

14

84

84

80

80

80

80

80

94

80

80

95

84

42

58

59

58

51

51

51

51

93

58

51

84

32

95

95

89

93

59

51

51

51

8

58

80

84

76

14

51

51

51

51

51

51

51

51

51

21

21

42

51

8

8

8

8

8

8

8

8

8

8

8

8

8

7

8

8

21

39

39

39

39

32

10

10

10

10

10

10

10

79

17

8

79

79

8

32

57

57

32

32

32

32

32

58

49

79

79

79

79

79

79

79

79

79

49

10

10

10

79

79

79

79

79

79

49

79

79

79

79

32

79

49

39

57

58

57

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

51

50

45

57

50

8

50

50

7

51

50

50

50

50

50

50

8

8

8

8

79

8

8

8

17

32

32

32

45

58

50

50

50

7

57

79

79

79

8

10

50

50

50

8

8

8

8

8

8

50

50

50

50

50

50

50

7

51

50

39

32

32

13

13

8

Page 8

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

DRAWING N UMBER

SHT

OF

SIZE

D

"G3Hot" (Always-Present) Rails

5300 mA

241 mA max load

1034 mA

Chipset "VCore" Rails

139 mA/ 0 mA

105 mA/ 241 mA

1182 mA

4500 mA

1.8V/DDR 1.5V Rails

5V Rails

3.3V-2.5V Rails

"GPU" Rails

500 mA max supp ly

"FW" (FireWire) Rails

190 mA

500 mA

130 mA

4771 mA

(1.1V f or A01)

OR 0.75 V

ENET Rails

Power Aliases

SYNC_MA STER=( MASTER)

051-7546

A.0.0

968

SYNC_DA TE=(MA STER)

=PPVP_ FW_POR T1

=PPVP_ FW_PHY _CPS_FE T

=PP3V3 _S0GPU _FET

=PP3V3 _FW_FW PHY

=PP1V0 _FW_RE G

=PP1V05 _S0_MCP_ SATA_AVD D0

PP1V2R1 V05_S5

MIN_NECK_W IDTH=0.2 m m

VOLTAGE=1. 05V

MAKE_BASE= TRUE

MIN_LINE_W IDTH=0.6 m m

=PP3V3 _FW_RE G

=PP1V5 _FC_CO N

=PP3V3 _S3_SM BUS_SMC _A_S3

=PP3V3 _FW_RE G

=PPBUS_G 3H

PPBUS_ CPU_IM VP_ISNS

MIN_LINE _WIDTH=0 .4 mm

MAKE_BAS E=TRUE

VOLTAGE= 12.6V

MIN_NECK _WIDTH=0 .25 mm

=PP3V3 _S3_FE T

=PPVIN _S5_P5V P3V3

=PP3V3 _S0_SM BUS_SMC _B_S0

=PP3V3 _S0_CP UTHMSNS

=PP3V3 _S0_IM VP

=PP3V3 _S0_XD P

=PP3V3 _S0_MCP COREIS NS

=PP3V3 _S0_FA N_RT

=PPVCO RE_S0_M CP

PP1V2_ S0

MIN_LINE_W IDTH=0.6 m m

MIN_NECK_W IDTH=0.2 m m

MAKE_BASE= TRUE

VOLTAGE=1. 2V

=PP2V5 _S0_GM UX

=PP1V0 5_ENET _FET

=PP3V3 _S0_MCP

=PP1V8R1 V5_S0_MC P_FET

=PPVIN_S 0_DDRREG _LDO

=PPVIN _S5_CP U_IMVP_ ISNS

=PP3V4 2_G3H_C HGR

=PP3V4 2_G3H_ TPAD

=PP3V4 2_G3H_ CPUCORE ISNS

=PP18V 5_DCIN _CONN

=PP3V3 _S0_EX CARD

=PP3V3 _S0_LV DSDDCMU X

=PP3V3 _S0_OD D

=PP3V3 _S0_AU DIO

=PPSPD _S0_MEM _B

=PPSPD _S0_MEM _A

=PP3V3 _S0_DD C_LCD

=PP3V3 _S0_PW RCTL

=PP3V3 _S0_FA N_LT

=PPVIN _S0GPU _P1V8P1 V1

=PP3V3 _S0_GP UTHMSNS

=PP3V3 _S0_SMB US_MCP _1

=PP3V3_ GPU_SMBU S_SMC_0_ S0

MIN_LINE_W IDTH=0.6 m m

MAKE_BASE= TRUE

MIN_NECK_W IDTH=0.2 m m

PP2V5_ S0

VOLTAGE=2. 5V

=PP1V2 _S0_GM UX

=PP1V8 _GPU_I FPX

VOLTAGE= 1.8V

MAKE_BAS E=TRUE

MIN_LINE _WIDTH=0 .6 mm

PP1V8_ GPUIFPX

MIN_NECK _WIDTH=0 .15 mm

=PP1V1_G PU_IFPCD _IOVDD

=PP1V1_G PU_VID_P LLVDD

=PP1V1_G PU_H_PLL VDD

=PP1V1_G PU_PLLVD D

=PP1V1 _S0GPU _REG

=PP1V1_G PU_PEX_P LLXVDD

=PP1V1_G PU_PEX_I OVDDQ

=PP1V1_G PU_PEX_I OVDD

=PP1V1_G PU_FBPLL AVDD

MAKE_BAS E=TRUE

PP1V8_ S0GPU_ ISNS

MIN_LINE _WIDTH=0 .6 mm

VOLTAGE= 1.8V

MIN_NECK _WIDTH=0 .2 mm

=PP1V8 _GPU_F B_VDDQ

=PP1V8 _GPU_F BIO

=PP3V3 _GPU_P 1V8S0

=PP1V8 _GPU_F B_VDD

=PP1V8 _GPU_F BVDDQ

=PP1V8 _S0GPU _ISNS

=PP1V5_S 3_MEM_A

=PP1V5_S 3_MEM_B

=PP3V3 _ENET_ MCP_RMG T

=PPVTT_ S0_VTTCL AMP

=PP0V75 _S0_MEM_ VTT_B

=PP0V75 _S0_MEM_ VTT_A

=PP1V05 _ENET_P1 V05ENETF ET

=PP1V05 _S5_MCP_ VDD_AUXC

=PP5V_ S3_MCP DDRFET

=PP5V_ S3_GPU VCORE

=PP5V_ S3_WLA N

MIN_NECK _WIDTH=0 .25 mm

MIN_LINE _WIDTH=0 .5 mm

MAKE_BAS E=TRUE

PP5V_S 3

VOLTAGE= 5V

=PP5V_ S3_BTCA MERA

PPVCOR E_S0_C PU

VOLTAGE= 1.25V

MIN_LINE _WIDTH=0 .6 mm

MAKE_BAS E=TRUE

MIN_NECK _WIDTH=0 .25 mm

=PP3V3 _GPU_V CORELOG IC

=PP3V3 _S5_SM C

=PP3V3 _S5_LP CPLUS

=PP3V4 2_G3H_ SMBUS_S MC_BSA

=PP1V8R1 V5_S0_FE T

=PP1V2 _S0_RE G

=PP2V5 _S0_RE G

=PP5V_ S3_P1V 05S0FET

=PP1V05 _S5_P1V0 5S0FET

=PP3V3 _ENET_ FET

=PP3V3 _ENET_ PHY

=PP1V0 5_ENET _PHY

=PP1V0 5_ENET _MCP_RM GT

=PP1V0 5_ENET _MCP_PL L_MAC

VOLTAGE =3.3V

MAKE_BA SE=TRU E

MIN_NEC K_WIDT H=0.2 m m

PP3V3_ ENET_P HY

MIN_LIN E_WIDT H=0.6 m m

VOLTAGE =1.05V

PP1V2R 1V05_E NET

MIN_LIN E_WIDT H=0.4 M M

MIN_NEC K_WIDT H=0.2 m m

MAKE_BA SE=TRU E

=PPVCO RE_S0_ CPU_REG

PP1V8_S 0

MIN_LINE_W IDTH=0.5 m m

MIN_NECK_W IDTH=0.2 m m

VOLTAGE=1. 8V

MAKE_BASE= TRUE

=PP3V3 _GPU_M IO

=PP3V3 _GPU_V DD33

=PP3V3R 1V8_S0_M CP_IFP_V DD

PPVCOR E_GPU

MIN_LINE _WIDTH=0 .6 mm

MIN_NECK _WIDTH=0 .2 mm

VOLTAGE= 1.2V

MAKE_BAS E=TRUE

MIN_LINE _WIDTH=0 .6 mm

MAKE_BAS E=TRUE

VOLTAGE= 1.25V

MIN_NECK _WIDTH=0 .2 mm

PP1V8_ S0GPU_ ISNS_R

=PPVCO RE_GPU

=PP1V8 _S0GPU _ISNS_R

=PPVCO RE_GPU _REG

=PP1V8 _GPU_R EG

=PPBUS _S5_FW _FET

=PP1V0 _FW_FW PHY

MIN_LINE _WIDTH=0 .4 mm

VOLTAGE= 1.00V

MAKE_BAS E=TRUE

MIN_NECK _WIDTH=0 .2 mm

PP1V0_ FW

=PPMCP CORE_S0 _REG

=PPDDR_S 3_REG

PP1V05_ S0_MCP_S ATA_AVDD

MAKE_BASE=T RUE

=PP3V4 2_G3H_ PWRCTL

=PP3V3 _S5_RTC _D

=PP5V_ S3_AUD IO_PWR

=PP5V_ RT_REG

=PP5V_ S0_CPUV TTS0

=PP3V4 2_G3H_ SMCUSBM UX

MIN_LINE _WIDTH=0 .4 mm

MIN_NECK _WIDTH=0 .2 mm

VOLTAGE= 12.6V

MAKE_BAS E=TRUE

PPVP_F W

MIN_LINE_WI DTH=0.6 mm

MIN_NECK_WI DTH=0.2 mm

MAKE_BASE=T RUE

VOLTAGE=1.0 5V

PPVCOR E_S0_MC P_REG

=PPVTT_S 3_DDR_BU F

=PP3V3 _FW_P1 V0FW

=PP5V_ S0_CPU _IMVP

=PP5V_ S3_RTU SB

=PP5V_ S3_DDR REG

=PP5V_ S3_IR

=PP5V_ S3_SYS LED

=PPVIN _S5_SM CVREF

=PPVIN _S5_CP U_IMVP

=PP5V_ S0_FAN _RT

=PP3V3 _S3_P3 V3S3FET

=PP3V3 _S5_MC P_A01

=PP3V3 _S5_RE G

=PP3V3 _FW_LA TEVG_AC TIVE

=PP3V3 _S5_ME MRESET

=PP3V3_ S0_BATT CHARGER TMPSNSR

=PP5V_ S3_REG

=PP3V4 2_G3H_ REG

=PP1V05 _S0_MCP_ PEX_AVDD 1

=PP3V3 _S3_VRE FMRGN

=PP1V05_ S0_SMC_L S

=PP1V05_ S0_MCP_F SB

=PP1V05 _S0_MCP_ SATA_DVD D0

=PP5V_ S3_VTT CLAMP

=PP5V_ S0_FAN _LT

=PP5V_ S0_KBD LED

=PP5V_ S0GPU_ P1V1P1V 8_GPU

=PP5V_ S0_LPC PLUS

=PPVIN _S0_CP UVTTS0

=PPVIN _S5_CP U_IMVP_ ISNS_R

=PP1V8_ S0_REG

=PP3V3_ S0_TPAD

=PP1V05 _S0_FET

PP1V8R1V 5_S0_FET

MIN_LINE_WI DTH=0.6mm

MIN_NECK_WI DTH=0.2mm

VOLTAGE=1.5 V

MAKE_BASE=T RUE

=PP1V5_S 3_MEMRES ET

MIN_NECK_WI DTH=0.1 mm

VOLTAGE=1.5 V

MAKE_BASE=T RUE

PP1V8R1V 5_S3

MIN_LINE_WI DTH=0.8 mm

=PP3V3 _S0_MCP _DAC_U F

=PP3V3 _S0_MCP _VPLL_ UF

=PP3V3 _S0_MCP _PLL_U F

=PP3V3 R1V5_S0 _MCP_H DA

=PPVCO RE_S0_ CPU

=PP5V_ S3_TPA D

=PPVIN _S0_P1 V05S5

=PPDCI N_S5_C HGR

=PP3V4 2_G3H_ LIDSWIT CH

=PP3V4 2_G3H_ BATT

=PP3V4 2_G3H_ BMON_IS NS

=PP3V3 _S3_SM S

=PPBUS _S0_LCD BKLT

MAKE_BAS E=TRUE

VOLTAGE= 12.6V

MIN_NECK _WIDTH=0 .25 mm

PPBUS_ G3H

MIN_LINE _WIDTH=0 .4 mm

=PP3V3 _S3_EXC ARD

=PP3V3 _S0_LP CPLUS

=PP3V3 _S0_GP U1V8ISN S

=PP3V3 _S0_MCP DDRISN S

=PP3V3 _S0_SM C

MIN_NECK _WIDTH=0 .20MM

MAKE_BAS E=TRUE

PP3V3_ S0

MIN_LINE _WIDTH=0 .30MM

VOLTAGE= 3.3V

=PP3V3 _S3_P1 V8S0

=PP3V3 _S3_SMB US_SMC _MGMT

=PP3V3 _S3_MC P_GPIO

=PP3V3 _S3_WL AN

=PP1V8R1 V5_S0_MC P_MEM

MAKE_BASE=T RUE

PPMCPDDR _ISNS

MIN_LINE_WI DTH=0.6 mm

MIN_NECK_WI DTH=0.2 mm

VOLTAGE=1.5 V

=PP1V05_ S0_MCP_S ATA_DVDD

=PP3V3 _S0_GMU X

=PP3V3 _S0_HDC PROM

=PP3V3 _S0_MCP _GPIO

=PP3V3_ S0_P1V2P 2V5

=PP3V3 _S0_VMO N

=PP3V3 _FC_CO N

MIN_LINE _WIDTH=0 .60 MM

VOLTAGE= 5V

PP5V_S 0

MAKE_BAS E=TRUE

MIN_NECK _WIDTH=0 .20 MM

=PP5V_ S0_HDD

=PP5V_ S0_ODD

=PP3V3 _S3_TP AD

=PP3V3 _S3_RE MTHMSNS

=PP3V3 _S5_DP_ PORT_P WR

=PP3V3 _S5_P3 V3ENETF ET

=PP3V3 _S5_P1 V05ENET FET

=PP3V3 _S5_MCP PWRGD

=PP3V3 _S0_P3 V3S0FET

=PP3V3 _S5_RO M

=PP3V3 _FW_LA TEVG

MIN_LINE _WIDTH=0 .50MM

MIN_NECK _WIDTH=0 .20MM

MAKE_BAS E=TRUE

PP3V3_ S3

VOLTAGE= 3.3V

=PP1V05_ S0_MCP_P EX_DVDD

PP1V05_ S0_MCP_P EX_AVDD

MAKE_BASE=T RUE

=PP1V05 _S5_MCP

=PPCPUVT T_S0_REG

=PP3V3 _S0_DPC ONN

=PP3V3 _S0_DPM UX

=PPVTT_ S0_DDR_L DO

MAKE_BASE=T RUE

MIN_NECK_WI DTH=0.2 mm

MIN_LINE_WI DTH=0.3 mm

VOLTAGE=0.7 5V

PPVTTDDR _S3

PP0V9R0 V75_S0_D DRVTT

MIN_LINE_W IDTH=2 mm

MIN_NECK_W IDTH=0.2 m m

VOLTAGE=0. 9V

MAKE_BASE= TRUE

=PP1V05_ S0_CPU

PPCPUVTT _S0

MIN_LINE_WI DTH=0.6 mm

MIN_NECK_WI DTH=0.2 mm

VOLTAGE=1.0 5V

MAKE_BASE=T RUE

=PP1V05 _S0_MCP_ PEX_AVDD 0

=PP1V05 _S0_MCP_ PEX_DVDD 1

=PP1V05 _S0_MCP_ PEX_DVDD 0

=PP1V05_ S0_VMON

=PP1V05_ S0_MCP_H DMI_VDD

=PP1V05_ S0_MCP_S ATA_DVDD

=PP1V05_ S0_MCP_P LL_UF

=PP1V05_ S0_MCP_P EX_DVDD

=PP1V05_ S0_MCP_A VDD_UF

MIN_LINE_WI DTH=0.6 mm

MIN_NECK_WI DTH=0.2 mm

VOLTAGE=1.0 5V

PP1V05_S 0_REG

MAKE_BASE=T RUE

=PPMCPD DR_ISNS

=PP1V5_S 0_MEM_B

=PP1V5_S 0_MEM_A

=PPMCPDD R_ISNS_R

=PP1V5_S 0_CPU

=PP1V5_S 0_EXCARD

=PP1V5_S 0_VMON

=PP3V3 _GPU_LV DS_DDC

=PP3V3 _GPU_P WRCTL

MIN_LINE _WIDTH=0 .30MM

MAKE_BAS E=TRUE

PP3V3_ S0GPU

MIN_NECK _WIDTH=0 .20MM

VOLTAGE= 3.3V

PP1V1_S0 GPU_REG

MIN_NECK_WI DTH=0.2 mm

MIN_LINE_WI DTH=0.6 mm

MAKE_BASE=T RUE

VOLTAGE=1.1 V

=PP1V8 _GPUIFP X_REG

=PP3V3 _S0_FE T

=PP3V3 _S0_SMB US_MCP _0

=PPVBA T_G3H_ P3V42G3 H

=PPVIN _S3_DDR REG

=PPVIN _S0_P5 VRTS0_M CPCORE

=PPVIN _GPU_GP UVCORE

=PPBUS _S5_FWP WRSW

MIN_NECK _WIDTH=0 .25 mm

VOLTAGE= 12.6V

MAKE_BAS E=TRUE

MIN_LINE _WIDTH=0 .6 mm

PPDCIN _G3H

MAKE_BAS E=TRUE

VOLTAGE= 3.42V

PP3V42 _G3H

MIN_NECK _WIDTH=0 .2 mm

MIN_LINE _WIDTH=0 .3 mm

MIN_LINE _WIDTH=0 .6 mm

MIN_NECK _WIDTH=0 .2 mm

VOLTAGE= 3.3V

MAKE_BAS E=TRUE

PP3V3_ S5

=PP3V3 _S5_MCP _GPIO

=PP3V3 _S5_MCP

=PP3V3 _S5_P1V 05FET

=PP3V3 _S5_PW RCTL

=PP3V3 _GPU_P 3V3GPUF ET

=PP3V3 _S5_LC D

62 13

24

12

46

24

59

79

74

52

76

22

46

21

11

38

13

24

22

58

76

73

74

24

24

43

24

76

75

25

78

68

64

44

14

49

24

12

46

95

24

24

19

53

24

10

25

24

24

12

43

95

20

24

38

38

69

36

67

20

7

8

32

45

8

61

7

69

63

45

48

62

6

47

49

22

7

83

34

21

69

64

46

61

50

46

60

32

80

39

54

29

28

7

68

49

82

48

45

45

7

83

77

7

77

75

75

75

82

70

70

70

72

7

9

72

67

73

71

47

28

29

18

69

29

28

34

22

69

78

31

7

31

7

78

42

44

45

69

86

86

69

69

34

33

33

18

24

7

7

62

7

75

6

18

7

7

71

47

46

82

37

36

7

65

64

24

63

26

9

65

66

40

7

7

27

67

62

40

64

41

43

43

62

49

69

23

63

37

30

48

63

60

17

27

43

9

20

69

7

51

82

44

66

46

67

51

69

7

30

7

25

25

24

21

11

51

67

61

41

60

46

52

85

7

32

44

47

47

43

7

67

45

21

31

16

7

8

83

25

18

86

68

32

7

39

39

50

48

81

34

34

26

69

44

38

7

8

24

67

66

81

80

64

7

7

6

7

17

17

17

68

18

8

24

8

24

7

47

29

28

47

11

32

68

80

68

7

7

67

69

45

60

64

65

78

37

7

7

7

18

22

69

68

69

79

Page 9

OUT

OUT

IN

OUT

OUT

OUT

OUT

OUT

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

DRAWING N UMBER

SHT

OF

SIZE

D

Frame Holes

Thermal Module Holes

MCP79 PCIe PRSNT# Straps

Digital Ground

If fou nd to be nece ssary, will move t o page1 4.csa

Exist in MRB but no t Inte l desi gns. Here fo r CYA.

Extra FSB Pull-ups

TM Hol e

CPU si gnals

TM Hol e TM Hol e

GPU si gnals

ETHERNET ALIASES

GMUX ALIASES

AUDIO ALIASES

Bottom Left GPU

Top GP U Righ t

Left C PU

TM Hol e

Right CPU

These ne ed work. Add ot her PRSN T# strap s if nee ded. .

Bosses for VRAM HS

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

3R2P5

5%

1/16W

402

MF-LF

47K

5%

1/16W

402

0

MF-LF

17

10K

5%

1/16W

MF-LF

402

SM

SM

1%

MF-LF

402

10

1/16W

10

1/16W

MF-LF

1%

402

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

3R2P5

TH

SL-3.1X2. 7-6CIR-NSP

3R2P5

3R2P5

3R2P5

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

402

0

5%

1/16W

MF-LF

17

83

NO STU FF

5%

1/16W

0

402

MF-LF

STDOFF -4.5OD .98H-1 .1-3.4 8-TH

10 14 87

10 14 87

10 13 14 87

10 14 87

10 14 62 87

62

1/16W

402

5%

MF-LF

NO STU FF

NO STU FF

220

MF-LF

402

5%

1/16W

NO STU FF

200

MF-LF

1/16W

5%

402

1%

150

MF-LF

1/16W

402

NO STU FF

1%

402

1/16W

MF-LF

150

NO STU FF

STDOFF -4.0OD 3.0H-T H

VENICE

STDOFF -4.0OD 3.0H-T H

VENICE

VENICE

STDOFF -4.0OD 3.0H-T H

STDOFF -4.0OD 3.0H-T H

STDOFF -4.0OD 3.0H-T H

1.4DIA -SHORT -EMI-M LB-M97 -M98

SM

4.0OD1 .65H-M 1.6X0. 35

4.0OD1 .65H-M 1.6X0. 35

4.0OD1 .65H-M 1.6X0. 35

0

5%

1/16W

402

MF-LF

SM

1.4DIA -SHORT -EMI-M LB-M97 -M98

1.4DIA -SHORT -EMI-M LB-M97 -M98

SM

1.4DIA -SHORT -EMI-M LB-M97 -M98

SM

2.0DIA -TALL- EMI-ML B-M97- M98

SM

2.0DIA -TALL- EMI-ML B-M97- M98

SM

2.0DIA -TALL- EMI-ML B-M97- M98

SM

2.0DIA -TALL- EMI-ML B-M97- M98

SM

3R2P5

Signal Aliases

9 96

A.0.0

051-7546

SYNC_MA STER=( MASTER)

SYNC_DA TE=(MA STER)

MIN_NECK _WIDTH=0 .09MM

MIN_LINE _WIDTH=0 .6MM

VOLTAGE= 0V

GND

GND_CH ASSIS_ CLUTCH

GND_BA TT_CHG ND

GND_CH ASSIS_ USB

MAKE_BASE=T RUE

TP_LVDS _IG_B_CL KN

=PP1V0 5_S0_M CP_SATA _AVDD1

LVDS_B _DATA_ N<3>

MAKE_BAS E=TRUE

JTAG_G MUX_TD O

IG_LCD _PWR_E N

IG_BKL T_EN

MAKE_BAS E=TRUE

LVDS_I G_PANE L_PWR

LVDS_IG _BKL_PWM

MAKE_BASE=T RUE

NC_LVD S_IG_A _DATAP< 3>

MAKE_BASE=T RUE

NC_LVD S_B_DA TAP<3>

FSB_BR EQ0_L

CPU_IN TR

FC_PRS NT_L

MAKE_BASE=T RUE

PCIE_F C_R2D_ C_N

MAKE_BASE=T RUE

=MCP_HDM I_TXD_N< 0..2>

MAKE_BAS E=TRUE

PCIE_F W_PRSN T_L

LVDS_A _DATA_ P<3>

MAKE_BAS E=TRUE

NC_RTL 8211_R EGOUT

=RTL82 11_REG OUT

=RTL82 11_ENS WREG

=PP1V0 5_S0_M CP_SATA _DVDD1

PCIE_F C_D2R_ N

MAKE_BASE=T RUE

TP_PE4 _PRSNT _L

MCP_MI I_PD

MAKE_BAS E=TRUE

=MCP_M II_COL

GND_CH ASSIS_ FAN

TP_USB _EXTCP

MAKE_BAS E=TRUE

USB_EX TC_P

=DVI_H PD_GMU X_INT

USB_MI NI_N

NO_TEST=TRU E

MAKE_BASE=T RUE

NC_LVDS_ A_DATAP< 3>

MAKE_BASE=T RUE

TP_LVDS _IG_B_CL KP

GPU_RESE T_L

MAKE_BASE=T RUE

DP_IG_DD C_DATA

=MCP_HDM I_DDC_CL K

DP_IG_ML _N<3>

MAKE_BASE=T RUE

=MCP_HDM I_TXC_N

DP_IG_ML _P<2..0>

MAKE_BASE=T RUE

=MCP_HDM I_TXD_P< 0..2>

=MCP_HDM I_TXC_P

MAKE_BASE= TRUE

PEG_R2D _C_P<0.. 15>

MAKE_BAS E=TRUE

PCIE_R ESET_L

VR_PWR GD_CLK EN_LTP_IMV P6_CLK EN_L

MAKE_BAS E=TRUE

MAKE_BASE=T RUE

CPU_VID< 0..6>

=MCP_BSE L<0..2>

=PEG_D2 R_P<0..1 5>

IMVP6_VI D<0..6>

CPU_BSEL <0..2>

MAKE_BASE=T RUE

MAKE_BAS E=TRUE

PM_SLP _RMGT_ L

LVDS_B_D ATA_N<3>

LVDS_A_D ATA_P<3>

LVDS_IG _B_CLK_N

LVDS_B _DATA_ P<3>

MAKE_BASE=T RUE

NC_LVD S_IG_A _DATAN< 3>

MAKE_BASE=T RUE

NO_TEST=TRU E

NC_LVDS_ B_DATAN< 3>

MAKE_BASE=T RUE

NO_TEST=TRU E

NC_LVDS_ B_DATAP< 3>

PCIE_C LK100M _FC_N

MAKE_BASE=T RUE

MAKE_BASE=T RUE

PCIE_F C_R2D_ C_P

=MCP_M II_CRS

=MCP_M II_RXE R

USB_EX TC_N

MAKE_BAS E=TRUE

TP_USB _MININ

MAKE_BAS E=TRUE

TP_USB _MINIP

USB_MI NI_P

USB_EX TD_N

USB_EX TD_P

VOLTAGE= 5V

PP5V_S 3_AUDI O_AMP

MIN_NECK _WIDTH=0 .25 mm

MIN_LINE _WIDTH=0 .5 mm

MAKE_BASE=T RUE

NC_LVD S_B_DA TAN<3>

MAKE_BASE=T RUE

NC_LVD S_A_DA TAP<3>

MAKE_BASE =TRUE

AUD_IP HS_SWI TCH_EN

PP5V_S 3_AUDI O

VOLTAGE= 5V

MIN_NECK _WIDTH=0 .25 mm

MIN_LINE _WIDTH=0 .5 mm

TP_USB _EXTDP

MAKE_BAS E=TRUE

NC_LVD S_IG_B _DATAP< 3>

MAKE_BASE=T RUE

MAKE_BASE=T RUE

TP_SPI_C S1_R_L_U SE_MLB

=DDRVTT_ ENMEM_VTT_ EN

MAKE_BASE=T RUE

=SPI_CS1 _R_L_USE _MLB

=PEG_D2 R_N<0..1 5>

MAKE_BASE= TRUE

PEG_D2R _N<0..15 >

LVDS_I G_B_DA TA_P<3>

LVDS_I G_A_DA TA_P<3>

LVDS_I G_A_DA TA_N<3>

LVDS_A _DATA_ N<3>

LVDS_I G_B_DA TA_N<3>

LVDS_A_D ATA_N<3>

MAKE_BASE=T RUE

TP_LVDS _IG_BKL_ PWM

TP_USB _EXTDN

MAKE_BAS E=TRUE

HDA_BI T_CLK

FC_RES ET_L

MAKE_BASE=T RUE

NO_TEST=TRU E

NC_LVDS_ A_DATAN< 3>

=P3V3E NET_EN

=PP3V3 _ENET_ PHY_VDD REG

PCIE_F C_D2R_ P

MAKE_BASE=T RUE

CPU_DP RSTP_L

GND_CH ASSIS_ BATTCON N

=PP1V0 5_S0_M CP_FSB

TP_PP3 V3_ENE T_PHY_V DDREG

MAKE_BAS E=TRUE

MAKE_BAS E=TRUE

PEG_PR SNT_L

=P1V05 ENET_E N

MAKE_BAS E=TRUE

TP_USB _EXTCN

MAKE_BASE=T RUE

DP_IG_ML _N<2..0>

LVDS_B_D ATA_P<3>

NC_LVD S_IG_B _DATAN< 3>

MAKE_BASE=T RUE

NC_LVD S_A_DA TAN<3>

MAKE_BASE=T RUE

CPU_NM I

GMUX_I NT

MAKE_BAS E=TRUE

PCIE_C LK100M _FC_P

MAKE_BASE=T RUE

TP_PCI E_CLK1 00M_PE4 N

MCP_SP KR

LVDS_IG _B_CLK_P

FC_CLK REQ_L

MAKE_BASE=T RUE

MEM_B_ A<15>

HDA_BI TCLK

MAKE_BAS E=TRUE

=PP5V_ S3_AUD IO_PWR

MAKE_BAS E=TRUE

TP_MEM _A_A<1 5>

GMUX_J TAG_TD O

MAKE_BAS E=TRUE

LVDS_I G_BKL_ ON

GMUX_J TAG_TM S

ALL_EG_P GOOD

DP_IG_ML _P<3>

MAKE_BASE=T RUE

MAKE_BAS E=TRUE

JTAG_G MUX_TD I

EG_RESET _L

MAKE_BASE=T RUE

MEM_A_ A<15>

SMC_MC P_SAFE _MODE

MAKE_BAS E=TRUE

TP_MEM _B_A<1 5>

EG_CLKRE Q_OUT_L

CPU_PE CI_MCP

TP_CPU _PECI_ MCP

MAKE_BAS E=TRUE

=PEG_R2 D_C_P<0. .15>

TP_PCI E_CLK1 00M_PE4 P

TP_PCI E_PE4_ R2D_CP

TP_PCI E_PE4_ R2D_CN

GMUX_J TAG_TD I

MAKE_BASE=T RUE

LCD_BKL T_EN

LVDS_BKL _ON

TP_MCP _GPIO_ 17

MAKE_BAS E=TRUE

AUD_IP _PERIP HERAL_D ET

TP_PCI E_PE4_ D2RN

TP_PCI E_PE4_ D2RP

TP_PE4 _CLKRE Q_L

=PEG_R2 D_C_N<0. .15>

MAKE_BASE= TRUE

PEG_R2D _C_N<0.. 15>

PEG_D2R _P<0..15 >

MAKE_BASE= TRUE

=PP1V8_G PU_FB_VR EF_B

GND_CH ASSIS_ SATA

=PP1V8_G PU_FB_VR EF_A

MAKE_BASE=T RUE

GPU_FB_A _VREF_DI V

MAKE_BASE=T RUE

GPU_FB_B _VREF_DI V

MAKE_BASE=T RUE

TP_LVDS_ MUX_SEL_ EG

LVDS_MUX _SEL_EG

=PP1V8_G PU_FB_VD DQ

DP_IG_DD C_CLK

MAKE_BASE=T RUE

=MCP_HDM I_DDC_DA TA

=MCP_HDM I_HPD

PM_ALL_G PU_PGOOD

MAKE_BASE=T RUE

DP_IG_HP D

MAKE_BASE=T RUE

MAKE_BAS E=TRUE

JTAG_G MUX_TM S

FSB_CP URST_L

GND_CH ASSIS_ LVDS

ZT0980

ZT0940

1

R0930

1

2

R0925

R0902

1 2

XW0900

12

XW0901

12

R0900

R0901

ZT0981

ZT0982

ZT0983

ZT0984

ZT0985

ZT0986

ZT0987

ZT0945

1

ZT0950

ZT0965

1

ZT0960

1

ZT0990

1

ZT0989

1

ZT0988

1

ZT0991

1

R0926

R0927

ZT0930

R0960

1

2

R0950

1

2

R0970

1

2

R0980

1

2

R0990

1

2

ZT0931

1

ZT0932

1

ZT0933

1

ZT0934

1

ZT0935

1

SH0910

1

ZT0951

1

ZT0952

1

ZT0953

1

R0903

SH0912

1

SH0911

1

SH0913

1

SH0902

1

SH0900

1

SH0903

1

SH0901

1

ZT0915

1

24 22

61

83

95

95

90

90

80

89

89

89

26

87 87

87

89

95

95

90

90

90

90

59

56

69

44

89

89

89

89

89

90

95

14

89

95

89

89

83

89

89

80

83

60

20

9

6

83

83

18

18

9

32

32

18

9

33

33

20

32

17

18

20

18

20

9

70

76

18

80 18

80 18

18

70

17

62

11

14

17

62

10

21

9

9

18

9

9

9

32

32

18

18

20

20

20

20

57

9

9

19

54

64 26

21

17 70

18

18

18

9

18

9

21

32

9

34

33

32

8

34

80

9

9

83

32

17

21

18

32 29

54

8

17

18

19

83

80

6

83

28

42

14

17

17

17

17

19

83 85

17

17

17

17

17

70

70

74

73

83

76

18

18

68

6

Page 10

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

IN

IN

IN

IN

OUT

IN

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

IN

IN

IN

IN

IN

IN

IN

IN

OUT

BI

BI

BI

BI

LOCK*

INIT*

A20M*

A6*

A3*

A4*

A14*

A16*

REQ0*

REQ1*

REQ2*

REQ3*

REQ4*

BCLK1

BCLK0

THERMTRI P*

THERMDA

PROCHOT*

DBR*

TRST*

TMS

TDO

TDI

TCK

PREQ*

PRDY*

BPM3*

BPM2*

BPM1*

BPM0*

HITM*

HIT*

TRDY*

RS2*

RS1*

RS0*

RESET*

IERR*

BR0*

DBSY*

DRDY*

DEFER*

BNR*

RSVD4

RSVD3

RSVD2

RSVD1

RSVD0

SMI*

LINT1

LINT0

STPCLK*

FERR*

ADSTB1*

A35*

A34*

A33*

A32*

A31*

A30*

A29*

A28*

A19*

A18*

A17*

ADSTB0*

A13*

A12*

BPRI*

A20*

A21*

A22*

A23*

A24*

A26*

A27*

A9*

A8*

A7*

A11*

A25*

THERMDC

IGNNE*

ADS*

A10*

A15*

A5*

RSVD5

RSVD6

RSVD7

RSVD8

1 OF 4

CONTROL

THERMAL

XDP/ITP SIGNALS

H CLK

ADDR GRO UP1

ICH

RESERVED

ADDR GRO UP0

TEST7

TEST6

DSTBP1*

DINV1*

D31*

D30*

D25*

D11*

D12*

D13*

D14*

DSTBP0*

DINV0*

D9*

D8*

D7*

D6*

D19*

D18*

D0*

D32*

D1*

D2*

D5*

D16*

D20*

D21*

D22*

D23*

D24*

D26*

D27*

D28*

D29*

DSTBN1*

GTLREF

TEST3

TEST4

TEST5

BSEL0

BSEL1

BSEL2

D33*

D34*

D35*

D36*

D37*

D38*

D39*

D40*

D41*

D42*

D43*

D44*

D45*

D46*

D47*

DSTBN2*

DSTBP2*

DINV2*

D48*

D49*

D50*

D51*

D52*

D53*

D54*

D55*

D56*

D57*

D58*

D59*

D60*

D61*

D62*

D63*

DSTBN3*

DSTBP3*

DINV3*

COMP0

COMP1

COMP2

COMP3

DPRSTP*

DPSLP*

DPWR*

PWRGOOD

SLP*

PSI*

D17*

D4*

D3*

DSTBN0*

D15*

D10*

TEST2

TEST1

2 OF 4

DATA GRP 3 DATA GRP 2

MISC

DATA GRP 0DATA GRP 1

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFOR MATION CON TAINED HE REIN IS TH E PROPRIE TARY

PROPERTY OF APPLE C OMPUTER, INC. THE P OSSESSOR

AGREES TO THE FOLLO WING

II NOT TO REPRODUCE OR COPY IT

III NOT T O REVEAL O R PUBLISH IN WHOLE OR PART

I TO MAIN TAIN THE D OCUMENT I N CONFIDEN CE

NOTICE OF PRO PRIETA RY PROP ERTY

DRAWING N UMBER

SHT

OF

SIZE

D

LAYOUT NOTE:

MAKE T RACE L ENGTH S HORTER THAN 0.5".

COMP0, 2 CONN ECT WIT H ZO=2 7.4OHM ,

MAKE T RACE L ENGTH S HORTER THAN 0.5".

COMP1, 3 CONN ECT WIT H ZO=5 5OHM,

PM_THR MTRIP#

SHOULD CONNE CT TO I CH AND

GMCH W ITHOUT T (NO STUB)

0.1" A WAY

PLACE TESTPO INT ON

FSB_IE RR_L W ITH A G ND

0.5" M AX LEN GTH FOR CPU_G TLREF

REFERE NCED T O GND

PLACE C1000 CLOSE T O CPU_ TEST4

PIN. M AKE SU RE CPU_ TEST4 IS

402

MF-LF

54.9

1/16W

1%

MF-LF

402

1/16W

5%

68

402

1K

MF-LF

1%

1/16W

402

1/16W

2.0K

MF-LF

1%

402

54.9

1/16W

MF-LF

1%

402

1%

MF-LF

1/16W

27.4

402

54.9

1/16W

MF-LF

1%

402

27.4

1/16W

MF-LF

1%

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

9

14 62 87

14 87

14 87

14 87

62

13 14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

9

87

9

87

9

87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

7

14 87

14 87

14 87

14 87

14 87

14 87

9

14 87

7

14 87

7

14 87

7

14 87

13 87

13 87

13 87

13 87

13 87

13 87

6

10 87

13 26

14 43 62 87

48 95

14 43 87

14 87

9

13 14 87

14 87

14 87

14 87

14 87

6

10 13 87

6

10 13 87

6

10 13 87

6

10 13 87

48 95

14 87

14 87

14 87

14 87

9

14 87

9

14 87

14 87

14 87

14 87

402

NOSTUF F

5%

MF-LF

1/16W

0

402

NOSTUF F

1K

MF-LF

5%

1/16W

402

54.9

MF-LF

1%

1/16W

402

54.9

1/16W

MF-LF

1%

402

1%

MF-LF

1/16W

54.9

402

1%

MF-LF

1/16W

54.9

14 87

14 87

14 87

14 87

402

1%

MF-LF

1/16W

649

402

MF-LF

NOSTUF F

1K

5%

1/16W

402

16V

10%

0.1uF

NOSTUF F

X5R

402

PLACEM ENT_NO TE=Plac e R102 4 near ITP c onnecto r (if presen t)

54.9

1/16W

MF-LF

1%

OMIT

PENRYN

FCBGA

OMIT

PENRYN

FCBGA

CPU FSB

10

A.0.0

051-7546

96

SYNC_MA STER=M 87_MLB

SYNC_DA TE=10/ 17/2007

XDP_TC K

XDP_TD O

XDP_TM S

XDP_TD I

XDP_TR ST_L

=PP1V0 5_S0_C PU

=PP1V0 5_S0_C PU

=PP1V0 5_S0_C PU

TP_CPU _RSVD8

TP_CPU _RSVD7

TP_CPU _RSVD6

TP_CPU _RSVD5

FSB_A_ L<5>

FSB_A_ L<15>

FSB_A_ L<10>

FSB_AD S_L

CPU_IG NNE_L

CPU_TH ERMD_N

FSB_A_ L<11>

FSB_A_ L<7>

FSB_A_ L<8>

FSB_A_ L<9>

FSB_A_ L<27>

FSB_A_ L<26>

FSB_A_ L<24>

FSB_A_ L<23>

FSB_A_ L<22>

FSB_A_ L<21>

FSB_A_ L<20>

FSB_BP RI_L

FSB_A_ L<12>

FSB_A_ L<13>

FSB_AD STB_L< 0>

FSB_A_ L<17>

FSB_A_ L<19>

FSB_A_ L<28>

FSB_A_ L<29>

FSB_A_ L<30>

FSB_A_ L<31>

FSB_A_ L<32>

FSB_A_ L<33>

FSB_A_ L<34>

FSB_A_ L<35>

FSB_AD STB_L< 1>

CPU_FE RR_L

CPU_ST PCLK_L

CPU_IN TR

CPU_NM I

CPU_SM I_L

TP_CPU _RSVD0

TP_CPU _RSVD1

TP_CPU _RSVD2

TP_CPU _RSVD3

TP_CPU _RSVD4

FSB_BN R_L

FSB_DE FER_L

FSB_DR DY_L

FSB_DB SY_L

FSB_BR EQ0_L

CPU_IE RR_L

FSB_CP URST_L

FSB_RS _L<0>

FSB_RS _L<1>

FSB_RS _L<2>

FSB_TR DY_L

FSB_HI T_L

FSB_HI TM_L

XDP_BP M_L<0>

XDP_BP M_L<1>

XDP_BP M_L<2>

XDP_BP M_L<3>

XDP_BP M_L<4>

XDP_BP M_L<5>

XDP_TC K

XDP_TD I

XDP_TD O

XDP_TM S

XDP_TR ST_L

XDP_DB RESET_ L

CPU_PR OCHOT_ L

CPU_TH ERMD_P

PM_THR MTRIP_ L

FSB_CL K_CPU_ P

FSB_CL K_CPU_ N

FSB_RE Q_L<4>

FSB_RE Q_L<3>

FSB_RE Q_L<2>

FSB_RE Q_L<0>

FSB_A_ L<4>

FSB_A_ L<3>

FSB_A_ L<6>

CPU_A2 0M_L

CPU_IN IT_L

FSB_LO CK_L

FSB_RE Q_L<1>