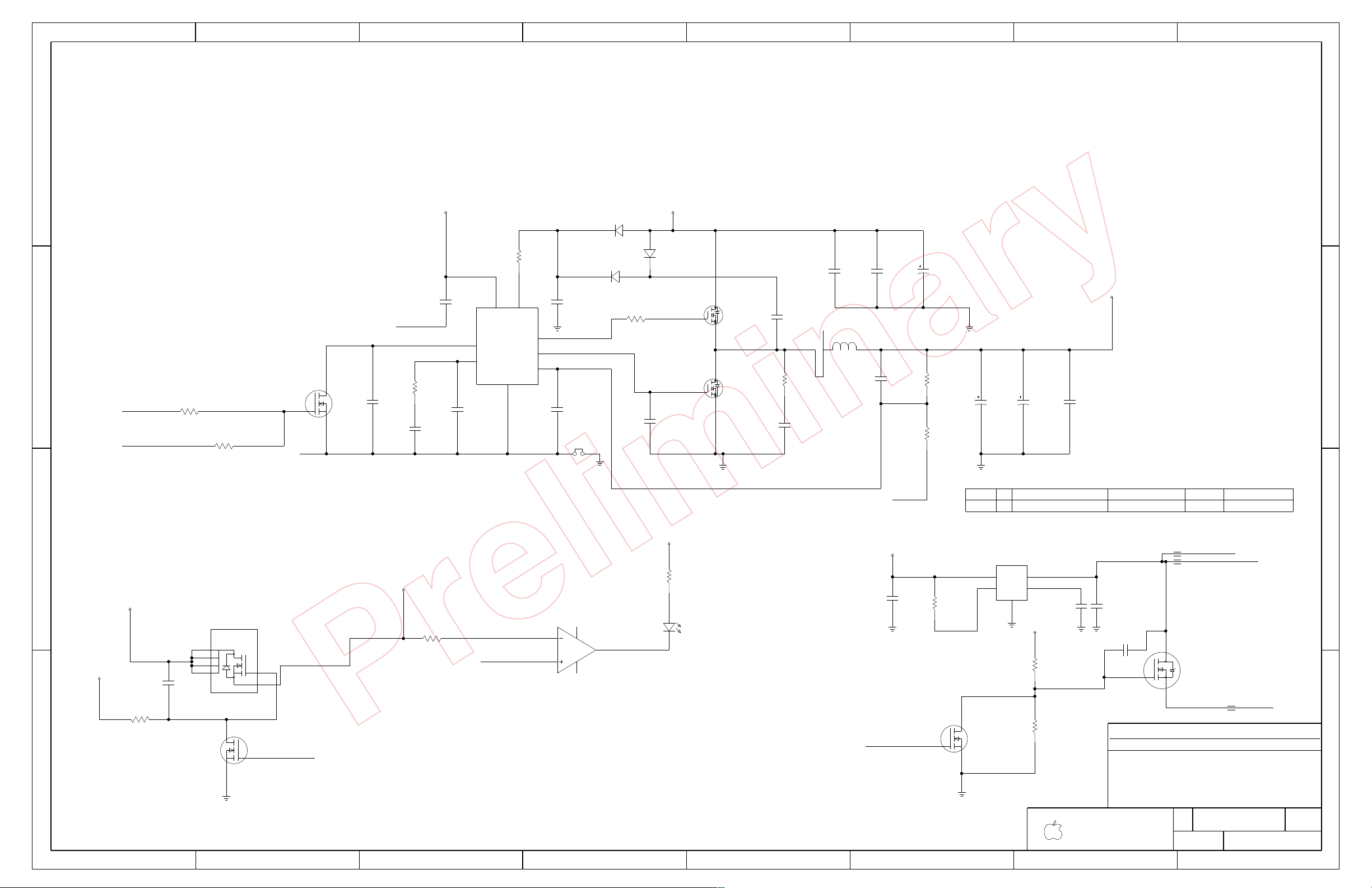

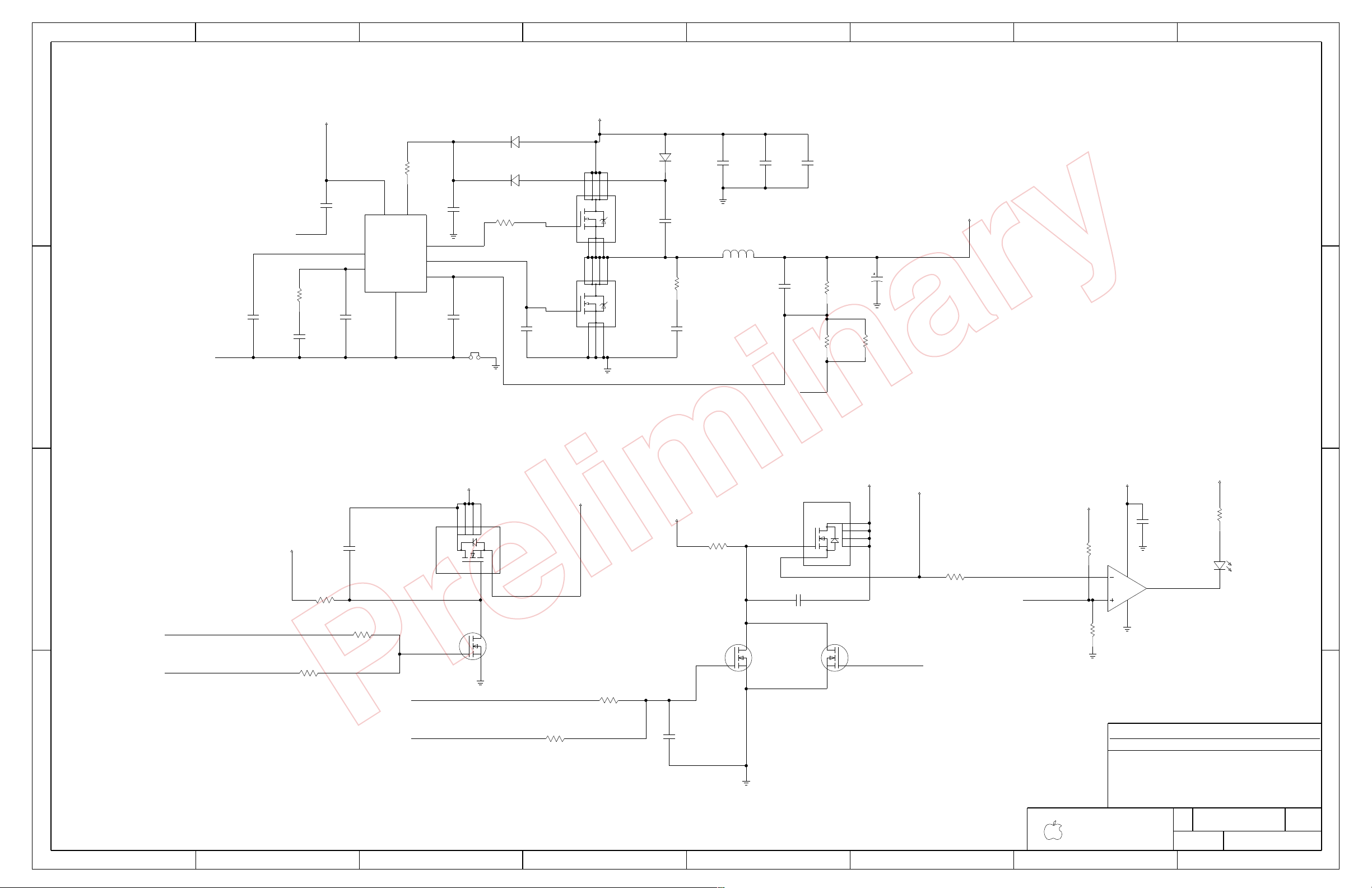

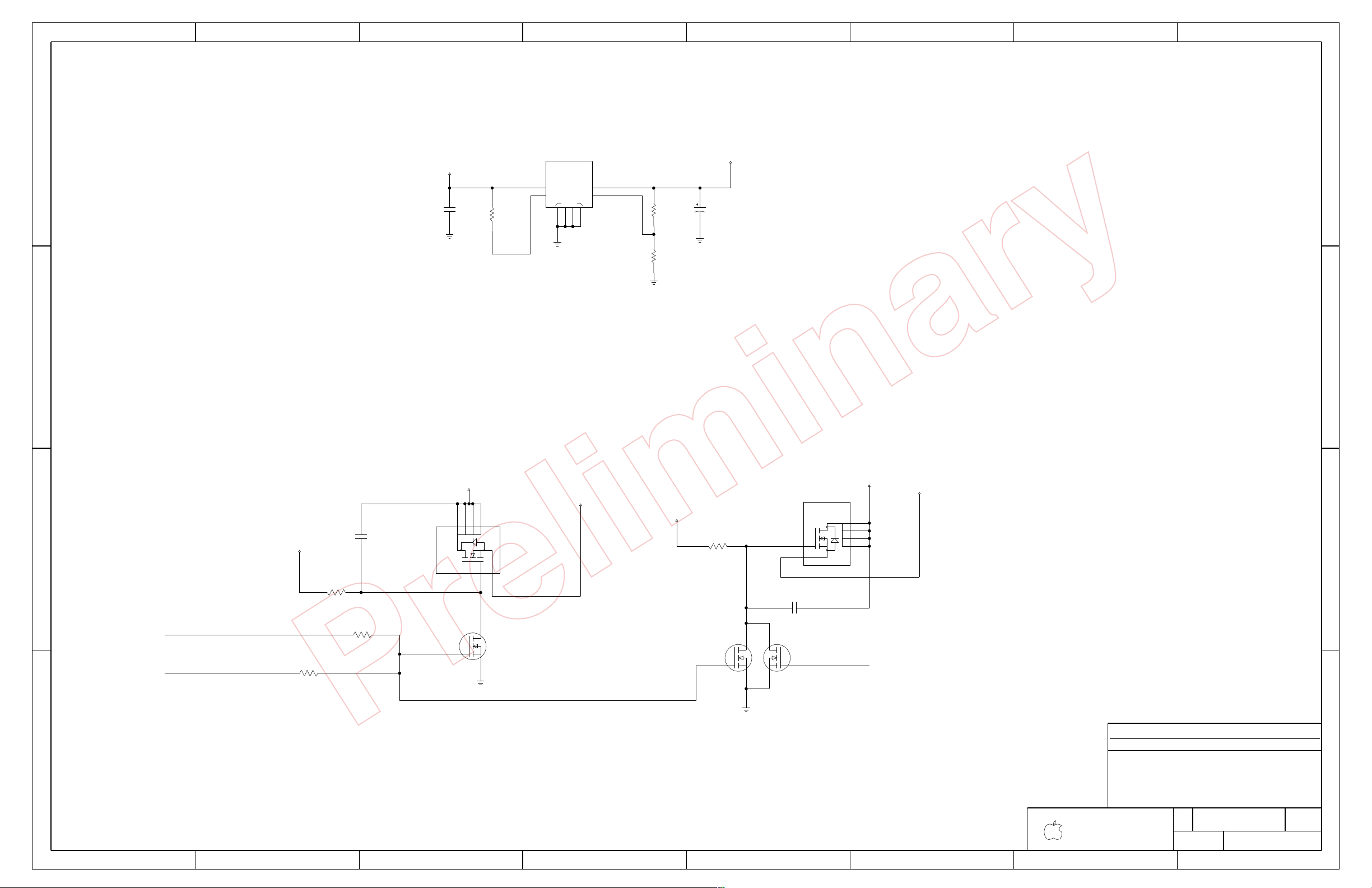

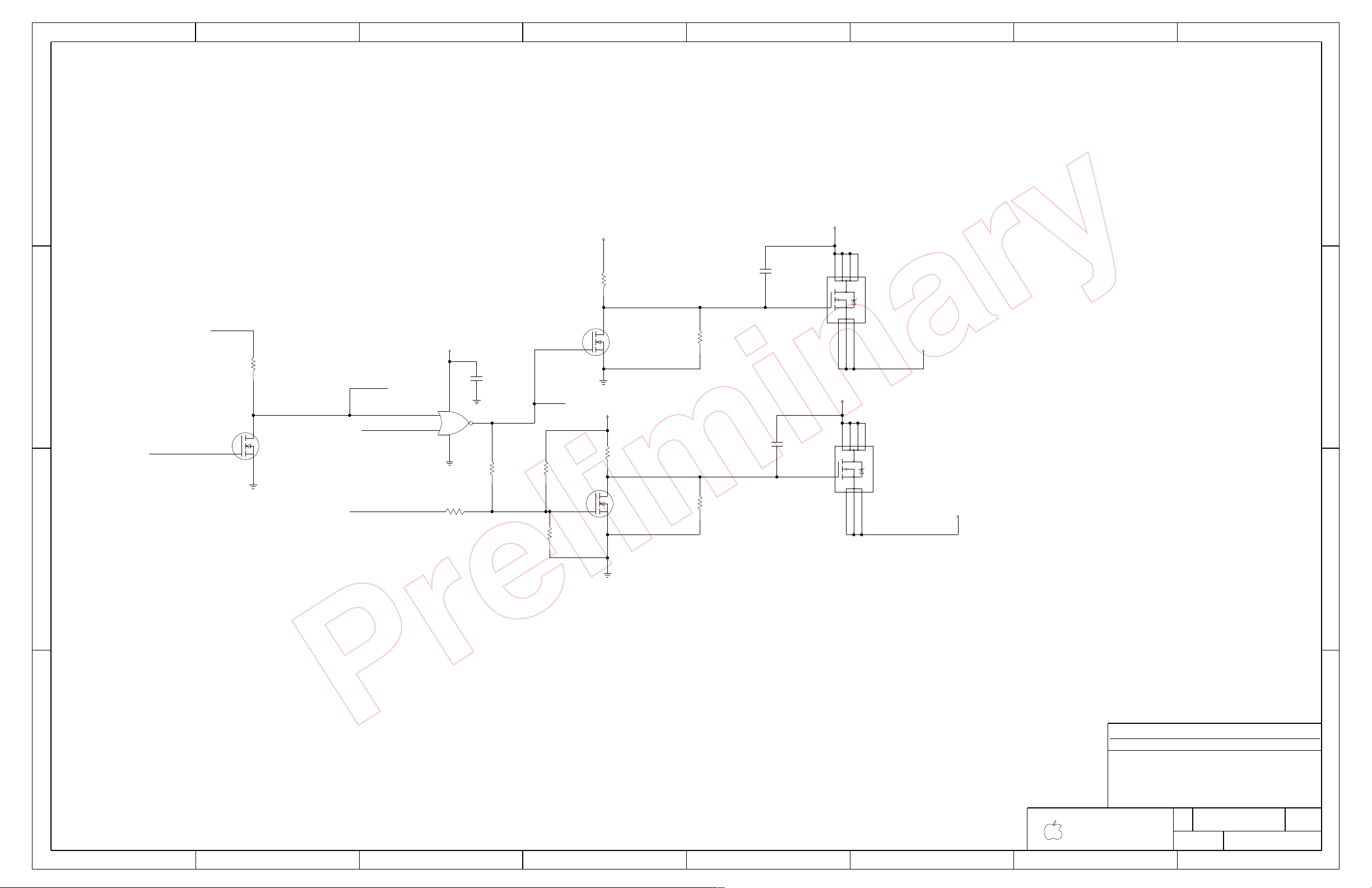

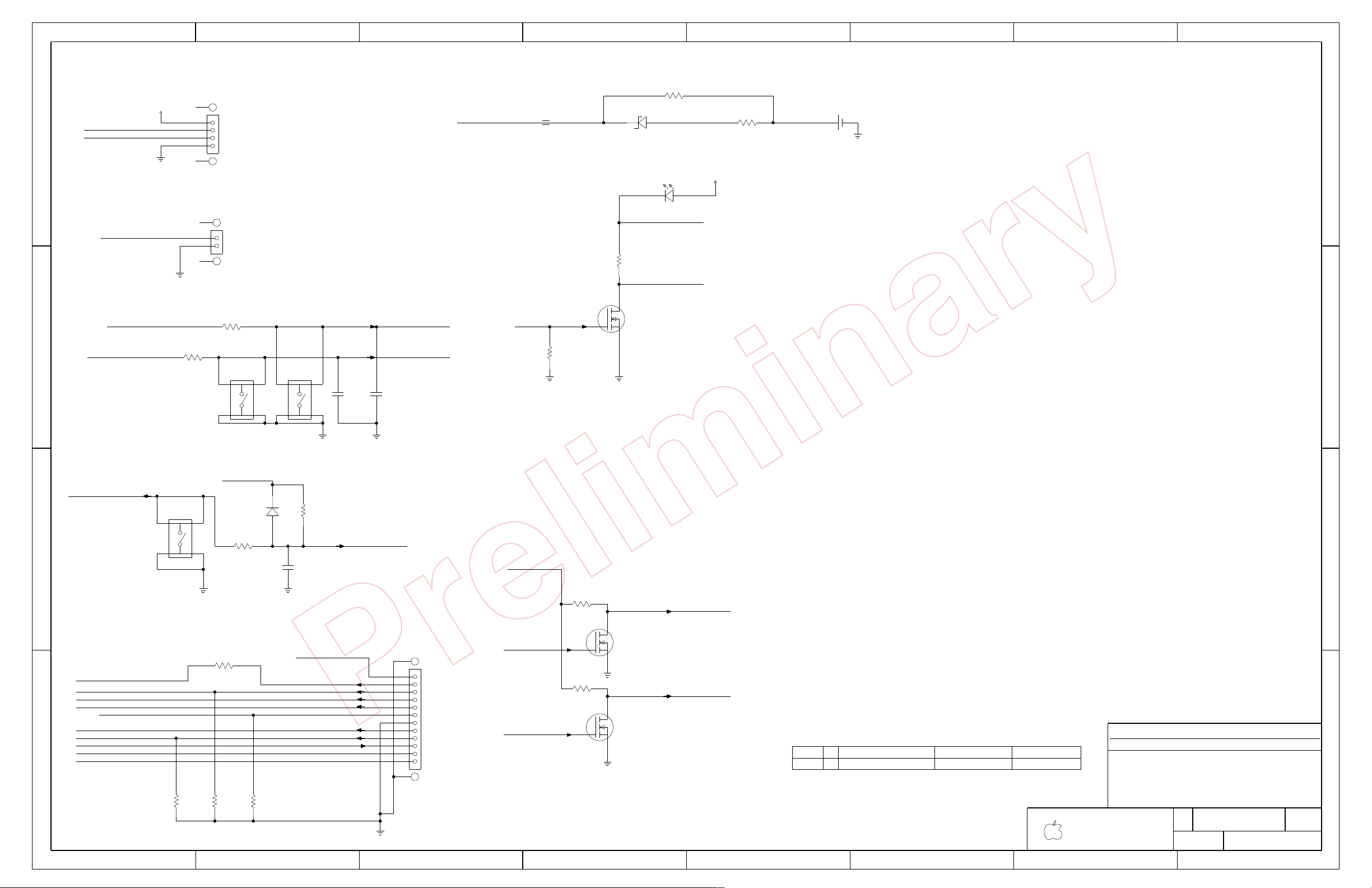

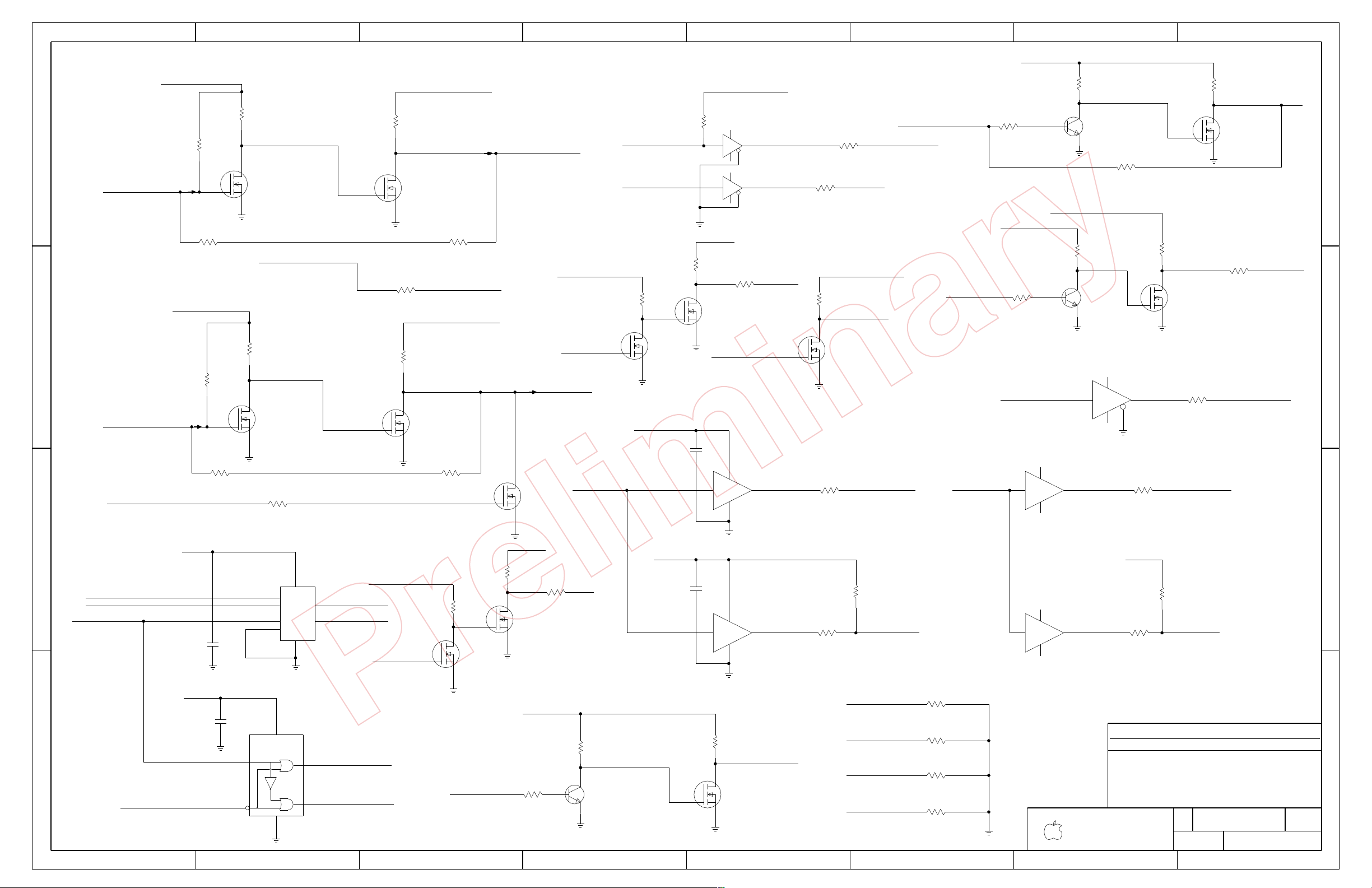

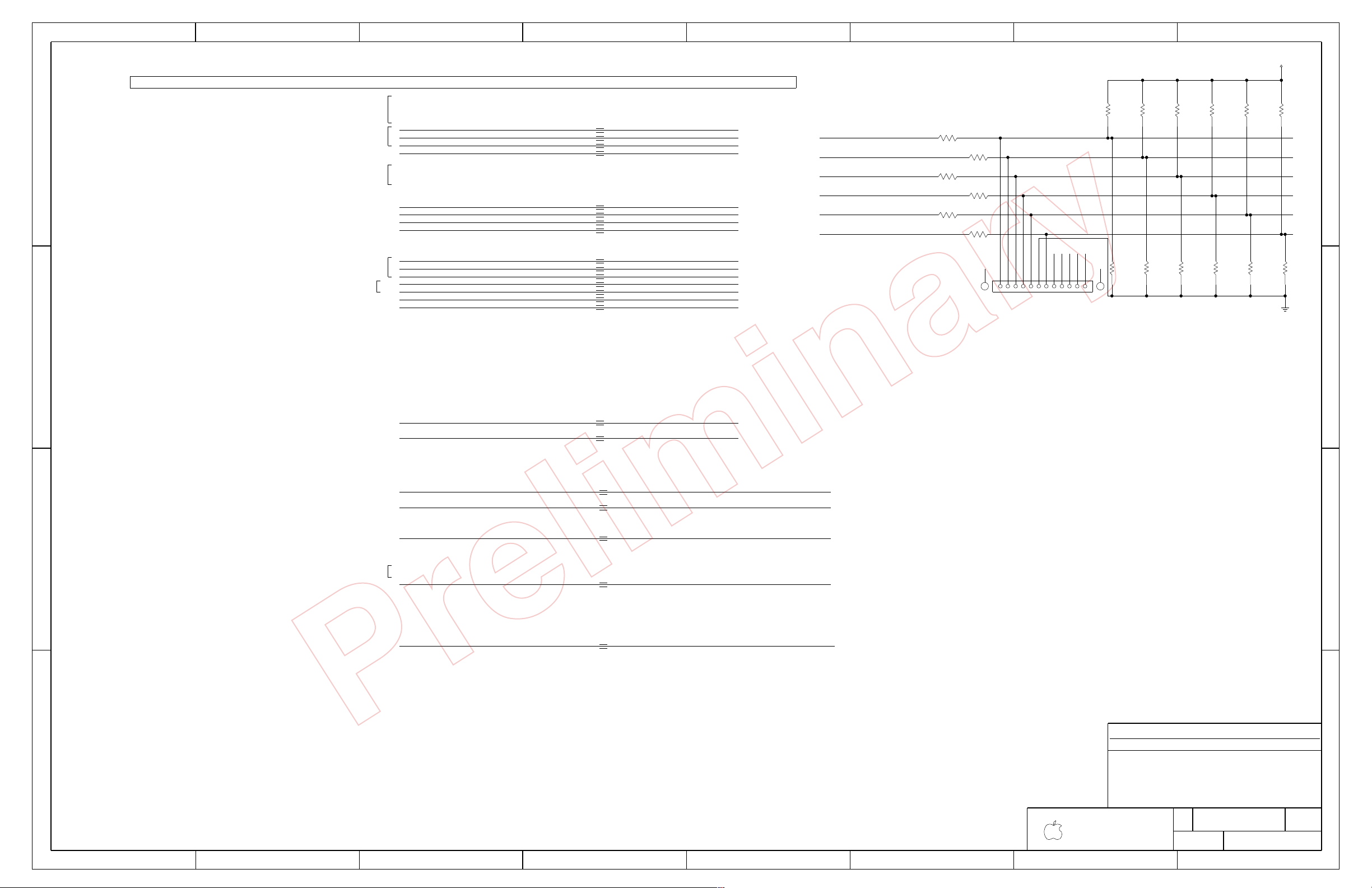

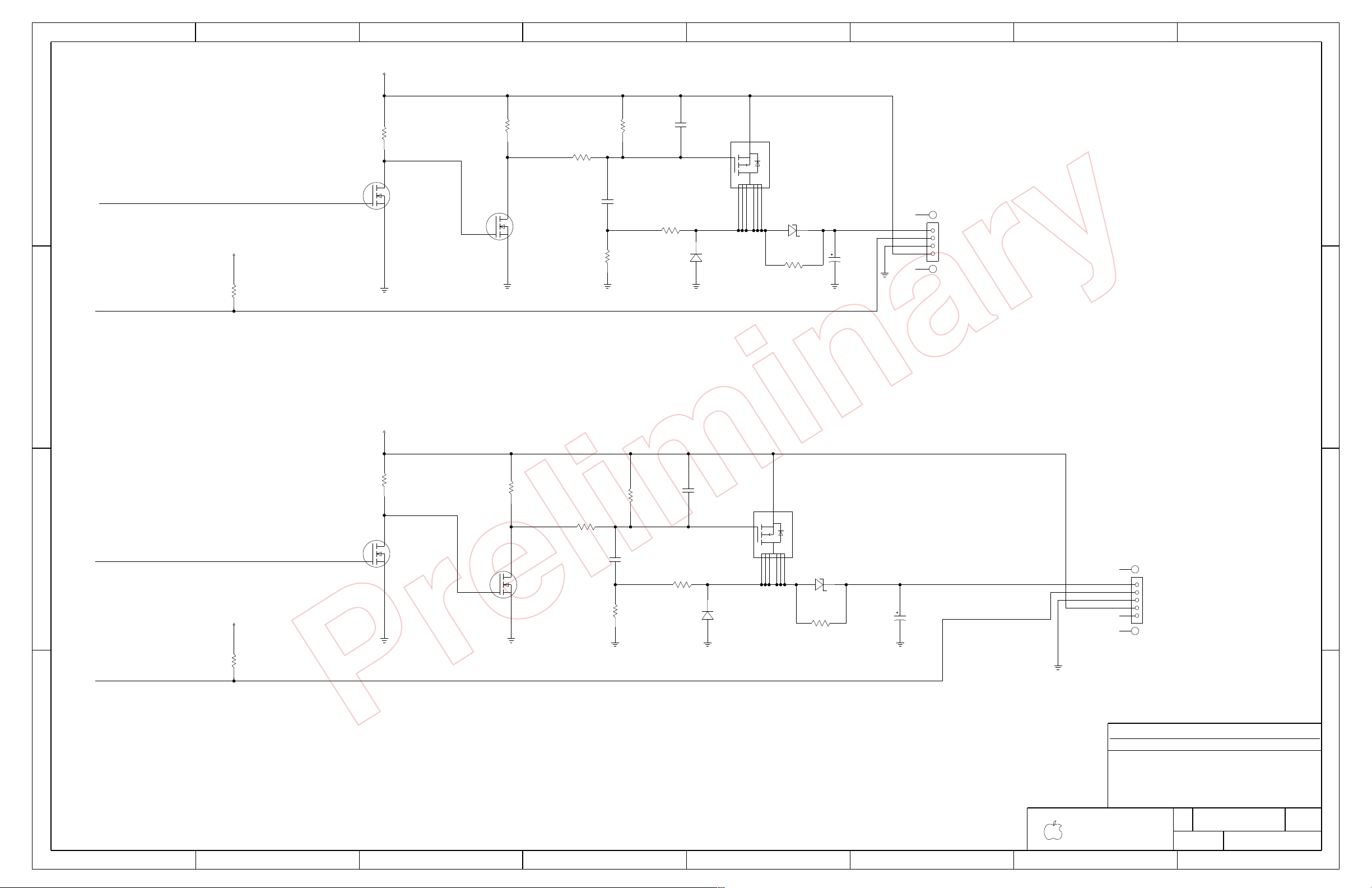

Apple IMAC G5 M33 Schematics

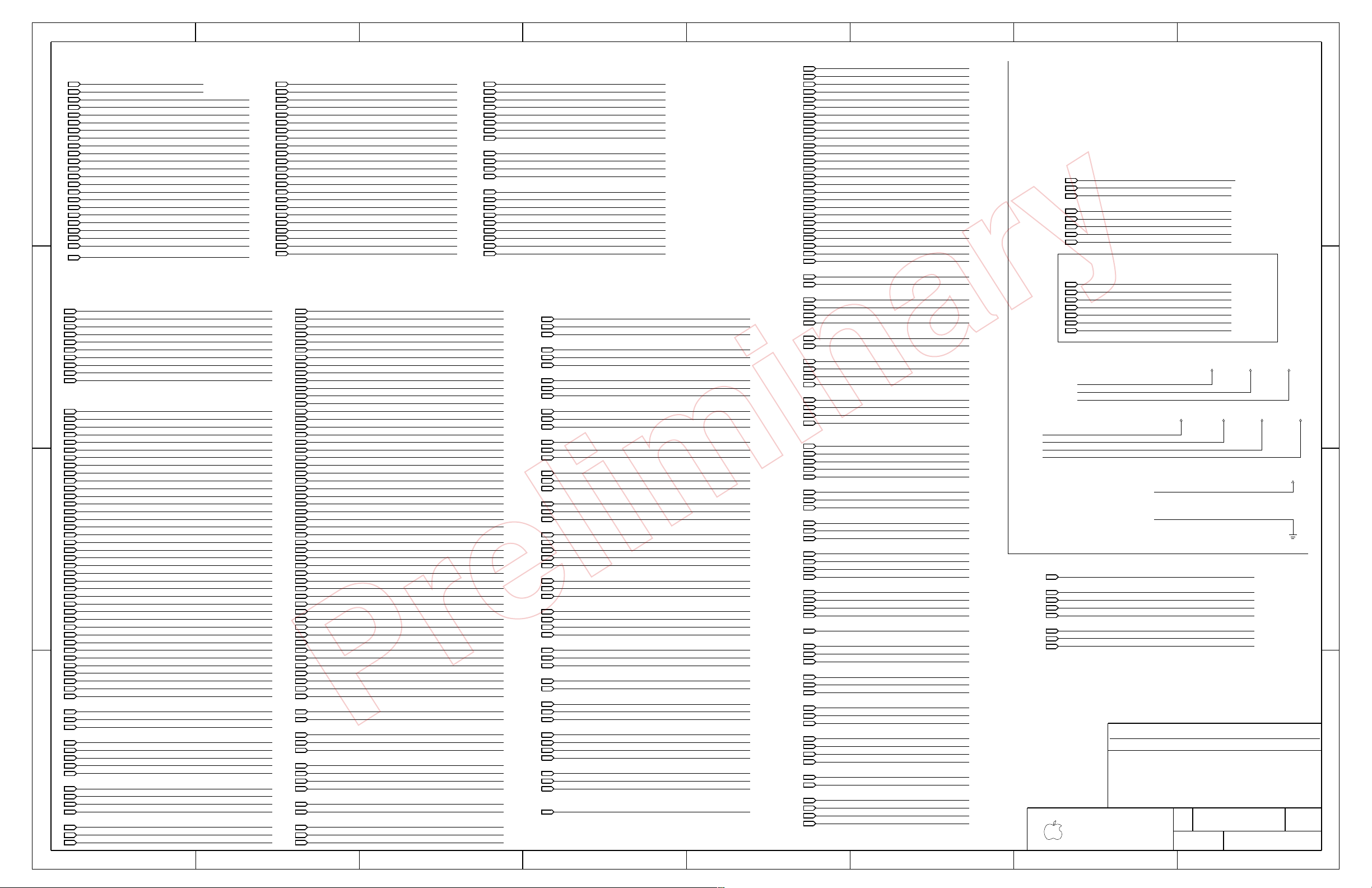

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

ANGLES

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

DATE

APPD

ENG

DATE

APPD

CK

ECN

ZONE

REV

DO NOT SCALE DRAWING

X.XXX

X.XX

XX

DIMENSIONS ARE IN MILLIMETERS

THIRD ANGLE PROJECTION

D

SIZE

APPLICABLE

NOTED AS

MATERIAL/FINISH

NONE

SCALE

DESIGNER

MFG APPD

DESIGN CK

RELEASE

QA APPD

ENG APPD

DRAFTER

METRIC

OF

SHT

DRAWING NUMBER

TITLE

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

Apple Computer Inc.

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

DESCRIPTION OF CHANGE

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEADTABLE_TABLEOFCONTENTS_HEAD TABLE_TABLEOFCONTENTS_HEAD

TABLE_TABLEOFCONTENTS_ITEMTABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

FINO M33

5/19/05

Shasta Serial / Misc

24

05/19/2005

18

FINO-ME

051-6863

SCH,MLB,FINO,M33

07

ENGINEERING RELEASED

381758

05/19/05

?

1

154

07

63

05/19/2005

FINO-EG

45

MEMORY ADDR BRANCHING

1.5V Vreg

12

05/19/2005

10

FINO-PC

CPU VCORE MORE BYPASS

52

05/19/2005

37

FINO-MS

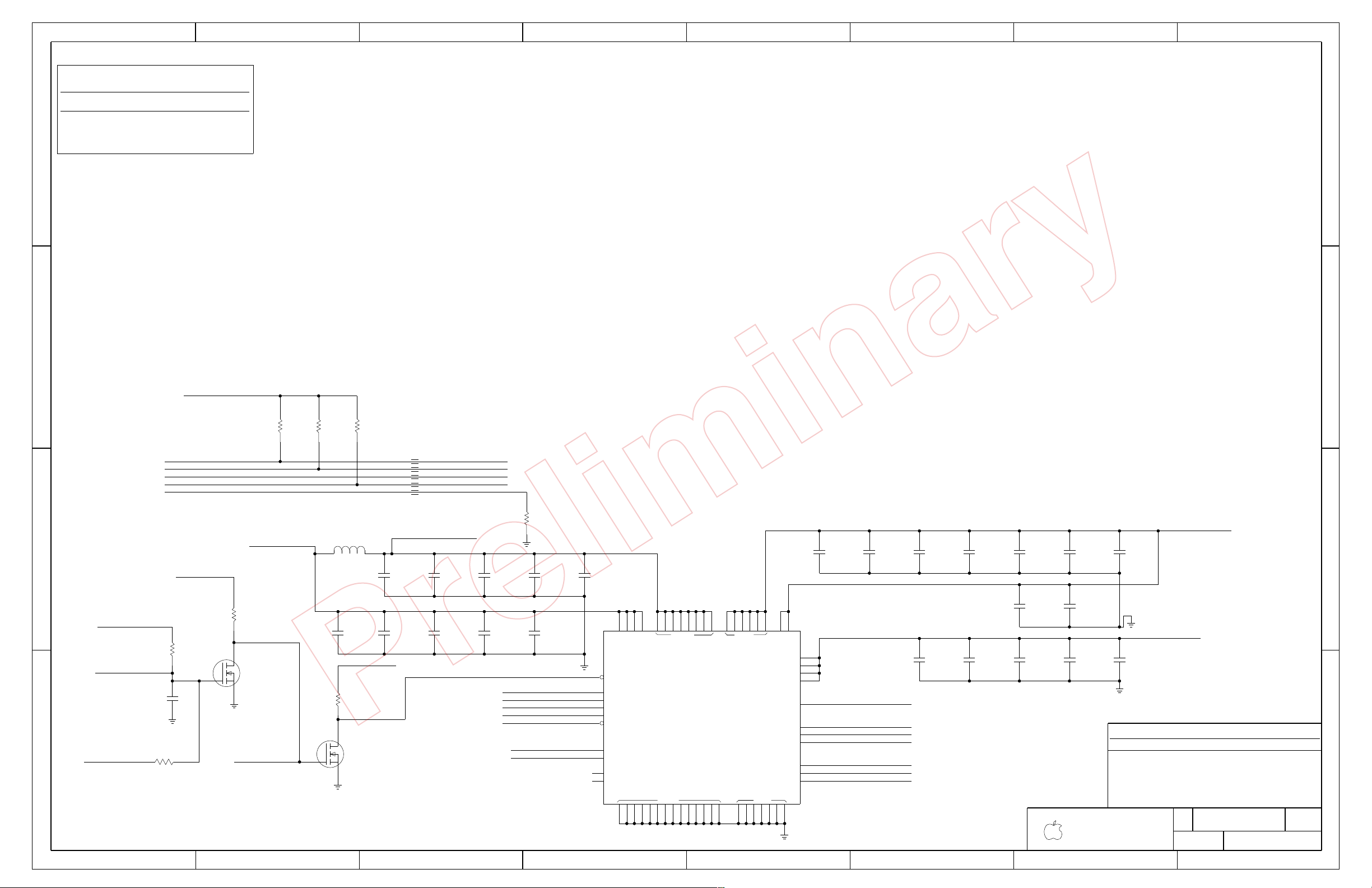

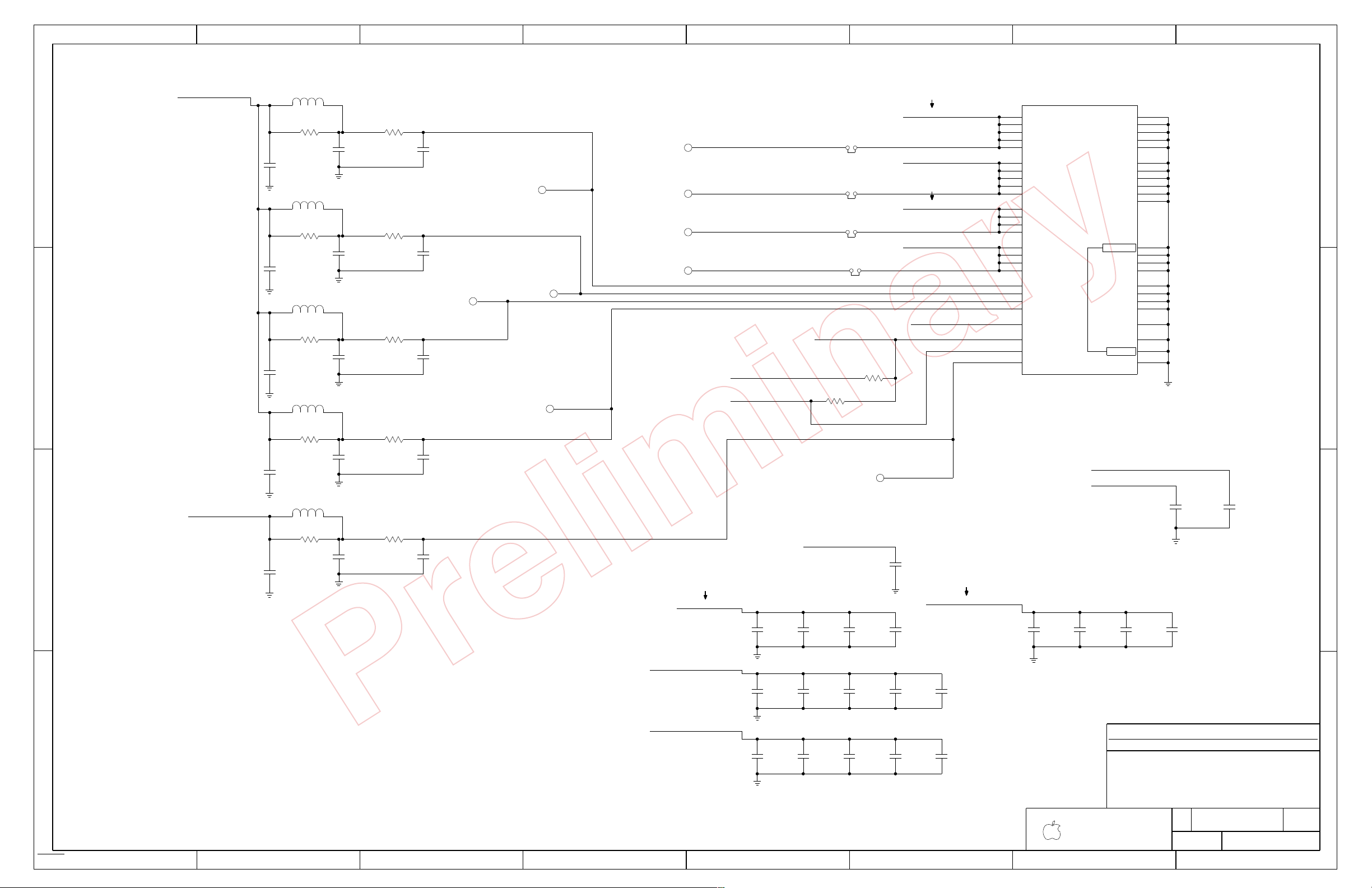

CPU VCORE VREG

50

05/19/2005

36

M33-MS

PROC DECOUPLING

49

05/19/2005

35

FINO-MS

CPU POWER AND BYPASS

48

05/19/2005

34

FINO-MS

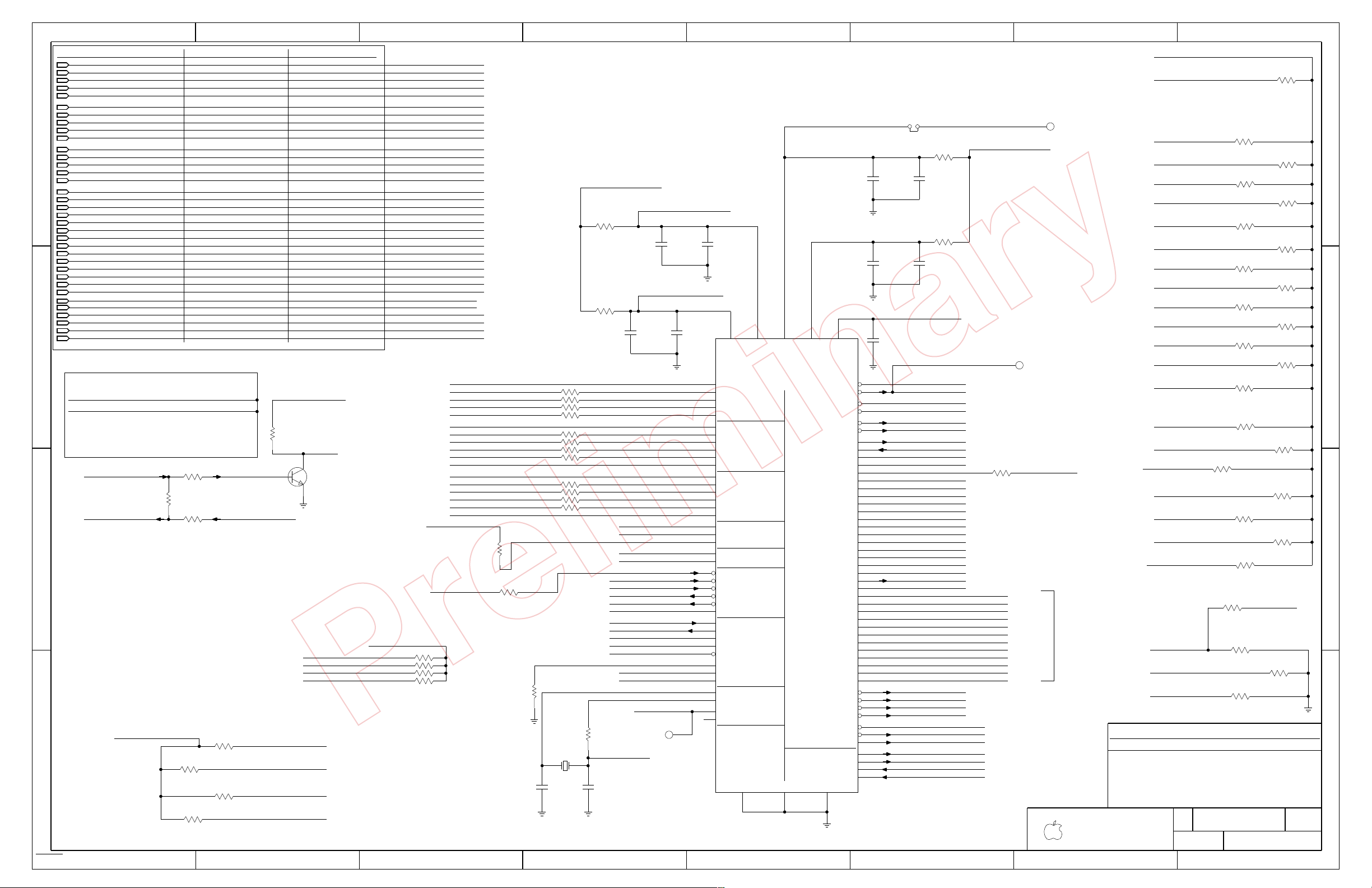

CPU STRAPS

47

05/19/2005

33

FINO-MS

KODIAK EI B

44

05/19/2005

32

Q63

CPU EI AND IO

43

05/19/2005

31

FINO-MS

KODIAK EI A

42

05/19/2005

30

Q63

KODIAK EI PWR & CAPS

41

05/19/2005

29

Q63

I2C Connections

39

05/19/2005

28

FINO-ME

Fan 2 & HD Temp

33

05/19/2005

27

FINO-PC

Fan 0, 1 & System Temp

32

05/19/2005

26

FINO-PC

SMU SUPPLEMENTAL (4)

31

05/19/2005

25

FINO-MS

SMU SUPPLEMENTAL (3)

30

05/19/2005

24

FINO-MS

SMU SUPPLEMENTAL (2)

29

05/19/2005

23

FINO-MS

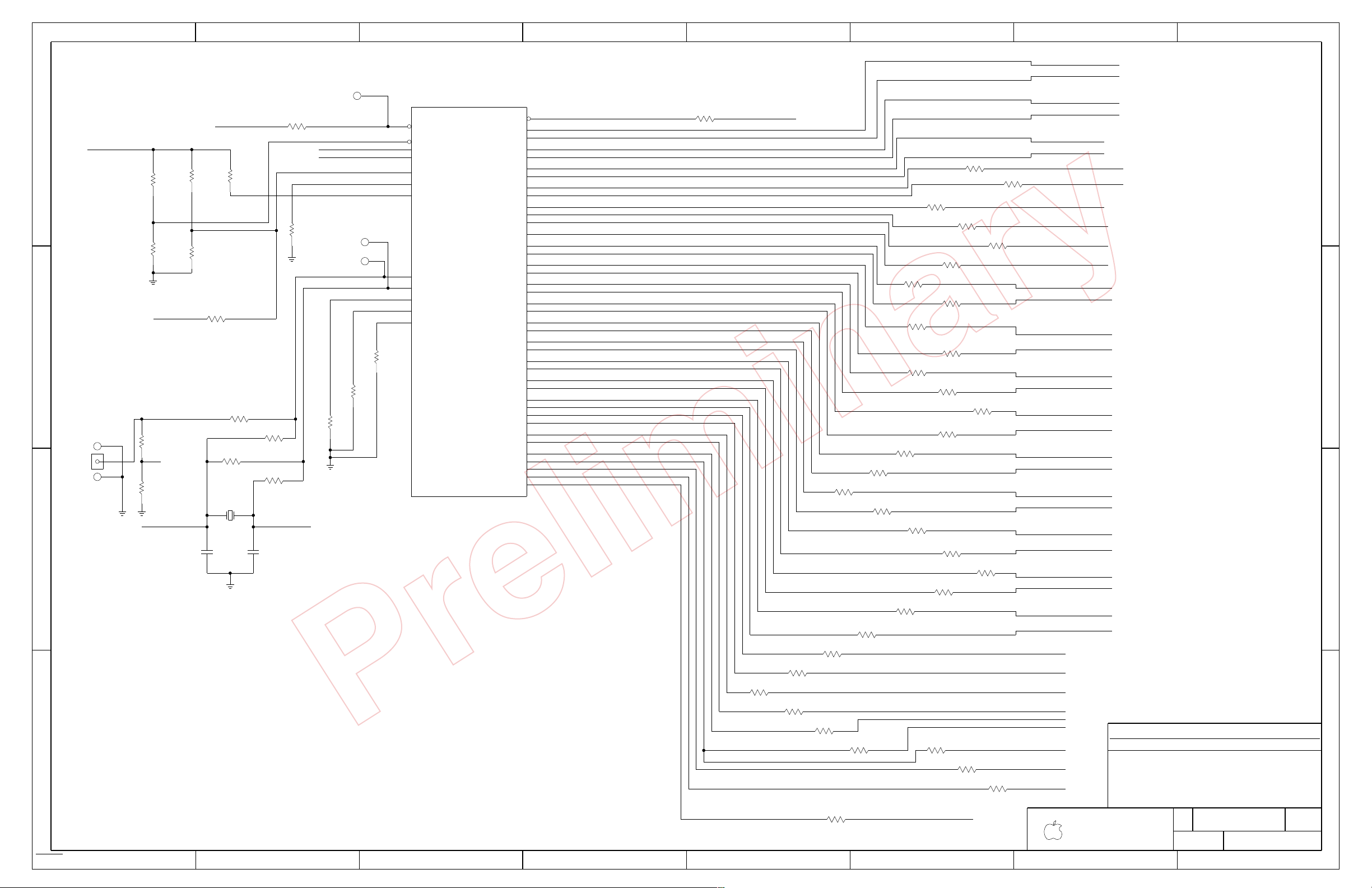

System Management Unit

28

05/19/2005

22

Q63

Pulsar Aliases

27

05/19/2005

21

FINO-ME

PULSAR2 CLOCKS

26

05/19/2005

20

FINO-ME

103

05/19/2005

Q63

65

Shasta HyperTransport

Shasta Core Power

23

05/19/2005

17

Q63

KODIAK & SHASTA MISC

20

05/19/2005

16

FINO-ME

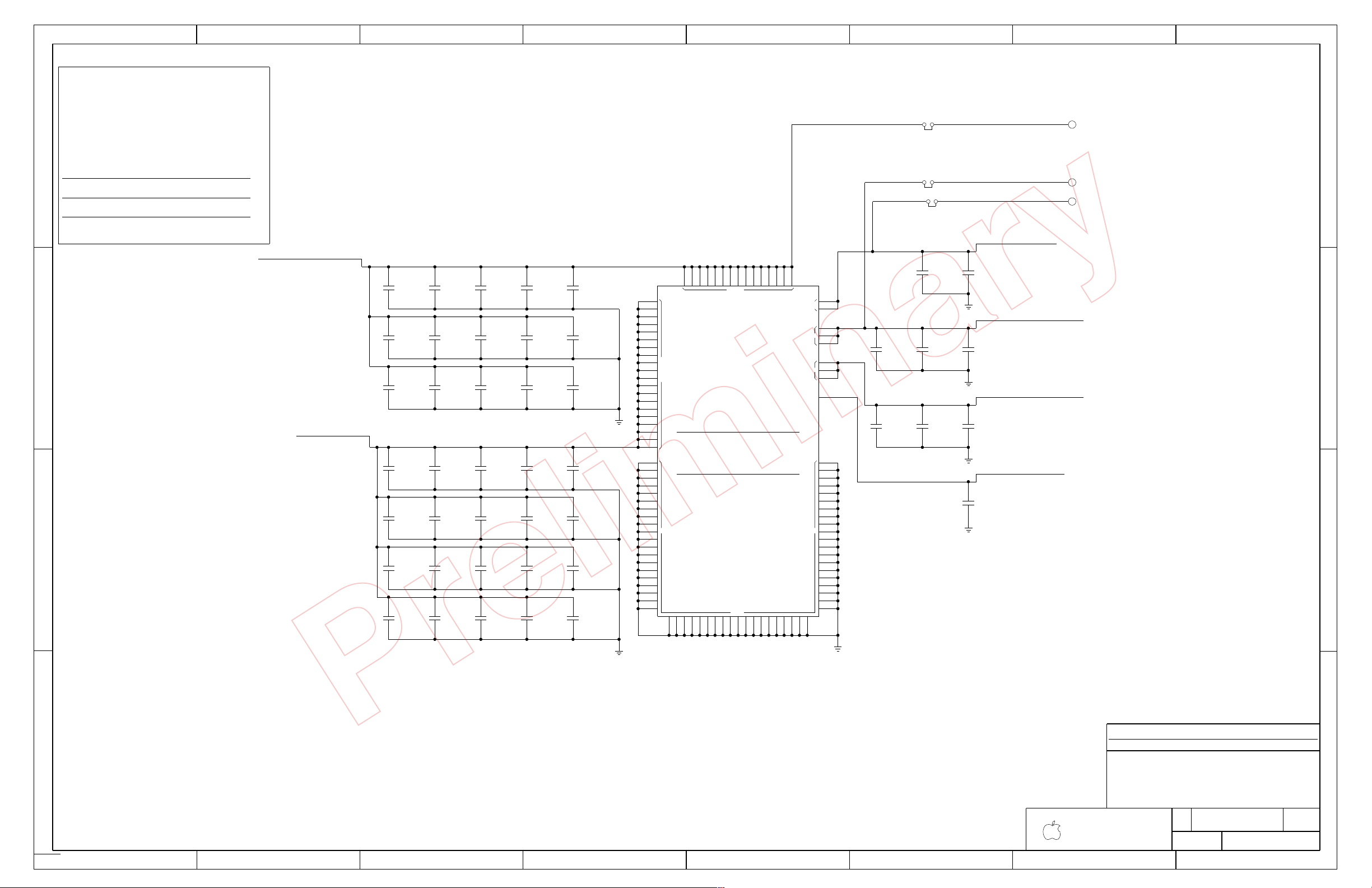

KODIAK CORE & BYPASS

19

05/19/2005

15

Q63

Vesta Core / Misc

17

05/19/2005

14

FINO-HC

5V & 3.3V Fets

16

05/19/2005

13

FINO-PC

2.5V Vreg

15

05/19/2005

12

FINO-PC

1.2V Vreg

13

05/19/2005

11

FINO-PC

1.8V VREG

11

05/19/2005

9

M33-PC

FUNC TEST 2 OF 2

9

05/19/2005

8

FINO-ME

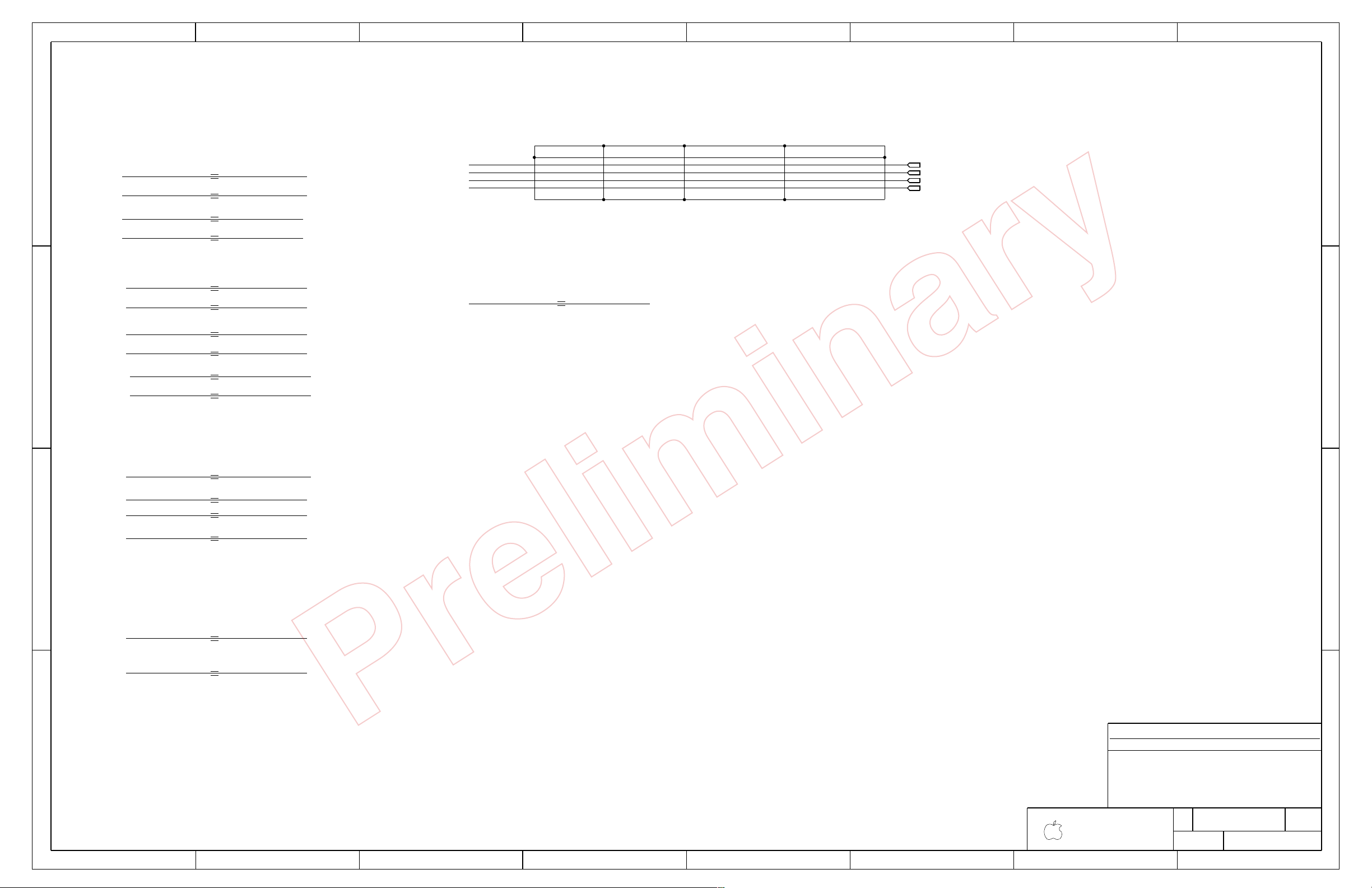

Signal Alias

8

05/19/2005

7

FINO-DD

POWER CONN / ALIAS

7

05/19/2005

6

M33-PC

FUNC TEST 1 OF 2

6

05/19/2005

5

FINO-ME

Table Items

5

05/19/2005

4

FINO-DD

Power Block Diagram

4

05/19/2005

3

FINO-PC

130

05/19/2005

FINO-HC

73

ENET SERIES TERM

129

05/19/2005

M33-MB

72

Disk Connectors

127

05/19/2005

M33-MB

71

Shasta Disk

125

05/19/2005

Q63

70

BootROM

122

05/19/2005

Q63

69

USB 2.0 PCI Interface

121

05/19/2005

FINO-EG

68

AIRPORT & BLUETOOTH

120

05/19/2005

FINO-EG

67

PCI SERIES TERMINATION

119

05/19/2005

Q63

66

Shasta PCI Interface

PULSAR2 POWER

25

05/19/2005

19

Q63

98

05/19/2005

Q63

63

KODIAK HT16

97

05/19/2005

FINO-DD

62

KODIAK PCI-E CONST

96

MASTERM33-DD

61

TMDS / ExtVGA

93

05/19/2005

FINO-DD

60

GPU DVI & DACs

92

05/19/2005

FINO-DD

59

GPU Straps

91

MASTERM33-DD

58

FB Parallel Termination

90

05/19/2005

FINO-DD

57

GPU GDDR SDRAM B

89

05/19/2005

FINO-DD

56

GPU GDDR SDRAM A

88

05/19/2005

FINO-DD

55

FB Series Termination

87

05/19/2005

FINO-DD

54

GPU Frame Buffer

86

05/19/2005

FINO-DD

53

GPU Core Power

85

MASTERM33-DD

52

Graphics Vregs

84

05/19/2005

FINO-DD

51

GPU PCIe

82

05/19/2005

Q63

50

KODIAK PCI-E X16

70

05/19/2005

FINO-RT

49

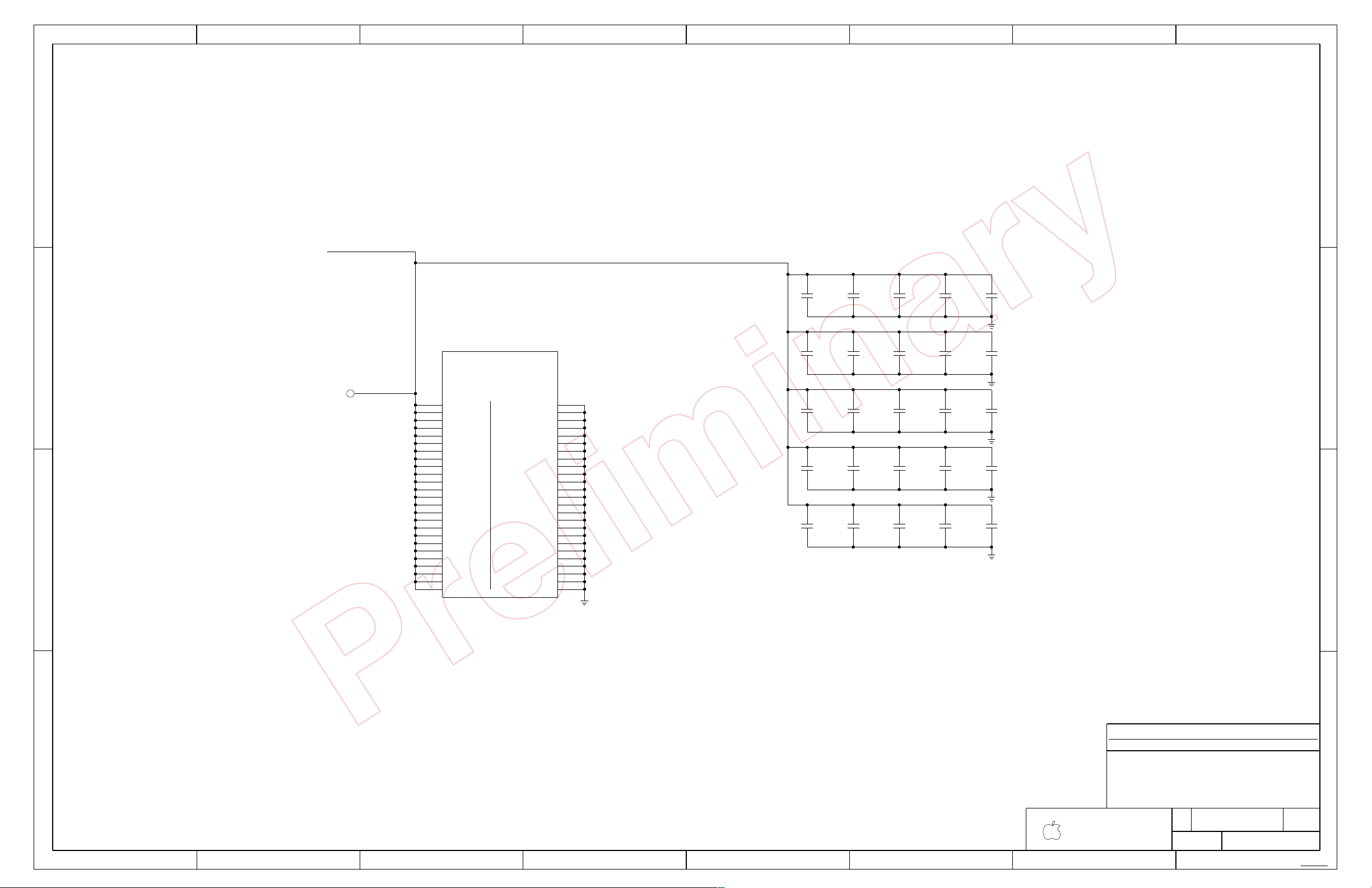

On-Board DDR SDRAM

69

05/19/2005

FINO-RT

48

On-Board DDR SDRAM

68

05/19/2005

FINO-RT

47

MLB Mem Series Term

67

05/19/2005

FINO-RT

46

Memory Dimm A

62

05/19/2005

FINO-RT

44

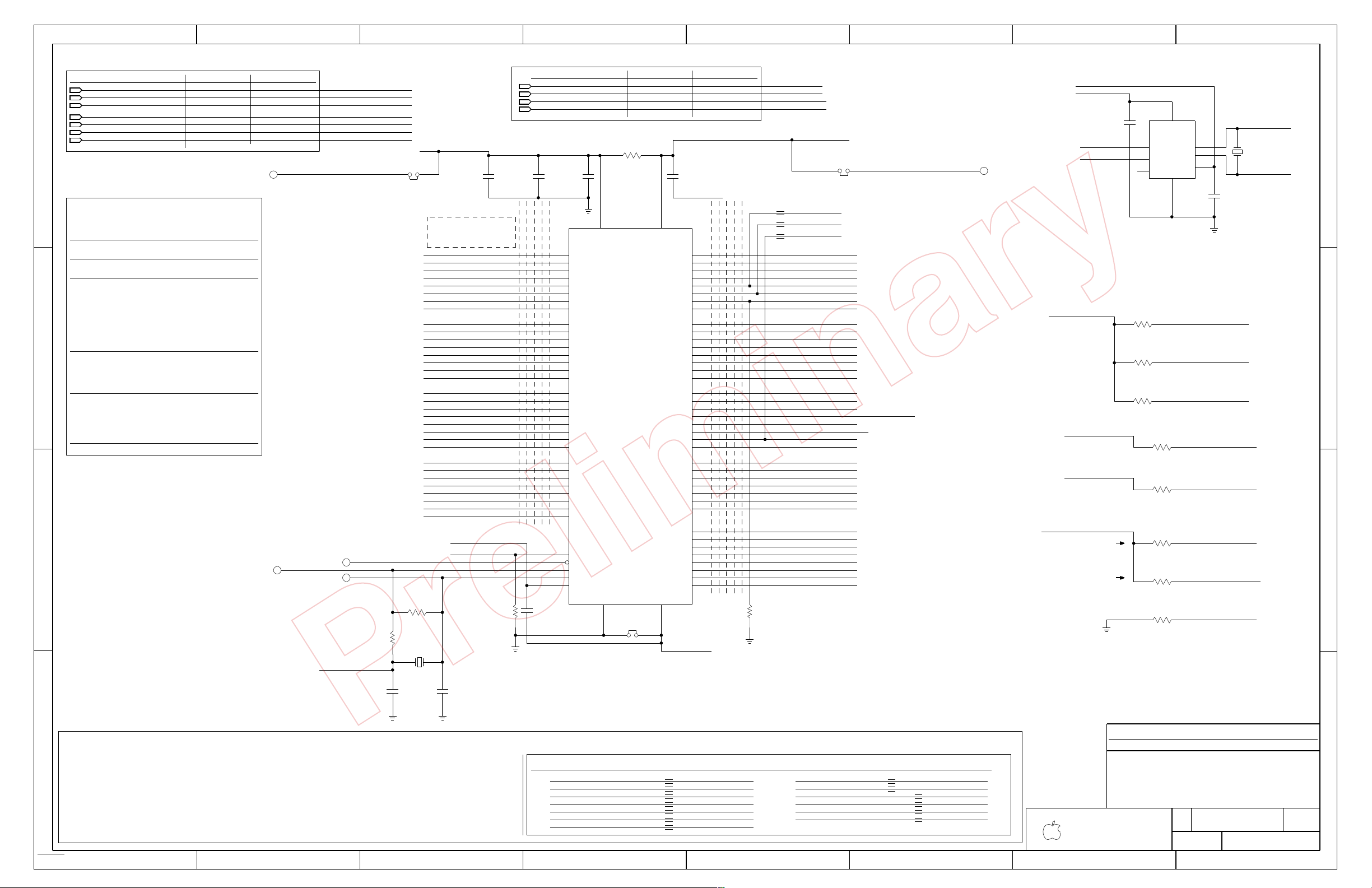

Main Memory Clock Buffer

61

05/19/2005

FINO-RT

43

Parallel Term

59

05/19/2005

FINO-RT

42

Kodiak Memory Dq/Ctl

58

05/19/2005

Q63

41

KODIAC NBMEM PWR & CAPS

56

05/19/2005

FINO-MS

40

CPU ALIASES & MISC

101

05/19/2005

FINO-EG

64

HT ALIASES

55

05/19/2005

FINO-MS

39

T,V,I SENSORS

89

FINO-SO

05/19/2005

154

AUDIO: POWER SUPPLIES

88

FINO-SO

05/19/2005

153

AUDIO: CONNECTORS

87

FINO-SO

05/19/2005

152

AUDIO: SPEAKER AMP

86

FINO-SO

05/19/2005

150

AUDIO: LINE OUT AMP

85

FINO-SO

05/19/2005

148

AUDIO: LINE INPUT AMP

84

FINO-SO

05/19/2005

147

AUDIO: CODEC

83

FINO-PC

05/19/2005

145

Flash Connector

82

FINO-PC

05/19/2005

144

Flash Media Ctrl

81

FINO-MB

05/19/2005

143

USB Device Interfaces

80

Q63

05/19/2005

142

USB Host Interfaces

79

FINO-HC

05/19/2005

140

FIREWIRE CONNECTORS

78

Q63

05/19/2005

139

Vesta FireWire PHY

77

Q63

05/19/2005

138

Shasta FireWire

76

FINO-HC

05/19/2005

136

ETHERNET CONNECTOR

75

Q63

05/19/2005

132

Vesta Ethernet PHY

74

Q63

05/19/2005

131

Shasta Ethernet

CONTENTS

DATE

SYNC MASTER

PDF CSACSAPDF DATE

CONTENTS

SYNC MASTER SYNC MASTER

DATEPDF CSA

CONTENTS

54

05/19/2005

FINO-MS

38

CPU AVDD VREG

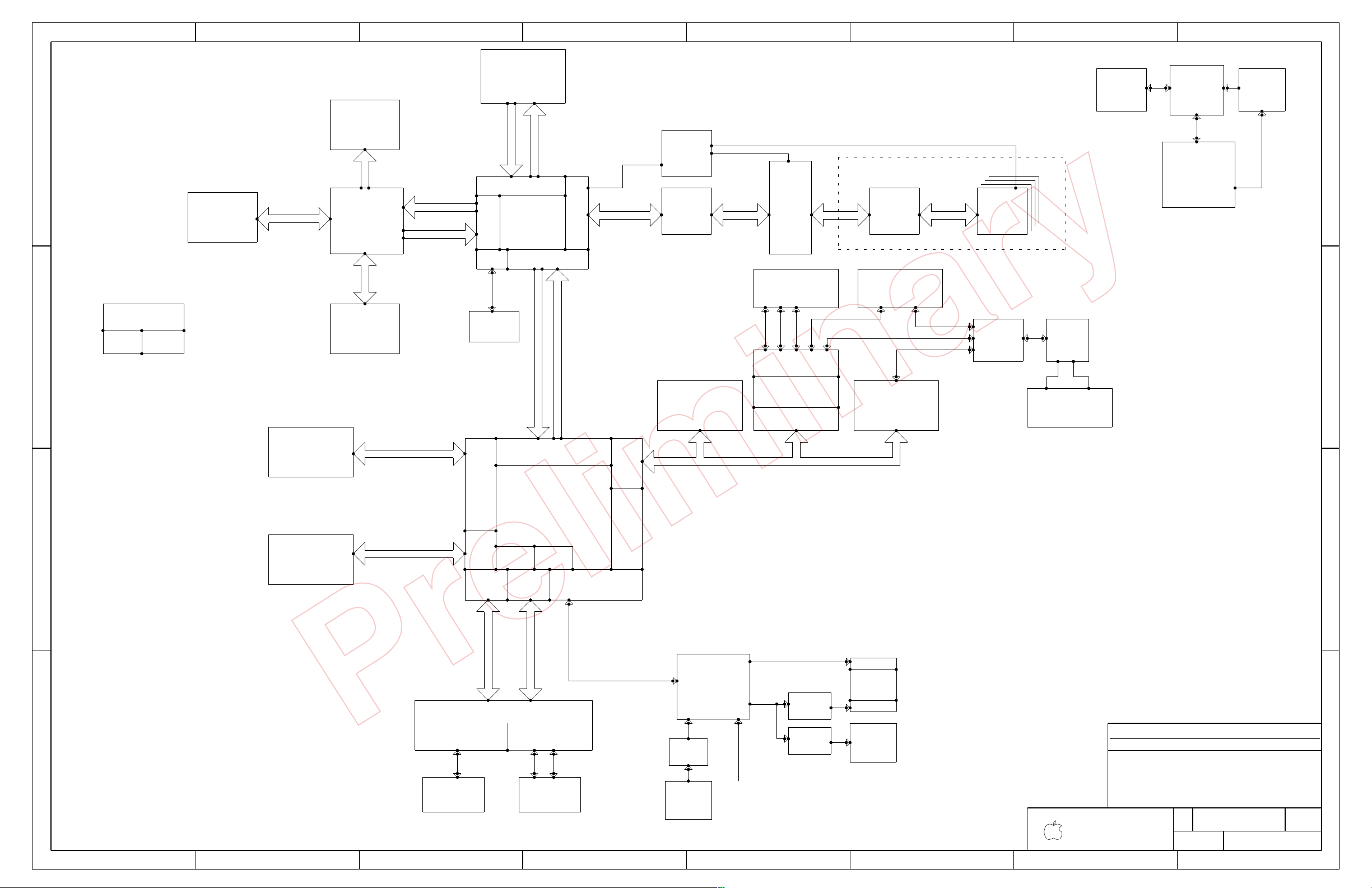

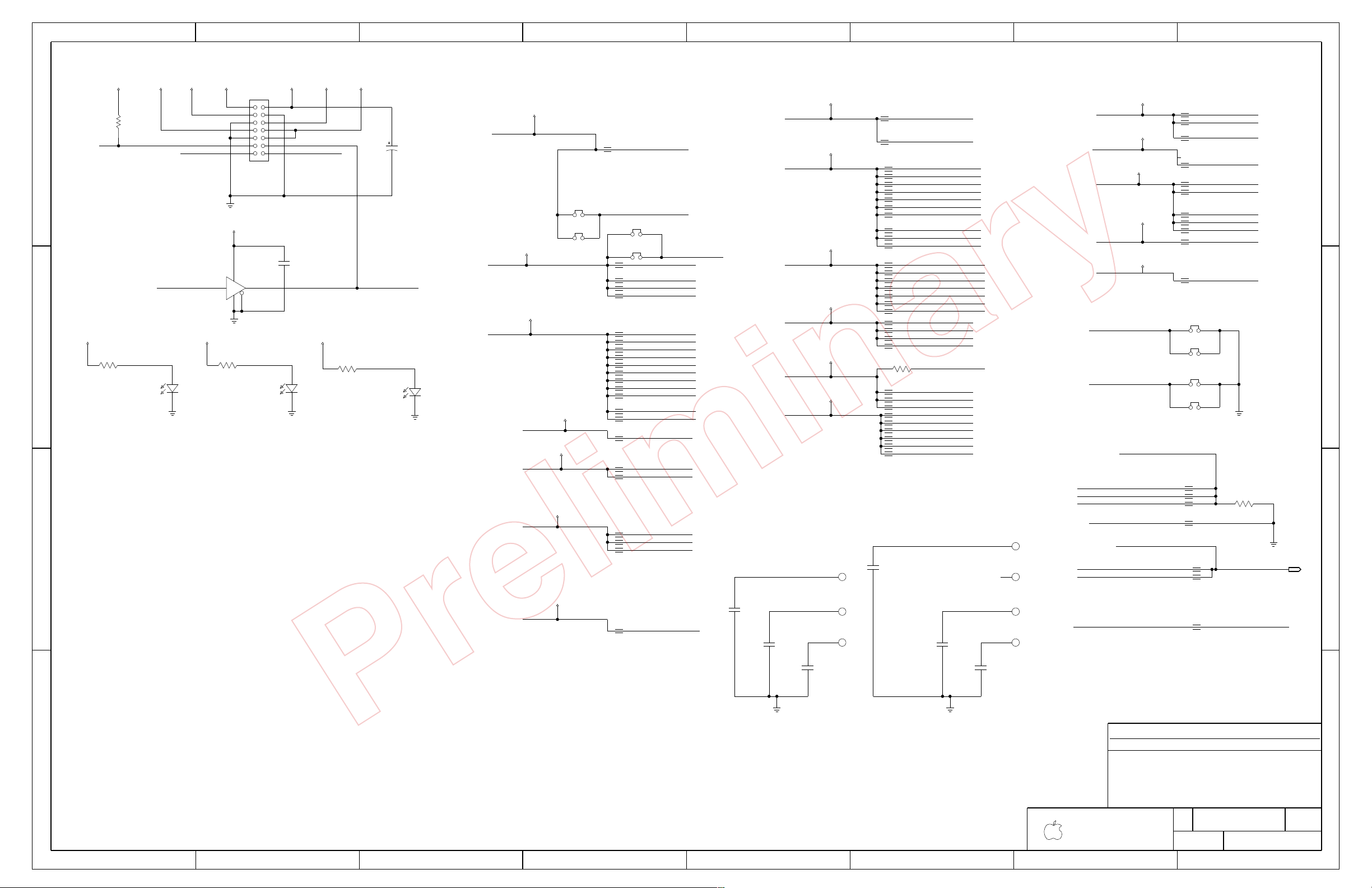

System Block Diagram

2

05/19/2005

2

FINO-DD

www.Vinafix.vn

Preliminary

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

PAGES 29,30

SMU SUPPLEMENTAL

U2801

RTC

PAGE 28

BATTERY

SYSTEM LED

ALS

BUTTONS

TEMP SENSORS

PAGE 28

SMU

U2800

PAGES 32,33

FANS

UE400

FLASH

667MHZ OR 733MHZ

JF303

PAGE 153

PAGE 153

JF301

PAGE 150

PAGE 152

JF300

PAGE 153

PAGE 148

PAGE 147

UE700

INTERFACE

BNDI

JEC00, JEC01

JD600

PAGE 136 PAGE 140

PAGE 139PAGE 132

U1701

PAGE 142

PAGE 127

PAGE 131 PAGE 138

PAGE 24

PAGE 24

PAGE 119

PAGE 103

PAGE 127

JC901

PAGE 129

PAGE 129

JC900

PAGE 142

UC200

UC500

PAGE 125 PAGE 122 PAGE 121

JC150

PAGE 145

PAGE 144

JE500

CF

CTLR

SD

MEDIA CARD CONNECTOR

UE401

PAGE 144

USB

HUB

PAGE 143 PAGE 143

JE350

JE310/JE320/JE330

PAGES 67,70

PAGES 68

J6700

PAGE 67

PAGE 61

ELASTIC INTERFACE

PARALLEL

U6200

64-BIT

PAGE 62

PAGE 39

PAGE 26PAGE 25

U2500

EXT VGA

TMDS

PAGE 96

PAGE 90

U9000, U9001

PAGE 89

U8900, U8901

M33:1.8V/700MHZ

M33:1.8V/700MHZ

M23:1.8V/600MHZ

M23:1.8V/600MHZ

M33:RV380 XT

PAGES 84,86,87,93

U8400

U1900

PAGE 19

PAGE 59

PAGE 98PAGE 20

82

PAGE 42

PAGE 43,48

U4300

GPU

TERM

DIMM

64MX8

MEMORY

SERIES

MAIN MEMORY

TERM

PCIE X16

MAIN MEMORY

1.8V/533MHZ

64-BIT

FRAME BUFFER

I2C

SATA

CONNECTOR

PCIE

KODIAK

PAGE

NEO 10S

CPU

HYPERTRANSPORT

HYPERTRANSPORT

CORE

CONTROL = 2.5V

HYPERTRANSPORT

8-BIT

APPLE PI

32-BIT

APPLE PI

BUFFER B

64-BIT

FRAME

BUFFER A

FRAME

MISC

SATA

U2300

SATA1 SATA2

1.2V/1.5GHZ

SATA/150

UATA/133

UATA

UATA

3.3V/133MHZ

CONNECTOR

PCI

GPIO/PCI64

CORE

PAGE 23

ETHERNET FIREWIRE

I2S2I2S0

I2S

I2S1

SCCA SCCB

8-bit TX/RX

2 Diff pairs

1

FIREWIRE A

0

GMII (3.3V/125MHz)

8-bit TX & 8-bit RX

CONNECTOR

4 Diff pairs

CLOCKS

POWER

ETHERNET

CONNECTORS

32-bit PCI (5V-3.3V/33MHz)

AMP

SPEAKER

CONNECTOR

COMBO OUT

OPTICAL OUT

LINE OUT

SPEAKER

CONNECTOR

LINE IN

CONNECTOR

LINE IN

AMP

AUDIO CODEC

AMP

LINE OUT

1394 OHCI (3.3V/98MHz)

S/PDIF

NCs

FRAME BUFFER

1.2V/800MHZ

PCM3052A

FIREWIRE A

GIG ETHERNET

SHASTA

VESTA

HARD DRIVE

OPTICAL

5

USB

321

uPD720101

PCI

BOOTROM

CONNECTOR

PULSAR2

CLOCK

BUFFER

ONBOARD MEMORY

4

WIRELESS

USB 2.0

USB

INTERFACE

BNDI

CONNECTORS

J9602, J9603

M23:RV370 XT

2.5GHZ

2

07

051-6863

154

System Block Diagram

SYNC_DATE=05/19/2005

SYNC_MASTER=FINO-DD

www.Vinafix.vn

Preliminary

IN

IN

LM339A

V+

GND

LM339A

V+

GND

IN

LM339A

V+

GND

IN

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

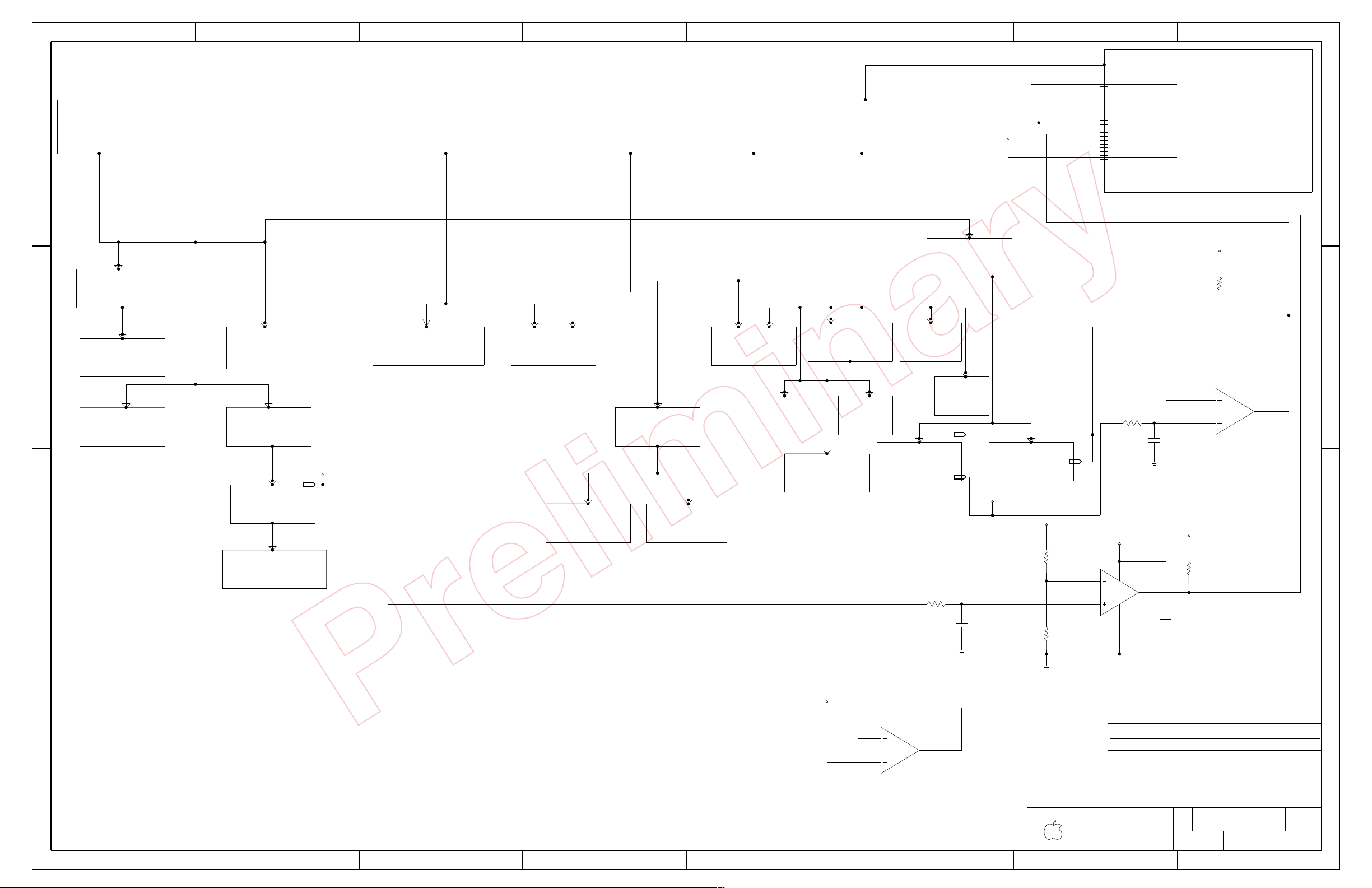

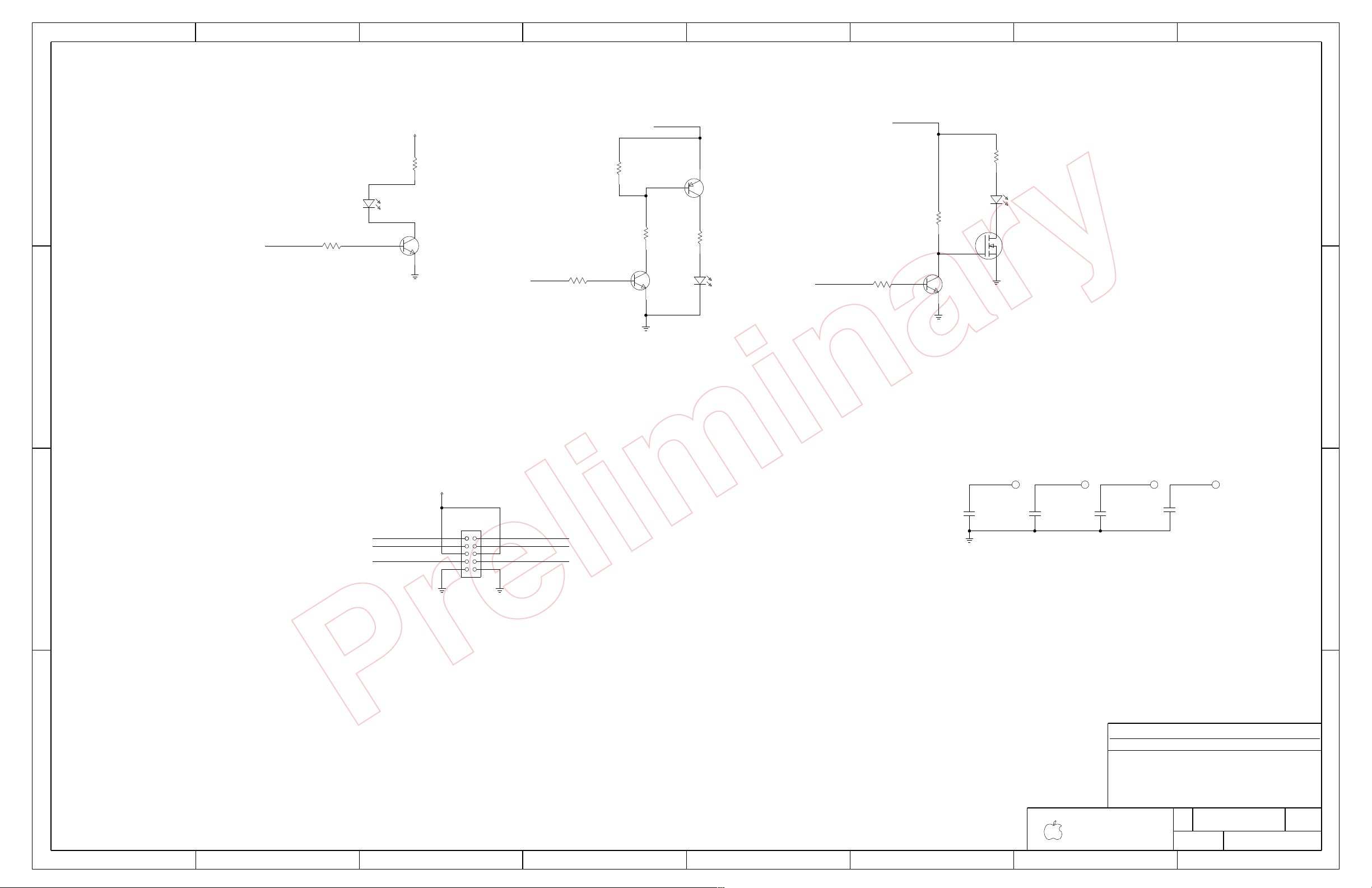

FET SWITCH

PP1V2_RUN

HT BUS

FET SWITCH

PP1V2_PWRON

SWITCHER

LINEAR

PP1V8_GPU

PAGE 13

SHASTA CORE

PAGE 85

FET SWITCH

PP1V2_ALL

PCI BUS

PP3V3_RUNPP3V3_ALL

SWITCHER

SYS_POWERUP_L

PAGE 13

CPU CORE

LINEAR

GPU CORE

FET SWITCH

PP5V_ALL

PP12V_RUN

POWER SW

PP1V8_RUN

PP12V_ALL

FW CONN

AUDIO CODEC

PP5V_RUN

PAGE 7

J700

SYS_POWERUP_L

USB CONN

PP5V_PWRON

VESTA CORE

SWITCHER

PP2V5_RUN

LINEAR

PP1V8_TPVDD

POWER CONNECTOR

FET SWITCH

PP2V5_PWRON

PP1V5_RUN

PP1V5_PWRON

PAGE 12

PAGE 12

PAGE 85 PAGE 11

PAGE 50

PAGE 11

PAGE 91

PAGE 15

PAGE 16

PAGE 85

PAGE 85

PAGE 13

PP1V5_VDDC_CT

PAGE 85

PP0V9_GPU_VTT

SWITCHER

20" PANEL POWER

EI

PULSAR

KODIAK CORE

17" LCD INVERTER

GPU MEMORY

OPTICAL

VESTA

MODEM & BT

SMU

POWER SEQUENCE PIN

PAGE 15

MAIN MEMORY

PP1V8_PWRON

PP3V3_PWRON

FET SWITCH

PAGE 16

PAGE 15

PP2V5_ALL

USB2 HOST

SWITCHER

PP1V2_TPVDD

LINEAR

PAGE 85

LINEAR

PP2V5_GPU_A2VDD

LINEAR

PP2V5_RUN_CPU_AVDD

PAGE 54

AUDIO CODEC

LINEAR

PP4V5_RUN_AUDIO

PAGE 154

FET SWITCH

LINEAR

LINEAR

0.01UF

402

CERM

16V

20%

2

1

C440

13 12 13 12

PP1V8_RUN

150K

5%

1/16W

MF-LF

402

2

1

R442

1%

1/16W

402

MF-LF

100K

2

1

R443

402

10K

MF-LF

1/16W

5%

2

1

R441

402

10K

MF-LF

1/16W

5%

2

1

R431

PP2V5_ALL

PP2V5_ALL

PP2V5_ALL

SOI-LF

3

14

9

8

12

U400

SOI-LF

3

1

7

6

12

U400

PP3V3_PWRON

PP1V2_PWRON

SOI-LF

3

2

5

4

12

U400

PP5V_ALL

PP2V5_ALL

10V

0.1UF

20%

CERM

402

2

1

C441

100K

5%

1/16W

MF-LF

402

21

R430

0.01UF

402

CERM

16V

20%

2

1

C430

100K

5%

1/16W

MF-LF

402

21

R440

Power Block Diagram

051-6863

07

154

4

SYNC_MASTER=FINO-PC

SYNC_DATE=05/19/2005

U400P2

SMU_PWRSEQ_P1_3

NC_SMU_PWRSEQ_P1_0

SMU_PWRSEQ_P1_0

SMU_PWRSEQ_P1_1

PS_1V_REF

COMPARE_PP1V2

PWR_GOOD_PP1V2

SMU_PWRSEQ_P9_6

SMU_PWRSEQ_P1_2

SMU_PWRSEQ_P9_5

TURN_ON_PP3V3_PWRON_L

PS_1V_REF

COMPARE_PP1V8

TURN_ON_PP1V2_L

PWR_GOOD_PP1V8

SMU_PWRSEQ_P1_4

NC_SMU_PWRSEQ_P1_4

16

28

6

28

28

4

28

28

28

15

4

28

6

www.Vinafix.vn

Preliminary

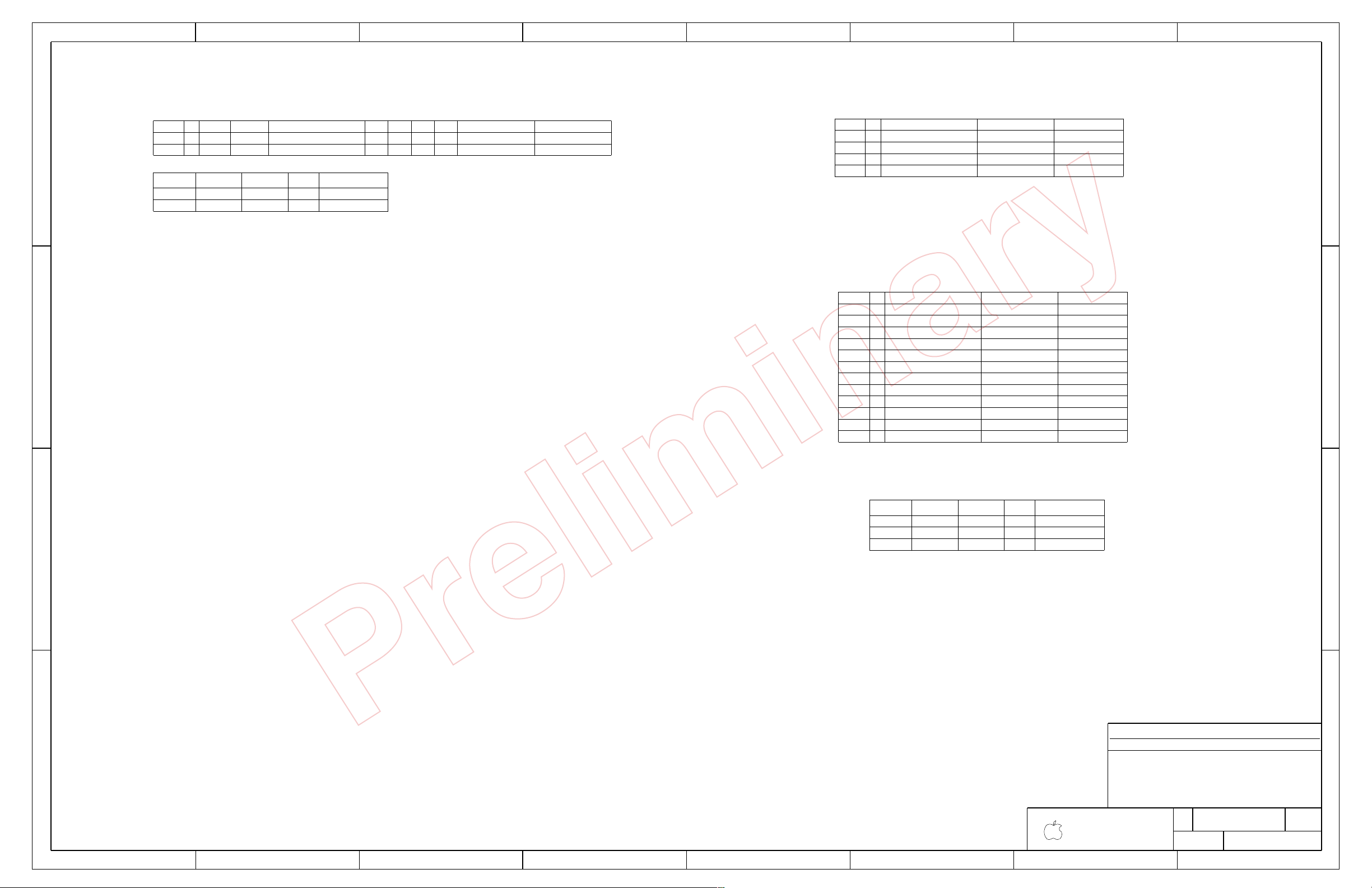

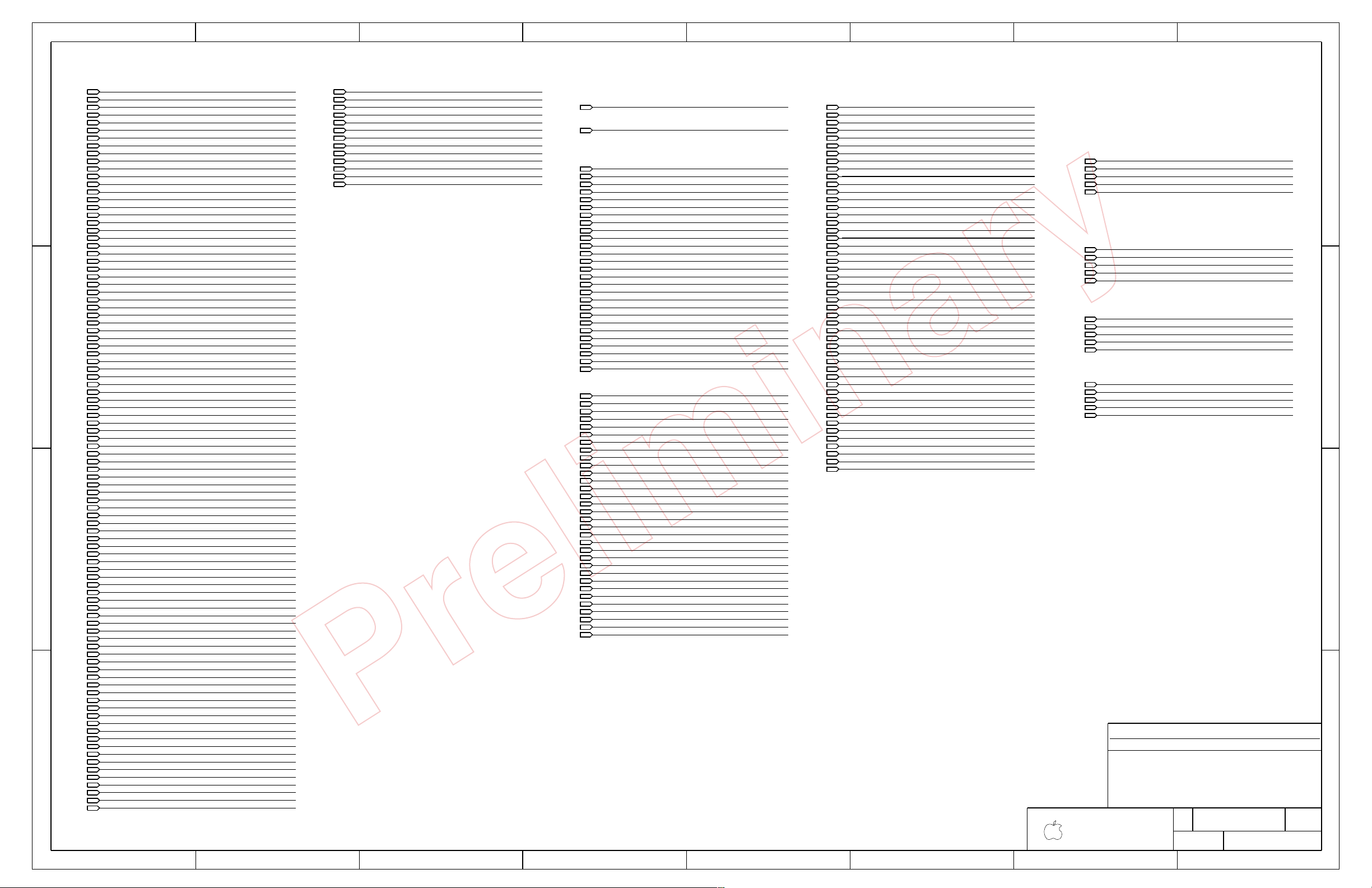

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_5_ITEM

TABLE_5_ITEM

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

TABLE_5_ITEM

TABLE_11_HEAD

TABLE_11_HEAD

TABLE_11_HEAD

REFERENCE DESIGNATOR(S)

BOM OPTION

QTY

DESCRIPTION

VALUE VOLT. WATT.

TOL.PART #

PACKAGE

DEVICE

TABLE_ALT_ITEM

TABLE_ALT_ITEM

MISC PARTS

ASICS

ALTERNATES

PROCESSORS

VOLTAGE

1.20V

1.20V

1

MECH1

17_INCH_LCD

M23 CPU HEATSINK

603-7318

1

341T1752

U2800

PURCH ASSY, SMU BIG

603-7322

M33 GPU HEATSINK

MECH2

20_INCH_LCD

1

1

875-1614

CPU GAP FILLER

GAP1

1

343S0319

IC,PULSAR2,100P,P8MM,BGA

U2500

LED700,LED702

378S0119

KINGBRIGHT LED

378S0114

Q5011,Q5021

MOSFET,N-CH,VISHAY

376S0207 376S0146

Q5010,Q5020

376S0204 376S0130

MOSFET,N-CH,VISHAY

1

U1900

IC,KODIAK,V1.1,PBGA,200MM

343S0371

343S0283

1

U2300

IC,ASIC,SHASTA,V1.1,PBGA

U1701

IC,ASIC,VESTA,V1.3

343S0324

1

341T1751

UC500

1

IC,FLASH,1MX8,3.3V,90NS

CPU_2_0GHZ

U4300

337S3165 337S3158

IC,DD3.1,2.0G,CJA

U4300

337S3164 337S3157 CPU_2_2GHZ

IC,DD3.1,2.0G,FJA

U4300

1

CPU_2_0GHZ2.0GHZ

CBGA-576-1MM

PROCESSOR

337S3158

1.15V

46W

50MV

IC,GPUL,DD3.1,2.0G,85C,CQA

U4300

CPU_2_2GHZ

1

CBGA-576-1MM

PROCESSOR

2.2GHZ337S3157

1.15V

51W

50MV

IC,GPUL,DD3.1,2.2G,85C,FQA

MECH1

1

20_INCH_LCD

M33 CPU HEATSINK

603-7321

SYNC_MASTER=FINO-DD

SYNC_DATE=05/19/2005

07

5

154

Table Items

051-6863

820-1783

1

MLB1

PCB,FAB,MLB,M23

17_INCH_LCD

051-6790

PCB,SCHEM,MLB,M23

SCH1

1

17_INCH_LCD

051-6863

PCB,SCHEM,MLB,M33

1

20_INCH_LCD

SCH1

1

PCB,FAB,MLB,M33

MLB1

20_INCH_LCD

820-1766

1

VPP1062-2082

SPEC,VENDOR PACKAGING PROCEDURE

825-6447

1

BARCODE LABEL, MLB

LBL1

www.Vinafix.vn

Preliminary

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

NO TEST XW NETS

EE IDENTIFIED NO TEST NETS

FUNC TEST NETS

NOTES FROM TOM FUSSELMAN

PLACE TWO TEST POINTS ON TOP SIDE

FOR PP3V3_ALL AND GND

PLACE WITHIN 1 INCH OF EACH OTHER

USE FAT TRACES

TOP SIDE ONLY

I1000

I1001

I1002

I1003

I1004

I1005

I1006

I1007

I1008

I1009

I1010

I1011

I1012

I1013

I1014

I1015

I1016

I1017

I1018

I1019

I1020

I1022

I1023

I1024

I1026

I1027

I1028

I1029

I1030

I1031

I1032

I1033

I1034

I1035

I1036

I1037

I1038

I1039

I1040

I1041

I1042

I1043 I1044

I1045

I1046

I1047

I1048

I1049

I1050

I1051

I1052

I1053

I1054

I1055

I1056

I1057

I1058

I1059

I1060

I1061

I1062

I1063

I1064

I1065

I1066

I1067

I1068

I1069

I1070

I1071

I1072

I1080

I1088

I1089

I1090

I1091

I1092

I1093

I1094

I1095

I1096

I1097

I1098

I1099

I1100

I1101

I1102

I1103

I1104

I1105

I1106

I1107

I1108

I1109

I1110

I1111

I1112

I1113

I1114

I1115

I1116

I1117

I1118

I1120

I1121

I1122

I1123

I1124

I1125

I1126

I1127

I1128

I1129

I1130

I1131

I1132

I1133

I1134

I1135

I1136

I1137

I1138

I1139

I1140

I1141

I1142

I1143

PP1V8_RUN PP3V3_RUN

PP1V5_PWRON

PP1V2_ALL

PP2V5_RUN

PP5V_ALL

PP3V3_ALL

PP12V_RUN

I1155

I1156

I1157

I1158

I1160

I1161

I1162

I1164

I1165

I1166

I1167

I1168

I1170

I1171

I1172

I1173

I1175

I1176

I1177

I1179

I1181

I1182

I1183

I1184

I1185

I1187

I1188

I1189

I1190

I1192

I1193

I1195

I1196

I1197

I1199

I1200

I1202

I1203

I1204

I1206

I1207

I1208

I1210

I1211

I1212

I1214

I1215

I1216

I1218

I1219

I1220

I1221

I1223

I1224

I1226

I1227

I1228

I1229

I1230

I1232

I1233

I1234

I1236

I1237

I1238

I1239

I1241

I1242

I1244

I1245

I1246

I1248

I1249

I1250

I1252

I1253

I1254

I1255

I1257

I1258

I1259

I1262

I1263

I1264

I1266

I1267

I1268

I1269

I1271

I1272

I1273

I1275

I1276

I1277

I1278

I1280

I1281

I1283

I1285

I1286

I1287

I1288

I1289

I1291

I1292

I1293

I1294

I1296

I1297

I1299

I1300

I1301

I1302

I1303

I1305

I1306

I1307

I1310

I1311

I1312

I1313

I1314

I1316

I1317

I1318

I1320

I1322

I1323

I1324

I1325

I1326

I1327

I1329

I1330

I1332

I1333

I1334

I1335

I1336

I1337

I1338

I1339

I1340

I1341

I1343

I1344

I1345

I1346

I1348

I1349

I1350

I307

I348

I349

I350

I356

I357

I358

I360

I361

I362

I375

I376

I428

I429

I826

I836

I837

I839

I841

I846

I847

I848

I849

I850

I851

I883

I947

I948

I949

I950

I951

I952

I953

I954

I955

I957

I958

I959

I960

I961

I962

I963

I964

I965

I969

I971

I972

I973

I974

I975

I976

I977

I978

I982

I984

I985

I986

I987

I988

I989

I990

I991

I992

I993

I994

I995

I996

I997

I998

I999

FUNC TEST 1 OF 2

051-6863

154

6

07

SYNC_MASTER=FINO-ME

SYNC_DATE=05/19/2005

FUNC_TEST=TRUE

PP1V8_RUN

PP3V3_RUN

FUNC_TEST=TRUE

PP1V5_PWRON

FUNC_TEST=TRUE

PP1V2_ALL

FUNC_TEST=TRUE

PP2V5_RUN

FUNC_TEST=TRUE

PP5V_ALL

FUNC_TEST=TRUE

PP3V3_ALL

FUNC_TEST=TRUE

FUNC_TEST=TRUE

PP12V_RUN

GND

FUNC_TEST=TRUE

NO_TEST=YES

TP_SB<25>

NC_SATA_TXD_P2

NO_TEST=YES

RFBD<3>

NO_TEST=YES

RAM_DQ_R<28>

NO_TEST=YES

NO_TEST=YES

RAM_DQ_R<44>

NO_TEST=YES

RAM_DQ_R<48>

RAM_DQ_R<5>

NO_TEST=YES

NO_TEST=YES

RAM_DQ_R<53>

NO_TEST=YES

RAM_DQ_R<52>

RFBD<113>

NO_TEST=YES

NO_TEST=YES

TP_SB<26>

RAM_DQ_R<3>

NO_TEST=YES

NO_TEST=YES

RAM_DQ_R<6>

RAM_DQ_R<7>

NO_TEST=YES

RAM_DQ_R<8>

NO_TEST=YES

RAM_DQ_R<10>

NO_TEST=YES

RFBD<62>

NO_TEST=YES

RFBD<66>

NO_TEST=YES

RFBD<96>

NO_TEST=YES

RFBD<106>

NO_TEST=YES

RFBD<109>

NO_TEST=YES

RFBD<110>

NO_TEST=YES

RFBD<112>

NO_TEST=YES

RFBD<116>

NO_TEST=YES

RFBD<121>

NO_TEST=YES

RFBD<125>

NO_TEST=YES

RFBD<126>

NO_TEST=YES

RFBD<97>

NO_TEST=YES

RFBD<100>

NO_TEST=YES

RFBD<101>

NO_TEST=YES

RFBD<105>

NO_TEST=YES

RFBD<104>

NO_TEST=YES

RFBD<98>

NO_TEST=YES

RFBD<108>

NO_TEST=YES

RFBD<122>

NO_TEST=YES

RFBD<102>

NO_TEST=YES

RFBD<118>

NO_TEST=YES

NO_TEST=YES

RFBD<117>

RFBD<120>

NO_TEST=YES

RFBD<114>

NO_TEST=YES

RFBD<85>

NO_TEST=YES

RFBD<86>

NO_TEST=YES

RFBD<87>

NO_TEST=YES

RFBD<88>

NO_TEST=YES

RFBD<90>

NO_TEST=YES

RFBD<91>

NO_TEST=YES

RFBD<92>

NO_TEST=YES

RFBD<95>

NO_TEST=YES

RFBD<67>

NO_TEST=YES

RFBD<74>

NO_TEST=YES

RFBD<75>

NO_TEST=YES

RFBD<76>

NO_TEST=YES

RFBD<79>

NO_TEST=YES

RFBD<83>

NO_TEST=YES

RFBD<82>

NO_TEST=YES

RFBD<71>

NO_TEST=YES

RFBD<72>

NO_TEST=YES

RFBD<70>

NO_TEST=YES

RFBD<69>

NO_TEST=YES

RFBD<94>

NO_TEST=YES

RFBD<81>

NO_TEST=YES

RFBD<78>

NO_TEST=YES

RFBD<65>

NO_TEST=YES

NO_TEST=YES

RAM_DQ_R<36>

NO_TEST=YES

RAM_DQ_R<29>

NO_TEST=YES

RAM_DQ_R<21>

NO_TEST=YES

RAM_DQ_R<14>

RAM_DQ_R<11>

NO_TEST=YES

FUNC_TEST=TRUE

SMU_MANUAL_RESET_L

FUNC_TEST=TRUE

SMU_BOOT_TXD

FUNC_TEST=TRUE

SMU_BOOT_BUSY

FUNC_TEST=TRUE

SMU_BOOT_CE

FUNC_TEST=TRUE

SMU_BOOT_CNVSS

SMU_BOOT_RXD

FUNC_TEST=TRUE

SMU_BOOT_SCLK

FUNC_TEST=TRUE

POWER_BUTTON_L

FUNC_TEST=TRUE

SYS_POWERUP_L

FUNC_TEST=TRUE

RESET_BUTTON_L

FUNC_TEST=TRUE

SMU_RESET_L

FUNC_TEST=TRUE

SYS_POWER_BUTTON_L

FUNC_TEST=TRUE

=PP5V_RUN_CPU

FUNC_TEST=TRUE

=PP3V3_ALL_SMU

FUNC_TEST=TRUE

FUNC_TEST=TRUE

PPVCORE_CPU

NO_TEST=YES

TP_NEC_SRCLK

TP_NEC_SRMOD

NO_TEST=YES

NO_TEST=YES

RAM_DQ_R<38>

RAM_DQ_R<39>

NO_TEST=YES

NO_TEST=YES

RAM_DQ_R<49>

NO_TEST=YES

TP_SB<24>

NO_TEST=YES

NC_CLK_RAI_GIGE_25MHZ

RFBD<5>

NO_TEST=YES

NO_TEST=YES

RAM_DQ_R<57>

NO_TEST=YES

RAM_DQ_R<40>

NO_TEST=YES

RAM_DQ_R<41>

NO_TEST=YES

RAM_DQ_R<43>

NO_TEST=YES

RAM_DQ_R<45>

NO_TEST=YES

RAM_DQ_R<34>

NO_TEST=YES

RAM_DQ_R<32>

NO_TEST=YES

RAM_DQ_R<30>

NO_TEST=YES

RAM_DQ_R<26>

NO_TEST=YES

RAM_DQ_R<25>

NO_TEST=YES

RAM_DQ_R<24>

NO_TEST=YES

RAM_DQ_R<22>

NO_TEST=YES

RAM_DQ_R<20>

NO_TEST=YES

RAM_DQ_R<17>

NO_TEST=YES

RAM_DQ_R<13>

NO_TEST=YES

RAM_DQ_R<12>

NO_TEST=YES

RAM_DQ_R<50>

NO_TEST=YES

RAM_DQ_R<54>

NO_TEST=YES

RAM_DQ_R<56>

NO_TEST=YES

RAM_DQ_R<58>

NO_TEST=YES

RAM_DQ_R<59>

NO_TEST=YES

RAM_DQ_R<60>

NO_TEST=YES

RAM_DQ_R<63>

RFBD<1>

NO_TEST=YES

RFBD<6>

NO_TEST=YES

RFBD<10>

NO_TEST=YES

RFBD<11>

NO_TEST=YES

RFBD<14>

NO_TEST=YES

RFBD<15>

NO_TEST=YES

RFBD<16>

NO_TEST=YES

NO_TEST=YES

RFBD<18>

RFBD<19>

NO_TEST=YES

RFBD<32>

NO_TEST=YES

RFBD<33>

NO_TEST=YES

RFBD<34>

NO_TEST=YES

RFBD<36>

NO_TEST=YES

RFBD<40>

NO_TEST=YES

RFBD<37>

NO_TEST=YES

RFBD<38>

NO_TEST=YES

RFBD<50>

NO_TEST=YES

RFBD<48>

NO_TEST=YES

RFBD<47>

NO_TEST=YES

RFBD<61>

NO_TEST=YES

RFBD<57>

NO_TEST=YES

RFBD<53>

NO_TEST=YES

GND_NEC_AVSS_R

NO_TEST=YES

GND_GPU_TPVSS

NO_TEST=YES

GND_U1100

NO_TEST=YES

GND_AUDIO_SPKRAMP_PLANE

NO_TEST=YES

KPGND2_FMAX

NO_TEST=YES

NO_TEST=YES

TDIODE_POS_FMAX

NO_TEST=YES

INA138_OUT

NO_TEST=YES

RAMCLK_AVSS

NO_TEST=YES

GND_AUDIO

NO_TEST=YES

GND_AUDIO_SPKRAMP

NO_TEST=YES

KOD_K07_GND

NO_TEST=YES

KOD_G10_GND

NO_TEST=YES

KOD_J13_GND

NO_TEST=YES

KOD_L13_GND

NO_TEST=YES

KOD_H08_GND

NO_TEST=YES

PCIE_SLOTA_PRSNT_L

NO_TEST=YES

U8500_GND

GND_GPU_TXVSSR

NO_TEST=YES

NO_TEST=YES

GND_GPU_VSSDI

NO_TEST=YES

GND_GPU_AVSSN

GND_GPU_AVSSQ

NO_TEST=YES

GND_GPU_A2VSSN

NO_TEST=YES

GND_GPU_A2VSSQ

NO_TEST=YES

KOD_L15_GND

NO_TEST=YES

NO_TEST=YES

PP_3V3SBPCI_B9

PP_VIOPCIUSB2_C2

NO_TEST=YES

PP_1V2PWRONDISKSB_CC

NO_TEST=YES

NO_TEST=YES

PP2V5_VESTA_BIASVDD1

NO_TEST=YES

PP2V5_VESTA_XTALVDD1

NO_TEST=YES

PP1V2_VESTA_PLLVDD2

NO_TEST=YES

PP1V2_VESTA_PLLVDD1

NO_TEST=YES

PP2V5_VESTA_BIASVDD2

NO_TEST=YES

PP2V5_VESTA_XTALVDD2

NO_TEST=YES

PP1V2_VESTA_FAVDDL

NO_TEST=YES

PP2V5_VESTA_FAVDDM

NO_TEST=YES

PP3V3_VESTA_FAVDDH

NO_TEST=YES

PP3V3_PWRON_NEC_AVDD

NO_TEST=YES

KPVDD2

NO_TEST=YES

KPGND2

NO_TEST=YES

CPU_DIODE_POS

FMAXT_P

NO_TEST=YES

CPU_DIODE_NEG

NO_TEST=YES

NO_TEST=YES

FMAXT_M

CORE_ISNS_P

NO_TEST=YES

CORE_ISNS_M

NO_TEST=YES

NO_TEST=YES

PPV_RUN_CPU_AVDD_R_L

NO_TEST=YES

NC_CLK_RAI_REFCLK_66M

NO_TEST=YES

NC_CPU_B_TBEN_CLK_US

NO_TEST=YES

NC_PMR_CLK_DIS_L

NC_SATA_RXD_N2_C

NO_TEST=YES

NC_SATA_TXD_N2

NO_TEST=YES

NO_TEST=YES

TP_SB<28>

NO_TEST=YES

TP_SB<29>

NO_TEST=YES

TP_SB<27>

GND_U1200

NO_TEST=YES

PP_2V5PWRONNBMISC

NO_TEST=YES

PP_1V2PWRONPULSAR1

NO_TEST=YES

PP_1V5PULSAR2

NO_TEST=YES

PP_1V5PWRONPULSAR2

NO_TEST=YES

NO_TEST=YES

PP_VEINB

PP_3V3ALLSMU

NO_TEST=YES

PP_3V3ALLSMUAVCC

NO_TEST=YES

GND_SMU_AVSS

NO_TEST=YES

NO_TEST=YES

GND_CPU_AVDD

VC_AGND

NO_TEST=YES

GND_GPU_PVSS

NO_TEST=YES

KPVDD2_FMAX

NO_TEST=YES

VC_OUTSEN_R

NO_TEST=YES

GND_GPU_MPVSS

NO_TEST=YES

NO_TEST=YES

GND_AUDIO_MIC

NO_TEST=YES

NC_EI_NB_TO_CPU_B_CLK_P

NO_TEST=YES

NC_EI_NB_TO_CPU_B_CLK_N

NC_EI_NB_TO_CPU_B_AD<0..43>

NO_TEST=YES

NO_TEST=YES

NC_EI_NB_TO_CPU_B_SR_P<0..1>

NO_TEST=YES

NC_EI_NB_TO_CPU_B_SR_N<0..1>

NO_TEST=YES

NC_EI_CPU_B_TO_NB_CLK_P

NO_TEST=YES

NC_EI_CPU_B_TO_NB_CLK_N

NO_TEST=YES

NC_EI_CPU_B_TO_NB_AD<0..43>

NO_TEST=YES

NC_EI_CPU_B_TO_NB_SR_P<0..1>

NC_NB_CPU_B0_INT_L

NO_TEST=YES

NC_CPU_B1_QACK_L

NO_TEST=YES

NC_HT_MB_TO_NB_CAD_P<8..15>

NO_TEST=YES

NO_TEST=YES

NC_HT_MB_TO_NB_CAD_N<8..15>

NC_HT_NB_TO_MB_CAD_P<8..15>

NO_TEST=YES

NO_TEST=YES

NC_HT_NB_TO_MB_CAD_N<8..15>

NC_CLK_RAI_200M_N<0>

NO_TEST=YES

NC_CLK_RAI_200M_P<0>

NO_TEST=YES

NC_CLK_RAI_PCIEA_N<0>

NO_TEST=YES

NO_TEST=YES

NC_CLK_RAI_PCIEA_P<0>

NC_CLK_RAI_PCIEB_N<0>

NO_TEST=YES

NC_CLK_RAI_PCIEC_N<0>

NO_TEST=YES

NC_CLK_RAI_PCIEB_P<0>

NO_TEST=YES

NC_CLK_RAI_PCIEC_P<0>

NO_TEST=YES

NO_TEST=YES

NC_A_AVREG_1

NO_TEST=YES

NC_A_AVREG_0

NO_TEST=YES

NC_A_AVREG_2

NO_TEST=YES

NC_CPU_B_APSYNC

NO_TEST=YES

NC_EI_CPU_B_SYSCLK_N

NC_HT_NB_TO_MB_CLK_N<1>

NO_TEST=YES

NO_TEST=YES

NC_EI_CPU_B_SYSCLK_P

NC_HT_NB_TO_MB_CLK_P<1>

NO_TEST=YES

NO_TEST=YES

NC_J2904_11

NO_TEST=YES

NC_J2904_12

NO_TEST=YES

NC_NCV1009_1

NO_TEST=YES

NC_NCV1009_3

NO_TEST=YES

NC_NCV1009_5

NO_TEST=YES

NC_NCV1009_ADJ

NO_TEST=YES

NC_NCV1009_4

NO_TEST=YES

NC_RAM_ARB0_REF25MHZ

NO_TEST=YES

NC_RAM_ARB1_REF25MHZ

NO_TEST=YES

NC_SMU_PWRSEQ_P1_0

NO_TEST=YES

NC_SMU_PWRSEQ_P1_4

NO_TEST=YES

TP_SB<21>

NO_TEST=YES

TP_SB<19>

NO_TEST=YES

TP_SB<18>

NO_TEST=YES

TP_SB<15>

NO_TEST=YES

TP_SB<14>

NO_TEST=YES

TP_SB<12>

NO_TEST=YES

TP_SB<13>

NO_TEST=YES

TP_SB<10>

NO_TEST=YES

TP_SB<9>

NO_TEST=YES

TP_SB<7>

NO_TEST=YES

TP_SB<8>

NO_TEST=YES

TP_SB<6>

NO_TEST=YES

TP_SB<4>

NO_TEST=YES

TP_SB<5>

NO_TEST=YES

TP_SB<2>

NO_TEST=YES

TP_SB<3>

NO_TEST=YES

TP_SB<1>

NO_TEST=YES

TP_SB<0>

RFBD<28>

NO_TEST=YES

RFBD<27>

NO_TEST=YES

RFBD<26>

NO_TEST=YES

RFBD<25>

NO_TEST=YES

RFBD<21>

NO_TEST=YES

RFBD<22>

NO_TEST=YES

RFBD<23>

NO_TEST=YES

RFBD<60>

NO_TEST=YES

RFBD<59>

NO_TEST=YES

RFBD<56>

NO_TEST=YES

RFBD<54>

NO_TEST=YES

RFBD<52>

NO_TEST=YES

RFBD<45>

NO_TEST=YES

RFBD<44>

NO_TEST=YES

RFBD<42>

NO_TEST=YES

RFBD<41>

NO_TEST=YES

NO_TEST=YES

AUD_4V5_FB

NO_TEST=YES

TP_FBBCS1_L

ITS_RUNNING

NO_TEST=YES

NO_TEST=YES

Q800_D

NO_TEST=YES

Q800_G

Q802_B

NO_TEST=YES

NO_TEST=YES

Q801_B

Q802_E

NO_TEST=YES

Q803_B

NO_TEST=YES

NO_TEST=YES

TP_USB2_PWREN<0>

NO_TEST=YES

TP_SB_FSTEST

NO_TEST=YES

TP_USB2_PWREN<1>

TP_SB_PLLTEST

NO_TEST=YES

TP_USB2_PWREN<2>

NO_TEST=YES

NO_TEST=YES

TP_USB2_PWREN<3>

TP_NEC_NTEST1

NO_TEST=YES

NO_TEST=YES

TP_USB2_PWREN<4>

TP_NEC_SMC

NO_TEST=YES

TP_NEC_SMI_L

NO_TEST=YES

TP_NEC_TEST

NO_TEST=YES

NO_TEST=YES

UATA_DASP_L_DS

RFBD<30>

NO_TEST=YES

NO_TEST=YES

TP_SB<16>

NO_TEST=YES

TP_SB<22>

NO_TEST=YES

TP_SB<23>

NO_TEST=YES

TP_SB<20>

NO_TEST=YES

TP_SB<17>

NO_TEST=YES

NC_SATA_RXD_P2_C

NO_TEST=YES

NC_NCV1009_2

RFBD<31>

NO_TEST=YES

RFBD<49>

NO_TEST=YES

NO_TEST=YES

TP_SB<11>

NC_I2S2_MCLK

NO_TEST=YES

NO_TEST=YES

RAM_DQ_R<16>

NO_TEST=YES

RAM_DQ_R<19>

NO_TEST=YES

RAM_DQ_R<33>

RFBD<7>

NO_TEST=YES

RFBD<8>

NO_TEST=YES

LED802_1

NO_TEST=YES

PCI_CLK66M_SB_INT_R

NO_TEST=YES

NO_TEST=YES

LED801_1

RFBD<13>

NO_TEST=YES

RFBD<2>

NO_TEST=YES

PP_OVDD_PULSAR1

NO_TEST=YES

PP_2V5PWRONSB

NO_TEST=YES

GND_AUD_LOAMP

NO_TEST=YES

NO_TEST=YES

GND_AUDIO_CODEC

NO_TEST=YES

GND_AUD_LOAMP_CHGPMP

RFBD<124>

NO_TEST=YES

NO_TEST=YES

RAM_DQ_R<2>

NO_TEST=YES

RAM_DQ_R<46>

RAM_DQ_R<1>

NO_TEST=YES

NC_NB_CPU_A1_INT_L

NO_TEST=YES

NO_TEST=YES

NC_EI_CPU_B_TO_NB_SR_N<0..1>

NC_CPU_B0_QACK_L

NO_TEST=YES

NC_CPU_A1_QACK_L

NO_TEST=YES

NC_NB_CPU_B1_INT_L

NO_TEST=YES

NO_TEST=YES

PP_3V3PWRONSBPCI64

NO_TEST=YES

GND_U1300

PP_1V2PWRONSBVCORE

NO_TEST=YES

PP_1V2PWRONSBPLL45VDD

NO_TEST=YES

PP_2V5PWRONSB_B9

NO_TEST=YES

PP12V_AUDIO_SPKRAMP

NO_TEST=YES

NO_TEST=YES

TDIODE_NEG_FMAX

NO_TEST=YES

DAGND

NO_TEST=YES

KOD_H05_GND

85 50

154

69

70

70

69

70

70

69

69

69

69

69

70

69

69

69

69

28

29

70

70

70

70

70

70

70

70

70

70

69

69

69

69

69

69

69

69

69

70

70

70

70

70

70

70

154

55

55

69

69

70

150

69

70

69

89

68

68

68

68

68

68

90

68

68

68

68

68

89

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

90

68

68

68

68

68

29

29

29

29

29

29

12

29

29

8

28

68

68

68

89

68

68

68

68

68

68

68

68

68

68

68

68

68

68

68

68

68

68

68

68

68

68

68

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

154

154

152

97

97

97

97

97

84

101

50

50

55

55

55

154

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

89

68

68

68

89

89

89

89

154

148

154

90

68

68

68

152

97

7

7

7

7

7

7

7

7

142

129

88

61

61

61

61

61

61

88

142

61

61

61

61

61

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

61

61

61

61

61

29

28

28

28

28

28

28

29

7

29

28

28

7

7

50

122

122

61

61

61

142

27

88

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

142

93 11

152

55

55

55

62

7

7

82

82

82

82

82

82

85

93

93

93

93

93

93

98

119

122

127

132

132

139

132

139

139

139

139

139

142

48

48

48

55

48

55

55

55

48

27

26

20

129

129

142

142

142

12

20

25

25

25

41

28

28

28

48

50

86

55

50

87

153

56

56

56

56

56

56

56

56

56

56

56

101

101

101

101

27

27

27

27

27

27

27

27

82

82

82

27

27

101

27

101

29

29

55

55

55

55

55

27

27

4

4

142

142

142

142

142

142

142

142

142

142

142

142

142

142

142

142

142

142

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

88

154

87

7

8

8

8

8

8

8

143

24

143

24

143

143

122

143

122

122

122

129

88

142

142

142

142

142

129

55

88

88

142

154

61

61

61

88

88

8

26

8

88

88

25

23

150

147

150

88

61

61

61

56

56

56

56

56

23

13

23

24

119

7

55

55

82

www.Vinafix.vn

Preliminary

125

OUT

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

P/N 518-0188

ON IN RUN AND SLEEP

PWRON RAILS

CHASSIS MOUNTING

GPU MOUNTING

ALL RAILS

RUN RAILS

SILKSCREEN:1 SILKSCREEN:2

SILKSCREEN:RUN

GND RAILS

ONLY ON IN RUN

ALWAYS ON WHEN UNIT HAS AC POWER (TRICKLE)

CHASSIS GND

PP5V_RUN

PP3V3_PWRON

PP1V5_PWRON

PP2V5_PWRON

PP1V2_PWRON

PP5V_ALL

PP5V_ALL

PP3V3_RUN

PP2V5_RUN

PP5V_PWRON

PP1V5_RUN

PP3V3_RUN

PP5V_RUN

SM

21

XW701

SM

21

XW702

SM

21

XW703

PP12V_RUN

PP1V2_RUN

CRITICAL

74LCX125

TSSOP

3

14

17

2

U700

CERM

0.1UF

10V

20%

402

2

1

C700

GREEN

2.0X1.25A

DEVELOPMENT

2

1

LED701

GREEN

2.0X1.25A

2

1

LED702

PP3V3_PWRON

330

1/10W

603

MF-LF

5%

21

R700

2.0X1.25A

GREEN

2

1

LED700

SM

21

XW705

SM

21

XW706

SM

21

XW707

PP12V_RUN

PP3V3_RUN

M-RT-TH

HM9607E-P2

9

87

65

43

2

1413

1211

10

1

J700

PP3V3_ALL PP12V_ALL

PP1V8_PWRON

OMIT

4P75R4

1

ZH700

OMIT

4P75R4

1

ZH701

OMIT

4P75R4

1

ZH702

OMIT

4P75R4

1

ZH703

0.01UF

20%

CERM

402

NOSTUFF

16V

2

1

C704

0.01UF

NOSTUFF

20%

16V

CERM

402

2

1

C702

NOSTUFF

16V

20%

CERM

402

0.01UF

2

1

C703

PP1V8_RUN

OMIT

4P25R3P5

ZH704

OMIT

4P25R3P5

ZH705

16V

NOSTUFF

0.01UF

20%

CERM

402

2

1

C707

0.01UF

20%

16V

CERM

402

NOSTUFF

2

1

C706

0.01UF

CERM

NOSTUFF

20%

16V

402

2

1

C705

MF-LF

402

1/16W

5%

10K

2

1

R702

PP3V3_ALL

PP3V3_ALL

PP1V2_ALL

PP2V5_ALL

PP12V_ALL

PP3V3_ALL

330

1/10W

5%

MF-LF

603

21

R710

MF-LF

NOSTUFF

0

5%

1/16W

402

21

R721

MF-LF

1/16W

5%

0

402

NOSTUFF

21

R711

SM

21

XW700

4P25R3P5

OMIT

1

ZH706

SM

21

XW708

SM-1

ELEC

6.3V

20%

330UF

2

1

C722

603

MF-LF

5%

330

1/10W

DEVELOPMENT

21

R701

PP5V_ALL

SYNC_MASTER=M33-PC

07

7

154

051-6863

POWER CONN / ALIAS

SYNC_DATE=05/19/2005

=PP5V_PWRON_BNDI

=PP5V_PWRON_USB

=PP3V3_ENET

=PP3V3_PWRON_BNDI

=PP3V3_PWRON_BT

=PP3V3_PWRON_CPU

=PP3V3_PWRON_PULSAR

=PP3V3_PWRON_SB

=PP3V3_PWRON_SB_PCI32

=PP3V3_PWRON_SB_PCI64

=PP3V3_PWRON_SMU

=PP3V3_PWRON_USB

MIN_NECK_WIDTH=0.20MM

MIN_LINE_WIDTH=0.60MM

VOLTAGE=0V

GND_CHASSIS_TMDS

=PP2V5_PWRON_NB_MISC

=PP2V5_PWRON_HT

=PP2V5_PWRON_NB_PCIE

=PP1V8_RUN_RAM

PP12V_AUDIO_SPKRAMP

=PP5V_RUN_CPU

ZH706P1

=PP5V_PATA

=PP3V3_AUDIO

=PP3V3_RUN_I2C

=PP3V3_RUN_PULSAR

=PP3V3_RUN_SMU

=PP3V3_SB_PCI

=PPVIO_PCI_USB2

=PP1V2_PWRON_HT_NBTX

=PP1V2_PWRON_PULSAR

=PP1V2_PWRON_SB_HT

=PP1V2_PWRON_SB_VCORE

INV_CUR_HI

GND_CHASSIS_FIREWIRE

GND_CHASSIS_RJ45

GND_CHASSIS_VGA

ZH700P1

GND_CHASSIS_USB

=PPOVDD_PULSAR

GND_CHASSIS_AUDIO_EXTERNAL

GND_AUDIO_SPKRAMP

=PPV_EI_CPU

=PPV_EI_NB

=PP1V5_PWRON_PULSAR

=PP1V8_PWRON_DIMM

=PP12V_GPU

=PP1V8_PWRON_NBMEM

=PP1V8_PWRON_RAM

=PPVCORE_PWRON_NB_HT

=PPVCORE_PWRON_NB

=PPVCORE_PWRON_NB_PCIE

=PP3V3_ALL_GPU

=PP2V5_ENETFW

=PP3V3_ENETFW

=PP2V5_RUN_I2C

=PPV_GPU_MEM

ZH703P1

=PP2V5_ENET

SYS_POWERUP_L

ITS_PLUGGED_IN

ITS_RUNNING

=PP2V5_PWRON_SB

GND_AUDIO

LCD_PWM

=PP1V2_GPU_PCIE

SYS_POWERFAIL_L

=PP2V5_PWRON_PULSAR

=PP1V2_ENETFW

=PP3V3_ALL_SMU

=PP3V3_FW

=PP12V_ALL_GPU

=PP5V_ALL_GPU

=PP3V3_ALL_CPU

ZH702P1

=PP12V_ALL_FW

=PP12V_CPU

HS_SDF801

ZH704P1

ZH705P1

=PP3V3_RUN_SB_PCI

=PP2V5_PWRON_NB_HT

PP5V_AUDIO_ANALOG

=PP3V3_RUN_CPU

=PP3V3_GPU

=PP3V3_PCI

=PP3V3_PATA

=PP1V8_PWRON_RAM_I2C_VDD

=PP5V_AUDIO

=PP5V_GPU

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

VOLTAGE=0

GND_CHASSIS_LEFT

NET_SPACING_TYPE=POWER

MIN_NECK_WIDTH=0.2MM

GND_CHASSIS_BNDI

MIN_LINE_WIDTH=0.6MM

VOLTAGE=0

MAKE_BASE=TRUE

NET_SPACING_TYPE=POWER

=PP1V2_PWRON_SB

=PP1V2_PWRON_DISK_SB

VOLTAGE=0

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

GND_CHASSIS_RIGHT

MIN_NECK_WIDTH=0.2MM

NET_SPACING_TYPE=POWER

ITS_ALIVE

SYS_POWERUP_L_BUF

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.6MM

VOLTAGE=5V

NET_SPACING_TYPE=POWER

NET_SPACING_TYPE=POWER

VOLTAGE=3.3V

NET_SPACING_TYPE=POWER

VOLTAGE=12V

NET_SPACING_TYPE=POWER

MAKE_BASE=TRUE

VOLTAGE=1.2V

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.6MM

NET_SPACING_TYPE=POWER

NET_SPACING_TYPE=POWER

NET_SPACING_TYPE=POWER

VOLTAGE=3.3V

NET_SPACING_TYPE=POWER

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2MM

NET_SPACING_TYPE=POWER

MAKE_BASE=TRUE

PP5V_ALL

MAKE_BASE=TRUE

VOLTAGE=12V

PP12V_ALL

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2MM

NET_SPACING_TYPE=POWER

VOLTAGE=2.5V

PP2V5_ALL

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

NET_SPACING_TYPE=POWER

NET_SPACING_TYPE=POWER

MIN_NECK_WIDTH=0.2MM

PP1V2_ALL

VOLTAGE=1.2V

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2MM

VOLTAGE=3.3V

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

PP3V3_ALL

PP1V8_RUN

MIN_NECK_WIDTH=0.2MM

VOLTAGE=1.8V

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6MM

NET_SPACING_TYPE=POWER

MIN_NECK_WIDTH=0.2MM

VOLTAGE=2.5V

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

PP1V8_PWRON

NET_SPACING_TYPE=POWER

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.6MM

PP3V3_RUN

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

MAKE_BASE=TRUE

PP12V_RUN

PP1V2_RUN

PP1V5_RUN

MIN_NECK_WIDTH=0.2MM

MAKE_BASE=TRUE

VOLTAGE=1.5V

MIN_LINE_WIDTH=0.6MM

NET_SPACING_TYPE=POWER

VOLTAGE=5V

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.25MM

MAKE_BASE=TRUE

PP5V_PWRON

VOLTAGE=2.5V

PP2V5_RUN

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

MAKE_BASE=TRUE

NET_SPACING_TYPE=POWER

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

VOLTAGE=1.2V

PP1V2_PWRON

VOLTAGE=2.5V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.6MM

PP2V5_PWRON

NET_SPACING_TYPE=POWER

PP1V5_PWRON

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

VOLTAGE=1.5V

MAKE_BASE=TRUE

NET_SPACING_TYPE=POWER

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.25MM

PP3V3_PWRON

VOLTAGE=5V

PP5V_RUN

NET_SPACING_TYPE=POWER

MIN_NECK_WIDTH=0.20MM

MIN_LINE_WIDTH=0.60MM

VOLTAGE=0V

119

56

85

96

56

39

154

48

59

91

50

138

93

24

43

145

30

153

28

154

47

56

70

58

59

139

139

90

28

119

139

29

154

92

136

23

30

144

28

103

152

8

152

20

154

152

30

42

25

69

39

42

132

132

89

12

24

154

132

28

55

153

55

91

125

92

16

143

143

132

121

55

25

20

23

23

28

142

96

20

98

82

61

6

6

129

147

39

25

30

119

122

98

25

103

23

92

140

136

96

143

25

153

6

29

41

12

67

96

20

62

98

19

82

85

17

17

39

87

136

6

6

23

6

92

84

28

25

17

6

140

85

85

55

140

50

8

24

98

150

54

85

121

129

67

91

143

24

127

16

6

6

6

6

6

6

6

6

www.Vinafix.vn

Preliminary

G

D

S

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

CPU HEATSINK MOUNTING HOLES

DIAG LED

(OVERTEMP LED)

SCC_GPIO_L

SCC_TRXC

SCC_TXD_L

SCC_RTS_L

SCC_DTR_L

SCC_RXD

SERIAL DEBUG

CHKSTOP LED

PLL LOCK LED

OMIT

4P75R4

1

ZH800

OMIT

4P75R4

1

ZH801

OMIT

4P75R4

1

ZH803

OMIT

4P75R4

1

ZH802

402

0.01UF

20%

16V

CERM

2

1

C880

402

0.01UF

20%

16V

CERM

2

1

C881

402

0.01UF

20%

CERM

16V

2

1

C882

402

0.01UF

20%

16V

CERM

2

1

C883

RED

SM

DEVELOPMENT

2

1

LED801

2N7002

SOT23-LF

DEVELOPMENT

Q800_D

2

1

3

Q800

2N3904LF

SOT23

DEVELOPMENT

Q801_B

2

3

1

Q801

SM

DEVELOPMENT

2N3906

2

3

1

Q802

1K

MF-LF

1/16W

DEVELOPMENT

402

5%

2

1

R835

GREEN

2.0X1.25A

DEVELOPMENT

2

1

LED802

180

MF-LF

402

5%

DEVELOPMENT

1/16W

2

1

R837

1/16W

MF-LF

DEVELOPMENT

1K

402

5%

2

1

R838

2N3904LF

SOT23

DEVELOPMENT

2

3

1

Q803

180

1/16W

MF-LF

402

5%

DEVELOPMENT

21

R839

SM

RED

2

1

LED850

SOT23

2N3904LF

2

3

1

Q850

5%

402

1/16W

1K

MF-LF

21

R851

PP5V_ALL

402

5%

1/16W

MF-LF

1K

2

1

R850

M-ST-5087

SM

DEVELOPMENT

9

8

7

65

4

3

2

10

1

J800

PP5V_PWRON

MF-LF

1/16W

5%

180

DEVELOPMENT

402

2

1

R833

5%

1/16W

MF-LF

DEVELOPMENT

1K

402

2

1

R834

402

MF-LF

5%

30K

1/16W

21

R836

SYNC_DATE=05/19/2005

SYNC_MASTER=FINO-DD

Signal Alias

07

8

154

051-6863

=PP5V_RUN_CPU

=PP5V_RUN_CPU

CPU_CHKSTOP_L

Q800_G

Q802_B

LED801_1

LED802_1

Q803_C

I2S1_RESET_L

I2S1_MCLK

I2S1_DEV_TO_SB_DTI

I2S1_SYNC

I2S1_BITCLK

I2S1_SB_TO_DEV_DTO

HS_SDF800

DIAG_LED

MAKE_BASE=TRUE

DIAG_LED_R

Q803_B

PLLLOCK

Q802_E

LED850P2

HS_SDF801 HS_SDF802 HS_SDF803

LED850P1

8 8 7

7

56

43

6

6

6

6

43

6

6

6

6

9

24

24

24 24

24

24

28

6

9

6

www.Vinafix.vn

Preliminary

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

ADDING FUNC_TEST=TRUE TO THESE NETS

OF THE BOARD

LAYOUT HAVING DIFFICULTY PLACING TEST POINTS ON THESE NETS

PCB LAYOUT ADDS TEST POINTS. THIS LIST IS A RESULT OF PCB

NOTE FOR SHARING: DO NOT INCLUDE THIS LIST UNTIL

WHEN THE DEVELOPMENT BOM OPTION IS ENABLED

THE FOLLOWING NETS DO NOT HAVE

AND SIGNAL INTEGRITY.

TEST COVERAGE WILL BE BY FCT

TEST POINT BECAUSE OF ROUTING DENSITY

THE FOLLOWING NETS ARE USED ONLY

TESTED VIA TEST JET

THE FOLLOWING PULSAR NETS WILL BE

JTAG TEST POINTS NEED TO BE ON THE BOTTOM

I1

I10

I100

I101

I102

I103

I106

I109

I11

I114

I115

I116

I117

I118

I119

I12

I120

I121

I122

I123

I124

I125

I126

I127

I128

I129

I13

I130

I131

I132

I133

I134

I135

I136

I137

I138

I139

I14

I140

I141

I142

I143

I144

I145

I146

I147

I148

I149

I15

I150

I151

I152

I153

I154

I155

I156

I157

I158

I159

I16

I160

I161

I162

I163

I164

I165

I166

I167

I168

I169

I17

I170

I171

I172

I173

I174

I175

I176

I177

I178

I179

I18

I180

I181

I182

I183

I184

I185

I186

I187

I188

I189

I19

I191

I192

I193

I194

I195

I196

I197

I198

I199

I2

I20

I200

I201

I202

I203

I204

I205

I206

I207

I208

I209

I21

I210

I211

I212

I213

I214

I215

I216

I217

I218

I219

I22

I220

I221

I222

I223

I224

I225

I226

I227

I228

I229

I23

I230

I232

I233

I234

I235

I236

I238

I239

I24

I240

I241

I242

I244

I245

I246

I247

I248

I25

I26

I27

I28

I29

I3

I30

I31

I32

I33

I34

I35

I36

I37

I38

I39

I4

I40

I41

I42

I43

I44

I45

I46

I47

I48

I49

I5

I50

I51

I52

I53

I54

I55

I56

I57

I58

I59

I6

I60

I61

I62

I63

I64

I65

I66

I67

I68

I69

I7

I70

I71

I72

I73

I74

I75

I76

I77

I78

I79

I8

I80

I81

I82

I83

I84

I85

I86

I87

I88

I89

I9

I90

I91

I92

I93

I94

I95

I96

I97

I98

I99

154

9

051-6863

SYNC_DATE=05/19/2005

SYNC_MASTER=FINO-ME

07

FUNC TEST 2 OF 2

FUNC_TEST=TRUE

TP_JTAG_VESTA_TDO

FUNC_TEST=TRUE

TP_JTAG_VESTA_TDI

FUNC_TEST=TRUE

TP_JTAG_VESTA_TCK

FUNC_TEST=TRUE

JTAG_NB_TMS

FUNC_TEST=TRUE

JTAG_NB_TCK

FUNC_TEST=TRUE

TP_JTAG_SB_TCK

FUNC_TEST=TRUE

JTAG_SB_TRST_L

NO_TEST=YES

PCIE_SLOTA_TO_NB_P<0..15>

NO_TEST=YES

NB_PLL_OUT_TRG_R

NO_TEST=YES

PP5V_T555

NO_TEST=YES

ENET_TX_EN

ENET_RXD<0>

NO_TEST=YES

ENET_RXD<2>

NO_TEST=YES

ENET_RXD_R<4>

NO_TEST=YES

100M_P<0>

NO_TEST=YES

NO_TEST=YES

CLK_RAIREF_200M_P_R

NO_TEST=YES

PP1V5_RUN_FOR_LED

NO_TEST=YES

LED_PP1V5_RUN_N

ENET_RXD_R<3>

NO_TEST=YES

NO_TEST=YES

ENET_RXD_R<2>

TP_VESTA_TXC_RXC_DELAY

NO_TEST=YES

NO_TEST=YES

PULSAR_1V5_RUN_SWITCH

TP_VESTA_TVCO_24

NO_TEST=YES

NO_TEST=YES

SB_AIRPRT_CLK_33MHZ_R

SB_CLK25M_SATA_R

NO_TEST=YES

NO_TEST=YES

QUA0_REF_25MHZ_R

NO_TEST=YES

LED_PP1V2_RUN_N

ENET_RXD<3>

NO_TEST=YES

ENET_RXD<4>

NO_TEST=YES

NO_TEST=YES

TSENSE_GPU_ADD0

NO_TEST=YES

ENET_TXD<6>

NO_TEST=YES

LED8700_P

NO_TEST=YES

TP_VESTA_LINK2_L

ENET_TXD<4>

NO_TEST=YES

NO_TEST=YES

LED_PP1V5_RUN_P

NO_TEST=YES

LED_PP1V8_RUN_N

NO_TEST=YES

NC_J3108_11

NO_TEST=YES

NC_J3108_10

ENET_TXD_R<4>

NO_TEST=YES

ENET_TXD_R<7>

NO_TEST=YES

ENET_TXD_R<6>

NO_TEST=YES

ENET_TXD_R<3>

NO_TEST=YES

ENET_TXD_R<2>

NO_TEST=YES

ENET_RXD_R<5>

NO_TEST=YES

ENET_TXD<3>

NO_TEST=YES

NO_TEST=YES

NC_SMU_FAN_TACH3

NC_SMU_FAN_TACH7

NO_TEST=YES

NC_SMU_SER_SEL

NO_TEST=YES

NO_TEST=YES

NC_SYS_DOOR_AJAR_L

NO_TEST=YES

NC_SMU_CPU_VID_LE1

NO_TEST=YES

NC_SMU_FAN_RPM3

NO_TEST=YES

NC_SMU_FAN_RPM4

NO_TEST=YES

TP_HT_MB_TO_NB_CLK_P<1>

NC_I2C_SMU_CPU_SCL_IN

NO_TEST=YES

NC_PSRO

NO_TEST=YES

ENET_RXD<1>

NO_TEST=YES

NO_TEST=YES

ENET_TX_ER_R

ENET_RXD<7>

NO_TEST=YES

ENET_RXD<6>

NO_TEST=YES

ENET_RXD<5>

NO_TEST=YES

ENET_RXD_R<0>

NO_TEST=YES

ENET_TXD<2>

NO_TEST=YES

ENET_TXD_R<1>

NO_TEST=YES

ENET_TXD_R<0>

NO_TEST=YES

ENET_TXD<7>

NO_TEST=YES

NO_TEST=YES

ENET_TXD<5>

ENET_TXD_R<5>

NO_TEST=YES

NO_TEST=YES

NC_SLOT_TOTAL_PWR

NO_TEST=YES

NC_CPU_AFN

NO_TEST=YES

TP_HT_MB_TO_NB_CLK_N<1>

NO_TEST=YES

NC_SMU_FAN_RPM5

NO_TEST=YES

NC_SMU_FAN_TACH4

ENET_TX_EN_R

NO_TEST=YES

NO_TEST=YES

ENET_TX_ER

TP_VESTA_PHYA<4>

NO_TEST=YES

NO_TEST=YES

TP_VESTA_SPD0

NO_TEST=YES

TP_VESTA_REGSUP2

NO_TEST=YES

TP_VESTA_RGMIIEN

NO_TEST=YES

TP_VESTA_REGCTL1

TP_VESTA_REGSEN2

NO_TEST=YES

NO_TEST=YES

TP_VESTA_MANMS

NO_TEST=YES

TP_VESTA_FDXLED_L

NO_TEST=YES

TP_VESTA_HUB

NO_TEST=YES

TP_VESTA_LINK1_L

NO_TEST=YES

TP_VESTA_2_5V_EN

NO_TEST=YES

TP_VESTA_DNC_C9

NO_TEST=YES

TP_VESTA_DNC_E9

NO_TEST=YES

TP_VESTA_EN_10B

NO_TEST=YES

TP_VESTA_FDX

NO_TEST=YES

TP_VESTA_AN_EN

NO_TEST=YES

NC_SMU_FAN_TACH5

NO_TEST=YES

TP_VESTA_ER

ENET_TXD<1>

NO_TEST=YES

ENET_RXD_R<6>

NO_TEST=YES

NO_TEST=YES

NC_SMU_CPU_VID_LE0

NC_PSRO_ENABLE

NO_TEST=YES

TP_VESTA_PHYA<0>

NO_TEST=YES

NO_TEST=YES

TP_VESTA_REGSEN1

TP_VESTA_PHYA<1>

NO_TEST=YES

NO_TEST=YES

TP_VESTA_RBC0

NO_TEST=YES

TP_VESTA_RBC1

TP_VESTA_REGCTL2

NO_TEST=YES

TP_VESTA_PHYA<3>

NO_TEST=YES

NO_TEST=YES

TP_VESTA_F1000

TP_VESTA_PHYA<2>

NO_TEST=YES

NO_TEST=YES

TP_VESTA_REGSUP1

TP_VESTA_TDBL<0>

NO_TEST=YES

ENET_RXD_R<1>

NO_TEST=YES

NO_TEST=YES

LED_PP1V8_RUN_P

NC_J3108_9

NO_TEST=YES

ENET_RXD_R<7>

NO_TEST=YES

NO_TEST=YES

TSENSE_GPU_ADD1

NO_TEST=YES

GPU_DIODE_PLUS

NO_TEST=YES

CPU_A_TBEN_CLK_R

NO_TEST=YES

CPU_B_TBEN_CLK_R

NO_TEST=YES

CPU_B_APSYNC_R

NO_TEST=YES

HT_SB_REFCLK_R

NO_TEST=YES

HT_NB_REFCLK_H0_R

NO_TEST=YES

CLK_RAIREF_200M_N_R

NO_TEST=YES

NB_PMR_CLK_P_R

NO_TEST=YES

NB_PMR_CLK_N_R

NO_TEST=YES

NB_PCIE_REFCLK_P_C

NO_TEST=YES

NB_PCIE_REFCLK_N_C

NO_TEST=YES

QUA1_REF_25MHZ_R

NO_TEST=YES

NB_DDR_REFCLK_N_R

NO_TEST=YES

NB_DDR_REFCLK_P_R

NO_TEST=YES

PCIE_C_REFCLKIN_N_C

NO_TEST=YES

PCIE_C_REFCLKIN_P_C

NO_TEST=YES

PCIE_B_REFCLKIN_N_C

NO_TEST=YES

PCIE_B_REFCLKIN_P_C

NO_TEST=YES

PCIE_A_REFCLKIN_N_C

NO_TEST=YES

PCIE_A_REFCLKIN_P_C

NO_TEST=YES

GFX_SLOT_PCIE_REFCLK_N_C

NO_TEST=YES

GFX_SLOT_PCIE_REFCLK_P_C

NO_TEST=YES

SB_USB2_CLK_33MHZ_R

NO_TEST=YES

CLK_RAI_REFCLK_66M_R

NO_TEST=YES

PCI_CLK33M_SB_EXT_R

NO_TEST=YES

NB_APSYNC_R

NO_TEST=YES

CLK_RAI_GIGE_25MHZ_R

NO_TEST=YES

ENET_TXD<0>

NO_TEST=YES

NC_PP1V5_PULSAR

NC_JTAGMUX_3

NO_TEST=YES

NC_J3108_8

NO_TEST=YES

NC_J3108_12

NO_TEST=YES

NO_TEST=YES

NC_CPU_TBEN_CLK

NO_TEST=YES

TP_SB_WATCHDOG

NO_TEST=YES

TP_NB_APSYNC

NO_TEST=YES

TP_I2S2_SB_TO_DEV_DTO

Q803_C

NO_TEST=YES

100M_N<0>

NO_TEST=YES

CKA_P<0>

NO_TEST=YES

HT_NB_P<0>

NO_TEST=YES

HT_NB_REFCLK_NF<0>

NO_TEST=YES

HT_NB_REFCLK_PF<0>

NO_TEST=YES

HT_NB_TO_SB_CAD_P<0..7>

NO_TEST=YES

HT_NB_TO_SB_CLK_P<0>

NO_TEST=YES

HT_NB_TO_SB_CLK_N<0>

NO_TEST=YES

NO_TEST=YES

HT_SB_TO_NB_CAD_N<0..7>

NO_TEST=YES

HT_SB_TO_NB_CAD_P<0..7>

NO_TEST=YES

EI_NB_TO_CPU_SR_N<0>

NO_TEST=YES

EI_NB_TO_CPU_CLK_P

NO_TEST=YES

EI_NB_TO_CPU_CLK_N

NO_TEST=YES

EI_CPU_TO_NB_SR_P<1>

NO_TEST=YES

EI_CPU_TO_NB_SR_N<1>

NO_TEST=YES

EI_CPU_TO_NB_CLK_P

NO_TEST=YES

EI_CPU_TO_NB_CLK_N

NO_TEST=YES

CLK_KOD_100M_PF<0>

NO_TEST=YES

CLK_KOD_100M_NF<0>

NO_TEST=YES

HT_SB_TO_NB_CTL_P<0>

NO_TEST=YES

HT_NB_TO_SB_CTL_N<0>

NO_TEST=YES

HT_NB_TO_MB_CTL_P<1>

NO_TEST=YES

HT_NB_TO_MB_CTL_N<1>

NO_TEST=YES

PCIE_NB_TO_SLOTA_PF<4>

NO_TEST=YES

PCIE_NB_TO_SLOTA_NF<12>

HT_SB_TO_NB_CLK_P<0>

NO_TEST=YES

NO_TEST=YES

HT_MB_TO_NB_CTL_N<1>

NO_TEST=YES

PCIE_NB_TO_SLOTA_PF<10>

NO_TEST=YES

PCIE_NB_TO_SLOTA_PF<14>

LED_PP1V2_RUN_P

NO_TEST=YES

NO_TEST=YES

KP_V<1>

NO_TEST=YES

KP_V<2>

NO_TEST=YES

PP1V2_RUN_FOR_LED

NO_TEST=YES

PCIE_NB_TO_SLOTA_PF<13>

NO_TEST=YES

PCIE_NB_TO_SLOTA_P<10>

PCIE_NB_TO_SLOTA_P<1>

NO_TEST=YES

PCIE_NB_TO_SLOTA_N<3>

NO_TEST=YES

NO_TEST=YES

UATA_DD<14>

PCIE_NB_TO_SLOTA_N<0>

NO_TEST=YES

CPU_SENSE_KP_V

NO_TEST=YES

NO_TEST=YES

NB_PLL_OUT_TRG

NO_TEST=YES

GPU_DIODE_MINUS

NO_TEST=YES

CPU_A_APSYNC_R

NO_TEST=YES

HT_NB_REFCLK_L0_R

LED8701_P

NO_TEST=YES

NO_TEST=YES

TSENSE_GPU_OVERTEMP_L

NO_TEST=YES

PP3V3_GPU_TSENSE

NO_TEST=YES

T555_PWM

NO_TEST=YES

T555_OUT

NO_TEST=YES

T555_THRES

NO_TEST=YES

T555_DISC

HT_SB_TO_NB_CLK_N<0>

NO_TEST=YES

CKA_N<0>

NO_TEST=YES

HT_NB_N<0>

NO_TEST=YES

PCIE_SLOTA_TO_NB_N<0..15>

NO_TEST=YES

NO_TEST=YES

UATA_DD<1>

NO_TEST=YES

PCIE_NB_TO_SLOTA_NF<7>

PCIE_NB_TO_SLOTA_NF<13>

NO_TEST=YES

NO_TEST=YES

UATA_DA<0>

HT_NB_TO_SB_CAD_N<0..7>

NO_TEST=YES

NO_TEST=YES

PLLLOCK

TP_VESTA_TEST_1394<1>

NO_TEST=YES

TP_VESTA_TEST_1394<0>

NO_TEST=YES

NO_TEST=YES

TP_NB_B_TRIGGER_OUT

NO_TEST=YES

TP_NB_A_TRIGGER_OUT

NO_TEST=YES

CARD_READER_ACTIVITY_R

TP_VESTA_TVCO

NO_TEST=YES

TP_VESTA_TEST<0>

NO_TEST=YES

TP_VESTA_TDBL<1>

NO_TEST=YES

TP_VESTA_TDBL<2>

NO_TEST=YES

TP_VESTA_TEST<1>

NO_TEST=YES

NO_TEST=YES

TP_VESTA_FAVDDL

NO_TEST=YES

EI_NB_TO_CPU_SR_P<0>

FUNC_TEST=TRUE

JTAG_NB_TRST_L

FUNC_TEST=TRUE

JTAG_NB_TDI

FUNC_TEST=TRUE

TP_JTAG_VESTA_TRST_L

FUNC_TEST=TRUE

TP_JTAG_VESTA_TMS

FUNC_TEST=TRUE

JTAG_NB_TDO

FUNC_TEST=TRUE

TP_JTAG_SB_TMS

FUNC_TEST=TRUE

TP_JTAG_SB_TDO

FUNC_TEST=TRUE

TP_JTAG_SB_TDI

JTAG_CPU_TCK

FUNC_TEST=TRUE

JTAG_CPU_TDI

FUNC_TEST=TRUE

JTAG_CPU_TDO

FUNC_TEST=TRUE

JTAG_CPU_TRST_L

FUNC_TEST=TRUE

JTAG_CPU_TMS

FUNC_TEST=TRUE

NO_TEST=YES

HT_MB_TO_NB_CTL_P<1>

97

132

132

132

132

132

132

132

132

132

132

132

132

132

132

132

132

132

132

97

97

97

97

97

47

30

30

24

84

131

131

131

131

97

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

131

97

97

101

101

101

56

56

56

56

56

56

56

97

97

97

97

97

97

97

84

84

84

129

84

97

101

84

129

97

97

129

43

56

30

30

43

43

43

47

43

20

20

20

20

82

92

130

130

130

130

82

26

12

12

130

130

132

12

139

26

26

26

13

130

130

93

130

136

132

130

12

11

31

31

130

130

130

130

130

130

130

31

31

31

31

31

31

31

101

31

56

130

130

130

130

130

130

130

130

130

130

130

130

31

56

101

31

31

130

130

132

132

17

132

17

17

132

132

132

132

17

17

17

132

132

132

31

132

130

130

31

56

132

17

132

132

132

17

132

132

132

17

139

130

11 31

130

93

93

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26