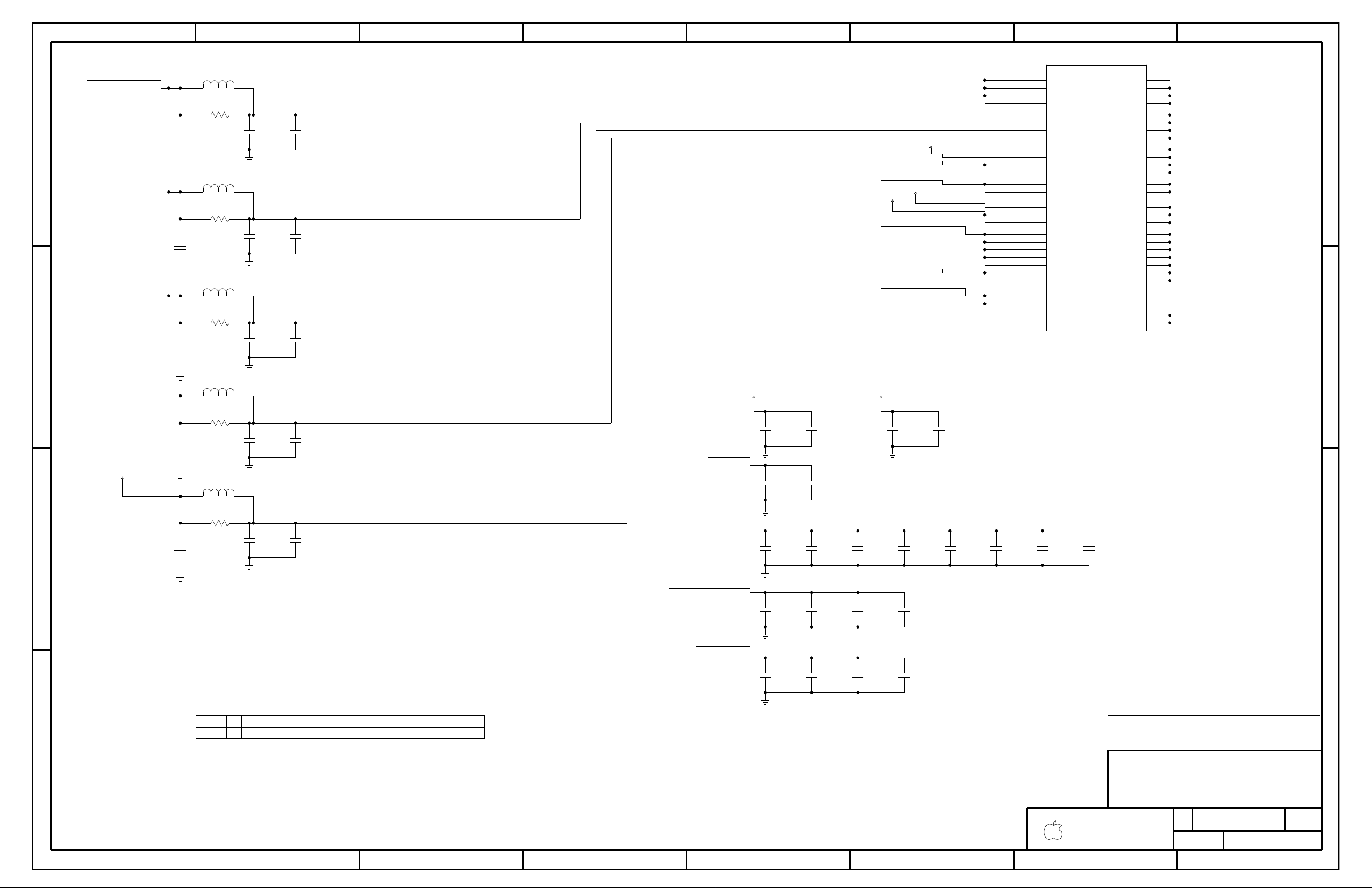

Apple iMac G5 GILLA EVT1 MLB 051-6482 Rev13 Schematic

ANGLES

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

DATE

APPD

ENG

DATE

APPD

CK

ECN

ZONE

REV

DO NOT SCALE DRAWING

X.XXX

X.XX

XX

DIMENSIONS ARE IN MILLIMETERS

THIRD ANGLE PROJECTION

D

SIZE

APPLICABLE

NOTED AS

MATERIAL/FINISH

NONE

SCALE

DESIGNER

MFG APPD

DESIGN CK

RELEASE

QA APPD

ENG APPD

DRAFTER

METRIC

OF

SHT

DRAWING NUMBER

TITLE

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

Apple Computer Inc.

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

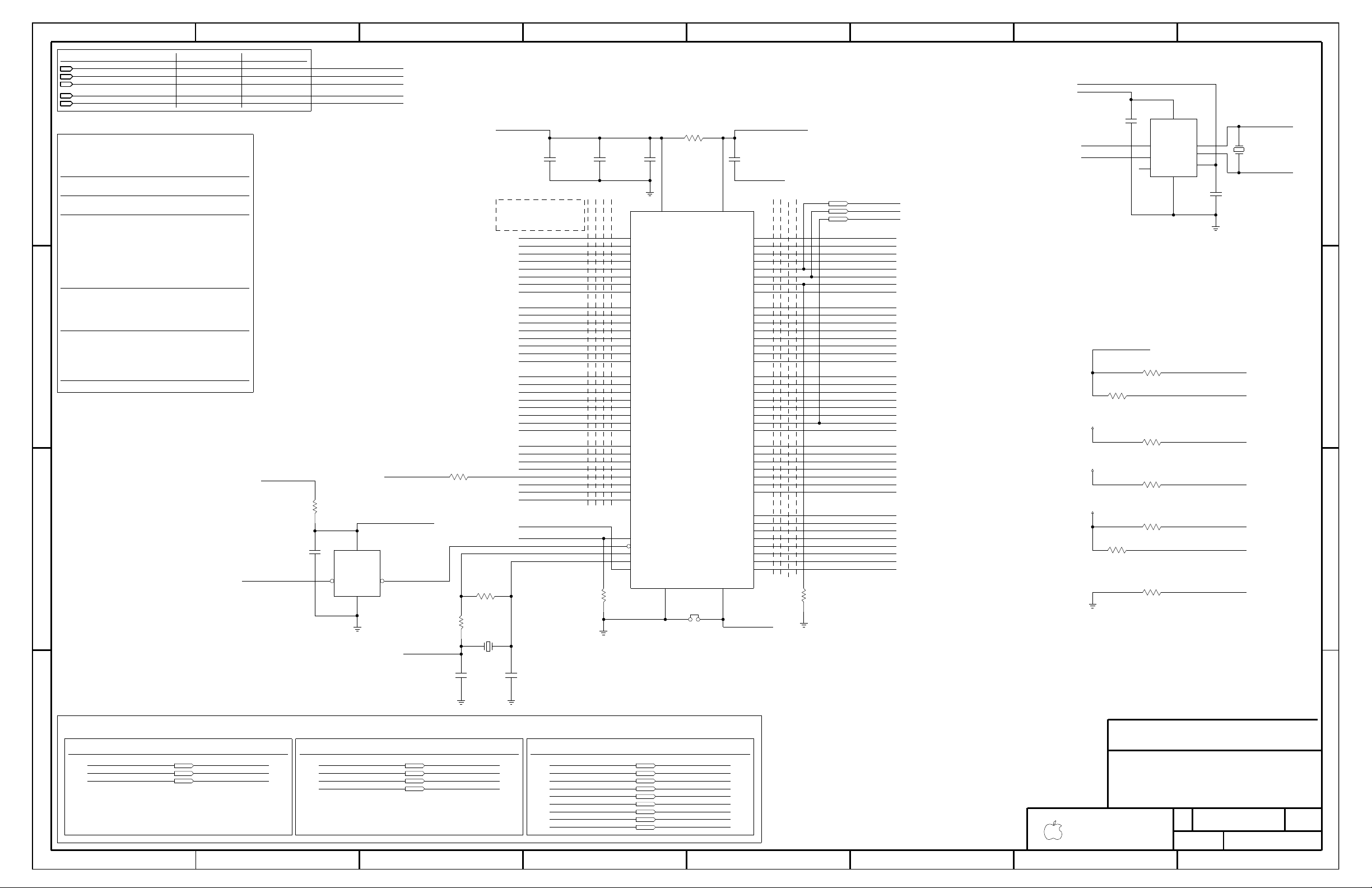

REV.

DESCRIPTION OF CHANGE

11/21/03

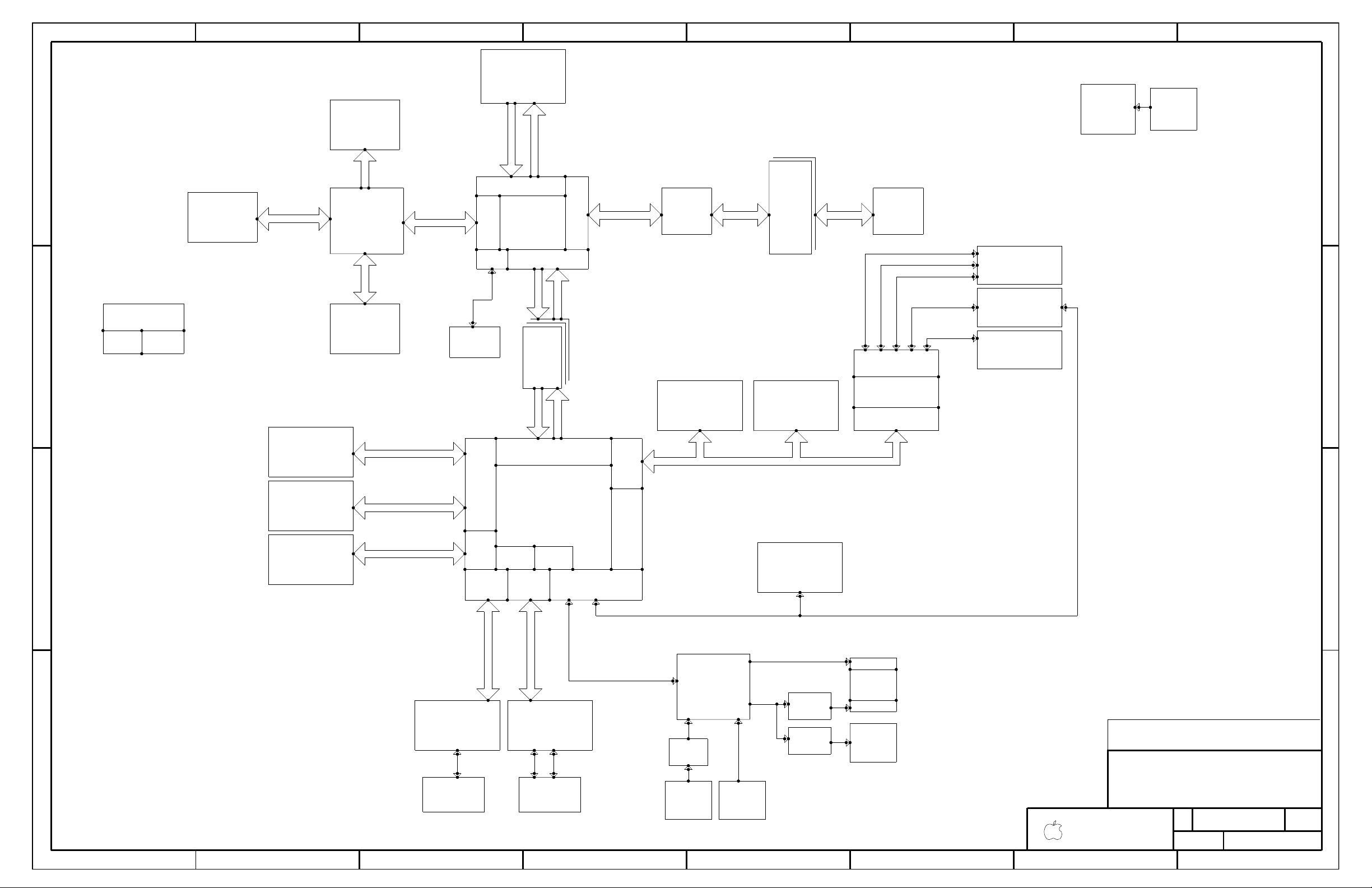

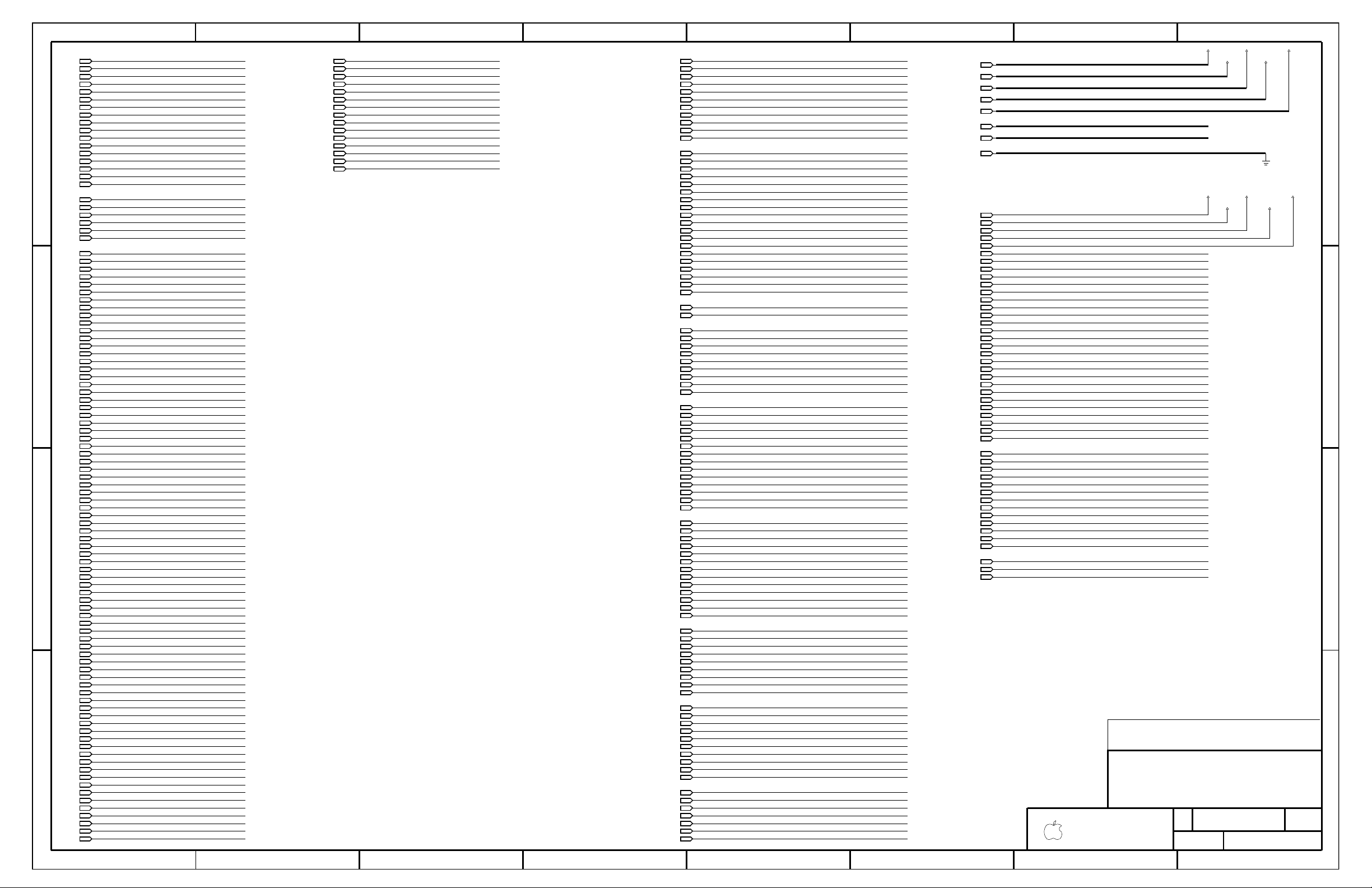

SYSTEM BLOCK DIAGRAM

REVISION HISTORY

7

4

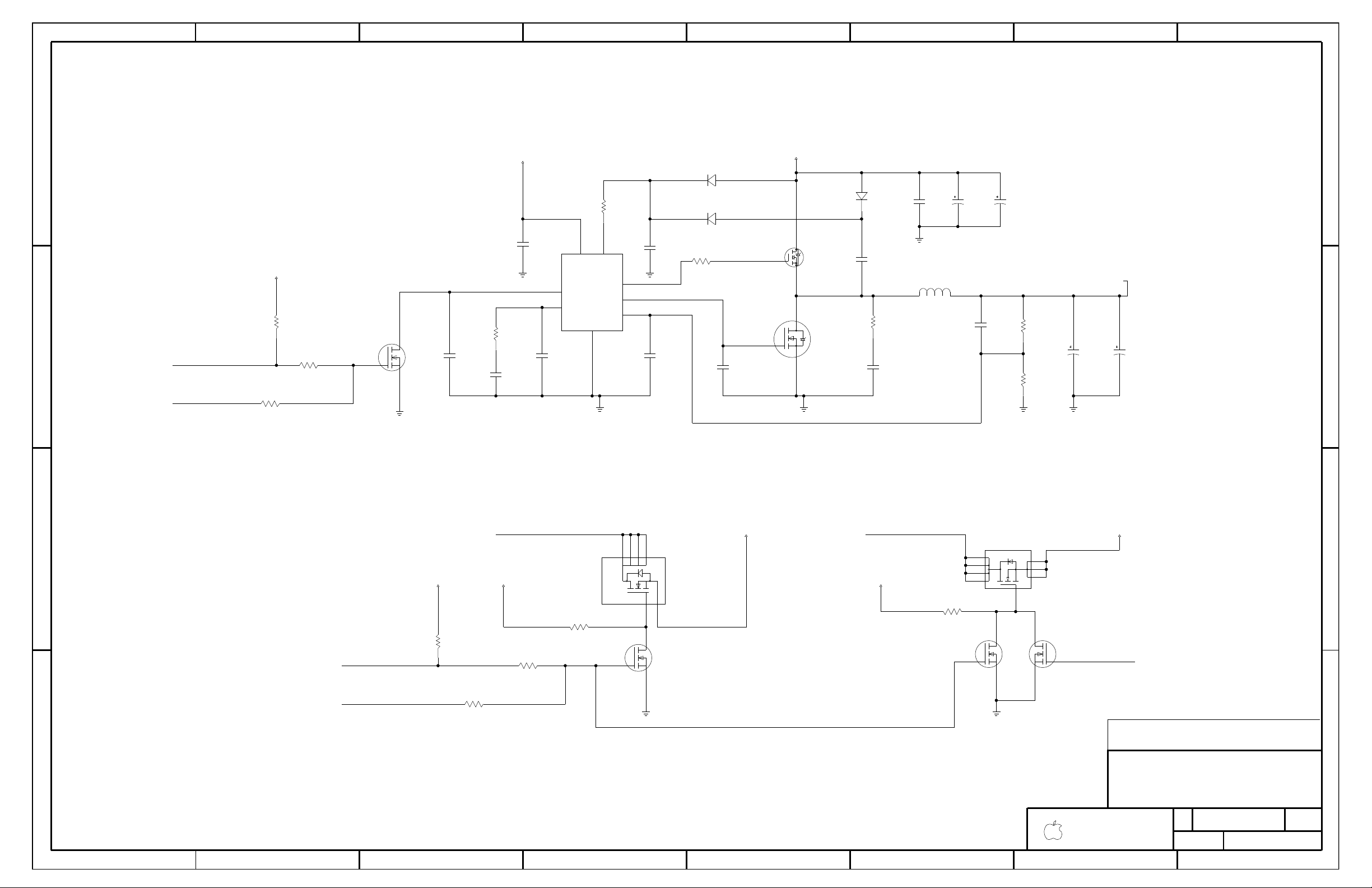

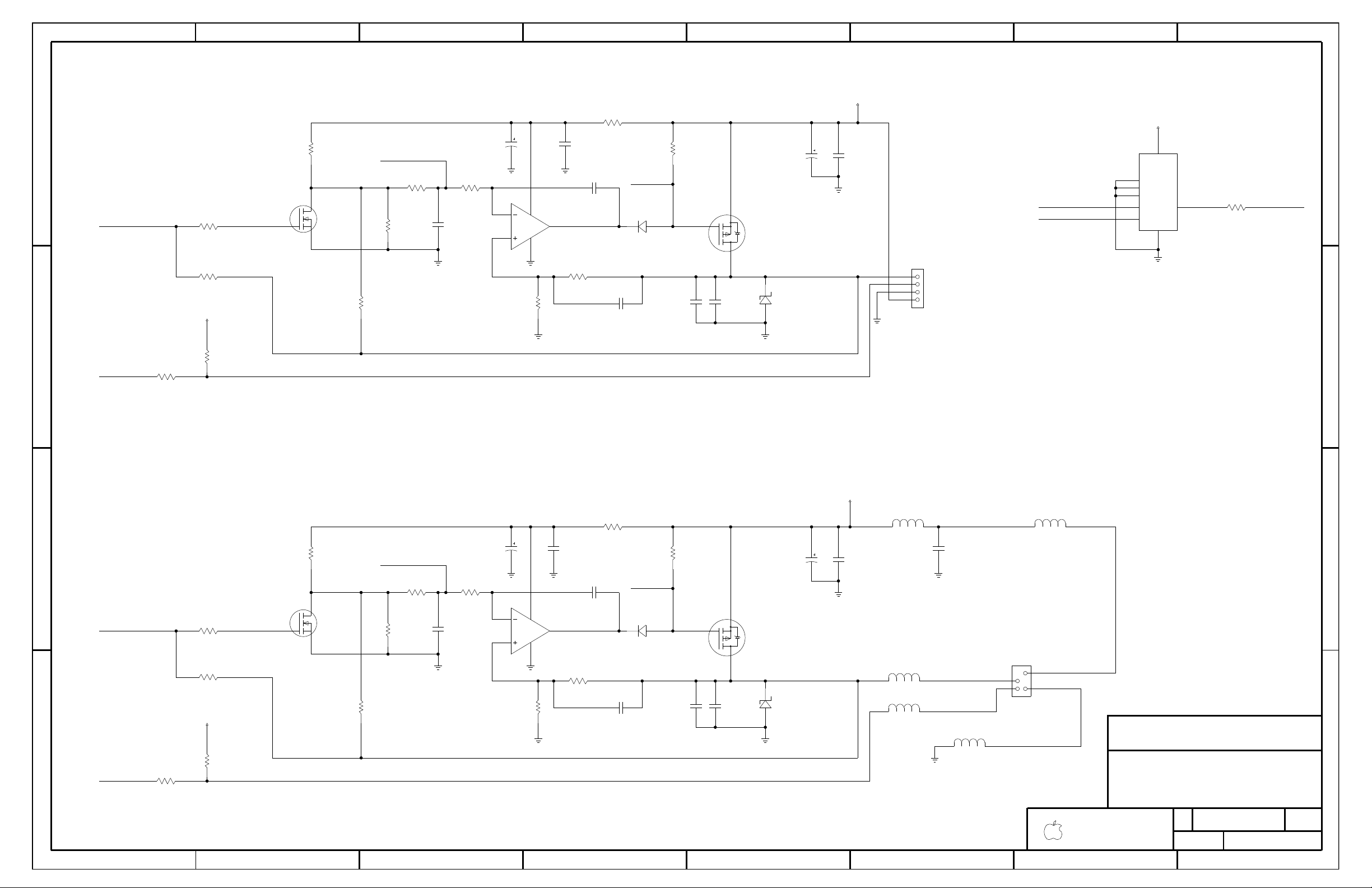

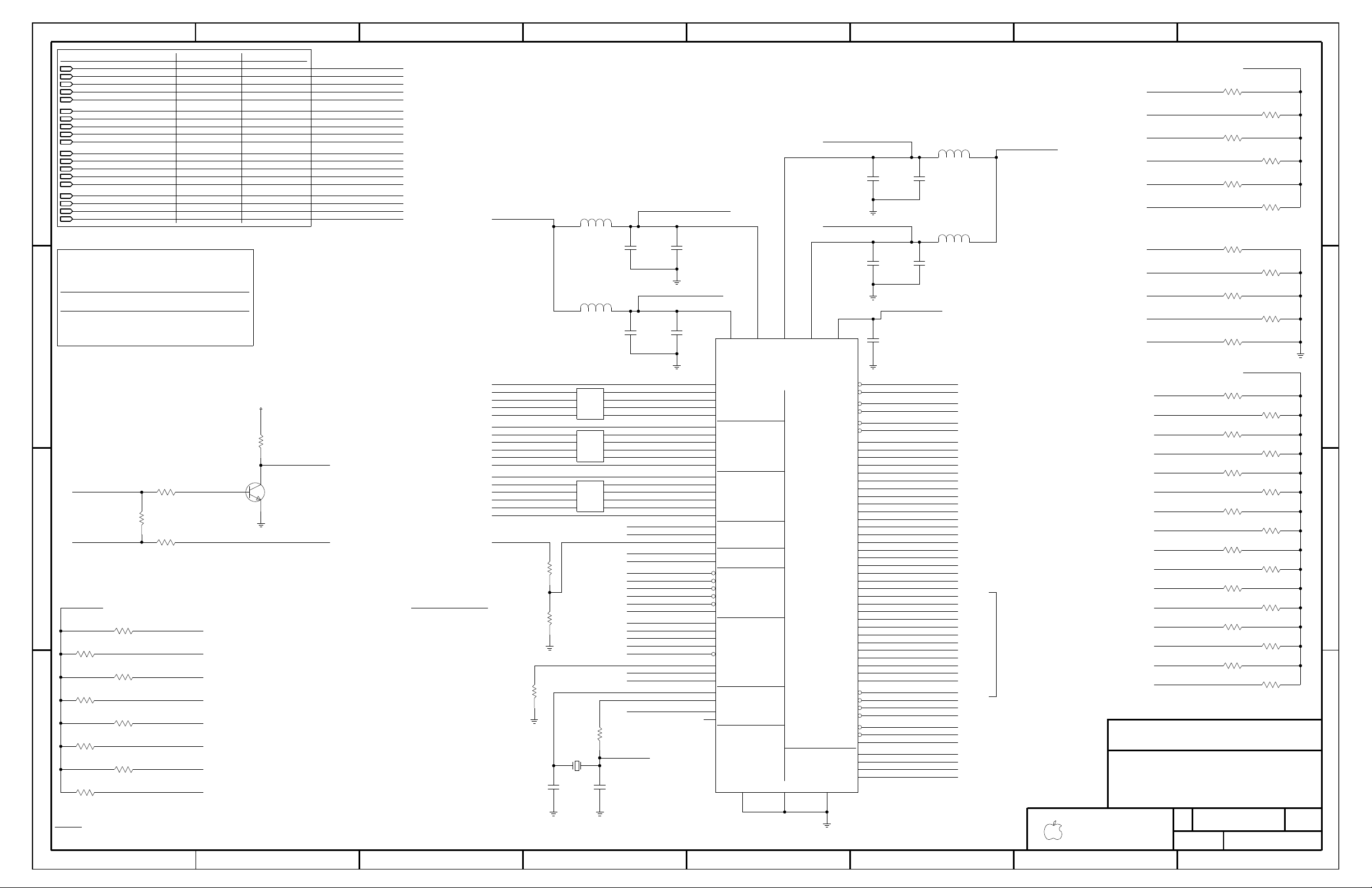

POWER BLOCK DIAGRAM

49

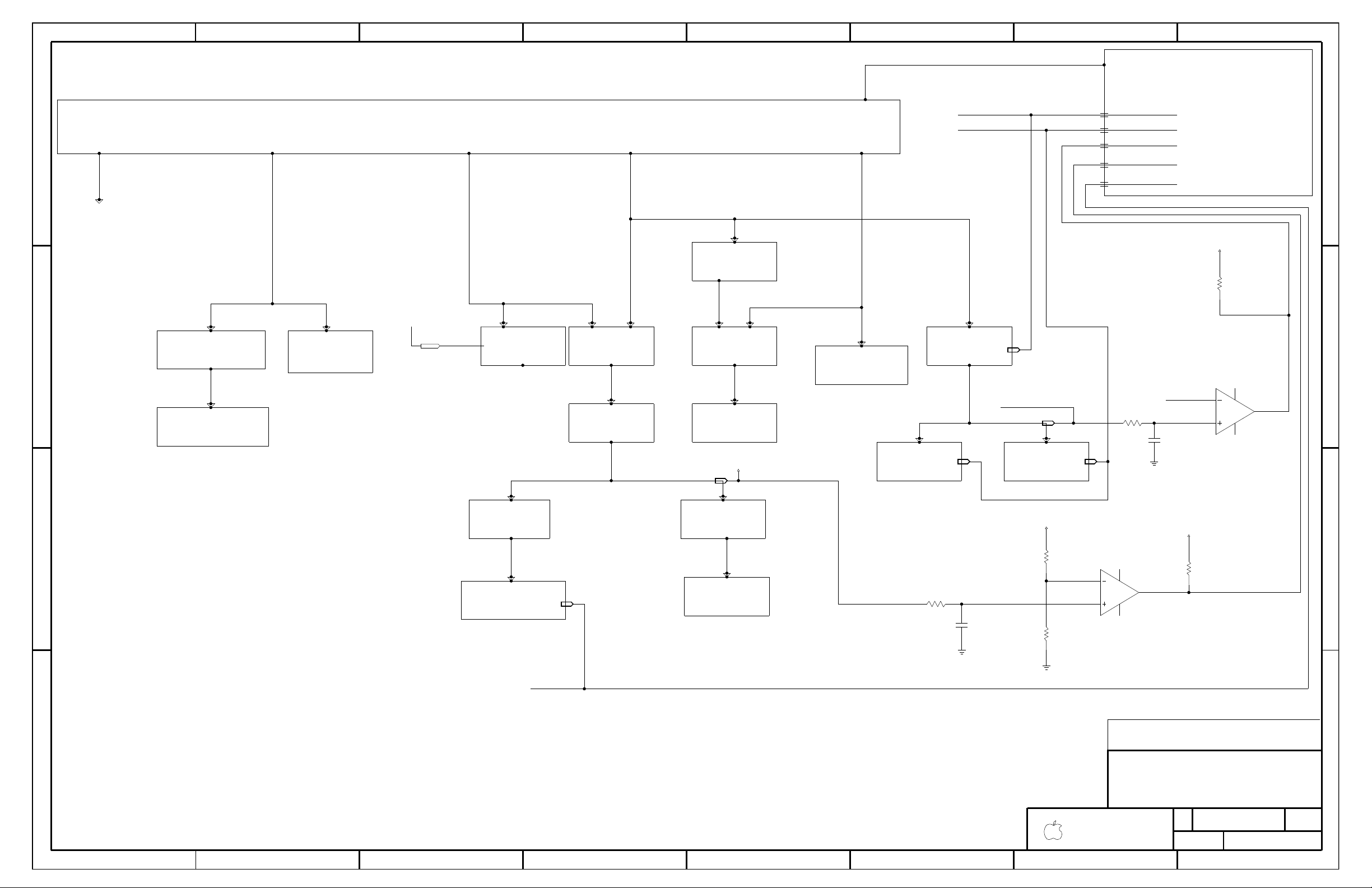

3.3V/5V PWRON SWITCHING

14

11

3

SHASTA DISK

PDF

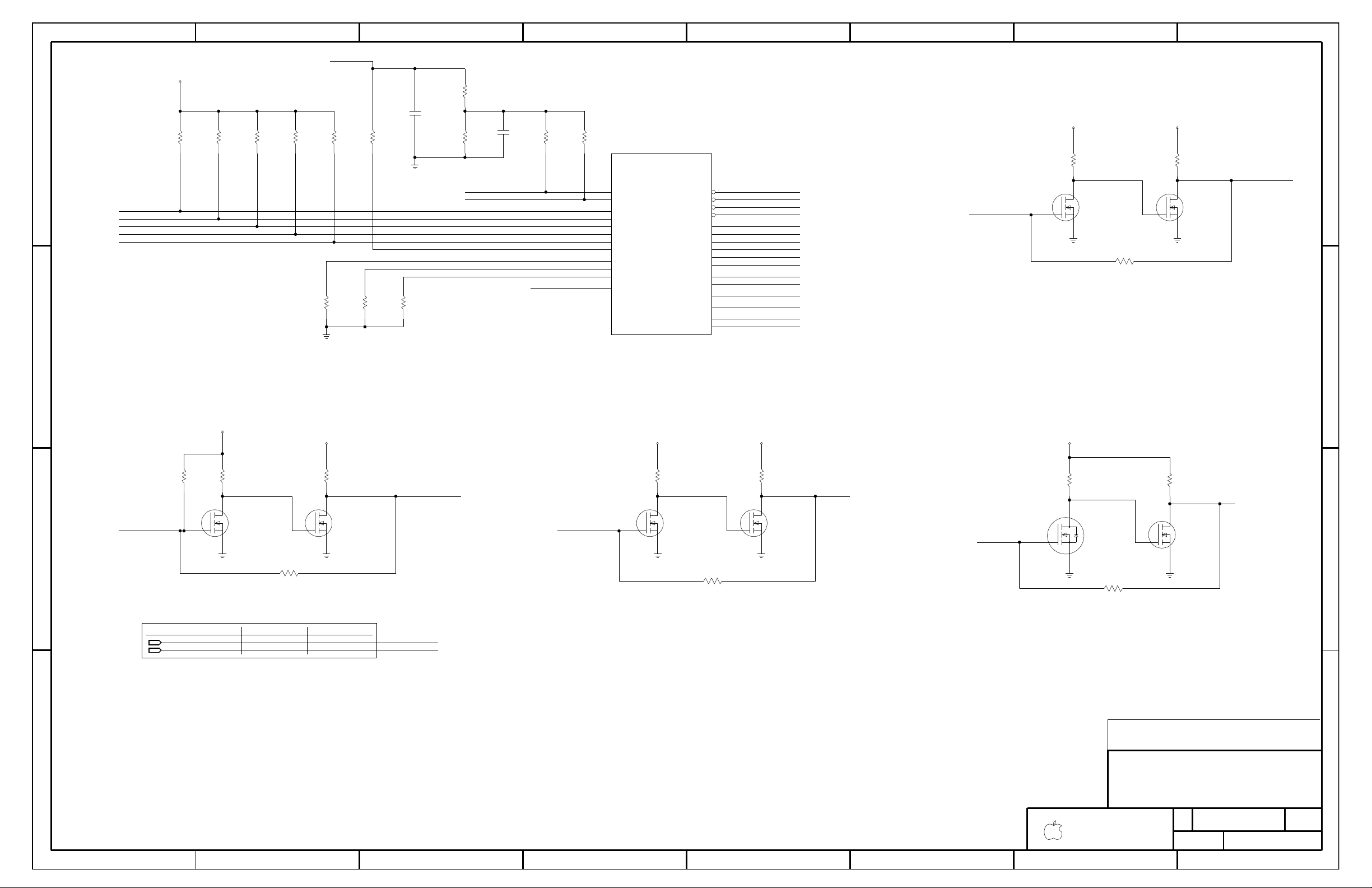

CPU FAN 1 CONTROL

41

CIRCUIT

EXTERNAL TMDS TRANSMITTER

BLOCK

18

17

DISK CONNECTORS

83

84*

87

FIREWIRE A PHY & CONNECTORS

76

59

HYPERTRANSPORT LA CONNECTORS

SHASTA PCI

BOOT ROM

56

55

14

34

33

32

29

30

28

31

27

20

25

22

24

19

23

26

16

13

15

11

2

10

8

9

DISK

AUDIO CONNECTORS

SPEAKER AMP

HEADPHONE / LINE OUT

AUDIO CODEC, LINE IN, MIC IN

AUDIO POWER SUPPLIES

MODEM CONNECTOR

USB HOST INTERFACE

SHASTA FIREWIRE

ETHERNET PHY & CONNECTORS

SHASTA ETHERNET

USB DEVICE INTERFACE

USB

MODEM

AUDIO

FIREWIRE

ETHERNET

90

88*

94

91*

96*

95*

98*

97*

99*

92

GRAPHICS

GPU FRAME BUFFER

74*

PAGE

77*

80*

75*

60*

62*

64

54

57

58

EXT VGA & TMDS

U3LITE HYPERTRANSPORT

SHASTA HYPERTRANSPORT

USB2 PCI

GRAPHICS DDR SDRAM A

GRAPHICS DDR SDRAM B

GPU STRAPS

GPU DAC & CLOCKS

50

51

52

53

48

PAGE PDF

U3LITE AGP

GPU VREG

GPU AGP

FRAME BUFFER TERMINATION

CIRCUIT

PCI

HT

BLOCK

AIRPORT EXTREME

GPU DVI & STRAPS

7

35

TOP

21

3

2

38

39

40

42

43

52

50

44

49

46

48

47

45

51

53

63

61

56

58

57

60

54

55

62

59

68

66

65

64

67

69

70

FUNC TEST

I2C CONNECTIONS

SHASTA SERIAL

PULSAR POWER

SHASTA CORE

VTT VREG

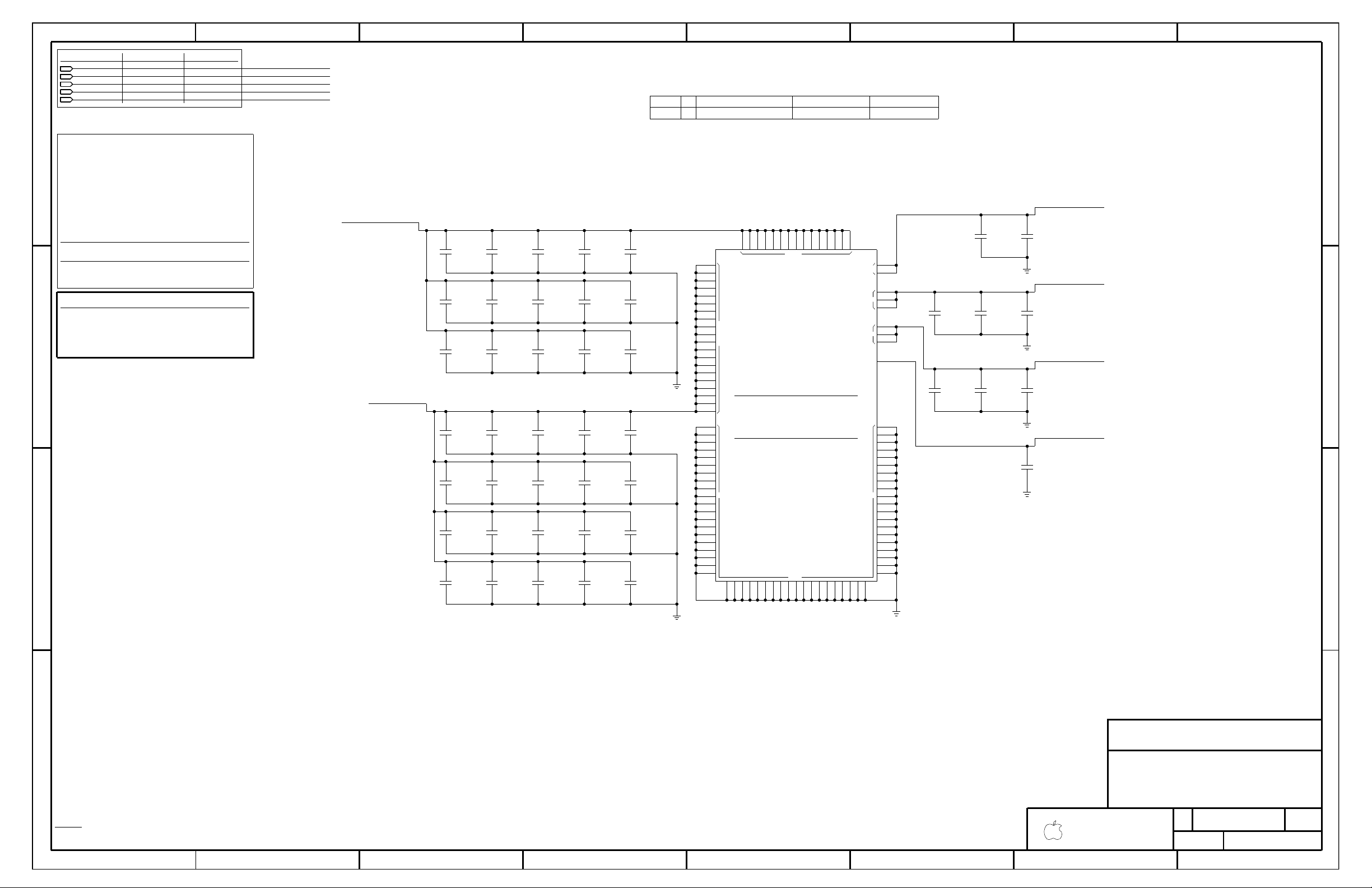

DIMMS

SERIES TERMINATION

PARALLEL TERMINATION

CPU DIODE CONDITIONER

CPU BYPASS

CPU VREG

U3LITE MEMORY

PARALLEL TERMINATION

CPU VREG OUTPUT CAPS

CPU VREG

NEO POWER & BYPASS

U3LITE CORE

1.2V VREG

SMU

8

6

9

18

16

22

10

23

24

25*

26

27

28*

29

30

31

32

33

34

35

38

36

37*

40

45

46

44

* PAGES WHERE MASTER PAGE IS IN A DIFFERENT SCHEMATIC

MEMORY

PROCESSOR

4

36

37

2.5V VREG

CPU LOGIC ANALYZER CONNECTOR

6

INDICATOR LED

21*

17

13*

CPU STRAPS

U3LITE APPLE PI

PULSAR CLOCKS

U3LITE MISC

12

CPU FAN 2 AND SYSTEM FAN CONTROL

POWER CONNECTOR / POWER ALIAS

11

5

TABLE OF CONTENTS

NEO APPLE PI

SIGNAL ALIAS

GILA

EVT1

??

? ?

99

1

051-6482

13

SCH,MLB,GILA

?

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

AIRPORT

EXTREME

BOOTROM

CONNECTOR

PAGE 24

J9401

CTL-LESS /

NCs

S/PDIF

U9000

U1300

SMU

PAGE 13

U1301

PAGE 13

RTC

1394 OHCI (3.3V/98MHz)

LINE OUT

AMP

AUDIO CODEC

CONNECTOR

TERM

PARALLEL

PAGES 44&45

CONNECTOR

MICRODASH MODEM

BLUETOOTH

CONNECTOR

CONNECTORS

PAGE 92

PAGE 94

PAGE 92

J9210/J9220/J9230

USB

J9400

J9240

54

USB 2.0

PAGE 91

USB

321

uPD720101

U7700

AMP

J9800

LINE IN

PAGE 97

PAGE 98

CONNECTOR

LINE IN

PAGE 98

MIC

J9802

J9801

CONNECTOR

SPEAKER

PAGE 98

LINE OUT

OPTICAL OUT

J9803

COMBO OUT

CONNECTOR

PAGE 98

PAGE 97

SPEAKER

PAGE 97

AMP

PAGE 95

U9500

PCM3052

CONNECTOR

NV18B/NV34

GPU

U4900

PAGE 49

PAGE 94

SOFT MODEM

32-bit PCI (5V-3.3V/33MHz)

J7600

PAGE 76

SERIES

PCI

GOOD,BETTER,BEST: HARD DRIVE

EDUCATION: NOT USED

PAGE 54

FREQUENCIES LISTED ARE MAXIMUM DATA TRANSFER RATES SUPPORTED BY U3LITE

PAGE 25

PAGE 25

PAGE 80PAGE 80

CONNECTORS

ETHERNET

POWER

PAGE 26

U2600

PULSAR

CLOCKS

PAGE 27

PAGE 87

4 Diff pairs

J8700

PAGE 87

10/100 ETHERNET

BCM5221

CONNECTOR

8-bit TX & 8-bit RX

U8700

GMII (3.3V/125MHz)

0

FIREWIRE A

FIREWIRE A

1

802A

PAGE 90

J9000, J9001

PAGE 90

2 Diff pairs

8-bit TX/RX

SCCA

To Shasta

SCCBSCCA

I2S1

I2S

I2S0 I2S2

PAGE 88

FIREWIREETHERNET

PAGE 84

PAGE 23

CORE

GPIO/PCI64

PAGE 74

PCI

U7500

PAGE 75 PAGE 77

FOR DEVELOPMENT ONLY

EDUCATION: HARD DRIVE

GOOD,BETTER,BEST: OPTICAL

PAGE 83

CONNECTOR

3.3V/133MHZ

UATA

J8302

PAGE 83

J8301

UATA

PAGE 83

JXXXX

SATA

SATA DEV

CONNECTOR

CONNECTOR

SATA/150

UATA/133

SATA/150

1.2V/1.5GHZ

1.2V/1.5GHZ

SATA2SATA1

U2300

SATA

AGP

U3

17",20" INVERTER

J5902, J5903

PAGE

MISC

DIMMS

J4001

J4000

PAGE 62

SHASTA

PAGE 91

FRAME

PAGE 55

8X AGP

J5900, J5901

2.6V/540MHZ

2.6V/540MHZ

TMDS

BUFFER A

FRAME

U5400, U5401

FRAME BUFFER

FRAME BUFFER

64-BIT

U5500, U5501

BUFFER B

333MHZ SUPPORTED

MAIN MEMORY

64/128-BIT

2.6V/400MHZ

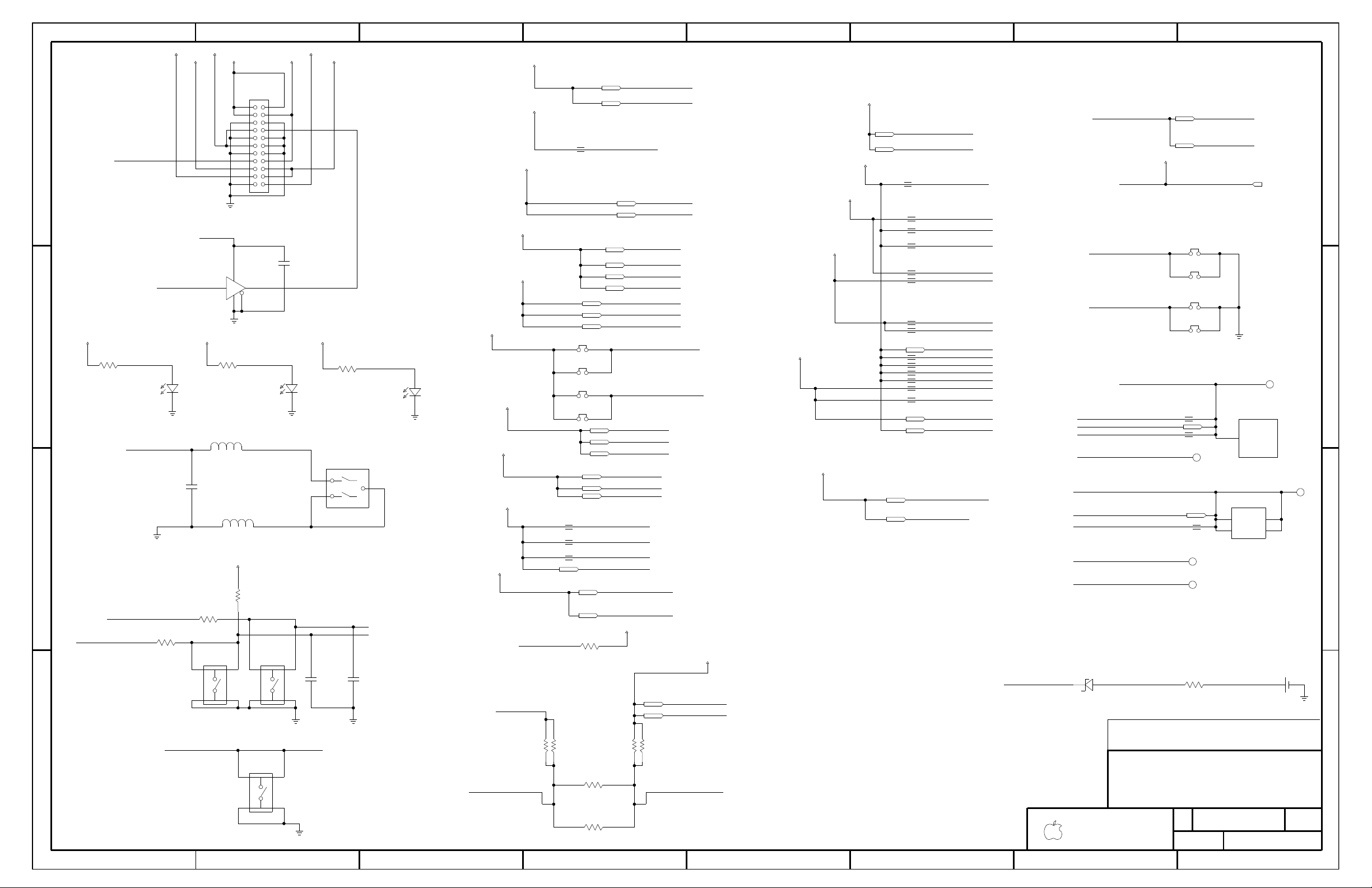

SYSTEM BLOCK DIAGRAM

APPLE PI

32-BIT

PAGE 29

APPLE PI

PAGE 28

MAIN MEMORY

PAGE 37

TERM

PAGE 40

PAGE 38

8-BIT

HYPERTRANSPORT

CONTROL = 2.5V

PAGE 60

CORE

PAGE 22

J6400

J6401

32-BIT

I/O = 1.5V

4X = 1.5V

1.2V/400MHZ

J6402

0.8V/533MHZ

48

HYPERTRANSPORT

HYPERTRANSPORT

U3LITE

PAGE 18

I2C

CPU

U2900

PAGE 64

HT

PAGE 59

EXT VGA

64-BIT

DEBUG

NEO 10S

ELASTIC INTERFACE

1.2V/900MHZ

992

13

051-6482

ALIAS

IN

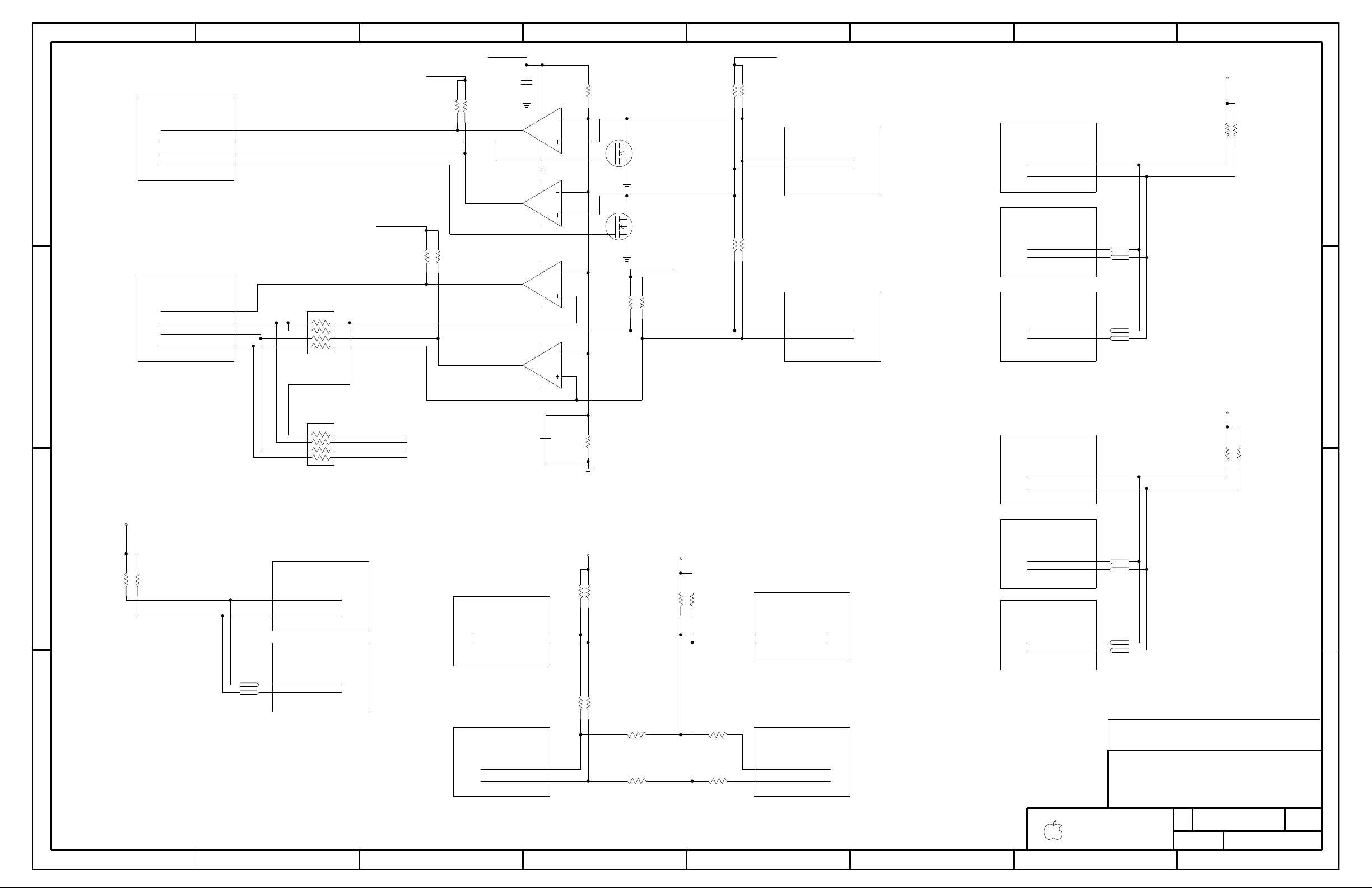

IN IN

IN

LM339A

V+

GND

IN

LM339A

V+

GND

IN

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

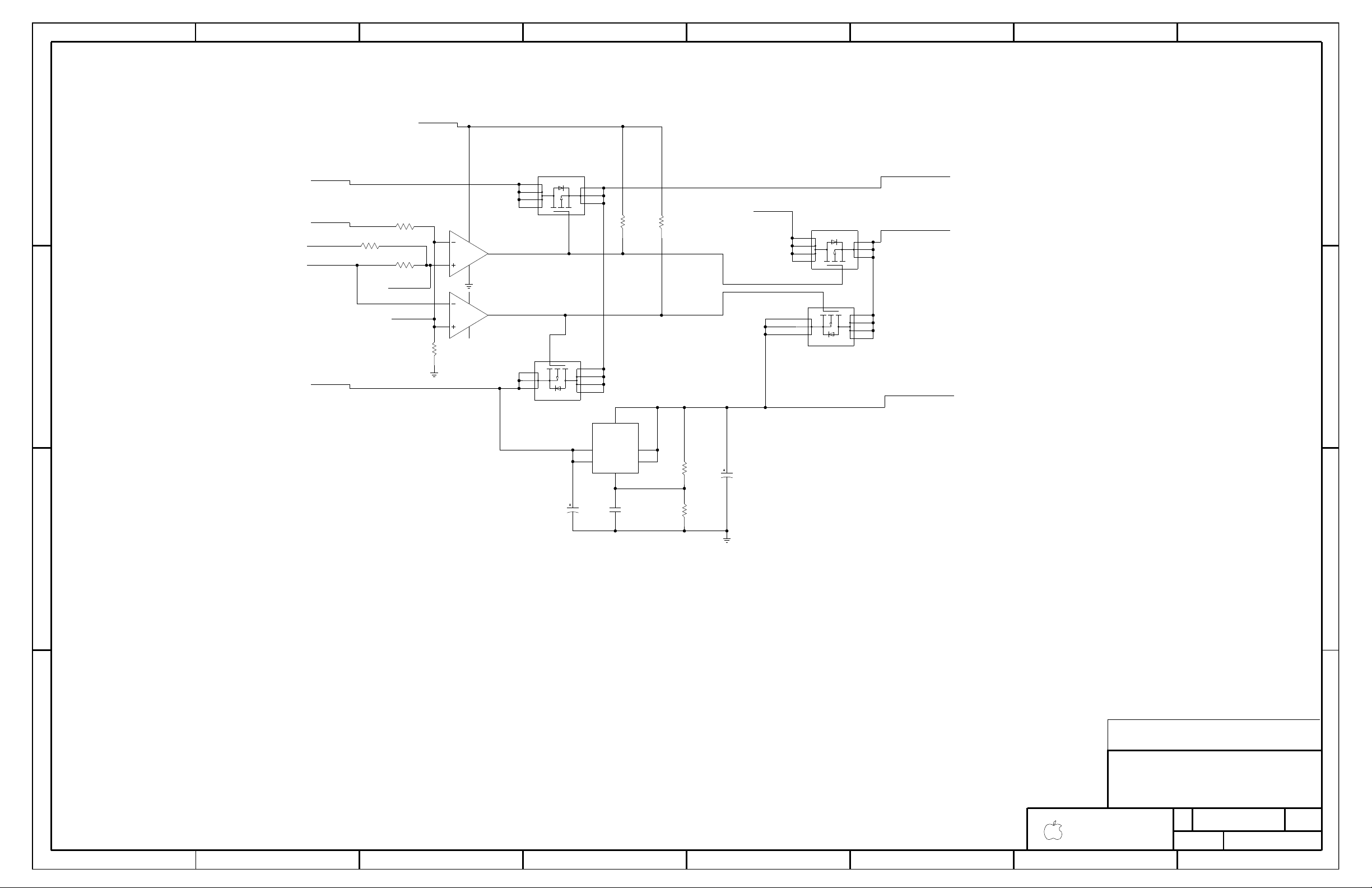

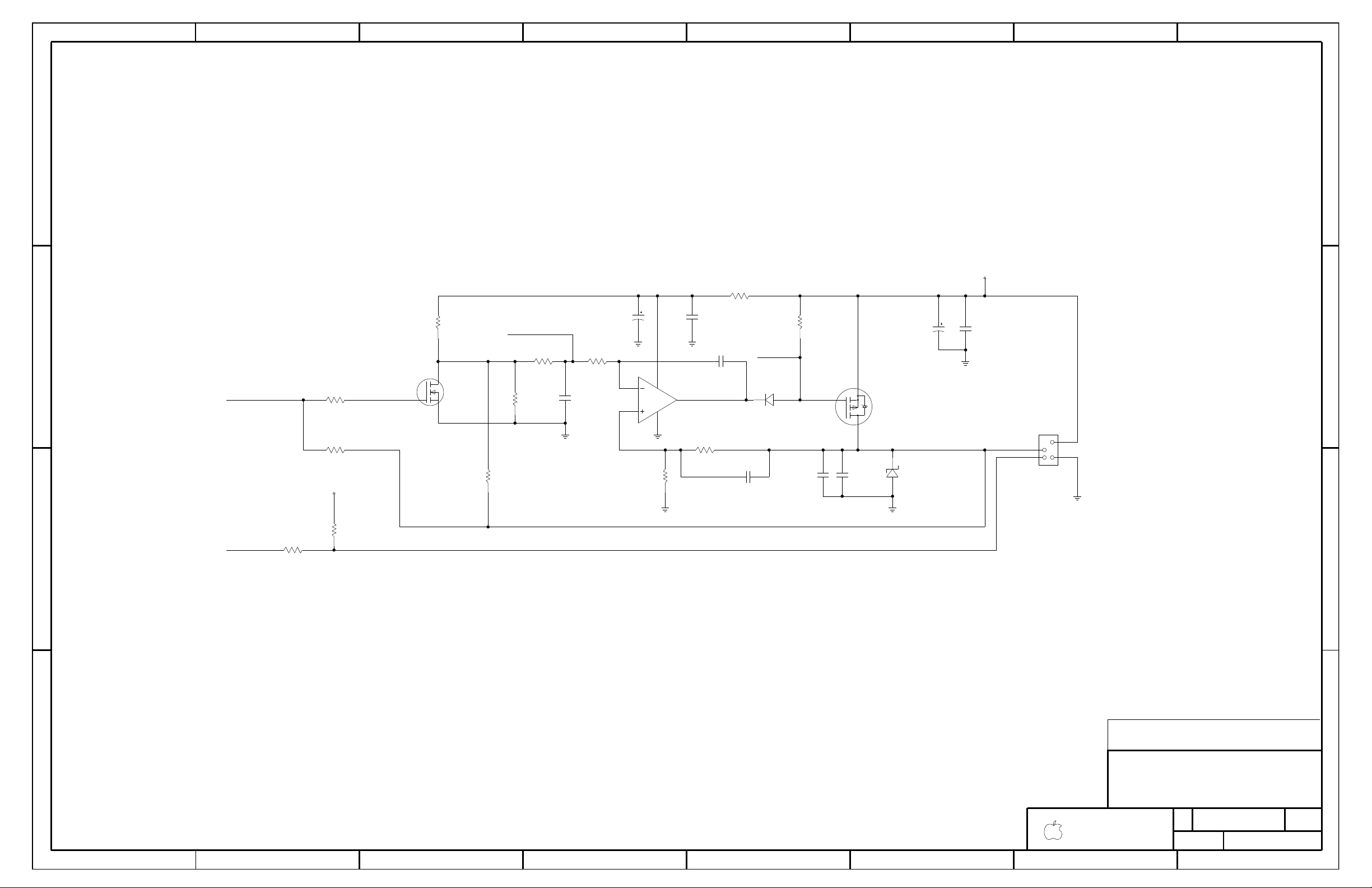

FET SWITCH

PP1V5_RUN

PP1V25_RAM_VTT

LINEAR

(TURN_ON_VTT)

(PWR_GOOD_PP2V5)

(PWR_GOOD_SB_CORE)

POWER SEQUENCE PIN

SYS_POWERUP_L

SWITCHER

PAGE 11

PP2V5_RUN_CPU_AVDD

SMU

SWITCHER

PP3V3_ALL

SWITCHER

2.62V

PULSAR CORE

1.6/1.4V

PP5V_PWRON

FET SWITCH

SWITCHER

FET SWITCH

PP1V2_PWRON

PWRON_DISK_SB

SYS_POWERUP_L

PAGE 10

PWRON_SD

PAGE 10

PP1V2_RUN

FET SWITCH

HT BUS

API BUS

1.2V

PAGE 10

SHASTA CORE

IRU3037ACS

PP1V2_SHASTA_CORE

5V

POWER SW

AGP BUS

4.5V

5V

PAGE 99

PAGE 99

PP5V_RUN_AUDIO

PP4V5_RUN_AUDIO

1.25V

PAGE 46

LINEAR

AUDIO CODEC

LINEAR

HP/LINEOUT AMP

0.8~1.2V

PAGE 33

SC1211*4

SC2643VX*1

SWITCHER

CPU CORE

PAGE 9

GPUL

2.5V

J700

PAGE 7

FW CONN

20" LCD INVERTER

PP24V_RUN

20" LCD INVERTER

PP12V_RUN

PP5V_RUN

LINEAR

PAGE 31

POWER CONNECTOR

HDD & OPTICAL

PP2V5_RUN

RAM VTT

PAGE 50

GRAPHIC FB

RAM TERM

PP2V5_PWRON

PAGE 9

IRU3037CS

DDR DIMM

SHASTA HT

CPU AVDD

5V

USB CONN

UDASH MODEM

PAGE 50

1.5V

1.5V

PAGE 22

IRU3037CS

U3LITE CORE

U3LITE CORE

PP1V5_PWRON

LINEAR

PAGE 11

3.3V

PAGE 11

3.3V

FET SWITCH

PP3V3_PWRON

LINEAR

USB2 HOST

MODEM & BT

ENET PHY

SMU

FW PHY

PAGE 50

GPU CORE

IRU3037CS

NV18B/NV34

PP5V_ALL

PCI BUS

PP3V3_RUN

AUDIO CODEC

POWER BLOCK DIAGRAM

20" PANEL POWER

402

CERM

16V

20%

0.01UF

PP2V5_PWRON

402

MF

1/16W

5%

150K

100K

5%

1/16W

MF

402

5%

1/16W

MF

10K

402

5%

1/16W

MF

10K

402

PP5V_ALL

PP3V3_ALL

SOI

PP3V3_ALL

SOI

402

MF

1/16W

5%

100K

0.01UF

20%

16V

CERM

402

402

MF

1/16W

5%

100K

3

99

13

051-6482

PWR_GOOD_PP2V5

TURN_ON_VTT

PWR_GOOD_SB_CORE

SMU_PWRSEQ_P1_2

SMU_PWRSEQ_P9_6

SMU_PWRSEQ_P9_5

SMU_PWRSEQ_P1_1

SMU_PWRSEQ_P1_0

TURN_ON_SHASTA_CORE_L

TURN_ON_PP1V2_L

COMPARE_SB_CORE

PP1V2_PWRON_SB_VCORE

RAIL_CTL_NEG

PS_2V_REF

COMPARE_PP2V5

CPU_AVDD_EN

PP5V_RUN_CPU

U1100

12

8

9

14

3

U1100

12

6

7

1

3

R330

1 2

C330

1

2

R340

1 2

C340

1

2

R342

1

2

R343

1

2

R341

1

2

R331

1

2

46

13

13

13

13

13 10

10 10

23 10

6

11

31

36 31 30

7 6

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

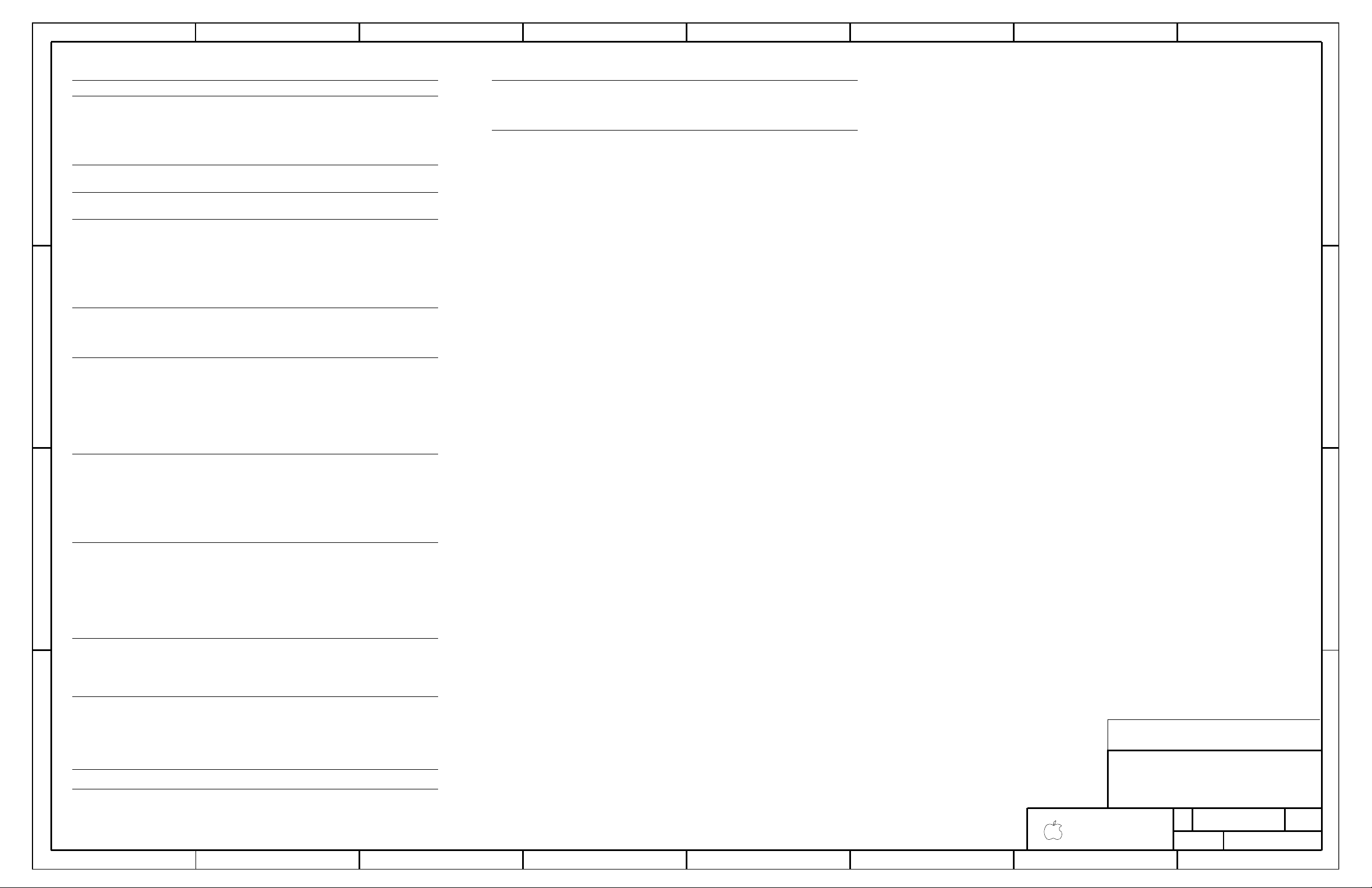

CHECKIN 12005

CHECKIN 12004

NO_TEST, FUNC_TEST UPDATES

11/17/03

CHANGED J8303 TO 5 PIN CONNECTOR

CHANGED MICRODASH MODEM HEIGHT AND CHANGED TO DEVELOPMENT BOM OPTION

MIN_LINE_WIDTH AND MIN_NECK_WIDTH UPDATES THROUGHOUT

RELEASE REV 12

ADDED NET_SPACING_TYPE=PROC_DIFF TO DIFF PAIRS THAT DIDN’T HAVE IT

MOVED SERIES TERM FOR PULSAR CLOCKS TO LOGIC ANALYZER PAGE

ADDED 6 OUTPUT CAPS (124-0322) TO CPU VCORE VREG

MASTER PAGE SYNC

CHECKIN 11001

RELEASE REV 11

NO_TEST UPDATES

UPDATED POWER SEQUENCING TO MATCH SMU PINOUT 1.4

ADDED SERIAL SIGNALS TO AIRPORT CARD FOR NEW MARTY CARD

CHANGED SHASTA P/N TO V1.1

11/11/03

11/10/03

NEW CONNECTORS FOR MODEM AND PATA

MASTER PAGE SYNC

CHANGED PULSAR SERIES TERM R2707, R2719, R2701, R2761, R2779 TO 0 OHM

ADDED EMI-SPRING AND TIED TO GND_CHASSIS_MODEM

CHECKIN 10001

REPLACED POWER CONNECTOR

NEW AIRPORT CONNECTOR

ADDED GAP FILLER

MASTER PAGE SYNC

MASTER PAGE SYNC

J8301 PATA CONNECTOR ROTATED 180 DEGREES

CHANGED PULSAR 2.2UF CAPS TO 10%

CHANGED Q1001 TO NTD60N02R

11/04/03

MAIN PROTO RELEASE (REV 10)

CHECKIN 09002

TERMINATION FOR CPU CLOCK NOW TRACKS PP1V2_EI_CPU RAIL

ADDED 5 PULLDOWNS FOR CPU VID SIGNALS

UNCONNECTED THERMAL PAD FOR U9600 HEADPHONE AMP

ADDED 4 SMT NUTS

REPINNED J9240 BLUETOOTH CONNECTOR

BOM CHANGES FOR R2910, R5727, R9139, R9810

11/03/03

CHECKIN 09001

10/15/03

TERMINATION FOR NB CLOCK NOW TRACKS PP1V2_EI_NB RAIL

10/14/03

REVISION HISTORY

DATE

TERMINATION FOR VSP CLOCK NOW TRACKS PP1V2_HT RAIL

10/13/03

CHANGED ALL 4 NB AVDDS TO PP1V5_PWRON_NB_AVDD RAIL

DESCRIPTION

SMU PART# UPDATED

FIREWIRE NET NAME CHANGES TO MATCH NAMING CONVENTION

CHANGED PART NUMBER OF NV18B

MANY MIN_NECK_WIDTH UPDATES

DC-DC UPDATES ON PAGES 9,10,22,33,34,50

UPDATED CRYSTAL CONSTRAINTS

U3600 PIN 6 TO PP5V_RUN

NO STUFFED R1303 BECAUSE WHITE LED IS ACTIVE HIGH

CHANGED ZH700 AND ZH701 TO HOL-315R138

LED3002, LED3600, AND LED800 CHANGED TO D3002, D3610, AND D810 P/N 378S0042

11/13/03

ADDED NET_SPACING_TYPE=PROC_DIFF TO TDIODE_POS, TDIODE_NEG, KPVDD2, AND KPGND2

ADDED LEDS FOR 5V ALL RAIL AND PANEL POWER

CHANGED U3LITE P/N TO V1.1

PULSAR SERIES TERM - CHANGED R2705,R2711,R2702 TO 0 OHM. R2770 -> 20 OHM

CHANGED CRYSTAL Y5700 TO 197S0026

CHANGED 20" INVERTER TO 518-0141

PLL-LOCK LED CHANGED TO GREEN

DC/DC NET NAME FIXES ON PAGES 9,10,22

CHECKIN 11002 - EVT DESIGN REVIEW

11/14/03

PIN SWAPPED L5908 FOR ROUTING

CHANGED 20" INVERTER DECOUPLING TO TWO 1UF 1210 CAPS

ADDED ECSET FOR PLS_EXTCLK NET. DROPPED PROP DELAY FROM OTHER CRYSTALS

R2742 CHANGED TO 806 OHM

11/15/03

CPU POWER SUPPLY FETS - VISHAY USED ON SAMSUNG BOMS AND ON SEMI ON HYNIX BOMS

INPUT AND OUTPUT CERM CAPS MARKED AS CRITICAL

CHANGED INPUT CAPS TO 124-0323

BOMOPTIONS AND SCHEMATIC CLEANUP TO AGP (BUSY, STOP, TYPEDET, GCDET)

ADDED MORE POWER AND GROUND SHORTS FOR AUDIO

MASTER PAGE SYNC

ALIASED PP5V_AUDIO TO PP5V_RUN RAIL

NEW LARGER CAP FOR VTT VREG. C4609 CHANGED TO 128S0022. C4608 NOSTUFFED

ADDED CIRCUIT SO 5V RAIL TO 17" INVERTER COMES UP AFTER 12V

CHANGED MODEM STANDOFFS TO 862-0035 AND ADDED ELECTRICAL CONNECTIONS

ADDED TWO MORE SMT NUTS FOR CPU HEATSINK

CHANGED LED700,701,702,5900,8301,8700,8701,8702 AND D3001 TO 378S0045

CHECKIN 12001

CHANGED DS870X TO LED870X TO FOLLOW CONVENTION

CHANGED PCI_CLK33M_SB_EXT NET NAME ON PAGE 27 FOR REUSE. ALIAS ADDED ON PAGE 8

MASTER PAGE SYNC

11/17/03

CHECKIN 12003

11/18/03

STUFFED TMDS INDUCTORS AND NOSTUFFED 0 OHM RESISTORS

CHANGED CRYSTAL FILTERING FOR PULSAR

ADDED CAPS TO GROUND FOR CPU HEATSINK SMT NUTS

CHASSIS MODEM NO LONGER TIES TO REST OF CHASSIS

MOVED RAM_CKE SIGNALS TO 62 OHM VTT PARALLEL TERM WITH 4.7K PULL-DOWN

ADDED POWER SEQUENCING FOR VTT VREG

MASTER PAGE SYNC

MASTER PAGE SYNC

CHECKIN 12002

SWAPPED EI_CPU_TO_NB_AD17 WITH EI_CPU_TO_NB_AD24 ON J1400

10/08/03

POWER BUTTON CONNECTOR SYMBOL UPDATED

CHANGED XW3302 TO LAYER 6 SHORT

STUFFING CHANGES FOR ETHERNET RESET

UPDATED CRITICAL LIST

CHANGE Y5700 TO 4 PIN CRYSTAL

11/20/03

CHANGED R2700 TO 22OHM AND NOSTUFFED

CPU VID SET TO 1.475V

J1400 CHANGED TO NOSTUFF

11/19/03

CHANGED HALF OF DIMM AND VTT DECOUPLING TO 1UF

PROTO RELEASE (REV 09)

EVT1 RELEASE (REV 13)

994

13

051-6482

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

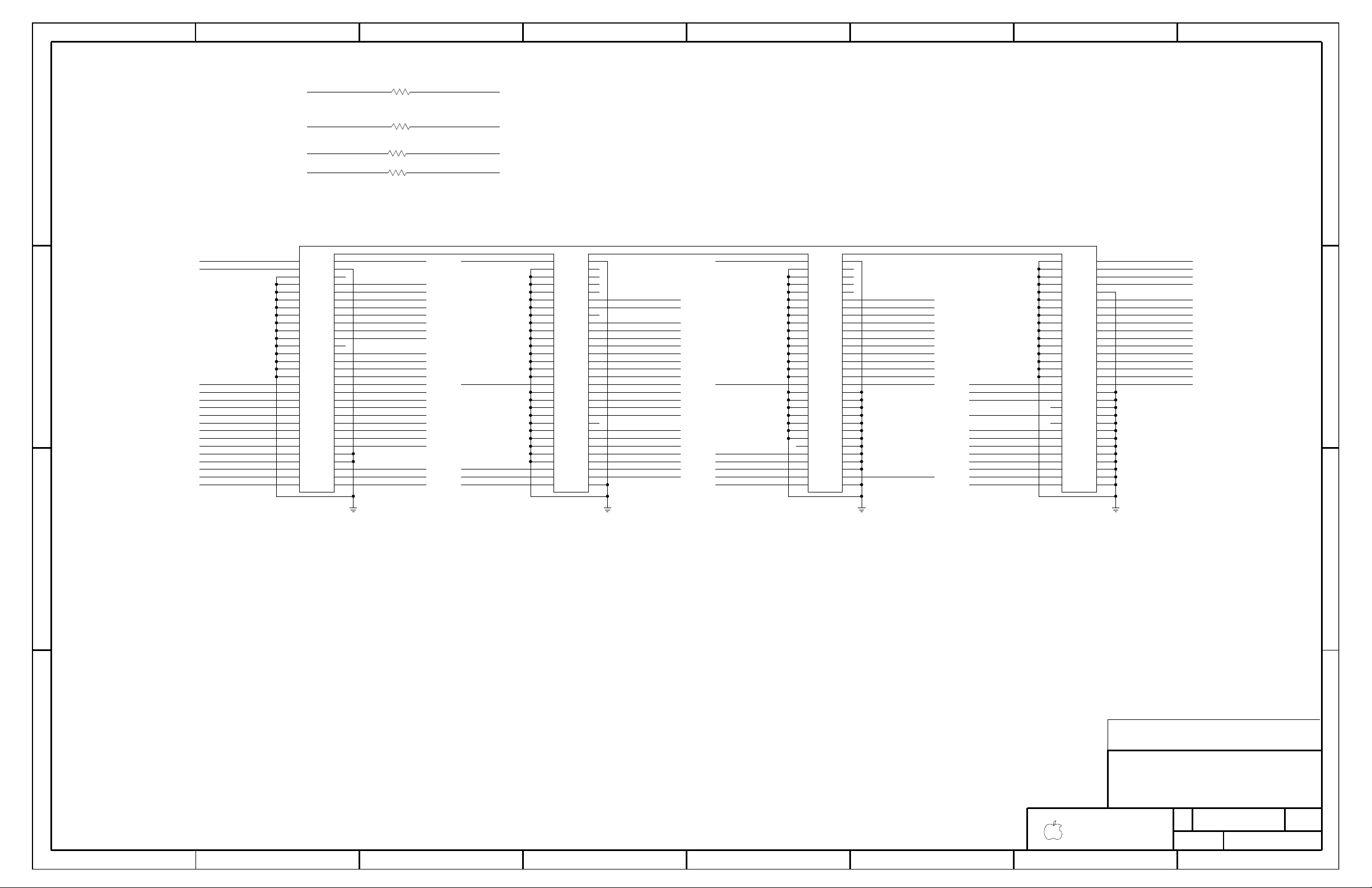

2 TEST POINTS

2 TEST POINTS

2 TEST POINTS

2 TEST POINTS

5 TEST POINTS

5 TEST POINTS

5 TEST POINTS

5 TEST POINTS

12 TEST POINTS

5 TEST POINTS

5 TEST POINTS

10 TEST POINTS

2 TEST POINTS

2 TEST POINTS

2 TEST POINTS

2 TEST POINTS

2 TEST POINTS

FUNC TEST

I10

I295

I296

I297

I298

I299

I3

I300

I302

I307

I311

I314

I315

I316

I317

I319

I320

I321

I322

I323

I336

I337

I338

I339

I340

I341

I342

I343

I344

I345

I346

I347

I348

I349

I350

I352

I354

I355

I356

I357

I358

I359

I360

I361

I362

I363

I364

I365

I371

I372

I373

I374

I375

I376

I377

I378

I379

I380

I381

I382

I383

I384

I385

I386

I387

I388

I389

I390

I391

I392

I393

I394

I395

I396

I397

I398

I399

I4

I400

I401

I402

I403

I404

I405

I406

I407

I408

I426

I428

I429

I430

I431

I432

I433

I434

I435

I436

I437

I438

I439

I440

I441

I442

I443

I444

I445

I446

PP5V_ALL

I5

PP12V_RUN

PP5V_RUN

I6

PP3V3_PWRON

PP5V_PWRON

PP2V5_RUN

PP1V5_RUN

PP1V2_PWRON

PP3V3_RUN

I7

PP24V_RUN

I781

I8

I9

051-6482

99

6

13

FUNC_TEST=TRUE

PP5V_ALL

FUNC_TEST=TRUE

PP12V_RUN

FUNC_TEST=TRUE

PP5V_RUN

GND

FUNC_TEST=TRUE

FUNC_TEST=TRUE

PP3V3_PWRON

FUNC_TEST=TRUE

PP5V_PWRON

FUNC_TEST=TRUE

PP2V5_RUN

FUNC_TEST=TRUE

PP1V5_RUN

FUNC_TEST=TRUE

PP1V2_PWRON

FUNC_TEST=TRUE

PP3V3_RUN

FUNC_TEST=TRUE

PP24V_RUN

FUNC_TEST=TRUE

GND_CHASSIS_TMDS

FUNC_TEST=TRUE

TD0M

FUNC_TEST=TRUE

ANALOG_HSYNC_L

FUNC_TEST=TRUE

ANALOG_VSYNC_L

FUNC_TEST=TRUE

FILT_ANALOG_BLU

FUNC_TEST=TRUE

FILT_ANALOG_RED

FUNC_TEST=TRUE

FILT_ANALOG_GRN

FUNC_TEST=TRUE

INV_20_LCD_PWM_

FUNC_TEST=TRUE

PP24V_INV

FUNC_TEST=TRUE

GND_20_INV

FUNC_TEST=TRUE

MON_DETECT

FUNC_TEST=TRUE

DDC_VCC_5

FUNC_TEST=TRUE

VGA_IIC_DAT

FUNC_TEST=TRUE

INV_17_LCD_PWM_F

FUNC_TEST=TRUE

LAMP_STS_F

FUNC_TEST=TRUE

PP5V_AGP_RL

FUNC_TEST=TRUE

PP12V_INV

FUNC_TEST=TRUE

GND_17_INV

FUNC_TEST=TRUE

INV_20_CUR_HI_F

FUNC_TEST=TRUE

CORE_ISNS_P

FUNC_TEST=TRUE

TDIODE_NEG_FMAX

FUNC_TEST=TRUE

CORE_ISNS_M

FUNC_TEST=TRUE

TDIODE_POS_FMAX

FUNC_TEST=TRUE

KPVDD2_FMAX

FUNC_TEST=TRUE

KPGND2_FMAX

TP_BUF_RST

NO_TEST=TRUE

TP_FRWRLPS

NO_TEST=YES

NO_TEST=YES

TP_DFPCLK_L

NO_TEST=TRUE

TP_DFPD0

NO_TEST=TRUE

TP_PSYNCOUT

TP_USB2_PWREN<4>

NO_TEST=TRUE

TP_PSRO1

NO_TEST=TRUE

NO_TEST=TRUE

TP_PSRO2

TP_EXT_TMDS_D1M

NO_TEST=YES

TP_EXT_TMDS_D2P

NO_TEST=YES

TP_EXT_TMDS_D1P

NO_TEST=YES

TP_EXT_TMDS_D0P

NO_TEST=YES

TP_EXT_TMDS_D0M

NO_TEST=YES

TP_EXT_TMDS_CKP

NO_TEST=TRUE

TP_EXT_TMDS_CKM

NO_TEST=YES

TP_DFPD3

NO_TEST=YES

TP_DFPD2

NO_TEST=TRUE

TP_VIPHCLK

NO_TEST=TRUE

TP_PROC_TRIGGER_OUT

NO_TEST=TRUE

NO_TEST=TRUE

TP_DFPD1

NO_TEST=YES

TP_DFPCLK

NO_TEST=TRUE

TP_USB2_PWREN<3>

NO_TEST=TRUE

TP_USB2_PWREN<2>

FUNC_TEST=TRUE

I2C_UDASH_SCL

FUNC_TEST=TRUE

I2S1_RESET_L

FUNC_TEST=TRUE

I2S1_SB_TO_DEV_DTO

FUNC_TEST=TRUE

I2S1_DEV_TO_SB_DTI

FUNC_TEST=TRUE

PCI_SLOTA_INT_L

FUNC_TEST=TRUE

PP5V_USB2_PORT2_F

FUNC_TEST=TRUE

UDASH_RESET_L

FUNC_TEST=TRUE

TD1M

FUNC_TEST=TRUE

TD0P

FUNC_TEST=TRUE

PPVCC_TMDS

FUNC_TEST=TRUE

PP3V3_ALL_SMU

FUNC_TEST=TRUE

PPVCORE_NB

FUNC_TEST=TRUE

ANALOG_GRN

FUNC_TEST=TRUE

AUDIO_LI_DETECT_L

FUNC_TEST=TRUE

UATA_DA<2..0>

FUNC_TEST=TRUE

UATA_CS0_L

FUNC_TEST=TRUE

UATA_RESET_L

FUNC_TEST=TRUE

UATA_CS1_L

FUNC_TEST=TRUE

UATA_DSTROBE_R

FUNC_TEST=TRUE

UATA_STOPUATA_STOP

FUNC_TEST=TRUE

UATA_HSTROBE

FUNC_TEST=TRUE

UATA_DMACK_L

FUNC_TEST=TRUE

UATA_DMARQ_R

FUNC_TEST=TRUE

UATA_IOCS16_PU

FUNC_TEST=TRUE

PP5V_DISK

FUNC_TEST=TRUE

PP12V_DISK

FUNC_TEST=TRUE

CPU_VID_R<5..0>

FUNC_TEST=TRUE

INV_17_CUR_HI_F

FUNC_TEST=TRUE

UATA_INTRQ_R

FUNC_TEST=TRUE

TCKP

FUNC_TEST=TRUE

UATA_CSEL_PD

FUNC_TEST=TRUE

TD1P

FUNC_TEST=TRUE

SYS_POWERFAIL_L

FUNC_TEST=TRUE

PCI_TRDY_L

FUNC_TEST=TRUE

PCI_SLOTA_IDSEL

FUNC_TEST=TRUE

PCI_IRDY_L

FUNC_TEST=TRUE

PCI_STOP_L

FUNC_TEST=TRUE

PCI_DEVSEL_L

FUNC_TEST=TRUE

PCI_PAR

NO_TEST=YES

TP_TMDS_TXD3M

TP_AGP_MB_AGP8X_DET_L

NO_TEST=TRUE

FUNC_TEST=TRUE

USB_BT_P

TP_ATTENTION

NO_TEST=TRUE

NO_TEST=TRUE

TP_GPU_INTB_L

TP_EXT_TMDS_D2M

NO_TEST=YES

TP_DFPD6

NO_TEST=YES

TP_DFPD5

NO_TEST=TRUE

NO_TEST=TRUE

TP_IFP1VREF

NO_TEST=TRUE

TP_NVAGP_TDO

NO_TEST=YES

TP_TMDS_TXD7P

TP_ENET_CLK125M_GTX

NO_TEST=TRUE

NO_TEST=TRUE

TP_ENET_TXD<7>

NO_TEST=TRUE

TP_AFN

NO_TEST=TRUE

TP_FW_CLK98M_LCLK

NO_TEST=TRUE

TP_ENET_TXD<5>

NO_TEST=TRUE

TP_ENET_TXD<4>

TP_NEC_NANDTEST

NO_TEST=TRUE

NO_TEST=TRUE

TP_NEC_AMC

NO_TEST=TRUE

TP_NEC_NTEST1

TP_NEC_SMI_L

NO_TEST=TRUE

NO_TEST=TRUE

TP_NEC_SMC

NO_TEST=TRUE

TP_NEC_SRDATA

NO_TEST=TRUE

TP_NEC_SRCLK

NO_TEST=TRUE

TP_NEC_SRMOD

NO_TEST=TRUE

TP_NEC_TEST

NO_TEST=TRUE

TP_NEC_TEB

NO_TEST=TRUE

TP_PLS_CLK_66M_0

NO_TEST=TRUE

TP_PLS_CLK_66M_1

FUNC_TEST=TRUE

PP5V_USB2_PORT1_F

FUNC_TEST=TRUE

ROM_CS_L

FUNC_TEST=TRUE

PCI_RESET_L

FUNC_TEST=TRUE

AIRPORT_CLKRUN_L_PD

FUNC_TEST=TRUE

ROM_WE_L

FUNC_TEST=TRUE

ROM_OE_L

FUNC_TEST=TRUE

PCI_FRAME_L

FUNC_TEST=TRUE

PCI_SLOTA_GNT_L

FUNC_TEST=TRUE

PCI_SLOTA_REQ_L

FUNC_TEST=TRUE

PCI_CLK33M_AIRPORT

FUNC_TEST=TRUE

FW_VGND

FUNC_TEST=TRUE

FW_TPI2N

FUNC_TEST=TRUE

FW_TPI2P

FUNC_TEST=TRUE

FW_TPO2P

FUNC_TEST=TRUE

FW_VP_PORT2

FUNC_TEST=TRUE

FW_TPI1N

FUNC_TEST=TRUE

FW_TPI1P

FUNC_TEST=TRUE

FW_TPO1P

FUNC_TEST=TRUE

UDASH_SDOWN

FUNC_TEST=TRUE

USB_BT_N

FUNC_TEST=TRUE

I2S1_SYNC

FUNC_TEST=TRUE

VGA_IIC_CLK

FUNC_TEST=TRUE

TMDS_DDC_CLK

FUNC_TEST=TRUE

TMDS_DDC_DAT

FUNC_TEST=TRUE

TCKM

FUNC_TEST=TRUE

TD2M

FUNC_TEST=TRUE

USB_UDASH_N

FUNC_TEST=TRUE

PP5V_USB2_PORT3_F

FUNC_TEST=TRUE

USB2_PORT2_N_F

FUNC_TEST=TRUE

PP3V3_DDC

FUNC_TEST=TRUE

UDASH_I2C_A1_PU

TP_PLS_REF_CML

NO_TEST=TRUE

TP_PLS_TEST1

NO_TEST=TRUE

TP_PLS_TEST2

NO_TEST=TRUE

TP_PLS_TEST3

NO_TEST=TRUE

TP_SB_FSTEST

NO_TEST=TRUE

TP_SB_PLLTEST

NO_TEST=TRUE

TP_VREF_CG

NO_TEST=TRUE

TP_SB_NC_P7

NO_TEST=TRUE

TP_SB_NC_P8

NO_TEST=TRUE

TP_SB_NC_R3

NO_TEST=TRUE

TP_SB_NC_R4

NO_TEST=TRUE

NO_TEST=TRUE

TP_SB_NC_R5

NO_TEST=TRUE

TP_SB_NC_R6

TP_SB_NC_R7

NO_TEST=TRUE

NO_TEST=TRUE

TP_SB_NC_R8

TP_SB_NC_T1

NO_TEST=TRUE

TP_SB_NC_T2

NO_TEST=TRUE

NO_TEST=TRUE

TP_SB_NC_T3

NO_TEST=TRUE

TP_SB_NC_T5

NO_TEST=TRUE

TP_SB_NC_T4

TP_SB_NC_T6

NO_TEST=TRUE

NO_TEST=TRUE

TP_SB_NC_T7

TP_SB_NC_T8

NO_TEST=TRUE

TP_SB_NC_U2

NO_TEST=TRUE

TP_SB_NC_U1

NO_TEST=TRUE

TP_SB_NC_U3

NO_TEST=TRUE

TP_SB_NC_U4

NO_TEST=TRUE

NO_TEST=TRUE

TP_SB_NC_U5

NO_TEST=TRUE

TP_SB_NC_U6

NO_TEST=TRUE

TP_SB_NC_V1

TP_SB_NC_V2

NO_TEST=TRUE

TP_SB_NC_V4

NO_TEST=TRUE

TP_SB_NC_V3

NO_TEST=TRUE

TP_SB_NC_W1

NO_TEST=TRUE

TP_SB_NC_W3

NO_TEST=TRUE

TP_SB_NC_Y1

NO_TEST=TRUE

FUNC_TEST=TRUE

TDIODE_NEG

FUNC_TEST=TRUE

TP_AIRPORT_RF_DISABLE

FUNC_TEST=TRUE

TP_AIRPORT_PME_L

NO_TEST=TRUE

TP_SB_NC_Y3

NO_TEST=TRUE

TP_SATA_CLK25M

TP_ENET_TCK

NO_TEST=TRUE

TP_USB2_PWREN<1>

NO_TEST=TRUE

TP_USB2_PWREN<0>

NO_TEST=TRUE

TP_DUMMY_A

NO_TEST=TRUE

NO_TEST=TRUE

TP_DUMMY_B

NO_TEST=TRUE

TP_RAM_CKE_R<2>

NO_TEST=TRUE

TP_RAM_CKE_R<7>

TP_RAM_CKE_R<3>

NO_TEST=TRUE

NO_TEST=TRUE

TP_RAM_CKE_R<6>

TP_RAM_CS_L_R<10>

NO_TEST=TRUE

TP_RAM_MUXEN0

NO_TEST=TRUE

TP_RAM_CS_L_R<3>

NO_TEST=TRUE

TP_RAM_CS_L_R<2>

NO_TEST=TRUE

TP_RAM_CS_L_R<11>

NO_TEST=TRUE

TP_RAM_MUXEN4

NO_TEST=TRUE

TP_NB_PM_SLEEP0

NO_TEST=TRUE

TP_J4000_SJRESET_L

NO_TEST=TRUE

FUNC_TEST=TRUE

FW_TPO1N

FUNC_TEST=TRUE

AUDIO_LO_DET_L

FUNC_TEST=TRUE

I2C_UDASH_SDA

FUNC_TEST=TRUE

USB2_PORT2_P_F

FUNC_TEST=TRUE

USB2_PORT1_P_F

FUNC_TEST=TRUE

USB2_PORT1_N_F

FUNC_TEST=TRUE

FW_TPO2N

FUNC_TEST=TRUE

FW_VP_PORT1

FUNC_TEST=TRUE

PCI_CBE_L<3..0>

FUNC_TEST=TRUE

PCI_AD<31..0>

FUNC_TEST=TRUE

VCORE_SENSE_GND

FUNC_TEST=TRUE

PP5V_RUN_CPU

FUNC_TEST=TRUE

PPVCORE_CPU

FUNC_TEST=TRUE

SMU_MANUAL_RESET_L

FUNC_TEST=TRUE

RESET_BUTTON_L

FUNC_TEST=TRUE

SMU_RESET_L

FUNC_TEST=TRUE

PP1V2_PWRON_SB_VCORE

FUNC_TEST=TRUE

ANALOG_BLU

FUNC_TEST=TRUE

POWER_BUTTON_L

FUNC_TEST=TRUE

PP12V_CPU

FUNC_TEST=TRUE

USB2_PORT3_P_F

FUNC_TEST=TRUE

USB2_PORT3_N_F

NO_TEST=TRUE

TP_TMDS_TXD7M

NO_TEST=YES

TP_TMDS_TXD3P

NO_TEST=TRUE

TP_GPU_THERMC

NO_TEST=TRUE

TP_GPU_THERMA

NO_TEST=TRUE

TP_FBBCS1_L

FUNC_TEST=TRUE

TD2P

FUNC_TEST=TRUE

USB_UDASH_P

FUNC_TEST=TRUE

MODEM_RING2SYS_L

FUNC_TEST=TRUE

I2S1_MCLK

TP_J4001_SJRESET_L

NO_TEST=TRUE

TP_CMP_SPARE

NO_TEST=TRUE

NO_TEST=TRUE

TP_ENET_TXD<6>

U2100_UNUSED

NO_TEST=TRUE

FUNC_TEST=TRUE

ROM_ONBOARD_CS_L

FUNC_TEST=TRUE

UATA_DD<15..0>

FUNC_TEST=TRUE

ROM_WP_L

FUNC_TEST=TRUE

SYS_POWERUP_L

FUNC_TEST=TRUE

SYS_POWER_BUTTON_L

FUNC_TEST=TRUE

VCORE_SENSE_VOUT

FUNC_TEST=TRUE

SYS_SLEEP

FUNC_TEST=TRUE

EXT_POWER_BUTTON_L

FUNC_TEST=TRUE

U900_FEEDBACK

FUNC_TEST=TRUE

U2200_FEEDBACK

FUNC_TEST=TRUE

ANALOG_RED

FUNC_TEST=TRUE

I2S1_BITCLK

11

7

11

27 18 11

18 11

11

59

7

59

59 57 56

59 57 56

59

59

59

59

59

59

59 58

59

59

59

59

59

59

59

59

36 33

36

36 33

36

36

36

57

58

58

58

29

92

29

29

58

58

58

58

58

58

58

58

58

57

29 14

58

58

92

92

94 18

94 25

94 76 25

94 76 25

76 25

92

94 25

59

59

59

22

7

59 57

83 80

83 80

83 80

83 80

83

83 80

6

83 80

6

83 80

83 80

83

83

83

7

83

7

33

8

59

83

59

83

59

13

8

77 76 74

76

77 76 74

77 76 74

77 76 74

77 76 74

58

48

92

29

49

58

58

58

58

49

58

87

87

29

90

87

87

77

77

77

77

77

77

77

77

77

77

27

27

92

76 75 74

77 76 75 74 51 49

76

76 75 74

76 75 74

77 76 74

76 74

76 74

8

90

90

90

90

90

90

90

90

94 25

92

94 25

59

59

59

59

59

94

92

92

59

94 27

27

27

27

25

25

48

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

36 31

76

76

91

27

87

92

92

24

24

37

37

37

37

37

37

37

37

37

37

24

40

90

98 25

94 18

92

92

92

90

90

77 76 74

77 76 75 74

33

36 31 30

7 3

36 35 34 33 32 31 29

7

13

8 7

7

13

8

23 10

3

59 57

7

34 33

92

92

58

58

58

58

52

59

94

94 25

94 25

40

36

87

21

76 75

83 80

75

33 13 11 10

7

13

7

33

50 46 27 11 10

9 8

13

9

22

59 57

94 25

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

125

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

IN

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

SILKSCREEN:2

GND RAILS

SILKSCREEN:1

PIN 13,19,11,22 ARE DIFFERENCE FROM ATX .

RESET

SMU RESET

CHASSIS GND

ALWAYS ON WHEN UNIT HAS AC POWER (TRICKLE)

ALWAYS ON (TRICKLE)

ONLY ON IN RUN

RUN RAILS

POWER CONN / ALIAS

ON IN RUN AND SLEEP

POWER

P/N 518-0137

SILKSCREEN:POWER

ALL RAILS

PWRON RAILS

SILKSCREEN:RUN

RTC BATTERY

PP3V3_RUN

PP5V_RUN

PP3V3_PWRON

PP1V5_PWRON

PP2V5_PWRON

PP3V3_RUN

PP1V2_PWRON

PP24V_RUN

PP5V_ALL

PP5V_ALL

PP3V3_RUN

PP2V5_PWRON

PP2V5_RUN

PP5V_PWRON

PP1V5_RUN

PP1V5_PWRON

PP5V_RUN

PP3V3_RUN

PP5V_RUN

PP12V_RUN

SM

SM

PP12V_RUN

315R138

SM

SM

0.1UF

20%

10V

CERM

402

0.1UF

20%

10V

CERM

402

PP12V_RUN

PP3V3_ALL

5%

1/16W

402

10K

MF

SPST

DEVELOPMENT

SM

1/16W

MF

402

1K

5%

SPST

DEVELOPMENT

SM

5%

402

1K

1/16W

MF

SPST

SM

PP24V_RUN

EMI-SPRING

SC57

315R138

160R138

6.00MM-PTH

225R125

1/16W

MF

402

5%

1K

SHLD-IO-CONN

Q45-TH

MBR0530

SM

805

FF

1/10W

5%

0

805

FF

1/10W

5%

0

805

FF

1/10W

5%

0 0

5%

1/10W

FF

805

NOSTUFF

0

5%

1/10W

FF

805

NOSTUFF

805

FF

1/10W

5%

0

PP1V2_RUN

TSSOP

74LCX125

CRITICAL

402

CERM

10V

20%

0.1UF

SYS_PWR_BTN_FILT

FERR-EMI-100-OHM

SM

SM

FERR-EMI-100-OHM

DEVELOPMENT

GREEN

2.0X1.25

GREEN

2.0X1.25

PP3V3_PWRON

1/16W

5%

MF

330

603

GREEN

2.0X1.25

43215-0012

F-RT-TH

CRITICAL

SM

SM

SM

SM

PWR-BUTT

ST-SM

PP12V_RUN

PP5V_RUN

PP3V3_RUN

MF

5%

1/16W

330

603

CERM

402

10V

20%

0.1UF

1/16W

5%

MF

DEVELOPMENT

330

603

PP5V_ALL

NOSTUFF

2512

FF

1W

5%

0

CRITICAL

BB10209-A5

TH

051-6482

997

13

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=10MIL

VOLTAGE=0V

MIN_NECK_WIDTH=8MIL

MIN_LINE_WIDTH=25MIL

VOLTAGE=3.3V

VOLTAGE=5V

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

MAKE_BASE=TRUE

MIN_LINE_WIDTH=25MIL

VOLTAGE=3.3V

MIN_NECK_WIDTH=10MIL

MAKE_BASE=TRUE

MIN_NECK_WIDTH=10MIL

MAKE_BASE=TRUE

VOLTAGE=1.5V

MIN_LINE_WIDTH=25MIL

MIN_LINE_WIDTH=25MIL

VOLTAGE=3.3V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=10MIL

MAKE_BASE=TRUE

VOLTAGE=1.2V

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

MAKE_BASE=TRUE

MAKE_BASE=TRUE

VOLTAGE=2.5V

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

MAKE_BASE=TRUE

VOLTAGE=2.5V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=10MIL

VOLTAGE=5V

MIN_LINE_WIDTH=25MIL

VOLTAGE=1.5V

MAKE_BASE=TRUE

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

VOLTAGE=12V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

VOLTAGE=24V

MAKE_BASE=TRUE

VOLTAGE=1.2V

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

MAKE_BASE=TRUE

MIN_NECK_WIDTH=10MIL

VOLTAGE=12V

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

MAKE_BASE=TRUE

VOLTAGE=5V

MIN_NECK_WIDTH=8MIL

MAKE_BASE=TRUE

MIN_LINE_WIDTH=25MIL

VOLTAGE=3.3V

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

VOLTAGE=5V

PP5V_ALL

PP24V_GRAPHICS

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=15MIL

GND_CHASSIS_AUDIO_EXTERNAL

VOLTAGE=0

MAKE_BASE=TRUE

GND_CHASSIS_VGA

PP12V_AUDIO_CODEC

PP12V_AUDIO_SPKRAMP

PP5V_AUDIO

PP5V_RUN_CPU

PP5V_AGP

GND_AUDIO_SPKRAMP

GND_AUDIO

PP12V_DISK

PP12V_AGP

ITS_PLUGGED_IN

ITS_RUNNING

PP3V3_ALL

_PP2V5_PWRON_SB

_PP3V3_PWRON_SB

GND_CHASSIS_LED

PPVCORE_PWRON_PULSAR

PP1V5_PWRON_NB_AVDD

GND_CHASSIS_TMDS

VOLTAGE=0

MIN_NECK_WIDTH=15MIL

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

VOLTAGE=3.3V

_PP3V3_ALL_RTC PP3V3_ALL_BATT_SAFETY

VOLTAGE=3.3V

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

PP3V3_ALL_BATT

VOLTAGE=3.3V

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

PPVCORE_CPU

PPVCORE_NB

PP1V2_HT

PP1V2_PULSAR

PPVCORE_PULSAR

PP1V5_AGP

_PP3V3_PCI

_PPVIO_PCI_USB2

_PP3V3_SB_PCI

PP3V3_AUDIO

PP3V3_RUN_CPU

PP3V3_AGP

PP3V3_PWRON_CPU

PP5V_PWRON_CPU

_PP3V3_PWRON_MODEM

_PP5V_PWRON_USB

_PP5V_PWRON_UDASH

_PP3V3_PWRON_BT

_PP3V3_PWRON_UDASH

PP3V3_PWRON_ENET

_PP3V3_PWRON_USB

_PP1V2_PWRON_SB

_PP1V2_PWRON_DISK_SB

_PP1V2_PWRON_HT

_PP2V5_PWRON_HT

PP2V5_HT

PP2V5_PWRON_RAM

_PP3V3_ALL_SMU

PP3V3_FW

PP24V_FW

_PPPCI64_PWRON_SB

_PPPCI32_PWRON_SB

PP5V_PATA

PP5V_DISK

PP2V5_GPU

PP2V5_RUN_CPU

PP2V5_RUN_RAM

PP2V5_RAM

VOLTAGE=1.2V

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

PP1V2_EI_NB

PP1V2_EI_CPU

VOLTAGE=1.2V

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

SMU_MANUAL_RESET_L

POWER_BUTTON_L

SYS_POWER_BUTTON_L

SYS_RESET_BUTTON_L

SYS_POWERUP_L

GND_CHASSIS_17_INCH_INVERTER

VOLTAGE=0

MIN_NECK_WIDTH=20MIL

MIN_LINE_WIDTH=20MIL

GND_CHASSIS_20_INCH_INVERTER

VOLTAGE=0

MIN_NECK_WIDTH=20MIL

MIN_LINE_WIDTH=20MIL

GND_CHASSIS_AUDIO_INTERNAL

MAKE_BASE=TRUE

SYS_POWER_BUTTON_L

VOLTAGE=3.3V

MIN_LINE_WIDTH=25MIL

MAKE_BASE=TRUE

PP3V3_ALL

MIN_NECK_WIDTH=10MIL

GND_CHASSIS_USB

GND_CHASSIS_FIREWIRE

PP12V_RUN_CPU

PP3V3_PATA

PP3V3_DISK

RESET_BUTTON_L

ITS_ALIVE

GND_SYS_PWR_BTN_FILT

SYS_POWERUP_L_BUF

POWER_GOOD

GND_CHASSIS_RJ45

VOLTAGE=0

MIN_NECK_WIDTH=15MIL

MIN_LINE_WIDTH=25MIL

R710

1 2

C703

1

2

R701

1 2

R707

1 2

J702

21

XW700

1 2

XW701

1 2

ZH700

1

XW702

1 2

XW703

1 2

C704

1

2

C705

1

2

R714

1

2

SW702

1 2

3 4

R713

1 2

SW701

1 2

3 4

R712

1 2

SW700

1 2

3 4

EMI700

1

ZH701

1

ZH702

1

ZH703

1

ZH704

1

R702

1 2

SH700

1

2 3

4

DS700

12

R703

1 2

R704

1 2

R705

1

2

R706

1

2

R708

1

2

R709

1

2

U700

2

7 1

14

3

C700

1

2

L700

1 2

L701

1 2

LED701

1

2

LED702

1

2

R700

1 2

LED700

1

2

J700

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

3

4

5

6

7

8

9

XW704

1 2

XW705

1 2

XW706

1 2

XW707

1 2

SW703

3

1

2

11

6

59

98

59

99

97

98

36 31 30

6 3

59 50 49

99 97

99

83

6

59 50

11

7

88 74 25 23

25 23

21

26

60 48 37 28

59

6

13

36 35 34 33 32 31 29

6

22

6

60 24

26

26

49 48

77 76 75 74 25

77

74

99 98 97 95

33

59 58 57 56 52 51 50 49 48

36

36

94

92

94

92

94

87

91

25

80

62

62

64 60

40

13

8

90

90

23

23

83

83

6

55 54 52

31

46 45 44

37 26

28 18 35 31 30 29 18

13

8 6

6

13

7 6

13

33 13 11 10

6

59

59

98

13

7 6

11

7

92

90

33

83

83

6

8

87

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

125

125

125

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_11_HEAD

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

TABLE_11_HEAD

REFERENCE DESIGNATOR(S)

BOM OPTION

QTY

DESCRIPTION

VALUE VOLT. WATT.

TOL.PART #

PACKAGE

DEVICE

TABLE_11_HEAD

TABLE_11_HEAD

TABLE_5_ITEM

TABLE_11_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_5_ITEM

CPU VID<0:5>

VID SET TO 1.475V TO ACHIEVE 1.45V AT PROCESSOR

SMU

NOTE:PULL UP CPU_VID<5>TO

2.2V FOR CPU VRM10.

998-0269

CONNECTOR

DOWNLOAD

(SMU_BOOT_EPM)

THESE PINS HAVE INTERNAL PULLUPS

PULSAR ERROR_L LED

SHASTA JTAG

PULL DOWN

SIGNAL ALIAS

PCI CLOCKS

CHEAPER SMU RESET

518S0104

CPU HEATSINK SMT NUTS

CONNECTION

POWER_FAIL_L

SMU ANALOG VREF

MISC PARTS

ALTERNATE FOR SERIAL NUMBER LABEL

NEED TO ADD THERMAL GREASE TO MLB BOM

5%

402

MF

10K

1/16W

402

100

MF

1/16W

5%

DEVELOPMENT

ST-HDR-HI-TEMP

TH

DEVELOPMENT

402

1/16W

10K

MF

5%

MF

5%

402

1/16W

10K

DEVELOPMENT

5%

MF

10K

1/16W

402

402

MF

1/16W

5%

0

NOSTUFF

1K

402

MF

1/16W

5%

NOSTUFF

402

CERM

6.3V

10%

1UF

NOSTUFF

SOT23

1N914

NOSTUFF

TSSOP

74LCX125

TSSOP

74LCX125

TSSOP

402

MF

1/16W

5%

4.7K

PP2V5_PWRON

10K

5%

1/16W

MF

402

MF

1/16W

5%

10K

402

MF

1/16W

5%

10K

402

MF

1/16W

5%

10K

402

MF

1/16W

5%

10K

402

NOSTUFF

402

10K

5%

1/16W

MF

402

10K

5%

1/16W

MF

NOSTUFF

402

10K

5%

1/16W

MF

NOSTUFF

402

10K

5%

1/16W

MF

NOSTUFF

402

MF

1/16W

5%

10K

NOSTUFF

PP3V3_RUN

402

10K

5%

1/16W

MF

402

20K

5%

1/16W

MF

HSK-NUT-6.5MMTHHSK-NUT-6.5MM

TH

HSK-NUT-6.5MM

TH

HSK-NUT-6.5MM

TH

DEVELOPMENT

RED

SM

HSK-NUT-6.5MM

THTH

HSK-NUT-6.5MM

CERM

16V

20%

0.01UF

402

CERM

16V

20%

0.01UF

402

CERM

16V

20%

0.01UF

402

CERM

16V

20%

0.01UF

402 402

0.01UF

20%

16V

CERM CERM

16V

20%

0.01UF

402

NOSTUFF

1/16W

402

MF

5%

0

PP3V3_ALL

U.FL-R_SMT

DEVELOPMENT

F-ST-SM

BM12B-SRSS-TB

F-ST-SM

NOSTUFF

1/16W

5%

0

MF

402

NOSTUFF

MF

402

0

5%

1/16W

NOSTUFF

1/16W

0

MF

5%

402

NOSTUFF

402

MF

1/16W

5%

0

NOSTUFF

0

1/16W

MF

5%

402

NOSTUFF

0

1/16W

MF

5%

402

NOSTUFF

DEVELOPMENT

5%

4.7K

402

MF

1/16W

DEVELOPMENT

MF

330

402

1/16W

5%

PP3V3_RUN

337S2787 2.0GHZ

NEO_REV3_2_0GHZ

65W

1 ?

PROCESSOR

1.15V U2900

13

8 99

051-6482

IC,MPU,NEO,10S,REV2,2.0GHZ,70C

2.0GHZ

NEO_REV2_2_0GHZ

65W

CBGA-576-1MM

PROCESSOR

1 ?

1.15V U2900

337S2785

45W

337S2784

U29001.15V

?1

PROCESSOR

CBGA-576-1MM

NEO_REV2_1_8GHZ

1.8GHZ

IC,MPU,NEO,10S,REV2,1.8GHZ,70C

1.8GHZ

PROCESSOR

NEO_REV3_1_8GHZ

45W

U29001.15V

?1

CBGA-576-1MM

337S2786

IC,MPU,NEO,10S,REV3,1.8GHZ,70C

HS_SDF802HS_SDF801HS_SDF800

HS_SDF804 HS_SDF805HS_SDF803

NB_PMR_OBSV

CPU_VID_R<4>

ERROR_LED

CLOCK_ERROR_L

SMU_SLEEP

SMU_BOOT_CE

SMU_BOOT_CNVSS

MAKE_BASE=TRUE

PCI_CLK33M_AIRPORT

_PCI_CLK33M_AIRPORT

MAKE_BASE=TRUE

TP_PCI_CLK_GP1

MAKE_BASE=TRUE

TP_PCI_CLK_P4

PCI_CLK_P4

_PCI_CLK33M_USB2

PCI_CLK_GP0

MAKE_BASE=TRUE

PCI_CLK33M_USB2

JTAG_SB_TRST_L_PP3V3_ALL_SMU

SMU_RESET_L

SMU_MANUAL_RESET_L

JTAG_SB_TDI

JTAG_SB_TCK

TP_JTAG_SB_TDI

MAKE_BASE=TRUE

TP_JTAG_SB_TCK

MAKE_BASE=TRUE

JTAG_SB_TMS

JTAG_SB_TDO

TP_JTAG_SB_TMS

MAKE_BASE=TRUE

TP_JTAG_SB_TDO

MAKE_BASE=TRUE

NB_THMOTP_THMO

MAKE_BASE=TRUE

NB_THMI

TP_NB_THMI

MAKE_BASE=TRUE

PCI_CLK_P3

PCI_CLK_GP1

SMU_WARM_RESET_L SYS_WARM_RESET_L

SYS_SLEEP

SMU_BOOT_RXD

SMU_BOOT_SCLK

SMU_BOOT_BUSY

J802_6

SMU_MANUAL_RESET_L

J802_2

SMU_BOOT_TXD

CPU_VID<3>

CPU_VID<2>

CPU_VID<0>

CPU_VID<5>

CPU_VID<4>

CPU_VID_R<1>

PCI_CLK_P1

MAKE_BASE=TRUE

PCI_CLK33M_SB_EXT

SMU_CHARGE_BATT

NO_TEST=TRUE

MAKE_BASE=TRUE

TP_SMU_CHARGE_BATT

ALS1_OUT

MAKE_BASE=TRUE

TP_ALS1_OUT

ALS0_OUT

TP_ALS0_OUT

MAKE_BASE=TRUE

SMU_PWRSEQ_P1_3

MAKE_BASE=TRUE

TP_SMU_PWRSEQ_P1_3

SMU_PWRSEQ_P1_4

MAKE_BASE=TRUE

TP_SMU_PWRSEQ_P1_4

SMU_ADAPTER_ID

TP_SMU_ADAPTER_ID

MAKE_BASE=TRUE

ALS_GAIN_BOOST

TP_ALS_GAIN_BOOST

MAKE_BASE=TRUE

TP_ACCEL_LOWPWR_L

MAKE_BASE=TRUE

ACCEL_LOWPWR_L

SMU_SPARE_P10_0

MAKE_BASE=TRUE

TP_SMU_SPARE_P10_0

ACCEL_INT_L

MAKE_BASE=TRUE

TP_ACCEL_INT_L

CPU_VID_R<5>

CPU_VID_R<3>

CPU_VID_R<0>

CPU_VID_R<2>

CPU_VID<1>

CBGA-576-1MM

74LCX125

IC,MPU,NEO,10S,REV3,2.0GHZ,70C

5%

1/16W

MF

47

402

PP3V3_ALL

5%

402

MF

10K

1/16W

5%

0

1/16W

MF

402

603

0.47UF

20%

10V

CERM

NOSTUFF

402

MF

1/16W

0

5%

1%

402

MF

1/16W

200

NOSTUFF

SSOT-23

2.5V

NOSTUFF

805

CERM

10V

20%

2.2UF

NOSTUFF

PP3V3_ALL_SMU_AVCC

SYS_POWERFAIL_L

_PPVREF_SMU

GND_SMU_AVSS

POWER_GOOD

PPVREF_SMU_ADC_REF

GND_SMU_AVSS_DAGND

1

062-2082

SPEC,VENDOR PACKAGING PROCEDURE

VPP1

MLB1

PCB,FAB,MLB

820-1540

1

1

LBL1825-2029

LBL,SER #,INP DEV

1

SCH1

PCB,SCHEM,MLB

051-6482

U7500

1

IC,FLASH,1MX8,3.3V,90NS

341T1366

1

742-0048

BT700

BAT,COIN,3V,220MAH,CR2032

1

GAP FILLER

GAP2900

875-1614

PURCH ASSY, SMU BIG

341T1395

1

U1300

1

875-1752

GPU GAP PAD

PAD4900

452-0678

CPU HEATSINK SCREW

SRW800,SRW801,SRW802,SRW803,SRW804,SRW805

6

870-1177

CPU HEATSINK SPRING

6

SPR800,SPR801,SPR802,SPR803,SPR804,SPR805

730-0291

1

CPU HEATSINK

HS2900

COMMON

BAR CODE LABEL

LBL1825-2029825-2808

CRITICAL

CRITICAL

CRITICAL

CRITICAL

CRITICAL

J800

3

2

1

R805

1

2

R812

1

2

R813

1 2

VR801

2 1

3

R818

1

2

C801

1

2

C802

1

2

J803

14131

101112

2345678

9

R819

1 2

R820

1 2

R821

1 2

R822

1 2

R823

1 2

R824

1 2

R801

1

2

R800

1

2

R825

1

2

R826

12

R802

1 2

J802

1

10

2

3 4

5 6

7 8

9

R803

1

2

R807

1

2

R806

1

2

R810

1 2

R815

1

2

C800

1

2

D800

1

3

R828

1 2

U700

5

7 4

14

6

U700

9

7

10

14

8

U700

12

7

13

14

11

R870

1

2

R814

1

2

R816

1

2

R817

1

2

R808

1

2

R809

1

2

R827

1

2

R829

1

2

R830

1

2

R831

1

2

R832

1

2

R804

1

2

R811

1

2

SDF800

1

SDF801

1

SDF803

1

SDF802

1

D810

1

2

SDF805

1

SDF804

1

C880

1

2

C881

1

2

C882

1

2

C883

1

2

C884

1

2

C885

1

2

24

33

6

27

13

13

13

6

76

27

77

27

25 13

7

13

6

13

8 7 6

25

25

25

25

24

24

27

27

24 13 87 77 74 25 24

50 46 27 11 10

9 6

13 13

13

13

8 7 6

13

13

13

13

13

13

33

6

27 74 27

13

13

13

13

13

13

13

13

13

13

33

6

33

6

33

6

33

6

13

13

13

6

13

36 33 13

7

36

36

D

G

S

D

G

S

D

G

S

FB

LD

HD

GND

COMP

SS

VCC

VC

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_5_ITEM

TABLE_5_ITEM

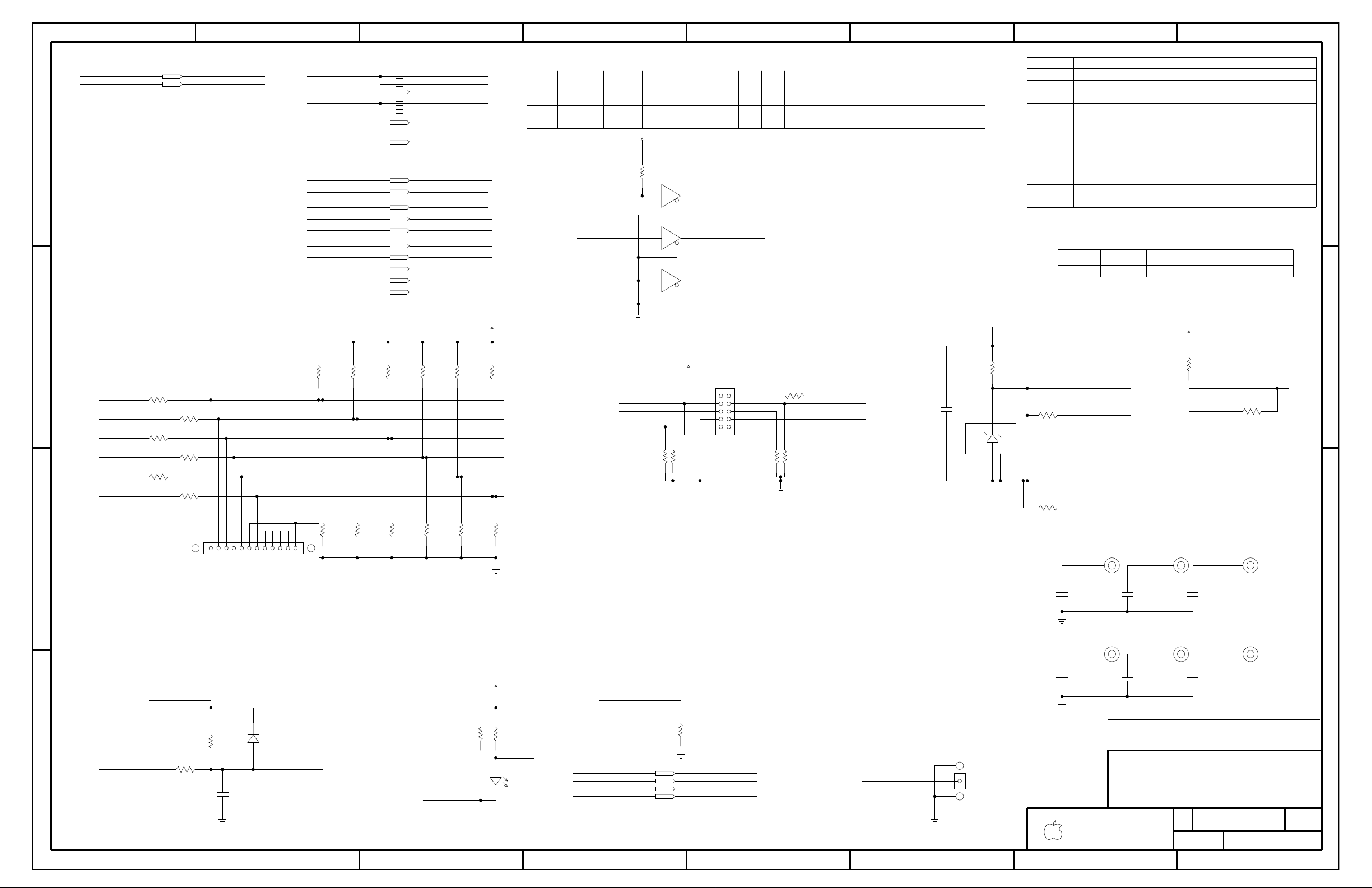

VOUT=VREF*(R903+R905)/R905=2.62VDC

IRU3037CS VREF=1.25VDC

9.24A WITHOUT DIMM TERMINATION

SET OUTPUT=2.62V FOR FRAMEBUFFER.

12.68A WITH DIMM TERMINATION

NOTE:

U900_FEEDBACK

2.5V VREG

2.5V VOLTAGE REGULATOR

PEAK CURRENT OF TOTAL RAILS

LOW TO ENABLE

0

FF

5%

1/10W

805

10K

1/16W

402

MF

1%

1.1K

1/8W

5%

1206

FF

NOSTUFF

6.3V

390UF

20%

ELEC

8X11.5-TH

20%

6.3V

ELEC

1800UF

TH-KZJ

1206

CERM

6.3V

20%

10UF

1800UF

6.3V

ELEC

20%

TH-KZJ

OMIT

PP5V_PWRON

805

CERM

25V

20%

1UF

PP5V_PWRON

IRF7410

SO-8

MBR0520L

SM

SM

MBR0520L

MBR0520L

SM

1UF

20%

10V

CERM

603

50V

10%

0.022UF

NOSTUFF

CERM

603

1UF

20%

25V

CERM

805

PP2V5_PWRON

PP2V5_RUN

CASE369

NTD70N03R

NTD70N03R

CASE369

402

CERM

5%

25V

220PF

TH

1.6UH

CRITICAL

SOI

IRU3037CS

402

MF

1/16W

1%

11K

CERM

16V

20%

603

0.1UF

402

MF

1%

1/16W

27.4K

5%

402

CERM

50V

56PF

50V

CERM

10%

603

3300PF

NOSTUFF

CERM

50V

5%

3900PF

603

5%

FF

805

1/10W

4.7

1206

25V

CERM

20%

1UF

NOSTUFF

390UF

20%

6.3V

ELEC

8X11.5-TH

CRITICAL

051-6482

13

9 99

C909

1

20_INCH_LCD

124-0322

CAP,AL ELEC,1800UF,6.3V

124-0324

1

C909

17_INCH_LCD

CAP,AL ELEC,1500UF,6.3V

MIN_LINE_WIDTH=25MIL

VOLTAGE=2.5V

MIN_NECK_WIDTH=10MIL

U900_VC

U900_VC_R

Q901_GATE

R901_P2

SYS_SLEEP

R904_P2

U900_GATE_H

U900_COMP

U900_SS

Q902_DRAIN

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

U900_GATE_L

U900_FEEDBACK

U900_VC_D

C901

1

2

C904

1

2

C905

1

2

C906

1

2

C907

1

2

C912

1

2

C902

1

2

R902

1 2

R905

1

2

R904

1

2

C903

1

2

C908

1

2

C909

1

2

Q903

5

6

7

8

4

1

2

3

D900

12

D901

12

D902

1

2

C917

1

2

C916

1

2

Q901

4

1

3

Q902

4

1

3

L901

1 2

U900

7

1

4

5

3

8

62

R903

1

2

C915

1

2

R901

1

2

C913

1

2

C914

1

2

R900

1

2

50 46 27 11 10

8 6

6

D

G

S

FB

LD

HD

GND

COMP

SS

VCC

VC

S

D

G

G

D

S

G

D

S

S

D

G

G

D

S

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

U1000_FEEDBACK

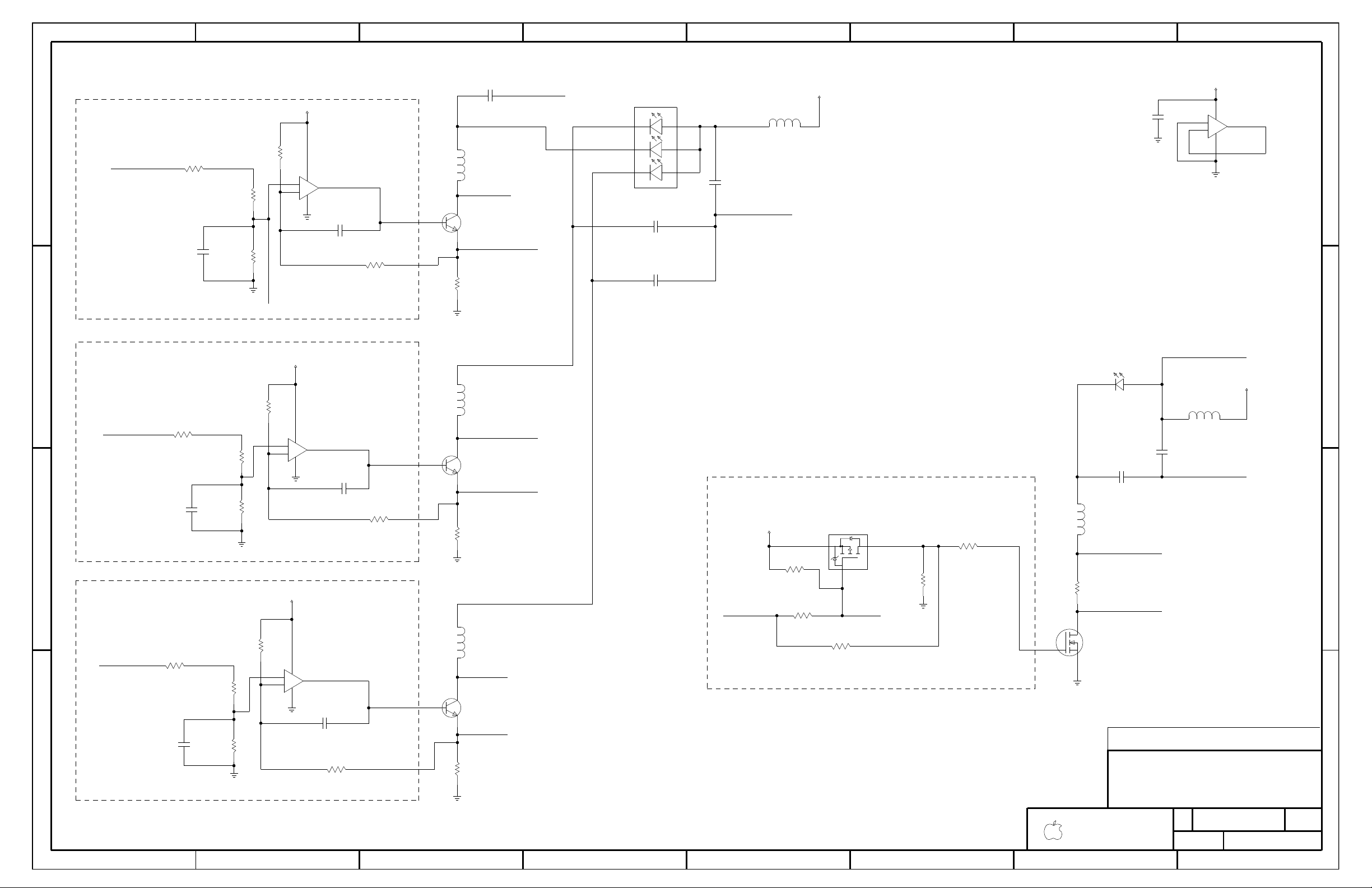

PP1V2_RUN FET SWITCH

PEAK CURRENT 4.43A

PP1V2_PWRON FET SWITCH

PEAK CURRENT 0.6A

1.2V VREG

VOUT=VREF*(R1003+R1005)/R1005=1.206VDC

SET OUTPUT=1.2V

NOTE:

5.96A

IRU3037ACS VREF=0.8VDC

PEAK CURRENT OF TOTAL RAILS

@ VGS=2.5 V

RDSON=0.016 OHM

@ VGS=2.5 V

RDSON=0.06 OHM

SHASTA CORE VOLTAGE REGULATOR

1.6UH

TH

603

CERM

3300PF

NOSTUFF

10%

50V

1%

MF

402

1/16W

10K

1206

NOSTUFF

FF

1.1K

1/8W

5%

1UF

20%

CERM

25V

1206

NOSTUFF

SM

MBR0520L

PP5V_ALL

CERM

10V

603

20%

1UF

CASE369

NTD70N03R

0.022UF

603

CERM

NOSTUFF

10%

50V

SM

MBR0520L

MBR0520L

SM

0

5%

1/10W

805

FF

805

CERM

20%

1UF

25V

25V

5%

CERM

402

220PF

20%

25V

805

CERM

1UF

IRU3037ACS

SOI

20%

ELEC

6.3V

1800UF

TH-KZJ

402

MF

1%

1/16W

5.11K

SM

2N7002

PP3V3_ALL

MF

402

5%

100K

1/16W

PP1V2_RUN

TH-KZJ

1800UF

ELEC

6.3V

20%

2N7002DW

SOT-363

2N7002DW

SOT-363

PP5V_ALL

MF

1/16W

402

100K

5%

PP5V_ALL

SI3446DV

TSOP

PP1V2_PWRON

2N7002

SM

5%

MF

1/16W

402

100K

PP5V_ALL

8X11.5-TH

ELEC

6.3V

390UF

20%

I70

SI9426DY

SOI

5%

CERM

603

50V

3900PF

5%

603

50V

CERM

68PF

0.1UF

20%

CERM

16V

603

27.4K

1%

402

MF

1/16W

1/16W

MF

0

5%

402

5%

0

NOSTUFF

MF

402-1

1/16W

5%

MF

1/16W

0

402

0

5%

1/16W

402-1

MF

NOSTUFF

PP3V3_ALL

ELEC

6.3V

20%

390UF

8X11.5-TH

MF

402

5%

1/16W

100K

805

FF

1/10W

5%

4.7

CASE369

NTD60N02R

CERM

6.3V

20%

10UF

1206

9910

13

051-6482

Q1001_GATE

Q1002_DRAIN

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

U1000_GATE_L

Q1005_G

SYS_SLEEP

PP1V2_PWRON_SB_VCORE

U1000_GATE_H

VOLTAGE=1.2V

MIN_NECK_WIDTH=15MIL

MIN_LINE_WIDTH=100

PP1V2_PWRON_SB_VCORE

Q1003_G

PP1V2_PWRON_SB_VCORE

U1000_SS

R1004_P2

R1001_P2

Q1006_G

U1000_FEEDBACK

U1000_COMP

Q1000_G

SYS_POWERUP_L

SYS_POWERUP_L

TURN_ON_SHASTA_CORE_L

TURN_ON_PP1V2_L

U1000_VC_DU1000_VC_R

U1000_VC

C1009

1

2

C1008

1

2

C1003

1

2

C1002

1

2

C1001

1

2

L1001

1 2

C1007

1

2

R1005

1

2

R1004

1

2

C1012

1

2

D1002

1

2

C1017

1

2

Q1002

4

1

3

C1005

1

2

D1000

12

D1001

12

R1000

1 2

C1000

1

2

C1006

1

2

C1004

1

2

U1000

7

1

4

5

3

8

62

R1003

1

2

Q1000

3

1

2

R1007

1

2

Q1004

3

5

4

Q1004

6

2

1

R1008

12

Q1006

125

63

4

Q1005

3

1

2

R1009

12

Q1003

5 6 7 8

4

1 2 3

C1014

1

2

C1013

1

2

C1015

1

2

R1001

1

2

R1010

1 2

R1011

1 2

R1012

1 2

R1013

1 2

R1014

1

2

R1002

1

2

Q1001

4

1

3

50 46 27 11

9 8 6

23 10

6 3

23 10

6 3

23 10

6 3

33 13 11 10

7 6

33 13 11 10

7 6

3

3

D

G

S

G

DS

LM339A

V+

GND

LM339A

V+

GND

TAB

VOUTVPWR

VCTRL

VOUT

ADJ

SENSE

D

G

S

G

DS

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

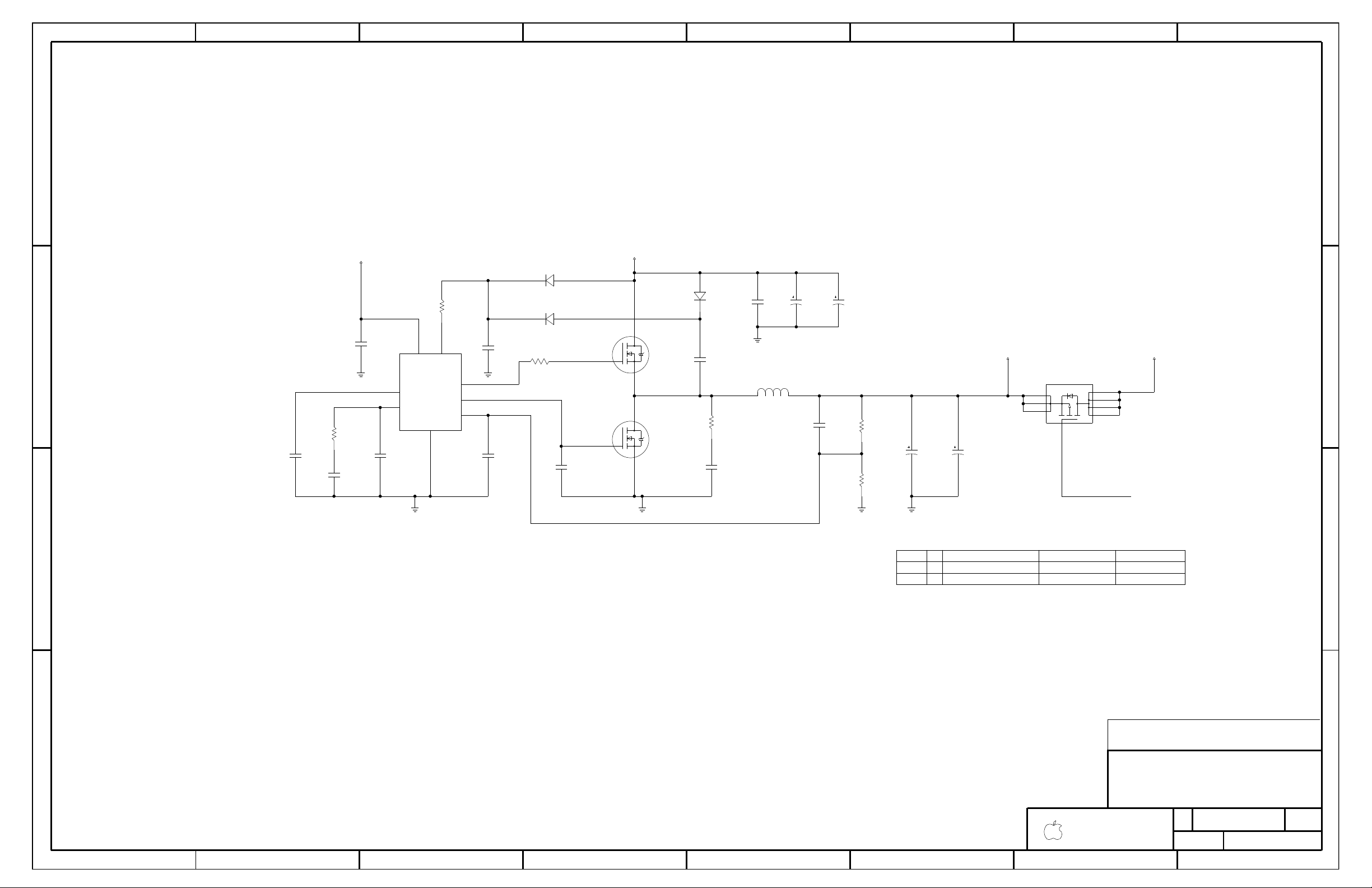

P-CHANNEL

FET ON IN SLEEP

Ron=11mOhm

FET ON IN RUN

FET ON IN SLEEP

5V & 3.3V VREGS

FET ON IN RUN

PP5V_PWRON

Vpwr >= Vout+0.35V

Vctrl >= Vout+1.25V

Ron=11mOhm

P-CHANNEL

R2

R1

Iadj=50uA typ

3.30V - 3.45V

Vref=1.250V typ

Vout=Vref(1+R2/R1)+Iadj(R2)

PROCESS SWING

SHUTDOWN -> FLOAT

SLEEP -> FLOAT

RUN -> LOW

SHUTDOWN -> FLOAT

SLEEP -> LOW

RUN -> FLOAT

SM

ELEC

10V

150UF

20%

CRITICAL

SM-1

SI4467DY

100K

5%

1/16W

MF

402

SM-1

SI4467DY

CRITICAL

CRITICAL

SOI

SOI

47.0K

1%

1/16W

MF

603

CRITICAL

SM

CS5253

402

5%

MF

100K

1/16W

402

1/16W

MF

5%

100K

124

1%

1/16W

MF

603

210

1%

1/16W

MF

603

0.1UF

N20P80%

16V

CERM

603

SI4467DY

SM-1

SM-1

SI4467DY

SM

100UF

ELEC

6.3V

20%

402

1K

1%

1/16W

MF MF

1/16W

1%

1K

402

9911

13

051-6482

RAIL_CTL_NEG

RAIL_CTL_POS

PP5V_ALL

PP3V3_ALL

PP3V3_RUN

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

VOLTAGE=3.3V

PP3V3_PWRON

MIN_LINE_WIDTH=20MIL

3_3V_ALL_ADJ

MIN_NECK_WIDTH=10MIL

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=25MIL

VOLTAGE=3.3V

PP3V3_ALL

PP5V_PWRON

VOLTAGE=5V

MIN_LINE_WIDTH=25MIL

MIN_NECK_WIDTH=10MIL

MIN_LINE_WIDTH=20MIL

RAIL_SLEEP_FET

MIN_NECK_WIDTH=10MIL

PP5V_RUN

SYS_POWERUP_L

SYS_SLEEP

PP5V_ALL

MIN_NECK_WIDTH=10MIL

RAIL_RUN_FET

MIN_LINE_WIDTH=20MIL

C1100

1

2

VR1100

2

1

4

3

6

5

R1105

1

2

R1106

1

2

C1101

1

2

C1102

1

2

Q1100

5

6

7

8

4

1

2

3

R1100

1 2

Q1101

5

6

7

8

4

1

2

3

U1100

12

10

11

13

3

U1100

12

4

5

2

3

R1102

1

2

R1103

1 2

R1104

1 2

Q1102

5

6

7

8

4

1

2

3

Q1103

5

6

7

8

4

1

2

3

R1107

1

2

R1101

1

2

3

11

7 6

11

7

6

27 18

6

11

7

18

6

6

33 13 10

7 6

50 46 27 10

9 8 6

11

7 6

RSET*

MR*

GND

VCC

P9[7]

P9[6]

P9[5]

P8[7]

P8[6]

P8[5]

P3[7]

P3[6]

P3[5]

P3[4]

P2[6]

P2[7]

P2[4]

P2[5]

P1[4]

P1[3]

P1[2]

P1[1]

P1[0]

P0[4]

P0[0]

P0[2]

P0[3]

P0[1]

P0[7]

P0[6]

P0[5]

P3[3]

P3[2]

P3[1]

P3[0]

P2[3]

P2[2]

P2[1]

P2[0]

P1[5]

P1[6]

P1[7]

PCNVSS

RESET*

XOUT

VREF

XIN

P7[7]

P7[6]

P7[5]

P7[4]

P7[3]

P7[2]

P7[1]

P7[0]

P6[7]

P6[6]

P6[5]

P6[4]

P6[3]

P6[2]

P6[1]

P6[0]

P10[0]

P10[1]

P9[3]

P9[2]

P9[1]

P9[0]

P8[4]

P8[3]

P8[2]

P8[1]

P8[0]

P10[6]

P10[7]

P10[2]

P10[3]

P10[4]

P10[5]

VCC

AVSS

VSS

AVCC

SQW/

OUT

VBAT

SDA

SCL

X1

X2

GND

VCC

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

ALIAS

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

AN25

AN26

Y

AN27

S

Y

Alternate Functions

Y1300’s load capacitance is 12pF

(CPU_SENSE_I/CPU_SENSE_V) requires

IOC5

Y

Y

Undervoltage Reset Circuit

2.7

2.6

2.5

Port

7.6

1.6

1.7

Port

1.5

10.7

7.4

7.2

0.0

0.2

6.0

0.3

6.2

6.1

Port

Tower & Server

Consumer

NNY

SSS

YY

YYY

S Y S

S

NNYY

NNYY

SSS

SSS

YYY

YY Y

Y

SDAmm

INT5*

INT4*

S Y S

S Y S S

S Y S

SYS

(see aliases below)

N = Alternate function

S = Spare

S

YNS

Y Y Y Y

Y Y Y Y

Y Y Y Y

Y Y Y Y

YYYY

Y

AN22

AN20

AN06

Y

Y

CTS0*

Keep crystal subcircuit close to SMU.

IOC7

TA2in

TA2out

Y

N

AN04

INT2*

YYYY

CE*

AN00

Y

Portable

Consumer

Server

Y

Y

AN23

AN21

Y

Y

Consumer

Y

TA3in

Y

Y

Y

N

AN0

SSS

Y

AN03

(BUSY)

TB0in

Y

Y

Y

Y

Y

Y

Y Y

Sin3

Master: Link

System Management Unit

signal (GND_SMU_AVSS). None of

NOTE: All analog inputs to SMU should have

provided on another page.

reference used by monitoring

(NONE)

(NONE)

- _PP3V3_PWRON_SMU

- _PP3V3_ALL_RTC

- _PP3V3_ALL_SMU

ELECTRICAL_CONSTRAINT_SET

BOM options provided by this page:

Signal aliases required by this page:

NOTE: CPU current/voltage monitoring

SMU_VREF should be same signal or

Real Time Clock

NC

provided on this page. Please.

reuire pull-ups that are not.

Tower

NYY

NNNY

Y Y

Y

SSY

Y

S

SSYY

Y

YY

YY

RTS0*/

TXD1

CLK1

RTS1*

TXD0

RXD0

CLK0

RXD1

AN07

AN05

AN01

AN02

Server

N

N

SNY

Y

Y Y

Y

Y Y

Y YYY

YY Y

Y

Y

Y

YYYY

Y Y

N

Y

Y

Y

Y

Y

Y

SYS

YYY

Y

YY

Y

SY

YY

YY

S

Y

YYY

Y

YY Y

Y

Y

Y

Y

Y

Y

YYYYY

Y

Y

Y

Y

SDA

TA4out

TA1in

AN24

TB1in

NMI*

INT1*

IOC2

SCLmm

Y

YY

S

YYYN

Y

NY

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

YYYY

N

Y

Y

YYYY

N

S

S

Sout3

AN1

AN2

AN3

KI0*

KI1*

KI2*

KI3*

YYYY

Y Y

Y

Y

Y

Y

INT0*

IOC4

IOC3

YY

Y

Y

SCL

this page.

CLK3

TB2in

Y

to ensure missing pull-ups are

review the latest SMU specification

Y

INT3*

- _PPVREF_SMU (SMU AVCC or 2.5V reference)

Power aliases required by this page:

Page Notes

IOC6

TA4in

TA3out

100K/10uF RC filter at SMU pins.

Caps should connect to GND_SMU_AVSS.

those capacitors are provided on

a 100pF capacitor to the SMU AVSS

circuit, but be aware that this will

affect other analog inputs such as

AC adapter ID.

NOTE: Some primary and alternate functions

NOTE: Pinout matches SMU pinout v1.4.

S

S

N

N

S

S

TA1out

S

YY

YN

S

Tower

Portable

Portable

DIFFERENTIAL_PAIR

System Management Unit

NET_SPACING_TYPE

Y = Primary function

S

Y

SMU Pull-ups / pull-down

Y

Y

Y

S

Y

0.1uF

20%

10V

402

CERM

20%

6.3V

10uF

CERM

805

MF

5%

402

1/16W

100K

402

1/16W

5%

10K

MF

1K

MF

5%

402

1/16W

MAX6804

SOT143

CERM

12pF

50V

5%

402

10M

402

MF

1/16W

5%

NO STUFF

0

5%

MF

1/16W

402