Page 1

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

78

6

5

4

3

ECN

ZONE

REV

DESCRIPTION OF CHANGE

SEEDY

11

365610

ENGINEERING RELEASED

12

CK

APPD

DATE

02/17/05

ENG

APPD

?

DATE

02/17/05

D

CSA

10

11

12

C

13

14

16

17

18 17

21

22

23

24

25

26

27

28

B

29

30

31

32

33

34

35

36

37

38

40

44

45

A

46

48

49

50

PDF

1

2

3

4

5

6

7 7

8

9

10

11

12

13

14

15

16

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

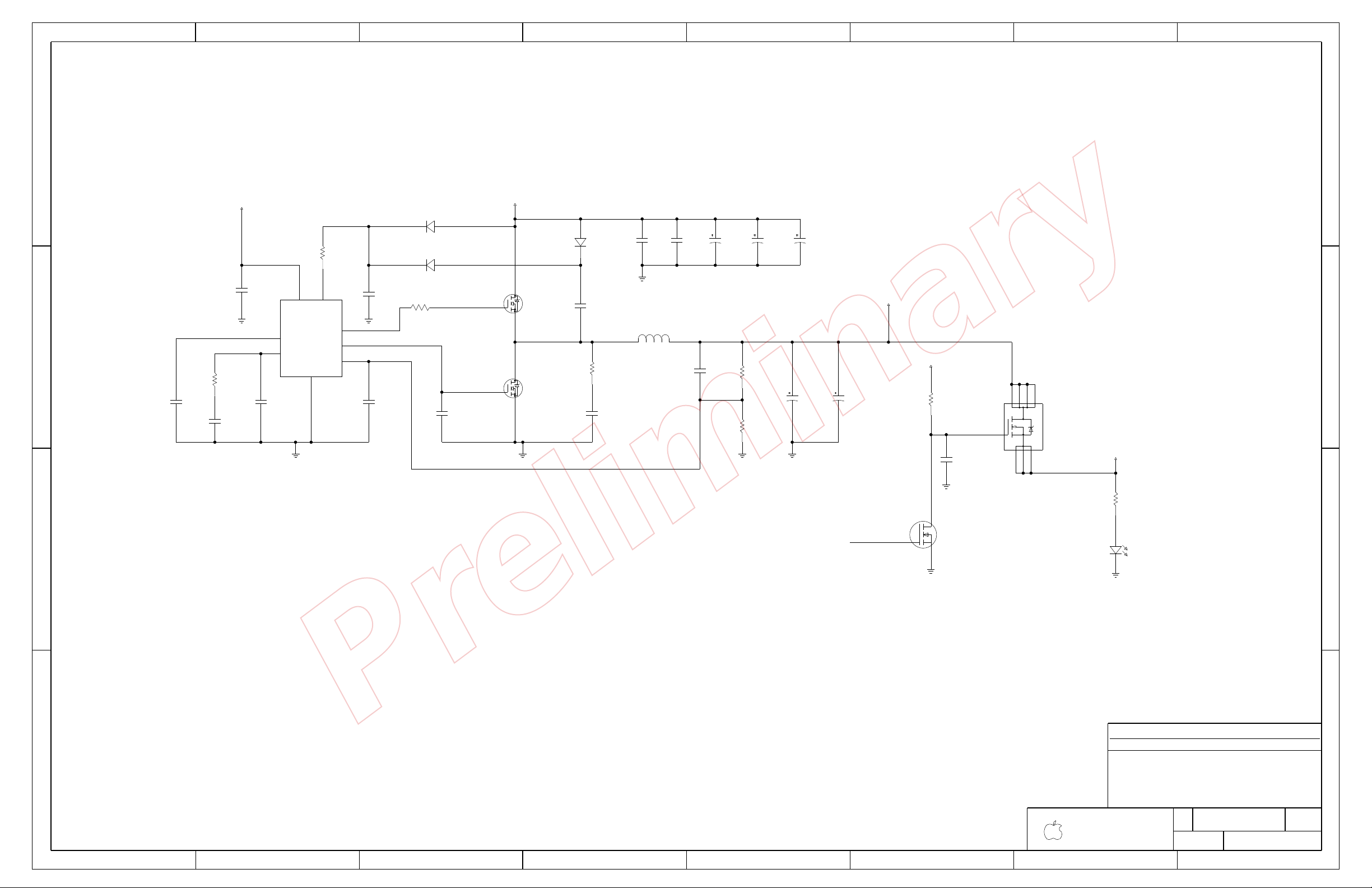

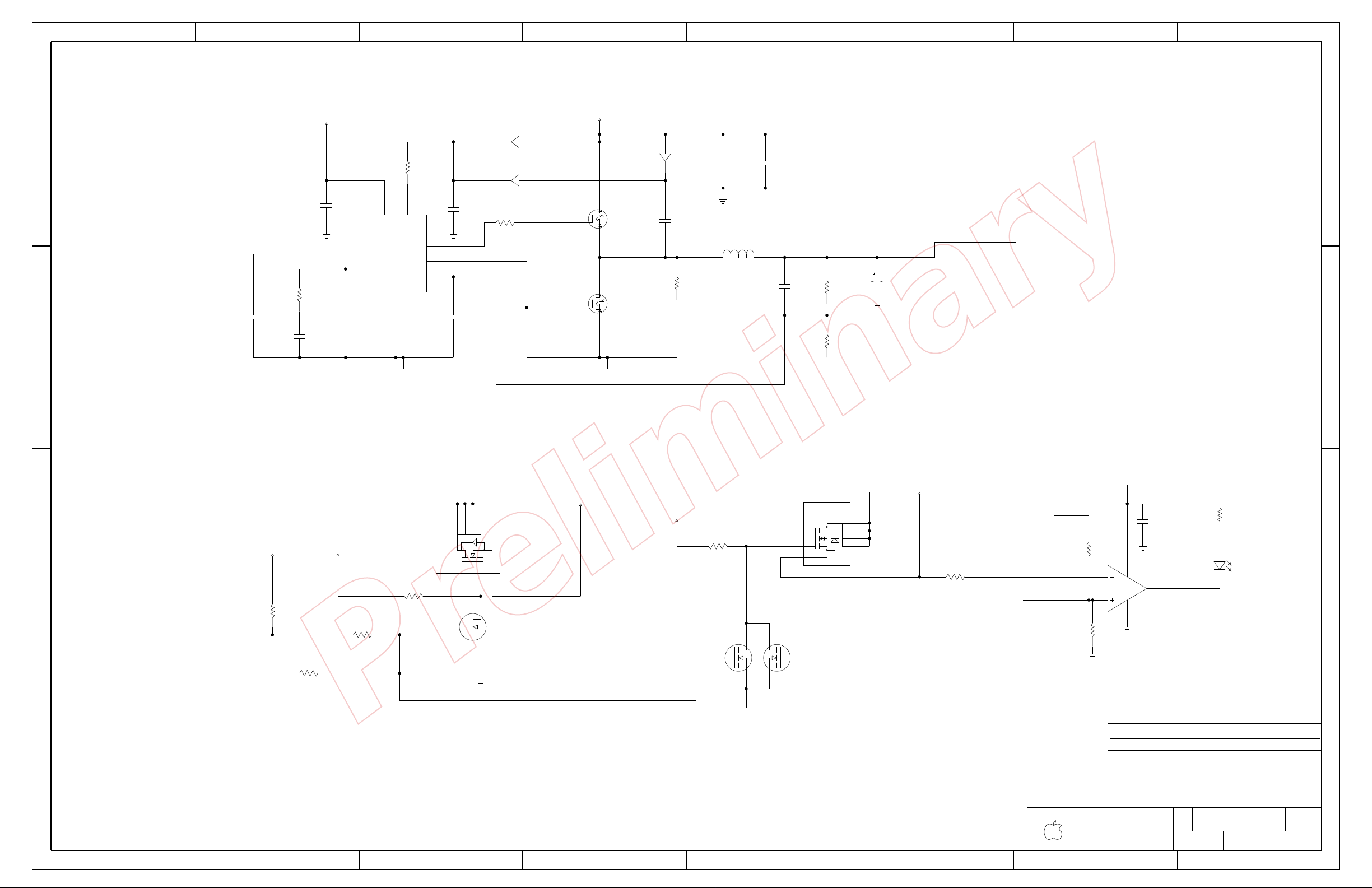

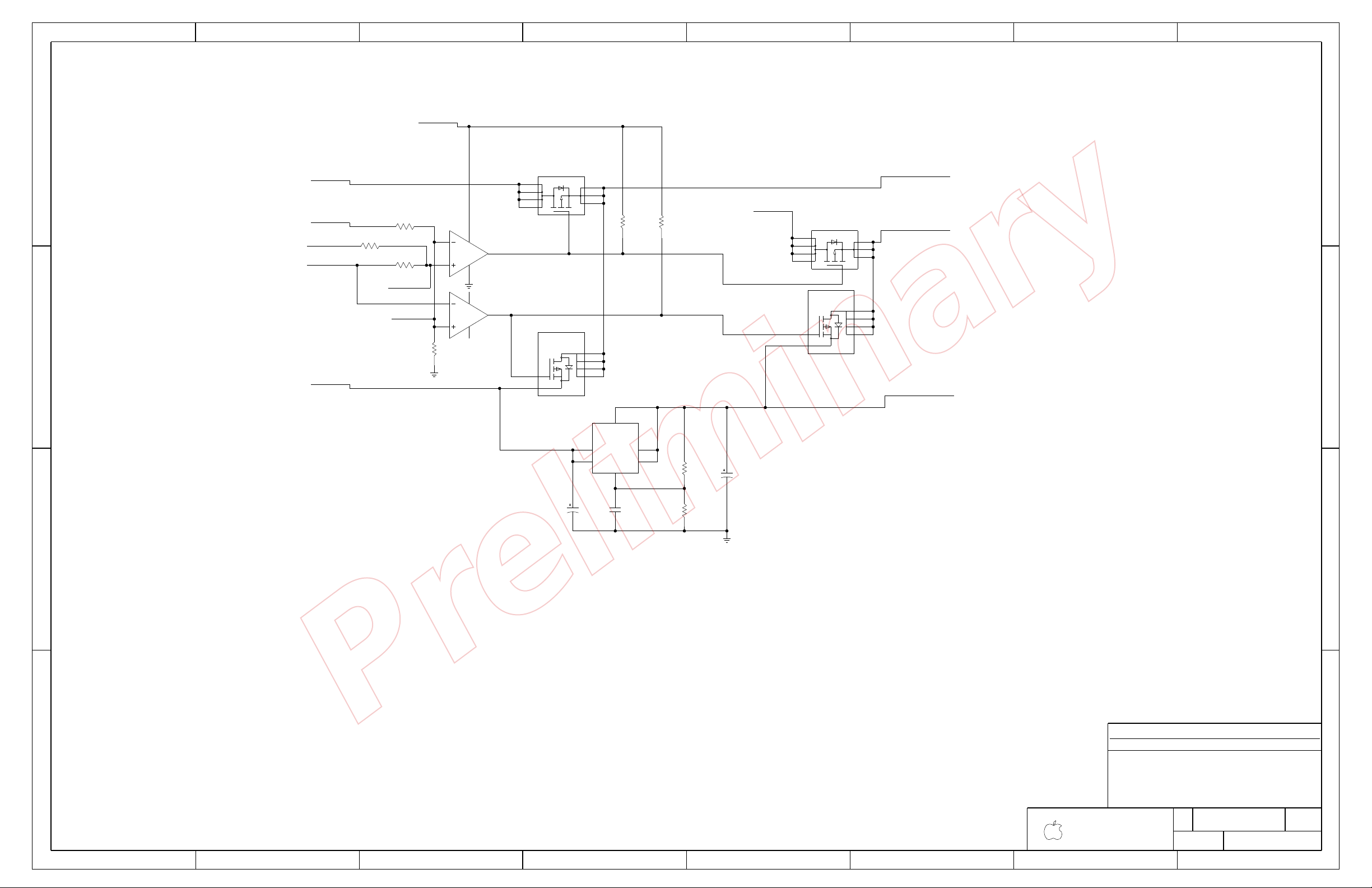

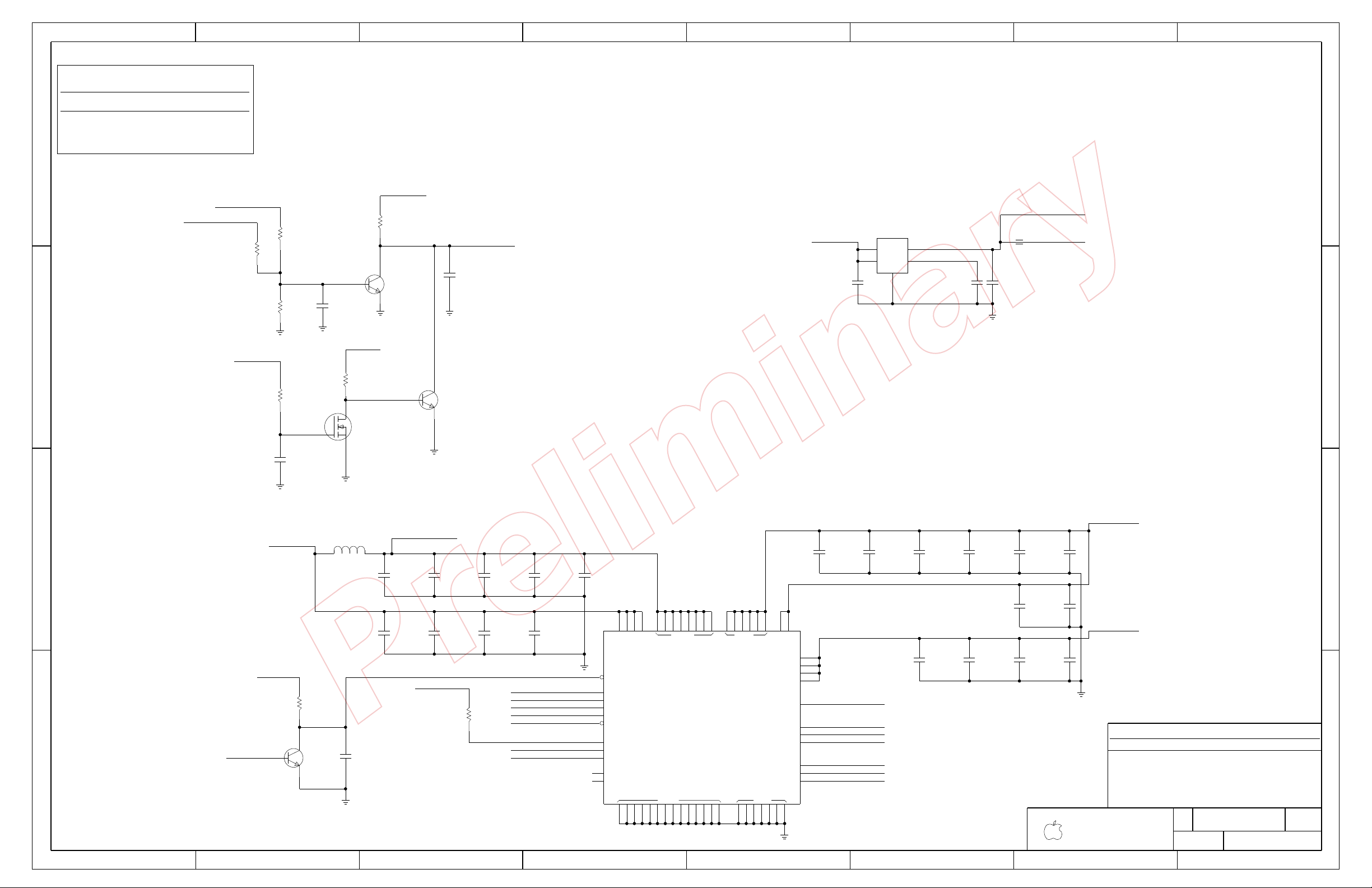

CIRCUIT

1

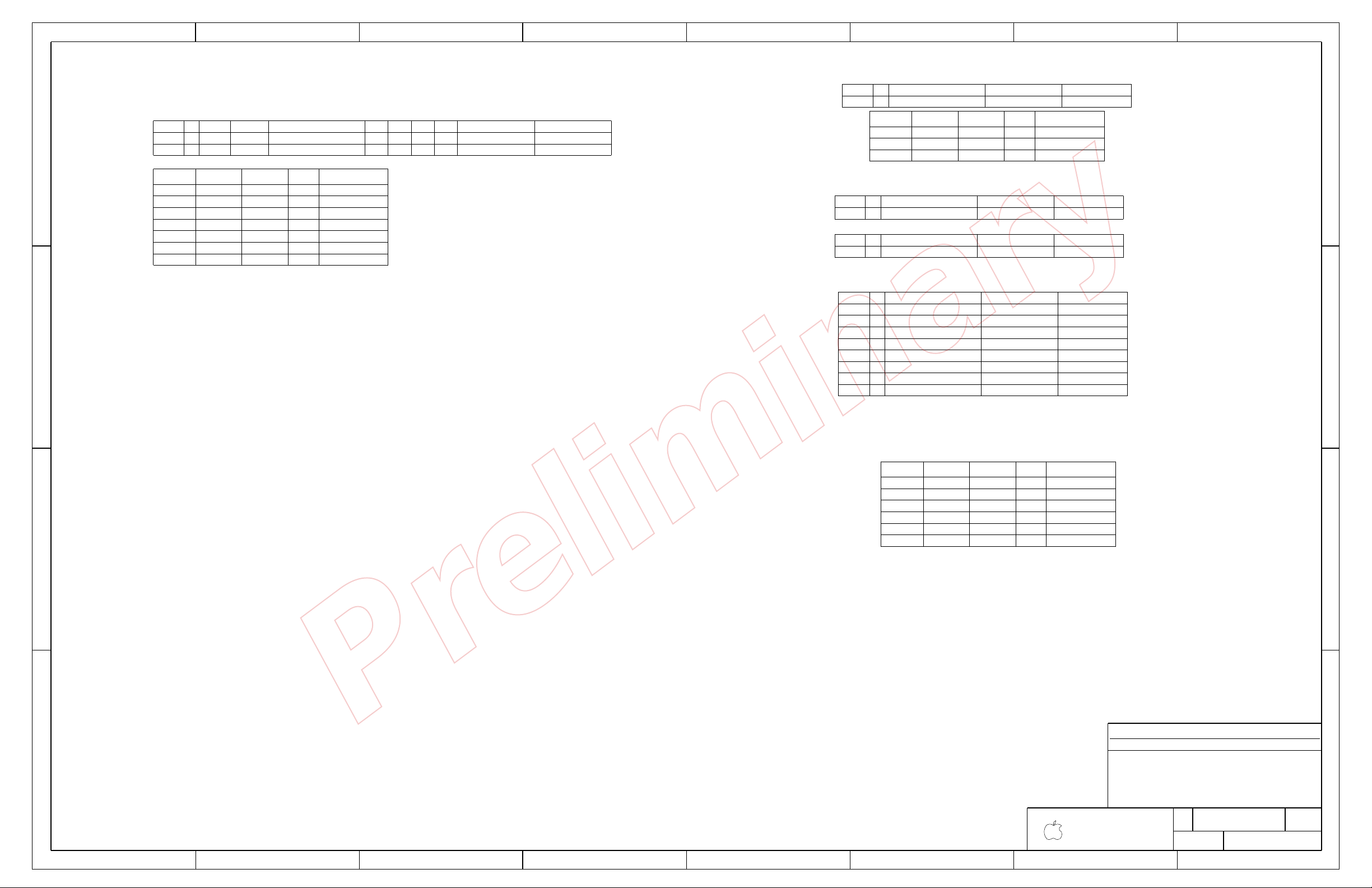

TABLE OF CONTENTS

2

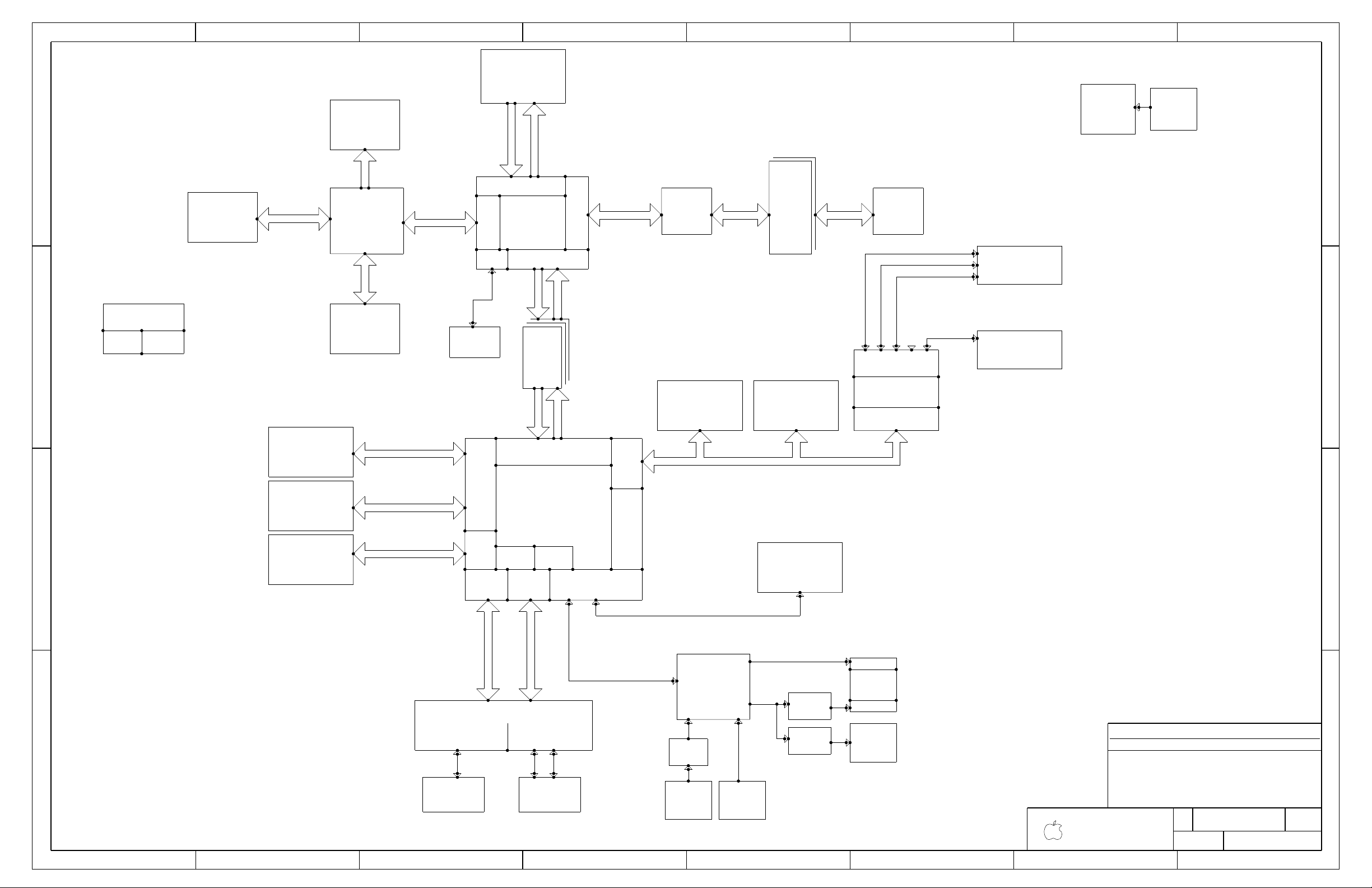

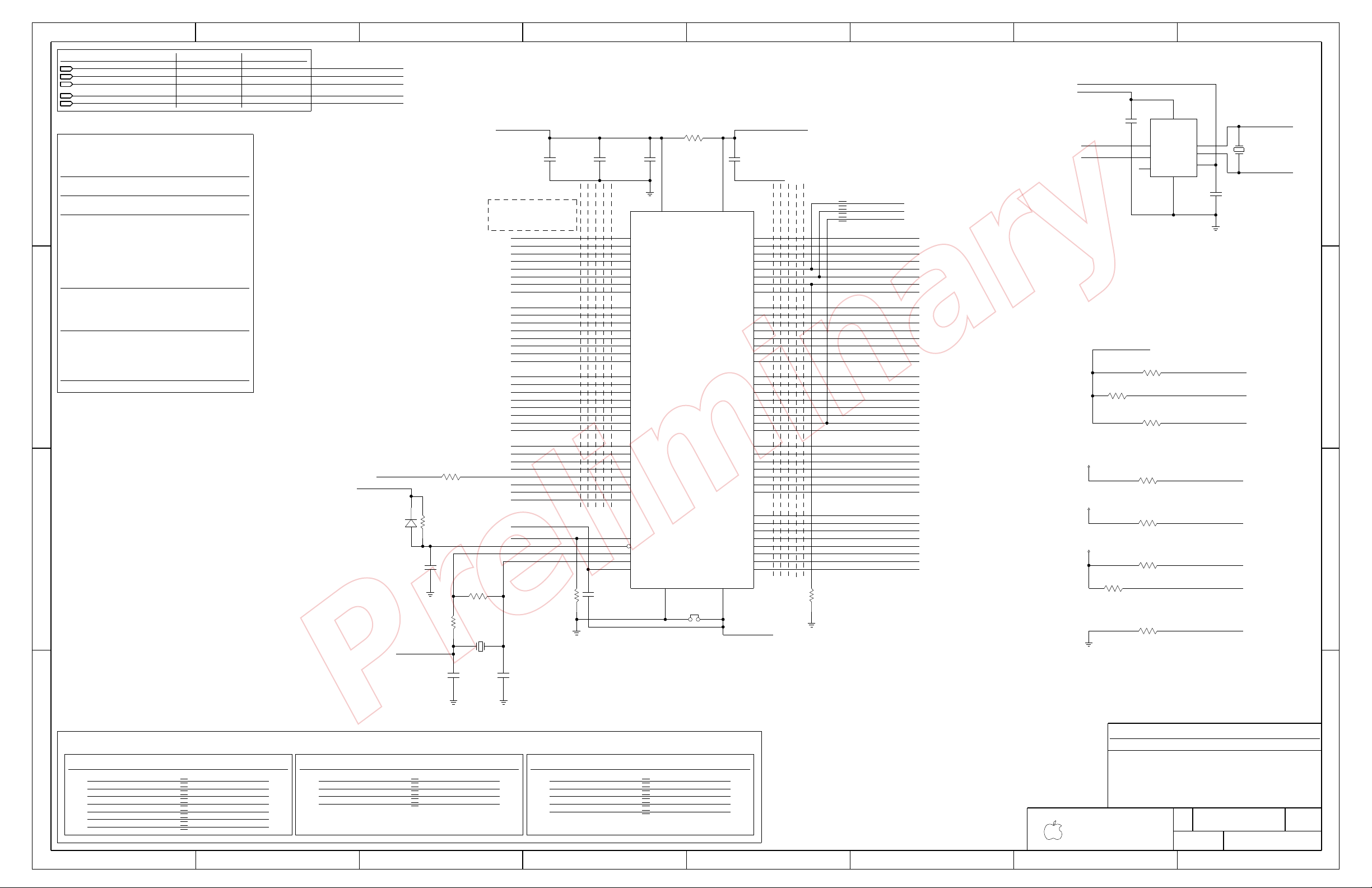

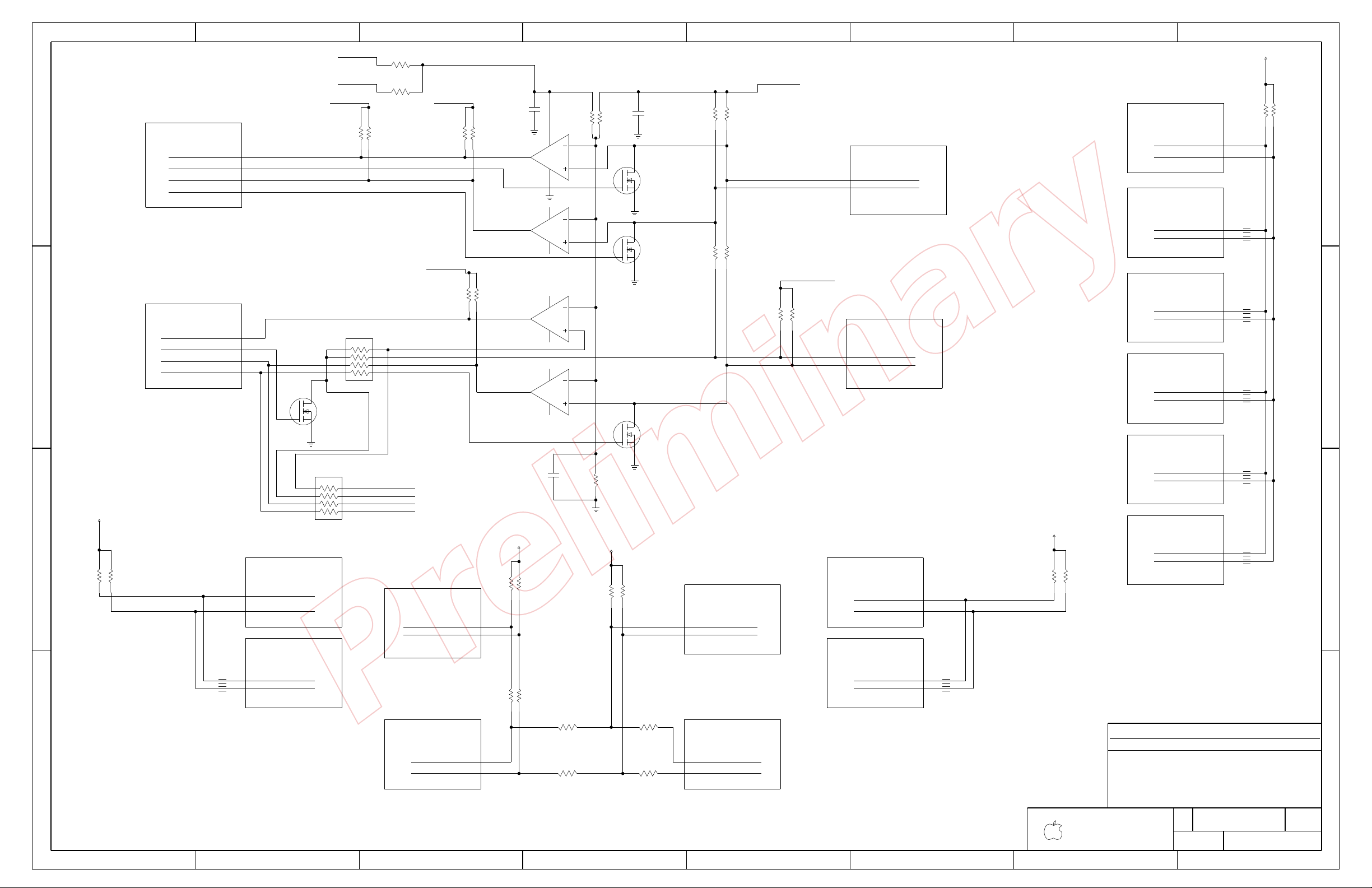

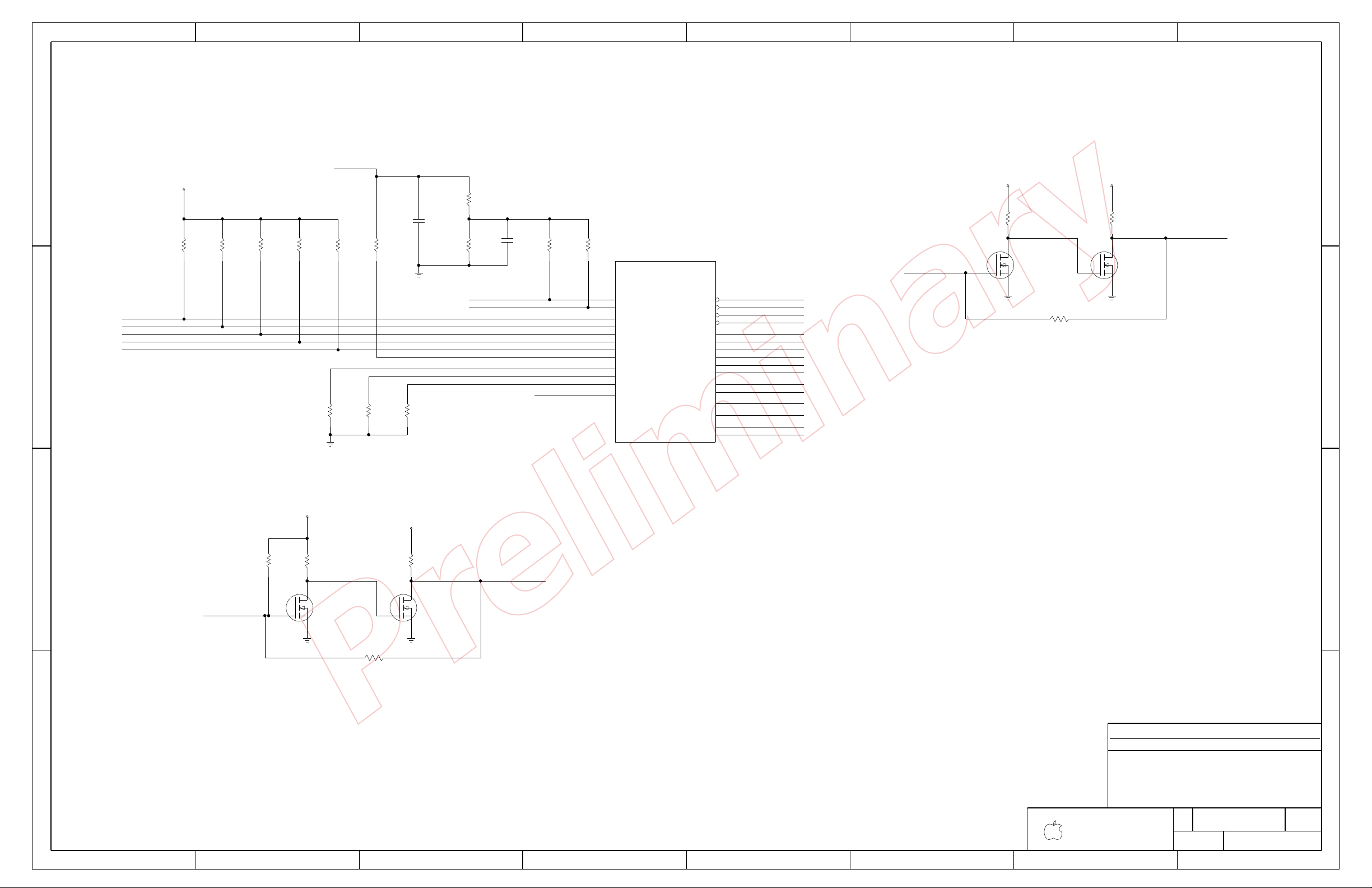

SYSTEM BLOCK DIAGRAM

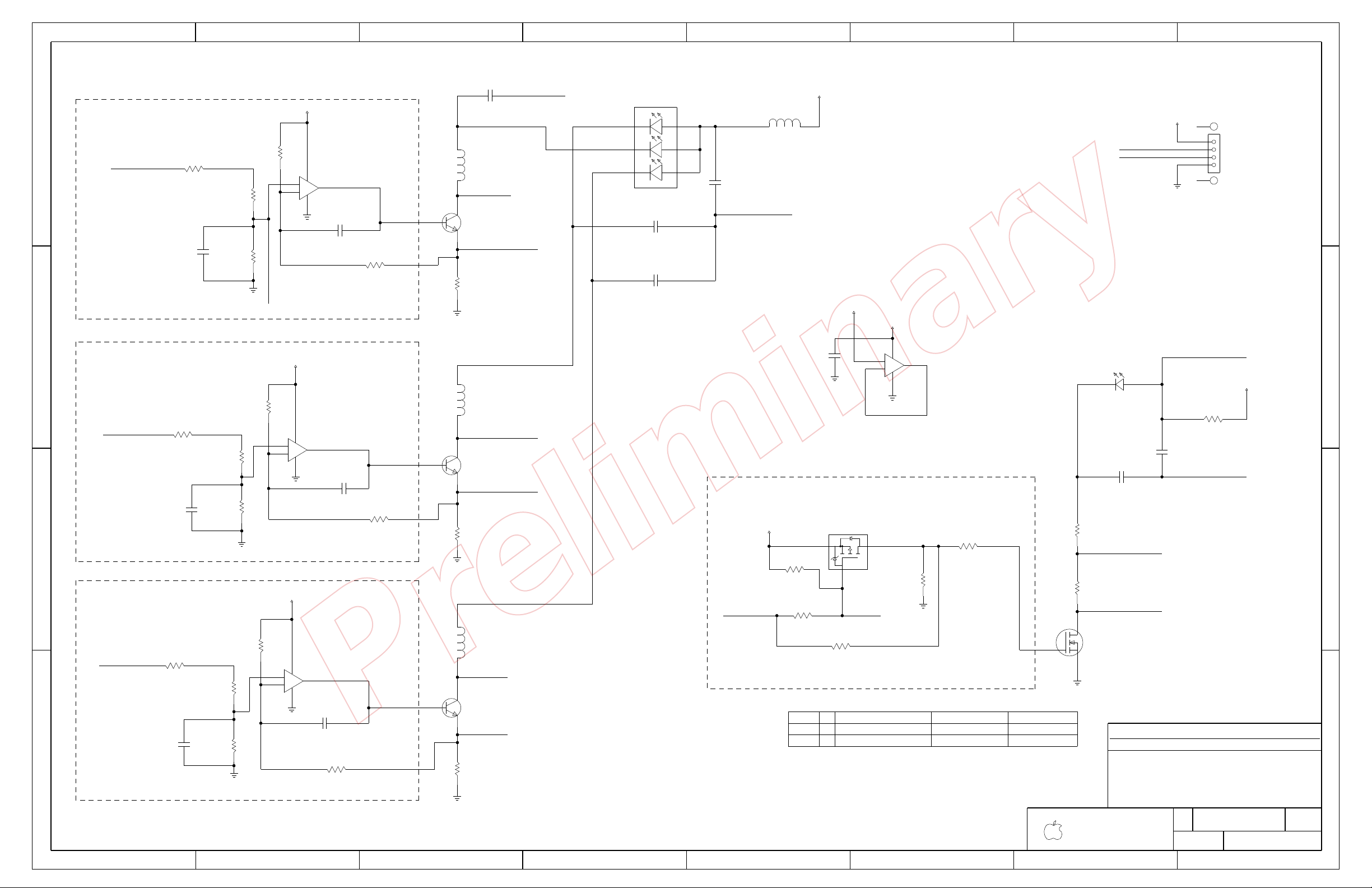

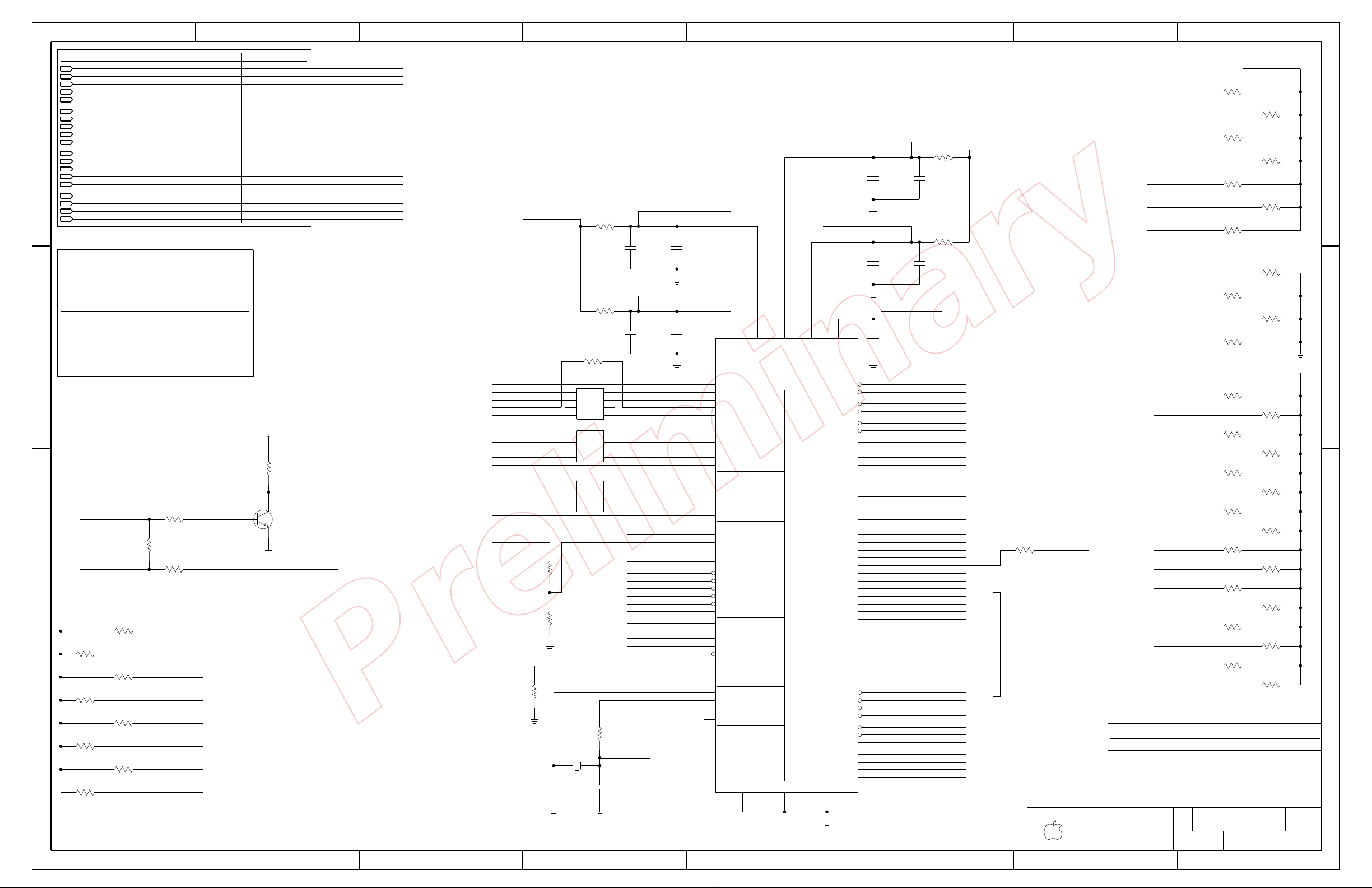

POWER BLOCK DIAGRAM

3

REVISION HISTORY

4

TABLE ITEMS

5

FUNC TEST

6

POWER CONNECTOR / POWER ALIAS

SIGNAL ALIAS

8

2.5V VREG

9

1.2V VREG

3.3V/5V PWRON SWITCHING

VESTA POWER

SMU

CPU LOGIC ANALYZER CONNECTOR

FAN 0, 1 AND SYSTEM TEMP SENSOR

FAN 2 AND HARD DRIVE TEMP SENSOR

I2C CONNECTIONS

INDICATOR LED / AMBIENT LIGHT SENSOR

1.5V VREG / U3LITE CORE

SHASTA CORE

U3LITE MISC

SHASTA SERIAL

PULSAR POWER

PULSAR CLOCKS

U3LITE APPLE PI

NEO APPLE PI

CPU STRAPS

NEO POWER & BYPASS

CPU BYPASS

CPU VREG

CPU VREG

CPU VREG OUTPUT CAPS

CPU DIODE CONDITIONER

U3LITE MEMORY

SERIES TERMINATION

DIMMS

PARALLEL TERMINATION

PARALLEL TERMINATION

VTT VREG

U3LITE AGP

GPU AGP

GRAPHICS VREGS

* PAGES WHERE MASTER PAGE IS IN A DIFFERENT SCHEMATIC

8

67

BLOCK

TOP

PROCESSOR

MEMORY

GRAPHICS

5

CSA

51

52

53

54

55

56

59

60

62

64

73

74

75

76

77

83

84

86

87

88

89

90

91

92

94

95*

96*

98*

100*

101*

102*

4

PDF

43

44

45

46

47

48

4958

50

51

52

53

54

55

56

57

58

5980

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

GPU CORE POWER

GPU FRAME BUFFER

FRAME BUFFER TERMINATION

GRAPHICS DDR SDRAM A

GRAPHICS DDR SDRAM B

GPU STRAPS

GPU DVI & DACS

EXT VGA & TMDS

U3LITE HYPERTRANSPORT

SHASTA HYPERTRANSPORT

HYPERTRANSPORT LA CONNECTORS

PCI SERIES TERMINATION

SHASTA PCI

BOOT ROM

AIRPORT EXTREME & BLUETOOTH

USB2 PCI

SHASTA DISK

DISK CONNECTORS

SHASTA ETHERNET

VESTA ETHERNET PHY

ETHERNET CONNECTOR

SHASTA FIREWIRE

VESTA FIREWIRE PHY

FIREWIRE CONNECTORS

USB HOST INTERFACE

USB DEVICE INTERFACE

MODEM CONNECTOR

PCM3052A AUDIO CODEC

LINE IN AMP

LINE OUT AMP

SPEAKER AMP

AUDIO CONNECTORS

AUDIO POWER SUPPLIES

DIMENSIONS ARE IN MILLIMETERS

X.XX

X.XXX

ANGLES

THIRD ANGLE PROJECTION

CIRCUIT

XX

DO NOT SCALE DRAWING

3

DRAFTER

ENG APPD

QA APPD

RELEASE

METRIC

MATERIAL/FINISH

NOTED AS

APPLICABLE

DESIGN CK

MFG APPD

DESIGNER

SCALE

NONE

SIZE

2

Apple Computer Inc.

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

TITLE

SCH,MLB,SEEDY

DRAWING NUMBER

D

051-6772

BLOCK

GRAPHICS

HT

PCI

DISK

ETHERNET

FIREWIRE

USB

MODEM

AUDIO

1

SHT

REV.

11

OF

1 102

D

C

B

A

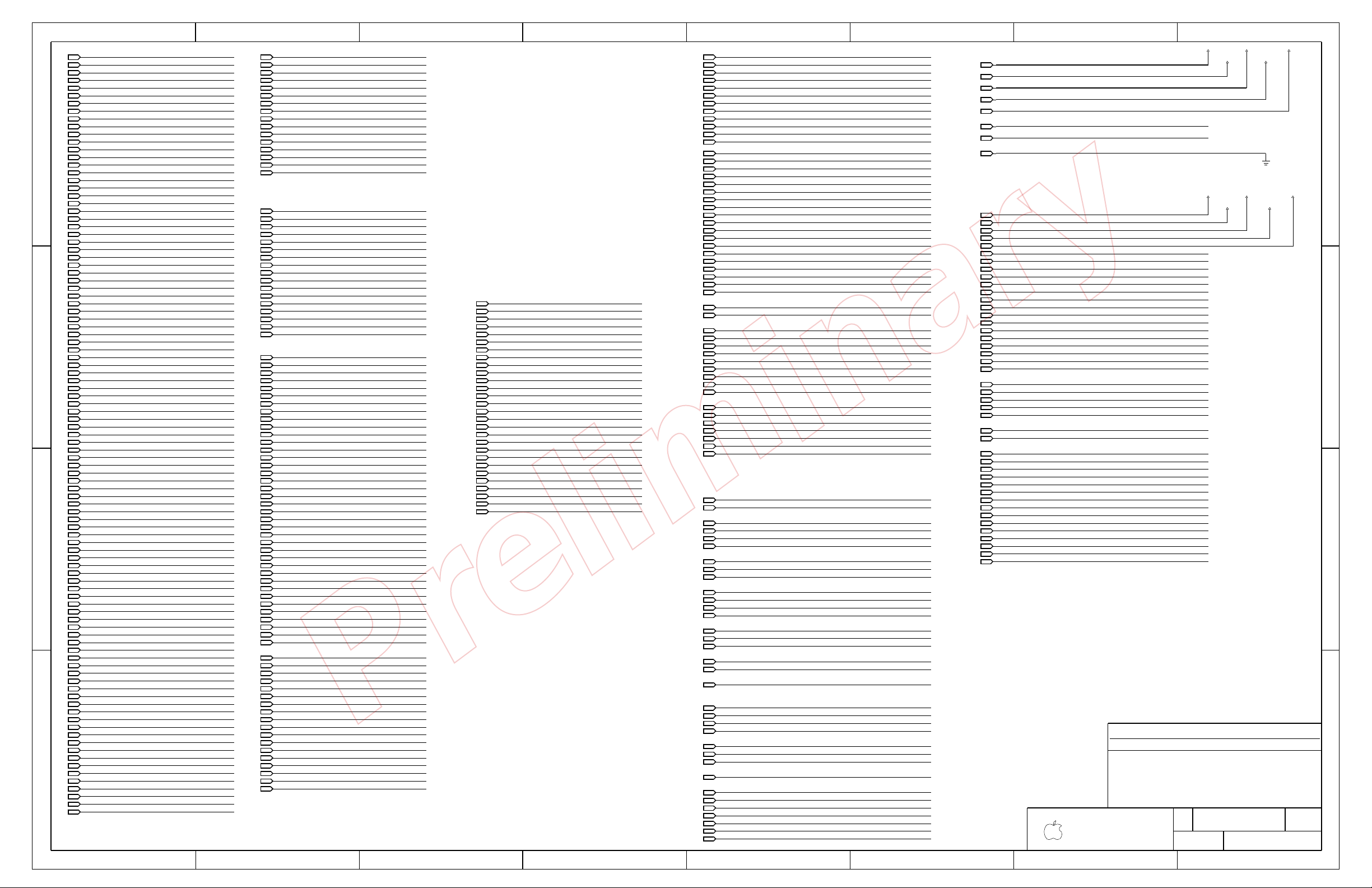

Page 2

FREQUENCIES LISTED ARE MAXIMUM DATA TRANSFER RATES SUPPORTED BY U3LITE

D

U5400, U5401

FRAME

BUFFER A

PAGE 54

U2600

PULSAR

POWER

C

PAGE 26

B

CLOCKS

PAGE 27

HARD DRIVE

FOR DEVELOPMENT ONLY

OPTICAL

78

64-BIT

FRAME BUFFER

2.6V/400MHZ

JXXXX

SATA

CONNECTOR

PAGE 83

J8302

SATA DEV

CONNECTOR

PAGE 83

J8301

UATA

CONNECTOR

PAGE 83

J5900, J5901

J5902, J5903

17",20" INVERTER

TMDS

EXT VGA

PAGE 59

U4900

GPU

RV351LE

PAGE 49

U5500, U5501

FRAME

BUFFER B

PAGE 55

SATA/150

1.2V/1.5GHZ

SATA/150

1.2V/1.5GHZ

UATA/133

3.3V/133MHZ

64-BIT

FRAME BUFFER

2.6V/400MHZ

6

32-BIT

8X AGP

0.8V/533MHZ

4X = 1.5V

I/O = 1.5V

U2900

CPU

NEO 10S

PAGE 29

APPLE PI

PAGE 28

U3

AGP

U3LITE

PAGE

48

HYPERTRANSPORT

MISC

PAGE 24

I2C

PAGE 18

SATA1 SATA2

PAGE 80 PAGE 80

ETHERNET FIREWIRE

PAGE 84

8-bit TX & 8-bit RX

GMII (3.3V/125MHz)

HYPERTRANSPORT

SATA

U2300

UATA

CORE

PAGE 23

PAGE 88

32-BIT

APPLE PI

ELASTIC INTERFACE

1.2V/900MHZ

CORE

PAGE 22

PAGE 60

J6400

J6401

J6402

HT

DEBUG

PAGE 64

PAGE 62

SHASTA

NCs

PAGE 91

1394 OHCI (3.3V/98MHz)

8-bit TX/RX

5

64/128-BIT

MAIN MEMORY

2.6V/400MHZ

PAGE 37

MAIN MEMORY

8-BIT

HYPERTRANSPORT

1.2V/800MHZ

CONTROL = 2.5V

I2S

PAGE 25

SCCA SCCB

I2S1

PAGE 74

PCI

PAGE 25

GPIO/PCI64

I2S2I2S0

SERIES

TERM

PAGE 38

U7500

BOOTROM

32-bit PCI (5V-3.3V/33MHz)

4

J4000

J4001

DIMMS

PAGE 40

J7600

AIRPORT

EXTREME

CONNECTOR

PAGE 76

J9401

CTL-LESS /

SOFT MODEM

CONNECTOR

PAGE 94

PAGES 44&45

1 2 3

U7700

USB 2.0

uPD720101

PARALLEL

TERM

USB

PAGE 91

PCI

PAGE 77PAGE 75

4 5

3

U1300

SMU

PAGE 13

U1301

RTC

PAGE 13

12

D

J9210/J9220/J9230

USB

CONNECTORS

PAGE 92

J9240

BLUETOOTH

CONNECTOR

PAGE 92

C

B

U9500

S/PDIF

AUDIO CODEC

U8600

VESTA

GIG ETHERNET

A

4 Diff pairs

J8700

ETHERNET

CONNECTOR

PAGE 87

8

67

FIREWIRE A

PAGE 89PAGE 86

1

0

2 Diff pairs

J9000, J9001

FIREWIRE A

CONNECTORS

PAGE 90

5

PCM3052A

LINE IN

AMP

PAGE 97

J9800

LINE IN

CONNECTOR

PAGE 98

PAGE 95

J9802

MIC

CONNECTOR

PAGE 98

LINE OUT

AMP

PAGE 97

SPEAKER

AMP

PAGE 97

4

OPTICAL OUT

J9803

COMBO OUT

CONNECTOR

PAGE 98

LINE OUT

J9801

SPEAKER

CONNECTOR

PAGE 98

SYSTEM BLOCK DIAGRAM

SYNC_MASTER=N/A

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

SIZE

DRAWING NUMBER

051-6772

APPLE COMPUTER INC.

3

2

D

SCALE

NONE

SHT

2

1

SYNC_DATE=N/A

OF

102

A

REV.

11

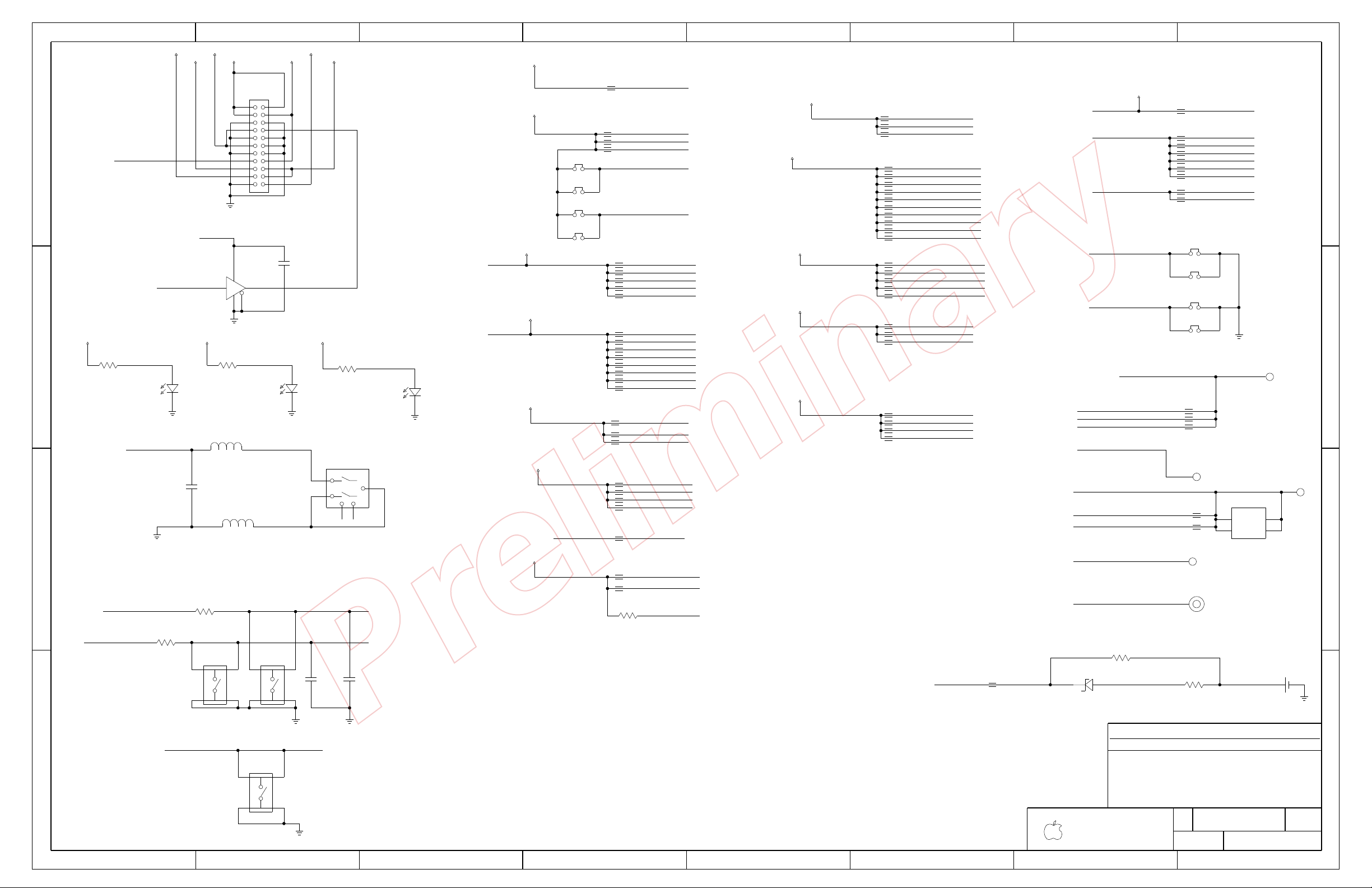

Page 3

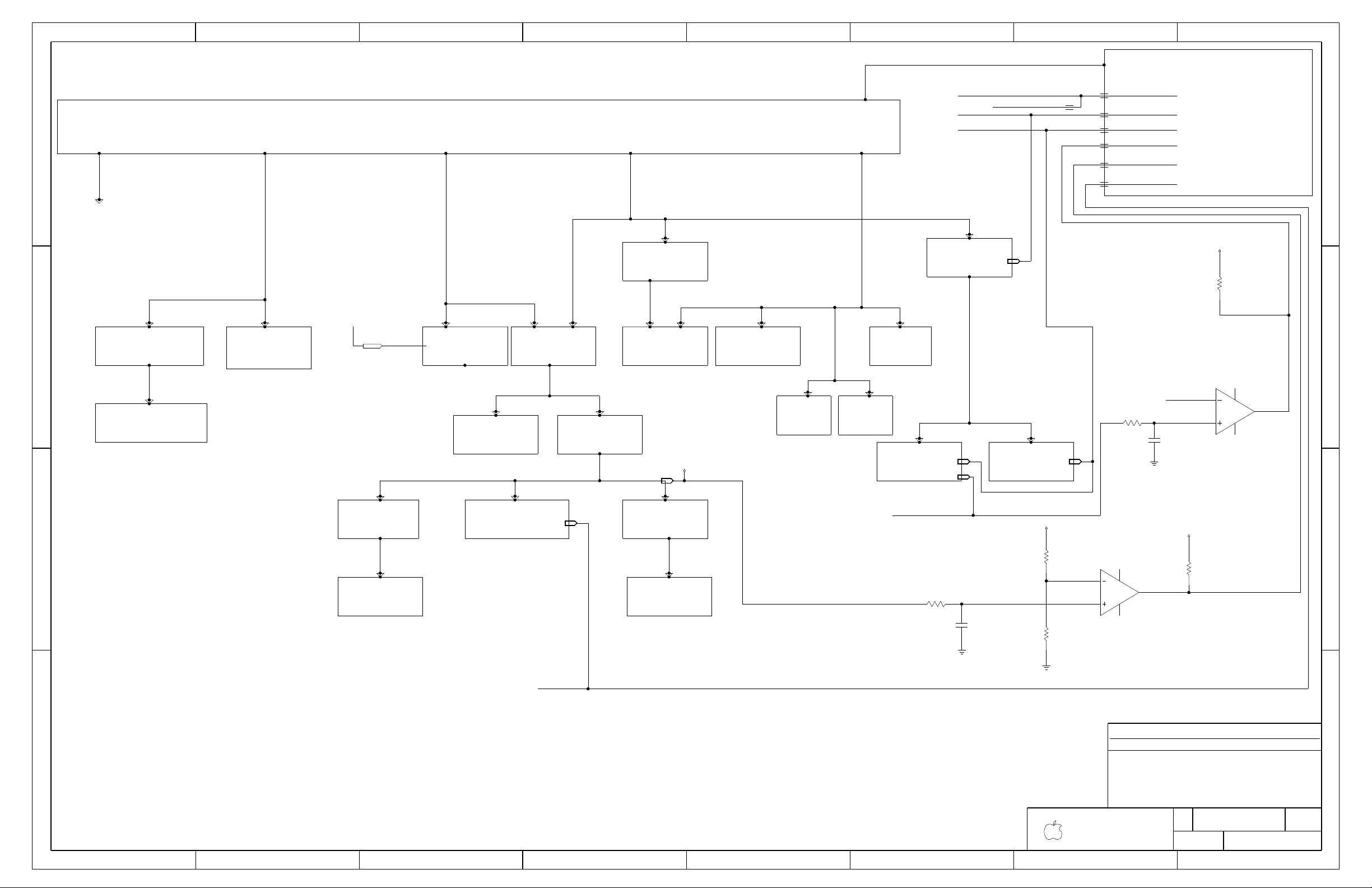

78

6

5

4

3

12

D

C

B

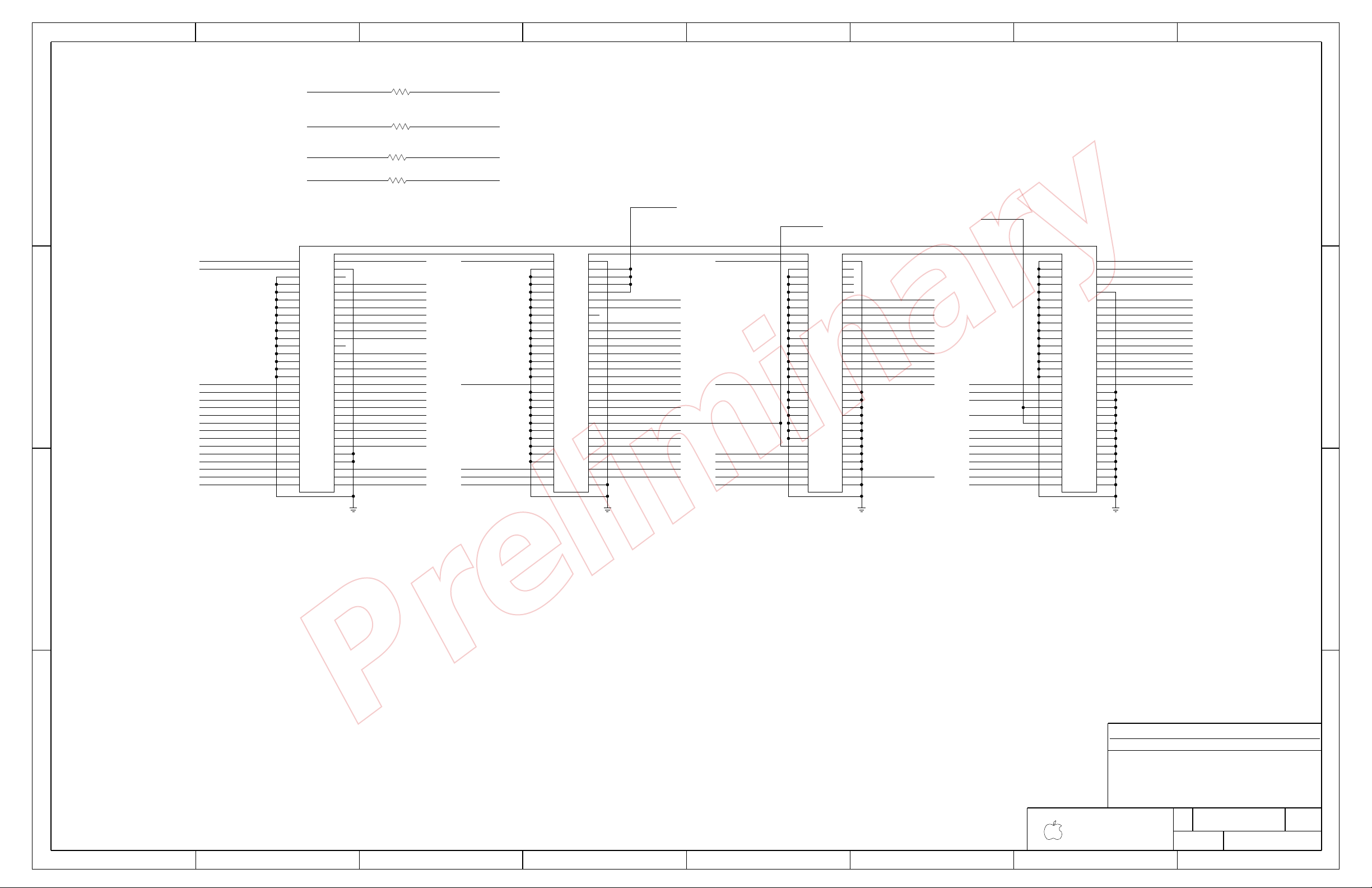

J700

PAGE 7

PP24V_RUN

PP5V_RUN_AUDIO

PAGE 99

5V

PP4V5_RUN_AUDIO

PAGE 99

4.5V

FW CONN

20" LCD INVERTER

LINEAR

LINEAR

HP/LINEOUT AMP

AUDIO CODEC

PP12V_RUN

CPU CORE

SWITCHER

PAGE 33

0.8~1.2V

20" PANEL POWER

20" LCD INVERTER

SC2643VX*1

SC1211*4

GPUL

=PP5V_RUN_CPU

ALIAS

PP2V5_RUN

FET SWITCH

PAGE 9

PP1V8_GPU

LINEAR

PAGE 50

POWER CONNECTOR

PP5V_RUN

HDD & OPTICAL

31

8 7

6

CPU_AVDD_EN

RAM TERM

GRAPHIC FB

PP2V5_RUN_CPU_AVDD

31

LINEAR

PAGE 31

2.8V

1.53V

GPU

CPU AVDD

U3LITE CORE

SWITCHER

PAGE 22

PP1V25_RAM_VTT

PAGE 46

1.3V

PP5V_PWRON

FET SWITCH

PAGE 11

5V

IRU3037CS

U3LITE CORE

LINEAR

2.59V

RAM VTT

PP5V_ALL

3.3V

USB CONN

3.3V

PP2V5_PWRON

SWITCHER

PAGE 9

IRU3037CS

SHASTA HT

DDR DIMM

IN

1.5V

PP3V3_ALL

LINEAR

PAGE 11

FW PHY

SMU

PP3V3_PWRON

FET SWITCH

PAGE 11

ENET PHY

USB2 HOST

MODEM & BT

PP2V5_PWRON

IN

PP1V5_PWRON

LINEAR

PAGE 50

PULSAR CORE

PP1V5_RUN

POWER SW

PAGE 50

AGP BUS

GPU CORE

SWITCHER

PAGE 50

1.20V

IRU3037ACS

RV351

PP1V8_TPVDD

PAGE 50

LINEAR

SYS_POWERUP_L

PP3V3_RUN

PCI BUS

AUDIO CODEC

PP2V5_GPU_A2VDD

PAGE 50

PP1V5_VDDC_CT

LINEAR

PAGE 50

PAGE 10

1.2V

LINEAR

GPU

GPUGPU

PP1V2_PWRON

FET SWITCH

PAGE 10

SHASTA CORE

PWRON_SD

PWRON_DISK_SB

=PPVCORE_PWRON_SB

6 7

23

R340

100K

1/16W

MF-LF

402

PULSAR_POWER_DOWN

MAKE_BASE=TRUE

TP_SMU_PWRSEQ_P1_0

MAKE_BASE=TRUE

TURN_ON_PP1V2_PWRON_L

10 10

=PULSAR_POWER_DOWN

27

5V

PP1V2_ALL

SWITCHER

IRU3037ACS

VESTA CORE

IN IN

IN

21

5%

1

C340

0.01UF

20%

16V

2

CERM

402

IN

PP1V2_RUN

FET SWITCH

PAGE 10

COMPARE_PP2V5

PP5V_ALL

HT BUS

1

R342

150K

5%

1/16W

MF-LF

402

2

PS_2V_REF

1

R343

100K

5%

1/16W

MF-LF

402

2

SYS_POWERUP_L

POWER SEQUENCE PIN

SMU_PWRSEQ_P1_4

SMU_PWRSEQ_P1_0

SMU_PWRSEQ_P1_1

SMU_PWRSEQ_P9_5

SMU_PWRSEQ_P9_6

SMU_PWRSEQ_P1_2

R330

100K

5%

1/16W

MF-LF

402

3

V+

U1100

GND

12

LM339A

SOI

6

7

RAIL_CTL_NEG

11

21

COMPARE_SB_CORE

1

C330

0.01UF

20%

16V

2

CERM

402

PP3V3_ALL

1

13

13

13

13

13

13

SMU

PP3V3_ALL

8

9

1

R341

10K

5%

1/16W

MF-LF

402

2

PWR_GOOD_PP2V5

(PWR_GOOD_SB_CORE)

(PWR_GOOD_PP2V5)

(TURN_ON_VTT)

1

R331

10K

5%

1/16W

MF-LF

402

2

PWR_GOOD_SB_CORE

3

LM339A

SOI

V+

U1100

GND

12

D

C

14

B

TURN_ON_VTT

46

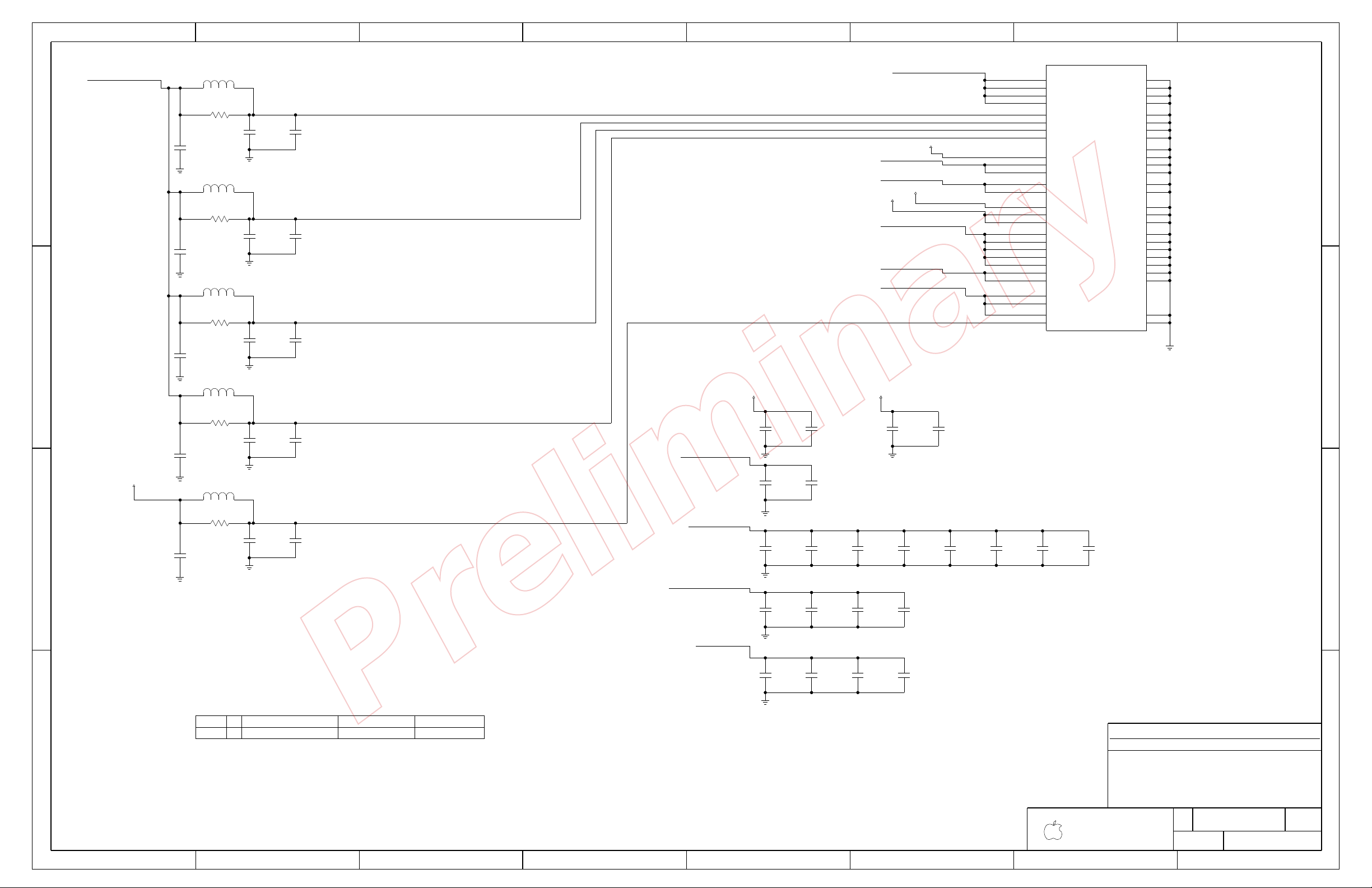

POWER BLOCK DIAGRAM

A

APPLE COMPUTER INC.

8

67

5

4

3

SYNC_MASTER=N/A

2

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

SIZE

D

SCALE

DRAWING NUMBER

NONE

051-6772

SHT

3

1

SYNC_DATE=N/A

OF

102

A

REV.

11

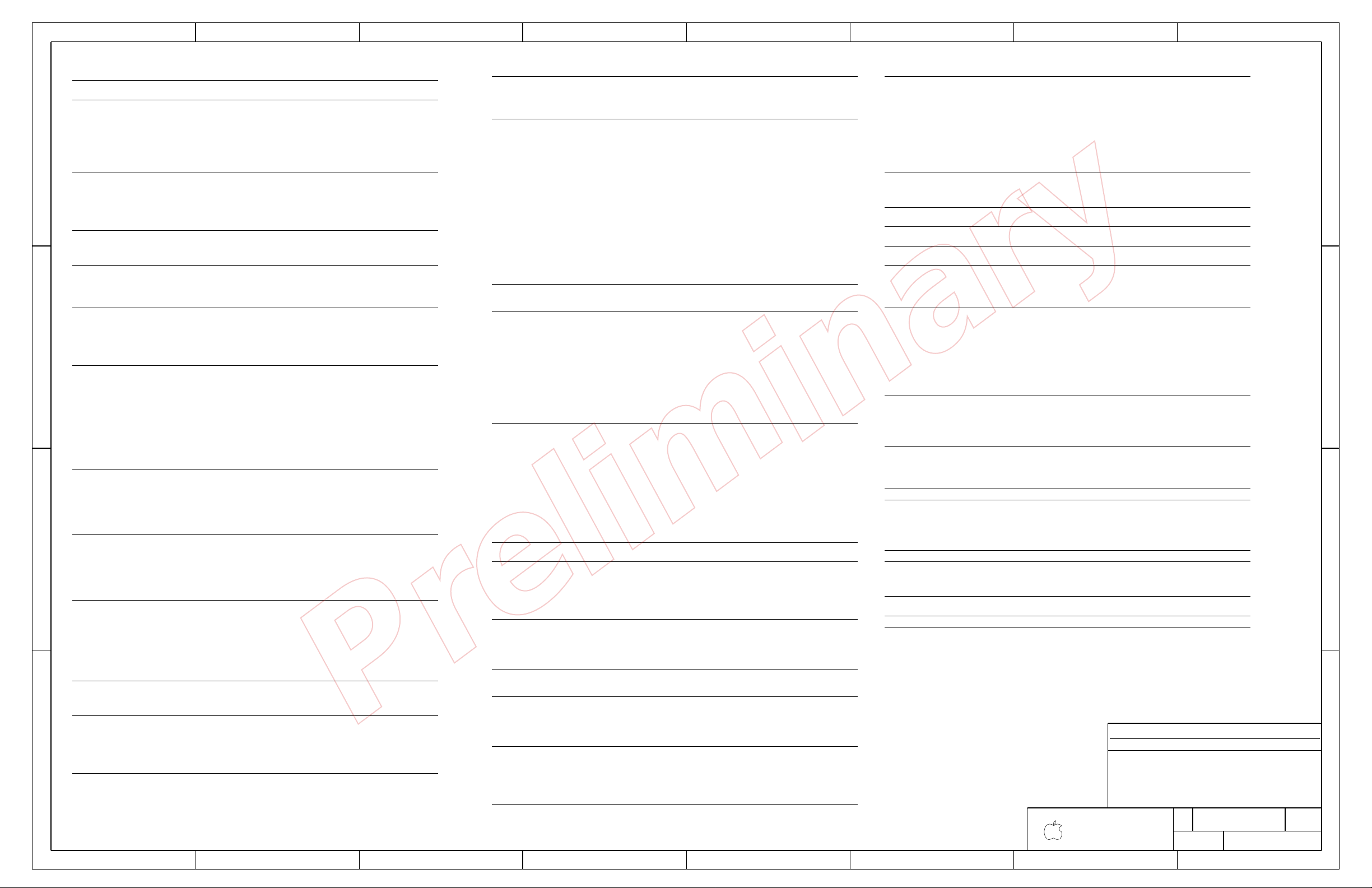

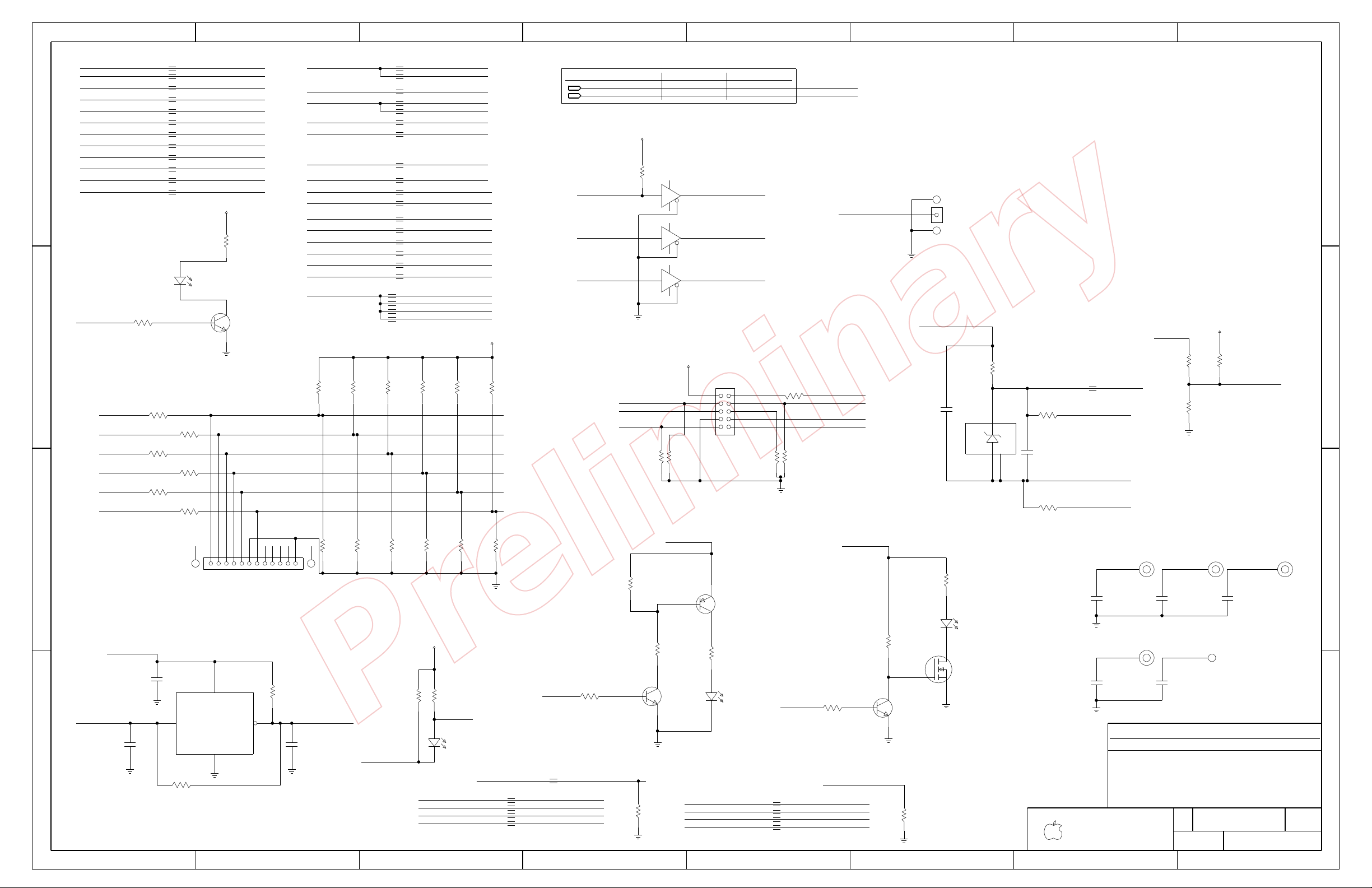

Page 4

78

6

5

4

3

12

DATE

10/20/04

10/21/04

D

10/22/04

10/26/04

10/28/04

11/01/04

C

11/03/04

11/04/04

11/06/04

B

11/07/04

11/08/04

11/09/04

A

11/10/04

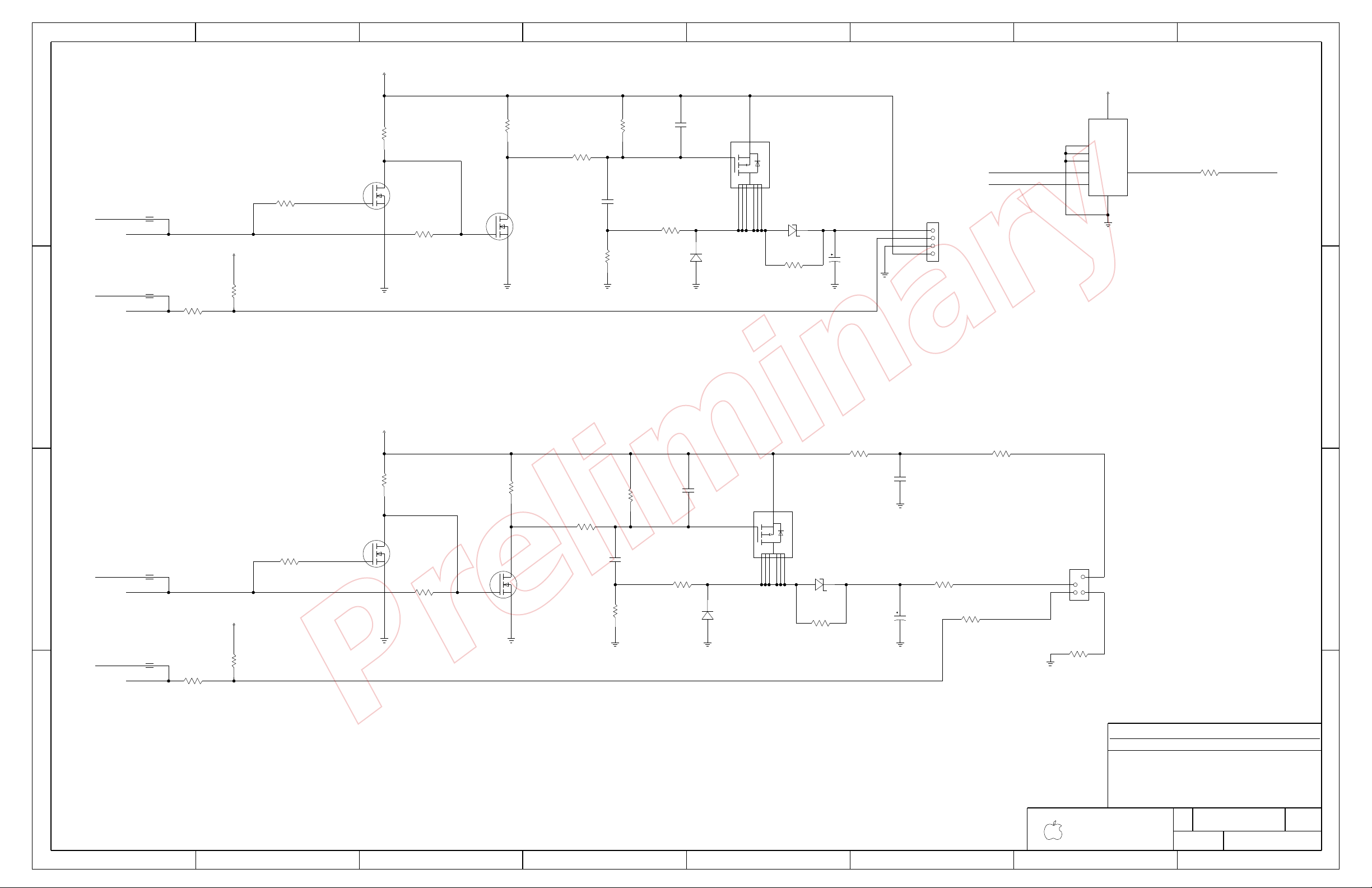

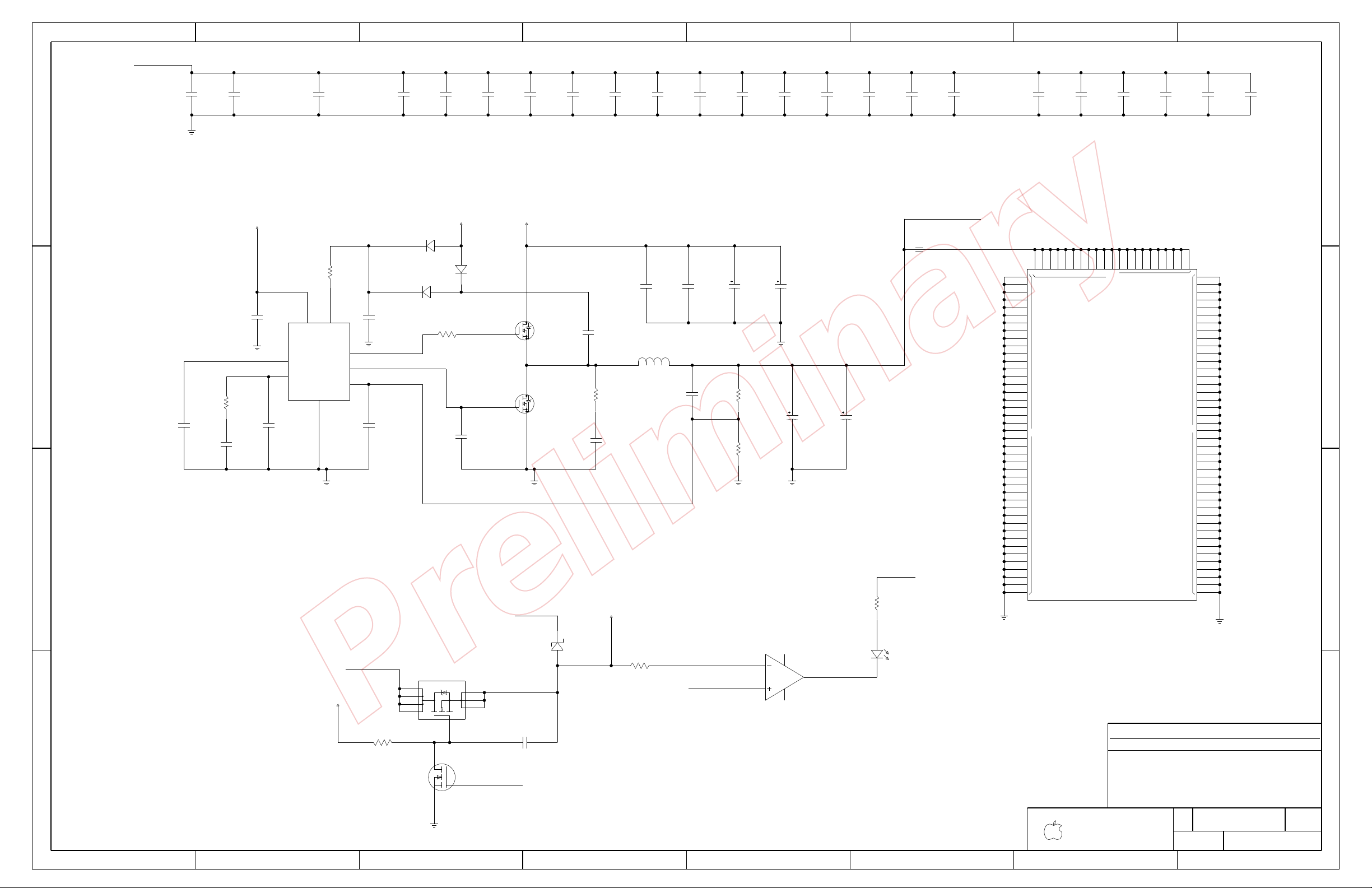

DESCRIPTION

CLONED DESIGN FROM GILA (Q45 A/B) REV G

CHECKIN 00002

ADDED VESTA

ADDED 1.2V REGULATOR FOR VESTA CORE

ADDED 2.5V LDO FOR VESTA

ADDED FW LATE VG PROTECTION

REMOVED BCM5231 ETHERNET PHY

REMOVED FW802A FW PHY

REMOVED FW PORT POWER CIRCUITRY

REMOVED MICRODASH CONNECTOR

CHECKIN 00003

REMOVED NV18/34 GPU

REMOVED AGP VREG (VR5001)

REMOVED GPU VTT VREG

ADDED 2.5V VREG FOR A2VDD

REMOVED EXTERNAL TMDS TRANSMITTER

ADDED RV351LE GPU

CHECKIN 00004

GPU CORE POWER UPDATES

ADDED VESTA ETHERNET LOWPWR CIRCUIT

ADDED DEVELOPMENT LEDS FOR VESTA ENET

CHECKIN 00005

CONNECTED FRAME BUFFER

ADDED 1.8V GPU VREG

CONNECTED GPU TMDS AND VGA

CONNECTED GPU POWER AND POWER FILTERS

CHECKIN 00006

ADDED VOLTAGE, LINE WIDTH, AND NECK WIDTH PROPERTIES FOR GRAPHICS (IN MM)

TIED PPVCORE_NB DIRECTLY TO PP1V5_PWRON (REMOVED R707)

REPLACED EMC FERRITES WITH 0 OHM RESISTORS FOR GRAPHICS AND FANS

REMOVED VESTA CORE REGULATOR

REPURPOSED 1.2V REGULATOR FOR VESTA AND SHASTA

CHANGED FW LATE VG CIRCUITRY TO MATCH Q78 & Q86

CHECKIN 00007

<RADAR 3848831> MOVED SMU RESET BUTTON TO DEVELOPMENT BOM

<RADAR 3849762> MOVED SMU DOWNLOAD CONNECTOR TO DEVELOPMENT BOM

<RADAR 3849798> REDUCED CAPACITANCE OF C1100 & C1102

MASTER PAGE SYNC:

FRAME BUFFER SWAPS FOR CLEANER ROUTING

REMOVED VESTA ROM

AUDIO COST REDUCTIONS <RADAR 3849747 & 3849751>

AUDIO 3052A CODEC

ADDED 1.55V VREG FOR GPU VDDC_CT

MOVED VTT VREG TO 2.5V PWRON TO REDUCE CURRENT THROUGH Q903

CHANGED FETS IN GPU CORE FOR COST REDUCTION

ADDED SPACING & PHYSICAL CONSTRAINTS TO FRAME BUFFER

CHECKIN 00008

REMOVED 1.6GHZ PROCESSORS

CHANGED VOLTAGE SETTING OF 2.5V VREG TO 2.588V FROM 2.62V

1.2V VREG COST REDUCTIONS - Q1002 TO NTD60N02R; C1002/3 TO 10UF CERM

U2850 - REMOVED MAXIM AS AN ALTERNATE

MOVED GPU ZENER DIODES TO VREG PAGE SINCE THEY SHOULD BE PLACED NEAR THE VREGS

ADDED 8MX32 GRAPHICS MEMORY

ADDED GIGABIT ETHERNET CONNECTOR

CHECKIN 00009

ADDED GPU STRAPS

CONNECTED GPU GPIOS

REMOVED ON BOARD POWER SUPPLY TEMP SENSOR

ADDED AMBIENT LIGHT SENSOR CONNECTOR

CONNECTED GPU TEMP SENSOR

REMOVED CPU VREG 4TH PHASE

ADDED DEVELOPMENT LEDS TO REGULATORS

CHECKIN 00010

ADDED MORE GPU CONSTRAINTS

<RADAR 3616348, 3621390> CHANGED FL5900-2 TO 220 OHM

<RADAR 3848846> 2.5V RUN FET COST REDUCTION

<RADAR 3848859> 1.2V, 1.5V RUN FET COST REDUCTIONS

<RADAR 3848887> 5V & 3.3V PWRON FET COST REDUCTIONS

<RADAR 3849622> STUFFED AROUND TMDS FILTERS

<RADAR 3849656> STUFFED AROUND RGB FILTERS

<RADAR 3849806> CHEAPER SMU CRYSTAL

<RADAR 3849857> CHEAPER USB2 CRYSTAL

BOM RELEASE REV 01

FRAME BUFFER PIN SWAPS

<RADAR 3848846> UPDATE OF 2.5V RUN FET COST REDUCTION

<RADAR 3849743> ADDED RESISTORS TO STUFF AROUND USB FILTERS

CHECKIN 01001

<RADAR 3848850> REGULATOR COST REDUCTIONS

<RADAR 3849767> 2.5V VREG COST REDUCTIONS

<RADAR 3849772> REMOVED OUTPUT CAP ON 1.2V_ALL VREG

<RADAR 3849820> SHASTA FILTER COST REDUCTION

<RADAR 3849854> GPU CORE VREG COST REDUCTION

<RADAR 3865344> SET GPU VDDC_CT VREG TO 1.55V

CHECKIN 01002

CHANGED SOURCE OF Q1003 TO PP1V2_ALL

RGB TERMINATION NOW CONNECTED TO DIGITAL GROUND

WHITE LED - CHANGED INDUCTORS TO 0 OHM RESISTORS

UPDATED POWER BLOCK DIAGRAM

CHECKIN 01003

<RADAR 3848850> 2.5V VREG COST REDUCTION

CHECKIN 01004

P

11/15/04

11/16/04

11/18/04

11/20/04

11/22/04

11/23/04

12/02/04

12/07/04

re

12/09/04

12/13/04

12/14/04

12/15/04

ADDED REGULATOR FOR GPU TPVDD

ADDED POWER SEQUENCING FOR GRAPHICS REGULATORS

ADDED TEST POINTS TO GRAPHICS FOR EXOR TESTING

REMOVED EXTERNAL S/PDIF TRANSMITTER

CHECKIN 01005

REMOVED P50 AIRPORT AND Q23 BLUETOOTH CONNECTORS, HOLES, & STANDOFFS

ADDED Q85 AIRPORT & BLUETOOTH CONNECTOR

CHECKIN 01006

(PP 16,17) REPLACED FAN CONTROL WITH NEW CIRCUIT

(P 76) FINISHED CONNECTING Q85 CONNECTOR

(P 7) ADDED PLATED HOLE ZH710 FOR TMDS GROUNDING

(P 7) TIED BOTH EI RAILS TO 1.5V

(P 5) NEW BOOTROM P/N

(P 9) ADDED EXTRA 10UF INPUT CAP

(P 12) VESTA_ENET_LOWPWR UPDATE

(P 18) <RADAR 3878118> MOVED SMU I2C E BUS

(P 22) CHANGED Q2250 TO 376S0143

(P 46) SLEEP SIGNAL TURNS OFF VTT VREG

(P 58) REPLACED THERMAL SENSOR WITH LM63

(P 59) TIED UNUSED BUFFER ENABLE PINS HIGH

(P 90) FIXED FW PORT NAMING

(P 90) CHANGED R9090 TO 665 OHM

(P 91) CHANGED USB2 CHIP GROUNDING

(P 8) ALIASED VESTA JTAG TO TEST POINT NETS

(P 9) <RADAR 3848846> ADDED PAD FOR 1NF CAP TO GATE OF Q903

CHECKIN 01007 / BOM RELEASE REV 02

ADDED PHYSICAL CONSTRAINTS

AUDIO STUFFING CHANGES

CHECKIN 02001

(P 36) CONNECTED NEW CPU DIODE REFERENCE

(P 77) USB2 IDESEL - NOW FROM USB2 SIDE

(P 56) ADDED BOMOPTIONS FOR MEMORY STRAPS

(PP 56, 58) CONNECTED PWM FROM RV351LEP & PUT IN PROTO WORKAROUND

(P 25) <RADAR 3849835> NEW SHASTA XTAL

(P 62) <RADAR 3849855> SHASTA HT_PLL FILTER COST REDUCTION

(P 91) <RADAR 3849858> USB CAP COST REDUCTION

(P 76) ADDED STANDOFFS FOR Q85 CARD

(PP 16,17) NEW FAN CIRCUIT CAPS (C1603, C1653, C1703)

(P 50) <RADAR 3865344> VDDC_CT SET TO 1.50V

(P 50) <RADAR 3877855> TP_VDD SET TO 1.80V

(P 12) VESTA_ENET_LOWPWR UPDATE

(PP 10, 22, 34, 50) USED COMPARATOR FOR LOW VOLTAGE RAIL LEDS

CHECKIN 02002

(P 49) CONNECTED AGPTEST RESISTOR TO VDDP

(P 56) ADDED PADS FOR STRAPPING RESISTORS TO GPU_GPIO<14>

(P 58) ADDED CONSTRAINT SETS

(P 59) STUFFED AROUND Q5900 PANEL PWR SEQUENCING

(P 59) LED 3 NOW DRIVEN FROM FPD_PWR_ON

(P 3) CONNECTED SHASTA CORE POWER FOR POWER SEQUENCING

(P 76) FIXED PCI_CBE_L<1> CONNECTION

MORE PHYSICAL & SPACING UPDATES

(P 83) <RADAR 3890225> OPTICAL DRIVE CONNECTOR CHANGED TO 516S0235

CHECKIN 02003

(P 56) ADDED OPTION OF USING PWM FROM SHASTA

<RADAR 3849718, 3849767, 3849854> MADE ON & VISHAY FETS TRUE ALTERNATES

(P5) ADDED U3L W/ NEW LAMINATE AS ALTERNATE

(P 16) C1653 - REPLACED WITH LOWER HEIGHT CAP

CHECKIN 02004

(P 76) TABLED IN NEW STANDOFFS FOR Q85 CARD

PROTO RELEASE (REV 3)

(P 90) FIXED ALIAS PROBLEM WITH FW_TPB2_PD

(P 90) FIXED FW_CPS SHORT

l

(P 35) REMOVED DS3500 & DS3501

(P 83) REMOVED SECOND SATA CONNECTOR

CHECKIN 03001

CONVERTED DISCRETES TO LEAD FREE

CHECKIN 03002

CHANGED U7700 BACK TO LEADED PART

(P 5) REMOVED ORIGINAL U3LITE (NEW LAMINATE ONLY FOR C/D)

(P 49) CHANGED GPU TO RV351LEP (338S0231)

(P 76) NOW HAVE CORRECT SYMBOL FOR STANDOFFS

(P 76) J7650 - NEW TO ALLOW 5MM CONNECTED HEIGHT

BOM RELEASE REV 04

CHANGED ALIASES TO SYNONYMS

CHANGED LINE AND NECK WIDTHS TO METRTIC

CHECKIN 04001

ADDED 2.0 GHZ AND ADDITIONAL 1.8 GHZ ALTERNATE PROCESSORS TO PG. 5 TABLE

VESTA XTAL: R5815=249, R8609=332, R8921=332

VESTA ENET: R1262=10K, C1260=10U, R1251=NO STUFF, C1250=2.2U

FANS: NO STUFF DZ1601, DZ1651, DZ1701

STUFFED R1604, R1654, R1704

CHECKIN 04002

2.5 V REGULATOR - NEW NARROWER OUTPUT CAPS (C908, C909)

(P 46) REMOVED SEMTECH REGULATOR, ADDED RICHTEK AS ALTERNATE VTT

(P 16) CHANGED FAN1 OUTPUT CAP BACK TO THROUGH-HOLE

(P 59) SWAPPED INVERTER CONNECTOR GENDER

CHECKIN 04003

(P 46) RICHTEK VTT UPDATES

BOM RELEASE REV 5

(P 6) ADDED NO_TESET PROPERTIES

(P 12) VESTA ENET LOW POWER FIX

CHECKIN 05001

i

i

m

12/16/04

12/17/04

12/20/04

01/11/05

01/18/05

01/25/05

01/27/05

a

02/01/05

n

02/03/05

02/04/05

02/08/05

02/09/05

02/10/05

02/15/05

02/16/05

02/17/05

FIXED I2C_TMDS_SDA/SCL ON P 6

(P 46) NOSTUFF RICHTEK VTT VREG

(P 59) STUFFED TMDS CHOKES

(P 56) USING PWM FROM ATI GPU

(P 38) FIXED MIN_NECK_WIDTH ON TD1 AND TD2

(P 92) ADDED NET_PHYSICAL_TYPE = USB2 TO TABLE

(P 7) ADDED BATTERY SAFETY BYPASS OPTION (NOSTUFF)

CHECKIN 05002

(P 50) ADDED Q5000 TO INPUT OF GPU VCORE VREG

(P 6) REMOVED SOME FUNC_TEST PROPERTIES

(P 50) GPU_VDCC_CT POWER SEQUENCING

CHECKIN 05003

(P 6) ADDED/REMOVED MORE FUNC_TEST PROPERTIES

CHECKIN 05004

(P 50) GPU POWER SEQUENCING

CHECKIN 05005

MINOR TEXT/COMMENT CHANGES

EVT RELEASE (REV 6)

(P 5) REMOVED BRA FROM ALTERNATE PROCESSOR TABLE, REPLACED BPA WITH BNA

(P 5) NEW SMU PART NUMBER

CHANGED SDF7601 TO PART 860-0567

BOM RELEASE REV 7

(P 5) CORRECTED 1.8GHZ CPU APPLE P/N FROM 337S2969 TO 337S2998 ON ALTERNATE PROCESSOR TABLE

(P 12) NOSTUFF Q1250 TO DISCONNECT ENETFW_RESET FROM SHASTA GPIO

(P 5) CORRECTED SMU PART NUMBER TO 341T1703

(P 16, 17) HAROLD’S FAN CIRCUIT CHANGES

CHECKIN 07002

(P 25) REPLACED R2566 WITH 0 OHM TO ELIMINATE FW_LOWPWR GLITCH

ADDED 0 OHM (R2570, NOSTUFF) TO BREAK FW_LOWPWR FROM SHASTA

(P 56) STUFF R5610 TO PULL DOWN ATI_PWM SIGNAL TO ELIMINATE GLITCH

(P 27,28,29) CONNECTED CPU_APSYNC FROM U3LITE AND DISCONNECTED FROM PULSAR

(P 11) CHANGED C1102 TO 16V FOR SUPPLY AND COST ISSUES

(P 5) ADDED KQA (337S3093) TO ALTERNATE PROCESSOR TABLE

CHECKIN 07003

(P 5) MODIFIED PROCESSOR TABLE TO MATCH IBM’S TABLE, AGAIN.

BOM RELEASE REV 8

(P 75) BOOTROM REFLASHING ISSUE FIX: CHANGED R7502 TO 470 OHM

(P 12) ENET_LOWPWR GLITCH FIX:ADDED A CLAMP CIRCUIT FOR ENET_LOWPWR GLITCH

(P 10,22) SHASTA & U3LITE VCORE POWER IMPROVEMENT: STUFF C1005 AND C2205 WITH 2200PF CAPS

(P 13) CHANGED U1301 TO LEADED PART (353S0653) DUE TO SUPPLY

(P 5) ADDED 34S0284 AND 34S0282 AS U3LITE ALTERNATES (OLD LAM)

BOM RELEASE REV 9

(P 28) CHANGED APSYNC SERIES TERMINATION R2806 TO 10 OHM

(P 5) ADDED LEAD FREE PARTS AS ALTERNATE FOR U1301 & VRA201 DUE TO SUPPLY

(P 8) REMOVED SMU DOWNLOAD CONNECTOR FROM DEVELOPMENT BOM

(P 92) STUFFED USB COMMON MODE CHOKES FOR EMC

CHECKIN 09002

(P 50) <RADAR 3919121> NOSTUFF U5090 AND RELATED COMPONENTS, STUFFED R5092 FOR 1.5V GPU VDCC_CT

(P 7) REMOVED ZH701

(P 12) STUFF R1251, CHANGE C1250 TO 10UF, R1262=100K TO LENGTHEN VESTA RESET AND LOWPWR DELAY

(P 59) <RADAR 3849662> STUFFED PANEL POWER SEQUENCING FOR BOTH 17 AND 20 INCH

CHECKIN 09003

(P 92) <RADAR 3742725> CHANGED USB COMMON MODE CHOKES TO 120-OHM 155S0232

(P 59) NOSTUFF R5950, STUFF R5923 FOR 17 INCH PANEL POWER FROM PP3V3_RUN INSTEAD OF PP3V3_ALL

CHECKIN 09004

(P 59) <RADAR 3919083> CHANGED R5971 AND R5972 TO 33 OHMS

(P 56) <RADAR 3960901, 4000359> GPU GPIO GLITCH STUFFED: U5600, U5601, NOSTUFF: R5609, R5621

DVT RELEASE (REV 10)

(P 56) <RADAR 3960901, 4000359> GPU GPIO GLITCH STUFFED: C5600, C5601

(P 12) CHANGED C1250 TO 6.3V PART, TO MATCH A PART ALREADY ON THE BOM

(P 5) ADDED 353S0687 (LEADED) AS ALTERNATE FOR 353S0959 (LEAD FREE) U9800

ADDED PAGE TITLE PROPERTIES FOR SCHEMATIC REUSE WITH M23/M33

(P 12) YET ANOTHER VESTA RESET/LOWPWR STUFFING CHANGE

(P 16,17,36) ADDED SIGNAL ALIASES FOR SCHEMATIC REUSE WITH M23

(P 50) RE-STUFFED GPU 1.5V VDCC_CT BECAUSE OF LEAKAGE WORRIES

BOM RELEASE REV 11

ry

NO STUFF: R2768,R2772,R2805,R2910

STUFF: R2806,R2911

11

SYNC_MASTER=N/A

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

SIZE

DRAWING NUMBER

051-6772

APPLE COMPUTER INC.

D

SCALE

NONE

SHT

4

SYNC_DATE=N/A

OF

102

D

C

B

A

REV.

11

8

67

5

4

3

2

1

Page 5

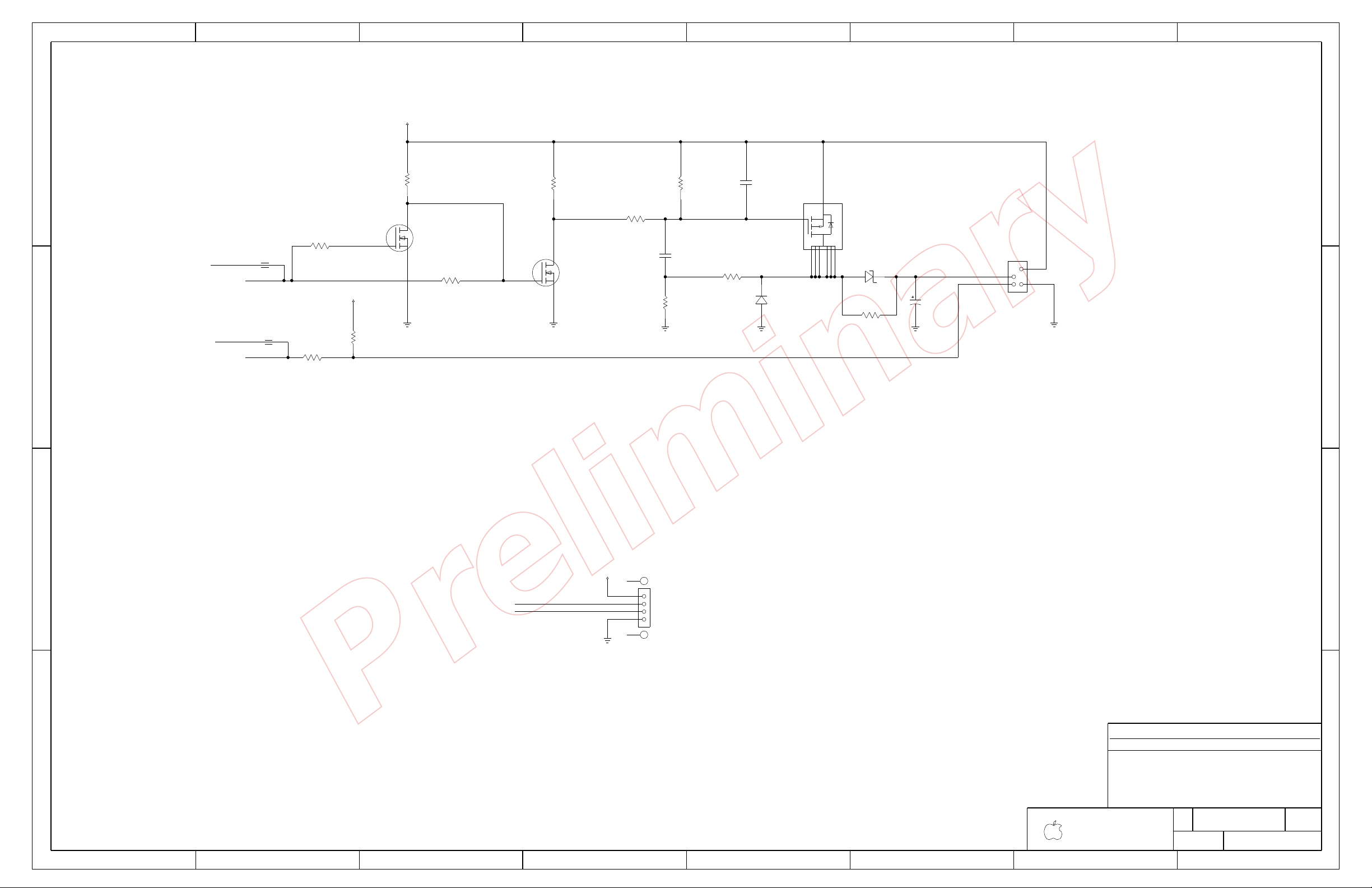

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_5_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_11_HEAD

TABLE_11_HEAD

REFERENCE DESIGNATOR(S)

BOM OPTION

QTY

DESCRIPTION

VALUE VOLT. WATT.

TOL.PART #

PACKAGE

DEVICE

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_5_ITEM

REFERENCE DESIGNATOR(S)

BOM OPTION

TABLE_5_HEAD

QTY

DESCRIPTION

PART#

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_11_HEAD

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

ALTERNATES

ASICS

MISC PARTS

QUALIFIED

VOLTAGE

1.20V

1.25V

1.20V

1.25V

1.25V

1.25V

PROCESSORS

1.15V

337S3056 337S3055

IC,DD3.1,2.0G,KRA

CPU_2_0GHZ

U2900

DS1338, L-F PART

353S0653

U1301

353S0958

353S0959 MAX9722 LEAD

U9800

353S0687

378S0119

KINGBRIGHT LED

LED700,LED702,LED5900

378S0114

VPP1

1

062-2082

SPEC,VENDOR PACKAGING PROCEDURE

IC,DD3.0,1.8G,BPA

CPU_1_8GHZ

U2900

337S3060337S2969

337S3055337S3059

IC,DD3.0,2.0G,CRA

CPU_2_0GHZ

U2900

U2900

CPU_2_0GHZ

337S3058

IC,DD3.0,2.0G,CPA

337S3055

U2900

CPU_2_0GHZ

IC,DD3.1,2.0G,KQA

337S3093 337S3055

U3L,OLD LAM,300MM

343S0284 343S0320

U3

CBGA-576-1MM

IC,GPUL,DD3.1,2.0G,85C,KPA

337S3055

PROCESSOR

42W ?

U29001.20V

2.0GHZ

CPU_2_0GHZ

1

1

343S0324

U8600

IC,ASIC,VESTA,V1.3

U31

343S0320

IC,U3LITE,NEW LAM,300MM,PBGA

MECH17

CRITICAL

17_INCH_LCD

1

603-6015

HEAT SINK ASSEMBLY 17 IN

U3L,OLD LAM,200MM

343S0282U3343S0320

102

5

11

051-6772

SYNC_MASTER=N/A

SYNC_DATE=N/A

TABLE ITEMS

IC,GPUL,DD3.1,1.8G,85C,JPA

CBGA-576-1MM

PROCESSOR

1.8GHZ

1.20V

337S3060

CPU_1_8GHZ

U2900

?1 42W

IC,DD3.1,1.8G,JRA

337S3061

U2900

CPU_1_8GHZ

337S3060

U2900

CPU_1_8GHZ

337S3060337S2970

IC,DD3.0,1.8G,BRA

353S0733

VRA201

MAX8510,L-F PART

353S0960

MOSFET,N-CH,VISHAY

376S0207

Q3311,Q3321,Q3411

376S0146

820-1747

1

MLB1

PCB,FAB,MLB

LBL1

1

825-6447

BARCODE LABEL, MLB, Q45

051-6772 SCH1

1

PCB,SCHEM,MLB

1

U7500

341T1667

IC,FLASH,1MX8,3.3V,90NS

U1300

IC,SMU,Q45C/D

1

341T1703

376S0204

MOSFET,N-CH,VISHAY

Q3310,Q3320,Q3410

376S0130

MECH20

CRITICAL

1

20_INCH_LCD

603-6016

HEAT SINK ASSEMBLY 20 IN

U3

U3L,NEW LAM,200MM

343S0321 343S0320

343S0283

1

U2300

IC,ASIC,SHASTA,V1.1,PBGA

Preliminary

Page 6

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

2 TEST POINTS

2 TEST POINTS

5 TEST POINTS

GENZ SHOULD USE J1400 FOR THE FOLLOWING NETS:

2 TEST POINTS

2 TEST POINTS

2 TEST POINTS

2 TEST POINTS

2 TEST POINTS

2 TEST POINTS

10 TEST POINTS

5 TEST POINTS

5 TEST POINTS

12 TEST POINTS

5 TEST POINTS

5 TEST POINTS

2 TEST POINTS

5 TEST POINTS

I307

I337

I338

I344

I345

I346

I347

I348

I349

I350

I354

I355

I356

I357

I358

I359

I360

I361

I362

I363

I364

I365

I371

I372

I373

I374

I375

I376

I377

I378

I379

I380

I381

I382

I383

I384

I385

I386

I387

I388

I389

I390

I391

I392

I393

I394

I395

I396

I397

I398

I399

I400

I401

I402

I403

I404

I405

I406

I407

I408

I428

I429

I430

I431

I432

I433

I434

I435

I436

I437

I438

I439

I440

I441

I442

I443

I444

PP5V_ALL

PP12V_RUN

PP5V_RUN

PP3V3_PWRON

PP5V_PWRON

PP2V5_RUN

PP1V5_RUN

PP1V2_PWRON

PP3V3_RUN

12 11

7

18 11 10

7

50 34 22 18 11 10

7

83

7

83

7

18 11

58 27 18 11

23

7 3

13

8 7

31

8 7 3

35 34 33

7

22

34 33

33

33

8 7

13

7

7

7

13

8

50 46 22 11 10

9 8

33 13 11 10

7

13

8

22

9

59 58

59 58

59 58

83 80

83 80

83 80

83 80

83

83 80

83 80

83 80

6

83 80

6

83 80

83

83

83

83

33

8

36

36

36

36 33

36

36 33

59

59

59

59

59 58

59

59

59

59

59

59

77 76 75 74 73

77 76 74 73

8

76 74

76 74

76 25

77 76 74 73

74 56

8

77 76 74 73

77 76 74 73

77 76 74 73

77 76 74 73

77 76 74 73

76 75 74

76

76 75 74

76 75 74

76

76 75

76

76

92

92

92

92

92

92

92

92

92

94 25

94 25

94 25

94 25

94 25

94 25

94 25

59

59

59

59

59

59

59

6

59

6

59

7

101

25

75

PP24V_RUN

36 31

I781

I782

I784

I785

I786

I787

I788

I789

I790

I791

I792

I793

I794

I795

I796

I797

I798

I799

I800

I801

I802

I803

I804

I805

I806

I807

I808

I809

I810

101

90

101

101

18 17

18 17

25 18

25 18

36 33 31

36 33 31

59

6

59

6

83

I824

I825

I826

I827

I828

I829

I830

I831

I832

I833

I834

I835

I836

I837

I838

I839

I840

I841

I842

I843

I844

I845

I846

I847

I848

I849

I850

I851

I852

I853

I854

I855

I856

I857

I858

I860

I861

I866

I867

I868

I869

I870

I871

I872

I873

I874

I875

I876

I878

I879

I880

I881

I882

I883

I884

I885

I886

I887

I888

I889

I890

I891

I892

I893

I894

I895

I896

I897

I898

I899

I900

I901

I902

I903

I904

I905

I906

I907

I908

I909

I910

I911

I912

I913

I914

I915

I916

I917

I918

I919

I920

I921

I922

I923

I924

I925

I926

I927

I928

I929

I930

I931

I932

I933

I934

I935

I936

I937

I938

I939

59

59

59

59

59

59 58

59 58

051-6772

102

6

11

SYNC_MASTER=N/A

SYNC_DATE=N/A

FUNC TEST

PP5V_ALL

FUNC_TEST=YES

PP12V_RUN

FUNC_TEST=YES

PP5V_RUN

FUNC_TEST=YES

GND

FUNC_TEST=YES

PP3V3_PWRON

FUNC_TEST=YES

PP5V_PWRON

FUNC_TEST=YES

PP2V5_RUN

FUNC_TEST=YES

PP1V5_RUN

FUNC_TEST=YES

PP1V2_PWRON

FUNC_TEST=YES

FUNC_TEST=YES

PP3V3_RUN

PP24V_RUN

FUNC_TEST=YES

TP_NEC_NANDTEST

NO_TEST=YES

FUNC_TEST=YES

VGA_HSYNC_R

NO_TEST=YES

TP_SB_NC_U6

TP_SB_NC_V3

NO_TEST=YES

NO_TEST=YES

TP_SB_NC_V2

TP_SB_NC_V4

NO_TEST=YES

NO_TEST=YES

TP_SB_NC_Y1

TP_SATA_CLK25M

NO_TEST=YES

NO_TEST=YES

Q2202_DRAIN

NO_TEST=YES

R904_P2

NO_TEST=YES

U5000_SS

NO_TEST=YES

U5000_GATE_L

U5000_GATE_H

NO_TEST=YES

LED802_1

NO_TEST=YES

NO_TEST=YES

PCI_CLK66M_SB_INT_R

NO_TEST=YES

PN1

PCI_CLK_P4_R

NO_TEST=YES

PCI_CLK_P3_R

NO_TEST=YES

HT_CLK66M_SB_R

NO_TEST=YES

TP_USB2_PWREN<4>

NO_TEST=YES

NO_TEST=YES

TP_NEC_NTEST1

TP_PLS_TEST2

NO_TEST=YES

NO_TEST=YES

TP_SB_NC_P7

NO_TEST=YES

TP_SB_NC_T3

FUNC_TEST=YES

=PP12V_DISK

NO_TEST=YES

EI_CPU_SYNC_R

EI_NB_SYNC_R

NO_TEST=YES

NO_TEST=YES

RFBD<16>

FUNC_TEST=YES

U2200_FEEDBACK

NO_TEST=YES

U900_VC

NO_TEST=YES

U900_VC_D

UATA_DASP_L_DS

NO_TEST=YES

NO_TEST=YES

U900_VC_R

TP_PCI_CLK_P4

NO_TEST=YES

U900_COMP

NO_TEST=YES

NO_TEST=YES

U2200_VC

U2200_VC_D

NO_TEST=YES

U2200_VC_R

NO_TEST=YES

TP_USB2_PWREN<0>

NO_TEST=YES

TP_USB2_PWREN<1>

NO_TEST=YES

TP_SB_NC_T8

NO_TEST=YES

TP_SB_NC_T7

NO_TEST=YES

NO_TEST=YES

TP_SB_NC_T6

NO_TEST=YES

TP_NEC_SRDATA

NO_TEST=YES

TP_NEC_SMI_L

TP_USB2_PWREN<3>

NO_TEST=YES

NO_TEST=YES

TP_USB2_PWREN<2>

TP_PSYNCOUT

NO_TEST=YES

NO_TEST=YES

TP_PSRO2

NO_TEST=YES

TP_AFN

TP_ATTENTION

NO_TEST=YES

TP_AGP_MB_AGP8X_DET_L

NO_TEST=YES

Q803_B

NO_TEST=YES

LED801_1

NO_TEST=YES

PN3

NO_TEST=YES

NO_TEST=YES

Q801_B

NO_TEST=YES

Q802_E

Q1002_DRAIN

NO_TEST=YES

NO_TEST=YES

Q800_D

NO_TEST=YES

RFBD<33>

NO_TEST=YES

RFBD<32>

FUNC_TEST=YES

USB_BT_P

USB2_PORT2_P_F

FUNC_TEST=YES

SYS_POWER_BUTTON_L

FUNC_TEST=YES

FUNC_TEST=YES

VCORE_SENSE_GND

USB2_PORT1_N_F

FUNC_TEST=YES

USB2_PORT1_P_F

FUNC_TEST=YES

NO_TEST=YES

Q5001_GATE

NO_TEST=YES

U3410_DRN

NO_TEST=YES

U5000_VC

U5000_FEEDBACK

NO_TEST=YES

NO_TEST=YES

U5000_COMP

RFBD<48>

NO_TEST=YES

RFBD<49>

NO_TEST=YES

U2200_COMP

NO_TEST=YES

U2200_GATE_H

NO_TEST=YES

Q5002_DRAIN

NO_TEST=YES

U3310_DRN

NO_TEST=YES

U3320_DRN

NO_TEST=YES

U2200_SS

NO_TEST=YES

U2200_GATE_L

NO_TEST=YES

NO_TEST=YES

RFBD<38>

RFBD<46>

NO_TEST=YES

RFBD<30>

NO_TEST=YES

NO_TEST=YES

RFBD<47>

RFBD<45>

NO_TEST=YES

NO_TEST=YES

RFBD<42>

RFBD<43>

NO_TEST=YES

RFBD<37>

NO_TEST=YES

NO_TEST=YES

RFBD<35>

RFBD<28>

NO_TEST=YES

RFBD<29>

NO_TEST=YES

NO_TEST=YES

RFBD<26>

RFBD<25>

NO_TEST=YES

RFBD<24>

NO_TEST=YES

RFBD<22>

NO_TEST=YES

RFBD<23>

NO_TEST=YES

RFBD<21>

NO_TEST=YES

RFBD<18>

NO_TEST=YES

NO_TEST=YES

RFBD<19>

RFBD<13>

NO_TEST=YES

RFBD<14>

NO_TEST=YES

RFBD<11>

NO_TEST=YES

RFBD<12>

NO_TEST=YES

NO_TEST=YES

RFBD<9>

RFBD<7>

NO_TEST=YES

RFBD<8>

NO_TEST=YES

RFBD<4>

NO_TEST=YES

NO_TEST=YES

RFBD<6>

RFBD<3>

NO_TEST=YES

RFBD<2>

NO_TEST=YES

RFBD<1>

NO_TEST=YES

TP_SB_NC_Y3

NO_TEST=YES

NO_TEST=YES

TP_SB_FSTEST

NO_TEST=YES

TP_SB_NC_P8

FUNC_TEST=YES

INV_17_CUR_HI_F

FUNC_TEST=YES

TDIODE_NEG_FMAX

TP_NEC_TEB

NO_TEST=YES

NO_TEST=YES

TP_FBBCS1_L

TP_J4000_SJRESET_L

NO_TEST=YES

PLS_CLK_66M_0_R

NO_TEST=YES

AUD_4V5_FB

NO_TEST=YES

NO_TEST=YES

AGP_CLK66M_NB_R

NO_TEST=YES

ERROR_LED

HT_CLK66M_NB_R

NO_TEST=YES

TP_PSRO1

NO_TEST=YES

NO_TEST=YES

TP_SB_NC_R5

NO_TEST=YES

TP_VREF_CG

NO_TEST=YES

EI_CPU1_SYNC

NO_TEST=YES

TP_PROC_TRIGGER_OUT

NO_TEST=YES

SYNCENABLE

NO_TEST=YES

RI_L

NO_TEST=YES

MCP_L

NO_TEST=YES

I2C_SMU_A_SCL_OUT_L

NO_TEST=YES

I2C_SMU_A_SDA_OUT_L

NO_TEST=YES

EI_SE

NO_TEST=YES

EI_QREQ_L

NO_TEST=YES

EI_QACK_L

NO_TEST=YES

EI_CPU1_CLK_P

NO_TEST=YES

CPU_HRESET_L

NO_TEST=YES

CPU_INT_L

NO_TEST=YES

EI_CPU1_CLK_N

NO_TEST=YES

CPU1_HTBEN

NO_TEST=YES

CHKSTOP_L

NO_TEST=YES

EI_NB_TO_CPU_CLK_N

EI_NB_TO_CPU_SR_N<0..1>

NO_TEST=TRUE

EI_NB_TO_CPU_SR_P<0..1>

NO_TEST=TRUE

NO_TEST=YES

EI_CPU_TO_NB_CLK_N

NO_TEST=TRUE

EI_CPU_TO_NB_SR_N<0..1>

NO_TEST=TRUE

EI_CPU_TO_NB_AD<0..43>

FUNC_TEST=YES

SYS_POWERUP_L

=PP5V_RUN_CPU

FUNC_TEST=YES

PPVCORE_NB

FUNC_TEST=YES

PPVCORE_CPU

FUNC_TEST=YES

PP12V_CPU

FUNC_TEST=YES

VCORE_SENSE_VOUT

FUNC_TEST=YES

SMU_MANUAL_RESET_L

FUNC_TEST=YES

POWER_BUTTON_L

FUNC_TEST=YES

RESET_BUTTON_L

FUNC_TEST=YES

SMU_RESET_L

FUNC_TEST=YES

ANALOG_RED

FUNC_TEST=YES

ANALOG_GRN

FUNC_TEST=YES

ANALOG_BLU

FUNC_TEST=YES

AUDIO_LO_DET_L

FUNC_TEST=YES

FUNC_TEST=YES

ROM_WP_L

FUNC_TEST=TRUE

UATA_DD<15..0>

FUNC_TEST=TRUE

UATA_DA<2..0>

TP_RAM_CKE_R<3>

NO_TEST=YES

TP_RAM_CS_L_R<11>

NO_TEST=YES

FUNC_TEST=YES

AIRPORT_CLKRUN_L_PD

PCI_STOP_L

FUNC_TEST=YES

FUNC_TEST=YES

I2S1_RESET_L

USB2_PORT3_P_F

FUNC_TEST=YES

USB2_PORT3_N_F

FUNC_TEST=YES

USB2_PORT2_N_F

FUNC_TEST=YES

USB_BT_N

FUNC_TEST=YES

FUNC_TEST=YES

ROM_ONBOARD_CS_L

PCI_PAR

FUNC_TEST=YES

FUNC_TEST=YES

PCI_SLOTA_IDSEL

PCI_DEVSEL_L

FUNC_TEST=YES

AUD_MIC_IN_P_CONN

FUNC_TEST=TRUE

NO_TEST=YES

TP_RAM_CS_L_R<10>

NO_TEST=YES

TEK_HT_B12

NO_TEST=YES

TEK_HT_A12

TP_NB_PM_SLEEP0

NO_TEST=YES

TP_RAM_MUXEN4

NO_TEST=YES

TP_RAM_CS_L_R<3>

NO_TEST=YES

TP_RAM_CS_L_R<2>

NO_TEST=YES

NO_TEST=YES

TP_RAM_CKE_R<7>

TP_RAM_CKE_R<6>

NO_TEST=YES

NO_TEST=YES

TP_NEC_SRCLK

NO_TEST=YES

TP_NEC_TEST

NO_TEST=YES

TP_PLS_CLK_66M_0

NO_TEST=YES

TP_PLS_TEST3

TP_SB_PLLTEST

NO_TEST=YES

TP_NEC_AMC

NO_TEST=YES

RAM_CLK66M_NB_R

NO_TEST=YES

NO_TEST=YES

R2204_P2

NO_TEST=YES

TP_DUMMY_B

NO_TEST=YES

Q2201_GATE

TP_RAM_CKE_R<2>

NO_TEST=YES

NO_TEST=YES

TP_SB_NC_V1

NO_TEST=YES

TP_SB_NC_U5

TP_SB_NC_U4

NO_TEST=YES

TP_SB_NC_U3

NO_TEST=YES

TP_SB_NC_U2

NO_TEST=YES

TP_SB_NC_U1

NO_TEST=YES

NO_TEST=YES

TP_SB_NC_T5

NO_TEST=YES

TP_SB_NC_T1

NO_TEST=YES

TP_SB_NC_R8

NO_TEST=YES

TP_SB_NC_R7

TP_PLS_CLK_66M_1

NO_TEST=YES

Q902_DRAIN

NO_TEST=YES

Q901_GATE

NO_TEST=YES

Q802_B

NO_TEST=YES

TP_PLS_REF_CML

NO_TEST=YES

NO_TEST=YES

TP_SB_NC_R4

NO_TEST=YES

TP_SB_NC_T4

TP_DUMMY_A

NO_TEST=YES

TP_SB_NC_W3

NO_TEST=YES

TP_SB_NC_W1

NO_TEST=YES

TP_SB_NC_R3

NO_TEST=YES

NO_TEST=YES

TP_SB_NC_R6

NO_TEST=YES

TP_SB_NC_T2

TP_NEC_SRMOD

NO_TEST=YES

TP_PLS_TEST1

NO_TEST=YES

TP_NEC_SMC

NO_TEST=YES

Q800_G

NO_TEST=YES

PN2

NO_TEST=YES

NO_TEST=YES

HT_VREF_DEBUG

NO_TEST=YES

CPU_HTBEN_R

NO_TEST=YES

ITS_RUNNING

NO_TEST=YES

AGP_CLK66M_GPU_R

AGP_CLK66M_NB_R

NO_TEST=YES

RFBD<36>

NO_TEST=YES

NO_TEST=YES

RFBD<40>

TEK_HT_B10

NO_TEST=YES

TP_J4001_SJRESET_L

NO_TEST=YES

NO_TEST=YES

U900_GATE_L

NO_TEST=YES

U900_GATE_H

TEK_HT_A10

NO_TEST=YES

TEK_HT_A9

NO_TEST=YES

U2100_UNUSED

NO_TEST=YES

TP_RAM_MUXEN0

NO_TEST=YES

PP5V_USB2_PORT1_F

FUNC_TEST=YES

PP5V_USB2_PORT2_F

FUNC_TEST=YES

FUNC_TEST=YES

PP5V_USB2_PORT3_F

NO_TEST=YES

U1000_FEEDBACK

NO_TEST=YES

U900_SS

PLS_CLK_66M_1_R

NO_TEST=YES

NO_TEST=YES

TEK_HT_A7

NO_TEST=YES

EI_CPU_TO_NB_CLK_P

NO_TEST=TRUE

EI_CPU_TO_NB_SR_P<0..1>

EI_NB_TO_CPU_CLK_P

NO_TEST=YES

NO_TEST=TRUE

EI_NB_TO_CPU_AD<0..43>

NO_TEST=YES

SB_CLK25M_ATA_R

AUD_MIC_IN_N_CONN

FUNC_TEST=TRUE

FW_VP

FUNC_TEST=TRUE

GND_AUDIO_MIC_CONN

FUNC_TEST=TRUE

I2C_HD_TEMP_SCL

FUNC_TEST=TRUE

FUNC_TEST=TRUE

I2C_HD_TEMP_SDA

FUNC_TEST=TRUE

I2C_SB_SCL

FUNC_TEST=TRUE

I2C_SB_SDA

FUNC_TEST=TRUE

KPGND2

I2C_TMDS_SDA

FUNC_TEST=YES

FUNC_TEST=YES

CORE_ISNS_P

PP5V_AGP_RL

FUNC_TEST=YES

FUNC_TEST=YES

I2S1_DEV_TO_SB_DTI

ROM_WE_L

FUNC_TEST=YES

ROM_OE_L

FUNC_TEST=YES

ROM_CS_L

FUNC_TEST=YES

PCI_IRDY_L

FUNC_TEST=YES

FUNC_TEST=YES

PCI_TRDY_L

FUNC_TEST=YES

PCI_FRAME_L

FUNC_TEST=YES

PCI_RESET_L

FUNC_TEST=YES

PCI_SLOTA_INT_L

FUNC_TEST=YES

PCI_SLOTA_GNT_L

FUNC_TEST=YES

PCI_SLOTA_REQ_L

FUNC_TEST=YES

PCI_CLK33M_AIRPORT

FUNC_TEST=TRUE

PCI_CBE_L<3..0>

FUNC_TEST=TRUE

PCI_AD<31..0>

I2C_TMDS_SCL

FUNC_TEST=YES

KPVDD2

FUNC_TEST=TRUE

FUNC_TEST=YES

=PP5V_DISK

FUNC_TEST=YES

=PPVCORE_PWRON_SB

=PP3V3_ALL_SMU

FUNC_TEST=TRUE

FUNC_TEST=YES

SYS_SLEEP

FUNC_TEST=YES

SYS_POWERFAIL_L

FUNC_TEST=YES

U900_FEEDBACK

UATA_CS0_L

FUNC_TEST=YES

UATA_CS1_L

FUNC_TEST=YES

UATA_RESET_L

FUNC_TEST=YES

FUNC_TEST=YES

UATA_DSTROBE_R

UATA_STOPUATA_STOP

FUNC_TEST=YES

UATA_DMARQ_R

FUNC_TEST=YES

UATA_DMACK_L

FUNC_TEST=YES

FUNC_TEST=YES

UATA_INTRQ_R

UATA_IOCS16_PU

FUNC_TEST=YES

UATA_CSEL_PD

FUNC_TEST=YES

FUNC_TEST=TRUE

UATA_DASP_L

TDIODE_NEG

FUNC_TEST=YES

GND_17_INV

FUNC_TEST=YES

FUNC_TEST=YES

KPVDD2_FMAX

FUNC_TEST=YES

CORE_ISNS_M

FUNC_TEST=YES

TDIODE_POS_FMAX

FUNC_TEST=YES

KPGND2_FMAX

FUNC_TEST=TRUE

CPU_VID_R<5..0>

FUNC_TEST=YES

INV_17_LCD_PWM_F

TD2P

FUNC_TEST=YES

TCKP

FUNC_TEST=YES

GND_20_INV

FUNC_TEST=YES

FUNC_TEST=YES

INV_20_LCD_PWM_

PP24V_INV

FUNC_TEST=YES

FUNC_TEST=YES

I2S1_SB_TO_DEV_DTO

TD2M

FUNC_TEST=YES

TD1P

FUNC_TEST=YES

FUNC_TEST=YES

MODEM_RING2SYS_L

FUNC_TEST=YES

I2S1_MCLK

FUNC_TEST=YES

I2S1_BITCLK

I2S1_SYNC

FUNC_TEST=YES

SATA_CLK25M_R

NO_TEST=YES

UATA_HSTROBE

FUNC_TEST=YES

FUNC_TEST=YES

INV_20_CUR_HI_F

FUNC_TEST=YES

VGA_VSYNC_R

MON_DETECT

FUNC_TEST=YES

FILT_ANALOG_GRN

FUNC_TEST=YES

FUNC_TEST=YES

FILT_ANALOG_RED

I2C_TMDS_SCL

FUNC_TEST=YES

FUNC_TEST=YES

I2C_TMDS_SDA

FUNC_TEST=YES

TD0P

NO_TEST=YES

EI_CPU1_SYNC_R

NO_TEST=YES

CPU1_HTBEN_R

FUNC_TEST=YES

GND_CHASSIS_TMDS

FUNC_TEST=YES

FILT_ANALOG_BLU

FUNC_TEST=YES

TD0M

PPVCC_TMDS

FUNC_TEST=YES

FUNC_TEST=YES

PP3V3_DDC

TMDS_D1M

FUNC_TEST=YES

TMDS_CKM

FUNC_TEST=YES

30

30

30

30

30

18

18

29

29

29

30

29

29

29

29

29

29

29

29

29

29

29

29

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

54

27

27

29

29

29

29

14

14

28

28

28

27

29

25

27

14

28

28

28

28

28

28

27

54

54

28

28

28

28

27

27

77

91

91

91

91

91

27

22

9

50

50

50

8

27

33

27

27

27

92

77

27

91

91

27

27

53

9

9

83

9

8

9

22

22

22

92

92

91

91

91

77

77

92

92

29

29

29

29

48

8

8

34

8

8

10

8

53

53

50

34

50

50

50

53

53

22

22

50

33

33

22

22

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

91

25

91

77

52

40

27

102

6

8

27

29

91

48 14

14

14

14

14

13

13

14

14

14

14

14

14

14

14

8

14

14

14

14

14

14

8

8

8

64

64

24

8

8

8

8

8

77

77

27

27

25

77

27

22

24

22

8

91

91

91

91

91

91

91

91

91

91

27

9

9

8

27

91

91

24

91

91

91

91

91

77

27

77

8

33

64

27

7

27

6

53

53

64

40

9

9

64

64

21

8

10

9

27

64

14

14

14

14

27

27

14

14

Preliminary

Page 7

125

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

SDF700 IS USED FOR CPU HEATSINK MOUNTING

RTC BATTERY

ALWAYS ON (TRICKLE)

805-5664

SILKSCREEN:POWER

ALL RAILS

ALWAYS ON WHEN UNIT HAS AC POWER (TRICKLE)

SILKSCREEN:RUN

POWER

GND RAILS

PWRON RAILS

CHASSIS GND

SILKSCREEN:2

RUN RAILS

SMU RESET

SILKSCREEN:1

PIN 13,19,11,22 ARE DIFFERENCE FROM ATX .

RESET

ONLY ON IN RUN

516S0248

FOXCONN

P/N 518-0159

ON IN RUN AND SLEEP

PP5V_RUN

PP3V3_PWRON

PP1V5_PWRON

PP2V5_PWRON

PP1V2_PWRON

PP24V_RUN

PP5V_ALL

PP5V_ALL

PP3V3_RUN

PP2V5_RUN

PP5V_PWRON

PP1V5_RUN

PP5V_RUN

PP3V3_RUN

PP5V_RUN

PP12V_RUN

SM

21

XW700

SM

21

XW701

315R138

1

ZH700

SM

21

XW702

SM

21

XW703

0.1UF

20%

10V

CERM

402

2

1

C704

0.1UF

402

10V

20%

CERM

2

1

C705

PP12V_RUN

SM

SPST

43

21

SW702

1/16W

MF-LF

402

1K

5%

21

R713

SM

DEVELOPMENT

SPST

43

21

SW701

MF-LF

1/16W

1K

402

5%

DEVELOPMENT

21

R712

SM

SPST

DEVELOPMENT

43

21

SW700

7R4.15

1

ZH702

6.00MM-PTH

1

ZH703

1K

402

1/16W

5%

MF-LF

21

R702

SHLD-IO-CONN

Q45-TH1

4

32

1

SH700

B0530WXF

SOD-123

2 1

DS700

PP1V2_RUN

TSSOP

74LCX125

CRITICAL

3

14

17

2

U700

0.1UF

10V

CERM

20%

402

2

1

C700

SM

FERR-EMI-100-OHM

SYS_PWR_BTN_FILT

21

L700

SM

FERR-EMI-100-OHM

21

L701

GREEN

2.0X1.25A

DEVELOPMENT

2

1

LED701

GREEN

2.0X1.25A

2

1

LED702

PP3V3_PWRON

1/10W

603

330

MF-LF

5%

21

R700

2.0X1.25A

GREEN

2

1

LED700

CRITICAL

HM96110-P2

F-RT-TH

9

8

7

6

5

4

3

22

21

20

2

19

18

17

16

15

14

13

12

11

10

1

J700

SM

21

XW704

SM

21

XW705

SM

21

XW706

SM

21

XW707

NOSTUFF

TH

HSK-NUT-6.5MM

1

SDF700

PP12V_RUN

PP24V_RUN

PWR-BUTT

ST-SM3

CRITICAL

2

1

54

3

SW703

PP3V3_RUN

5%

0

NOSTUFF

MF-LF

1/8W

805

21

R720

315R138

1

ZH710

NOSTUFF

402

MF-LF

1/16W

5%

0

21

R703

603

330

1/10W

5%

MF-LF

21

R710

402

0.1UF

20%

CERM

10V

2

1

C703

603

MF-LF

5%

330

1/10W

DEVELOPMENT

21

R701

PP5V_ALL

TH

CRITICAL

BB10209-A5

1 2

J702

11

7

102

051-6772

SYNC_MASTER=N/A

SYNC_DATE=N/A

POWER CONN / ALIAS

VOLTAGE=0V

MIN_NECK_WIDTH=0.25MM

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.25MM

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

VOLTAGE=5V

PP5V_RUN

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.6MM

VOLTAGE=3.3V

VOLTAGE=1.5V

MIN_NECK_WIDTH=0.25MM

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

VOLTAGE=2.5V

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.25MM

MAKE_BASE=TRUE

VOLTAGE=1.2V

MIN_NECK_WIDTH=0.25MM

MIN_LINE_WIDTH=0.6MM

MIN_LINE_WIDTH=0.6MM

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.25MM

VOLTAGE=2.5V

MIN_LINE_WIDTH=0.6MM

VOLTAGE=5V

MIN_NECK_WIDTH=0.2MM

MAKE_BASE=TRUE

VOLTAGE=1.5V

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.5MM

MIN_NECK_WIDTH=0.25MM

MAKE_BASE=TRUE

VOLTAGE=1.2V

MIN_LINE_WIDTH=0.5MM

MIN_NECK_WIDTH=0.25MM

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.25MM

MIN_LINE_WIDTH=0.6MM

VOLTAGE=12V

MIN_NECK_WIDTH=0.25MM

MIN_LINE_WIDTH=0.6MM

VOLTAGE=24V

MAKE_BASE=TRUE

VOLTAGE=3.3V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.3MM

PP3V3_RUN

VOLTAGE=5V

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

PP5V_ALL

MAKE_BASE=TRUE

VOLTAGE=0

GND_CHASSIS_20_INCH_INVERTER

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

MIN_NECK_WIDTH=0.2MM

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6MM

PP3V3_ALL_RTC

VOLTAGE=3.3V

=PP5V_PWRON_VESTA

_PP5V_PWRON_USB

=PP5V_PWRON_CPU

=PPPCI64_PWRON_SB

=PPPCI32_PWRON_SB

=PP3V3_PWRON_USB

PP5V_AUDIO

=PP5V_PATA

=PP3V3_PWRON_RAM

=PP3V3_PWRON_VESTA

=PP3V3_PWRON_EI

=PP2V5_PWRON_SB

=PP2V5_PWRON_RAM

=PP2V5_PWRON_HT

=PP1V5_PWRON_NB_AVDD

=PP2V5_ENET

=PP3V3_PWRON_CPU

=PPVCORE_NB

ITS_RUNNING

=PP1V2_PWRON_SB

=PP1V2_PWRON_DISK_SB

SMU_MANUAL_RESET_L

RESET_BUTTON_L

SYS_POWER_BUTTON_L

ITS_PLUGGED_IN

=PP3V3_ALL_RTC

=PP1V2_PWRON_HT

PP3V3_ALL

GND_AUDIO_SPKRAMP

ITS_ALIVE

=PP24V_GRAPHICS

PP12V_AUDIO_SPKRAMP

=PPVCORE_CPU

MAKE_BASE=TRUE

PPVCORE_CPU

GND_AUDIO

SYS_POWER_BUTTON_L

SYS_RESET_BUTTON_L

VOLTAGE=0

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

GND_CHASSIS_17_INCH_INVERTER

=PP5V_ALL_CPU

=PPVCORE_PWRON_SB

PPVCORE_GPU

POWER_GOOD

PP12V_AUDIO_CODEC

=PP12V_RUN_CPU

=PP12V_AGP

SYS_POWERUP_L_BUF

=PP2V5_RUN_CPU

POWER_BUTTON_L

=PP5V_DISK

GND_SYS_PWR_BTN_FILT

=PP5V_AGP

=PP1V2_EI_NB

=PP1V2_EI_CPU

=PPVCORE_PULSAR

=PP2V5_RUN_RAM

=PP5V_RUN_CPU

=PP1V2_HT

=PP1V2_PULSAR

PP2V5_GPU

PP3V3_VESTA

=PP3V3_ENETFW

=PP3V3_FW

=PP3V3_ENET

=PP3V3_ALL_CPU

MAKE_BASE=TRUE

PP3V3_ALL

VOLTAGE=3.3V

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

PP1V2_VESTA

GND_CHASSIS_AUDIO_EXTERNAL

VOLTAGE=0

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.25MM

MIN_LINE_WIDTH=0.6MM

=PP3V3_ALL_SMU

VOLTAGE=1.2V

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.25MM

PP1V2_ALL

=PP1V2_ENETFW

MAKE_BASE=TRUE

GND_CHASSIS_AUDIO_INTERNAL

PP3V3_AUDIO

=PPVIO_PCI_USB2

=PP3V3_SB_PCI

=PP3V3_RUN_CPU

=PP3V3_PCI

=PP3V3_PATA

=PP3V3_DISK

=PP3V3_AGP

_PP3V3_PWRON_MODEM

_PP3V3_PWRON_BT

=PP3V3_PWRON_SB

=PPVCORE_PWRON_PULSAR

VOLTAGE=3.3V

PP3V3_ALL_BATT_SAFETY

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

PP3V3_ALL_BATT

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

VOLTAGE=3.3V

=PP12V_DISK

=PP2V5_HT

GND_CHASSIS_LED

GND_CHASSIS_VGA

MIN_LINE_WIDTH=0.6MM

VOLTAGE=0

GND_CHASSIS_RJ45

MIN_NECK_WIDTH=0.25MM

VOLTAGE=0

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.25MM

GND_CHASSIS_TMDS

GND_CHASSIS_FIREWIRE

GND_CHASSIS_USB

=PP1V5_AGP

SYS_POWERUP_L

50 34 59 22

31

77

58

33

18

18

88

46

60

36

35

30

31

102

76

56

13

11

11

12

74

40

48

13

59

32

34

13

23

51

28

29

8

55

59 13

101

75

50

74

50

11

10

10

11

25

37

37

8

7

11

102

31

33

7

6

50

59

83

59

18

18

45

6

60

54

90

87

11

102

8

89

100

74

49

25

83

64

59

49

10

6

6

6

59

12

92

36

23

23

91

101

83

46

12

28

23

26

62

28

87

36

22

6

25

80

6

6

6

13

62

7

100

59

100

29

6

102

6

13

59

36

3

22

8

102

33

50

31

6

6

50

14

14

26

44

3

24

26

52

12

89

89

86

36

7

12

101

6

10

86

101

95

77

74

33

25

83

83

48

94

76

23

26

6

60

21

59

87

6

90

92

48

6

Preliminary

Page 8

125

125

125

G

D

S

MC33465N_30ATR

RESETDELAY

VCC

GND

VOLTAGE DETECTOR

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

1

2

3

4

5

67

8

12

3

4

5

6

78

B

C

D

A

B

C

D

A

REV.

APPLE COMPUTER INC.

SCALE

NONE

CPU VID<0:5>

CHKSTOP LED

THESE PINS HAVE INTERNAL PULLUPS

NET_SPACING_TYPE

ELECTRICAL_CONSTRAINT_SET

DIAG LED

SMU

PCI CLOCKS

PULL DOWN

SHASTA JTAG

CONNECTION

SIGNAL FROM POWER SUPPLY

518S0104

PLL LOCK LED

SMU ANALOG VREF

2.2V FOR CPU VRM10.

NOTE:PULL UP CPU_VID<5>TO

VID CONTROLLED BY SMU

DIFFERENTIAL_PAIR

PULSAR ERROR_L LEDBACKUP SMU RESET CIRCUIT

518-0158

J802 & R826 CAN MOVE TO DEVELOPMENT BOM POST RAMP

POWER_GOOD IS A 5V DRIVEN

2K PULLUP INSIDE P/S

POWER_FAIL_L

SDF700 IS ALSO

USED FOR HEATSINK

MOUNTING

CPU HEATSINK SMT NUTS

(SMU_BOOT_EPM)

VESTA JTAG

CONNECTOR

DOWNLOAD

5%

402

MF-LF

10K

1/16W

2

1

R825

100

5%

1/16W

MF-LF

402

2 1

R826

402

MF-LF

1/16W

0

5%

21

R802

5%

10K

402

MF-LF

1/16W

2

1

R803

402

MF-LF

1/16W

5%

10K

NOSTUFF

2

1

R807

MF-LF

10K

1/16W

402

5%

2

1

R806

NOSTUFF

0

402

5%

1/16W

MF-LF

21

R828

74LCX125

TSSOP

6

14

47

5

U700

74LCX125

TSSOP

8

14

10

7

9

U700

TSSOP

74LCX125

11

14

13

7

12

U700

4.7K

5%

1/16W

MF-LF

402

2

1

R870

PP2V5_PWRON

10K

5%

1/16W

MF-LF

402

2

1

R814

402

MF-LF

5%

10K

1/16W

2

1

R816

402

MF-LF

1/16W

5%

10K

2

1

R817

5%

1/16W

MF-LF

402

10K

2

1

R808

5%

402

10K

MF-LF

1/16W

2

1

R809

402

1K

MF-LF

1/16W

5%

NOSTUFF

2

1

R827

402

MF-LF

5%

1K

NOSTUFF

1/16W

2

1

R829

402

MF-LF

5%

1K

NOSTUFF

1/16W

2

1

R830

402

MF-LF

1/16W

5%

1K

NOSTUFF

2

1

R831

PP3V3_RUN

402

10K

5%

1/16W

MF-LF

2

1

R804

402

20K

5%

1/16W

MF-LF

2

1

R811

NOSTUFF

HSK-NUT-6.5MM

TH

1

SDF800

TH

NOSTUFF

HSK-NUT-6.5MM

1

SDF801

HSK-NUT-6.5MM

TH

NOSTUFF

1

SDF803

TH

NOSTUFF

HSK-NUT-6.5MM

1

SDF802

RED

SM

DEVELOPMENT

2

1

D810

OMIT

6P15R5P4

1

ZH804

CERM

16V

20%

0.01UF

402

2

1

C880

CERM

16V

20%

0.01UF

402

2

1

C881

16V

CERM

20%

0.01UF

402

2

1

C882

CERM

16V

20%

0.01UF

402

2

1

C883

402

0.01UF

20%

16V

CERM

2

1

C884

DEVELOPMENT

5%

1/16W

MF-LF

402

180

2

1

R833

DEVELOPMENT

SM

RED

2

1

LED801

Q800_D

DEVELOPMENT

SOT23-LF

2N7002

2

1

3

Q800

DEVELOPMENT

5%

402

MF-LF

1/16W

180

2

1

R834

Q801_B

DEVELOPMENT

SOT23

2N3904LF

2

3

1

Q801

2N3906

DEVELOPMENT

SM

2

3

1

Q802

MF-LF

1/16W

180

5%

DEVELOPMENT

402

2

1

R835

5%

DEVELOPMENT

402

MF-LF

1/16W

180

21

R836

DEVELOPMENT

2.0X1.25A

GREEN

2

1

LED802

DEVELOPMENT

1/16W

5%

402

MF-LF

180

2

1

R837

5%

1/16W

MF-LF

402

DEVELOPMENT

1K

2

1

R838

DEVELOPMENT

SOT23

2N3904LF

2

3

1

Q803

DEVELOPMENT

5%

402

MF-LF

1/16W

180

21

R839

402

MF-LF

1/16W

5%

NOSTUFF

1K

2

1

R832

I246

I247

SM

RED

2

1

LED850

SOT23

2N3904LF

2

3

1

Q850

5%

MF-LF

402

1/16W

1K

21

R851

PP5V_ALL

1/16W

MF-LF

5%

402

180

2

1

R850

MF-LF

5%

430

1/16W

402

2

1

R813

1/16W

4.7K

5%

402

MF-LF

2

1

R860

1/16W

NOSTUFF

1K

MF-LF

5%

402

2

1

R890

NOSTUFF

CERM

1uF

10%

6.3V

402

2

1

C891

SM

NOSTUFF

2

1

3

5

U890

0.01UF

NOSTUFF

402

10%

16V

CERM

2

1

C890

402

MF-LF

5%

0

1/16W

21

R810

NOSTUFF

402

CERM

20%

10V

0.1uF

2

1

C800

M-ST-TH

HC17051

9

87

65

43

2

10

1

J802

5%

1/16W

10K

MF-LF

402

2

1

R840

5%

MF-LF

1/16W

402

0

NOSTUFF

2

1

R805

PP3V3_ALL

U.FL-R_SMT

DEVELOPMENT

F-ST-SM

1

2

3

J800

PP3V3_ALL

NOSTUFF

5%

402

MF-LF

10K

1/16W

2

1

R812

2.5V

SSOT-23

NOSTUFF

3

12

VR801

NOSTUFF

200

1/16W

MF-LF

402

1%

2

1

R818

NOSTUFF

2.2UF

20%

10V

CERM

805

2

1

C801

NOSTUFF

CERM

10V

20%

0.47UF

603

2

1

C802

BM12B-SRSS-TB

NOSTUFF

F-ST-SM

9876543

2

121110

11314

J803

1/16W

5%

0

MF-LF

402

21

R819

MF-LF

402

0

5%

1/16W

21

R820

1/16W

0

MF-LF

5%

402

21

R821

402

MF-LF

1/16W

5%

0

21

R822

0

1/16W

MF-LF

5%

402

21

R823

0

1/16W

MF-LF

5%

402

21

R824

4.7K

DEVELOPMENT

5%

402

MF-LF

1/16W

2

1

R801

DEVELOPMENT

MF-LF

330

402

1/16W

5%

2

1

R800

PP3V3_RUN

051-6772

102

8

11

SYNC_MASTER=N/A

SYNC_DATE=N/A

SIGNAL ALIAS

J802_6

SMU_MANUAL_RESET_L

SMU_BOOT_TXD

SMU_MANUAL_RESET_L

CPU_VID_R<4>

CPU_VID_R<1>

MAKE_BASE=TRUE

TP_NB_THMI

MAKE_BASE=TRUE

TP_RAM_CKE_R<2>

MAKE_BASE=TRUE

TP_RAM_CKE_R<6>

MAKE_BASE=TRUE

TP_RAM_MUXEN0

MAKE_BASE=TRUE

TP_RAM_MUXEN4

RAM_CS_L_R<2>

RAM_CS_L_R<3>

SMU_BOOT_RXD

SMU_BOOT_BUSY

MAKE_BASE=TRUE

PPVREF_SMU

SMU_BOOT_CNVSS

CPU_VID_R<3>

CPU_VID_R<2>

J802_2

NB_SUSPEND_ACK_L

=PP3V3_ALL_SMU

=PCI_USB2_RESET_L

CPU_VID_R<0>

CPU_VID_R<5>

MAKE_BASE=TRUE

PCI_RESET_L

PCI_CLK_GP0

CPU_VID<4>

CPU_VID<2>

CPU_VID<0>

CPU_VID<5>

CPU_VID<3>

CPU_VID<1>

DIAG_LED

MAKE_BASE=TRUE

DIAG_LED_R

LED850P2

LED850P1

=PP5V_RUN_CPU

NB_SUSPENDACK_L

SYS_SLEEP

SMU_WARM_RESET_L SYS_WARM_RESET_L

=PPVREF_SMU

PP3V3_ALL_SMU_AVCC

Q802_E

HS_SDF803

HS_SDF800 HS_SDF801 HS_SDF802

GND_SMU_AVSS

Q803_C

LED802_1

Q800_G

LED801_1

NB_PMR_OBSV

GND_SMU_AVSS_DAGND

PPVREF_SMU_ADC_REF

SMU_SLEEP

Q802_B

PLLLOCK

HS_SDF804

=PP5V_RUN_CPU

POWER_GOOD

SYS_POWERFAIL_L

CHKSTOP_L

JTAG_SB_TRST_L

SMU_RESET_L

ERROR_LED

CLOCK_ERROR_L

PCI_CLK_P3

_PCI_CLK33M_AIRPORT

NB_THMI

MAKE_BASE=TRUE

TP_THMO NB_THMO

RAM_CKE_R<2>

MAKE_BASE=TRUE

TP_RAM_CKE_R<3>

RAM_CKE_R<3>

RAM_CKE_R<6>

TP_RAM_CKE_R<7>

MAKE_BASE=TRUE

RAM_CKE_R<7>

RAM_MUXEN0

RAM_CS_L_R<11>

MAKE_BASE=TRUE

PCI_CLK33M_AIRPORT

=PCI_CLK33M_USB2

MAKE_BASE=TRUE

PCI_CLK33M_USB2

RAM_MUXEN4

MAKE_BASE=TRUE

TP_PCI_CLK_GP1

PCI_CLK_GP1

PCI_CLK_P4

MAKE_BASE=TRUE

TP_PCI_CLK_P4

MAKE_BASE=TRUE

PCI_CLK33M_SB_EXT

PCI_CLK_P1

RAM_CS_L_R<10>

MAKE_BASE=TRUE

TP_RAM_CS_L_R<3>

MAKE_BASE=TRUE

TP_RAM_CS_L_R<2>

MAKE_BASE=TRUE

TP_RAM_CS_L_R<10>

TP_ALS0_OUT

MAKE_BASE=TRUE

ALS0_OUT

ALS1_OUT

TP_ALS1_OUT

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_ALS_GAIN_BOOST

ALS_GAIN_BOOST

SMU_ONEWIRE

TP_SMU_ONEWIRE

MAKE_BASE=TRUE

SYS_SLOT_PWR

TP_SYS_SLOT_PWR

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_RAM_CS_L_R<11>

TP_SMU_PWRSEQ_P1_3

MAKE_BASE=TRUE

SMU_PWRSEQ_P1_3

SYS_DOOR_AJAR_L

TP_SYS_DOOR_AJAR_L

MAKE_BASE=TRUE

MAKE_BASE=TRUE

TP_FAN_PWM8

FAN_PWM8

TP_SYS_DRIVE_BAY_INT_L

MAKE_BASE=TRUE

SMU_WARM_RESET_L

MAKE_BASE=TRUE

SYS_DRIVE_BAY_INT_L

NB_WARM_RESET_L

PCI_AIRPORT_RESET_L

GPU_RESET_L

=PCI_ROM_RESET_L

SYS_WARM_RESET_L

SMU_RESET

P25MM

SYS_COLD_RESET_L

SMU_RESET

P25MM

Q803_B

MAKE_BASE=TRUE

JTAG_VESTA_TRST_L

=JTAG_VESTA_TRST_L

=JTAG_VESTA_TCK

MAKE_BASE=TRUE

TP_JTAG_VESTA_TCK

MAKE_BASE=TRUE

TP_JTAG_VESTA_TDI

=JTAG_VESTA_TDI

=JTAG_VESTA_TDO

MAKE_BASE=TRUE

TP_JTAG_VESTA_TDO

MAKE_BASE=TRUE

TP_JTAG_VESTA_TMS

=JTAG_VESTA_TMS

JTAG_SB_TCK

JTAG_SB_TDI

MAKE_BASE=TRUE

TP_JTAG_SB_TDI

MAKE_BASE=TRUE

TP_JTAG_SB_TDO

JTAG_SB_TDO

JTAG_SB_TMS

MAKE_BASE=TRUE

TP_JTAG_SB_TMS

MAKE_BASE=TRUE

TP_JTAG_SB_TCK

SMU_BOOT_SCLK

SMU_BOOT_CE

50 46

31

22

31

8

11

77

8

77

8

8

13

74

7

10

74

36

7

29

74

7

7

33

33

33

33

7

33

33

56

6

9

13 25

33

6

13

14

13

74

13

25

24

6

6

6

13

6

6

6

6

6

6

6

37

37

13

13

13

6

6

24

6

77

6

6

6

27

13

13

13

13

13

13

13

3

13

6

8 8

13

13

6

13

6 6

6

24

36

36

13

6

29

3

7

6

6

25

6

6

27

27

76

24

24

37

6

37

37

6

37

37

37

6

77

37

27

27

6

27 27

37

6

6

6

13

13

13

13

13

6

13

13

13

8

13

24

76

49

75

8

13

12

12

12

12

12

25

25

25

25

13

13

Preliminary

Page 9

FB

LD

HD

GND

COMP

SS

VCC

VC

G

D

S

G

D

S

G

D

S

D

SIZE

OF

SHT

DRAWING NUMBER

NOTICE OF PROPRIETARY PROPERTY

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

AGREES TO THE FOLLOWING

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR