Analog Devices AD6644 c Datasheet

14-Bit, 40 MSPS/65 MSPS

a

FEATURES

65 MSPS Guaranteed Sample Rate

40 MSPS Version Available

Sampling Jitter < 300 fs

100 dB Multitone SFDR

1.3 W Power Dissipation

Differential Analog Inputs

Digital Outputs

Twos Complement Format

3.3 V CMOS Compatible

Data Ready for Output Latching

APPLICATIONS

Multichannel, Multimode Receivers

AMPS, IS-136, CDMA, GSM, Third Generation

Single Channel Digital Receivers

Antenna Array Processing

Communications Instrumentation

Radar, Infrared Imaging

Instrumentation

A/D Converter

AD6644

Designed for multichannel, multimode receivers, the AD6644 is

part of ADI’s new SoftCell™ transceiver chipset. The AD6644

achieves 100 dB multitone, spurious-free dynamic range (SFDR)

through the Nyquist band. This breakthrough performance eases

the burden placed on multimode digital receivers (software radios)

which are typically limited by the ADC. Noise performance is

exceptional; typical signal-to-noise ratio is 74 dB.

The AD6644 is also useful in single channel digital receivers designed for use in wide-channel bandwidth systems (CDMA,

W-CDMA). With oversampling, harmonics can be placed outside

the analysis bandwidth. Oversampling also facilitates the use of

decimation receivers (such as the AD6620), allowing the noise

floor in the analysis bandwidth to be reduced. By replacing traditional analog filters with predictable digital components, modern

receivers can be built using fewer RF components, resulting in decreased manufacturing costs, higher manufacturing yields, and

improved reliability.

The AD6644 is built on Analog Devices’ high speed complementary bipolar process (XFCB) and uses an innovative, multipass

circuit architecture. Units are packaged in a 52-lead Plastic Low

Profile Quad Flat Pack (LQFP) specified from –25°C to +85°C.

PRODUCT DESCRIPTION

The AD6644 is a high speed, high performance, monolithic

14-bit analog-to-digital converter. All necessary functions,

including track-and-hold (T/H) and reference, are included onchip to provide a complete conversion solution. The AD6644

provides CMOS compatible digital outputs. It is the third generation in a wideband ADC family, preceded by the AD9042 (12-bit

41 MSPS) and the AD6640 (12-bit 65 MSPS, IF sampling).

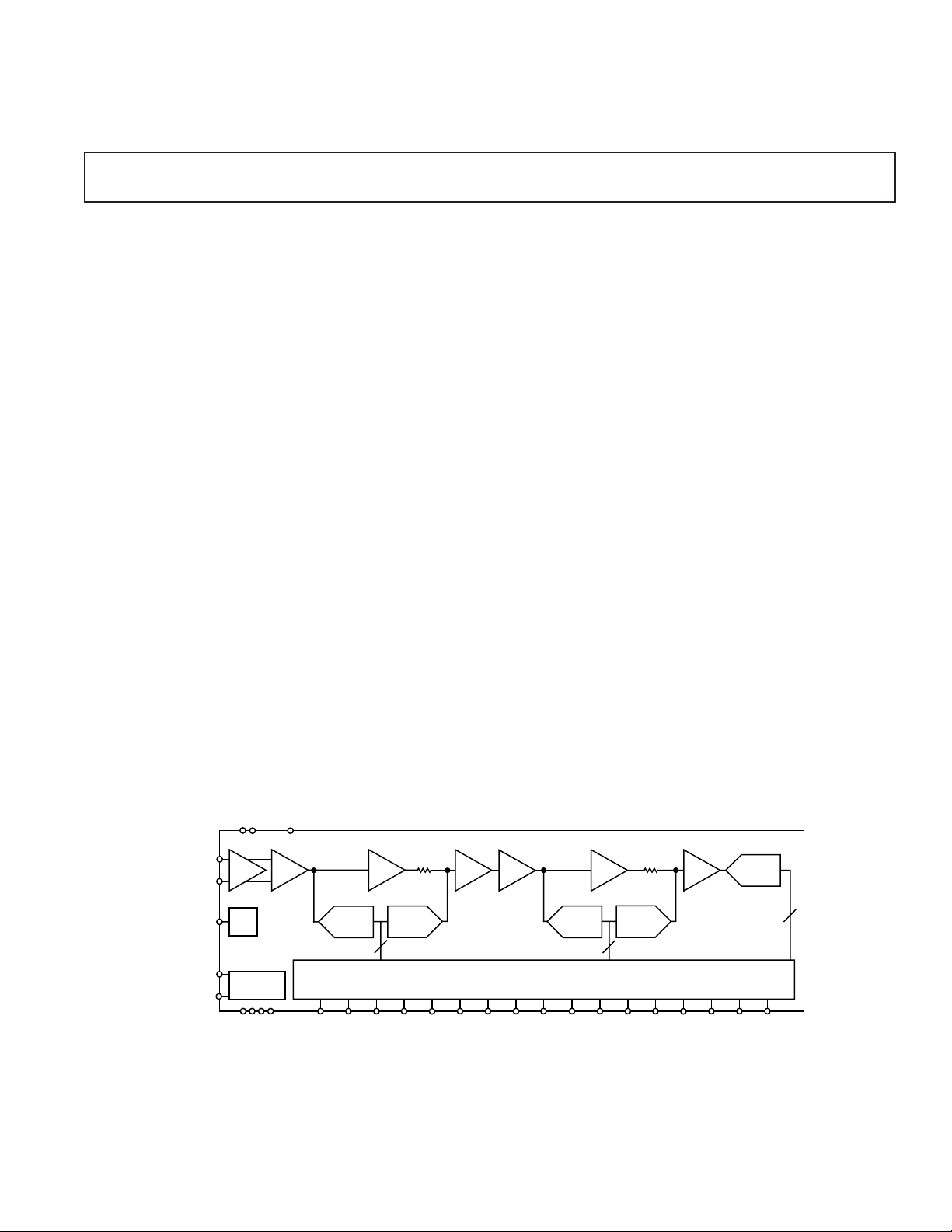

FUNCTIONAL BLOCK DIAGRAM

AIN

AIN

V

REF

ENCODE

ENCODE

AVCCDV

2.4V

INTERNAL

TIMING

CC

TH2TH1A1

ADC1 DAC1

5

MSB LSB

GND D8D9D10D11D12D13DRYOVRDMID D0D1D2D3D4D5D6D7

A2

DIGITAL ERROR CORRECTION LOGIC

PRODUCT HIGHLIGHTS

1. Guaranteed sample rate is 65 MSPS.

2. Fully differential analog input stage.

3. Digital outputs may be run on 3.3 V supply for easy interface

to digital ASICs.

4. Complete solution: reference and track-and-hold.

5. Packaged in small, surface-mount, plastic, 52-lead LQFP.

TH3

TH4

ADC2 DAC2

5

TH5

ADC3

6

AD6644

REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

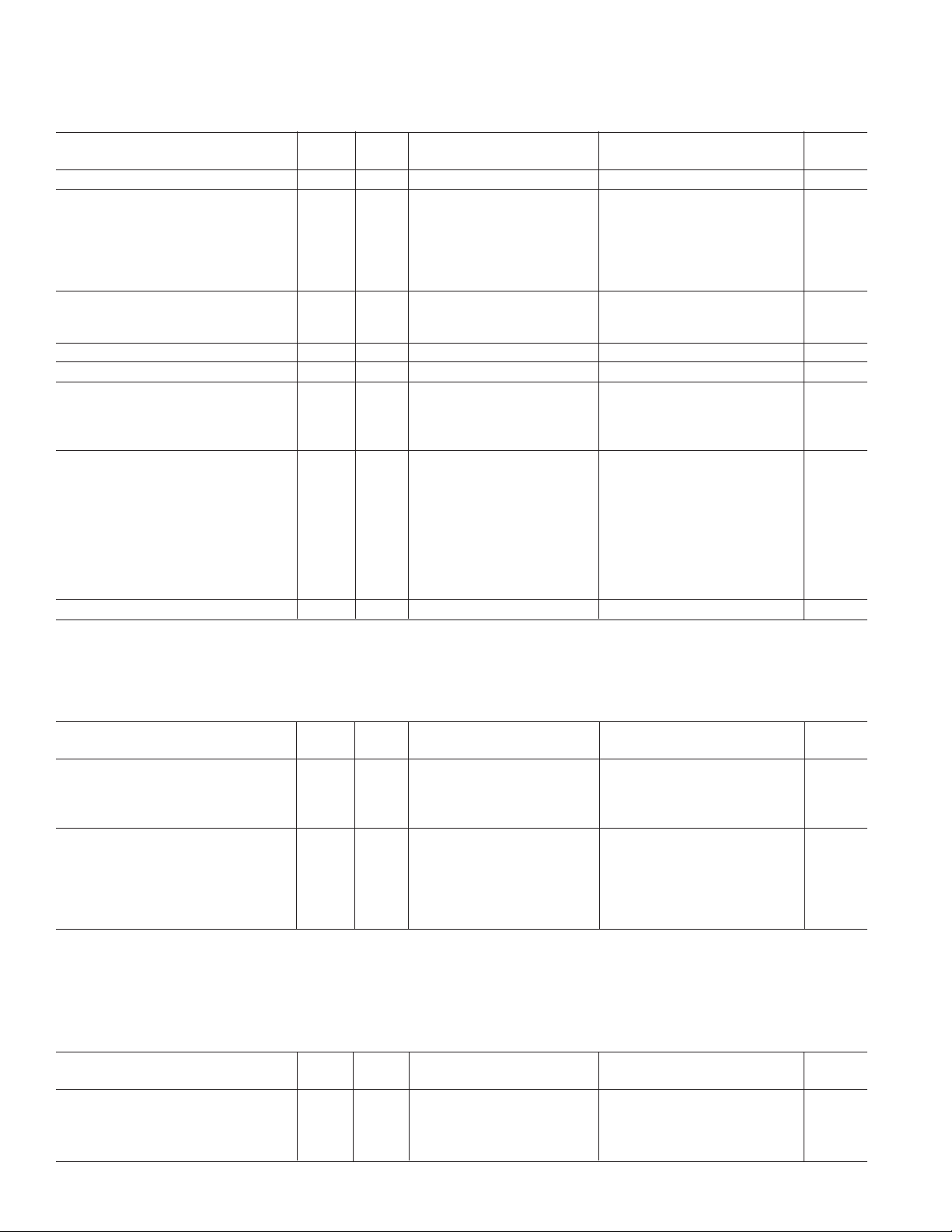

AD6644–SPECIFICATIONS

DC SPECIFICATIONS

(AVCC = 5 V, DVCC = 3.3 V; T

= –25ⴗC, T

MIN

= +85ⴗC)

MAX

Test AD6644AST-40 AD6644AST-65

Parameter Temp Level Min Typ Max Min Typ Max Unit

RESOLUTION 14 14 Bits

ACCURACY

No Missing Codes Full II Guaranteed Guaranteed

Offset Error Full II –10 3 +10 –10 3 +10 mV

Gain Error Full II –10 – 6 +10 –10 –6 +10 % FS

Differential Nonlinearity (DNL) Full II –1.0 ± 0.25 +1.5 –1.0 ± 0.25 +1.5 LSB

Integral Nonlinearity (INL) Full V ±0.50 ±0.50 LSB

TEMPERATURE DRIFT

Offset Error Full V 10 10 ppm/∞C

Gain Error Full V 95 95 ppm/∞C

POWER SUPPLY REJECTION (PSRR) Full V ± 1.0 ±1.0 mV/V

REFERENCE OUT (V

) Full V 2.4 2.4 V

REF

ANALOG INPUTS (AIN, AIN)

Differential Input Voltage Range Full V 2.2 2.2 V p-p

Differential Input Resistance Full V 1 1 kW

Differential Input Capacitance 25∞CV 1.5 1.5 pF

POWER SUPPLY

Supply Voltage

AV

DV

CC

1

CC

Full II 4.85 5.0 5.25 4.85 5.0 5.25 V

Full II 3.0 3.3 3.6 3.0 3.3 3.6 V

Supply Current

(AVCC = 5.0 V) Full II 245 276 245 276 mA

IA

VCC

(DVCC = 3.3 V) Full II 30 36 30 36 mA

ID

VCC

AV

CC

2

Full IV 15 ms

Rise Time

POWER CONSUMPTION Full II 1.3 1.5 1.3 1.5 W

NOTES

1

AVCC may be varied from 4.85 V to 5.25 V. However, rated ac (harmonics) performance is valid only over the range AVCC = 5.0 V to 5.25 V.

2

Specified for dc supplies with linear rise time characteristics.

Specifications subject to change without notice.

DIGITAL SPECIFICATIONS

(AVCC = 5 V, DVCC = 3.3 V; T

= –25ⴗC, T

MIN

= +85ⴗC)

MAX

Test AD6644AST-40 AD6644AST-65

Parameter Temp Level Min Typ Max Min Typ Max Unit

ENCODE INPUTS (ENC, ENC)

Differential Input Voltage

1

Full IV 0.4 0.4 V p-p

Differential Input Resistance 25∞CV 10 10 kW

Differential Input Capacitance 25∞CV 2.5 2.5 pF

LOGIC OUTPUTS (D13–D0, DRY, OVR)

Logic Compatibility CMOS CMOS

Logic “1” Voltage

Logic “0” Voltage

2

2

Full V 2.5 2.5 V

Full V 0.4 0.4 V

Output Coding Twos Complement Twos Complement

DMID Full V DVCC/2 DVCC/2 V

NOTES

1

All ac specifications tested by driving ENCODE and ENCODE differentially. Reference TPC 15 for performance versus encode power.

2

Digital output logic levels: DVCC = 3.3 V, C

Specifications subject to change without notice.

= 10 pF. Capacitive loads >10 pF will degrade performance.

LOAD

(AVCC = 5 V, DVCC = 3.3 V; ENCODE and ENCODE = Maximum Conversion Rate MSPS;

T

SWITCHING SPECIFICATIONS

= –25ⴗC, T

MIN

Test AD6644AST-40 AD6644AST-65

Parameter Temp Level Min Typ Max Min Typ Max Unit

Maximum Conversion Rate Full II 40 65 MSPS

Minimum Conversion Rate Full IV 15 15 MSPS

ENCODE Pulsewidth High Full IV 10 6.5 ns

ENCODE Pulsewidth Low Full IV 10 6.5 ns

Specifications subject to change without notice.

= +85ⴗC)

MAX

–2–

REV. C

AD6644

1

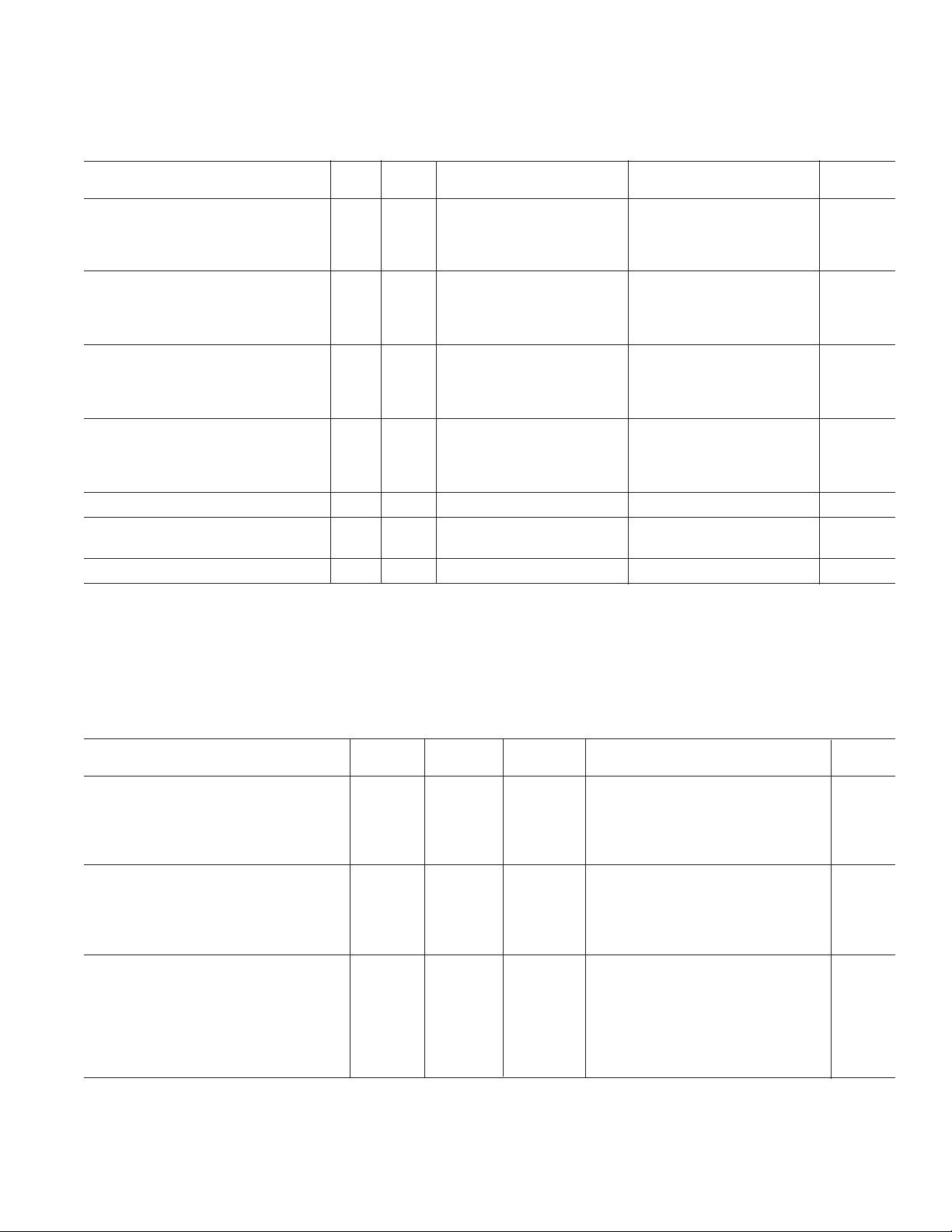

AC SPECIFICATIONS

(AVCC = 5 V, DVCC = 3.3 V; ENCODE and ENCODE = Maximum Conversion Rate MSPS; T

Test AD6644AST-40 AD6644AST-65

Parameter Temp Level Min Typ Max Min Typ Max Unit

SNR

Analog Input 2.2 MHz 25∞CII 74.5 72 74.5 dB

@ –1 dBFS 15.5 MHz 25∞CII 74.0 72 74.0 dB

30.5 MHz 25∞CII 73.5 72 73.5 dB

2

SINAD

Analog Input 2.2 MHz 25∞CII 74.5 72 74.5 dB

@ –1 dBFS 15.5 MHz 25∞CII 74.0 72 74.0 dB

30.5 MHz 25∞CV 73.0 73.0 dB

WORST HARMONIC

(2ND

or 3RD)

2

Analog Input 2.2 MHz 25∞CII 92 8392 dBc

@ –1 dBFS 15.5 MHz 25∞CII 90 8390 dBc

30.5 MHz 25∞CV 85 85 dBc

WORST HARMONIC (4

TH

or Higher)

2

Analog Input 2.2 MHz 25∞CII 93 8593 dBc

@ –1 dBFS 15.5 MHz 25∞CII 92 8592 dBc

30.5 MHz 25∞CV 92 92 dBc

TWO-TONE SFDR2,

TWO-TONE IMD REJECTION

3, 4

Full V 100 100 dBFS

2, 4

F1, F2 @ –7 dBFS Full V 90 90 dBc

ANALOG INPUT BANDWIDTH 25∞CV 250 250 MHz

NOTES

1

All ac specifications tested by driving ENCODE and ENCODE differentially.

2

AVCC = 5 V to 5.25 V for rated ac performance.

3

Analog input signal power swept from –7 dBFS to –100 dBFS.

4

F1 = 15 MHz, F2 = 15.5 MHz.

Specifications subject to change without notice.

= –25ⴗC, T

MIN

= +85ⴗC)

MAX

(AVCC = 5 V, DVCC = 3.3 V; ENCODE and ENCODE = Maximum Conversion Rate MSPS;

T

SWITCHING SPECIFICATIONS

= –25ⴗC, T

MIN

Parameter Name Temp Level Min Typ Max Unit

ENCODE INPUT PARAMETERS

Encode Period1 @ 65 MSPS t

Encode Period

Encode Pulsewidth High

1

@ 40 MSPS t

2

Encode Pulsewidth Low @ 65 MSPS t

1

@ 65 MSPS t

ENC

ENC

ENCH

ENCL

ENCODE/DATA READY

Encode Rising to Data Ready Falling t

Encode Rising to Data Ready Rising t

DR

E_DR

@ 65 MSPS (50% Duty Cycle) Full IV 10.3 11.1 12.3 ns

@ 40 MSPS (50% Duty Cycle) Full IV 15.1 15.9 17.1 ns

ENCODE/DATA (D13:0), OVR

ENC to DATA Falling Low t

ENC to DATA Rising Low t

ENCODE to DATA Delay (Hold Time)

ENCODE to DATA Delay (Setup Time)

3

4

E_FL

E_RL

t

H_E

t

S_E

Encode = 65 MSPS (50% Duty Cycle) Full IV 6.2 9.8 11.6 ns

Encode = 40 MSPS (50% Duty Cycle) Full IV 15.9 19.4 21.2 ns

= +85ⴗC, C

MAX

= 10 pF)

LOAD

Test AD6644AST-40/65

Full V 15.4 ns

Full V 25 ns

Full IV 6.2 7.7 9.2 ns

Full IV 6.2 7.7 9.2 ns

Full IV 2.6 3.4 4.6 ns

t

+ t

ENCH

DR

Full IV 3.8 5.5 9.2 ns

Full IV 3.0 4.3 6.4 ns

Full IV 3.0 4.3 6.4 ns

t

– t

ENC

E_FL

REV. C

–3–

AD6644–SPECIFICATIONS

Test AD6644AST-40/65

Parameter Name Temp Level Min Typ Max Unit

DATA READY (DRY

Data Ready to DATA Delay (Hold Time)

Encode = 65 MSPS (50% Duty Cycle) Full IV 8.0 8.6 9.4 ns

Encode = 40 MSPS (50% Duty Cycle) Full IV 12.8 13.4 14.2 ns

Data Ready to DATA Delay (Setup Time)

@ 65 MSPS (50% Duty Cycle) Full IV 3.2 5.5 6.5 ns

@ 40 MSPS (50% Duty Cycle) Full IV 8.0 10.3 11.3 ns

APERTURE DELAY t

APERTURE UNCERTAINTY (JITTER) t

NOTES

1

Several timing parameters are a function of t

2

To compensate for a change in duty cycle for t

Newt

= (t

H_DR

Newt

3

ENCODE to DATA Delay (Hold Time) is the absolute minimum propagation delay through the analog-to-digital converter.

4

ENCODE to DATA Delay (Setup Time) is calculated relative to 65 MSPS (50% duty cycle). In order to calculate t

Newt

5

DRY is an inverted and delayed version of the encode clock. Any change in the duty cycle of the clock will correspondingly change the duty cycle of DRY.

6

Data Ready to DATA Delay (t

and t

Newt

Newt

Specifications subject to change without notice.

H_DR

= (t

S_DR

S_DR

= t

S_E

ENC(NEW)

for a given encode use the following equations:

S_DR

= t

H_DR

ENC(NEW)

= t

S_DR

ENC(NEW)

5

)/DATA, OVR

– % Change(t

– % Change(t

– t

+ t

ENC

/2 – t

ENCH

/2 – t

ENCH

2

and t

ENC

)) ¥ t

ENCH

)) ¥ t

ENCH

(i.e., for 40 MSPS: Newt

S_E

and t

H_DR

+ t

H_DR

+ t

S_DR

H_DR

/2

ENC

/2.

ENC

) is calculated relative to 65 MSPS (50% duty cycle) and is dependent on t

S_DR

(i.e., for 40 MSPS: Newt

(i.e., for 40 MSPS: Newt

2

and t

t

H_DR

t

S_DR

A

J

.

ENCH

use the following equations:

S_DR

S_E(TYP)

H_DR(TYP)

S_DR(TYP)

25∞CV 100 ps

25∞CV 0.2 ps rms

= 25 ¥ 10–9 – 15.38 ¥ 10–9 + 9.8 ¥ 10–9 = 19.4 ¥ 10–9).

= 12.5 ¥ 10–9 – 7.69 ¥ 10–9 + 8.6 ¥ 10–9 = 13.4 ¥ 10–9).

= 12.5 ¥ 10–9 – 7.69 ¥ 10–9 + 5.5 ¥ 10–9 = 10.3 ¥ 10–9).

Note 6

Note 6

for a given encode use the following equation:

S_E

and duty cycle. In order to calculate t

ENC

H_DR

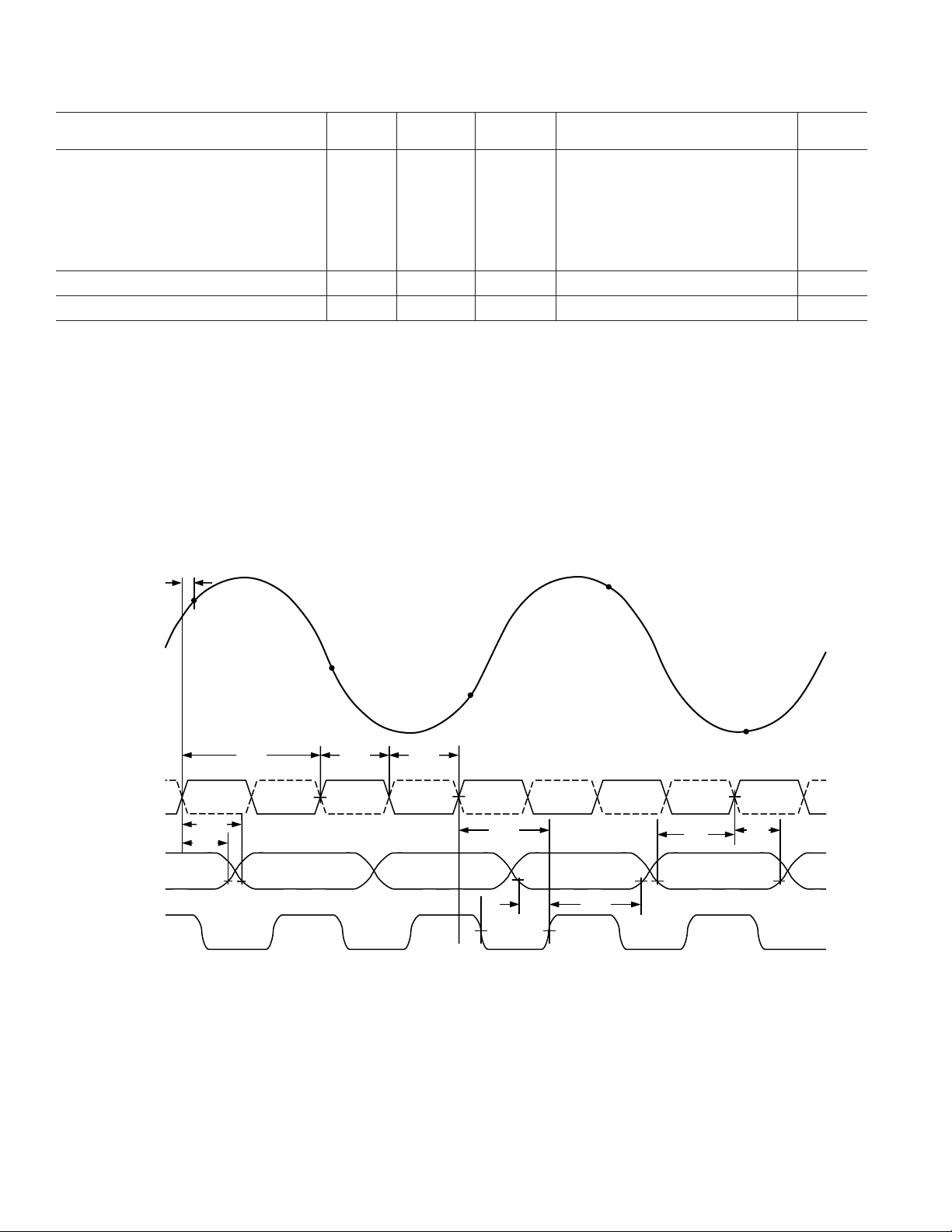

AIN

ENC, ENC

D[13:0], OVR

DRY

t

A

Nⴙ3

N

Nⴙ1

Nⴙ2

t

t

E_FL

E_RL

t

ENC

N

N–3

t

ENCH

Nⴙ1

t

ENCL

N–2

Nⴙ2Nⴙ3Nⴙ4

t

E_DR

N–1

t

DR

t

S_DR

t

H_DR

t

S_E

Nⴙ4

t

H_E

N

Figure 1. Timing Diagram

–4–

REV. C

AD6644

ABSOLUTE MAXIMUM RATINGS

1

EXPLANATION OF TEST LEVELS

Test Level

Parameter Min Max Unit

ELECTRICAL

AV

Voltage 0 7 V

CC

DV

Voltage 0 7 V

CC

Analog Input Voltage 0 AV

CC

V

Analog Input Current 25 mA

Digital Input Voltage 0 AV

CC

V

Digital Output Current 4 mA

ENVIRONMENTAL

2

I 100% production tested.

II 100% production tested at 25∞C, and guaranteed by

design and characterization at temperature extremes.

III Sample tested only.

IV Parameter is guaranteed by design and characterization

testing.

V Parameter is a typical value only.

Operating Temperature Range

(Ambient) –25 +85 ∞C

Maximum Junction Temperature 150 ∞C

Lead Temperature (Soldering, 10 sec) 300 ∞C

Storage Temperature Range (Ambient) –65 +150 ∞C

NOTES

1

Absolute maximum ratings are limiting values to be applied individually, and

beyond which the serviceability of the circuit may be impaired. Functional

operability is not necessarily implied. Exposure to absolute maximum rating

conditions for an extended period of time may affect device reliability.

2

Typical thermal impedances (52-lead LQFP): qJA = 33∞C/W; qJC = 11∞C/W.

These measurements were taken on a 6-layer board in still air with a solid ground

plane.

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD6644AST-40 –25∞C to +85∞C (Ambient) 52-Lead LQFP (Low Profile Quad Flat Package) ST-52

AD6644AST-65 –25∞C to +85∞C (Ambient) 52-Lead LQFP (Low Profile Quad Flat Package) ST-52

AD6644ST/PCB Evaluation Board with AD6644AST–65

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD6644 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. C

–5–

AD6644

PIN FUNCTION DESCRIPTIONS

Pin No. Name Function

1, 33, 43 DV

CC

2, 4, 7, 10, 13, 15, 17, 19, 21, 23, GND Ground.

25, 27, 29, 34, 42

3V

REF

5 ENCODE Encode Input; conversion initiated on rising edge.

6 ENCODE Complement of ENCODE; differential input.

8, 9, 14, 16, 18, 22, 26, 28, 30 AV

CC

11 AIN Analog Input.

12 AIN Complement of AIN; Differential Analog Input.

20 C1 Internal Voltage Reference; bypass to ground with 0.1 mF microwave

24 C2 Internal Voltage Reference; bypass to ground with 0.1 mF microwave

31 DNC Do not connect this pin.

32 OVR Overrange Bit; high indicates analog input exceeds ±FS.

35 DMID Output Data Voltage Midpoint; approximately equal to (DV

36 D0 (LSB) Digital Output Bit (Least Significant Bit); Twos Complement.

37–41, 44–50 D1–D5, D6–D12 Digital Output Bits in Twos Complement.

51 D13 (MSB) Digital Output Bit (Most Significant Bit); Twos Complement.

52 DRY Data Ready Output.

3.3 V Power Supply (Digital) Output Stage Only.

2.4 V (Analog Reference). Bypass to ground with 0.1 mF microwave

chip capacitor.

5 V Analog Power Supply.

chip capacitor.

chip capacitor.

)/2.

CC

DV

GND

V

REF

GND

ENCODE

ENCODE

GND

AV

AV

GND

AIN

AIN

GND

CC

CC

CC

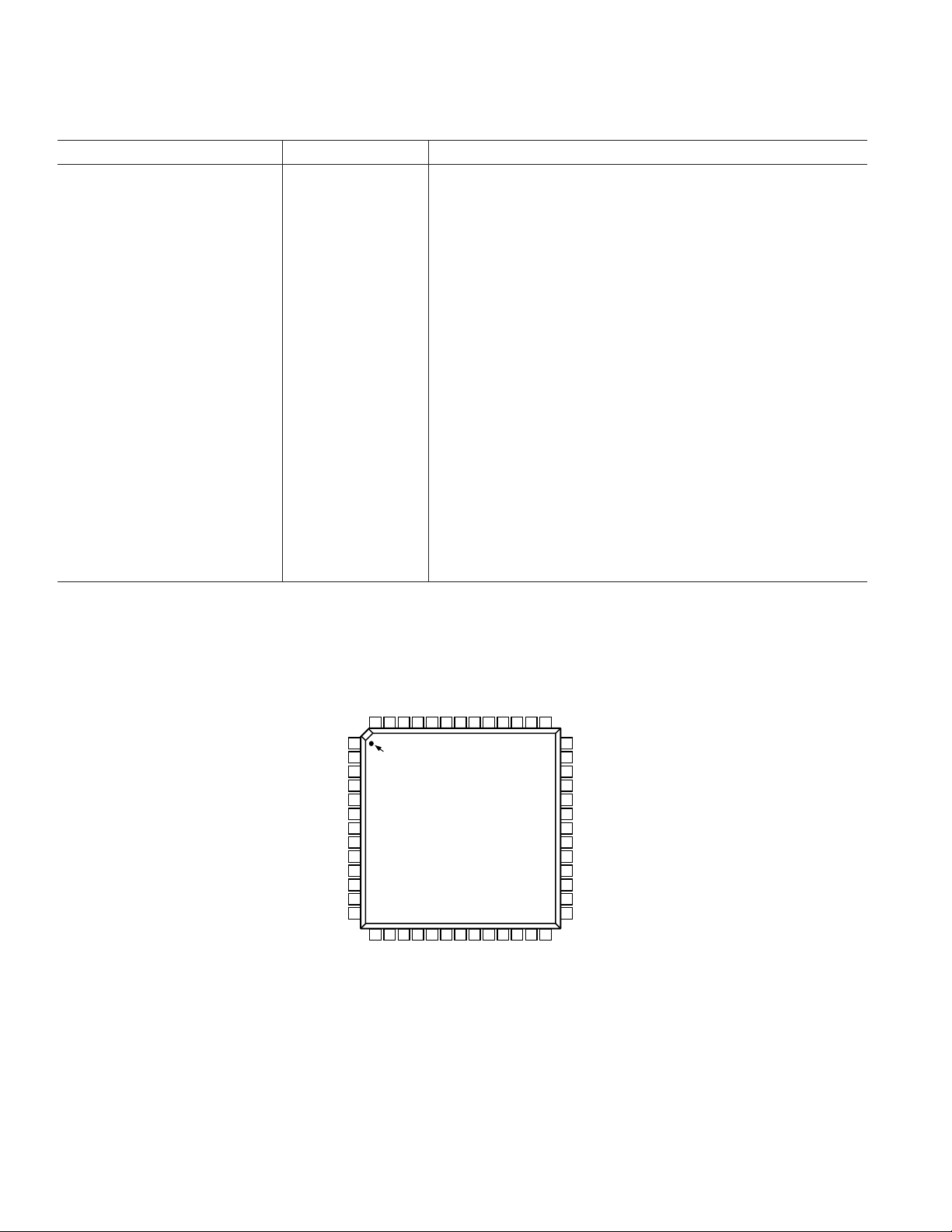

PIN CONFIGURATION

D8

D9

D10

D11

D12

D13 (MSB)

DRY

1

PIN 1

IDENTIFIER

2

3

4

5

6

7

8

9

10

11

12

13

14 151617 18

CC

AV

GND

AD6644

TOP VIEW

(Not to Scale)

19 20 21 22 23 24 25 26

CC

CC

AV

DNC = DO NOT CONNECT

GND

AV

GND

C1

D7

GND

AV

CC

D4

D5

GND

DV

D6

CC

GND

40414243444546474849505152

39

D3

D2

38

37

D1

D0 (LSB)

36

DMID

35

34

GND

DV

33

CC

32

OVR

31

DNC

AV

30

CC

29

GND

AV

28

CC

GND

27

CC

C2

GND

AV

–6–

REV. C

Loading...

Loading...