Analog Devices AD6635 Datasheet

4-Channel, 80 MSPS WCDMA

Receive Signal Processor (RSP)

AD6635

FEATURES

Four 80 MSPS Wideband Inputs (14 Linear Bits Plus 3 RSSI)

4 Real Input Ports/2 Complex Input Ports

Processes 4 Wideband Channels (UMTS or cdma2000

1x) or 8 GSM/EDGE, IS136 Channels

8 Independent Digital Receivers in a Single Package

Four 16-Bit Parallel Output Ports and Four 8-Bit Link Ports

4 Programmable Digital AGC Loops with 96 dB Range

Digital Resampling for Noninteger Decimation Rates

Programmable Decimating FIR Filters

4 Interpolating Half-Band Filters

Flexible Control for Multicarrier and Phased Array

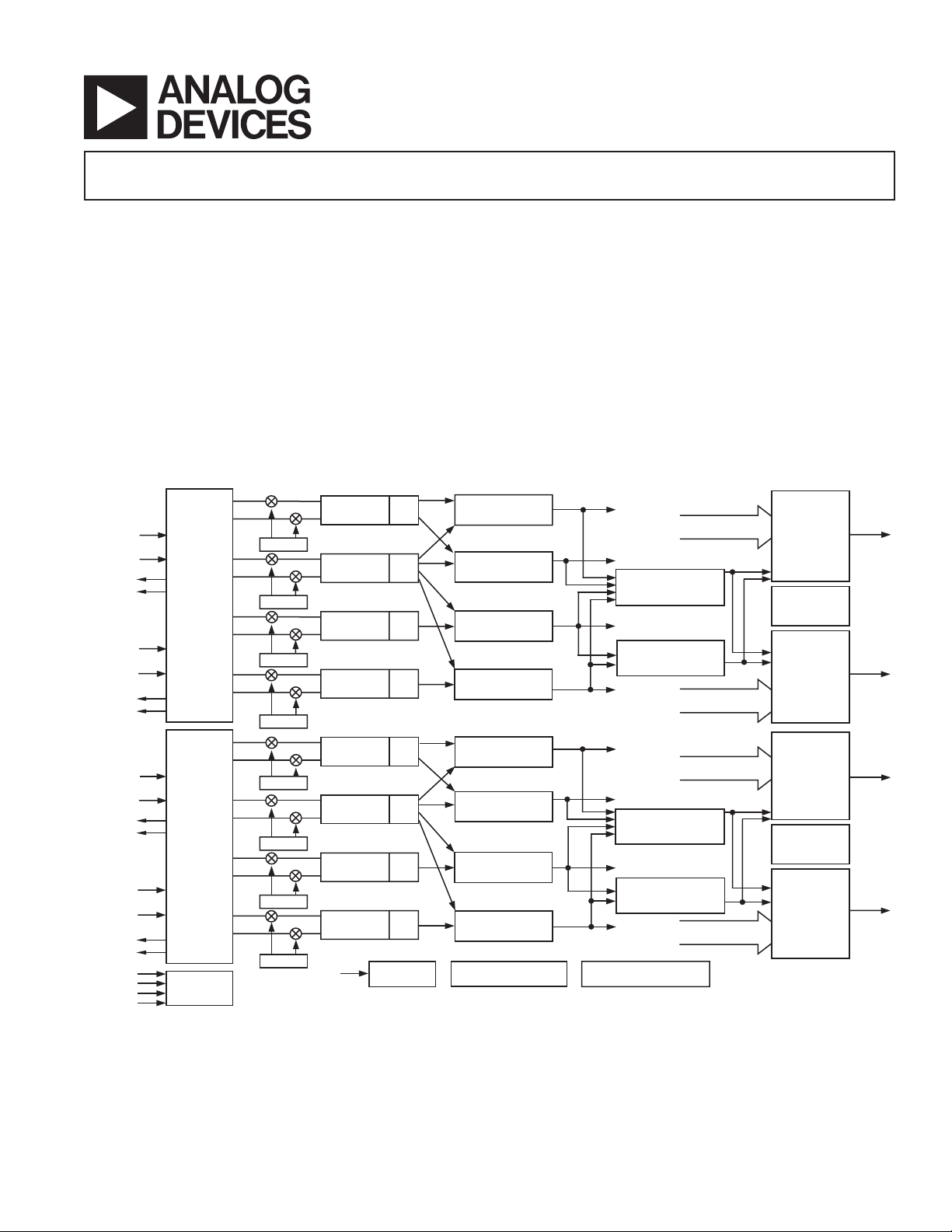

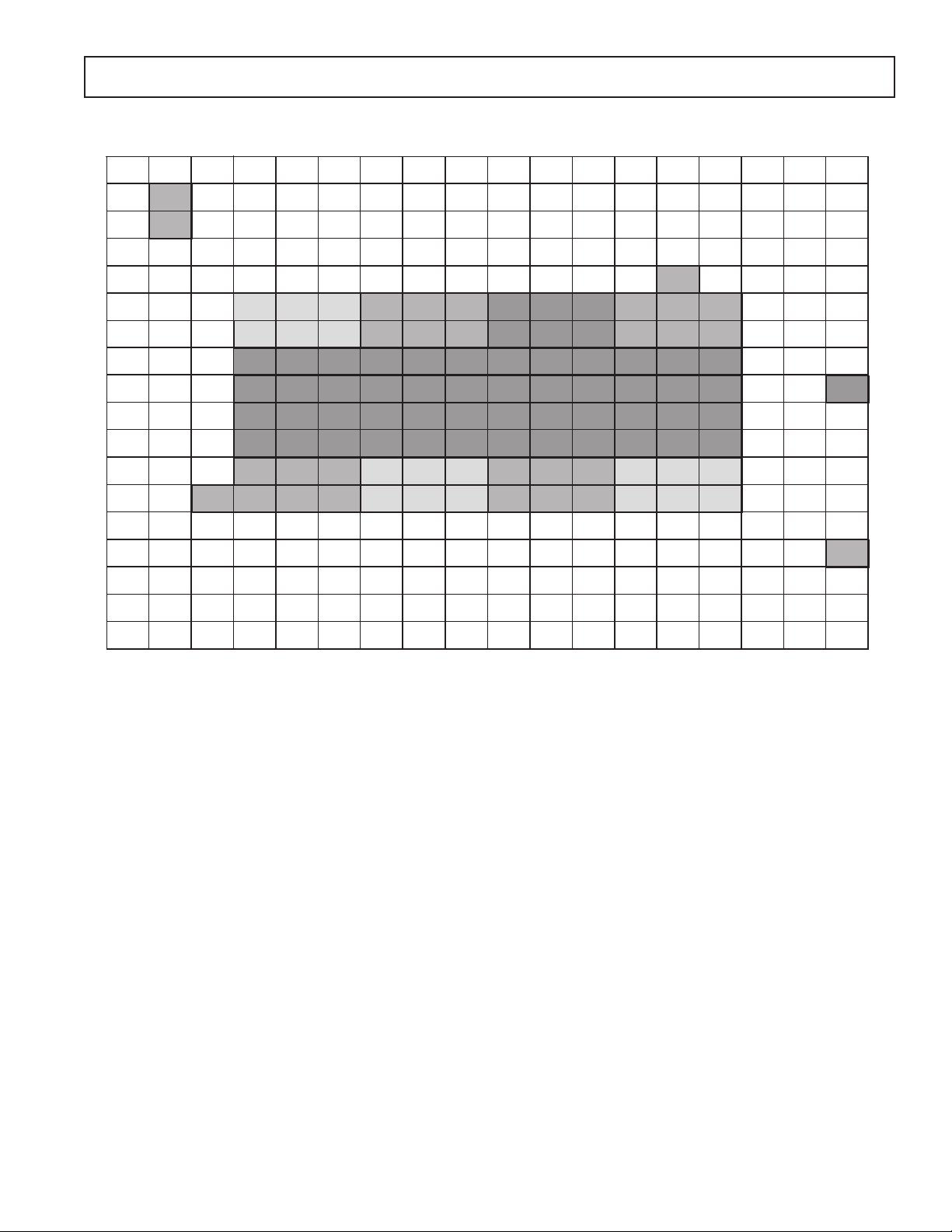

FUNCTIONAL BLOCK DIAGRAM

INA[13:0]

EXPA[2:0]

IENA

LIA-A

LIA-B

INB[13:0]

EXPB[2:0]

IENB

LIB-A

LIB-B

INC[13:0]

EXPC[2:0]

IENC

LIB-A

LIB-B

IND[13:0]

EXPD[2:0]

IEND

LID-A

LID-B

SYNCA

SYNCB

SYNCC

SYNCD

I

N

P

U

T

M

A

T

R

I

X

I

N

P

U

T

M

A

T

R

I

X

EXTERNAL

SYNC.

CIRCUIT

NCO

NCO

NCO

NCO

NCO

NCO

NCO

NCO

rCIC2

RESAMPLER

rCIC2

RESAMPLER

rCIC2

RESAMPLER

rCIC2

RESAMPLER

rCIC2

RESAMPLER

rCIC2

RESAMPLER

rCIC2

RESAMPLER

rCIC2

RESAMPLER

CLK

CIC5

CIC5

CIC5

CIC5

CIC5

CIC5

CIC5

CIC5

RSP

CLK

Programmable Attenuator Control for Clip Prevention and

External Gain Ranging via Level Indicator

3.3 V I/O, 2.5 V CMOS Core

User Configurable Built-in Self Test (BIST) Capability

APPLICATIONS

Multicarrier, Multimode Digital Receivers

GSM, IS136, EDGE, PHS, IS95, UMTS, cdma2000

Micro and Pico Cell Systems, Software Radios

Wireless Local Loop

Smart Antenna Systems

In-Building Wireless Telephony

RAM

COEFFICIENT

FILTER

CHANNEL 0

RAM

COEFFICIENT

FILTER

CHANNEL 1

RAM

COEFFICIENT

FILTER

CHANNEL 2

RAM

COEFFICIENT

FILTER

CHANNEL 3

RAM

COEFFICIENT

FILTER

CHANNEL 4

RAM

COEFFICIENT

FILTER

CHANNEL 5

RAM

COEFFICIENT

FILTER

CHANNEL 6

RAM

COEFFICIENT

FILTER

CHANNEL 7

BUILT-IN (BIST)

SELF-TEST CIRCUITRY

TO A AND B

OUTPUT

PORTS

TO A AND B

OUTPUT

PORTS

CH A INTERPOLATING

HALF-BAND FILTER,

INTERLEAVING & AGC

TO A AND B

OUTPUT

PORTS

CH B INTERPOLATING

HALF-BAND FILTER,

INTERLEAVING & AGC

TO A AND B

OUTPUT

PORTS

TO C AND D

OUTPUT

PORTS

TO C AND D

OUTPUT

PORTS

CH C INTERPOLATING

HALF-BAND FILTER,

INTERLEAVING & AGC

TO C AND D

OUTPUT

PORTS

CH D INTERPOLATING

HALF-BAND FILTER,

INTERLEAVING & AGC

TO C AND D

OUTPUT

PORTS

MICROPORT OR SERIAL

PORT CONTROL

RCF OUTPUTS

CHANNELS 0,

RCF OUTPUTS

CHANNELS 0,

RCF OUTPUTS

CHANNELS 4, 5, 6, 7

RCF OUTPUTS

CHANNELS 4,

1, 2,

1, 2,

5, 6,

PORT A

LINK PORT

3

OR

PARALLEL

PORT

CH A AND B

OUTPUT MUX

CIRCUITRY

PORT B

LINK PORT

OR

PARALLEL

PORT

3

PORT C

8-BIT DSP

LINK PORT

OR

16-BIT

PARALLEL

OUTPUT

CH C AND D

OUTPUT MUX

CIRCUITRY

PORT D

8-BIT DSP

LINK PORT

OR

16-BIT

7

PARALLEL

OUTPUT

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

AD6635

GENERAL DESCRIPTION

The AD6635 is a multimode, 8-channel, digital Receive Signal

Processor (RSP) capable of processing up to four WCDMA

channels. Each channel consists of four cascaded signal-processing elements: a frequency translator, two CIC decimating filters,

and a programmable coefficient-decimating filter. Each input

port has input level threshold detection circuitry for accommodating large dynamic ranges or situations where gain ranging

converters are used. Quad 16-bit parallel output ports accommodate high data rate WBCDMA applications. On-chip

interpolating half-band filters can also be used to further

increase the output rate. In addition, each output port has a

digital AGC for accommodating large dynamic ranges using

smaller bit widths. The AGCs can maintain either signal level or

clipping level, depending on their mode. Link port outputs are

provided to enable glueless interfaces to Analog Devices’

TigerSHARC DSP core.

The AD6635 is part of Analog Devices’ SoftCell Multicarrier

transceiver chipset designed for compatibility with Analog Devices’

family of high sample rate IF sampling ADCs (AD9238/AD6645

12-bit and 14-bit). The SoftCell receiver comprises a digital

receiver capable of digitizing an entire spectrum of carriers and

digitally selecting the carrier of interest for tuning and channel

selection. This architecture eliminates redundant radios in wireless

base station applications.

High dynamic range decimation filters offer a wide range of

decimation rates. The RAM-based architecture allows easy

reconfiguration for multimode applications.

The decimating filters remove unwanted signals and noise from

the channel of interest. When the channel of interest occupies

less bandwidth than the input signal, this rejection of out-of-band

noise is called “processing gain.” By using large decimation

factors, processing gain can improve the SNR of the ADC by

30 dB or more. In addition, the programmable RAM coefficient

filter allows antialiasing, matched filtering, and static equalization functions to be combined in a single, cost-effective filter.

Half-band interpolating filters at the output are used in various

applications, especially in WCDMA or cdma2000 applications,

to increase the output rate from 2¥ to 4¥ the chip rate. The

AD6635 is equipped with four independent automatic gain

control (AGC) loops for direct interface to a RAKE receiver.

The AD6635 is compatible with standard ADC converters, such

as the AD664x, AD943x, AD923x, and the AD922x families of

data converters. The AD6635 is also compatible with the

AD6600 Diversity ADC, and hence can be designed into existing systems that use AD6600 ADCs.

REV. 0–2–

TABLE OF CONTENTS

AD6635

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . 2

ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

RECOMMENDED OPERATING CONDITIONS . . . . . . . 7

ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . 7

GENERAL TIMING CHARACTERISTICS . . . . . . . . . . . . 8

MICROPROCESSOR PORT TIMING

CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . 10

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . 11

ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

PIN CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . 12

PIN CONFIGURATION (PIN OUT) . . . . . . . . . . . . . . . . 13

PIN FUNCTION DESCRIPTION . . . . . . . . . . . . . . . . . . 14

TIMING DIAGRAMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

INPUT DATA PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Input Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Input Enable Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Gain Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Input Data Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Scaling with Fixed-Point ADCs . . . . . . . . . . . . . . . . . . . . 24

Scaling with Floating-Point or Gain-Ranging ADCs . . . . 25

NUMERICALLY CONTROLLED OSCILLATOR . . . . . 26

Frequency Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

NCO Frequency Hold-Off Register . . . . . . . . . . . . . . . . . 26

Phase Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

NCO Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

By-Pass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Phase Dither . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Amplitude Dither . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Clear Phase Accumulator on Hop . . . . . . . . . . . . . . . . . . 26

Input Enable Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Mode 00: Blank on IEN Low . . . . . . . . . . . . . . . . . . . 27

Mode 01: Clock on IEN High . . . . . . . . . . . . . . . . . . . 27

Mode 10: Clock on IEN Transition to High . . . . . . . . 27

Mode 11: Clock on IEN Transition to Low . . . . . . . . . 27

WB Input Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Sync Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

SECOND-ORDER rCIC FILTER . . . . . . . . . . . . . . . . . . . 27

rCIC2 Rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Example Calculations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Decimation and Interpolation Registers . . . . . . . . . . . . . . 29

rCIC2 Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

FIFTH-ORDER CIC FILTER . . . . . . . . . . . . . . . . . . . . . . 29

CIC5 Rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

RAM COEFFICIENT FILTER . . . . . . . . . . . . . . . . . . . . . 30

RCF Decimation Register . . . . . . . . . . . . . . . . . . . . . . . . 30

RCF Decimation Phase . . . . . . . . . . . . . . . . . . . . . . . . . . 30

RCF Filter Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

RCF Output Scale Factor and Control Register . . . . . . . . 31

INTERPOLATING HALF BAND FILTERS . . . . . . . . . . 32

AUTOMATIC GAIN CONTROL . . . . . . . . . . . . . . . . . . . 32

The AGC Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Desired Signal Level Mode . . . . . . . . . . . . . . . . . . . . . . . 33

Desired Clipping Level Mode . . . . . . . . . . . . . . . . . . . . . 34

Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

USER CONFIGURABLE BUILT IN SELF TEST

(BIST) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

RAM BIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Channel BIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

CHIP SYNCHRONIZATION . . . . . . . . . . . . . . . . . . . . . . 36

Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Start with No Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Start with Soft Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Start with Pin Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Hop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Set Freq No Hop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Hop with Soft Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Hop with Pin Sync . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

PARALLEL OUTPUT PORTS . . . . . . . . . . . . . . . . . . . . . 37

Channel Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

AGC Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Master/Slave PCLKn Modes . . . . . . . . . . . . . . . . . . . . . . 39

Parallel Port Pin Functionality . . . . . . . . . . . . . . . . . . . . . 39

LINK PORT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Link Port Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Link Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

TigerSHARC Configuration . . . . . . . . . . . . . . . . . . . . . . 41

AD6635 CHANNEL MEMORY MAP . . . . . . . . . . . . . . . . 41

0x00-0x7F: Coefficient Memory (CMEM) . . . . . . . . . . . 42

0x80: Channel Sleep Register . . . . . . . . . . . . . . . . . . . . . 42

0x81: Soft_SYNC Register . . . . . . . . . . . . . . . . . . . . . . . 42

0x82: Pin_SYNC Register . . . . . . . . . . . . . . . . . . . . . . . . 42

0x83: Start Hold-Off Counter . . . . . . . . . . . . . . . . . . . . . 42

0x84: NCO Frequency Hold-Off Counter . . . . . . . . . . . 42

0x85: NCO Frequency Register 0 . . . . . . . . . . . . . . . . . . 42

0x86: NCO Frequency Register 1 . . . . . . . . . . . . . . . . . . 42

0x87: NCO Phase Offset Register . . . . . . . . . . . . . . . . . . 42

0x88: NCO Control Register . . . . . . . . . . . . . . . . . . . . . 42

0x90: rCIC2 Decimation – 1 (MrCIC2-1) . . . . . . . . . . . 44

0x91: rCIC2 Interpolation – 1 (LrCIC2-1) . . . . . . . . . . . 44

0x92: rCIC2 Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

0x93: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

0x94: CIC5 Decimation – 1 (MCIC5-1) . . . . . . . . . . . . . 44

0x95: CIC5 Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

0x96: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

0xA0: RCF Decimation – 1 (MRCF-1) . . . . . . . . . . . . . 44

0xA1: RCF Decimation Phase (PRCF) . . . . . . . . . . . . . . 44

0xA2: RCF Number of Taps Minus 1 (NRCF-1) . . . . . . 44

0xA3: RCF Coefficient Offset (CORCF) . . . . . . . . . . . . 44

0xA4: RCF Control Register . . . . . . . . . . . . . . . . . . . . . . 45

0xA5: BIST Register for I . . . . . . . . . . . . . . . . . . . . . . . . 45

0xA6: BIST Register for Q . . . . . . . . . . . . . . . . . . . . . . . 45

0xA7: BIST Control Register . . . . . . . . . . . . . . . . . . . . . 45

0xA8: RAM BIST Control Register . . . . . . . . . . . . . . . . 45

0xA9: Output Control Register . . . . . . . . . . . . . . . . . . . . 45

Memory Map for Input Port Control Registers . . . . . . . . . . 46

Input Port Control Registers . . . . . . . . . . . . . . . . . . . . . . . . 46

0x00: Lower Threshold A: . . . . . . . . . . . . . . . . . . . . . . . . 46

0x01: Upper Threshold A: . . . . . . . . . . . . . . . . . . . . . . . . 46

0x02: Dwell Time A: . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

0x03: Gain Range A Control Register: . . . . . . . . . . . . . . . 46

0x04: Lower Threshold B: . . . . . . . . . . . . . . . . . . . . . . . . 47

0x05: Upper Threshold B: . . . . . . . . . . . . . . . . . . . . . . . . 47

0x06: Dwell Time B: . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

0x07: Gain Range B Control Register: . . . . . . . . . . . . . . . 47

Memory Map for Output Port Control Registers . . . . . . . . . 47

REV. 0

–3–

AD6635

TABLE OF CONTENTS

0x08: Port A Control Register . . . . . . . . . . . . . . . . . . . . . 50

0x09: Port B Control Register . . . . . . . . . . . . . . . . . . . . . 50

0x0A AGC A Control Register . . . . . . . . . . . . . . . . . . . . . 50

0x0B AGC A Hold off Counter . . . . . . . . . . . . . . . . . . . . 50

0x0C AGC A Desired Level . . . . . . . . . . . . . . . . . . . . . . . 50

0x0D AGC A Signal Gain . . . . . . . . . . . . . . . . . . . . . . . . 51

0x0E AGC A Loop Gain . . . . . . . . . . . . . . . . . . . . . . . . . 51

0x0F AGC A Pole Location . . . . . . . . . . . . . . . . . . . . . . . 51

0x10 AGC A Average Samples . . . . . . . . . . . . . . . . . . . . . 51

0x11 AGC A Update Decimation . . . . . . . . . . . . . . . . . . 51

0x12 AGC B Control Register . . . . . . . . . . . . . . . . . . . . . 51

0x13 AGC B Hold off Counter . . . . . . . . . . . . . . . . . . . . 51

0x14 AGC B Desired Level . . . . . . . . . . . . . . . . . . . . . . . 51

0x15 AGC B Signal Gain . . . . . . . . . . . . . . . . . . . . . . . . . 51

0x16 AGC B Loop Gain . . . . . . . . . . . . . . . . . . . . . . . . . 51

0x17 AGC B Pole Location . . . . . . . . . . . . . . . . . . . . . . . 52

0x18 AGC B Average Samples . . . . . . . . . . . . . . . . . . . . . 52

0x19 AGC B Update Decimation . . . . . . . . . . . . . . . . . . 52

0x1A Parallel Port Control A . . . . . . . . . . . . . . . . . . . . . . 52

0x1B Link Port Control A . . . . . . . . . . . . . . . . . . . . . . . . 52

0x1C Parallel Port Control B . . . . . . . . . . . . . . . . . . . . . . 52

0x1D Link Port Control B . . . . . . . . . . . . . . . . . . . . . . . . 53

0x1E Port Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . 53

MICROPORT CONTROL . . . . . . . . . . . . . . . . . . . . . . . . 53

External Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Access Control Register (ACR) . . . . . . . . . . . . . . . . . . . . 54

Channel Address Register (CAR) . . . . . . . . . . . . . . . . . . . 54

SOFT_SYNC Control Register . . . . . . . . . . . . . . . . . . . . 55

PIN_SYNC Control Register . . . . . . . . . . . . . . . . . . . . . . 55

SLEEP Control Register . . . . . . . . . . . . . . . . . . . . . . . . . 55

Data Address Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Write Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Read Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Read/Write Chaining . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Intel Nonmultiplexed Mode (INM) . . . . . . . . . . . . . . . . . 56

Motorola Nonmultiplexed Mode (MNM) . . . . . . . . . . . . 56

SERIAL PORT CONTROL . . . . . . . . . . . . . . . . . . . . . . . . 56

Serial Port Timing Specifications . . . . . . . . . . . . . . . . . . . 56

SDI0, SDI4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

SCLK0, SCLK4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

INTERNAL WRITE ACCESS . . . . . . . . . . . . . . . . . . . . . . 58

Write Pseudocode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

INTERNAL READ ACCESS . . . . . . . . . . . . . . . . . . . . . . . 58

Read Pseudocode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . 59

REV. 0–4–

AD6635

ARCHITECTURE

Each channel of the AD6635 has four signal processing stages:

a Frequency Translator, a second-order Resampling Cascaded

Integrator Comb FIR Filter (rCIC2), a fifth-order Cascaded

Integrator Comb FIR Filter (CIC5), and a RAM Coefficient

FIR Filter (RCF). Multiple modes are supported for clocking

data into and out of the chip, and for providing flexibility for interfacing to a wide variety of digitizers. Programming and control is

accomplished via serial and/or microprocessor interfaces.

Frequency translation is accomplished with a 32-bit complex

Numerically Controlled Oscillator (NCO). Real data entering

this stage is separated into inphase (I) and quadrature (Q) components by multiplying with the complex NCO word. This stage

translates the input signal from a digital intermediate frequency

(IF) to digital baseband. Phase and amplitude dither may be

enabled on-chip to improve spurious performance of the NCO.

A phase-offset word is available to create a known phase relationship between multiple AD6635s or between channels.

Following frequency translation is a fixed coefficient, high speed,

second-order, Resampling Cascade Integrator Comb (rCIC2) filter

that reduces the sample rate based on the ratio between the decimation and interpolation registers.

The next stage is a fifth-order Cascaded Integrator Comb (CIC5)

filter whose response is defined by the decimation rate. The purpose of these filters is to reduce the data rate to the final filter stage

(RCF), so that it can calculate more taps for the same RCF bandwidth. The CIC5 filter has better antialiasing (filtering) compared

to rCIC2. In light of this, the user is advised to use this filter only if

resampling is required or if the required decimation cannot be

handled by CIC5 alone.

The final stage is a sum-of-products FIR filter with programmable 20-bit coefficients, and decimation rates programmable

from 1 to 256 (1 to 32 in practice). The RAM Coefficient FIR

Filter (RCF) can handle a maximum of 160 taps.

The data coming out of the RCF can be sent to output ports or

to an interleaver. This section can interleave data from more

than one channel. One carrier can be processed using more than

one channel and the interleaver will interleave the data back into

the output section. This way, processing power from more than

one channel can be used for one carrier.

The interleaved data is sent into a fixed coefficient half-band

interpolation filter where data is interpolated by a factor of two.

Digital AGC following the half-band filter has a gain range of

96.3 dB. This AGC section is completely programmable in

terms of its response. Four each of half-band filters and AGCs

are present in the AD6635, as shown in the Functional Block

Diagram. These half-band filters and AGC sections can be

bypassed independent of each other.

The overall filter response for the AD6635 is the composite of

all decimating and interpolating stages. Each successive filter

stage is capable of narrower transition bandwidths, but requires

a greater number of CLK cycles to calculate the output. More

decimation in the first filter stage will minimize overall power

consumption. Each independent filter stage can be bypassed in

a unique way. Data from the chip is interfaced to the DSP via

either a high speed parallel port or a TigerSHARC compatible

link port. Each output can be independently configured to use

either the parallel port or the link port.

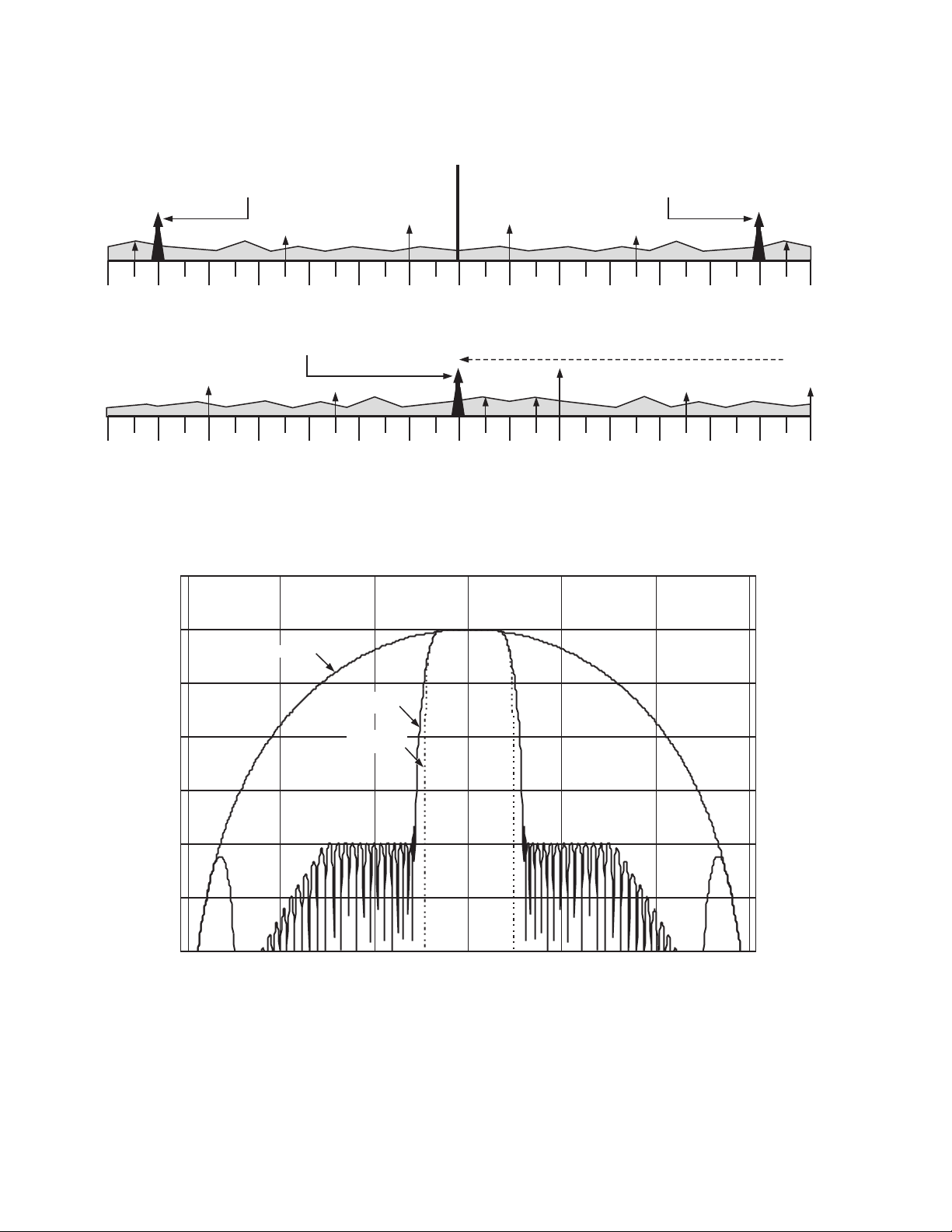

Figure 1 illustrates the tuning function of the AD6635 NCOs to

select and filter a single channel from a wide input spectrum.

The frequency translator “tunes” the desired carrier to baseband. Figure 2 shows the combined filter response of the rCIC2,

CIC5, and RCF filters for a sample filter configuration.

REV. 0

–5–

AD6635

–

f

/2 –3

S

–

f

/2 –3

S

WIDEBAND INPUT SPECTRUM

SIGNAL OF INTEREST “IMAGE” SIGNAL OF INTEREST

f

/8 –5

f

/16 –

f

/4 –3

f

/16 –

f

/8 –

f

/8 –

/16

S

f

/16

S

S

f

/8 –5

S

S

f

S

S

AFTER FREQUENCY TRANSLATION NCO “TUNES” SIGNAL TO BASEBAND

/16 –

f

S

S

WIDEBAND INPUT SPECTRUM (e.g., 30MHz FROM HIGH SPEED ADC)

/4 –3

f

S

FREQUENCY TRANSLATION (e.g., SINGLE 1MHz CHANNEL TUNED TO BASEBAND)

/16 –

S

f

S

f

/2 TO

f

(

SAMPLE

dc

dc

f

/16

S

f

/16

S

SAMPLE

f

S

f

S

/2)

/8

3f

/16

f

S

/8

3f

/16

S

/4

S

f

/4

S

Figure 1. AD6635 Frequency Translation of Wideband Input Spectrum

20

5f

/16

3f

/8

f

S

5f

/16

S

S

3f

/8

S

/2

S

f

/2

S

0

CIC RESPONSE

dBc

–100

–120

–20

–40

–60

–80

–1.5 10

4

–1.0 10

COMPOSITE

RESPONSE

DESIRED

RESPONSE

4

–5000 0 5000

kHz

1.0 10

4

1.5 10

4

Figure 2. Composite Filter Response of rCIC2, CIC5, and RCF for a Sample Filter Configuration

REV. 0–6–

AD6635

SPECIFICATIONS

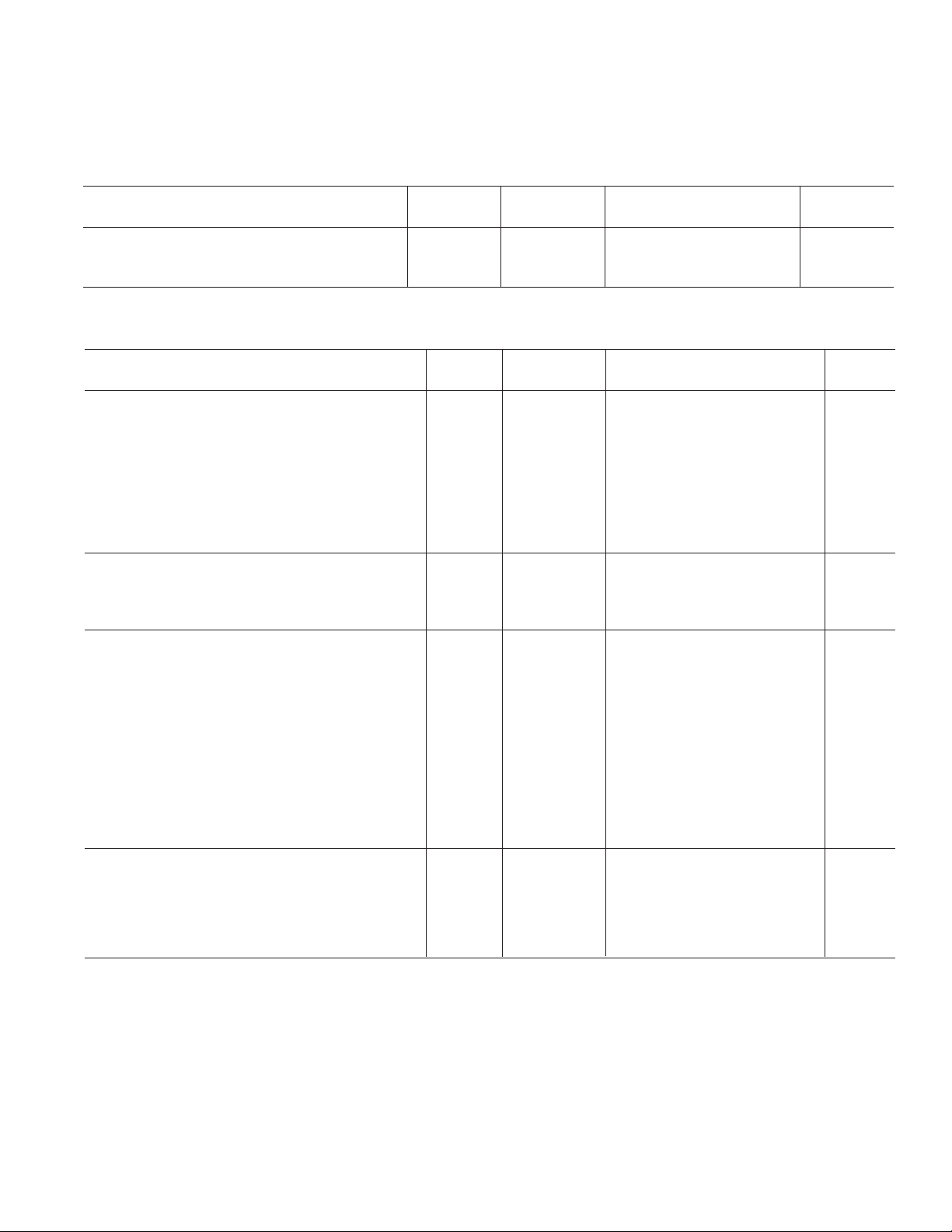

RECOMMENDED OPERATING CONDITIONS

Test AD6635BB

Parameter Temp Level Min Typ Max Unit

VDD IV 2.25 2.5 2.75 V

VDDIO IV 3.0 3.3 3.6 V

T

AMBIENT

ELECTRICAL CHARACTERISTICS

Parameter (Conditions) Temp Level Min Typ Max Unit

LOGIC INPUTS (5 V TOLERANT)

Logic Compatibility Full IV 3.3 V CMOS

Logic 1 Voltage Full IV 2.0 5.0 V

Logic 0 Voltage Full IV –0.3 +0.8 V

Logic 1 Current Full IV 1 10 A

Logic 0 Current Full IV 1 10 A

Logic 1 Current (inputs with pull-down) Full IV

Logic 0 Current (inputs with pull-up) Full IV

Input Capacitance 25∞CV 4 pF

LOGIC OUTPUTS

Logic Compatibility Full IV

Logic 1 Voltage (I

Logic 0 Voltage (IOL = 0.25 mA) Full IV 0.2 0.4 V

IDD SUPPLY CURRENT

CLK = 80 MHz, (VDD = 2.75 V, VDDIO = 3.6 V) Full IV

I

VDD

I

VDDIO

CLK = GSM Example (65 MSPS, VDD = 2.5 V,

VDDIO = 3.3 V, 4 Channels) 25∞CV

I

VDD

I

VDDIO

CLK = WCDMA Example (76.8 MSPS,

VDD = 2.5V, VDDIO = 3.3 V, 2 Channels) 25∞CV

I

VDD

I

VDDIO

= 0.25 mA) Full IV 2.4 VDD – 0.2 V

OH

IV –40 +25 +85 ∞C

Test AD6635BB

880 mA

150 mA

485 mA

60 mA

830 mA

120 mA

POWER DISSIPATION

CLK = 80 MHz Full IV 2.8 W

CLK = 65 MHz GSM/EDGE Example V 1.4 mW

CLK = 76.8 MHz WCDMA Example V 2.5 W

CLK = 78.64 MHz cdma2000 Example V 2.3 W

All Channels in Sleep Mode Full IV 570 W

Specifications subject to change without notice.

REV. 0

–7–

AD6635

SPECIFICATIONS

GENERAL TIMING CHARACTERISTICS

(continued)

1, 2

Test AD6635BB

Parameter (Conditions) Temp Level Min Typ Max Unit

CLKn TIMING REQUIREMENTS

t

CLK

t

CLKL

t

CLKH

CLKn Period Full I 12.5 ns

CLKn Width Low Full IV 5.6 0.5 ⫻ t

CLKn Width High Full IV 5.6 0.5 ⫻ t

CLK

CLK

ns

ns

RESET TIMING REQUIREMENTS

t

RESL

RESET Width Low Full I 30.0 ns

INPUT WIDEBAND DATA TIMING REQUIREMENTS

t

SI

t

HI

Input to ≠CLKn Setup Time Full IV 2.0 ns

Input to ≠CLKn Hold Time Full IV 1.0 ns

LEVEL INDICATOR OUTPUT SWITCHING CHARACTERISTICS

t

DLI

≠CLKn to LIx-y Output Delay Time Full IV 3.3 10.0 ns

SYNC TIMING REQUIREMENTS

t

SS

t

HS

SYNC(A, B, C, D) to ≠CLKn Setup Time Full IV 2.0 ns

SYNC(A, B, C, D) to ≠CLKn Hold Time Full IV 1.0 ns

SERIAL PORT CONTROL TIMING REQUIREMENTS

SWITCHING CHARACTERISTICS

t

SCLK

t

SCLKL

t

SCLKH

SCLKn (n = 0, 4) Period Full IV 16 ns

SCLKn Low Time Full IV 3.0 ns

SCLKn High Time Full IV 3.0 ns

2

INPUT CHARACTERISTICS

t

SSI

t

HSI

PARALLEL PORT TIMING REQUIREMENTS

(MASTER MODE) SWITCHING CHARACTERISTICS

t

DPOCLKL

t

DPOCLKLL

t

DPREQ

t

DPP

SDIn to ØSCLKn Setup Time Full IV 1.0 ns

SDIn to ØSCLKn Hold Time Full IV 1.0 ns

3

ØCLKn to ≠PCLKn Delay (Divide by 1) Full IV 6.5 10.5 ns

ØCLKn to ≠PCLKn Delay (Divide by 2, 4, or 8) Full IV 8.3 14.6 ns

≠CLKn to ≠PxREQ Delay 1.0 ns

≠CLKn to Px[15:0] Delay 0.0 ns

INPUT CHARACTERISTICS

t

SPA

t

HPA

PARALLEL PORT TIMING REQUIREMENTS

(SLAVE MODE) SWITCHING CHARACTERISTICS

t

POCLK

t

POCLKL

t

POCLKH

t

DPREQ

t

DPP

PxACK to ØPCLKn Setup Time 7.0 ns

PxACK to ØPCLKn Hold Time –3.0 ns

3

PCLKn Period Full I 12.5 ns

PCLKn Low Period (when PCLK Divisor = 1) Full IV 2.0 0.5 ⫻ t

PCLKn High Period (when PCLK Divisor = 1) Full IV 2.0 0.5 ⫻ t

≠CLKn to ≠PxREQ Delay 10.0 ns

≠CLKn to Px[15:0] Delay 11.0 ns

POCLK

POCLK

ns

ns

REV. 0–8–

AD6635

GENERAL TIMING CHARACTERISTICS

1, 2

Test AD6635BB

Parameter (Conditions) Temp Level Min Typ Max Unit

INPUT CHARACTERISTICS

t

SPA

t

HPA

LINK PORT TIMING REQUIREMENTS

SWITCHING CHARACTERISTICS

t

RDLCLK

t

FDLCLK

t

RLCLKDAT

t

FLCLKDAT

NOTES

1

All Timing Specifications valid over VDD range of 2.25 V to 2.75 V, and VDDIO range of 3.0 V to 3.6 V.

2

C

= 40 pF on all outputs unless otherwise specified.

LOAD

3

The timing parameters for Px[15:0], PxREQ, PxACK, LxCLKOUT, and Lx[7:0] apply for output ports A, B, C, and D. (x stands for A, B, C, or D.)

Specifications subject to change without notice.

PxACK to ØPCLKn Setup Time 1.0 ns

PxACK to ØPCLKn Hold Time 1.0 ns

3

≠PCLKn to ≠LxCLKOUT Delay Full IV 2.5 ns

ØPCLKn to ØLxCLKOUT Delay Full IV 0 ns

≠LxCLKOUT to Lx[7:0] Delay Full IV 0 2.9 ns

ØLxCLKOUT to Lx[7:0] Delay Full IV 0 2.2 ns

REV. 0

–9–

AD6635

MICROPROCESSOR PORT TIMING CHARACTERISTICS

1, 2

Test AD6635BB

Parameter (Conditions) Temp Level Min Typ Max Unit

MICROPROCESSOR PORT, MODE MNM (MODE = 0)

MODE INM WRITE TIMING

t

SC

t

HC

t

HWR

t

SAM

t

HAM

t

DRDY

t

ACC

Control3 to ≠CLKn Setup Time Full IV 2.0 ns

Control3 to ≠CLKn Hold Time Full IV 2.5 ns

WR(RW) to RDY(DTACK) Hold Time Full IV 7.0 ns

Address/Data to WR(RW) Setup Time Full IV 3.0 ns

Address/Data to RDY(DTACK) Hold Time Full IV 5.0 ns

WR(RW) to RDY(DTACK) Delay Full IV 8.0 ns

WR(RW) to RDY(DTACK) High Delay Full IV 4 ⫻ t

CLK

5 ⫻ t

CLK

9 ⫻ t

CLK

ns

MODE INM READ TIMING

t

SC

t

HC

t

SAM

t

HAM

t

DRDY

t

ACC

Control3 to ≠CLKn Setup Time Full IV 5.0 ns

Control3 to ≠CLKn Hold Time Full IV 2.0 ns

Address to RD(DS) Setup Time Full IV 0.0 ns

Address to Data Hold Time Full IV 5.0 ns

RD(DS) to RDY(DTACK) Delay Full IV 8.0 ns

RD(DS) to RDY(DTACK) High Delay Full IV 8 ⫻ t

CLK

10 ⫻ t

CLK

13 ⫻ t

CLK

ns

MICROPROCESSOR PORT, MODE MNM (MODE = 1)

MODE MNM WRITE TIMING

t

SC

t

HC

t

HDS

t

HRW

t

SAM

t

HAM

t

DDTACK

t

ACC

Control3 to ≠CLKn Setup Time Full IV 2.0 ns

Control3 to ≠CLKn Hold Time Full IV 2.5 ns

DS(RD) to DTACK(RDY) Hold Time Full IV 8.0 ns

RW(WR) to DTACK(RDY) Hold Time Full IV 7.0 ns

Address/Data to RW(WR) Setup Time Full IV 3.0 ns

Address/Data to RW(WR) Hold Time Full IV 5.0 ns

DS(RD) to DTACK(RDY) Delay Full IV 8.0 ns

RW(WR) to DTACK(RDY) Low Delay Full IV 4 ⫻ t

CLK

5 ⫻ t

CLK

9 ⫻ t

CLK

ns

MODE MNM READ TIMING

t

SC

t

HC

t

HDS

t

SAM

t

HAM

t

DDTACK

t

ACC

NOTES

1

All Timing Specifications valid over VDD range of 2.25 V to 2.75 V, and VDDIO range of 3.0 V to 3.6 V.

2

C

3

Specification pertains to control signals: R/W, (WR), DS, (RD), CS0, CS1.

Specifications subject to change without notice.

Control3 to ≠CLKn Setup Time Full IV 5.0 ns

Control3 to ≠CLKn Hold Time Full IV 2.0 ns

DS(RD) to DTACK(RDY) Hold Time Full IV 8.0 ns

Address to DS(RD) Setup Time Full IV 0.0 ns

Address to Data Hold Time Full IV 5.0 ns

DS(RD) to DTACK(RDY) Delay Full IV 8.0 ns

DS(RD) to DTACK(RDY) Low Delay Full IV 8 ⫻ t

= 40 pF on all outputs unless otherwise specified.

LOAD

CLK

10 ⫻ t

CLK

13 ⫻ t

CLK

ns

REV. 0–10–

AD6635

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6 V

Input Voltage . . . . . . . . . . . . . –0.3 V to +5.3 V (5 V Tolerant)

Output Voltage Swing . . . . . . . . . . . –0.3 V to VDDIO + 0.3 V

Load Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200 pF

Junction Temperature Under Bias . . . . . . . . . . . . . . . . . 150∞C

Thermal Characteristics

324-Lead BGA:

= 16.87∞C/W, no airflow.

JA

Thermal measurements made in the horizontal position on a

4-layer board.

Storage Temperature Range . . . . . . . . . . . . . –65∞C to +150∞C

Lead Temperature (5 sec) . . . . . . . . . . . . . . . . . . . . . . . 280∞C

*Stresses greater than those listed above may cause permanent damage to the device

These are stress ratings only; functional operation of the devices at these or any

other conditions greater than those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

EXPLANATION OF TEST LEVELS

I 100% Production Tested.

II 100% Production Tested at 25∞C, and Sample Tested at

Specified Temperatures.

III Sample Tested Only.

IV Parameter Guaranteed by Design and Analysis.

V Parameter is Typical Value Only.

VI 100% Production Tested at 25∞C, and Sample Tested at

Temperature Extremes.

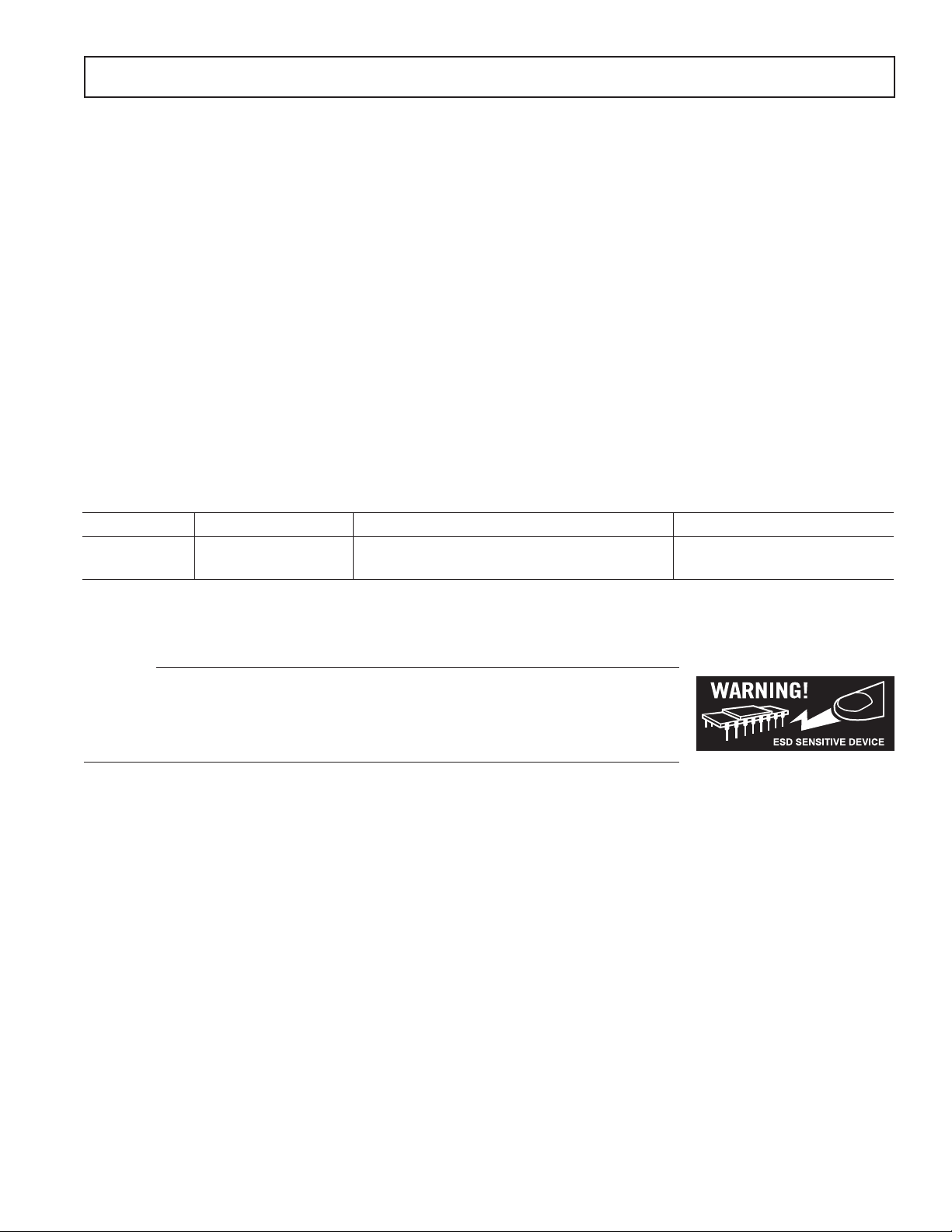

ORDERING GUIDE

Model Temperature Range Package Descriptions Package Option

AD6635BB –40ºC to +85ºC 324-Lead PBGA (Ball Grid Array) B-324

AD6635BB/PCB Evaluation Board with AD6635 and Software

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD6635 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

REV. 0

–11–

AD6635

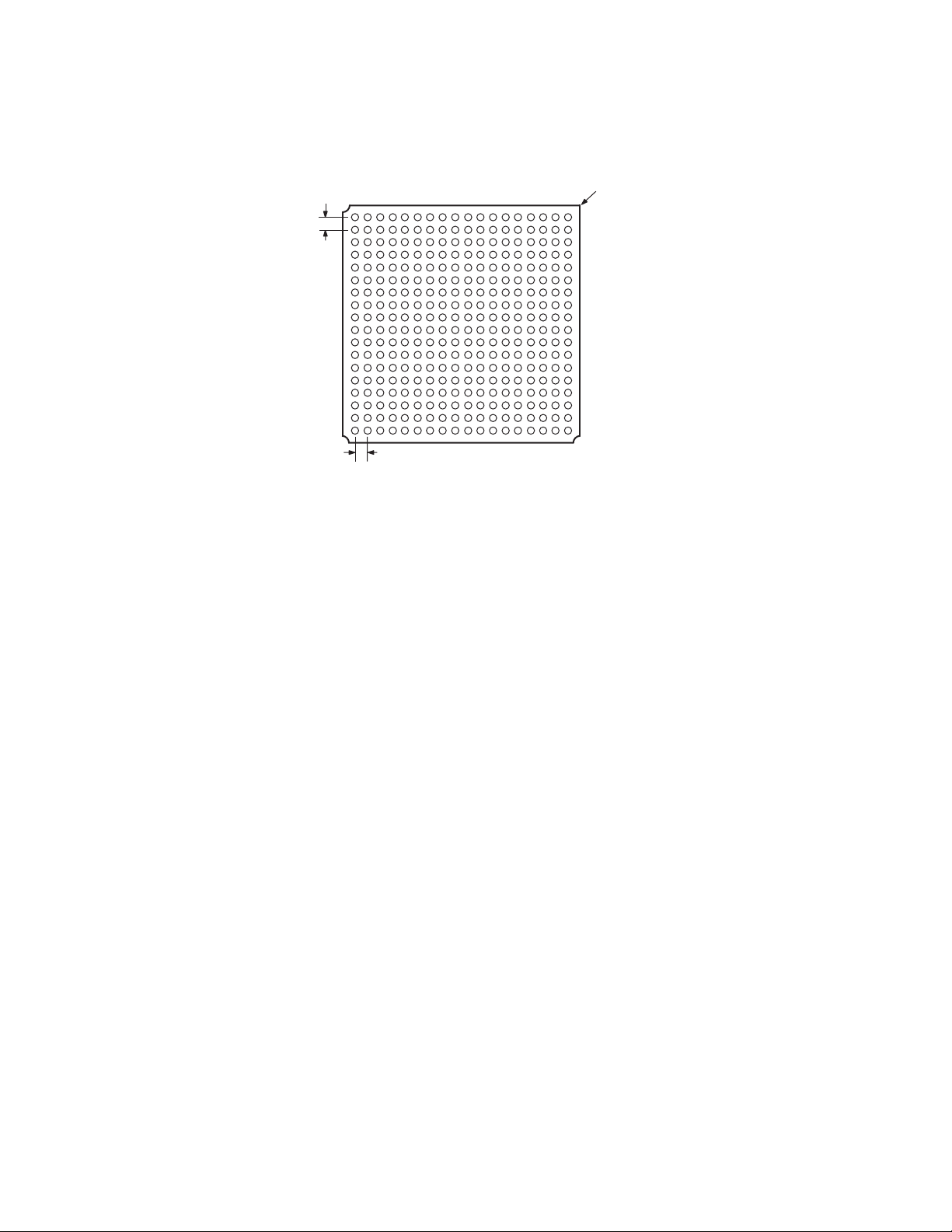

PIN CONFIGURATION

19mm 19mm – 18

2

BALL ZAPHOD PACKAGE

1.00

BSC

BSC

1.00

BOTTOM VIEW

A1 BALL

CORNER

1234567891018 17 16 15 14 13 12 11

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

REV. 0–12–

PIN CONFIGURATION (PIN OUT)

AD6635

123456789

A

B

C

D

CHIP0_ID1

E

F

G

PBCH0_

H

PBCH1_

J

PB2_LB2

K

L

M

N

P

R

T

U

V

CLK0

CLK1

PA AC K

SCLK0

PCLK0

LBCLK

OUT

LBCLK

IN

PB11

PB13

PB12

PBREQ

EXPB0

EXPB1

EXPB2

IENC

VDDIO

(Reserved)

VDDIO

(Reserved)

CHIP0_ID0

CHIP0_ID2

PAIQ

SDI0

PBIQ

PB0_LB0

PB4_LB4

PB1_LB1

PB9

PB14

PB15

INB10

INB9

INB8

INB7

INC1 INC8 INC11

PAREQ

PB6_LB6

PB7_LB7

PB3_LB3

PB5_LB5 GND

PB8

PB10

VDDIO

(Reserved)

PBACK

INB11

INB4

INB5

INB6

INC7

INC2

LID-A

VDD

VDD

GND

GND

GND

VDDIO

VDDIO

PA 1 5

INB12

INB3

INB2

INB1

INC12

IND2

IND1

INC9

LID-B IND0 IND5

INC10

INC3

INC4

INC5

VDD

VDD

VDD

VDD

GND

GND

GND GND

GND

GND

GND

GND

VDDIO VDDIO

VDDIO

VDDIO

PA 1 4

PA 1 3

EXPA0

INB13

EXPA1

INB0

INA13

LIB-B

INA12

IENB

IND3 IND7

IND4 IND6

INC13

EXPC2 EXPC1

INC6

VDDIO

VDDIO

VDDIO

VDDIO

GND

GND

GND

GND GND

VDD

VDD

PA 1 0

EXPA2

INA9 INA8

INA10

INA11

IEND

GND

GND

GND

VDD

VDD

PA 1 2

PA 9

INA7

INA6

INC0

123456789

10

IND8

IND11

IND9 IND12

IND10

IND13

EXPC0

VDDIO GND

VDDIO GND

PA 0_LA0 PA2_LA2

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

VDDIO VDDIO

VDD

VDD VDDIO

PA 3_LA3

PA 1 1

LIC-B

PA 8

INA5

INA3

INA4

INA2

10

11

EXPD1

EXPD2

EXPD0

VDD

VDD

GND

GND

GND

GND

GND

GND

VDDIO

LIC-A

PA 5_LA5

PA 1_LA1

INA1

INA0

11

12

PDREQ

PD14

PDACK

PD12

PD15

PD9

VDD

PD13

VDD

VDDIO VDDIO

GND

GND

VDDIO VDDIO

GND

GND

GND

GND

GND

GND

GND

GND

VDDIO VDD

VDDIO

VDD

DNC

DNC

CS0

DNC

DTACK

SYNCD

SYNCA

LIA-A

IENA

LIB-A

12

13

13

14

PD10

PD11

PD1_LD1

PCACK

VDDIO

(Reserved)

GND GND

GND

GND GND

GND GND

VDD VDD

VDD

DNC

D4

RESET

SYNCC

LIA-B

14

15

PD8

PD4_LD4

PD2_LD2

CHIP1_ID1

DNC

VDDIO

VDDIO

GND

VDD

D7

D3

PA 7_LA7

PA 6_LA6

SYNCB

15

16

PD5_LD5

PD3_LD3

PD0_LD0

PCIQ

CHIP1_ID0

PCREQ

PC11

PC10

PC8

PC1_LC1

A1

PC6_LC6

A0

D0

CS1

DNC

PA 4_LA4

PACH0_

LACLK

OUT

16

17

PDCH1_

LDCLK

IN

PD7_LD7

SDI4

PD6_LD6

CHIP1_ID2

PC14

PC13

PC9

PC0_LC0

PC3_LC3

PC5_LC5

PC7_L

C7

A2

D1

R/W

D5

MODE

PACH1_

LACLK

IN

17

18

PDCH0_

LDCLK

OUT

PDIQ

PCLK1

SCLK4

PC15

PC12

DNC

GND

(Reserved)

PC2_LC2

PC4_LC4

PCCH1_

LCCLK

IN

PCCH0_

LCCLK

OUT

DS

VDDIO

(Reserved)

D2

D6

18

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

REV. 0

–13–

AD6635

PIN FUNCTION DESCRIPTION

Name Type Function

POWER SUPPLY

VDD P 2.5 V Core Supply (also called DVCORE)

VDDIO P 3.3 V IO Supply (also called DVRING)

GND G Ground

INPUTS

INA[13:0]

EXPA[2:0]

IENA

INB[13:0]

EXPB[2:0]

IENB

INC[13:0]

EXPC[2:0]

IENC

IND[13:0]

EXPD[2:0]

IEND

RESET IActive Low Reset Pin

CLK0 I Input Clock 0 (Master Clock for Channels 0–3 and Ports A, B)

CLK1 I Input Clock 1 (Master Clock for Channels 4–7 and Ports C, D)

PCLK0 I/O Link/Parallel Port Clock for Output Ports A and B

PCLK1 I/O Link/Parallel Port Clock for Output Ports C and D

LACLKIN I Link Port A Data Ready

LBCLKIN I Link Port B Data Ready

LCCLKIN I Link Port C Data Ready

LDCLKIN I Link Port D Data Ready

SYNCA

SYNCB

SYNCC

SYNCD

CHIP0_ID[2:0]

CHIP1_ID[2:0]

1

1

2

1

1

2

1

1

2

1

1

2

1

1

1

1

1

1

IA Input Data (Mantissa)

IA Input Data (Exponent)

I Input Enable—Input A

IB Input Data (Mantissa)

IB Input Data (Exponent)

I Input Enable—Input B

IC Input Data (Mantissa)

IC Input Data (Exponent)

I Input Enable—Input C

ID Input Data (Mantissa)

ID Input Data (Exponent)

I Input Enable—Input D

IAll Sync Pins Go to All Eight Channels

IAll Sync Pins Go to All Eight Channels

IAll Sync Pins Go to All Eight Channels

IAll Sync Pins Go to All Eight Channels

IChip ID Selector for Channels 0–3 and Ports A, B

IChip ID Selector for Channels 4–7 and Ports C, D

CONTROL

PAACK I Parallel Port A Acknowledge

PAREQ O Parallel Port A Request

PBACK I Parallel Port B Acknowledge

PBREQ O Parallel Port B Request

PCACK I Parallel Port C Acknowledge

PCREQ O Parallel Port C Request

PDACK I Parallel Port D Acknowledge

PDREQ O Parallel Port D Request

REV. 0–14–

PIN FUNCTION DESCRIPTION (continued)

Name Type Function

MICROPORT CONTROL

D[7:0] I/O/T Bidirectional Microport Data

A[2:0] I Microport Address Bus

DS (RD)IActive Low Data Strobe (Active Low Read)

DTACK (RDY)

2

O/T Active Low Data Acknowledge (Microport Status Bit)

R/W (WR)IRead Write (Active Low Write)

MODE I Intel or Motorola Mode Select

1

CS0

CS1

1

IChip Select for Channels 0–3 and Ports A, B

IChip Select for Channels 4–7 and Ports C, D

AD6635

SERIAL PORT CONTROL

1

SDI0

SCLK0

1

SDI4

SCLK4

I Serial Port Control Data Input for Channels 0–3 and Ports A, B

1

I Serial Port Control Clock for Channels 0–3 and Ports A, B

I Serial Port Control Data Input for Channels 4–7 and Ports C, D

1

I Serial Port Control Clock for Channels 4–7 and Ports C, D

OUTPUTS

LIA-A O Level Indicator—Input A, Interleaved-Data A

LIA-B O Level Indicator—Input A, Interleaved-Data B

LIB-A O Level Indicator—Input B, Interleaved-Data A

LIB-B O Level Indicator—Input B, Interleaved-Data B

LIC-A O Level Indicator—Input C, Interleaved-Data A

LIC-B O Level Indicator—Input C, Interleaved-Data B

LID-A O Level Indicator—Input D, Interleaved-Data A

LID-B O Level Indicator—Input D, Interleaved-Data B

LACLKOUT O Link Port A Clock Output

LBCLKOUT O Link Port B Clock Output

LCCLKOUT O Link Port C Clock Output

LDCLKOUT O Link Port D Clock Output

LA[7:0] O Link Port A Output Data

LB[7:0] O Link Port B Output Data

LC[7:0] O Link Port C Output Data

LD[7:0] O Link Port D Output Data

PA[15:0] O Parallel Output Data Port A

PB[15:0] O Parallel Output Data Port B

PC[15:0] O Parallel Output Data Port C

PD[15:0] O Parallel Output Data Port D

PACH[1:0] O Parallel Output Port A Channel Indicator

PBCH[1:0] O Parallel Output Port B Channel Indicator

PCCH[1:0] O Parallel Output Port C Channel Indicator

PDCH[1:0] O Parallel Output Port D Channel Indicator

PAIQ O Parallel Port A I/Q Data Indicator

PBIQ O Parallel Port B I/Q Data Indicator

PCIQ O Parallel Port C I/Q Data Indicator

PDIQ O Parallel Port D I/Q Data Indicator

NOTES

1

Pins with a pull-down resistor of nominal 70 kW.

2

Pins with a pull-up resistor of nominal 70 kW.

REV. 0

–15–

AD6635

TIMING DIAGRAMS

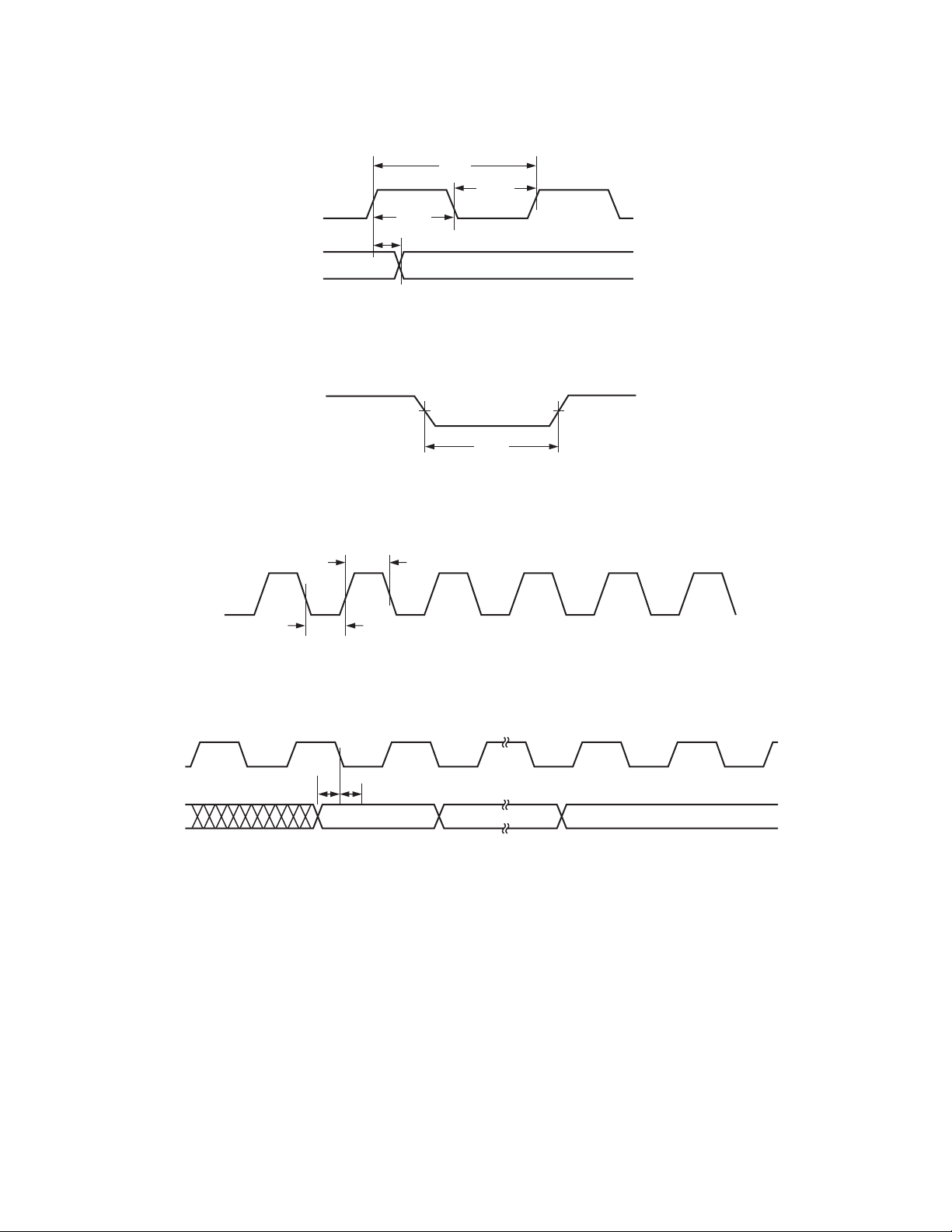

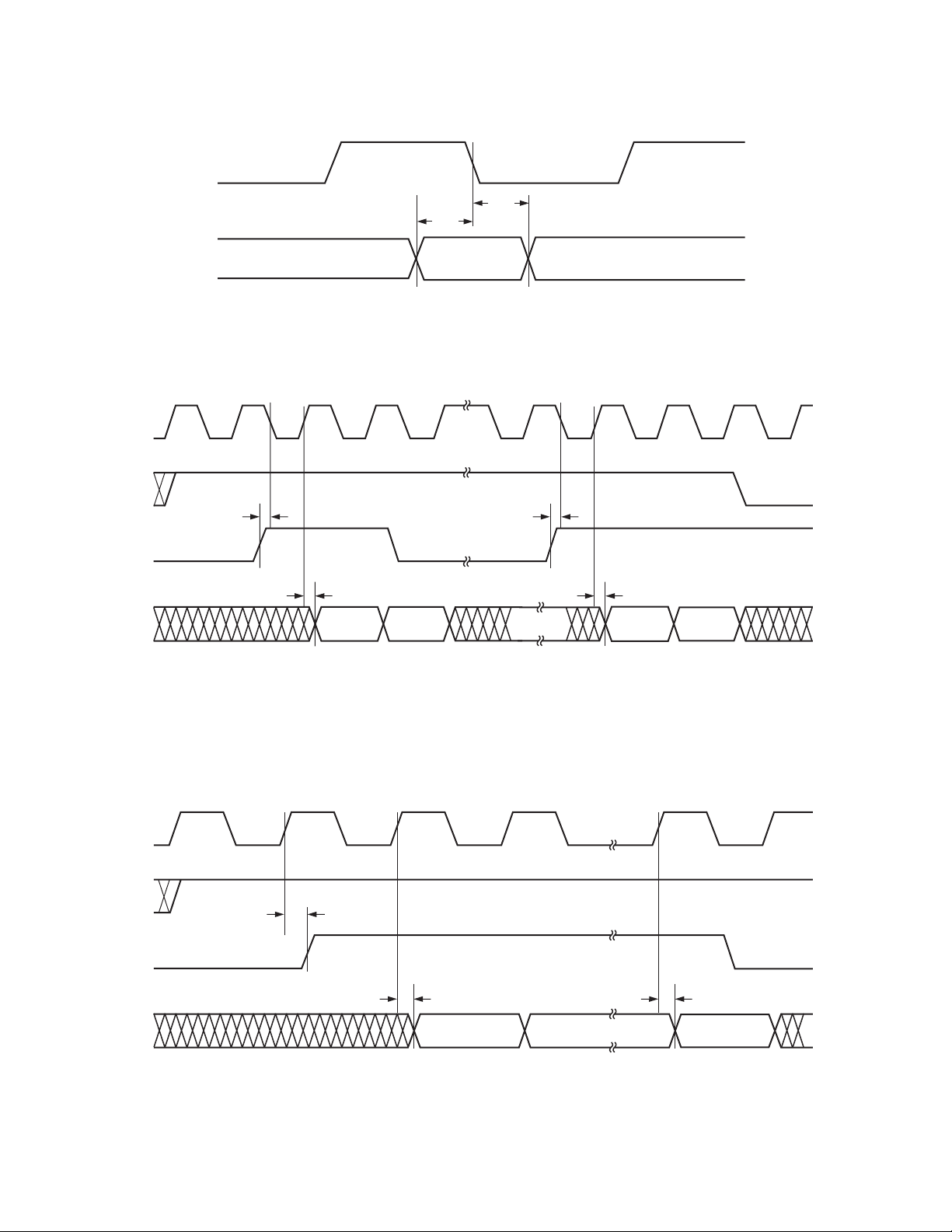

Figure 3. Level Indicator Output Switching Characteristics (x = A, B, C, D; and y = A, B)

(For x = A and B, n = 0; and for x = C or D, n = 1)

CLKn

LIx–y

RESET

t

CLK

t

CLKL

t

CLKH

t

DLI

t

RESL

Figure 4. Reset Timing Requirements

SCLKn

SDIn

SCLKn

t

SCLKH

t

SCLKL

Figure 5. SCLK Switching Characteristics (n = 0, 4)

t

SSI

t

HSI

DATA

Figure 6. Serial Port Input Timing Characteristics (n = 0, 4)

REV. 0–16–

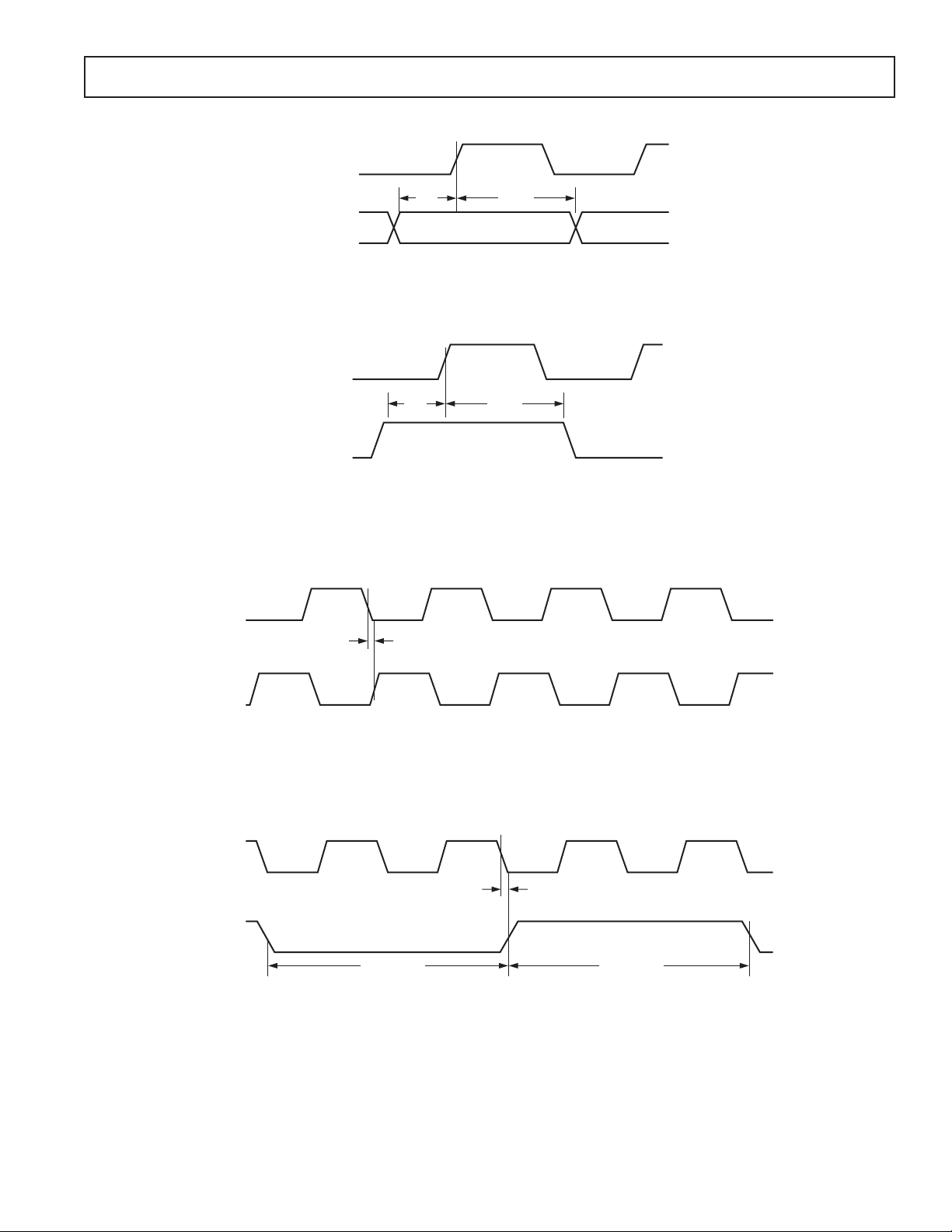

CLKn

AD6635

CLKn

PCLKn

t

HI

INx[13:0]

EXPx[2:0]

IENx

t

SI

Figure 7. Input Timing for A and B Channels

CLKn

t

HS

SYNCA

SYNCB

SYNCC

SYNCD

t

SS

Figure 8. SYNC Timing Inputs

t

DPOCLKL

Figure 9. PCLKn to CLKn Switching Characteristics Divide by 1

CLKn

t

DPOCLKLL

PCLKn

t

POCLKLH

t

POCLKL

Figure 10. PCLKn to CLKn Switching Characteristics Divide by 2, 4, or 8

REV. 0

–17–

AD6635

PCLKn

PxREQ

PCLKn

PxACK

t

t

SPA

HPA

Figure 11. Master Mode PxACK to PCLKn Setup and Hold Characteristics

(n = 0 and x = A, B; or n = 1 and x = C, D)

t

SPA

t

SPA

PxACK

Px[15:0]

PCLKn

PxACK

PxREQ

t

DPP

DATA 1 DATA 2 DATA N–1 DATA N

t

DPP

Figure 12. Master Mode PxACK to PCLKn Switching Characteristics

(n = 0 and x = A, B; or n = 1 and x = C, D)

t

DPREQ

Px[15:0]

t

DPP

DATA 1 DATA N

Figure 13. Master Mode PxREQ to PCLKn Switching Characteristics

(n = 0 and x = A, B; or n = 1 and x = C, D)

t

DPP

REV. 0–18–

Loading...

Loading...