Monolithic Synchronous

FEATURES

Full-scale frequency (up to 2 MHz) set by external system

clock

Extremely low linearity error (0.005% max at 1 MHz FS,

0.02% max at 2 MHz FS)

No critical external components required

Accurate 5 V reference voltage

Low drift (25 ppm/°C max)

Dual- or single-supply operation

Voltage or current input

MIL-STD-883 compliant versions available

PRODUCT DESCRIPTION

The AD652 synchronous voltage-to-frequency converter

(SVFC) is a powerful building block for precision analog-todigital conversion, offering typical nonlinearity of 0.002%

(0.005% maximum) at a 100 kHz output frequency. The inherent monotonicity of the transfer function and wide range of

clock frequencies allow the conversion time and resolution to

be optimized for specific applications.

The AD652 uses a variation of the charge-balancing technique

to perform the conversion function. The AD652 uses an

external clock to define the full-scale output frequency, rather

than relying on the stability of an external capacitor. The result

is a more stable, more linear transfer function, with significant

application benefits in both single- and multichannel systems.

Gain drift is minimized using a precision low drift reference

and low TC, on-chip, thin-film scaling resistors. Furthermore,

initial gain error is reduced to less than 0.5% by the use of laserwafer-trimming.

The analog and digital sections of the AD652 have been

designed to allow operation from a single-ended power source,

simplifying its use with isolated power supplies.

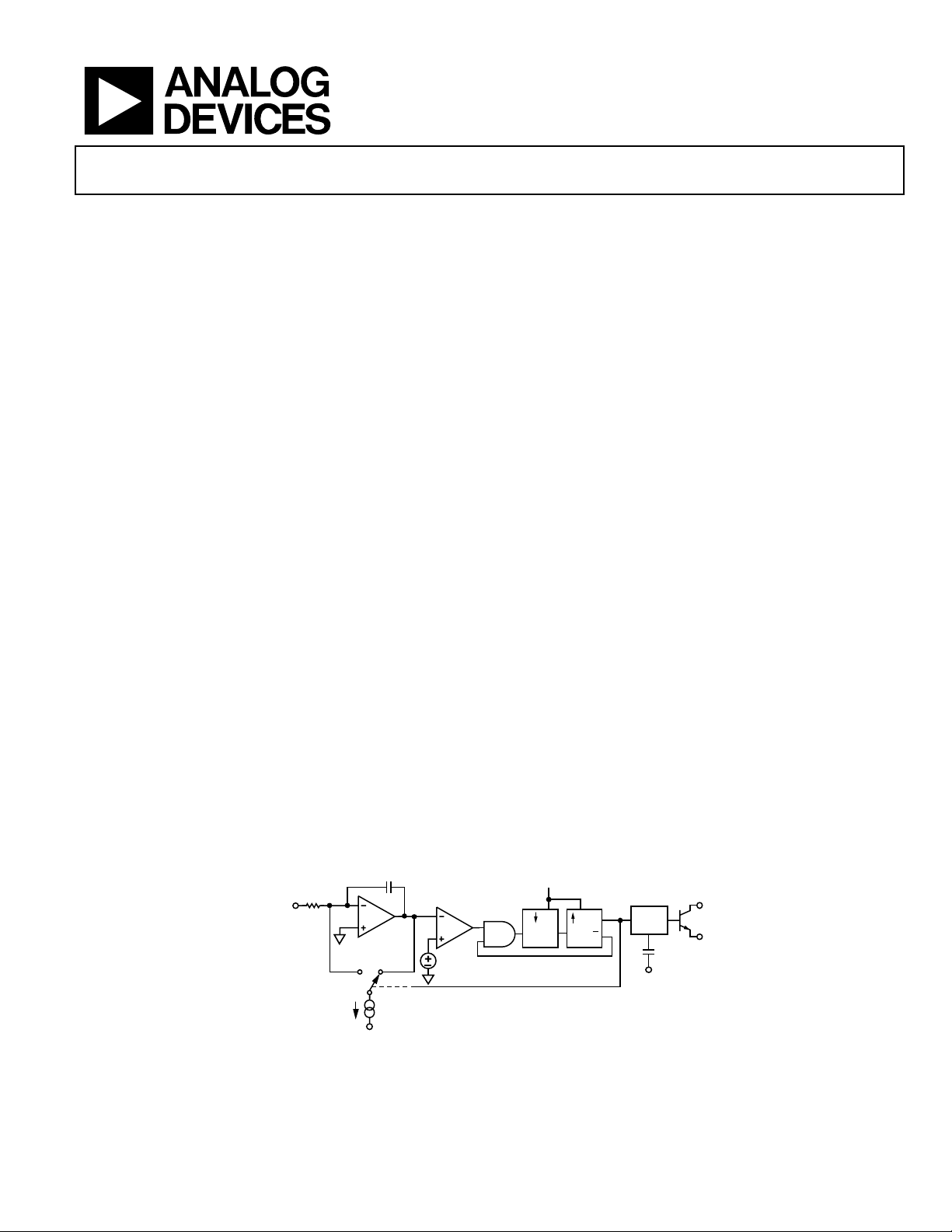

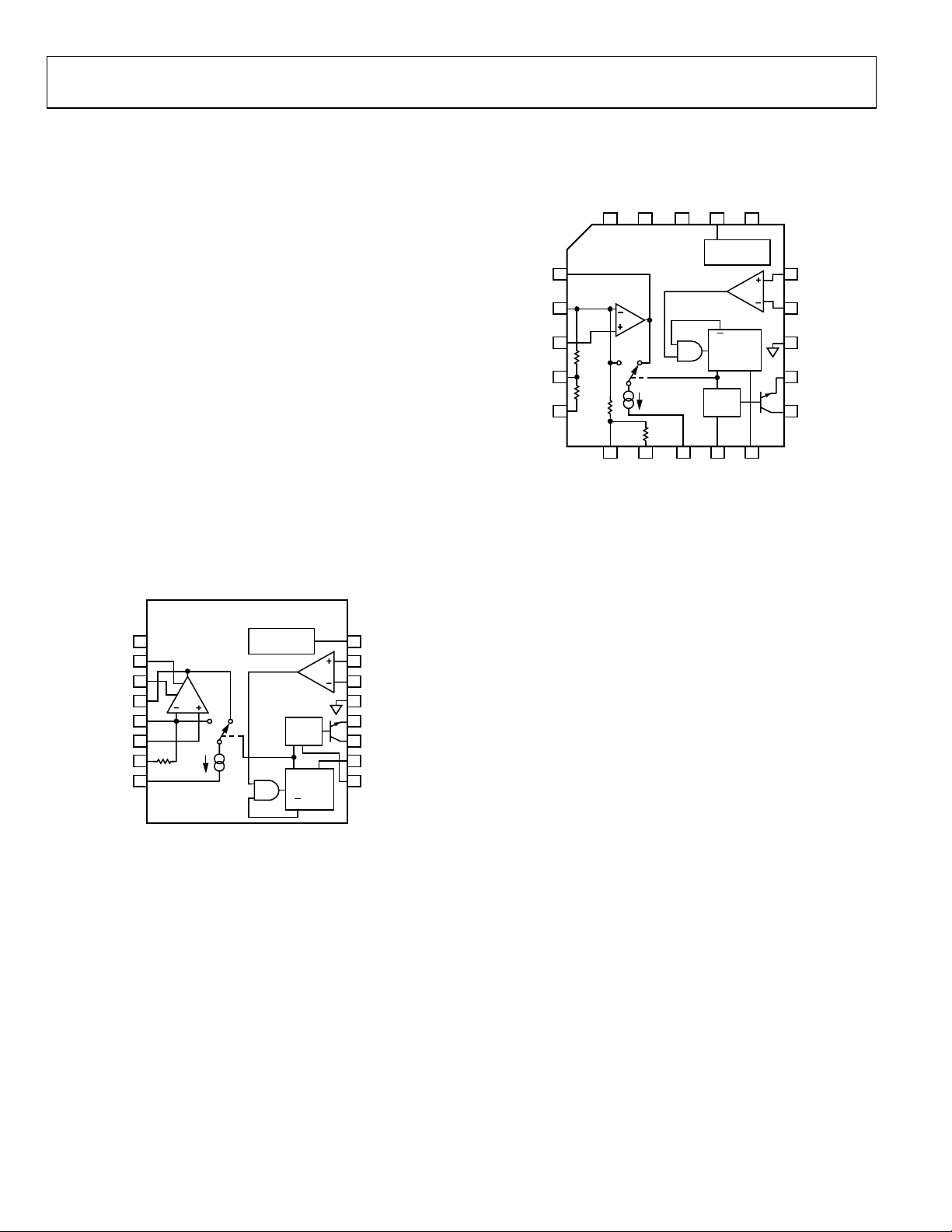

FUNCTIONAL BLOCK DIAGRAM

R

IN

V

IN

INTEGRATOR

HL

C

INT

COMPARATOR

5V

Voltage-to-Frequency Converter

AD652

The AD652 is available in five performance grades. The 20-lead

PLCC-packaged JP and KP grades are specified for operation

over the 0°C to +70°C commercial temperature range. The

16-lead CERDIP-packaged AQ and BQ grades are specified for

operation over the −40°C to +85°C industrial temperature

range. The AD652SQ is available for operation over the full

−55°C to +125°C extended temperature range.

PRODUCT HIGHLIGHTS

1. The use of an external clock to set the full-scale frequency

allows the AD652 to achieve linearity and stability far

superior to other monolithic VFCs. By using the same clock

to drive the AD652 and set the counting period (through a

suitable divider), conversion accuracy is maintained

independent of variations in clock frequency.

2. The AD652 synchronous VFC requires only one external

component (a noncritical integrator capacitor) for

operation.

3. The AD652 includes a buffered, accurate 5 V reference.

4. The AD652’s clock input is TTL and CMOS compatible and

can also be driven by sources referred to the negative power

supply. The flexible open-collector output stage provides

sufficient current sinking capability for TTL and CMOS

logic, as well as for optical couplers and pulse transformers.

A capacitor-programmable one-shot is provided for selection of optimum output pulse width for power reduction.

5. The AD652 can also be configured for use as a synchronous

F/V converter for isolated analog signal transmission.

6. The AD652 is available in versions compliant with

MILSTD-883. Refer to the Analog Devices Military

Products Databook or current AD652/883B data sheet for

detailed specifications.

CLOCK IN

D FLOP LATCH

CKQDG

AND

Q

D

Q

ONE

SHOT

C

OS

1mA

–V

S

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

Figure 1.

00798-001

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

AD652

TABLE OF CONTENTS

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Definitions of Specifications....................................................... 5

Theory of Operation ........................................................................ 6

Overrange...................................................................................... 8

SVFC Connection for Dual Supply, Positive Input Voltages .. 9

SVFC Connections for Negative Input Voltages ...................... 9

SVFC Connection for Bipolar Input Voltages ........................ 10

PLCC Connections..................................................................... 11

Gain and Offset Calibration...................................................... 11

Gain Performance ......................................................................12

Reference Noise .......................................................................... 12

Digital Interfacing Considerations........................................... 12

Component Selection ................................................................ 12

Digital Ground............................................................................ 13

Single-Supply Operation........................................................... 14

Frequency-to-Voltage Converter ............................................. 15

Decoupling and Grounding...................................................... 16

Frequency Output Multiplier.................................................... 17

Single-Line Multiplexed Data Transmission .......................... 18

Isolated Front End...................................................................... 22

A-to-D Conversion .................................................................... 22

Delta Modulator......................................................................... 23

Bridge Transducer Interface...................................................... 24

Outline Dimensions....................................................................... 25

Ordering Guide............................................................................... 26

REVISION HISTORY

5/04—Data Sheet Changed from Rev. B to Rev. C

Updated Format..............................................................Universal

Changes to Gain and Offset Calibration section.................... 11

Updated Outline Dimensions................................................... 25

Changes to Ordering Guide...................................................... 26

2/00—Data Sheet Changed from Rev. A to Rev. B

Rev. C | Page 2 of 28

AD652

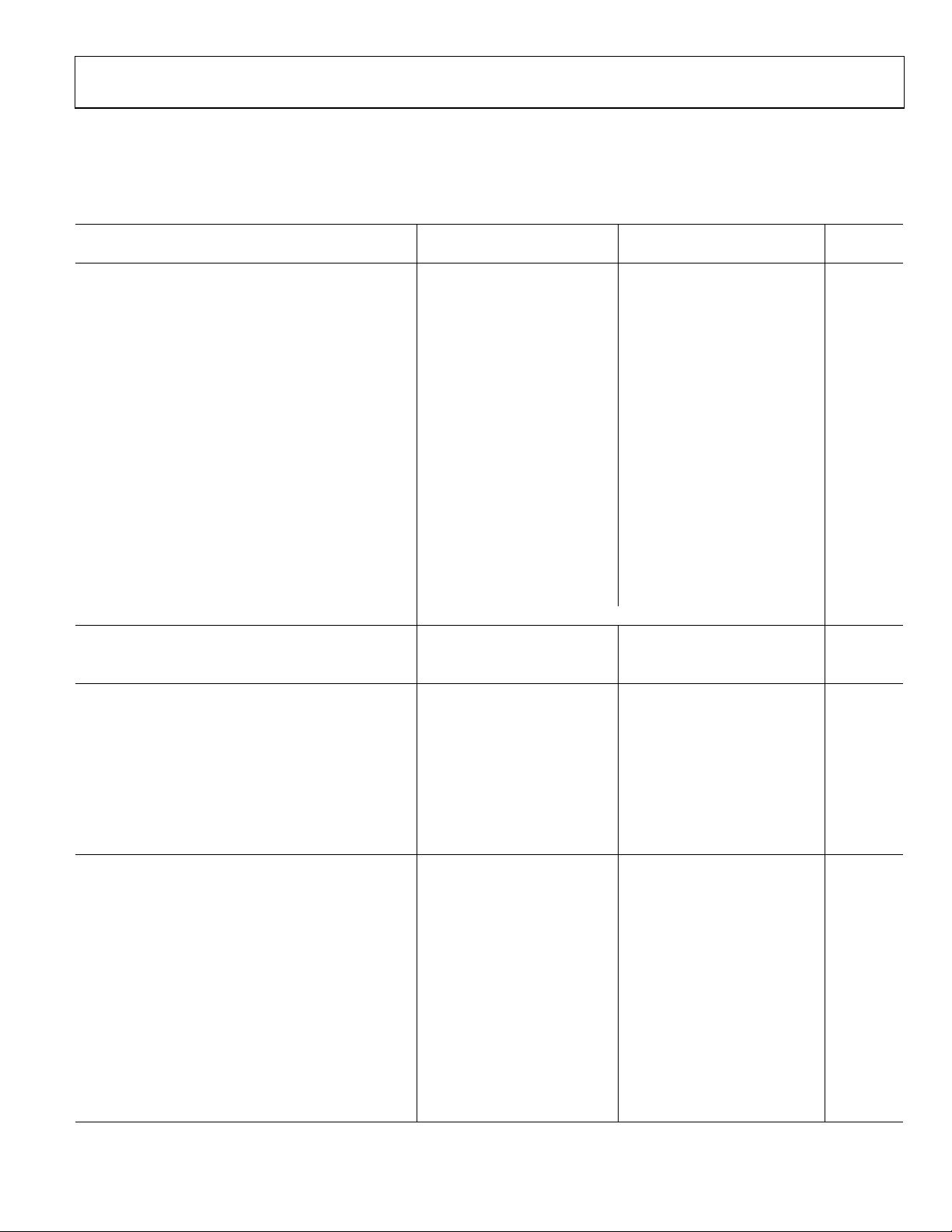

SPECIFICATIONS

Typical @ TA = 25°C, VS = ±15 V, unless otherwise noted. Specifications in boldface are 100% tested at final test and are used to measure

outgoing quality levels.

Table 1.

AD652JP/AQ/SQ AD652KP/BQ

Parameter Min Typ Max Min Typ Max Unit

VOLTAGE-TO-FREQUENCY MODE

Gain Error

f

= 200 kHz ±0.5 ±1 ±0.25 ±0.5 %

CLOCK

f

= 1 MHz ±0.5

CLOCK

f

= 4 MHz ±0.5

CLOCK

±1

±1.5

Gain Temperature Coefficient

f

= 200 kHz ±25 ±50 ±15 ±25 ppm/°C

CLOCK

f

= 1 MHz ±25

CLOCK

±10

f

= 4 MHz ±25

CLOCK

Power Supply Rejection Ratio 0.001

±50

±50

±75

0.01

Linearity Error

f

= 200 kHz ±0.002 ±0.02 ±0.002 ±0.005 %

CLOCK

f

= 1 MHz ±0.002

CLOCK

f

= 2 MHz ±0.01 ±0.02 ±0.002 ±0.005 %

CLOCK

f

= 4 MHz ±0.02

CLOCK

Offset (Transfer Function, RTI) ± 1

Offset Temperature Coefficient ±10

±0.02

±0.05

±3

±50

Response Time One Period of New Output Frequency Plus One Clock Period.

FREQUENCY-TO-VOLTAGE MODE

Gain Error, fIN = 100 kHz FS ±0.5 ±1 ±0.25 ±0.5 %

Linearity Error, fIN = 100 kHz FS ±0.002 ±0.02 ±0.002 ±0.01 %

INPUT RESISTORS

CERDIP (Figure 2)(0 to 10 V FS Range) 19.8 20 20.2 19.8 20 20.2 kΩ

PLCC (Figure 3)

Pin 8 to Pin 7 9.9 10 10.1 9.9 10 10.1 kΩ

Pin 7 to Pin 5 (0 V to 5 V FS Range) 9.9 10 10.1 9.9 10 10.1 kΩ

Pin 8 to Pin 5 (0 V to 10 V FS Range) 19.8 20 20.2 19.8 20 20.2 kΩ

Pin 9 to Pin 5 (0 V to 8 V FS Range) 15.8 16 16.2 15.8 16 16.2 kΩ

Pin 10 to Pin 5 (Auxiliary Input) 19.8 20 20.2 19.8 20 20.2 kΩ

Temperature Coefficient (All) ±50

±100

INTEGRATOR OP AMP

Input Bias Current

Inverting Input (Pin 5) ±5

Noninverting Input (Pin 6) 20

Input Offset Current 20

±20

50

70

Input Offset Current Drift 1 3 1 2 nA/°C

Input Offset Voltage ±1

±3

Input Offset Voltage Drift ±10 ±25 ±10 ±15 µV/°C

Open-Loop Gain 86 86 dB

Common-Mode Input Range –VS + 5 +VS – 5 –VS + 5 +VS – 5 V

CMRR 80 80 dB

Bandwidth 14 95 14 95 MHz

Output Voltage Range

−1

− 4) −1

(+V

S

(Referred to Pin 6, R1 > = 5 kΩ)

±0.25

±0.25

±15

±10

±15

0.001

±0.002

±0.01

±1

±10

±50

±5

20

20

±1

±0.5

±0.75

±25

±30

±50

0.01

±0.005

±0.02

±2

±25

±100

±20

50

70

±2

(+VS − 4)

%

%

ppm/°C

ppm/°C

ppm/°C

%/V

%

%

mV

µV/°C

ppm/°C

nA

nA

nA

mV

V

1

Rev. C | Page 3 of 28

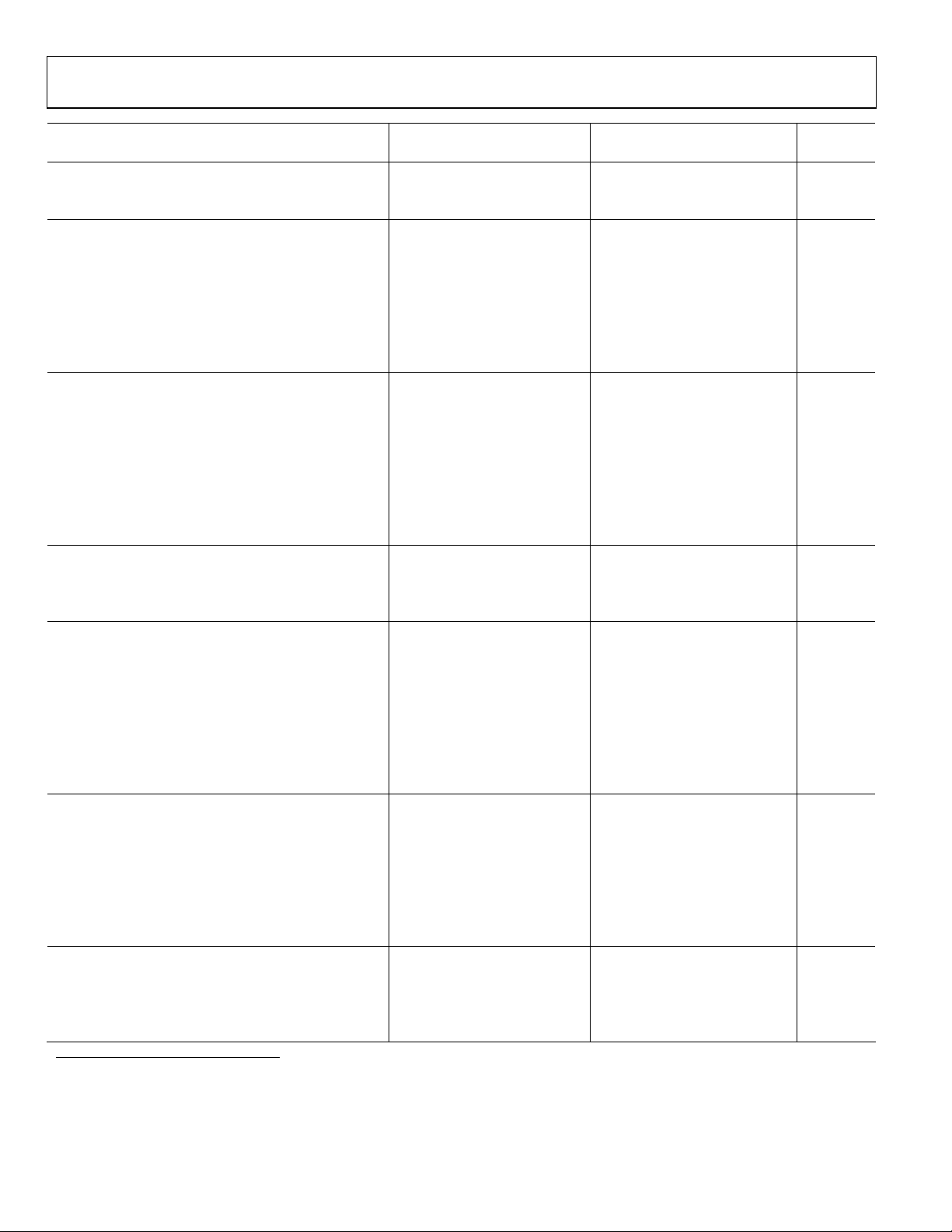

AD652

AD652JP/AQ/SQ AD652KP/BQ

Parameter Min Typ Max Min Typ Max Unit

COMPARATOR

Input Bias Current 0.5 5 0.5 5 µA

Common-Mode Voltage −VS + 4 + VS − 4 −VS + 4 +VS − 4 V

CLOCK INPUT

Maximum Frequency

4

Threshold Voltage (Referred to Pin 12) 1.2 1.2 V

T

to T

MIN

MAX

0.8

Input Current

(−VS < V

< +VS) 5

CLK

Voltage Range −VS +V

Rise Time 2 2 µs

OUTPUT STAGE

VOL (I

= 10 mA)

OUT

I

OL

VOL < 0.8 V

VOL < 0.4 V, T

MIN

to T

MAX

IOH (Off Leakage) 0.01

Delay Time, Positive Clock Edge to Output Pulse

Fall Time (Load = 500 pF and I

= 5 mA) 100 100 ns

SINK

150

Output Capacitance 5 5 pF

OUTPUT ONE-SHOT

Pulse Width, t

COS = 300 pF

OS

1

COS = 1000 pF 4 5 6 4 5 6 µs

REFERENCE OUTPUT

Voltage

4.950

Drift

Output Current

Source T

MIN

to T

MAX

10

Sink 100 500 100 500 µA

Power Supply Rejection

Supply Range = ±12.5 V to ±17.5 V 0.015 0.015 %/V

Output Impedance (Sourcing Current) 0.3

POWER SUPPLY

Rated Voltage ±15 ±15 V

Operating Range

Dual Supply ±6 ±15 ±18 ±6 ±15 ±18 V

Single Supply (−VS = 0) +12 +36 +12 +36 V

Quiescent Current ±11

Digital Common −VS +VS − 4 –V

Analog Common −V

S

TEMPERATURE RANGE

Specified Performance

JP, KP Grade 0 +70 0 +70 °C

AQ, BQ Grade −40 +85 −40 +85 °C

SQ Grade −55 +125 °C

1

Referred to internal V

. In PLCC package, tested on 10 V input range only.

REF

5

2.0 0.8

20

S

0.4

15

8

10

200

1.5

5.0

250 150

2

5.050 4.975

100

2

±15

+V

S

4

5

−V

S

0.01

1 1.5

10

0.3

±11

S

−V

S

5 MHz

2.0

20

+V

0.4

15

8

10

200

250

2

5.0

5.025

50

mA

2

±15

+VS − 4 V

+V

V

µA

S

V

V

mA

mA

µA

ns

µs

V

ppm/°C

Ω

mA

S

V

Rev. C | Page 4 of 28

AD652

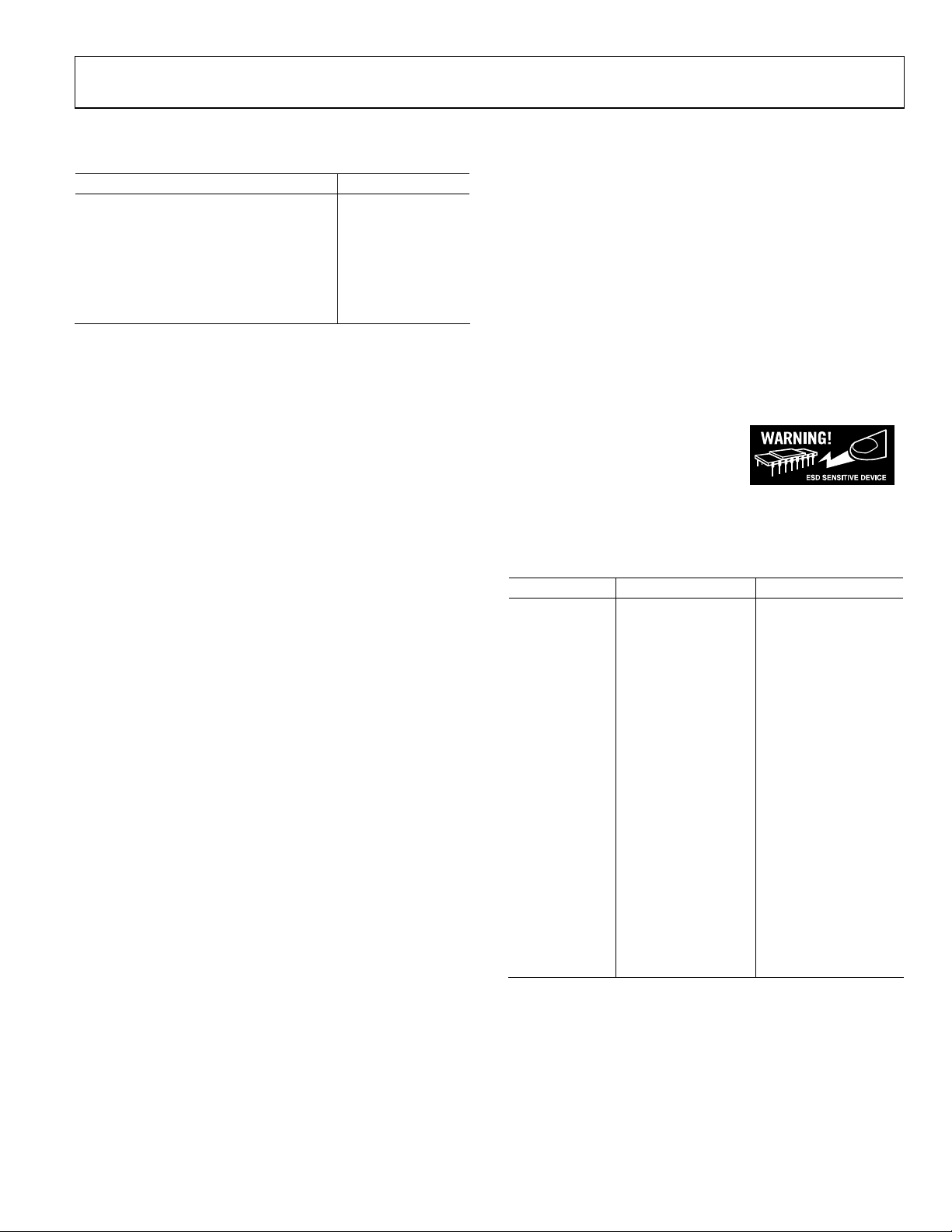

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Ratings

Total Supply Voltage +VS to −V

Maximum Input Voltage (Figure 6) 36 V

Maximum Output Current

(Open Collector Output)

Amplifier Short-Circuit to Ground Indefinite

Storage Temperature Range: CERDIP −65°C to +150°C

Storage Temperature Range: PLCC −65°C to +150°C

S

36 V

50 mA

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

DEFINITIONS OF SPECIFICATIONS

Gain Error

The gain of a voltage-to-frequency converter is the scale factor

setting that provides the nominal conversion relationship, e.g.,

1 MHz full scale. The gain error is the difference in slope

between the actual and ideal transfer functions for the V-F

converter.

Linearity Error

The linearity error of a V-F is the deviation of the actual

transfer function from a straight line passing through the

endpoints of the transfer function.

Gain Temperature Coefficient

The gain temperature coefficient is the rate of change in fullscale frequency as a function of the temperature from +25°C to

or T

T

MIN

MAX

.

Table 3. Pin Configurations

Pin No. Q-16 Package P-20A Package

1 +V

2 TRIM +V

3 TRIM NC

4 OP AMP OUT OP AMP OUT

5 OP AMP “−“ OP AMP “−“

6 OP AMP “+” OP AMP “+”

7 10 VOLT INPUT 5 VOLT INPUT

8 −V

9 C

10 CLOCK INPUT OPTIONAL 10 V INPUT

11 FREQ OUT −V

12 DIGITAL GND C

13 ANALOG GND CLOCK INPUT

14 COMP “−“ FREQ OUT

15 COMP “+” DIGITAL GND

16 COMP REF ANALOG GND

17 COMP “−“

18 COMP “+”

19 NC

20 COMP REF

S

S

OS

NC

S

10 VOLT INPUT

8 VOLT INPUT

S

OS

Rev. C | Page 5 of 28

AD652

T

THEORY OF OPERATION

A synchronous VFC is similar to other voltage-to-frequency

converters in that an integrator is used to perform a chargebalance of the input signal with an internal reference current.

However, rather than using a one-shot as the primary timing

element, which requires a high quality and low drift capacitor, a

synchronous voltage-to-frequency converter (SVFC) uses an

external clock. This allows the designer to determine the system

stability and drift based upon the external clock selected. A

crystal oscillator may also be used if desired.

The SVFC architecture provides other system advantages

besides low drift. If the output frequency is measured by

counting pulses gated to a signal that is derived from the clock,

the clock stability is unimportant and the device simply

performs as a voltage-controlled frequency divider, producing a

high resolution A/D. If a large number of inputs must be

monitored simultaneously in a system, the controlled timing

relationship between the frequency output pulses and the usersupplied clock greatly simplifies this signal acquisition. Also, if

the clock signal is provided by a VFC, the output frequency of

the SVFC is proportional to the product of the two input

voltages. Therefore, multiplication and A-to-D conversion on

two signals are performed simultaneously.

AD652

SYNCHRONOUS

+V

TRIM

TRIM

OP AMP OUT

OP AMP "–"

OP AMP "+"

10 VOLT INPUT

–V

VOLTAGE-TO-

FREQUENCY

1

S

CONVERTER

2

3

4

5

6

20kΩ

7

1mA

8

S

Figure 2. CERDIP Pin Configuration

5V

REFERENCE

ONE

SHOT

QCK

D

AND

Q

"D"

FLOP

COMP REF

16

COMP "+"

15

14

COMP "–"

13

ANALOG GND

DIGITAL GND

12

FREQ OUT

11

10

CLOCK INPUT

9

C

OS

00798-002

S

OP AMP OU

OP AMP "–"

OP AMP "+"

5V INPUT

10V INPUT

NC3+V

AD652

SYNCHRONOUS

VOLTAGE-TO-FREQUENCY

4

5

6

7

8

CONVERTER

10kΩ

10kΩ

16kΩ

9

8V INPUT

2

1mA

4kΩ

10

10V INPUT

OPTIONAL

NC1COMP REF20NC

5V

REFERENCE

"D"

Q

FLOP

D

AND

Q

CK

ONE

SHOT

11

12

S

OS

–V

C

19

18

17

16

15

14

13

NC = NO CONNECT

INPUT

CLOCK

COMP "+"

COMP "–"

ANALOG GND

DIGITAL GND

FREQ OUT

Figure 3. PLCC Pin Configuration

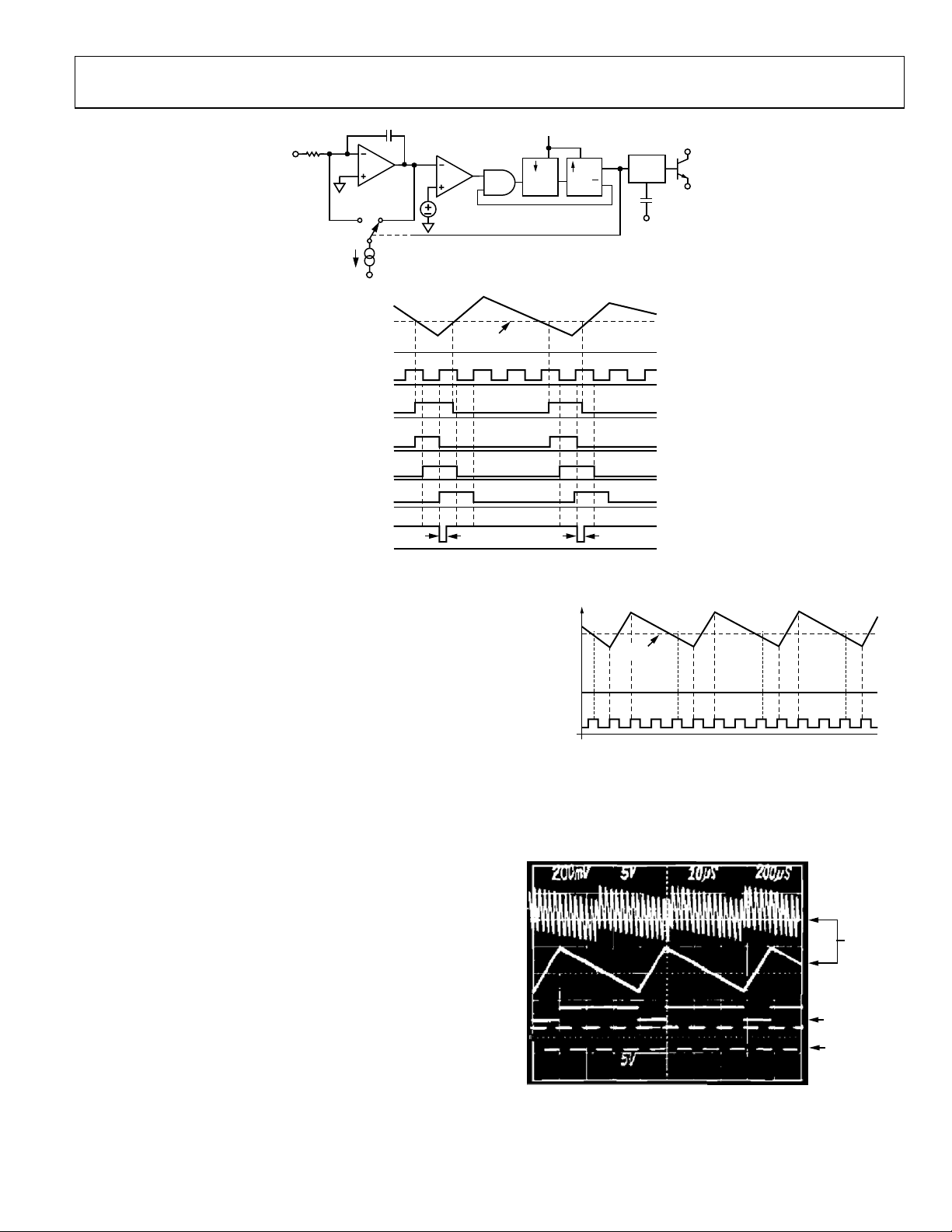

Figure 4 shows the typical up-and-down ramp integrator output

of a charge-balance VFC. After the integrator output has

crossed the comparator threshold and the output of the AND

gate has gone high, nothing happens until a negative edge of the

clock comes along to transfer the information to the output of

the D FLOP. At this point, the clock level is low, so the latch does

not change state. When the clock returns high, the latch output

goes high and drives the switch to reset the integrator; at the

same time, the latch drives the AND gate to a low output state.

On the very next negative edge of the clock, the low output state

of the AND gate is transferred to the output of the D FLOP.

When the clock returns high, the latch output goes low and

drives the switch back into the Integrate mode. At the same

time, the latch drives the AND gate to a mode where it

truthfully relays the information presented to it by the

comparator.

00798-003

The pinouts of the AD652 SVFC are shown in Figure 2 and

Figure 3. A block diagram of the device configured as an SVFC,

along with various system waveforms, is shown in Figure 4.

Rev. C | Page 6 of 28

Because the reset pulses applied to the integrator are exactly one

clock period long, the only place where drift can occur is in a

variation of the symmetry of the switching speed with

temperature.

Since each reset pulse is identical, the AD652 SVFC produces a

very linear voltage-to-frequency transfer relation. Also, because

all reset pulses are gated by the clock, there are no problems

with dielectric absorption causing the duration of a reset pulse

to be influenced by the length of time since the last reset.

AD652

R

CLOCK IN

D FLOP LATCH

CKQDG

AND

ONE

Q

D

SHOT

Q

t

OS

C

OS

00798-004

V

IN

R

IN

1mA

INTEGRATOR

COMPARATOR

C

INT

INTEGRATOR

HL

–V

S

OUTPUT

CLOCK

OUT

AND

OUT

D FLOP

OUT

LATCH

OUT

FREQ

OUT

COMPARATOR

5V

THRESHOLD

t

OS

Figure 4. Block Diagram and System Waveforms

Figure 4 shows that the period between output pulses is

constrained to be an exact multiple of the clock period.

Consider an input current of exactly one quarter the value of

the reference current. In order to achieve a charge balance, the

output frequency equals the clock frequency divided by four:

one clock period for reset and three clock periods of integrate.

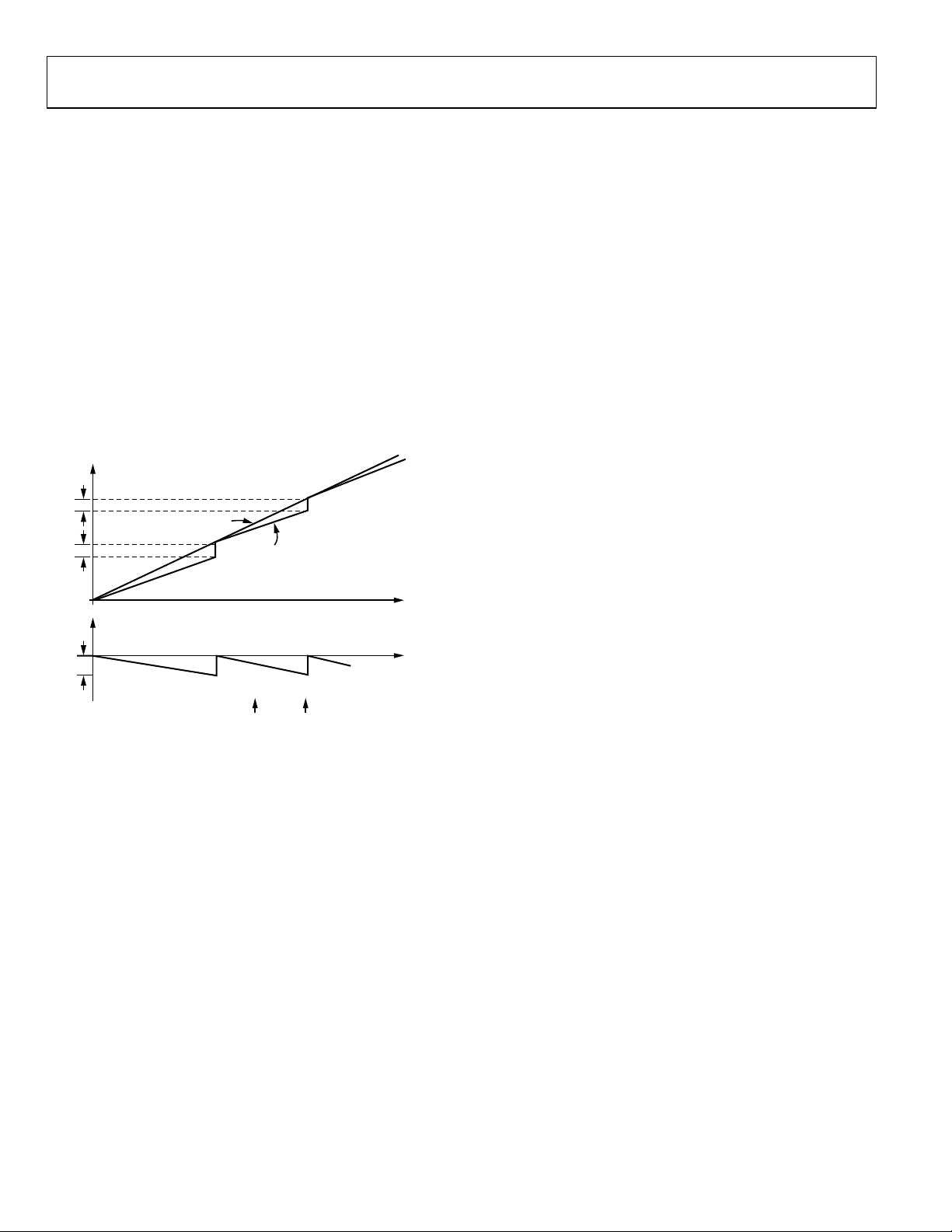

This is shown in Figure 5. If the input current is increased by a

very small amount, the output frequency should also increase

by a very small amount. Initially, however, no output change is

observed for a very small increase in the input current. The

output frequency continues to run at one quarter of the clock,

delivering an average of 250 µA to the summing junction. Since

the input current is slightly larger than this, charge accumulates

in the integrator and the sawtooth signal starts to drift downward. As the integrator sawtooth drifts down, the comparator

threshold is crossed earlier and earlier in each successive cycle,

until finally, a whole cycle is lost. When the cycle is lost, the

integrate phase lasts for two periods of the clock instead of the

usual three periods. Thus, among a long string of divide-byfours, an occasional divide-by-three occurs; the average of the

output frequency is very close to one quarter of the clock, but

the instantaneous frequency can be very different.

INTEGRATO

OUT

THRESHOLD

CLOCK

Figure 5. Integrator Output for I

= 250 µA

IN

Because of this, it is very difficult to observe the waveform on

an oscilloscope. During all of this time, the signal at the output

of the integrator is a sawtooth wave with an envelope that is also

a sawtooth. See Figure 6.

200µs/BOX

C

INT

100µs/BOX

FREQ OUT

10µs/BOX

CLOCK IN

10µs/BOX

00798-006

Figure 6. Integrator Output for I

Slightly Greater than 250 µs

IN

00798-005

Rev. C | Page 7 of 28

AD652

Another way to view this is that the output is a frequency of

approximately one-quarter of the clock that has been phase

modulated. A constant frequency can be thought of as

accumulating phase linearly with time at a rate equal to 2πf

radians per second. Therefore, the average output frequency,

which is slightly in excess of a quarter of the clock, requires

phase accumulation at a certain rate. However, since the SVFC

is running at exactly one-quarter of the clock, it does not

accumulate enough phase (see Figure 7). When the difference

between the required phase (average frequency) and the actual

phase equals 2π, a step-in phase is taken where the deficit is

made up instantaneously. The output frequency is then a steady

carrier that has been phase modulated by a sawtooth signal (see

Figure 7). The period of the sawtooth phase modulation is the

time required to accumulate a 2π difference in phase between

the required average frequency and one quarter of the clock

frequency. The sawtooth phase modulation amplitude is 2π.

PHASE

2

π

2

π

EXPECTED

PHASE

ACTUAL PHASE

The result of this synchronism is that the rate at which data may

be extracted from the series bit stream produced by the SVFC is

limited. The output pulses are typically counted during a fixed

gate interval and the result is interpreted as an average

frequency. The resolution of such a measurement is determined

by the clock frequency and the gate time. For example, if the

clock frequency is 4 MHz and the gate time is 4.096 ms, a

maximum count of 8,192 is produced by a full-scale frequency

of 2 MHz. Thus, the resolution is 13 bits.

OVERRANGE

Since each reset pulse is only one clock period in length, the

full-scale output frequency is equal to one-half the clock

frequency. At full scale, the current steering switch spends half

of the time on the summing junction; thus, an input current of

0.5 mA can be balanced. In the case of an overrange, the output

of the integrator op amp drifts in the negative direction and the

output of the comparator remains high. The logic circuits

simply settle into a divide-by-two of the clock state.

TIME

φ

MOD (t)

2

π

V

(t) = COS (2

OUT

CARRIER FREQUENCY

Figure 7. Phase Modulation

π×f

AVE

AVERAGE

×

t +φMOD (t))

TIME

PHASE

MODULATION

00798-007

Rev. C | Page 8 of 28

AD652

V

C

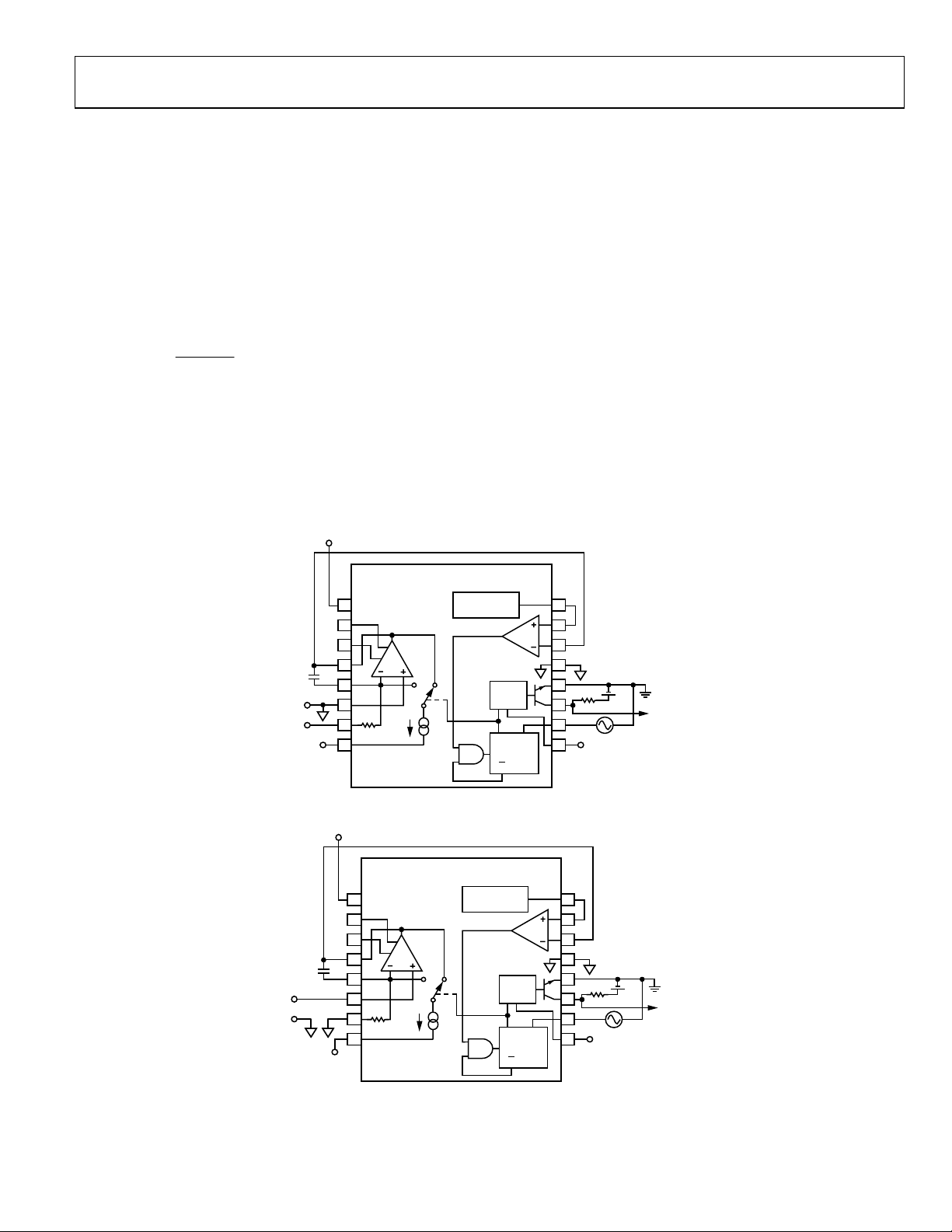

SVFC CONNECTION FOR DUAL SUPPLY, POSITIVE INPUT VOLTAGES

Figure 8 shows the AD652 connection scheme for the

traditional dual supply, positive input mode of operation. The

range is from ±6 V to ±18 V. When +VS is lower than 9.0 V,

±V

S

As shown in Figure 8, three additional connections are required

The first connection is to short Pin 13 to Pin 8 (Analog Ground

) and add a pull-up resistor to +VS (as shown in

to −V

S

Figure 21). The pull-up resistor is determined by the following

equation:

V

V52 −

S

R

PULLUP

=

These connections ensure proper operation of the 5 V reference.

Tie Pin 16 to Pin 6 (as shown in Figure 21) to ensure that the

integrator output ramps down far enough to trip the

comparator.

The CERDIP-packaged AD652 accepts either a 0 V to 10 V or

0 mA to 0.5 mA full-scale input signal. The temperature drift of

µA500

+

S

the AD652 is specified for a 0 V to 10 V input range using the

internal 20 kΩ resistor. If a current input is used, the gain drift is

degraded by a maximum of 100 ppm/°C (the TC of the 20 kΩ

resistor). If an external resistor is connected to Pin 5 to establish

a different input voltage range, drift is induced to the extent that

the external resistor’s TC differs from the TC of the internal

resistor. The external resistor used to establish a different input

voltage range should be selected to provide a full-scale current

of 0.5 mA (i.e., 10 kΩ for 0 V to 5 V).

SVFC CONNECTIONS FOR NEGATIVE INPUT VOLTAGES

Voltages that are negative with respect to ground may be used

as the input to the AD652 SVFC. In this case, Pin 7 is grounded

and the input voltage is applied to Pin 6 (see Figure 9). In this

mode, the input voltage can go as low as 4 V above −V

configuration, the input is a high impedance, and only the

20 nA (typical) input bias current of the op amp must be

supplied by the input signal. This is contrasted with the more

usual positive input voltage configuration, which has a 20 kΩ

input impedance and requires 0.5 mA from the signal source.

. In this

S

AD652

SYNCHRONOUS

VOLTAGE-TO-

FREQUENCY

1

CONVERTER

2

3

INT

–

V

+

4

5

6

IN

–V

20kΩ

7

1mA

8

S

5V

REFERENCE

ONE

SHOT

QCK

D

AND

Q

"D"

FLOP

16

15

14

13

ANALOG

GND

12

R

L

11

10

9

5V

CLOCK

+V

S

Figure 8. Standard V/F Connection for Positive Input Voltage with Dual Supply

+V

S

AD652

SYNCHRONOUS

VOLTAGE-TO-

FREQUENCY

1

CONVERTER

2

3

C

INT

–

V

IN

+

4

5

6

20kΩ

7

1mA

8

–V

S

5V

REFERENCE

ONE

SHOT

QCK

D

AND

Q

"D"

FLOP

16

15

14

13

ANALOG

GND

12

R

L

11

10

9

5V

CLOCK

+V

S

Figure 9. Negative Voltage Input

DIGITAL

GND

FREQ

OUT

DIGITAL

GND

FREQ

OUT

00798-008

00798-009

Rev. C | Page 9 of 28

Loading...

Loading...