Internally Trimmed

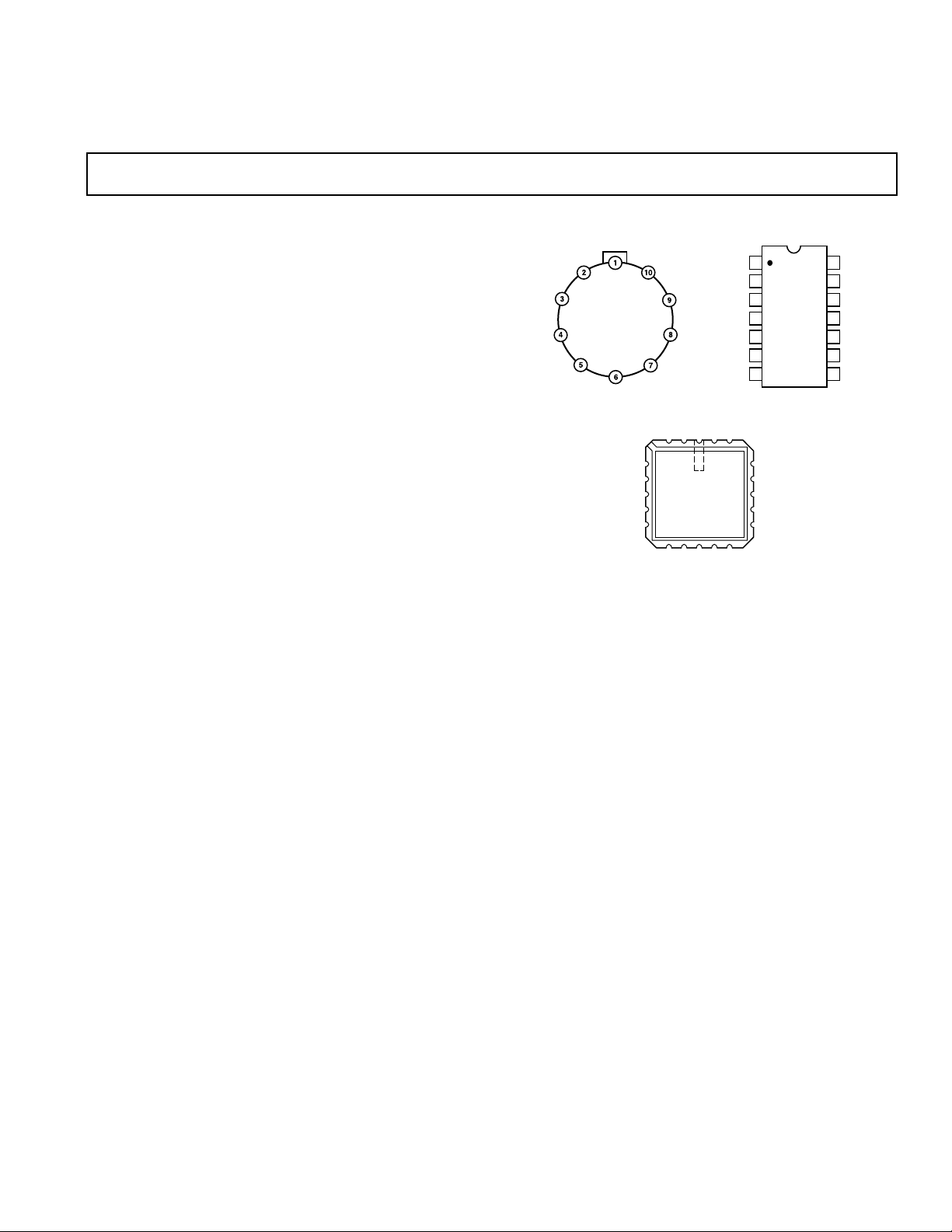

TOP VIEW

(Not to Scale)

14

13

12

11

10

9

8

1

2

3

4

5

6

7

NC = NO CONNECT

Z+V

S

AD532

OUT Y

1

–V

S

Y

2

NC V

OS

NC GND

NC X

2

X

1

NC

TOP VIEW

(Not to Scale)

20 191

2

3

18

14

15

16

17

4

5

6

7

8

910111213

NC = NO CONNECT

–V

S

Y

2

OUTNC

AD532

NC

NC

NC

V

OS

NC

NC

NC

GND

ZX1NCNC

+V

S

NC

Y

1

X

2

Y

1

Y

2

V

OS

GND

X

2

X

1

–V

S

OUT

Z

+V

S

TOP VIEW

(Not to Scale)

AD532

a

Integrated Circuit Multiplier

AD532

FEATURES

Pretrimmed to ⴞ1.0% (AD532K)

No External Components Required

Guaranteed ⴞ1.0% max 4-Quadrant Error (AD532K)

Diff Inputs for (X

– X2) (Y1 – Y2)/10 V Transfer Function

1

Monolithic Construction, Low Cost

APPLICATIONS

Multiplication, Division, Squaring, Square Rooting

Algebraic Computation

Power Measurements

Instrumentation Applications

Available in Chip Form

PRODUCT DESCRIPTION

The AD532 is the first pretrimmed single chip monolithic multiplier/divider. It guarantees a maximum multiplying error of

±1.0% and a ±10 V output voltage without the need for any

external trimming resistors or output op amp. Because the

AD532 is internally trimmed, its simplicity of use provides

design engineers with an attractive alternative to modular multipliers, and its monolithic construction provides significant advantages in size, reliability and economy. Further, the AD532

can be used as a direct replacement for other IC multipliers that

require external trim networks (such as the AD530).

FLEXIBILITY OF OPERATION

The AD532 multiplies in four quadrants with a transfer function of (X

a 10 V Z/(X

– X2)(Y1 – Y2)/10 V, divides in two quadrants with

1

– X2) transfer function, and square roots in one

1

quadrant with a transfer function of ±√10 V Z. In addition to

these basic functions, the differential X and Y inputs provide

significant operating flexibility both for algebraic computation and

transducer instrumentation applications. Transfer functions,

such as XY/10 V, (X

are easily attained and are extremely useful in many modulation

and function generation applications, as well as in trigonometric

calculations for airborne navigation and guidance applications,

where the monolithic construction and small size of the AD532

offer considerable system advantages. In addition, the high

CMRR (75 dB) of the differential inputs makes the AD532

especially well qualified for instrumentation applications, as it

can provide an output signal that is the product of two transducergenerated input signals.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

2

2

– Y

)/10 V, ±X

2

/10 V and 10 V Z/(X1 – X2),

GUARANTEED PERFORMANCE OVER TEMPERATURE

The AD532J and AD532K are specified for maximum multi-

plying errors of ±2% and ±1% of full scale, respectively at

+25°C, and are rated for operation from 0°C to +70°C. The

AD532S has a maximum multiplying error of ±1% of full scale

at +25°C; it is also 100% tested to guarantee a maximum error

of ±4% at the extended operating temperature limits of –55°C

and +125°C. All devices are available in either the hermetically-

sealed TO-100 metal can, TO-116 ceramic DIP or LCC packages.

J, K and S grade chips are also available.

ADVANTAGES OF ON-THE-CHIP TRIMMING OF THE

MONOLITHIC AD532

1. True ratiometric trim for improved power supply rejection.

2. Reduced power requirements since no networks across supplies are required.

3. More reliable since standard monolithic assembly techniques

can be used rather than more complex hybrid approaches.

4. High impedance X and Y inputs with negligible circuit

loading.

5. Differential X and Y inputs for noise rejection and additional

computational flexibility.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

PIN CONFIGURATIONS

AD532–SPECIFICATIONS

(@ +25ⴗC, V

= ⴞ15 V, R ≥ 2 k⍀ V

S

grounded)

OS

Model Min Typ Max Min Typ Max Min Typ Max Units

AD532J AD532K AD532S

MULTIPLIER PERFORMANCE

Transfer Function

Total Error (–10 V ≤ X, Y ≤ +10 V) ±1.5 ⴞ2.0 ±0.7 ⴞ1.0 ±0.5 ⴞ1.0 %

T

= Min to Max ±2.5 ±1.5 ⴞ4.0 %

A

Total Error vs. Temperature ±0.04 ±0.03 ±0.01 ⴞ0.04 %/°C

(X1– X2)( Y1– Y2)

10V

(X1– X2)( Y1– Y2)

10V

(X1– X2)( Y1– Y2)

10V

Supply Rejection (±15 V ± 10%) ±0.05 ±0.05 ±0.05 %/%

Nonlinearity, X (X = 20 V pk-pk, Y = 10 V) ±0.8 ±0.5 ±0.5 %

Nonlinearity, Y (Y = 20 V pk-pk, X = 10 V) ±0.3 ±0.2 ±0.2 %

Feedthrough, X (Y Nulled,

X = 20 V pk-pk 50 Hz) 50 200 30 100 30 100 mV

Feedthrough, Y (X Nulled,

Y = 20 V pk-pk 50 Hz) 30 150 25 80 25 80 mV

Feedthrough vs. Temperature 2.0 1.0 1.0 mV p-p/°C

Feedthrough vs. Power Supply ±0.25 ±0.25 ±0.25 mV/%

DYNAMICS

Small Signal BW (V

1% Amplitude Error 75 75 75 kHz

Slew Rate (V

Settling Time (to 2%, ∆V

OUT

= 0.1 rms) 1 1 1 MHz

OUT

20 pk-pk) 45 45 45 V/µs

= 20 V) 1 1 1 µs

OUT

NOISE

Wideband Noise f = 5 Hz to 10 kHz 0.6 0.6 0.6 mV (rms)

Wideband Noise f = 5 Hz to 5 MHz 3.0 3.0 3.0 mV (rms)

OUTPUT

Output Voltage Swing ±10 ±13 ±10 ±13 ±10 ±13 V

Output Impedance (f ≤ 1 kHz) 1 1 1 Ω

Output Offset Voltage ±40 ⴞ30 ⴞ30 mV

Output Offset Voltage vs. Temperature 0.7 0.7 2.0 mV/°C

Output Offset Voltage vs. Supply ±2.5 ±2.5 ±2.5 mV/%

INPUT AMPLIFIERS (X, Y and Z)

Signal Voltage Range (Diff. or CM

Operating Diff) ±10 ±10 ±10 V

CMRR 40 50 50 dB

Input Bias Current

X, Y Inputs 3 1.5 4 1.5 4 µA

X, Y Inputs T

Z Input ±10 ±5 ⴞ15 ±5 ⴞ15 µA

Z Input T

Offset Current ±0.3 ±0.1 ±0.1 µA

MIN

MIN

to T

to T

MAX

MAX

10 8 8 µA

±30 ±25 ±25 µA

Differential Resistance 10 10 10 MΩ

DIVIDER PERFORMANCE

Transfer Function (Xl > X2) 10 V Z/(X1–X2) 10 V Z/(X1–X2) 10 V Z/(X1–X2)

Total Error

(V

= –10 V, –10 V ≤ VZ ≤ +10 V) ±2 ±1 ±1%

X

(V

= –1 V, –10 V ≤ VZ ≤ +10 V) ±4 ±3 ±3%

X

SQUARE PERFORMANCE

Transfer Function

Total Error ±0.8 ±0.4 ±0.4 %

(X1– X2)

10V

2

(X1– X2)

10V

2

(X1– X2)

2

10V

SQUARE ROOTER PERFORMANCE

Transfer Function –√10 V Z –√10 V Z –√10 V Z

Total Error (0 V ≤ VZ ≤ 10 V) ±1.5 ±1.0 ±1.0 %

POWER SUPPLY SPECIFICATIONS

Supply Voltage

Rated Performance ±15 ±15 ±15 V

Operating ±10 ⴞ18 ±10 ⴞ18 ±10 ±22 V

Supply Current

Quiescent 46 46 46 mA

PACKAGE OPTIONS

TO-116 (D-14) AD532JD AD532KD AD532SD

TO-100 (H-10A) AD532JH AD532KH AD532SH

LCC (E-20A) AD532SE/883B

Specifications subject to change without notice.

Specifications shown in boldface are tested on all production units at final

electrical test. Results from those tests are used to calculate outgoing quality

levels. All min and max specifications are guaranteed, although only those shown

in boldface are tested on all production units.

–2–

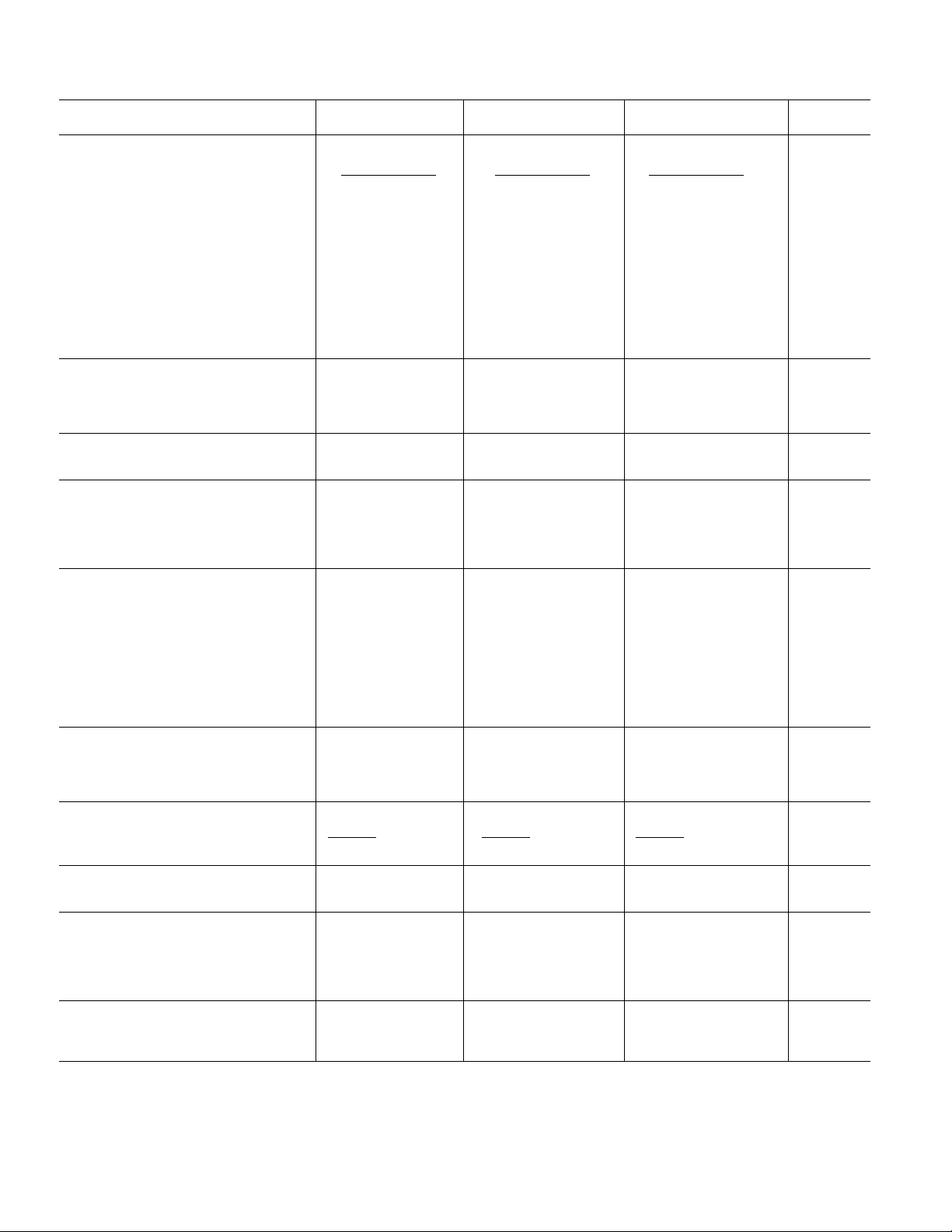

Thermal Characteristics

H-10A: θJC = 25°C/W; θJA = 150°C/W

E-20A: θ

D-14: θ

= 22°C/W; θJA = 85°C/W

JC

= 22°C/W; θJA = 85°C/W

JC

REV. B

AD532

ORDERING GUIDE

Temperature Package Package

Model Ranges Descriptions Options

AD532JD 0°C to +70°C Side Brazed DIP D-14

AD532JD/+ 0°C to +70°C Side Brazed DIP D-14

AD532KD 0°C to +70°C Side Brazed DIP D-14

AD532KD/+ 0°C to +70°C Side Brazed DIP D-14

AD532JH 0°C to +70°C Header H-10A

AD532KH 0°C to +70°C Header H-10A

AD532J Chip 0°C to +70°C Chip

AD532SD –55°C to +125°C Side Brazed DIP D-14

AD532SD/883B –55°C to +125°C Side Brazed DIP D-14

JM38510/13903BCA –55°C to +125°C Side Brazed DIP D-14

AD532SE/883B –55°C to +125°C LCC E-20A

AD532SH –55°C to +125°C Header H-10A

AD532SH/883B –55°C to +125°C Header H-10A

JM38510/13903BIA –55°C to +125°C Header H-10A

AD532S Chip –55°C to +125°C Chip

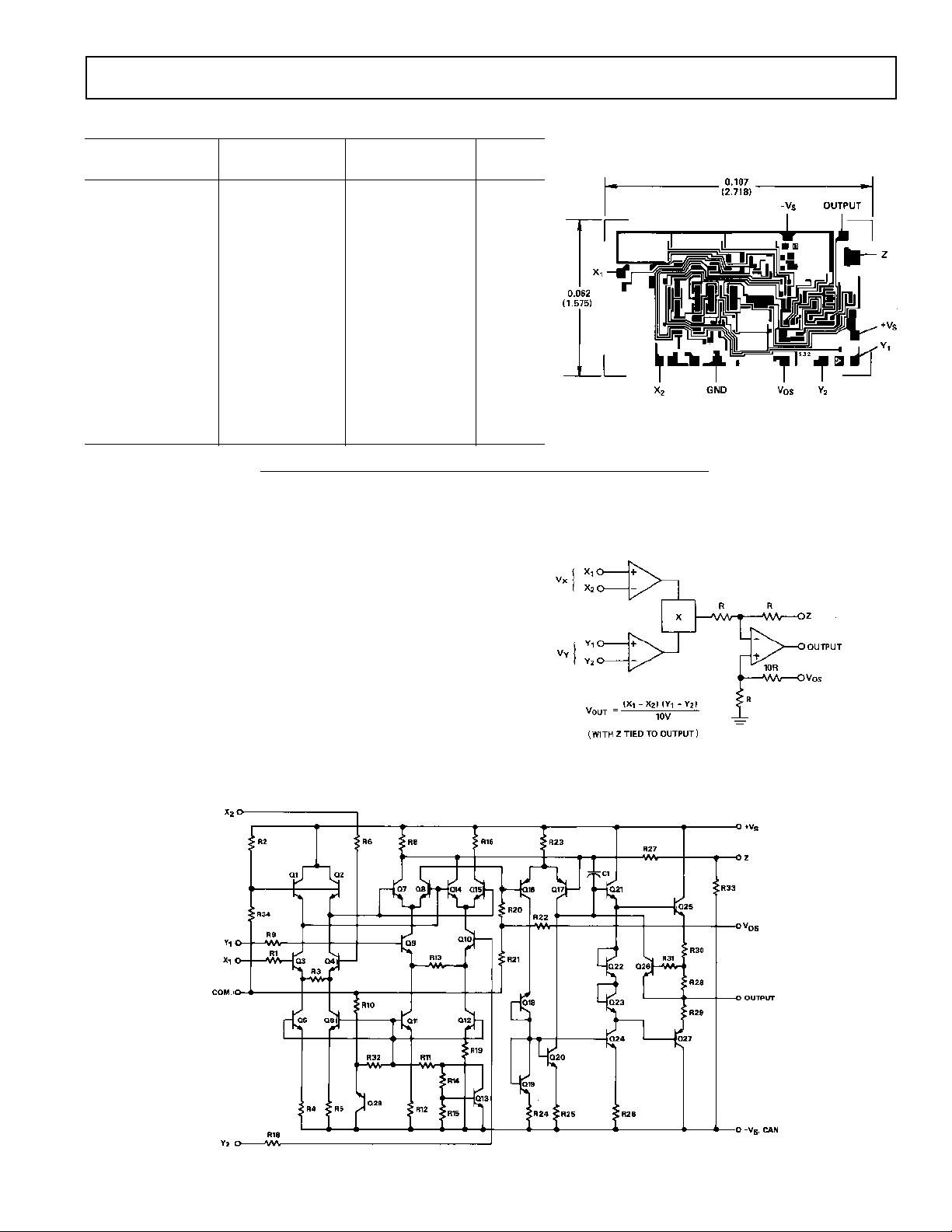

FUNCTIONAL DESCRIPTION

The functional block diagram for the AD532 is shown in Figure

1, and the complete schematic in Figure 2. In the multiplying

and squaring modes, Z is connected to the output to close the

feedback around the output op amp. (In the divide mode, it is

used as an input terminal.)

The X and Y inputs are fed to high impedance differential amplifiers featuring low distortion and good common-mode rejection. The amplifier voltage offsets are actively laser trimmed

to zero during production. The product of the two inputs is

resolved in the multiplier cell using Gilbert’s linearized transconductance technique. The cell is laser trimmed to obtain

= (X1 – X2)(Y1 – Y2)/10 volts. The built-in op amp is used

V

OUT

to obtain low output impedance and make possible self-contained

operation. The residual output voltage offset can be zeroed at

in critical applications . . . otherwise the VOS pin should be

V

OS

grounded.

CHIP DIMENSIONS AND BONDING DIAGRAM

Contact factory for latest dimensions.

Dimensions shown in inches and (mm).

Figure 1. Functional Block Diagram

REV. B

Figure 2. Schematic Diagram

–3–

Loading...

Loading...