Analog Devices AD5253 4 Datasheet

Quad 64-/256-Position I2C Nonvolatile

FEATURES

AD5253: Quad 64-position resolution

AD5254: Quad 256-position resolution

1 kΩ, 10 kΩ, 50 kΩ, 100 kΩ

Nonvolatile memory

protection

Power-on refreshed to EEMEM settings in 300 µs typ

EEMEM rewrite time = 540 µs typ

Resistance tolerance stored in nonvolatile memory

12 extra bytes in EEMEM for user-defined information

2

C® compatible serial interface

I

Direct read/write accesses of RDAC

Predefined linear increment/decrement commands

Predefined ±6 dB step change commands

Synchronous or asynchronous quad channel update

Wiper setting readback

4 MHz bandwidth—1 kΩ version

Single supply 2.7 V to 5.5 V

Dual supply ±2.25 V to ±2.75 V

2 slave address decoding bits allow operation of 4 devices

100-year typical data retention, T

Operating temperature: –40°C to +85°C

APPLICATIONS

Mechanical potentiometer replacement

Low resolution DAC replacement

RGB LED backlight control

White LED brightness adjustment

RF base station power amp bias control

Programmable gain and offset control

Programmable attenuators

Programmable voltage-to-current conversion

Programmable power supply

Programmable filters

Sensor calibrations

GENERAL DESCRIPTION

The AD5253/AD5254 are quad channel, I2C, nonvolatile memory, digitally controlled potentiometers with 64/256 positions,

respectively. These devices perform the same electronic adjustment functions as mechanical potentiometers, trimmers, and

variable resistors.

The AD5253/AD5254’s versatile programmability allows multiple modes of operation, including read/write accesses in the

RDAC and EEMEM registers, increment/decrement of

resistance, resistance changes in ±6 dB scales, wiper setting

readback, and extra EEMEM for storing user-defined information, such as memory data for other components, look-up table,

or system identification information.

1

stores wiper settings with write

2

and EEMEM registers

= 55°C

A

Memory Digital Potentiometers

AD5253/AD5254

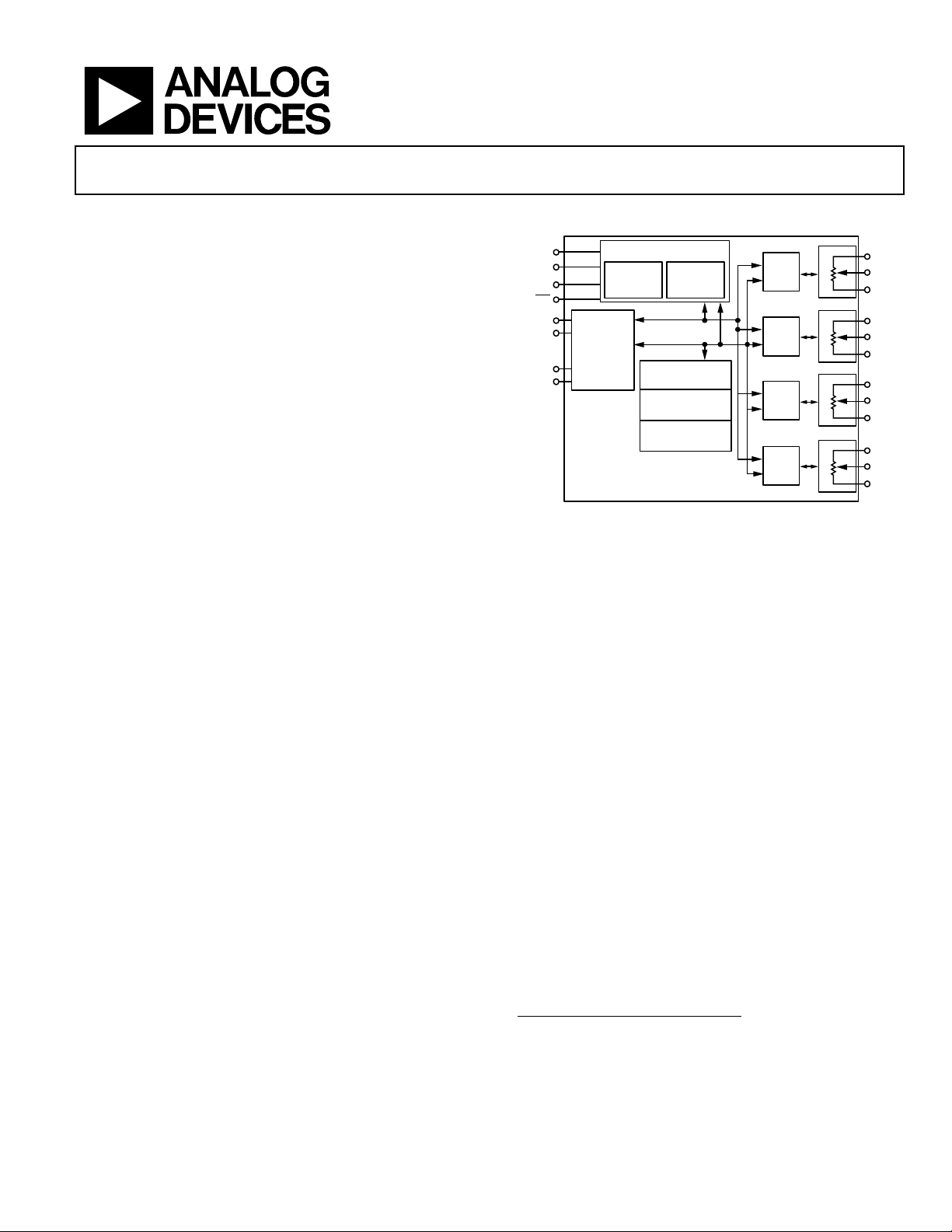

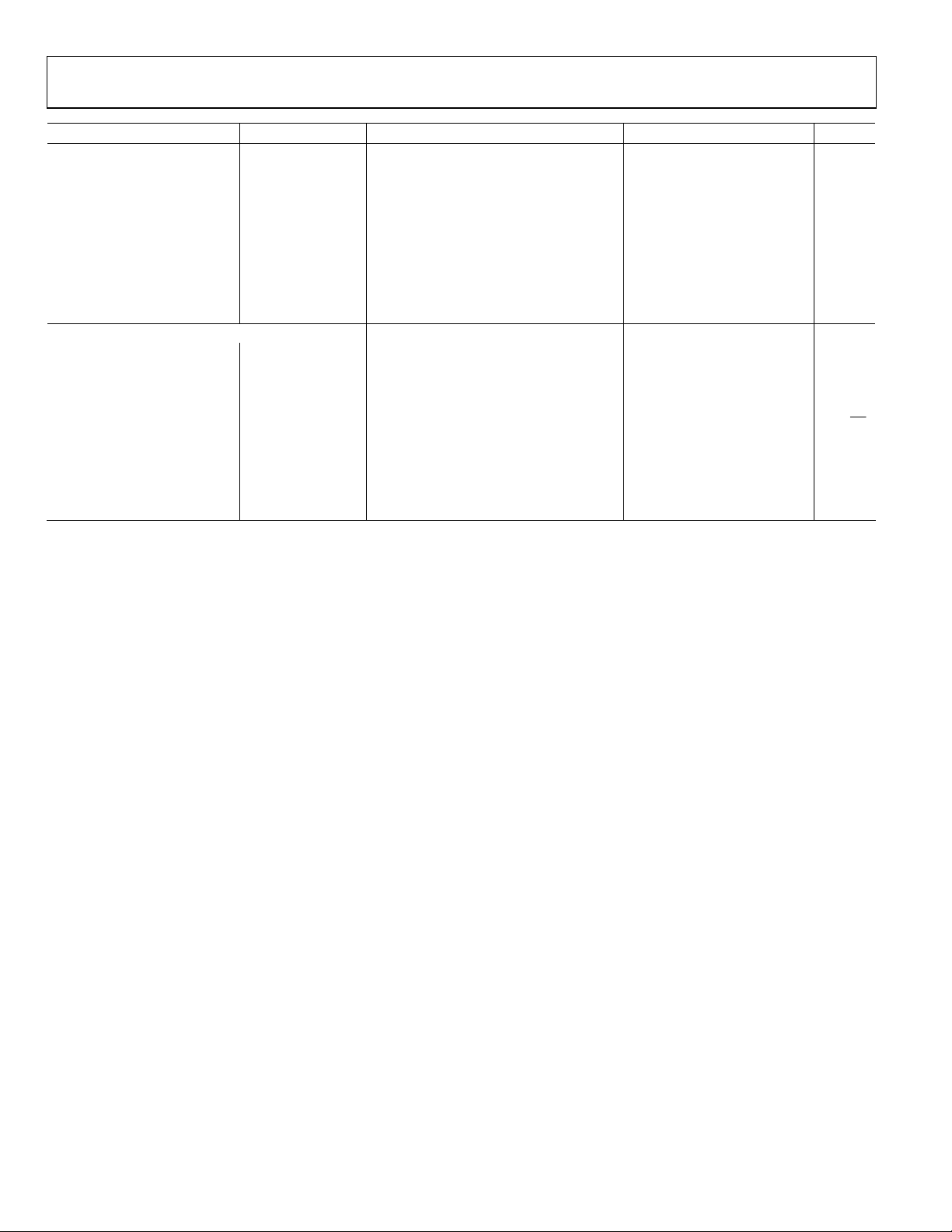

FUNCTIONAL BLOCK DIAGRAM

V

DD

V

SS

DGND

WP

SCL

SDA

AD0

AD1

SERIAL

INTERFACE

The AD5253/AD5254 allow the host I2C controllers to write any

of the 64-/256-step wiper settings in the RDAC registers and

store them in the EEMEM. Once the settings are stored, they are

restored automatically to the RDAC registers at system poweron; the settings can also be restored dynamically.

The AD5253/AD5254 provide additional increment, decrement,

+6 dB step change, and –6 dB step change in synchronous or

asynchronous channel update modes. The increment and

decrement functions allow stepwise linear adjustments, while

±6 dB step changes are equivalent to doubling or halving the

RDAC wiper setting. These functions are useful for steep-slope

nonlinear adjustment applications such as white LED brightness

and audio volume control.

The AD5253/AD5254 have a patented resistance tolerance

storing function that allows the user to access the EEMEM and

obtain the absolute end-to-end resistance values of the RDACs

for precision applications.

The AD5253/AD5254 are available in TSSOP-20 packages in

1 kΩ, 10 kΩ, 50 kΩ, and 100 kΩ options. All parts are

guaranteed to operate over the –40°C to +85°C extended

industrial temperature range.

1

The terms nonvolatile memory and EEMEM are used interchangeably.

2

The terms digital potentiometer and RDAC are used interchangeably.

RDAC EEMEM

EEMEM

POWER-ON

REFRESH

DATA

I2C

CONTROL

COMMAND

DECODE LOGIC

ADDRESS

DECODE LOGIC

CONTROL LOGIC

AD5253/AD5254

RAB TOL

Figure 1.

RDAC0

REGIS-

TER

RDAC1

REGIS-

TER

RDAC2

REGIS-

TER

RDAC3

REGIS-

TER

RDAC0

RDAC1

RDAC2

RDAC3

A0

W0

B0

A1

W1

B1

A2

W2

B2

A3

W3

B3

03824-0-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

AD5253/AD5254

TABLE OF CONTENTS

Electrical Characteristics ................................................................. 3

1 kΩ Version.................................................................................. 3

10 kΩ, 50 kΩ, 100 kΩ Versions ................................................... 5

Interface Timing Characteristics (All Parts)............................. 7

Absolute Maximum Ratings............................................................ 8

ESD Caution.................................................................................. 8

Pin Configuration and Functional Descriptions.......................... 9

Typical Performance Characteristics........................................... 10

I2C Interface..................................................................................... 14

I2C Interface General Description............................................ 14

I2C Interface Detail Description............................................... 15

I2C Compatible 2-Wire Serial Bus............................................ 19

Theory of Operation ...................................................................... 20

Linear Increment and Decrement Commands ......................20

±6 dB Adjustments (Doubling/Halving Wiper Setting)........ 20

Digital Input/Output Configuration........................................ 21

Multiple Devices On One Bus .................................................. 21

Terminal Voltage Operation Range ......................................... 22

Power-Up and Power-Down Sequences .................................. 22

Layout and Power Supply Biasing ............................................ 22

Digital Potentiometer Operation ............................................. 23

Programmable Rheostat Operation......................................... 23

Programmable Potentiometer Operation ............................... 24

Applications..................................................................................... 25

RGB LED LCD Backlight Controller....................................... 25

Outline Dimensions....................................................................... 27

Ordering Guide .......................................................................... 27

REVISION HISTORY

Revision 0: Initial Version

Rev. 0 | Page 2 of 28

AD5253/AD5254

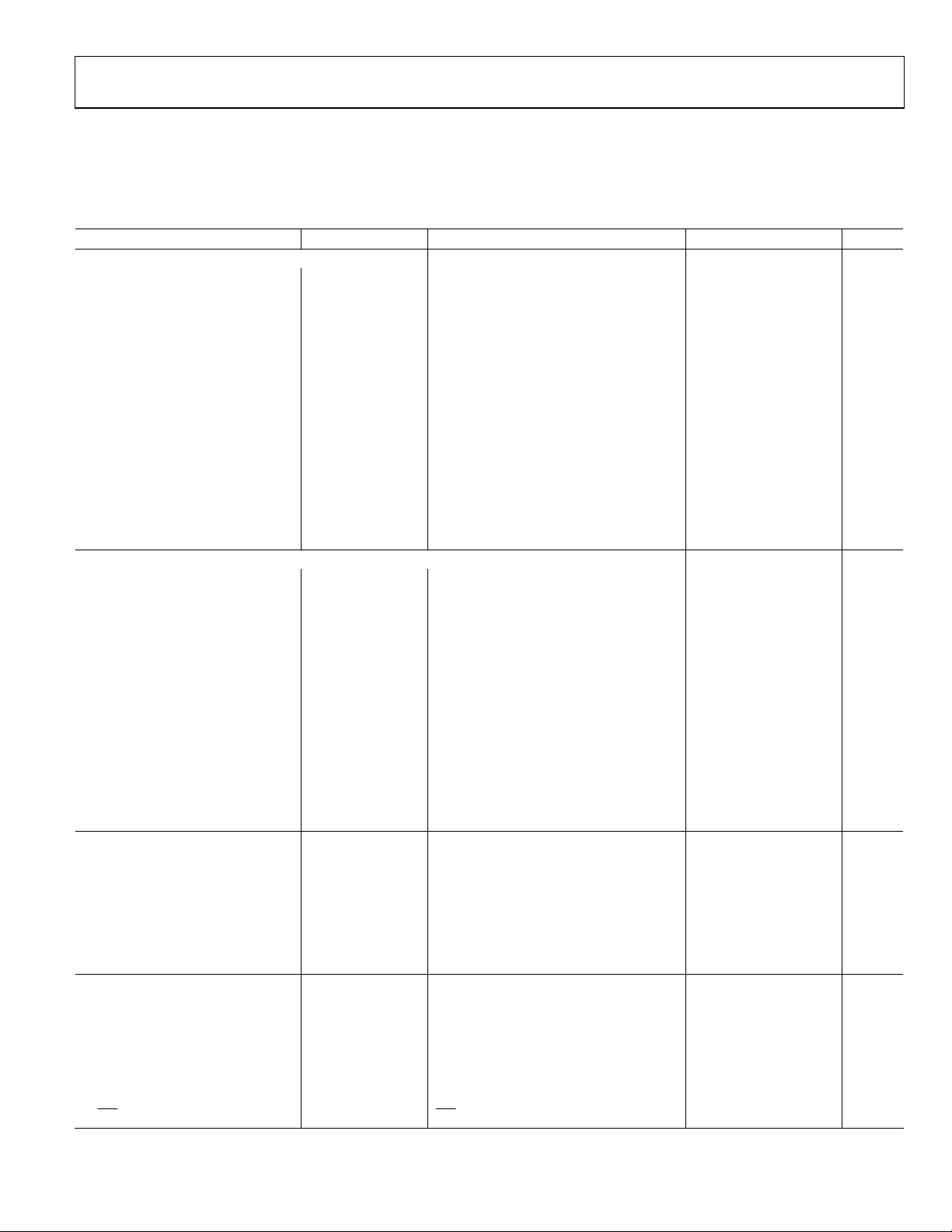

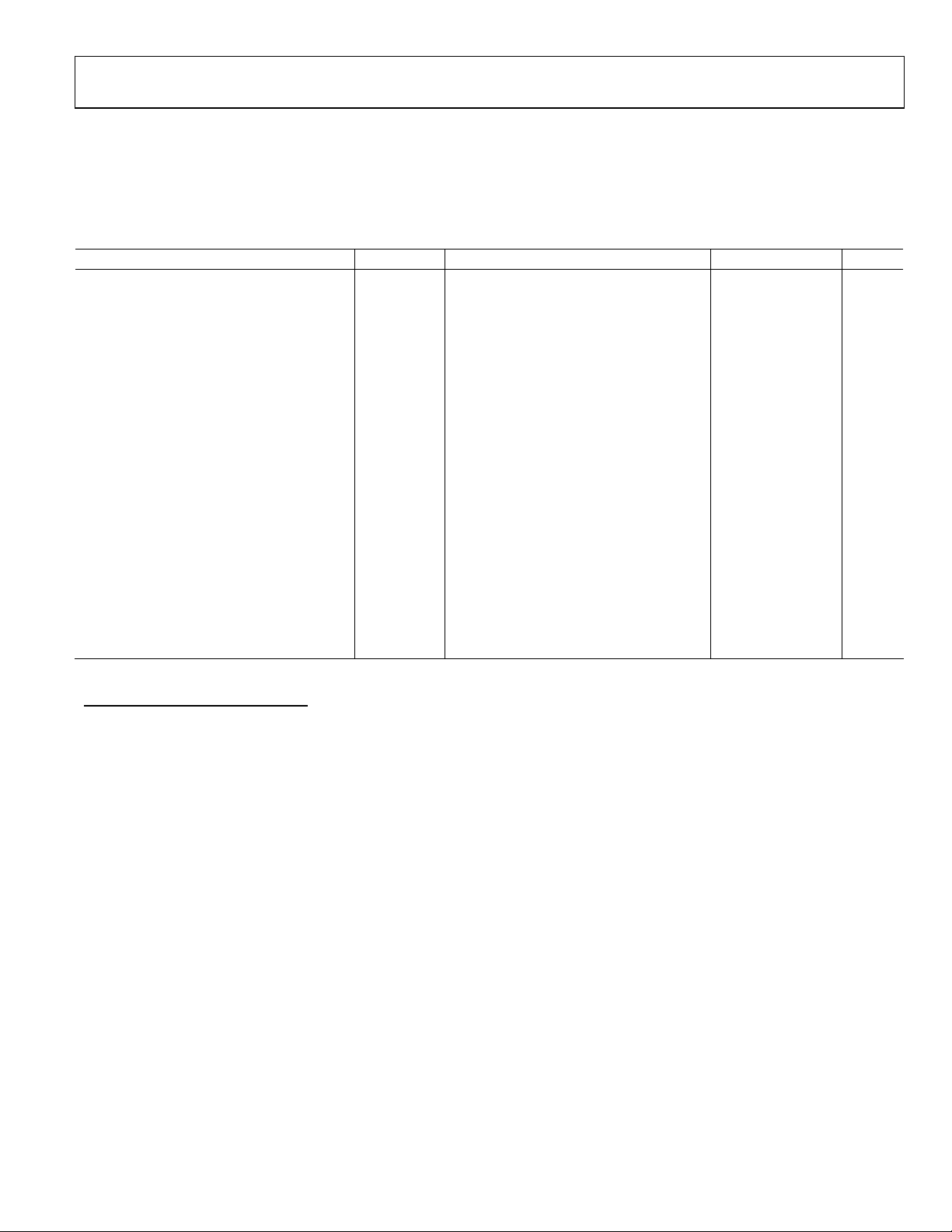

ELECTRICAL CHARACTERISTICS

1 kΩ VERSION

VDD = +3 V ± 10% or +5 V ± 10%, VSS = 0 V or VDD/VSS = ±2.5 V ± 10%, VA = +VDD, VB = 0 V, –40°C < TA < +85°C, unless otherwise noted.

Table 1.

Parameter Symbol Conditions Min Typ1Max Unit

DC CHARACTERISTICS—RHEOSTAT MODE

Resolution N AD5253/AD5254 6/8 Bits

Resistor Differential Nonlinearity

R

R

R

Resistor Nonlinearity2 R-INL RWB, RWA = NC, VDD = 5.5V, AD5253 –0.5 ±0.2 +0.5 LSB

R

R

R

Nominal Resistor Tolerance ∆RAB/R

Resistance Temperature

Coefficient

Wiper Resistance R

I

Channel Resistance Matching ∆R

DC CHARACTERISTICS—POTENTIOMETER DIVIDER MODE

Differential Nonlinearity

3

AD5254 –1 ±0.25 +1 LSB

Integral Nonlinearity3 INL AD5253 –0.5 ±0.2 +0.5 LSB

AD5254 –2 ±0.5 +2 LSB

Voltage Divider Temperature

Coefficient

Full-Scale Error V

Code = Full scale, VDD = 5.5 V, AD5254 –16 –11 0 LSB

Code = Full scale, VDD = 2.7 V, AD5253 –6 –4 0 LSB

Code = Full scale, VDD = 2.7 V, AD5254 –23 –16 0 LSB

Zero-Scale Error V

Code = Zero scale, VDD = 5.5 V, AD5254 0 11 16 LSB

Code = Zero scale, VDD = 2.7 V, AD5253 0 4 6 LSB

Code = Zero scale, VDD = 2.7 V, AD5254 0 15 20 LSB

RESISTOR TERMINALS

Voltage Range

4

Capacitance5 Ax, Bx CA, C

Capacitance5 Wx C

Common-Mode Leakage

Current

DIGITAL INPUTS AND OUTPUTS

Input Logic High V

V

Input Logic Low V

V

Output Logic High (SDA) V

Output Logic Low (SDA) V

WP Leakage Current

2

R-DNL RWB, RWA = NC, VDD = 5.5V, AD5253 –0.5 ±0.2 +0.5 LSB

, RWA = NC, VDD = 5.5V, AD5254 –1 ±0.25 +1 LSB

WB

, RWA = NC, VDD = 2.7V, AD5253 –0.75 ±0.3 +0.75 LSB

WB

, RWA = NC, VDD = 2.7V, AD5254 –1.5 ±0.3 +1.5 LSB

WB

, RWA = NC, VDD = 5.5V, AD5254 –2 ±0.5 +2 LSB

WB

, RWA = NC, VDD = 2.7V, AD5253 –1 +2.5 +4 LSB

WB

, RWA = NC, VDD = 2.7V, AD5254 –2 +9 +14 LSB

WB

TA = 25°C –30 +30 %

IW = 1 V/R, VDD = 5 V 75 130 Ω

= 1 V/R, VDD = 3 V 200 300 Ω

W

0.15 %

(∆R

W

AB

) × 106/∆T 650 ppm/°C

AB/RAB

/∆R

AB1

AB2

DNL AD5253 –0.5 ±0.1 +0.5 LSB

(∆V

VA, VB, V

) × 106/∆T Code = Half scale 25 ppm/°C

W/VW

WFSE

WZSE

W

B

Code = Full scale, VDD = 5.5 V, AD5253 –5 –3 0 LSB

Code = Zero scale, VDD = 5.5 V, AD5253 0 3 5 LSB

V

f = 1 kHz, measured to GND,

SS

85 pF

VDDV

Code = Half scale

W

f = 1 kHz, measured to GND,

95 pF

Code = Half scale

I

CM

IH

IL

OH

OL

I

WP

VA = VB = VDD /2 0.01 1 µA

VDD = 5 V, VSS = 0 V 2.4 V

= +2.7 V/0 V or VDD/VSS = ±2.5 V 2.1 V

DD/VSS

VDD =5 V, VSS = 0 V 0.8 V

= +2.7 V/0 V or VDD/VSS = ±2.5 V 0.6 V

DD/VSS

R

= 2.2 kΩ to VDD = 5 V, VSS = 0 V 4.9 V

PULL-UP

R

= 2.2 kΩ to VDD =5 V, VSS = 0 V 0.4 V

PULL-UP

WP = V

DD

5 µA

Rev. 0 | Page 3 of 28

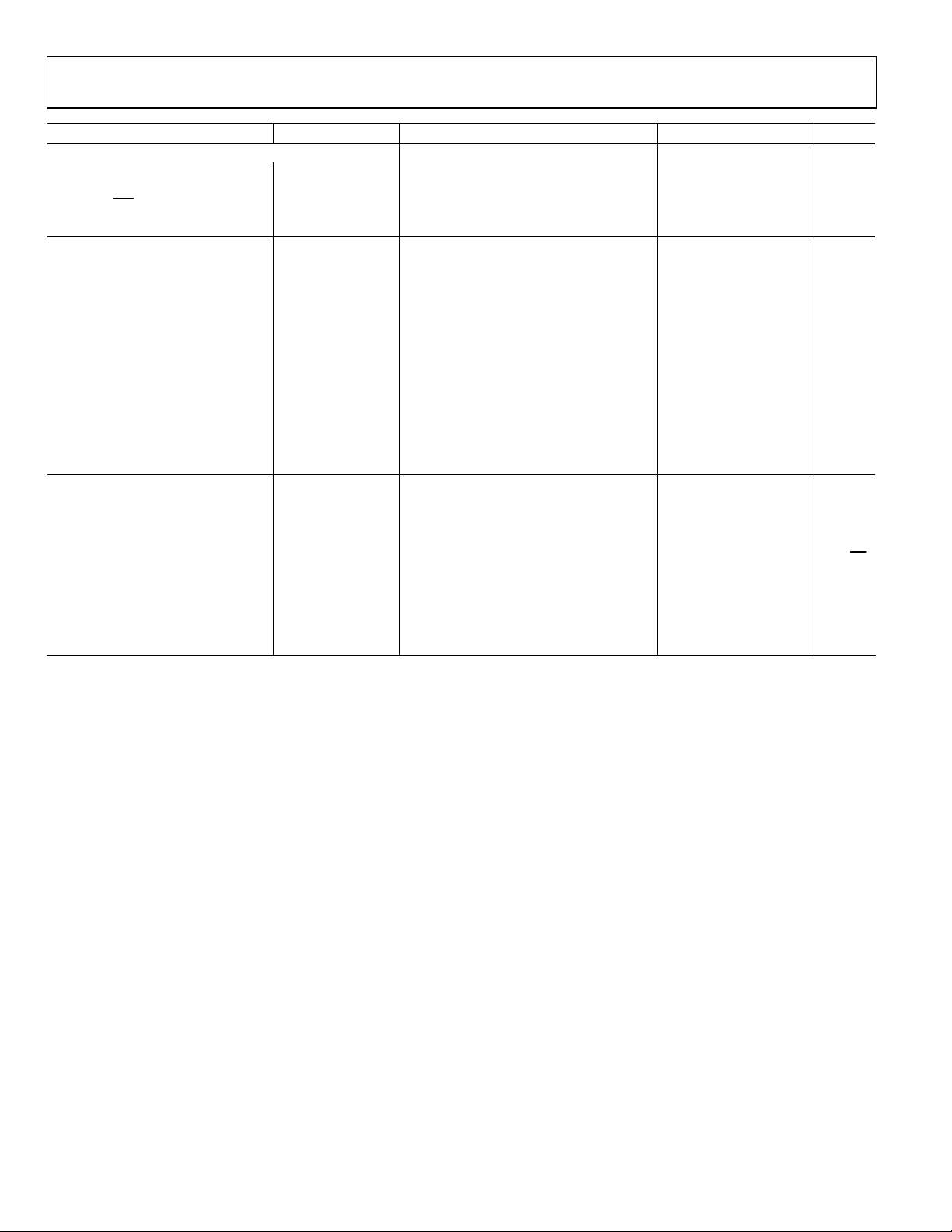

AD5253/AD5254

Parameter Symbol Conditions Min Typ1Max Unit

DIGITAL INPUTS AND OUTPUTS (continued)

A0 Leakage Current I

A0

Input Leakage Current (Other

WP and A0)

than

I

I

Input Capacitance5 CI 5 pF

POWER SUPPLIES

Single-Supply Power Range V

Dual-Supply Power Range VDD/V

Positive Supply Current I

Negative Supply Current I

DD

SS

DD

SS

EEMEM Data Storing Mode

Current

EEMEM Data Restoring Mode

Power Dissipation

Current

6

7

I

DD_STORE

I

DD_RESTORE

P

DISS

Power Supply Sensitivity PSS ∆VDD = 5 V ±10% −0.025 0.01 0.025 %/%

∆VDD = 3 V ±10% –0.04 0.02 0.04 %/%

DYNAMIC CHARACTERISTICS

5, 8

Bandwidth –3 dB BW RAB = 1 kΩ 4 MHz

Total Harmonic Distortion THD VA =1 V rms, VB = 0 V, f = 1 kHz 0.05 %

VW Settling Time t

Resistor Noise Voltage e

Digital Crosstalk C

Analog Coupling C

S

N_WB

T

AT

A0 = GND 3 µA

VIN = 0 V or V

DD

±1 µA

VSS = 0 V 2.7 5.5 V

±2.25 ±2.75 V

VIH = VDD or VIL = GND 5 15 µA

VIH = VDD or VIL = GND, VDD = +2.5 V,

V

= –2.5 V

SS

–5 –15 µA

VIH = VDD or VIL = GND 35 mA

VIH = VDD or VIL = GND 2.5 mA

VIH = VDD = 5 V or VIL = GND 0.075 mW

VA = VDD, VB = 0 V 0.2 µs

RWB = 500 Ω, f = 1 kHz. Thermal noise

3

nV/√Hz

only.

VA = VDD, VB = 0 V, measure VW with

–80 dB

adjacent RDAC making full-scale change

Signal input at A0 and measure the

–72 dB

output at W1, f = 1 kHz

Rev. 0 | Page 4 of 28

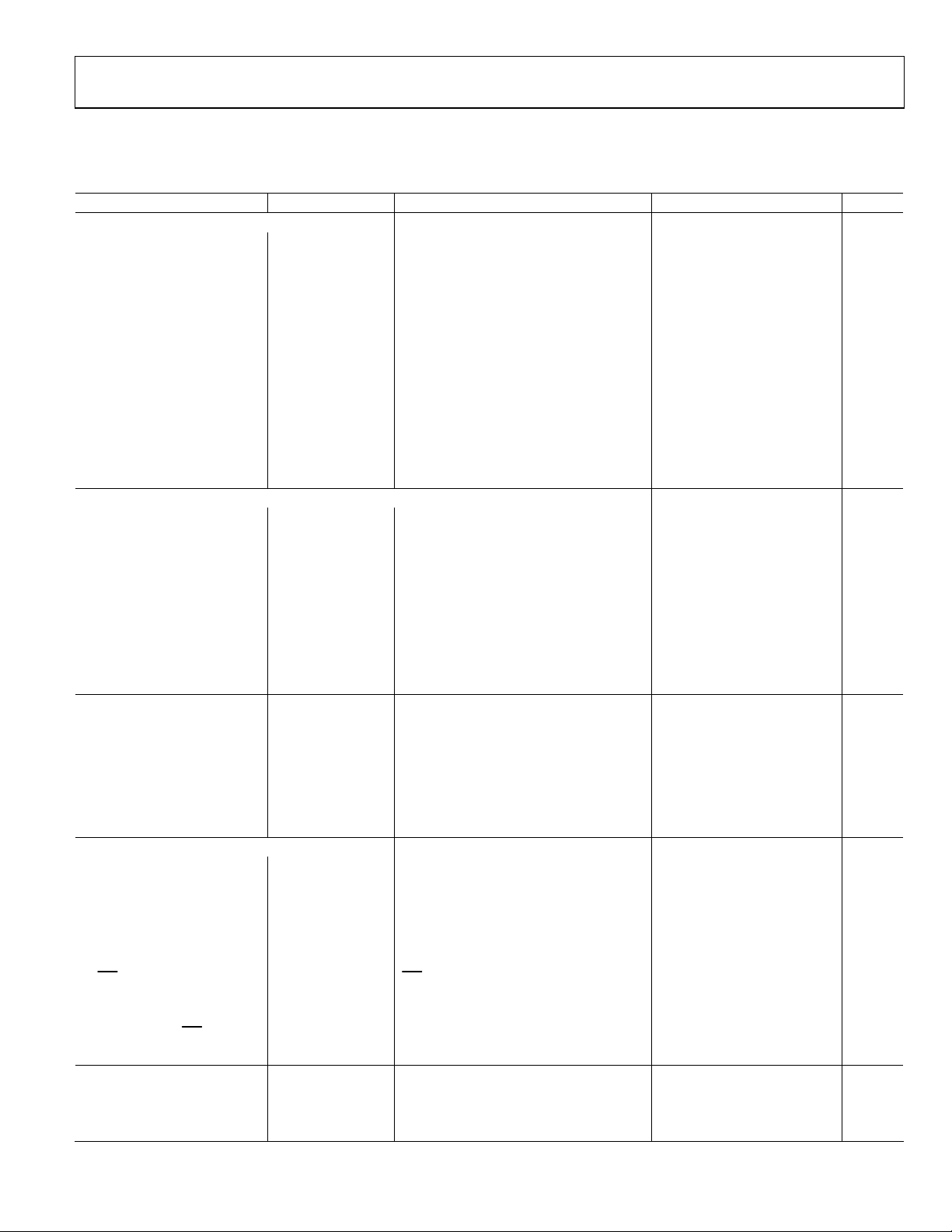

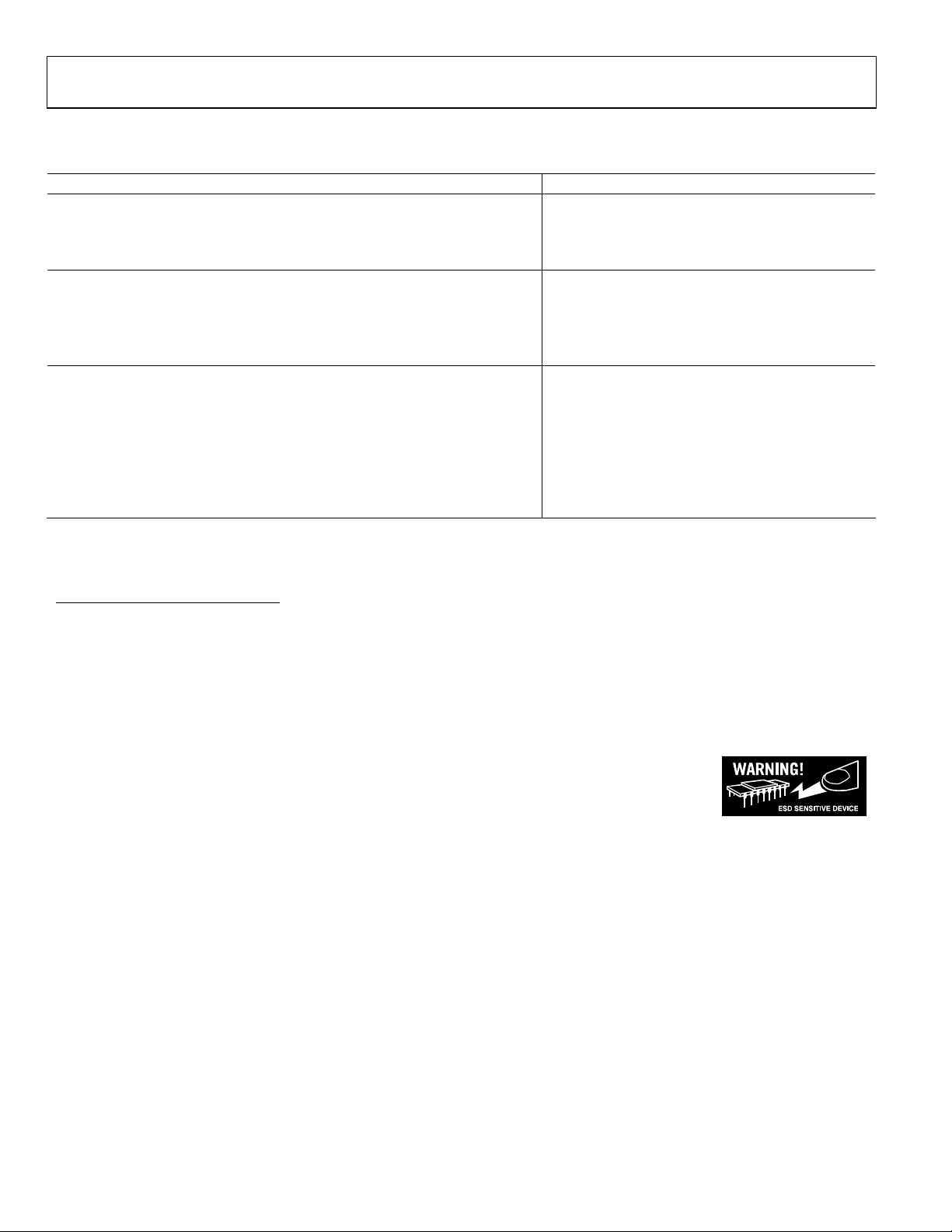

AD5253/AD5254

10 kΩ, 50 kΩ, 100 kΩ VERSIONS

VDD = +3 V± 10% or +5 V± 10%, VSS = 0 V or VDD/VSS = ±2.5 V ± 10%, VA = +VDD, VB = 0 V, –40°C < TA < +85°C, unless otherwise noted.

Table 2.

Parameter Symbol Conditions Min Typ1 Max Unit

DC CHARACTERISTICS—RHEOSTAT MODE

Resolution N AD5253/AD5254 6/8 Bits

Resistor Differential

Nonlinearity

R

Resistor Nonlinearity2 R-INL RWB, RWA = NC, AD5253 −0.75 ±0.25 +0.75 LSB

R

Nominal Resistor Tolerance ∆RAB/R

Resistance Temperature

Coefficient

Wiper Resistance R

I

Channel Resistance

Matching

R

DC CHARACTERISTICS—POTENTIOMETER DIVIDER MODE

Differential Nonlinearity3 DNL AD5253 −0.5 ±0.1 +0.5 LSB

AD5254 −1 ±0.3 +1 LSB

Integral Nonlinearity3 INL AD5253 −0.5 ±0.15 +0.5 LSB

AD5254 −1.5 ±0.5 +1.5 LSB

Voltage Divider

Temperature Coefficient

Full-Scale Error V

Code = Full scale, AD5254 −3 −1 0 LSB

Zero-Scale Error V

Code = Zero scale, AD5254 0 1.2 3 LSB

RESISTOR TERMINALS

Voltage Range4 V

Capacitance5 Ax, Bx CA, C

Capacitance5 Wx C

Common-Mode Leakage

Current

DIGITAL INPUTS AND OUTPUTS

Input Logic High V

V

Input Logic Low V

V

Output Logic High (SDA) V

Output Logic Low (SDA) V

WP Leakage Current

A0 Leakage Current I

Input Leakage Current

(Other than

Input Capacitance5 C

POWER SUPPLIES

Single-Supply Power Range V

Dual-Supply Power Range VDD/V

Positive Supply Current I

2

R-DNL RWB, RWA = NC, AD5253 −0.75 ±0.1 +0.75 LSB

, RWA = NC, AD5254 −1 ±0.25 +1 LSB

WB

, RWA = NC, AD5254 −2.5 ±1 +2.5 LSB

WB

TA = 25°C −20 +20 %

IW = 1 V/R, VDD = 5 V 75 130 Ω

= 1 V/R, VDD = 3 V 200 300 Ω

W

R

= 10 kΩ, 50 kΩ 0.15 %

AB

= 100 kΩ 0.05 %

AB

Code = Full scale, AD5253 −1 −0.3 0 LSB

Code = Zero scale, AD5253 0 0.3 1 LSB

V

f = 1 kHz, measured to GND,

SS

85 pF

VDDV

(∆R

W

∆R

(∆V

WFSE

WZSE

A

AB

) × 106/∆T 650 ppm/°C

AB/RAB

/∆R

AB1

AB2

) × 106/∆T Code = Half scale 15 ppm/°C

W/VW

, VB, V

W

B

Code = Half scale

W

f = 1 kHz, measured to GND,

95 pF

Code = Half scale

6

ICMVA = VB = VDD/2 0.01 1 µA

VDD = 5 V, VSS = 0 V 2.4 V

= +2.7 V/0 V or VDD/VSS = ±2.5 V 2.1 V

DD/VSS

VDD = 5 V, VSS = 0 V 0.8 V

= +2.7 V/0 V or VDD/VSS = ±2.5 V 0.6 V

DD/VSS

R

= 2.2 kΩ to VDD = 5 V, VSS = 0 V 4.9 V

PULL-UP

R

= 2.2 kΩ to VDD = 5 V, VSS = 0 V 0.4 V

PULL-UP

WP = V

DD

5 µA

A0 = GND 3 µA

VIN = 0 V or V

DD

±1 µA

5 pF

VSS = 0 V 2.7 5.5 V

±2.25 ±2.75 V

VIH = VDD or VIL = GND 5 15 µA

WP and A0)

IH

IL

OH

OL

I

WP

A0

I

I

I

DD

SS

DD

Rev. 0 | Page 5 of 28

AD5253/AD5254

Parameter Symbol Conditions Min Typ1 Max Unit

POWER SUPPLIES (continued)

Negative Supply Current I

SS

VIH = VDD or VIL = GND, VDD = +2.5 V,

= −2.5 V

V

SS

EEMEM Data Storing Mode

Current

EEMEM Data Restoring

Mode Current

6

I

Power Dissipation7 P

I

DD_STORE

DD_RESTORE

DISS

VIH = VDD or VIL = GND, TA = 0°C to 85°C 35 mA

VIH = VDD or VIL = GND, TA = 0°C to 85°C 2.5 mA

VIH = VDD = 5 V or VIL = GND 0.075 mW

Power Supply Sensitivity PSS ∆VDD = 5 V ± 10% −0.005 +0.002 +0.005 %/%

∆VDD = 3 V ± 10% −0.01 +0.002 +0.01 %/%

DYNAMIC CHARACTERISTICS

5, 8

–3 dB Bandwidth BW RAB = 10 kΩ/50 kΩ/100 kΩ 400/80/40 kHz

Total Harmonic Distortion THDW VA = 1 Vrms, VB = 0 V, f = 1 kHz 0.05 %

VW Settling Time t

Resistor Noise Voltage e

S

N_WB

VA = VDD, VB = 0 V,

= 10 kΩ/50 kΩ/100 kΩ

R

AB

RAB = 10 kΩ/50 kΩ/100 kΩ, Code =

Midscale, f = 1 kHz. Thermal noise only.

Digital Crosstalk C

T

VA = VDD, VB = 0 V, Measure VW with

adjacent RDAC making full scale change

Analog Coupling C

AT

Signal input at A0 and measure

output at W1, f = 1 kHz

−5 −15 µA

1.5/7/14 µs

9/20/29

nV/√

Hz

−80 dB

−72 dB

Rev. 0 | Page 6 of 28

AD5253/AD5254

INTERFACE TIMING CHARACTERISTICS (ALL PARTS)

Guaranteed by design, not subject to production test. See Figure 23 for location of measured values. All input control voltages are specified

= tF = 2.5 ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V. Switching characteristics are measured using both

with t

R

= 3 V and 5 V. When the part is not in operation, the SDA and SCL pins should be pulled high. When these pins are pulled low, the

V

DD

2

C interface at these pins conducts current of about 0.8 mA at VDD = 5.5 V and 0.2 mA at VDD = 2.7 V.

I

Table 3.

Parameter Symbol Conditions Min Typ1 Max Unit

SCL Clock Frequency f

t

Bus Free Time between STOP and START t

BUF

t

Hold Time (Repeated START) t

HD;STA

t

Low Period of SCL Clock t

LOW

t

High Period of SCL Clock t

HIGH

t

Setup Time for START Condition t

SU;STA

t

Data Hold Time t

HD;DAT

t

Data Setup Time t

SU;DAT

tF Fall Time of Both SDA and SCL Signals t

tR Rise Time of Both SDA and SCL Signals t

t

Setup Time for STOP Condition t

SU;STO

EEMEM Data Storing Time t

EEMEM Data Restoring Time at Power On

EEMEM Data Restoring Time upon Restore

Command or RESET Operation

9

EEMEM Data Rewritable Time10 t

SCL

1

2

3

4

5

6

7

8

9

10

EEMEM_STORE

9

t

EEMEM_RESTORE1

t

EEMEM_RESTORE2VDD

EEMEM_REWRITE

FLASH/EE MEMORY RELIABILITY

Endurance

11

100 kCycles

Data Retention12 100 Years

400 kHz

1.3 µs

After this period, the first clock pulse is

0.6 µs

generated

1.3 µs

0.6 µs

0.6 µs

0 0.9 µs

100 ns

300 ns

300 ns

0.6 µs

26 ms

VDD rise time dependent. Measure without

decoupling capacitors at V

and VSS.

DD

300 µs

= 5 V 300 µs

540 µs

1

Typical values represent average readings at 25°C and VDD = 5 V.

2

Resistor position nonlinearity error (R-INL) is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper

positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic, except R-DNL of AD5254 1 kΩ

version at V

3

INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = VDD and VB = 0 V. DNL

specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions.

4

Resistor terminals A, B, and W have no limitations on polarity with respect to each other.

5

Guaranteed by design and not subject to production test.

6

cmd 0 NOP should be activated after cmd 1 in order to minimize I

7

P

is calculated from (IDD × VDD = 5 V).

DISS

8

All dynamic characteristics use VDD = 5 V.

9

During power-up, all outputs preset to midscale before restoring EEMEM contents. RDAC0 has the shortest whereas RDAC3 has the longest EEMEM restore time.

10

Delay time after power-on or RESET before new EEMEM data to be written.

11

Endurance is qualified to 100,000 cycles per JEDEC Std. 22 method A117, and is measured at –40°C, +25°C, and +85°C; typical endurance at +25°C is 700,000 cycles.

12

Retention lifetime equivalent at junction temperature (TJ) = 55°C per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6eV derates

with junction temperature.

= 2.7V, IW = VDD/R for both VDD = 3 V or VDD = 5 V.

DD

current consumption.

DD_RESTORE

Rev. 0 | Page 7 of 28

AD5253/AD5254

ABSOLUTE MAXIMUM RATINGS

Table 4. TA = 25°C, unless otherwise noted

Parameter Rating

VDD to GND −0.3 V, +7 V

VSS to GND +0.3 V, −7 V

VDD to V

SS

VA, VB, VW to GND VSS, V

Maximum Current

IWB, IWA Pulsed ±20 mA

IWB Continuous (RWB ≤ 1 kΩ, A Open)

1

IWA Continuous (RWA ≤ 1 kΩ, B Open)1 ±5 mA

IAB Continuous (RAB = 1 kΩ/10 kΩ/50 kΩ/100 kΩ)1 ±5 mA/±500 µA/±100 µA/±50 µA

Digital Inputs and Output Voltage to GND 0 V, 7 V

Operating Temperature Range −40°C to +85°C

Maximum Junction Temperature (T

) 150°C

J MAX

Storage Temperature −65°C to +150°C

Lead Temperature (Soldering, 10 sec) 300°C

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

TSSOP-20 Thermal Resistance2 θ

JA

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only;

functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not

implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

7 V

DD

±5 mA

143°C/W

1

Maximum terminal current is bounded by the maximum applied voltage across any two of the A, B, and W terminals at a given resistance, the maximum current

handling of the switches, and the maximum power dissipation of the package. V

2

Package power dissipation = (T

JMAX

− TA)/θJA.

= 5V.

DD

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 8 of 28

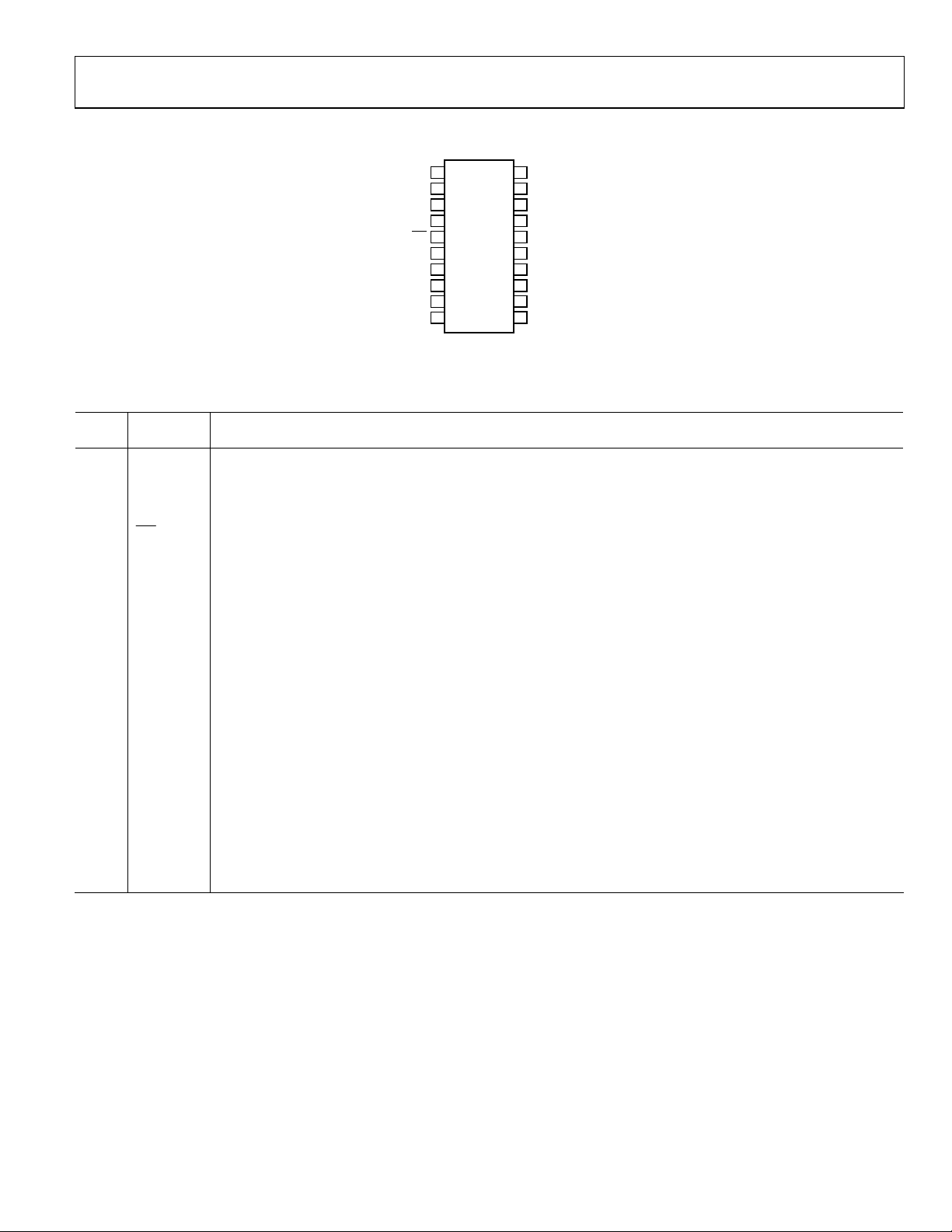

AD5253/AD5254

A

PIN CONFIGURATION AND FUNCTIONAL DESCRIPTIONS

W0

1

2

B0

AD5253/

A0

3

AD5254

4

AD0

SD

V

WP

W1

B1

A1

SS

TOP VIEW

(Not to Scale)

5

1

2

3

4

5

Figure 2. AD5253/AD5254 Pin Configuration

Table 5. AD5253/AD5254 Pin Function Descriptions

Pin

No. Mnemonic Description

1 W0 Wiper Terminal of RDAC0. VSS ≤ VW0 ≤ VDD.

2 B0 B Terminal of RDAC0. VSS ≤ VB0 ≤ VDD.

3 A0 A Terminal of RDAC0. VSS ≤ VA0 ≤ VDD.

4 AD0 I2C Device Address 0. AD0 and AD1 allow four AD5253/AD5254s to be addressed.

5

WP

Write Protect, Active Low. VWP ≤ VDD + 0.3 V.

6 W1 Wiper Terminal of RDAC1. VSS ≤ VW1 ≤ VDD.

7 B1 B Terminal of RDAC1. VSS ≤ VB1 ≤ VDD.

8 A1 A Terminal of RDAC1. VSS ≤ VA1 ≤ VDD.

9 SDA

Serial Data Input/Output Pin. Shifts in one bit at a time on positive clock CLK edges. MSB loaded first. Open-drain

MOSFET requires pull-up resistor.

10 V

SS

Negative Supply. Connect to 0 V for single supply or –2.7 V for dual supply, where VDD – VSS ≤ +5.5 V. If VSS is used,

rather than grounded, in dual supply, V

must be able to sink 35 mA for 26 ms when storing data to EEMEM.

SS

11 A2 A Terminal of RDAC2. VSS ≤ VA2 ≤ VDD.

12 B2 B Terminal of RDAC2. VSS ≤ VB2 ≤ VDD.

13 W2 Wiper Terminal of RDAC2. VSS ≤ VW2 ≤ VDD.

14 SCL

Serial Input Register Clock Pin. Shifts in one bit at a time on positive clock edges. V

is recommended for SCL to ensure minimum power.

15 DGND Digital Ground. Connect to system analog ground at a single point.

16 AD1 I2C Device Address 1. AD0 and AD1 allow four AD5253/AD5254s to be addressed.

17 A3 A Terminal of RDAC3. VSS ≤ VA3 ≤ VDD.

18 B3 B Terminal of RDAC3. VSS ≤ VB3 ≤ VDD.

19 W3 W Terminal of RDAC3. VSS ≤ VW3 ≤ VDD.

20 V

DD

Positive Power Supply Pin. Connect +2.7 V to +5 V for single supply or ±2.7 V for dual supply, where VDD – VSS ≤ 5.5 V.

must be able to source 35 mA for 26 ms when storing data to EEMEM.

V

DD

V

10

DD

9

W3

8

B3

7

A3

6

AD1

DGND

10

9

SCL

8

W2

7

B2

6

A2

03842-0-002

≤ (VDD + 0.3 V). Pull-up resistor

SCL

Rev. 0 | Page 9 of 28

Loading...

Loading...