Page 1

D R -635

S e r v i c e M a n u a l

CONTENTS

SPECIFICATIONS

1) GENERAL

....................

1...'.......... 2

2) TRANSMITTER....................................................

3) RECEIVER

.................................................I..'...... 3

CIRCUIT DESCRIPTION

1) VHF Reception..........................................:./4

2) UHF Reception

........

. . . . . i .

...............

..... 5

3) FM Reception........................................................6

4) V/V(VHF-VHF) Dual Reception

5) U/U (UHF-UHF) Dual Reception

6) VHF Squelch Control

7) UHF Squelch Control

8) Transmit Signal Path

........................... ....... 7

................i...........................

......................................... 7

9) VHF Transmit Signal Path...................................

......................... 6

............................

.

10) UHF Transmit Signal Path.......................................8

11) VHFTxAPC Circuit

...............................................

12) UHFTx APC Circuit...................................... 8

13) VHF PTT Circuit

........................................

14) UHF PTT Circuit....................................

15) VHF PLL

..........................

...................................

...... 8

...............

16) UHF PLL................................................................9

17) Power-on Circuit

.................................................

SEMICONDUCTOR DATA

1) M5218FP (XA0068)..........

...................................

2) NJM78L05UA (XA0098)....................................... 10

3) NJM7808FA (XA0102)........................................ 10

4) TC4S66F (XA0115)........................................... 11

5) AN8010M (XA0119)

.............................................11

6) BU4052BF (XA0236)............................................ 11

7) TA75S01F (XA0332)............................................ 12

8) TC4W53FU (XA0348)

9) TA31136FN (XA0404).................................

10) LA4425A (XA0410)

..........................................

.........

..............................................

11) NJM2904V (XA0573)............................................ 13

12) NJM2902V-TE1 (XA0596).................................... 13

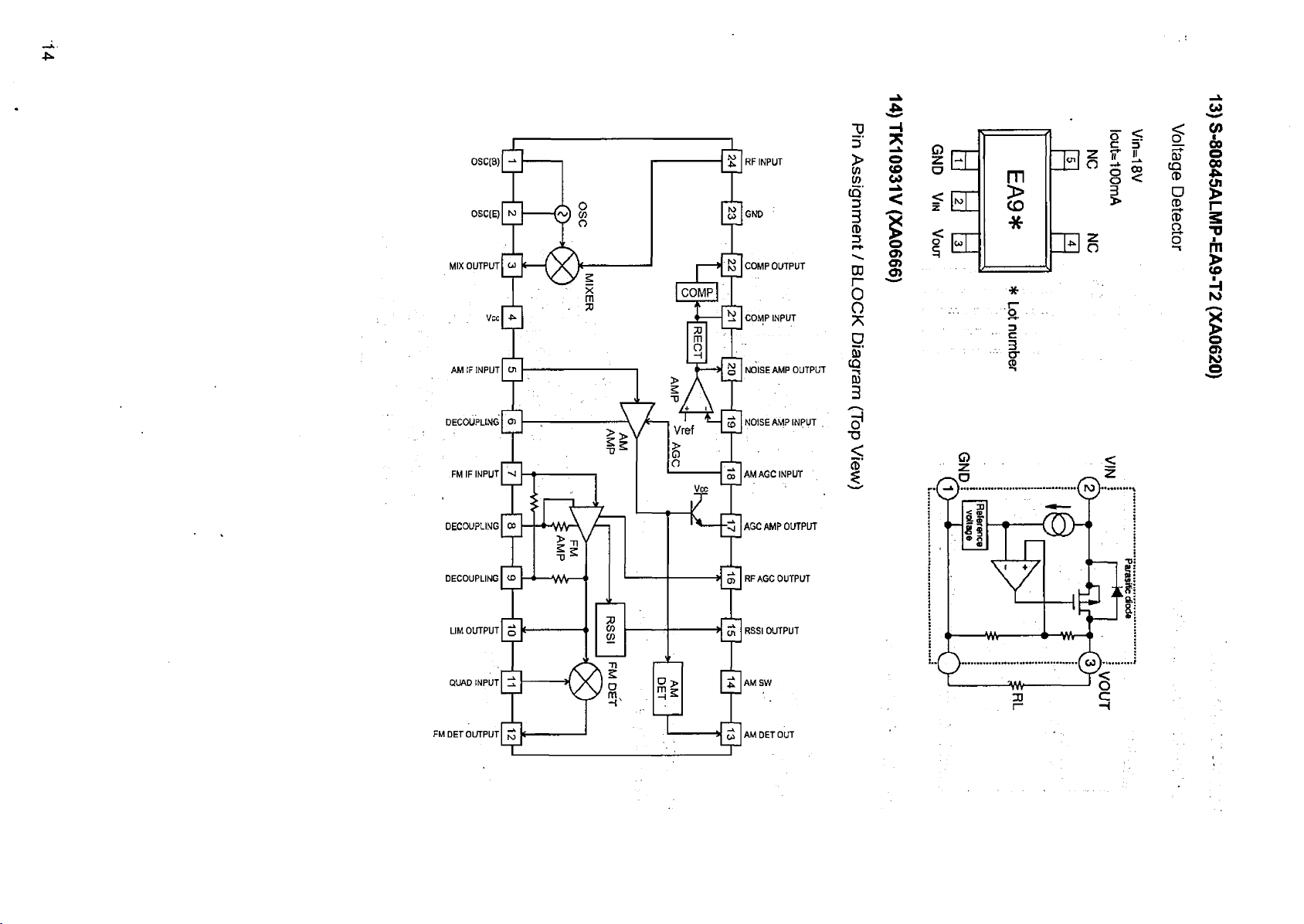

13) S-80845ALMP-EA9-T2 (XA0620)

14) TK10931V (XA0666)

............................................

.........................

.2

. 6

7

7

! 9

..9

.. 9

10

12

12

13

14

14

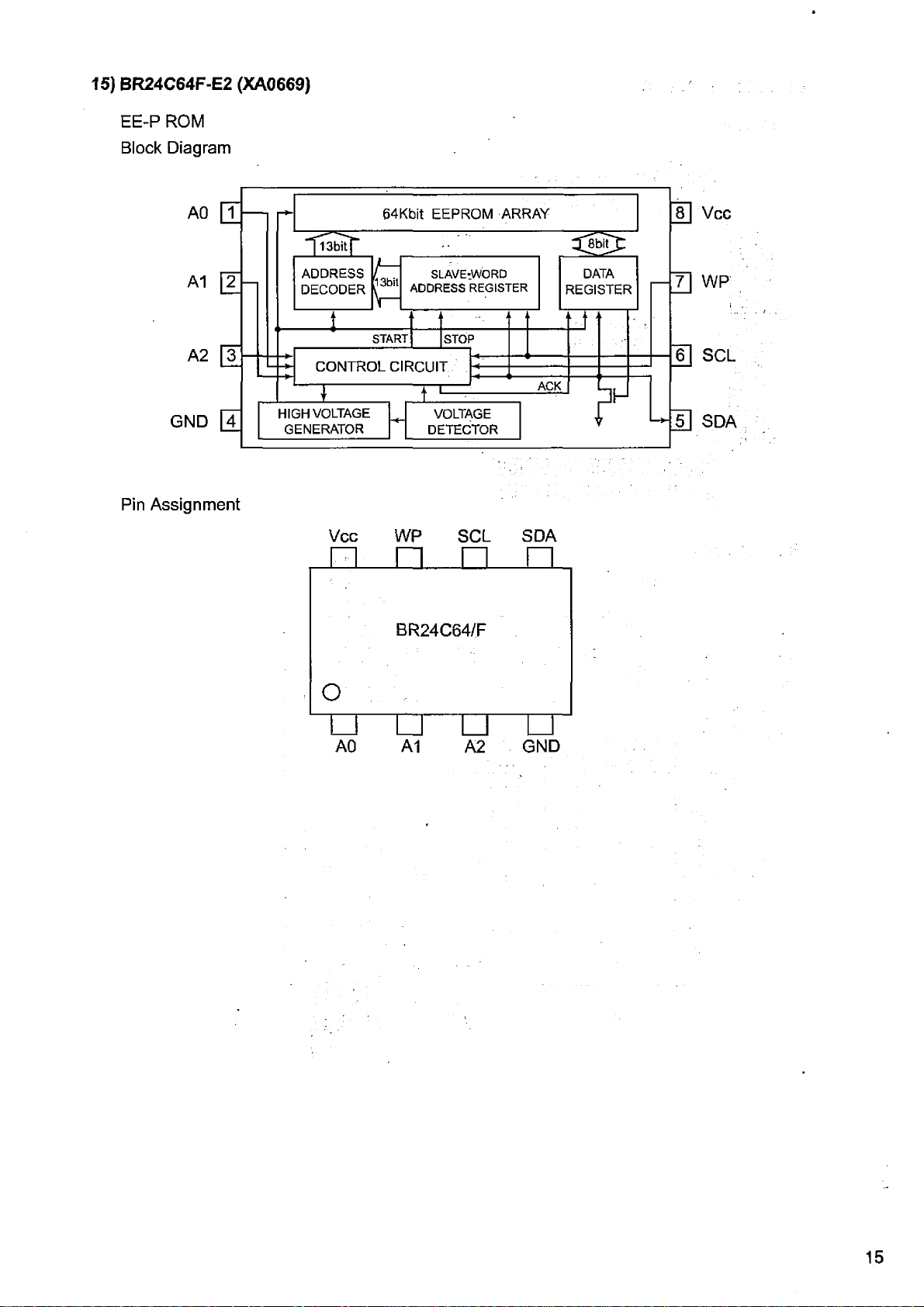

15) BR24C64F-E2 (XA0669).

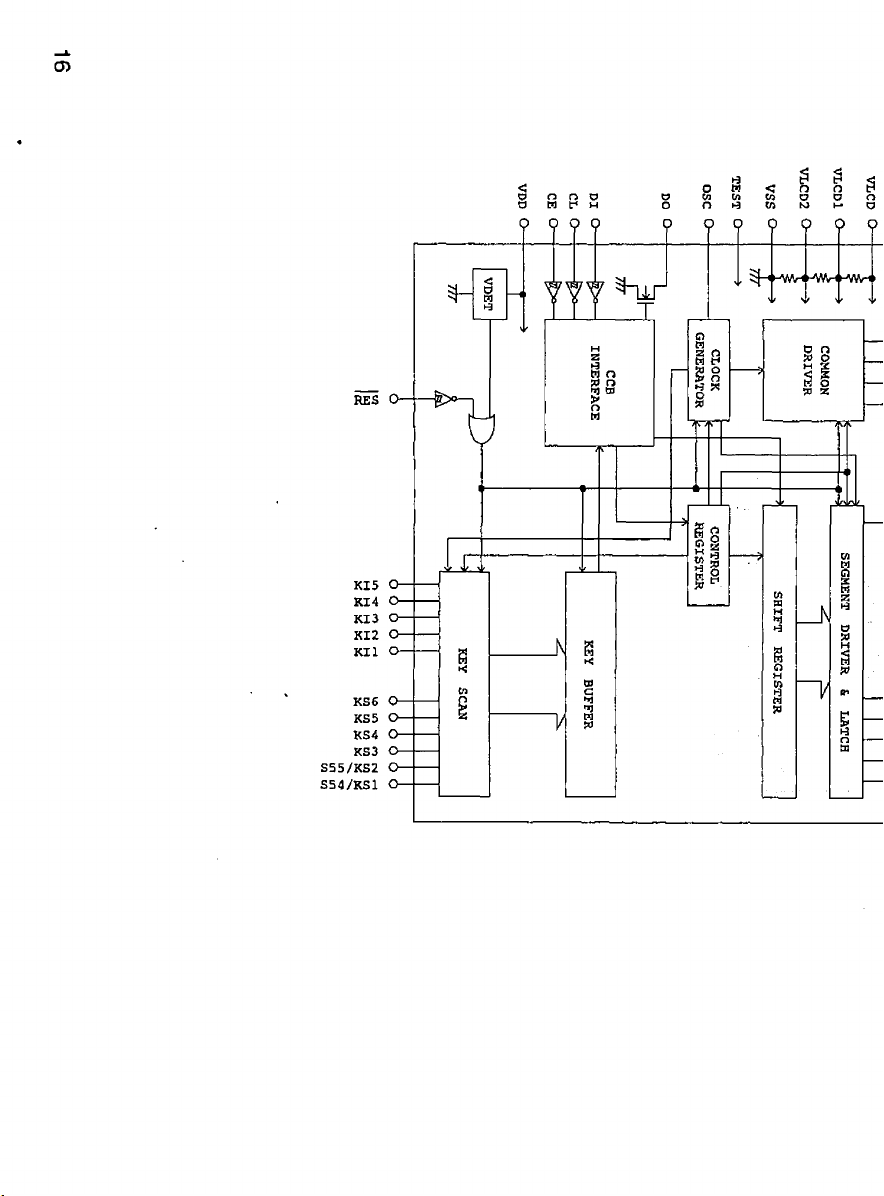

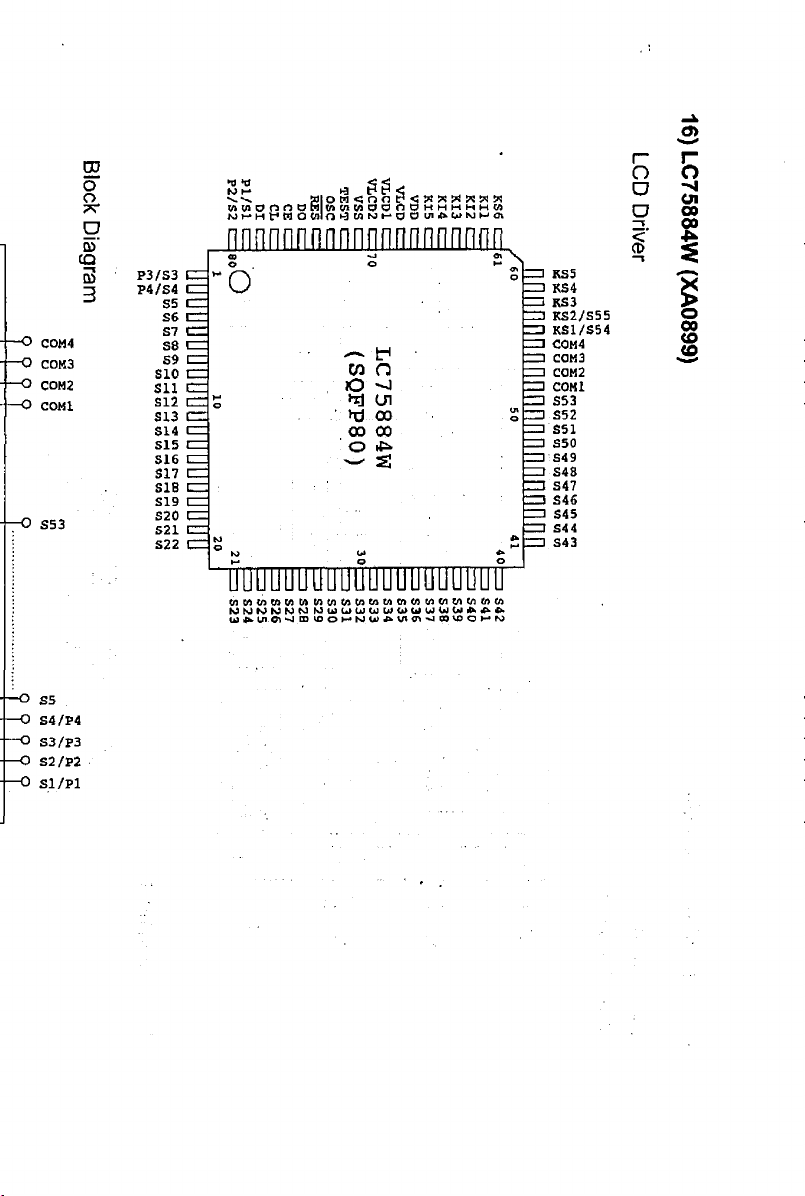

16) LC75884W (XA0899) ................

17) M51132FP ( X A 0 9 0 0 )

18) M38503M2H667FP (XA0914).......

19) M64076AGP (XA0915)

20) S-816A50AMC (XA0925)

21) NJM78M05DL1A (XA0947)

22) M30624FGPGP (XA1081/XA1082)

23) Transistor, Diode, and LED Outline Drawings.... 23-24

24) LCD Connection

EXPLODE D VIEW

1) Front View

2) Bottom View...................................................................2 7

PARTS LIST

Front Unit.......................................................................28

8

LED Unit

Main Unit.................................................................28-37

Mechanical Parts

Packing Parts

Accessories (Screw Set)..............................................37

ADJU S TME NT

1) Adjustment Spot

2) Adjustment Mode................

- 3) VHF Adjustment Specification....................................

4) UHF Adjustment Specification ...................................

5) VHF Test Specification

6) UHF Test Specification...............

PC BOARD VIEW

1) Front Side A

2) Front Side B ...................................................................44

3) Main Side A ...................................................................45

4) Main Side B ...................................................................46

FRONT SCHEMATIC D IAG R A M .............................. 47

MAIN SCHEM A TIC DIAG R AM ......................................48

FRONT BLOC K DIA G RA M

MAIN B L O CK D IA G R A M ................................................50

................................ 24-25

......................................................................

........................................................................

...................................

...................

...................................................................44

....................................

......

.....................

....................................

........

...........................................

........

..............

....................

.........................................................

.............................

............

...........................38

........................................39

.......................................

................................

...........................................

......

15

......

16

17

....... 17-18

.....

.........

19

20

......

.,.

......

20

20-22

26

28

37

40

41

42

43

49

37

ALINCO, INC.

Page 2

SPECIFICATIONS

1) GENERAL

Frequency coverage

DR-635T (U.S amateur)

DR-635E (European amateur)

Operating mode

Frequency resolution

Number of memory channels

Antenna impedance

Power requirement

Ground method

Current drain Receive

Transmit

Operating temperature

Frequency stability

Dimensions

Weight

87.500 - 107.995MHz (WFM RX)

108.000 - 135.995MHz (AM RX)

136.000 - 173.995MHz (RX)

144.000-147.995MHz (TX)

335.000 - 479.995MHz (RX)

430.000 - 449.995MHz (TX)

87.500 - 107.995MHz (WFM)

144.000 - 145.995MHz (RX, TX)

430.000 - 439.995MHz (RX, TX)

16K0F3E (Wide mode) 8K50F3E (Narrow mode)

5, 8.33, 10, 12.5,15, 20, 25, 30, 50,100kHz

20 0

50£} unbalanced

13.8V DC±15% (11.7 to 15.8V)

Negative ground

0.6A (Max.) 0.4A (Squelched)

11.0A

- 10 to 60°C

±2.5ppm

142 (w) x 40 (h) x 174 (d) mm

(w/o knobs)

Approx. 1.0kg

2) TRANSMITTER

Output power

Modulation system

Maximum frequency deviation

Spurious emission

Adjacent channel power

Modulation Distortion

Microphone impedance

High : 50W (VHF)

35 W(UHF)

Mid : 20W

Low : 5W

Variable reactance frequency modulation

±5kHz (Wide mode) ±2.5kHz (Narrow mode)

-60dB

-60dB

Lass than 3%

2kn

Page 3

3 ) R E C E IV E R

Sensitivity

Receiver circuitry

Intermediate frequency

-16dBu for 12dB SINAD

Double conversion superheterodyne

18‘ 21.7MHz 2nd 450kHz (VHF)

1st 45.1MHz 2nd 455kHz (UHF)

Squelch sensitivity

Selectivity (-6dB / -60dB)

Spurious and image rejection ratio

Audio output power

-18dBu

12kHz/24kHz

70dB

2.0W (80, 10% THD)

I Note : All specifications are subject to change without notice or obligation.

Page 4

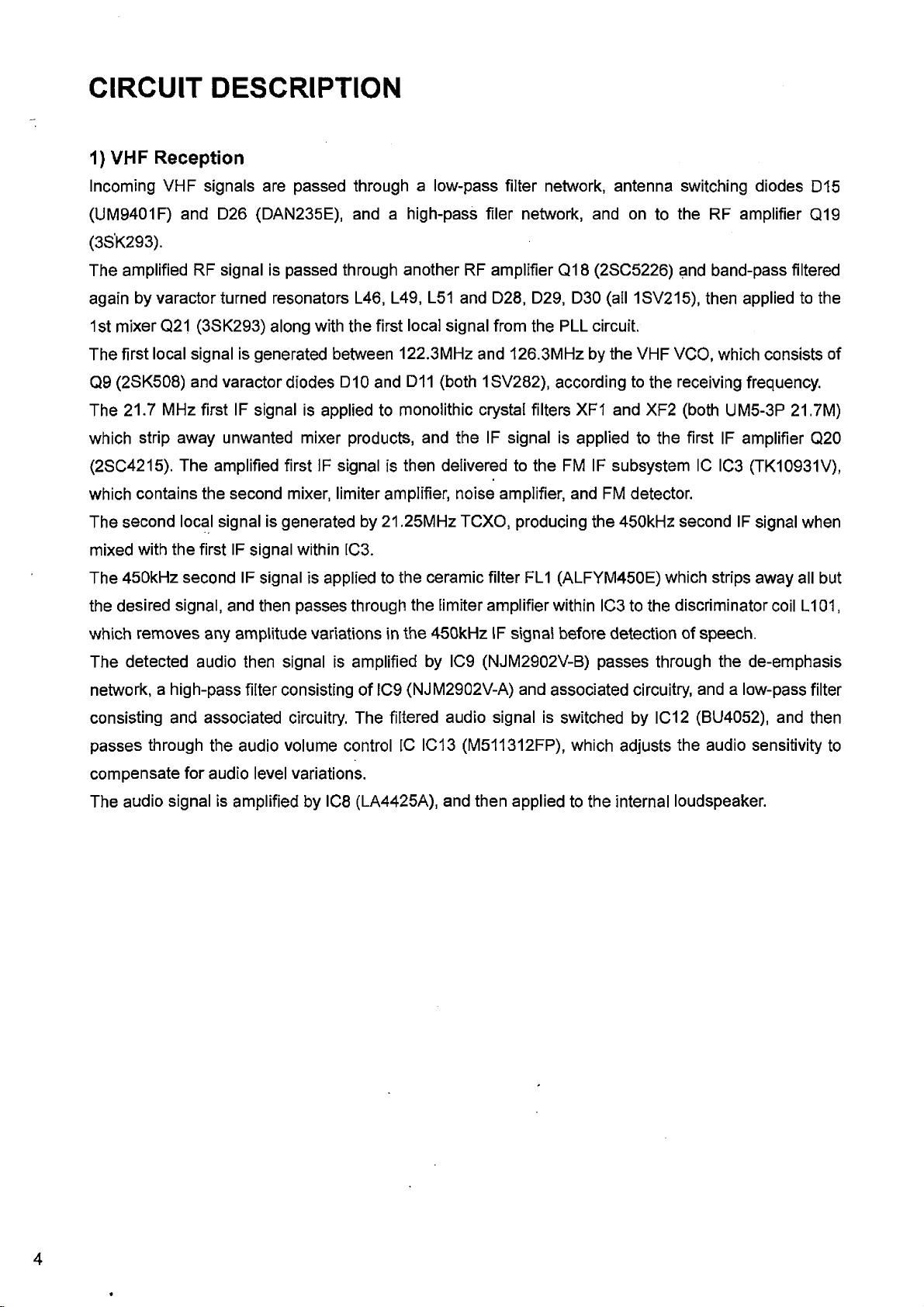

CIRCUIT DESCRIPTION

1 ) V H F R e c e p t io n

Incoming VHF signals are passed through a low-pass filter network, antenna switching diodes D15

(UM9401F) and D26 (DAN235E), and a high-pass filer network, and on to the RF amplifier Q19

(3SK293).

The amplified RF signal is passed through another RF amplifier Q18 (2SC5226) and band-pass filtered

again by varactor turned resonators L46, L49, L51 and D28, D29, D30 (all 1SV215), then applied to the

1st mixer Q21 (3SK293) along with the first local signal from the PLL circuit

The first local signal is generated between 122.3MHz and 126.3MHz by the VHF VCO, which consists of

Q9 (2SK508) and varactor diodes D10 and D11 (both 1SV282), according to the receiving frequency.

The 21.7 MHz first IF signal is applied to monolithic crystal filters XF1 and XF2 (both UM5-3P 21.7M)

which strip away unwanted mixer products, and the IF signal is applied to the first IF amplifier Q20

(2SC4215). The amplified first IF signal is then delivered to the FM IF subsystem IC IC3 (TK10931V),

which contains the second mixer, limiter amplifier, noise amplifier, and FM detector.

The second local signal is generated by 21.25MHz TCXO, producing the 450kHz second IF signal when

mixed with the first IF signal within 1C3.

The 450kHz second IF signal is applied to the ceramic filter FL1 (ALFYM450E) which strips away all but

the desired signal, and then passes through the limiter amplifier within IC3 to the discriminator coil L101,

which removes any amplitude variations in the 450kHz IF signal before detection of speech.

The detected audio then signal is amplified by IC9 (NJM2902V-B) passes through the de-emphasis

network, a high-pass filter consisting of IC9 (NJM2902V-A) and associated circuitry, and a low-pass filter

consisting and associated circuitry. The filtered audio signal is switched by IC12 (BU4052), and then

passes through the audio volume control IC IC13 (M511312FP), which adjusts the audio sensitivity to

compensate for audio level variations.

The audio signal is amplified by IC8 (LA4425A), and then applied to the internal loudspeaker.

Page 5

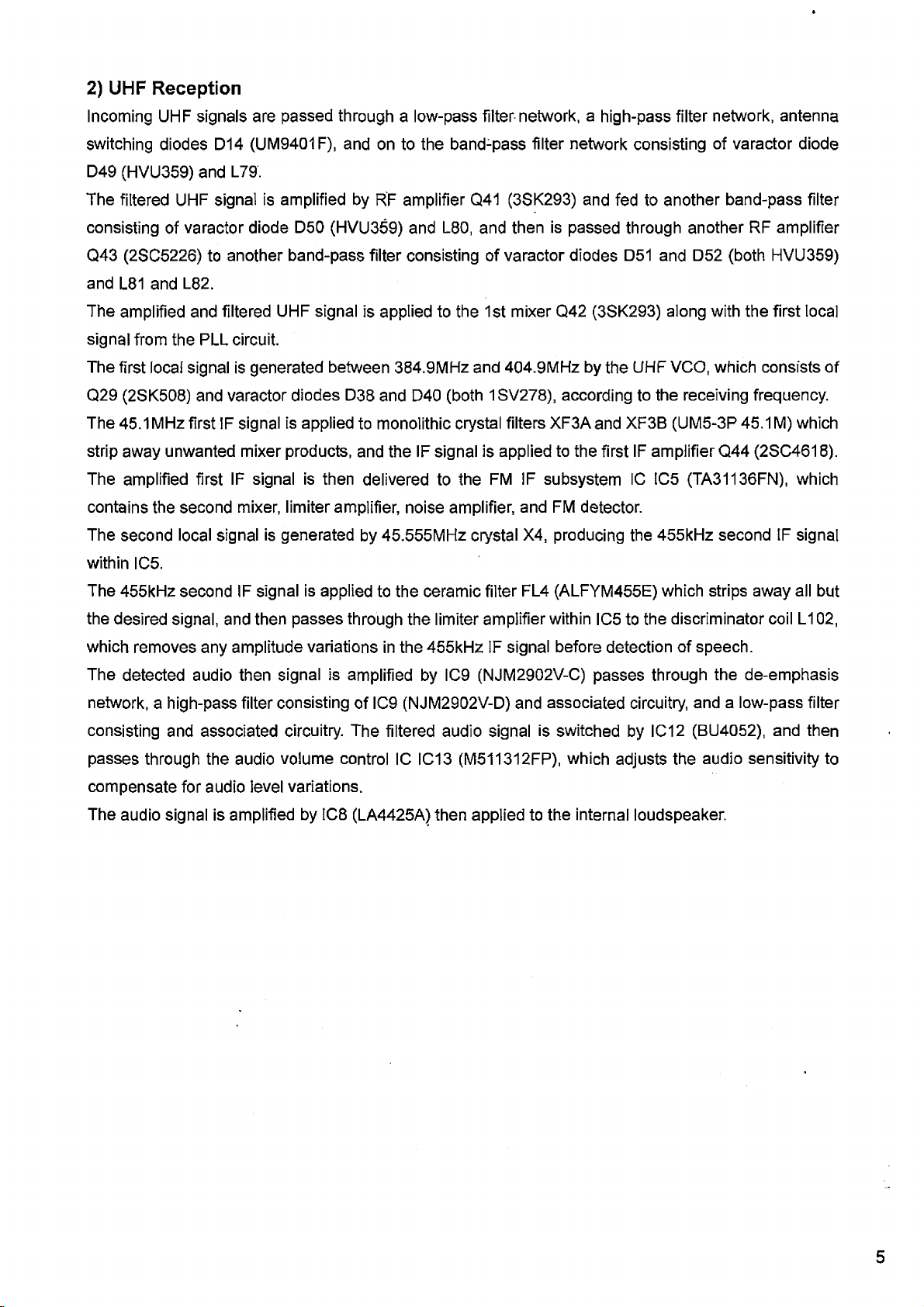

2 ) U H F R e c e p t io n

Incoming UHF signals are passed through a low-pass filter network, a high-pass filter network, antenna

switching diodes D14 (UM9401F), and on to the band-pass filter network consisting of varactor diode

D49 (HVU359) and L79.

The filtered UHF signal is amplified by R'F amplifier Q41 (3SK293) and fed to another band-pass filter

consisting of varactor diode D50 (HVU359) and L80, and then is passed through another RF amplifier

Q43 (2SC5226) to another band-pass filter consisting of varactor diodes D51 and D52 (both HVU359)

and L81 and L82.

The amplified and filtered UHF signal is applied to the 1st mixer Q42 (3SK293) along with the first local

signal from the PLL circuit.

The first local signal is generated between 384.9MHz and 404.9MHz by the UHF VCO, which consists of

Q29 (2SK508) and varactor diodes D38 and D40 (both 1SV278), according to the receiving frequency.

The 45.1 MHz first IF signal is applied to monolithic crystal filters XF3A and XF3B (UM5-3P 45.1M) which

strip away unwanted mixer products, and the IF signal is applied to the first IF amplifier Q44 (2SC4618).

The amplified first IF signal is then delivered to the FM IF subsystem IC ICS (TA31136FN), which

contains the second mixer, limiter amplifier, noise amplifier, and FM detector.

The second local signal is generated by 45.555MHz crystal X4, producing the 455kHz second IF signal

within IC5.

The 455kHz second IF signal is applied to the ceramic filter FL4 (ALFYM455E) which strips away all but

the desired signal, and then passes through the limiter amplifier within IC5 to the discriminator coil L102,

which removes any amplitude variations in the 455kHz IF signal before detection of speech.

The detected audio then signal is amplified by IC9 (NJM2902V-C) passes through the de-emphasis

network, a high-pass filter consisting of IC9 (NJM2902V-D) and associated circuitry, and a low-pass filter

consisting and associated circuitry. The filtered audio signal is switched by IC12 (BU4052), and then

passes through the audio volume control IC IC13 (M511312FP), which adjusts the audio sensitivity to

compensate for audio level variations.

The audio signal is amplified by IC8 (LA4425A) then applied to the internal loudspeaker.

5

Page 6

3 ) F M R e c e p tio n

Incoming FM signals are passed through a low-pass filter network, antenna switching diodes D15

(UM9401F) and D26 (DAN235E), and a high-pass filter network, and on the RF amplifier Q36

(2SC5066).

The amplified RF signal is passed through band-pass filtered L, C, then applied to the 1st mixer Q33

(2SC5066) along with the first local signal from the circuit.

The first local signal is generated between 86.7MHz and 118.7MHz by the FM VCO, which consists of

Q14 (2SC4808) and varactor diodes D23 and D25 (both 1SV282), according to the receiving frequency.

The 10.7MHz first IF signal is applied to ceramic filters FL3 and FL6 (both SFT10.7MAS) which strip

away unwanted mixer products, and the IF signal is applied to the first IF amplifier Q37 (2SC4618).

The amplified first IF signal is then delivered to the FM IF subsystem IC IC3 (TK10931V), limiter amplifier,

noise amplifier, and FM detector.

The 10.7MHz first IF signal is applied to the discriminator coil L53, which removes any amplitude

variations in the 10.7MHz IF signal before detection of speech.

4 ) V /V (V H F -V H F ) D u a l R e c e p t io n

During V & V operation, the incoming VHF "sub" band signal is passed through a low-pass filter network,

antenna switching diode D15 (UM9401F) and a high-pass filter network to the RF amplifier Q19

(3SK293).

The amplified RF signal is passed through a high-pass filter network, VHF "sub" RF amplifier Q31

(2SC5066), and a low-pass filter network, then is applied to the VHF "sub" first mixer Q32 (2SC5066)

along with the 45.1MHz VHF "sub" first local signal from the VHF "sub" VCO circuit.

The VHF "sub" first local signal is generated between 189.1 MHz and 193.1MHz by the VHF "sub" VCO

Q38 (2SC4080).

The 45.1MHz VHF "sub" second IF signal is applied to the UHF receiving circuit.

The VHF "sub" signal is amplified, filtered, and demodulated, etc., by the UHF "main" receiving circuit,

described previously.

5 ) U /U (U H F -U H F ) D u a l R e c e p t i o n

During U & U operation, the incoming UHF "sub" band signal is passed through a high-pass and a

low-pass filter networks, antenna switching diode D14 (UM9401F), and another high-pass filter network

to the RF amplifier Q51 (2SC5066).

The amplified RF signal is passed through a low-pass filter network, UHF "sub" RF amplifier Q49

(2SC5066), and a low-pass filter network, then is applied to the UHF "sub" first mixer Q52 (2SC5066)

along with the 21 .7MHz UHF "sub" first local signal from the UHF "sub" VCO.

The UHF "sub" first local signal is generated between 408.3MHz and 428.3MHz by the UHF "sub" VCO

Q13 (2SC5066).

The 21.7MHz UHF "sub" second IF signal is applied to the VHF receiving circuit.

The UHF "sub" signal is amplified, filtered, and demodulated, etc., by the VHF "main" receiving circuit,

described previously.

Page 7

6 ) V H F S q u e lc h C o n t r o l

When no VHF carrier is being received, noise at the output of the detector stage in IC3 is amplified and

band-pass filtered by the noise amp section of IC3, then passes through the noise adjust VR (VR8) to

CPU. The resulting DC voltage is applied to pin 88 of main CPU IC19 (M30624FGPGP), which

compares the squelch threshold level to that which set by the front panel VHF SQL knob.

While no carrier is received, pin 55 of IC19 remains "high" turning on the squelch switch Q108

(DTC363EK) to disable audio output from the speaker.

7 ) U H F S q u e lc h C o n t r o l

When no UHF carrier is being received, noise at the output of the detector stage in ICS is amplified and

band-pass filtered by the noise amp section of ICS, then passes through the noise adjust VR (VR9) to

CPU.

The resulting DC voltage is applied to pin 90 of main CPU IC19, which compares the squelch threshold

level to that which set by the front panel UHF SQL knob.

While no carrier is received, pin 56 of IC19 remains "high" turning on the squelch switch Q109

(DTC363EK) to disable audio output from the speaker.

8 ) T r a n s m it S ig n a l P a t h

The speech signal from the microphone passes through the MIC jack CN601 to AF amplifier IC601

(M5218FP) on the FRONT UNIT

The amplified speech signal is subjected to amplitude limiting by IC601 (M5218FP), then passes through

the front interface jacks CN602 and CN2 to MAIN UNIT

On the MAIN UNIT, the speech signal passes through the audio mute switch IC7 (TC4066F), MIC gain

control VR5 and buffer amplifier IC1 (NJM2902V-B) and a low-pass filter network at IC1 (NJM2902V-A)

to deviation control VR3 (for VHF TX audio) or VR4 (for UHF TX audio).

9 ) V H F T r a n s m it S ig n a l P a th

The adjusted speech signal from VR3 is delivered to VHF VCO Q9, which frequency modulates the

transmitting VCO D6 (1SV278).

The modulated transmit signal passes through buffer amplifier Q7 (2SC5066), a low-pass filter network,

and another buffer amplifier Q3 (2SC5226) to another low-pass filter network.

The filtered transmit signal is applied to the Pre-Drive amplifier Q2 (2SK3074) and Drive amplifier Q1

(2SK2975), then finally is amplified by Power amplifier Q4 (RD70HV1) up to 50 Watts.

This three-stage power amplifier’s gain is controlled by the APC circuit.

The 50 Watts RF signal passes through a low-pass filter network, antenna switch D1 and D71 (both

UM9401F), and another low-pass filter network, and then is delivered to the ANT jack.

7

Page 8

1 0 ) U H F T r a n s m it S ig n a l P a th

The adjusted speech signal from VR4 is delivered to UHF VCO Q29, which frequency modulates the

transmitting VCO D35 (1SV278).

The modulated transmit signal passes through buffer amplifier Q28 (2SC5066) to a high-pass filter

network.

The filtered transmit signal is applied to the Pre-Drive amplifier Q2 (2SK3074) and Drive amplifier Q1

(2SK2975), then finally is amplified by Power amplifier Q4 (RD70HV1) up to 35 Watts.

This three-stage power amplifier's gain is controlled by the APC circuit.

The 35 Watts RF signal passes through a high-pass filter network, antenna switch D12 and D13 (both

UM9401F), a low-pass filter and a high-pass filter networks, and then is delivered to the ANT jack.

1 1 ) V H F T x A P C C ir c u it

A portion of the power amplifier output is rectified by D8 (MA4S713), D9 (MA4S713) and Q12 (2SC4081),

and then delivered to APC IC1 (NJM2902V-D) as a DC voltage, which is proportional to the output level

of the power amplifier.

The APC IC1 compares the rectified DC voltage from the power amplifier and the reference voltage from

the main CPU IC19, producing a control voltage for the Automatic Power Controller Q8 (RN2107) and

Q11 (RN1107) which regulates supply voltage to the Pre-Drive amplifier Q2, Drive amplifier Q1, and

Power amplifier Q4, so as to maintain stable output power under varying antenna loading conditions.

1 2 ) U H F T x A P C C ir c u i t

A portion of the power amplifier output is rectified by D9 (M4S713), D22 (MA4S713) and Q12 (2SC4081),

and then delivered to APC IC1 (NJM2902V-D) as a DC voltage, which is proportional to the output level

of the power amplifier.

The APC IC1 compares the rectified DC voltage from the power amplifier and the reference voltage from

the main CPU IC19, producing a control voltage for the Automatic Power Controller Q8 (RN2107) and

Q11 (RN1107) which regulates supply voltage to the Pre-Drive amplifier Q2, Drive amplifier Q1, and

Power amplifier Q4, so as to maintain stable output power under varying antenna loading conditions.

1 3 ) V H F P T T c ir c u i t

When the PTT switch is pressed, pin 4 of front CPU IC604 (M38503M) goes "low" which sends the

"PTT" command to the main CPU IC19.

When it receives the "PTT" command, pin71 of IC19 goes "high" to control local switch D5 (1SV306),

filter switches D2 and D3, Tx switch D17 (DAN235E), and APC switches Q8 and Q11, which activates

the VHF Tx circuit.

Meanwhile, pin 69 of !C19 goes "low" which disables the VHF Rx circuit.

Page 9

1 4 ) U H F P T T c ir c u it

When the PTT switch is pressed, pin 4 of front CPU IC604 (M38503M) goes "low" which sends the

"PTT" command to the main CPU IC19.

When it receives the "PTH command, pin72 of IC19 goes "high" to control local switch D76 (1SV306),

filter switches D74 and D75, Tx switch D17 (DAN235E) and APC switches Q8 and Q11, which activates

the UHF Tx circuit.

Meanwhile, pin 70 of IC19 goes "low" which disables the UHF Rx circuit. _

1 5 ) V H F P L L

A portion of the output from the VHF VCO Q9 (2SK508) passes through buffer amplifiers Q7 (2SC5066)

and Q5 (2SC5066) to the programmable divider section of the PLL IQ IC2 (M64076AGP), which divides

the frequency according to the frequency dividing data from the main CPU IC19.

It is then sent to the phase comparator.

The 21.25MHz frequency of the reference oscillator circuit, made up of TCXO X1, Is divided by the

reference frequency divider section of IC2 into 4250 or 3400 parts to become 5kHz or 6.25kHz

comparative reference frequencies, which are utilized by the phase comparator.

The phase comparator section of IC2 compares the phase between the frequency-divided oscillations

frequency of the VCO circuit and comparative frequency, and its output is a pulse corresponding to the

phase difference.

This pulse is integrated by the charge pump and loop filter of IC2 into a control voltage (VCV) to control

the oscillation frequency of the VHF VCO Q9.

1 6 ) U H F P L L

A portion of the output from the UHF VCO Q29 (2SK508) passes through buffer amplifier Q28

(2SC5066) and Q39 (2SC5066) to the programmable divider section of the PLL IC IC2 (M64076AGP),

which divides the frequency according to the frequency dividing data from the main CPU IC19.

It is then sent to the phase comparator.

The 21.25MHz frequency of the reference oscillator circuit, made up of TCXO X1, is divided by the

reference frequency divider section of IC2 into 4250 or 3400 parts to become 5kHz or 6.25kHz

comparative reference frequencies, which are utilized by the phase comparator

The phase comparator section of IC2 compares the phase between the frequency-divided oscillations

frequency of the VCO circuit and comparative frequency, and its output is a pulse corresponding to the

phase difference.

This pulse is integrated by the charge pump and loop filter of IC2 into a control voltage (VCV) to control

the oscillation frequency of the UHF VCO Q29.

1 7 ) P o w e r - o n C ir c u it

When the POWER switch is turned on, pin 18 of man CPU IC19 goes "low".

When pin 18 of IC19 goes "low", pin 79 of IC19 goes "high" to activate the power switches Q63

(2SB1386) and Q74 (2SC4081), which supply the DC power to the radio.

Page 10

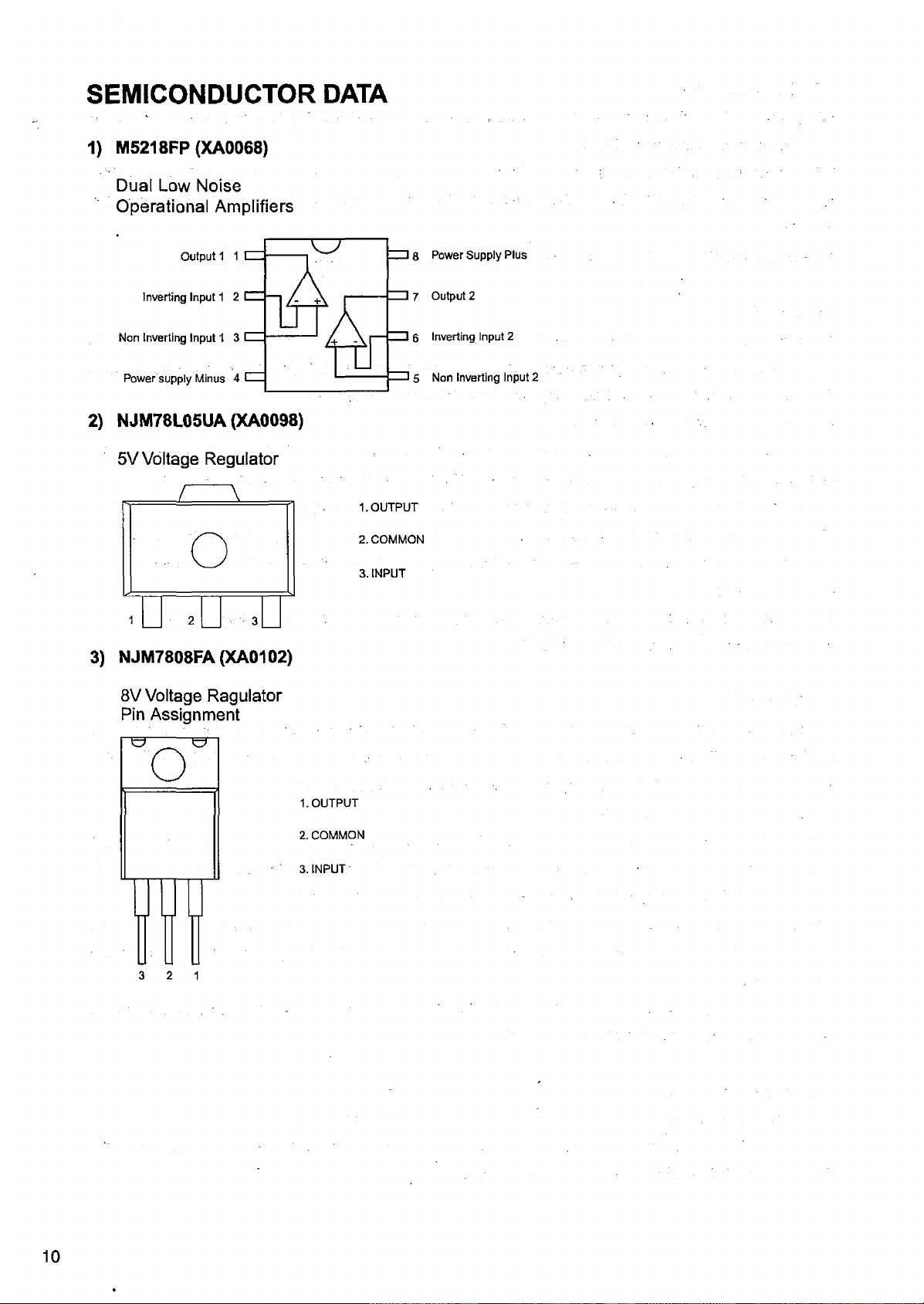

SEMICONDUCTOR DATA

1) M 5 2 1 8 F P ( X A 0 0 6 8 )

Dual Low Noise

Operational Amplifiers

Output 1 1

Inverting Input 1 2

Non Inverting Input 1 3

Power supply Minus 4

2 ) N J M 7 8 L 0 5 U A (X A 0 0 9 8 )

5V Voltage Regulator

/ \

1

___

2

___

3 1

3 ) N J M 7 8 0 8 F A (X A 0 1 0 2 )

8V Voltage Ragulator

Pin Assignment

Power Supply Plus

Output 2

Inverting Input 2

Non Inverting Input 2

1. OUTPUT

2. COMMON

3. INPUT

o

3 2 1

1. OUTPUT

2. COMMON

3. INPUT'

10

Page 11

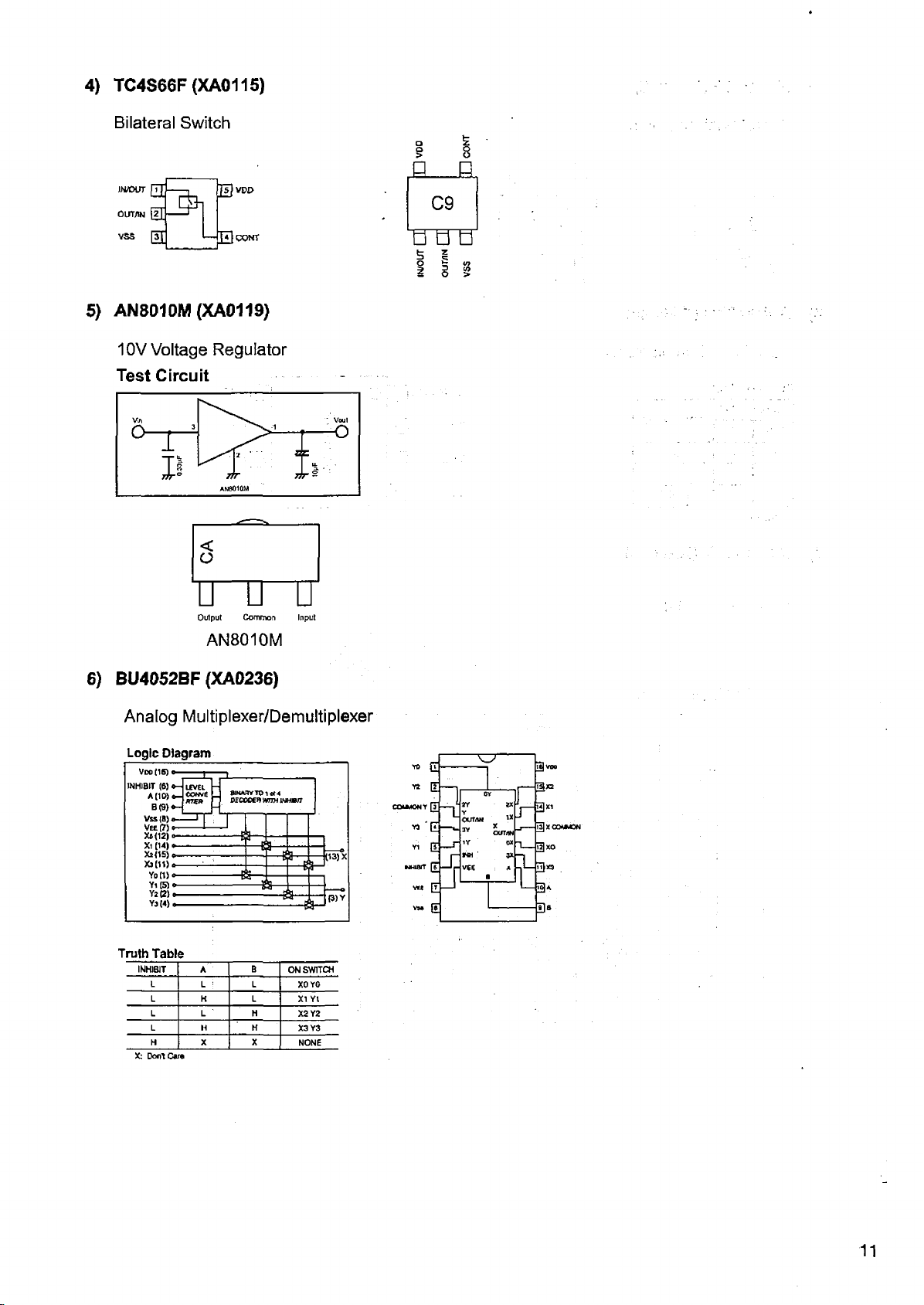

4) TC4S66F (XA0115)

Bilateral Switch

1 MDUT [TJ

OUTAN {H

3 » i

vss [äjj

5 ) A N 8 0 1 0 M (X A 0 1 1 9 )

L.

H)VDD

T*1co n t

10V Voltage Regulator

Test Circuit

§ 8

f l

_ _ _

C9

□ □ □

B l

U " □ U

Output Common Input

AN8010M

6) B U 4 0 5 2 B F (X A 0 2 3 6 )

Analog Multiplexer/Demultiplexer

Logic Diagram

Voo (16) o-

1NHIBIT (6) o-

Truth Table

INHIBIT A

LEVEL

CONVE

A (10) o-

STE»

B (9)

VS S(8) o-

Vee (7) ®-

Xo(12) »-

Xt (14) -

X2(1S) »-

Xs(11) «-

Yo(1)«-

Yi(5)o-

Y2(2) e-

YS (4) a-

L

L K

L L '

L H

H

L !

X

B

L

L

H

H

X

ON SWITCH

XO YO

XI Y1

X2Y2

X3 Y3

NONE

(13) X

¥0 ¡7

Y1 |T

COW ONY [T

« E

vi d

inhibit |T

vu [7

V » {?

¡3 V»

¡3»

¡3*’

tä]X00MM0N

«Ixo

‘IL

n i»

3

T|b

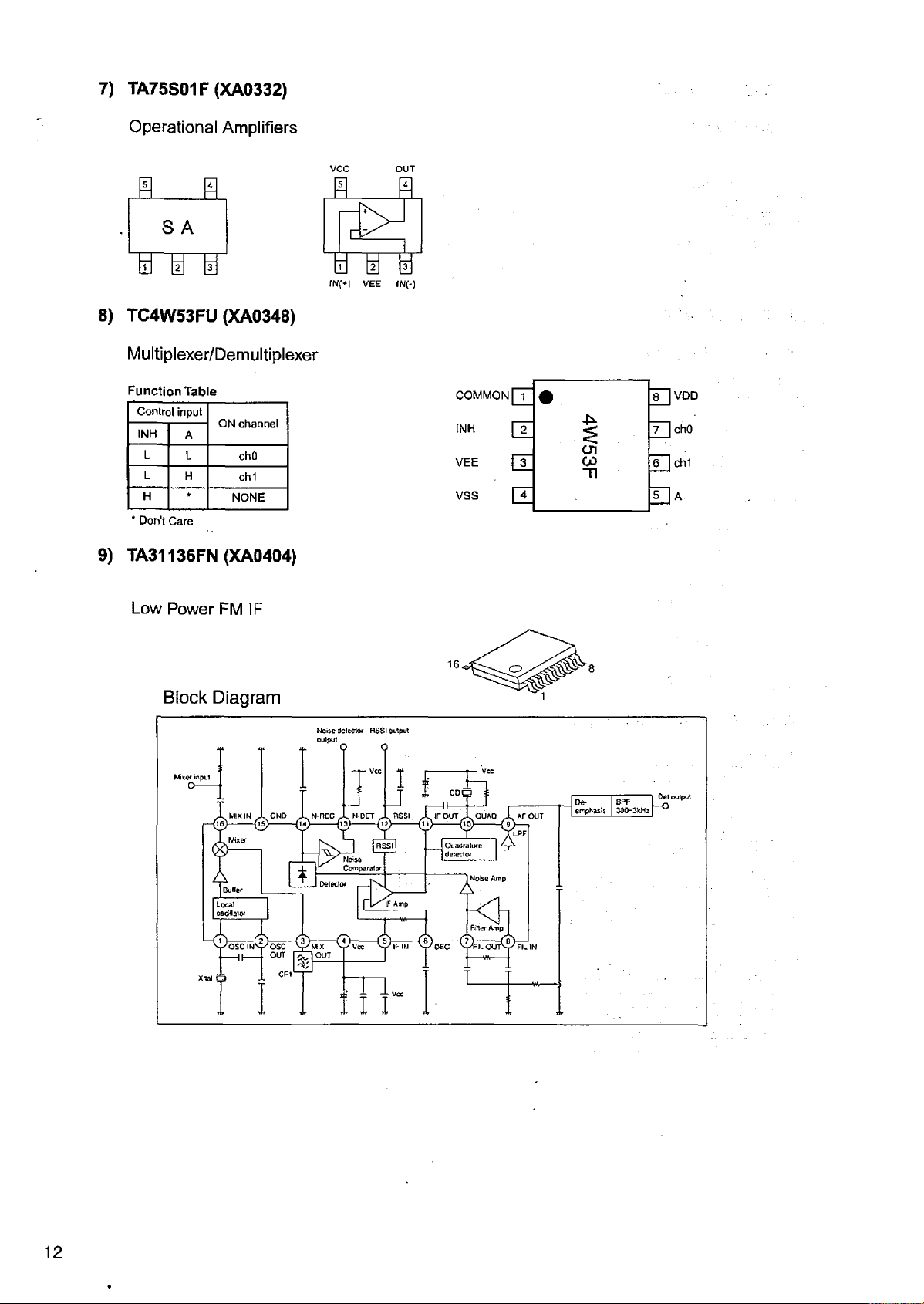

Page 12

7) TA75S01F (XA0332)

Operational Amplifiers

i

____

a

s

____

a

S A

8) T C 4 W 5 3 F U (X A 0 3 4 8 )

Multiplexer/Demultiplexer

Function Table

Control input

INH

L

L

H

* Don't Care

9) T A 3 1 1 36 F N (X A 0 4 0 4 )

Low Power FM IF

A

L

H

*

ON channel

chO

ch1

NONE

> j

r

JN ( +) VE E IN (-)

I

COMMON |~T

INH

VEE

VSS

IZ

Cl

E

•

-P»

cn

CO

T |

~B | VDD

7~~| chO

6 | ch1

E a

Block Diagram

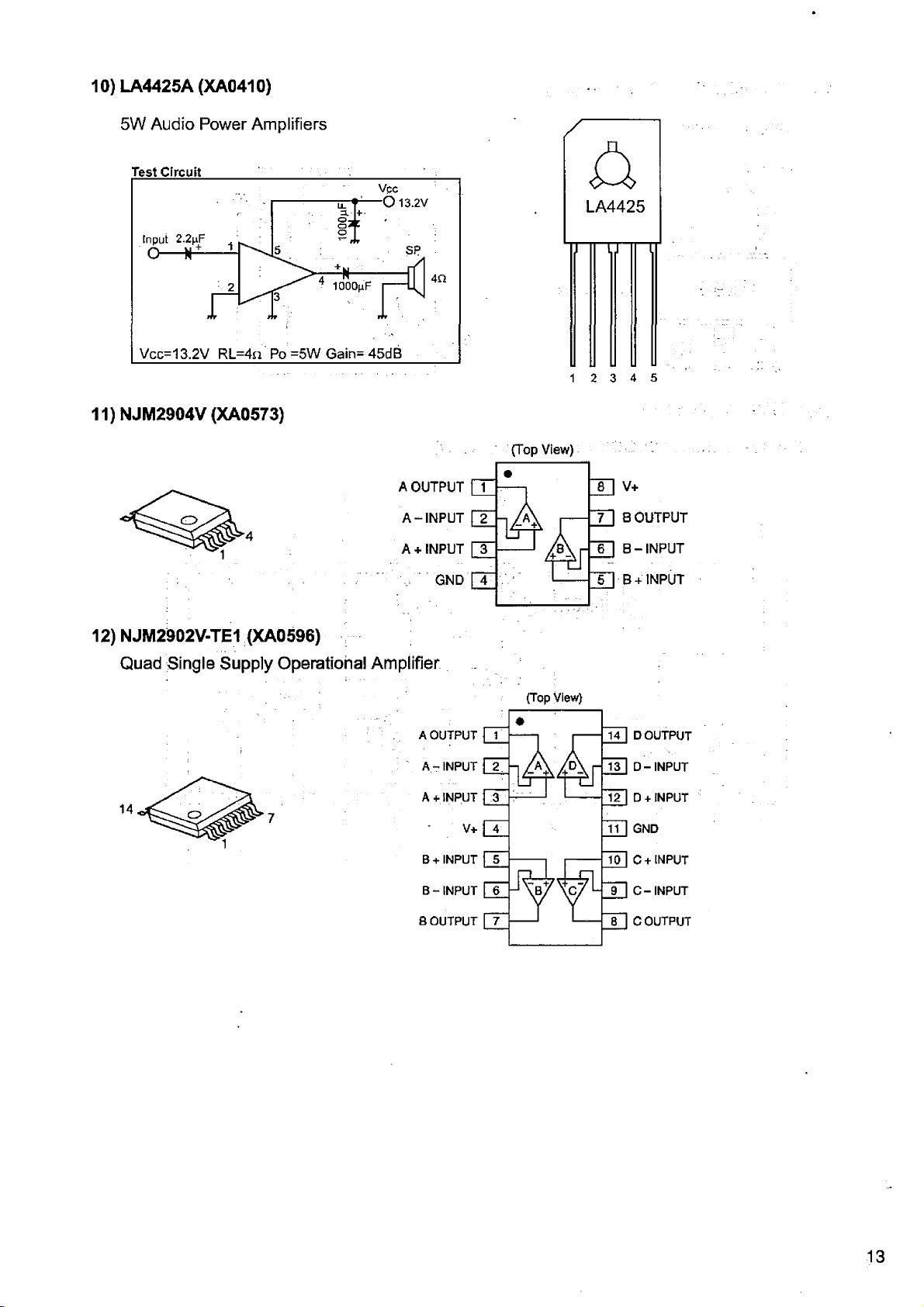

Page 13

10) LA442 5A (XA0410)

5W Audio Power Amplifiers

Test Circuit

11) NJM2904V (XA0573)

1 2 3 4 5

(Top View)

12) NJM2902V-TE1 (XA0596)

Quad Single Supply Operational Amplifier

A OUTPUT □

A -IN P U T \ j T _

A + INPUT [~3~

GND [ T

1 2 V+

T "1 B OUTPUT

6 ] B - INPUT

X I B + INPUT

(Top View)

141 DOUTPUT

U1 D- INPUT

~12l D + INPUT

TTI GND

l0 l C + INPUT

T"1 C-INPUT

~T| C OUTPUT

Page 14

OSC{B)

OSC(E)

MIX OUTPUT

AM IF INPUT

£ RF INPUT

GND

COMP OUTPUT

COMP INPUT

NOISE AMP OUTPUT

CQ

CQ

TJ

u'

>

Cfl

to

3

3

CD

3

Ft

w

l~

O

o

□

S'

£

3

H

*

0

CD

w

<

1

o

o>

o

■£

*

3

C

3

cr

(0

CQ

I

r-^

CD

CD

o

CD

CD

&

O

13) S-80845ALMP-EA9-T2 (XA0620)

DECOUPLING

FM IF INPUT

DECOUPLING

DECOUPLING

LIM OUTPUT

QUAD INPUT

FMDET OUTPUT

NOISE AMP INPUT

AMAGC INPUT

AGC AMP OUTPUT

RFAGC OUTPUT

RSSI OUTPUT

—V.

AW DETOUT

ca

1?

TJ

CD

<

Page 15

15) BR24C64F-E2 (XA0669)

EE-P ROM

Block Diagram

AO 1

A1 2

A2 3

GND 4

Pin Assignment

13bit

ADDRESS

DECODER

CONTROL CIRCUIT

HIGH VOLTAGE

GENERATOR

Vcc WP SCL SDA

64Kbit EEPROM ARRAY

t ~

,13bit

START

S L A V E -W O R D

A D D R E S S R E G I S T E R

STOP

E E

VOLTAGE

DETECTOR

BR24C64/F

AC K

DATA

REGISTER

H

?

8 Vcc

71 WP

6 SCL

5 SDA

o

u

AO

A1 A2

U

GND

15

Page 16

O)

RES

KI5

KI4

KI3

KI2

KI1

KS6

KS5

KS4

KS3

S55/KS2

S54/KS1

Page 17

16) LC75884W (XA0899)

s 53

CQ

to

o

o

Q)

Q)

3

4 í S <

Wjo

iWtnCaWOOOÖHHMHH«

Knln^MNHOaUI^^MHO)

n n n n n n n n n n n n o n m m n n n

UU UU UU UU UU UU UU UU 'ÏÏUU U

MMWOTWwt/iwwwwMmt/ícnMWWWw

MKIMMMM MUUIdUUUUU UU»» «.

U^UlOl'jm'ÛOHNWÂUim'JOlÛOHW

KS5

KS4

KS3

KS2/S55

KS1/S54

COM4

COM3

COM2

COMI

S53

S52

S51

S50

S49

S48

S47

S46

S45

S44

S43

O

O

0

1

Page 18

17) M51132FP (XA0900)

2ch Electronic Volume

Ref. supply out [ T

Filter [2

NC [T

g n d [T

Volume 1 cont. [T

Noise cont. [T

Volume 2 cont. \T_

VCA SW |T

18) M38503M2H667FP (XA0914)

Front CPU

Vcc

V ref

AVss

P44/INT3/PW M

P43/INT2/SCMP2

P42/INT1

P4i/IN To

P4o/C NT R i

P27/CN TR o/S rdvi

P26/SCLK

P25/Tx D

. P24/RxD

P23

.........P22

CNVss

P2i/Xcin

P2q/Xco ut

RESET

XlN

XOUT

Vss

P3o/ANo

P31/AN1

P 32/AN 2

P 33/AN 3

P34/AN4

P00/SIN2

P0l/SOUT2

P02/SCLK2

P03/SRDV2

P04

P05

P06

P07

P1o/(LEDo)

P li/( L E D i)

P12/(LED2)

P13/(LED3)

P14/(LED4)

P15/(LED5)

P16/(LED6)

P17/(LED7)

Page 19

Terminal Function of Front CPU

No. Pin Name Function I/O Logic Description

1

Vcc

2 Vref

3 Avss

4 P44 PTT I

P43 RE1 I Pulse Dial (rotary encoder) input

5

6 P42 UP I Activ iow

7 P41 D OW N I Activ low Key input (D O W N )

8

P40

9 P27

10 P26 H/L I

11 P25/TxD RXD1 I

12 P24/RxD TXD1

13 P23 TS /D CS

14 P22 MH z I Activ low

15 CNVss

16 P21 CALL I

17 P20

RES E T RES E T

18

19 Xin

20 Xout X OU T

21 Vss

22 P17 V/M

23 P16

24 P15 GREEN

25 P14

26 P13 MRLED

27 P12 SRLED

28 P11 DIM1 0

P10 DIM2 0

29

30 P07

P06

31

32 P05

33 P04 CE O

34 P03

35 P02 DI 0

P01 MUTE

36

37 P00 R E2

P34/AN 4

38

39 P33/AN3

P32/AN 2

40

41 P31/AN1 M VR I

42 P30/AN0 SVR

VCC

VR E F

AVSS

Activ low

FUNC I

SQL I Activ low

CNVS S

BAND I

XIN I Pulse

GND

RED 0

TXLED

DO I Pulse Data input for LCD driver IC

CL O

Activ low

Activ low

Pulse Serial Com munication port for Main CPU

Pulse Serial Com munication port for Main CPU

O

Activ low

I

Activ low

Activ low

Activ low

I

0

I

Activ low

Activ high

Activ high

O

Activ high

O

Activ high MAIN RX LED O N /O FF

O

Activ hiqh

0

Activ high

Activ high

Activ high

Pulse

Pulse

0

Activ high

I Dial (rotary encoder) input

A/D

l A /D

PTT key input

Key input (UP)

Key input (FUN C )

Key input (SQ L)

Key input (H/L)

Kev input (TS/DCS)

Kev input (M Hz)

Key input (CALL)

Key input (BAND)

Reset input

CPU clock input

CPU clock output

Key Input (UP)

Lighting color O N/OFF (RE D )

Lightinq color ON /OF F (YELLOW)

TX LED ON /O FF

SUB RX LED ON /O FF

Dommer control 1

Dimmer control 2

Strobe for LCD driver IC

Clock output for LCD driver IC

Data output for LCD driver IC

-

MAIN volume voltage input

SUB volume voltage inpput

Page 20

19) M64076AGP (XA0915)

Dual PLL Synthesizer

Equivalent Circuit

F in 2 ^ 5 ) -)

-------

SW

T

SW

1/6 4, 65

2 mod ules

presc aler

Parameter

Power supply voltage

Symbol Condition

Vcc

LPF supply voltage VF

Local oscillator input level Vin

Local oscillator input frequency

Xin input level

Fin

Vxin

Xin input frequency Fxin

— Data latch (1 7bit)

Lo cal 2

progra m m a ble divid er

il— D a ta latch (16bl1)

Fin=80-520MHz

Vin—lOdBm

Fin=80~520MHz

Vin—20—4dBm

Vcc=2.7~5.5V

Vcc=2.7-5.5V

Fxin=10-25MHz

Sine wave

Vcc=2.7-5.5V.

Vxin=Q.4-1.4Vp-p

Min.

2.7

-

-20

80

0.4

to

Typ. Max.

5.5

-

9 12

•4 :

•

520

-

1.4

-

25

Unit

V

V

dBm

MHz

Vp-p

MHz

(?)— <Ä M ^-

XBo

Xout(l8>

Xin(Í5>

in 1( 6 )

SÍ0 -

C P S ( 3 ) -

--------

Refere n ce fre que ncy 2

program m able divid er

osc

sw :

[ a M ^ > -Fin

SW

1/2

divider

1/64, 65

2 modulus

presc aler

Refere n ce frequ e ncy 1

pro gra m m a ble divid er

"— D ata latch (1 6bit)

Lo cal 1

pro gra m m a ble d iv id er

< '— D a ta latch (17 bit)

11— D ata latch (6bit)

B U £ >

-------

(ÍÍ) G N D

(l7 )O P 2

21 bit shift resistor

21 bit pulse c oun ter

R S T

GND

19

Page 21

20) S-816A50AMC (XA0925)

Voltage Regulator

Top View

5

B

____

B .

4

No.

1 EXT

2

3 ON/OFF

B B B

1 2 3

4 VIN

5 VOUT

21) NJM78M05DL1A (XA0947)

Terminal

VSS

-T 1 - ■

Voltage Regulator

1.INPUT

2.GND

3.OUTPUT

22) M30624FGPGP (XA1081/XA1082)

Main CPU

= Jff iass aaaa a £ » . .........

p g p g Q ? < i| < ^ < 5' l i S S ii S i i

S t o S k O '1, S n ? 3 ! a f . ii i 3 o i-

Û.Û.Q_&,(X,Û-ILÛ-Q_a_û_Û_Û_>0_>tl,[XQ,[rnfc{LÛ_Q_CL

M M tM M IH H M iM

E i z n i m n i s

PI2/D10 ■

P11/03 ■

P1tt/Da ■

P07/D7

P0e/0« ■

P05/Û5 -

POVEu '

P03/t>3 -

PÛ2/D2 -

PO1/D1 -

PCWDo -

P10T/AN7/Kla-

P1 CtefANtiKI? -

PI Os/AN s/Kh ■

P1ÛVAN4-K10 ■

PKh/ANa■

P10Z/AN2 -

P1 0i/AN t ■

AVss ■

PIOtfANo ■

Vhef "

AVcc "

P97/AOtooîS»j4 "

P9&'ANEX1/Sout4 '

P96/ANE X0/CLK4 '

-

o

M30624FGPGP

o

Il!0l3|D|3|Q|Q]Q|B|B|ID|lE|iE|E|E|IE|E|!El!E!2|3!!"|2|2IS

O

P42/A10

P43/Al9_

P44/CS0

PAHCSt

P4afCS2

P47.C S3

___

P50AWRL/WR

P5t/WRH/BH E

P52/RD

P53/BCLK

P5*/HL DA

P& /H QLD

PSe/ALE

PSj^RDV/CLKout

P6tfCTSo/RTSo

P61/CL K0

P6?/R*Do

■ P63/TXD0

____

P64/CTSi/RTSi ;CL KS i

■ P65/C LK 1

P6e/HxDt

P67fl"x0 t

P7o/r*D2iSDA/rAOouns 1 )

P7i/RxD2/SCL/TA0in/TBSw ( ii 1 )

P72,‘CLK2/TA10Ln/V

z z « n nm cjz tihC 0 2

“ " 5

Z Z Z * * 2

111

Page 22

Terminal Function of Main CPU

No. Pin Name

1 P94/DA1

2 P93/DA0

P92

3

4 P91

5 P90

BYTE

6

7 CNVss

P87

8

9 P86

10 RESET

11

Xout

12

Vss

13 Xin

14

Vcc

15 P85

16 P84

17 P83

P82

18

19 P81

20 P80

21 P77

22 P76

23 P75

24 P74

25 P73

P72

26

27 P71

28 P70

29 P67

30 P66

31 P65

32 P64

33 P63

34 P62

35 P61

36 P60

37 P57

38 P56

39 P55

40 P54

41 P53

P52

42

43 P51

44 P50

P47

45

46 P46

47 P45

P44

48

49 P43

P42

50

P41

51

52 P40

53 P37

54 P36

P35

55

56 P34

Function | I/O

TONE

APC

DATA

STB

CLK

BYTE I GND

CNVss I H

-

-

RESET

XOUT

VSS

XIN

VCC

NMI

BU I L

SEC

PSW

CLKS O

MVRC

LAMP I L • up

SVRC 0 Pulse :

-

TUV o Pulse 144MHz Tuninq-voltage control

-

TUU

RXD2

TXD2

TXD1

RXD1

SCLK

BUSY

TXD

RXD I Pulse . Serial Communication port for Front CPU

SCL

SDA I/O Pulse Serial dara output for EEPROM

DUD

SCR

EPM I Activ low up Witer control

PTTM

T5

SQC 0 Activ tow Squelch control for TNC

STBD

DSQ I

TNCB

W C S

UVCS

DCSW

C/S

VAD o Activ high

UAD

M/S

WIDE

NAR 0 Activ low

MUTV

MUTU

Logic up Description

O D/A CTCSS tone output/DCS output

D/A

O

Pulse Serial data output for PLL IC

0

O Pulse

Pulse Sériai clock output for PLL IC

O

O

O

L Reset input

I

O Main clock output

-

I

-

I Activ high Interruption .

I Activ hiqh

L Power switch input

I

Activ high

0 Pluse

0

o

Pulse 430M H z Tuning-voltaqe control

0

I Pulse Serial Communication port for Clone

Pulse Serial Communication port for Clone

0

0 Pulse Serial Communication port for IN C

I Pulse

Pulse Witer control

0

Power output control

Strobe for PLL IC

Witer control

- . .

_ ; ' : -

GND

Main clock input

CPU power terminal

Backup signal detection input

Aleam(SCR) sinal input

CPU clock-shift output

Main volume control

Lighting color selection (H:2color)

Sub volume control

Serial Communication port for TNC

o Pulse W iter control

0 Pulse

o Pulse

I Activ low up Digital unit detect

Activ low up

I

Activ low

I

Activ low

0

o Pulse

Activ hiqh

o

Activ hiqh

0

Activ hiqh

0

Activ hiqh

Activ hiqh DCS switch

0

Activ low

0

o

Activ hiqh

o

Activ hiqh

Activ low Wide mode select

0

0 Activ low

Activ low

0

Serial Communication port for Front CPU

Serial clock output for EEPROM

Ready sigunal for digital unit

PTT input for TNC

up

TX power output ON/OFF

Strobe for Digital unit

Squelch signal input for Digital unit

Power switch ON/OFF for TNC

VHF Main VCO ON/OFF

UHF Main VCO ON/OFF

Diqital/TNC mode ON/OFF

VHF diqital ON/OFF

UHF digital ON/OFF

MAIN/SUB band select

Narrow mode select

VHF AF mute signal output

VHF AF mute signal output

Page 23

57 P33

58

P32

59 P31

60

Vcc

61

P30

62

Vss

P27

63

64 P26

65 P25

66 P24

67

P23

68 P22

69 P21

70 P20

71 P17

72 P16

73

P15

74 P14

75 P13

P12

76

77 P11

78 P10

79 P07

80 P06

81 P05

82 P04

83 P03

84 P02

85 P01

86 POO

87

P107/AN7

88 P106/AN6

89 P 105/AN 5

90 P104/AN4

91 P 103/AN 3

92 P102/AN2

93 P101/AN1

94

Avss

95

P100/AN0

96 Vref

97

Avcc

98 P97

99 P96/ANEX1

100 P95/ANEX0

XBR 0 Activ high

DCSV

DCSU 0

VCC

SCRB 0

VSS

VMMT o

0 Activ high

Activ high

-

Activ low Power output for Aleam

-

Activ high

XBR mute siqnal

VHF DCS switch

UHF DCS switch

CPU power terminal

GND

VHF mod mute output

UMMT 0 Activ high UHF mod mute output

MMUT 0

ULV

ULU

AM 0

5RV

5RU

5TV 0

5TU 0

14RS o

S43RS 0

FMS 0

43 RS o

S14RS 0

87RS o

5VS 0

C5S 0

ALAM o

TB o

BEP1

BEP2 0

Activ low

Activ high

I

Activ high

I

Activ high

Activ high

0

0

Activ hiqh

Activ high

Activ high

Activ high

Activ high

Activ hiqh

Activ hiqh

Activ high

Activ high

Activ high

Activ high

Activ low

Pulse ART/Toneburst signal output

Pulse

0

Pulse

Mic mute output

VHF unlock input

UHF unlock input ! \

AM mode ON/OFF

VHF RX power ON/OFF

UHF RX power ON/OFF

VHF TX power ON/OFF

UHF TX power ON/OFF

MAIN 144MHz power OM/O FF

SUB 430MHz power ON/OFF

FM power O N/OFF

MAIN 430MHz power OM/OFF

SUB 144MHz power ON/OFF

Ext band power ON/O FF

5V power ON/OFF

5V power ON/OFF

AF mute for Aleam

Beep sound 1 output

Beep sound 2 output

0

FAN 0

Activ high

SMTV I A/D

SQLV I

A/D VHF noise input for squelch

Air FAN power ON/OFF

VHF S-meter signal input

SMTU I A/D UHF S-meter signal input

SQLU I

A/D UHF noise input for squelch

TINV I A/D VHF CTCSS/DCS tone input

TINU I A/D

BAT I

AVSS

BP1 I

VREF

AVCC

A/D Power-supply voltage input

-

A/D Band plan

-

-

UHF CTCSS/D CS tone input

AD converter Gnd

AD converter ref. power

AD converter power

BP2 j Ext.Band plan

BP3 !

THC

I A/D PA Temperature detection

CH Band plan (L:CH)

Page 24

23) Transistor, Diode, and LED Outline Drawings

Page 25

RD70VHF1 (XE0047)

NchMOSFET

ABSOLUTE MAXIMUM RATING

Symbol Test conditions

Pch

VDSS Vqs=0V

VGSS Vds=0V ±20 V

Tj =

Tstg

ELECTRICAL CHARACTERISTIC(Ta=25°C)

Parameter Symbol

Saturated drain current IDSS Vds=17V, Vgs=0V

Gate to source leakage current

Threshold voltage

Output power 1 Po1 f=175MHz, Pin=6W

Drain officiency 1

Output power 2

Drain officiency 2

IGSS Vds=10V, Vgs=0V 5

Vth

t|D1’

Po2

T[D2 50

Test conditions

Vds=12V, Ids=1ma

Vds=12.5V

lds(idle)=2.0A

f=520MHz, Pin=10W

Vds=12.5V

ldsfidle)=2.0A

Tc=25°C

Rating

150 W

30

+175

-40 ~ +125

Limits

Min

Max

300

1.3 2.3

70

55

50

Unit

V

‘C

. °c

Unit

UA

UA

V

W

%

W

%

24) LCD Connection

24

COMMON

O DPI

@ =^ JM L ( m m ) □) CD C l I f)

Q1 qz BUSY-1 T—1 T—2 T-3 T-4

O DP2

® Ö

Q3 Q4 Q5

i m m □ □ a a I )

BUSY-2 ¥-1 W-2 W-3 W-4 W-5

T-5

T—6

Page 26

S1

S2

S3

S4

S5

S 6

S7

S8

S9

S10

S 1 1

S12

/0 M ‘

;om:

íom :

:o m '

S13

S14

S15

S16

S17

S18

S19

S20

S21

S22

S23

S24

S25

S26

S27

S28

S29

S30

S31

S32

S33

S34

S35

S36

S37

S38

S39

S40

S41

S42

S43

S44

S45

S46

S47

S48

S49

S50

S51

S52

COM1 COM2

10k

10a 10b 10c

101

COM3

10h

111 k 1 1 1 11 h

11a 11b 11c

12k 121

12a 12b 12c

13k 131 13h

13a 13b 13c

14k

14a 14b 14c

15k

141

151

12h

14h

15h 15p

15a 15b 15c

COM3

COM2

COM1

Q2

15}

Q4

T4T

R Q5

15g

15m

15f 15e

14g

14m

TNC 14f 14e

J 3 L

13g

13m

Q3 13f 13e

J 2 i

Q1

1 1 ¡

SUB

1 Q¡ 1 0 m 10n

12g

12f 12e

Hg

11f 11e

1 2 m 12n

1 1 m

DCS 10f 10e

SQ

9L

minusM 9f 9r

3l

plus(+)

Nar 7f 7e

M .

8 c l

8f

Za.

3L M .

BU S Y- 2 W-1

9m

8m

8e 8e

7m

6 m 6 n

Lo 6f 6e

A

_5a.

5m

Mi 5f 5e

4L

AM 4f 4e 4d

A s l

3a 3f

4m 4n

3e 3d

2a 2f 2e 2d

SQL

2c

3c

2b

3b

1b,c

2 a.

3g_

4k 41 4h 4 p

4a 4b 4c

5k

5a

6k

6a

51

5b

61

6 b 6c

5h

5c

6h

7k 71 7h

7a

8k

8a

9k 9T

7b 7c

8!

8 FT

8b 8c

9h

9a 9b 9c

N.C.

COM4

10p

W-2

11 p

W-3

12p

DP2

13p

W-4

14p

W-5

5-2

COM4

15n

15d

14n

14d

13n

13d

12d

11 n

11 d

10d

9n

9r

8n

7n

7e

6e

5 ñ

5e

BUSY-1

T-1

T-2

T-3

5p

T-4

DP1

7P

T-5

8 p

T-6

_9p_

5-1

25

Page 27

E X P L O D E D V IE W

1) Front View

AX0OO3

26

Page 28

2) Bo ttom View

Page 29

P A R T S L I S T

PART LIST

Front Unit

Ref.

Part No.

No.

C601 CU3535

C602 . CS0424

CU3523 iChipC. GRM36CH101J50PT

C603

C604

CU0108

CU3551 Chip C. GRM36B223K16PT

C605

C606

CU3535 Chip C.

C607

CS0424

C608 CU3535 ¡Chip C. GRM36B102K50PT

CU0108 TChip C. 2012 B 10V 1UF ¡ 1

C609

C610 'CU3535

CU3535 Chip C. GRM36B102K50PT i: i

C611

CU3535 Chip C.

C612

C613

CU3535 Chip C.

C614

CU3535

CS0424 ¡Chip Tantalum' :TMCMA1C106MTR

C615

C616

CU3535 Chip C. ! GRM36B102K50PT

C617

CS0424

CU3533 Chip C. GRM36B681K50PT

C618

CU3535 Chip C. GRM36B102K50PT

C619

C620 CU3535 Chip C. GRM36B102K50PT

CU3535

C621

C622

CU3535

C623

CU3543

CU3543 Chip C. GRM36B472K25PT

C624

C625

CU3551 iChip C. GRM36B223K16PT i! 1

C626

CU3523 iChip C.

CU3523 Chip C. GRM36CH101J50PT

C627

UE0035 . Connector

CN601

CN602

UJ0052 Jack

D601

XD0254

XD0254 Chip Diode 1SS355

D606

DB11

XL0069 Chip LED FA1111C

D612

XL0108

XL0069 Chip LED FA1111C

D613

D614

XL0092 Chip LED MPG3338S

D618

XL0051

XD0254 Chip Diode 1SS355

D620

IC601

XA0068

IC602

XA0947

XA0899 tc LC75884W

IC603

XA0914 IC M38503M2H667FP

IC604

LCD601

EL0054.

XT0095 Chip Transistor 2SC4081

Q601

Q602

XT0095 Chip Transistor 2SC4081

Q603

XU0193

0604

XT0095

XU0193

0605

Q606

XU0192

Q607

XU0173

XU0173 Chip Transistor DTD114EK-T146

Q608

Q610

XU0193

Q611

XT0095

XU0193

Q612

R601

RK3566 Chip R.

R602

RK3550

RK3551 Chip R. 1005 1/16W12K OHM J

R603

R604

RK3538 Chip R.

R605

RK3560

RK3543 Chip R. 1005 1/16W2.7K OHMJ

R606

R607

RK3550 Chip R.

R608

RK3550 Chip R.

RK3538 Chip R. 1005 1/16W 1.0K OHMJ

R609

R610

RK3550 Chip R.

R611

RK3550

RK3526 Chip R. 1005 1/16W 100 OHM J

R612

R613

RK3522 Chip R. 1005 1/16W47 OHMJ

R614

RK3501 Chip R.

R615

RK3546

R616

RK3550 Chip R.

R617

RK3546 Chip R.

R618

RK3550

RK3550 Chip R. 1005 1/16W 10K OHMJ

R619

R620

RK3550 Chip R.

R621

RK3550

RK3550 Chip R. 1005 1/16W 10K OHM J

R622

R623

RK3550

R624

RK3550 Chip R.

R625

RK3550

R626

RK3550 Chip R. 1005 1/16W 10K OHM J

R627

RK3550 Chip R.

RK3550 Chip R. 1005 1/16W 10K OHM J

R628

R629

RK3550 Chip R. 1005 1/16W 10K OHM J

R630

RK3546

Description

Chip C.

Chip Tantalum

Chip C.

Chip Tantalum

Chip C. GRM36B102K50PT

Chip C.

Chip Tantalum

Chip C. GRM36B102K5ÜPT ' 1

Chip C. GRM36B102K50PT

Chip C.

Chip Diode 1SS355 1

Chip LED SML512BC4TT86 1

Chip LED

IC

[C NJM78M05DL1A-TE1 1

LCD

Chip Transistor RN1107 TE85L

Chip Transistor 2SC4081 i

Chip Transistor

Chip Transistor RN2107 TE85L

Chip Transistor DTD114EK-T146 1

Chip Transistor RN1107 TE85L

Chip Transistor 2SC4081

Chip Transistor

Chip R. 1005 1/16W 10K OHM J i

Chip R. 1005 1/16W68K OHMJ

Chip R.

Chip R. 1005 1/16W4.7K OHMJ

Chip R. 1005 1/16W 10K OHMJ

Chip R.

Chip R.

Chip R. 1005 1/16W 10K OHM J

Chip R.

Parts Name

GRM36B102K50PT

TMCMA1C106MTR

2012 B 10V 1UF ;

GRM36B102K50PT 1 1. 1 R639

TMCMA1C106MTR

GRM36B102K50PT il i R646

GRM36B102K5ÛPT

GRM36B102K50PT

TMCMA1C106MTR

GRM36B472K25PT

GRM36CH101J50PT 1

MIC FM214-8SMPY

HJC0163-01-022 1

VRPG3312X 1

IC M5218FP

LCD DR620

RN1107 TE85L

RN1107 TE85L

1005 1/16W220KOHMJ

1005 1/16W1.0K OHMJ

1005 1/16W 10K OHM J i

1005 1/16W 10K OHM J 1

1005 1/16W10K OHM J

1005 1/16W 10K OHM J

1005 1/16W 0 OHM J

1005 1/16W 10K OHMJ

1005 1/16W4.7K OHMJ

1005 1/16W 10K OHM J ! 1 1

1005 1/16W 10K OHM J

1005 1/16W 10K OHM J

1005 1/16W 10K OHM J

1005 1/16W 10K OHM J

1005 1/16W 4.7K OHMJ

Qty

(T )" (E)

1

1i 1

1 1 R635

1 ! 1 R636

I 1

1

1 1

: j t ; : . i

■i

11 : • i R653

1F 1 R655

i¡ 1 R656

i! 1

,1

1

V R662

1: 1

1

- 1

1

1

1

V

: 1

1

1

1

i

i

i

i

i

1

r

1

1

1

1

i

i

i

i

1

1

1

1

1

1

1

•1

1 1

i

i

i

i

1

1

1

1

1

1

. 1

11 1

Ref.

Part No.

No.

R631

RK3550

R632 "

1 R633

1

i R641

i R642

i R659 .

i R660

i R669

i R670

1 SW601

1

i SW604

i

i SW607

i SW608

i

1 VR601

i

i

i

i

1

1

1

1 D603

1 D604

1 D605

1 D607

i D608

i D609

i D610

i D615 XL0108 Chip LED SML512BC4TT86

i

i D617

i D619

1

1 R648

1 R649

1

1 R665

1

i

i

i

i

i C4

i C5

1

1 C8

RK3542

RK3526 Chip R.

R634

RK3526 Chip R.

RK3558 Chip R.

RK3538 Chip R. .

R637

RK3538 Chip R.

RK3026

R640 RK3550 Chip R.

RK3570 IChip R.

RK3538 iChip R.

R643

RK3574

R645

RK3030 [Chip R.

RK3534 Chip R.

R651

RK3530 :ChipR.

R652 j RK3530 Chip R.

RK3535 Chip R.

R654

RK3532 Chip R.

RK3528

RK3535 Chip R.

R657

RK3528 Chip R.

R658- ■

RK3550 Chip R.

RK3550 Chip R.

RK3014 Chip R.

RK3023 Chip R.

R663 RK3538 Chip R.

R666

RK3538 Chip R.

RÍB67

RK3538 Chip R.

R668 -

RK3538 Chip R.

RK3538

RK3035 Chip R.

RE 601 UR0015 - Dial

UU0015Z Switch

SW602

UU0015Z

SW603 UU0015Z Switch

UU0015Z Switch

SW605

UU0015Z Switch

SW606 UU0015Z Switch

UU0015Z Switch

UU0015Z Switch

SW609

UU0015Z

RV0035 Variable R.

VR602

RV0035

X601

XB0029

DG0041

FG0352

FG0358

FM0034 :

FP0034

ST0081

TL0028 REFLECTIVE SHEET

TL0029

LED Unit

Ref.

V No.

D602 XL0077 Chip LED

D616 XL0108 Chip LED SML512BC4TT86

R647

R650

R664 RK3014 Chip R.

Main Unît

C1

C3

C6 jCU3019

C9

Part No.

XL0077

XL0077

XL0108 Chip LED

XL0077 Chip LEO

XL0108

XL0077 Chip LED 1

XL0077

XL0108

XL0108

RK3028

RK3028 Chip R.

RK3028 Chip R.

RK3014

RK3014 Chip R.

Ref.

'Part No.

No.

CU3035

CU3535 Chip C.

CU3031 Chip C.

CU4003

CU3035 Chip C.

CU7046

Description Parts Name

Chip R.

Chip R.

Chip R.

Chip R.

Chip R. 1005 1/16W 150 OHMJ

Chip R.

Switch EVQPPPA25 TACT SW

Switch

Variable R. EVUF2JFK4B14

Ceramic OSC EFOS4914E5

Description Parts Name

Chip LED FA1111 C-TR C/D/ERANKi 1 1

Chip LED FA1111 C-TR C/D/ERANK

Chip LED : SML512BC4TT86

Chip LED

Chip LED

Chip LED

Chip R. 1608 1/10W 150 OHMJ

Chip R. 1608 1/10W 10 OHMJ

Description Parts Name

Chip C.

Chip C.

Chip C.

Chip C.

1005 1/16W 10K OHM J

______

1005 1/16W2.2K OHMJ

1005 1/16W 100 OHM J

1005 1/16W 100 OHMJ

1005 1/16W 47 K OHMJ

1005 1/16W 1.0K OHMJ

1005 1/16W1.0K OHMJ

1608 1/10W 100 OHM J

1005 1/16W 10K OHM J

1005 1/16W470K OHMJ

1005 1/16W 1.0K OHMJ

1005 1/16W 1.0M OHMJ

1608 1/10W 220 OHM J

1005 1/16W 470 OHM J

1005 1/16W220 OHM J

1005 1/16W 220 OHM J

1005' 1/16W 560 OHM J

1005 1/16W330 OHM J

1005 1/16W 560 OHM J

1005 1/16W 150 OHMJ

1005 1/16W1 OK OHMJ

1005 1/16W 10K OHM J

1608 1/10W 10 OHM J

1608 1/10W56 OHMJ

1005 1/16W 1.OK OHMJ Í 1i 1

1005 1/16W 1.0K OHMJ

1005 1/16W 1.0K OHMJ

1005 1/16W 1.0K OHMJ

1005 1/16W 1.OK OHMJ . 1 1

1608 1/1OW 560 OHMJ

RH90N74E20-A90770

EVQPPPA25TACT SW

EVQPPPA25TACT SW

EVQPPPA25 TACT SW

EVOPPPA25TACT SW

EVQPPPA25 TACT SW

EVQPPPA25TACT SW

EVQPPPA25 TACT SW

EVQPPPA25 TACT SW

EVUF2JFK4B14

¡LCD LIGHT DR620

iLCD RUBBER CONNECTC 1 1

¡LCD CUSHION DR620

¡MIC GND PLATE

1 MIC SPACER DR110

LCD HOLDER DR620

DIFFUSION SHEET

FA1111C-TR C/D/ERANKl 1

SML512BC4TT86

FA1111 C-TR C/D/ERANK

FA1111C-TR C/D/ERANK

FA1111 C-TR C/D/ERANK

SML512BC4TT86

SML512BC4TT86

1608 1/10W 150 OHM J

1608 1/10W 150 OHM J

1608 1/10W 10 OHM J

1608 1/10W 10 OHM J

1608 B 50V 0.001 UF

GRM36B102K50PT

1608 B 50V 470PF K

GRM42-6CK020C500PT 1 1

1608 CH 50V 47PFJ

1608 B 50V 0.001UF

3225 C 500V 27PF

Qty

* CO (É)

1 i 1

1

1 1

1

1 ! 1

1

1

1

1

1

1

1

1 1

1

I 1

1

1 1

1

1 1

11 1

11 1

1 ! 1

1 1

1

1 1

1

1

1

1 1

1 1

1 1

1

1 1

1 1

1

Qty

(T) (E)

1 1

1 1

1

1 1

1 1

1 1

1

1 1

1

1

1 1

11 1

1i 1

11 1

1

1

Qty

<T)

1 1

1 1

1

1 1

1 1

1

(E)

1

1

1

1

1

1

1

1

1

-|

1

1

1

1

1

1

1

Í

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Page 30

i Part No. 1 Description j Parts Name

C10 ;CU3035 jChipC. ! 1608 B 50V 0.001 UF ¡ 1! 1

C11

CU3035 j Chip C. • : 1608 B 50V 0.001 UF ¡ 11 1

C12

CU3057 jChipC. j 1608 CH 50V 13PF - ¡ 1j 1 C107 'CU3551 ¿Chip C. 'GRM36B223K16PT

C13 ;CU3057 ¡ChipC. Í1608 CH50V 13PF . ! 1| 1 C108 CU3035 IChip C. j 1608 B 50V 0.001UF

C14 ÍCU40Z3

C15 ÍCU7052 Chip C. <3225 F 500V 82PF . ! 1

C16 ÍCU3507 ChipC. 1GRM36CH060D50PT ! 1

C17 ÍCU7054

C18 ÍCU3535 Chip C. j GRM36B102K50PT i 1 C113 ;CU3502 [Chip C. GRM36CK010C50PT

C19 ÍCU3517 ChipC. i GRM36CH330J50PT ¡ 1

C20 |CU4023

C21 ¡CU3535

C22 ¡CU3511 Chip C. GRM36CH100D50PT ! 1 Cl 17 ICU4007 ¡ChipC.

C23 CU3035 Chip C. 1608 B 50V 0.001 UF ! 1

CU3535

C26

C27 CU3515 Chip C. GRM36CH220J50PT | 1

C29 CU3515 Chip C. GRM36CH220J50PT i 1 C121 CU3535

CU3535

C30

C31 CU3535 Chip C. GRM36B102K50PT

C32 CU3024 Chip C. 1608 CH 50V 120PFJ : C124 CU4006 Chip C.

C33 CU3024 Chip C.

C35 CU4016 Chip C.

C36 CU4015 ¡Chip C.

C38 CU4016 iChip C.

C39

CU4014 ¡Chip C. GRM42-6CH180 J500PT

C40 CU7050 ¡ChipC. 3225 F 500V 56PF

C42 CU3513 ¡ChipC. GRM36CH150J50PT .

C43

CU3518 ¡Chip C.

C44 CU3515 ¡ChipC. GRM36CH220J50PT

CU3035 jchip C.

C45

C46

CU3001 ¡Chip C. M608 CH 50V .5PF C

CU3001

C48

C49 CU4013

C51 [CU3511

C52 ¡CU0108

C53 ÍCU0108 Chip C. 2012 B 10V 1UF

C54 >CU3035 Chip C. ¡1603 8 50V 0.001 UF .

C55 'CU3515 Chip C. ! GRM36CH220J50PT

C56 ¡CU3511 ChipC. ¡GRM36CH100D50PT C144 CU3035

C57 'CU4012 ChipC. ! GRM42-6CH120J500PT C145

C58 CU3509 Chip C. GRM36CH080D50PT C146 CU3535

C59 ÍCU3510 Chip C. 1005 CH 50V 9PF D

C60 ¡CU3514

C61 ICU3514 Chip C. GRM36CH180J50PT

C62 ICE0339 Electrolytic C. 16V 10UF

C63 CU4015

C64 CU3535 Chip C. GRM36B102K50PT

C65 CS0424 Chip Tantalum TMCMA1C106MTR

C66

CU3503 ¡ChipC.

C67 CU3535 'Chip C. GRM36B102K50PT C155 CU3535 I Chîp C. GRM36B102K50PT ! II . 1

C68 CU3019 ¡ChipC. 11608 CH 50V 47PFJ

CU3530 ¡Chip C. ¡GRM36B391K50PT

C70 CEÓ420 : Electrolytic C. ¡16MV22SZ C159 CU3506 Chip C.

C71 CU3011 IChipC. i 1608 CH 50V 10PF C Cl 60 CU3007

C72

CU3012 ÍChipC. ¡1608 CH50V 12PFJ

C73 CU3015 ChipC. ¡1608 CH 50V 22PF J

CU3035

C74

C75 CU3514

C76 CU3514 "Chip C. ¡GRM36CH180J50PT

C78 CU3531 ChipC. ■ ! GRM36B471K50PT

C79 CU3535

C80 CU3535 Chip C. GRM36B102K5ÖPT C168 ÍCU3535 . ¡Chip C. ÍGRM36B102K50PT

C81 CU3511 Chip C. GRM36CH100D50PT

C82 ¡CU3547

C83 ICU3535 Chip C. GRM36B102K50PT

C84 jCU3111 . Chip C. 1608 B 25V 0.1 UF C173 CU3515

C85 (CU3035

C86 1CU3535 Chip C. G RM36B102K50PT

C87 CU3035 Chip C. 1608 B 50V 0.001 UF '

C88

CU3035 ¡Chip C.

C89

CU3111 iChip C. •

C91

CU3502 ¡ChipC. ’ :gRM36CK010C50PT ; i 1; 1 C179 ÍCU3503 • iChip C. ¡GRM36CK020C50PT

C92

CU3547 ChipC. • :GRM36B103K16PT : | l! 1

C93 CU3035 .

C94 JÓU35Í1 ChipC. -GRM36CH100D50PT 1i 1 C182 'CU3512 Chip C. :GRM36CH120J50PT

C95 CU3111 'Chip C. ! 1608 B 25V 0.1 UF ! 1j 1 C183

C96 CU3035

C97 ¡CU3535 ChipC. ■ \GRM36B102K50PT . j 1 • 1 C185 CU3527 ÍChipC. ; GRM36CH221J25PT

C98 ; CS0220 : Chip Tantalum ! 16V 2.2UF

C99 1CU3035 ¡ChipC.- 11608 B 50V 0.001UF | 1 C187

C100 'CU3035 'Chip C. ¡1608 B 50V 0.001UF

C101 CU3535 IChip C. |GRM36B102K50PT

C102 CU3506 , Chip C. GRM36CH050C50PT

C103 CU4Û19 IChip C. Chip C. GRM36CJ030C50PT J_ 1

Chip C. ;'GRM42-6CH10f J500PT i II í

ChipC. i 2012 <J 100V 22PF ! i! 1

Chip C.

Chip C. GRM36B102K50PT ! 1

Chip C.

Chip C. GRM36B102K50PT

Chip C. í 1608 CH 50V ,5PF C

Chip C. ¡GRM42-6CH150J500PT

Chip C. ¡GRM36CH100D50PT

Chip C.

Chip C-

Chip C. GRM42-6CH220J500PT C151 CU3523

ChipC. 11608 B 50V 0.001 UF

ChipC. ÍGRM36CH180J50PT

Chip C.

Chip C. GRM36B103K16PT

Chip C.

ChipC. ¡1608 B 50V 0.001 UF ¡ 1j: 1 C181 CU3502 :ChipC. ;GRM36CK010C50PT

ChipC. ;1608 B 50V 0.001UF

GRM42-6CH101J500PT Í 1 i

GRM36B102K50PT I 1

1608 CH 50V 120PF J

GRM42-6CH270J500PT 1 C126

GRM42-6CH220J500PT

GRM42-6CH270J500PT

GRM36CH390J50PT C132 ¡CU3535 Chip C.

1608 B 50V 0.001 UF

2012 B 10V 1UF

GRM36CH180J50PT

GRM36CK020C50PT

GRM36B102K50PT

1608 B 50V 0.001 UF

1608 B 50V 0.001 UF I It 1

1608 B 25V 0.1UF ■ | l| ■ 1 C178 'CU3515 'Chip C. ‘GRM36CH220J50PT

GRM42-6CH470J500PT

Qty

(T) ! (E)

11 1

li 1

i! 1

i| 1

1

1 1 : 1

^ 7 ^ ■ 1

Î

1 : 1

1

—

_ .i

j Part No. j Description | Parts Name

C105 ÍCU3512 IChip C. iGRM36CH120J50PT 1 11 ■ 1

C106 i CU4008 ! Chip C. i GRM42-6CH070D500PT

CW9 :CU3535 ¡Chip C. 'GRM36BJ02K50PT

C110 ¡CU3547 ¡ChipC. ÍGRM36B103K16PT

i

C111 ;CU0002 ;ChipC. -2012 CH 50V 1.0PF C

i

Cl 12 ¡CU4006 IChipC.

Cl 14 CS0063 'Chip Tantalum 35V 0.1 UF 1 1

i

i Cl 16

i

i

i

1

1

1

1

1

1

1 C136

1

1

1

i

i

i

i C152

1

1

1

1 C157

1 C161

1

1

i

i

1

CU3005 iChip C. 1608 CH 50V 4PF C

Cl 15

CU4010 ¡Chip C. GRM42-6CH090D500PT

Cl 18 CU3547 ¡ChipC.

CE0420 ! Electrolytic C. 16MV22SZ

C119

C120 CU3535 ■ Chip C. GRM36B102K50PT

CU3523 Chip C. GRM36CH101J50PT

C122

C123 CU3035 Chip C. 1608 B 50V 0.001 UF i! i

C125 CU4001

CU4007 Chip C.

C127 CU4Ö16 Chip C.

C128 CU3511

CU3001 Chip C. 1608 CH 50V -5PF C

C129

C130 CU3001 Chip C.

C131 ICU4019

CU3035 Chip C.

C133

C134 CU3035

C135 CS0063

CU3531 Chip C.

C137 CU3535

CU3523 Chip C. GRM36CH101J50PT

C138

C139 CU3035 Chip C.

C141 CU3035

CU3523 Chip C. GRM36CH101J50PT

CI42

C143 CU3035

CU3535 ChipC. ¡GRM36B102K50PT ! 1

C147 CU3523

CU3547 ChipC. ¡GRM36B103K16PT j 1

C148

C149 CU3535

C150 CU3111

CU3547 Chip C.

CU3512 ¡ChipC.

C153

CU3007 Chip C. 1608 CH 50V 6PF C

C154

C156 CU3023

CU3006 Chip C. 1608 CH 50V 5PF C

CU3035 ChipC. 1608 B 50V 0.001 UF , !. 1; 1

CU3508

Cl 62

C163 CU3504

CU3547 ‘ChipC. ¡GRM36B103K16PT

C164

C165 CU3503 ÍChipC. ¡GRM36CK020C50PT

CU3535 iChipC. !GRM36B102K50PT

C166

CU3535 ¡ChipC. ¡GRM36B102K50PT

C167

C169 ÍCU3547 Chip C. ¡GRM36B103K16PT

C170 ¡CU3513 ChipC. IGRM36CH150J50PT

C171 CU3547 ChipC. ¡GRM36B103K16PT

C174 CU3511

C175 CU3511 ChipC. GRM36CH100D50PT

CÎ76 !CU0108

Cl 77 ¡CU3503 jChipC. ¡GRM36CK020C50PT

¿180 CU3502 'Chip C. IGRM36CK010C50PT

CU3535 ¡Chip C. !GRM36B102K50PT . : 1

CU3529 : 'Chip C. IGRM36B331K50PT

C184 ”

C186 ICU3111 'Chip C. ¡ 1608 B 25V 0.1UF . • . ¡ il 1

CU3535 ' ¡Chip C. IGRM368102K50PT

CU3513 Chip C. TqRM36CH i 50J50PT

C188

C189 CU3516

C190 CU3535

CÎ 91 CU3504 ■

C192 'CU3535

Chip C.

Chip C.

Chip C.

Chip C.

Chip C.

Chip Tantalum 35V 0.1 UF

Chip C. GRM36B102K50PT

Chip C.

ChipC. 11608 B 50V 0.001 UF ! 1! 1

Chip C. [ 1608 B 50V 0.001 UF ¡ 1: 1

ChipC. ¡GRM36B102K50PT ; 1

Chip C. ¡GRM36CH101J50PT j 1

ChipC. IGRM36B102K50PT ! H 1

ChipC. ¡1608 B 25V 0.1 UF | 1

ChipC. ;GRM36CH101 J50PT j 1 1

Chip C.

ChipC. 11608 CH 50V 6PF C

ChipC. ¡1005 CH 50V 7PFD . ! l! 1

Chip C. 1GRM36CJ030C50PT

Chip C.. IGRM36CH220J50PT

Chip C.

Chip C. 12012 B 10V 1UF

Chip C.

Chip C.

Chip C.

GRM42-6C H050C500PT

GRM42-6CH060D500PT

GRM36B103K16PT

GRM36B102K50PT

GRM42-6CH050C500PT

GRM42-6CK01OC500PT

GRM42-6CH060D500PT

GRM42-6CH270J500PT

GRM36CH100D50PT :

1608 CH 50V .5PF C

GRM42-6CH470J500PT

GRM36B102K50PT

1608 B 50V 0.001 UF

1608 B 50V 0.001 UF

GRM36B471K50PT

1608 B 50V 0.001 UF

1608 B 50V 0.001UF

GRM36B103K16PT j 1| 1

GRM36CH120 J50PT

1608 CH 50V 100PF J

GRM36CH050C50PT

!

GRM36CH10OD50PT

GRM36CH270J50PT j . 11 1

GRM36B102K5ÖPT ! 11 1

GRM36B102K50pt I ” ’ 11 1C104 CS0220 :Chip Tantalum 16V2.2UF

Qty

(T) I (E)

ll 1

1 i 1

1¡ 1

il I

1Í 1

il ï

1 1

1

1 1

1.

1i 1

11 1

t l

.. ......

11 1

11 1

11 1

i

i

1S 1

11 1

1Í 1

li 1

1 i 1

li 1

1¡ 1

í¡ 1

11 1

. . . . . I L . J

1¡ 1

1¡ 1

li 1

1! 1

í! 1

1

___ __

------

--

1¡ ■ 1

r

i ¡. iC69

1 i 1

- —

j f — j

!

1

1

1

r

i

i

i

i

il i

1! 1

n 1i

1

* 1

1 i 1

-------

U-— j

1

i

1

i

1

1

29

Page 31

” ef- I Part No.

No. '

C196 ¡CS0049

C197 ICS0063 Chip Tantalum

C198 ¡CU3535 .ChipC. C288 :CU3547 ChipC. GRM36B103K16PT I 1 ¡ 1

C199 ICU3515 iChipC. . GRM36CH220J50PT I 1l 1

C200 CU3517 IChipC. ¡GRM36CH330J50PT ~7 1; 1 C290 'CU3518 ;Chip C. :GRM36CH390J50PT . I 1

C201 ¡CU3519 ¡Chip C. ¡ GRM36CH470J50PT \ ij 1

C202 ¡CU3507 ichip C. IGRM36CH060D50PT ! 1| Í

C203 CU3547 IChipC. ■ :GRM36B103K16PT ] 1

C205

CU3513 iChip C. ; ,GRM36CH150J50PT ! 1 1

CU3547 ¡ChipC.

C206

CU353S ¡ChipC.

C207

C208 ! CU3111 - Chip C.

C20S JCU311f CWpC. 1608 B 25V O.ÍUF i '1 1

C210 ICU3111 IChipC.

C211 ¡CU3547

C213 ÍCU3535 ChipC. ÍGRM36B102K50PT 1 1 C305 ¡CU3511

CU353S

C214

C215 CU3535

C216

CU3522

CU3522

C218

CU3522 ¡ChipC.

C219

C220

CU3535 ' Chip C.

C221 CU3547 jchip C. GRM36B103K16PT 1 Ï C313 CU3502

CU3535 Chip C.

C222

C223 CU3535 ChipC.

C224 CU3111 IChipC. 1608 B 25V 0.1UF 1 ; 1 C316 CU0108

C225 CU3535 ! ChipC. GRM36B102K50PT 1 1

C226 ¡CU3515 Chip C.

C227 ÍCU3111 ChipC. -

C228 ! CU3511

C229 ¡CU3111

C230 ICU3111 Chip C. neos B 25V 0.1 UF 1 : 1 C322 CU3547

CU3111

C231

CU3111

C232

C233 CU3111 Chip C.

CU3111

C234

C235 CU3111

C236 CU0108 Chip C.

CU3535

C237

C238 CU3551

C239

CU3535

CU353)

C240

C242 CU3523 Chip C.

C243

CU3503

C244 CU3535 Chip C. GRM36B102K50PT r i 1 C335 CU3511

C245

CS0424 Chip Tantalum

C246

CU3535

CU3506

C247

C248 CU3547 Chip C.

C249 CU3511 Chip C. GRM36CH100D50PT 1 1 C342

CU3531

C250

C251

CU3502 Chip C.

C252 CU3519 Chip C. GRM36CH470J50PT

C253 CS0424 Chip Tantalum TMCMA1C106MTR 1 C347 CU3111 Chip C.

C254 CU3547

C255 CS0220

C256 CU3547 Chip C. GRM36B103K16PT 1 1 C350 CU3535

C257 CS0220

C258 CU3504 Chip C. GRM36CJ030C50PT 1 1 C354

C259 CU3515 Chip C.

C260

CU3514 Chip C.

C261 CU3535 Chip C. GRM36B102K50PT 1 1 C357

CU3111

C262

C263

CU3523

C264 CU3535 Chip C.

CS0063

C265

C266

CU3524 Chip C.

C267 CU3547 Chip C. GRM36B103K16PT 1 1 C363

C268 CU3515 Chip C. GRM36CH220J50PT 1 1 C364 CS0237 Chip Tantalum 10V4.7UF 1

C269 CU3519

C27D CU35J6 Chip C GRM36CH270J50PT 1. 1 C366

C271 CU3535 Chip C. GRM36B102K50PT 1 1 C367 CU3511 Chip C.

C272

CU3535

C273

CU3504

C274 CU3535 Chip C. GRM36B102K50PT 1 1 C370

C275

CU3535

C276

CU3535

CU3513

C278

C279 CU3535 Chip C.

C280 CU3547

CU35I4

C28I

C282 CU3518 Chip C.

C283

CU3524

CU3504

C284

C285 ICU3524 Chip C. 1005 CH 50V 120PF J 1

Description Parts Name ^

Chip Tantalum PÍ6V _1ÜF

Chip C. IGRM36B103K16PT : 1

ChipC. GRM36B102K50PT 1 C306 ICU3547

ChipC. GRM36B102K50PT

Chip C. ! GRM36CH82O05ÖPT• 1 1 C309

Chip C. IGRM36CH820J50PT - 1 C310

Chip C.

Chip C.

Chip C. 1608 B25V 0.1UF 1 1 C323 CU3511

Chip C.

Chip C. 1608 B25V 0.1UF 1 1 C326 rCU3504

ChipC.

Chip C. GRM36B102K50PT 1 C329 CU3512 Chip C.

ChipC.

Chip C.

Chip C. GRM36B471K50PT 1 1 C332 CU3535 Chtp C.

Chip C.

Chip C.

Chip C. GRM36CH050C50PT 1 1 C339 ÍCS0237 Chip Tantalum 10V 4.7UF 1

Chip C. GRM36B471K50PT 1 1 C344

Chip C.

Chip Tantalum 16V 2.2UF

Chip Tantalum

Chip C. 1608 B25V 0.1UF 1 1 C358 CU3535

Chip C.

Chip Tantalum 35V 0.1 UF 1 1 C361 LCU3527

Chip C.

Chip C.

Chip C. GRM36CJ030C50PT 1 1 C369

Chip C.

Chip C. GRM36B102K50PT 1 1 C372

Chip C. GRM36CH150J50PT . 1 1 C373

Chip C.

Chip C. GRM36CHt80J50PT 1 1 C376 CU3535 ¡ChipC. ¡GRM36B J 02K50PT 1

Chip C.

Chip C. GRM36CJ030C50PT

35V0.1UF 1 11 1

GRM36B102K5ÖPT I i f 1

GRM36B103K16PT I 1! 1

GRM36B102K50PT

1608 B 25V 0.1 UF

1608 B25V 0.1 UF 1 1

GRM36CH820J50PT

GRM36B102K5ÖPT 1 C312

GRM36B102K50PT 1 C314

GRM36B102K50PT

GRM36CH220J50PT

1608 B 25V 0.1 UF

GRM36CH100D50PT

1608 B 25V 0.1 UF

1608 B25V 0.1UF

1608 B 25V 0.1UF

1608 B 25V O.IUF

2012 B 10V 1UF

GRM36B223K16PT

GRM36B102K50PT

GRM36CH101J50PT 71

GRM36CK020C50PT 1 1 C334

TMCMA1C106MTR

GRM36B102K50PT 1 1 C338

GRM36B103K16PT

GRM36CK010C50PT

GRM36B103K16PT

16V 2.2UF 1

GRM36CH220J50PT

GRM36CH180J50PT

GRM36CH101J50PT

GRM3 6B102K50PT

1005 CH 50V 120PF J

GRM36CH470J50PT

GRM36B102K50PT

GRM36B102K50PT

GRM36B102K50PT

GRM36B103K16PT 1 1 C375

GRM3 6C H390J50PT

1005 CH 50V 120PF J 1 1 C378

............ ¡

------

.......

1 i 1

L li 1

1 ' 1 C300 ! CU3512 ¡ChipC. ■ 1GRM36CH120J50PT

1

1

1

1

1 1 C319

1

1

1

1 1 C325

1 1 C327 CU3503

1

1 1

1

1

1 1 C337 CU3111

1

1 1

1

1

1 1 C349

1 1 C355 CU3535

1

1

1 1 C360

1

1

1 1

1 1 C371 CU3543

1

1

1

1

C286 CU3511 'ChipC. GRM36CH100D50PT i 1

C287 CU3547 'Chip C. GRM36B103K16PT | 1

C289 CU3535 ¡Chip C. :gRM36B102K50PT < 1

C291 ‘CU3535 ¡ChipC. GRM36B102K50PT i 1¡ 1

C292 CU3518 ¡ChipC. ¡GRM36CH390J50PT 1 1 1

■ 1 C294 ÍCU3514 ¡ChipC. GRM36CH180J50PT 1

C295 ¡CU3547 ¡ChipC. ¡GRM36B103K16PT |' 1

C296 ¡CU3547 I Chip C. ;GRM36B103K16PT j l l 1

C298 1CU3547 íChip C. ¡GRM36B103K16PT ■ ' :j 1.

C301 ICU3535 ChipC. j GRM36B î 02K50PT

C302 CU3535

1 C303 ¡CU3535 ÍChip C. ; GRM36B102K50PT 1 1

C308

1

1

C311 CU3535

1 C315

C317

1 C318

■ 1

C320

1 C321

1 C324

1 C328

C330

1 C331

1 C333

1 C340

C345

1 C346

1 C348

1 C353

1 C356

1 C359

1 C362

1 C365

C368

1

C374 CU3111 ¡Chip C.

1

C377 CU3547 IChip C.

1 C379

1 C380 CU3503 ¡ChipC. IGRM36CK020C50PT

Part No. Description

No.

Chip C. ¡ GRM36B102K50PT '

ChipC. ¡GRM36CH100D50PT

ChipC. !GRM36B103K16PT

CU3535

CU3535

CU3547 IChipC. IGRM36B103K16PT

CU3511

CU3535 1

CU3503

CU3535 n

CS0063

CU3111

CU3501

CU3547

CU0108 Chip C.

CU3535

CU3503

CU3505

CU3515

CU3111

¡CU3505

CU3512

CU3508 Chip C.

CU3547

CU3505 Chip C. ¡GRM36CH040C50PT

CU3535

CU3535

CU3535

CU3523

CU3504

CU3547

CU3547

CU3547

CU3522

CU3551

CS0424

CU3535

CS0424 Chip Tantalum

CU3535

CU3111

CU3111

CU3535

CU3527

CU3111 ¡ChipC.

CU3547 ¡ChipC.

CU3101 j Chip C.

CU3111 ¡ChipC.

Chip C.

Chip C. GRM36B102K50PT i

Chip C. ¡ GRM36B102K50PT

ChipC. ¡GRM36CH100D50PT

Chip C. ¡GRM36CK0{0C5OPT

ChipC. j GRM36B102K50PT

Chip C. ¡GRM36CK020C50PT 1

Chip C. ¡2012 B 10V tUF

Chip C. IGRM36B102K50PT 1

Chip Tantalum ¡35V 0.1UF

ChipC. ¡1608 B25V 0.1UF i 1

ChipC. GRM36CK0R5C50PT

Chip C. GRM36B103K16PT i 1

Chip C. ¡GRM36B103K16PT

Chip C. i GRM36CH10OD5OPT

Chip C. GRM36B102K50PT 1

Chip C.

Chip C. GRM36CK020C50PT 1

Chip C. 1005 CH 50V 7PF D

Chip C.

Chip C. i GRM36CH220J50PT 1

Chip C.

Chip C. GRM36C H040C50PT 1

Chip C. GRM36CH100D50PT

Chip C.

Chip C. GRM36CH120 J50PT

Chip C. GRM36B103K16PT 1 1

Chip C. GRM36B Î02K50PT 1 1

Chip C. GRM36B102K50PT 1 1

Chip C. GRM36B102K50PT

Chip C. GRM36CH101J50PT 1 1

Chip C. GRM36B102K50PT

Chip C. GRM36CJ030C50PT 1

Chip C. GRM36B103K16PT 1

Chip C. GRM36B102K50PT

Chip C. GRM36B103K16PT 1 1

Chip C. GRM36B103K16PT 1 1

Chip C.

Chip C. GRM36CH820J50PT

Chip C. GRM36B223K16PT 1 1

Chip C. GRM36CH221J25PT

Chip Tantalum

Chip C. GRM36B102K50PT 1 1

Chip C. GRM36B102K50PT

Chip C.

Chip C. 1608 B25V 0.1UF 1 1

Chip C. GRM36B102K50PT 1

Chip C.

Chip C. GRM36CH221J25PT 1 1

Parts Name

GRM36B102K50PT 1

2012 B 10V 1UF 1

GRM36CJ030C50PT

GRM36CH120 J50PT

GRM36CH040C50PT 1 1

GRM36B1D2K50PT

1608 B 25V 0.1UF

1608 B 25V 0.1UF 1 1

1005 CH 50V 7PF D

1608 B 25V 0.1UF

GRM36B102K50PT

TMCMA1C106MTR 1

TMCMA1C106MTR I 1 1

GRM36CH100D50PT

1608 B 25V 0.1UF

GRM36B472K25PT

1608 B 25V0.1UF 1

1608 B 25V0.1UF

GRM36B103K16PT 1

GRM36B103K16PT

1608 B 50V 0.047UF K 1 1

1608 B25V 0.1UF

Qtv

1

1

1

t

1

1

1

1

1i 1

1

1

1

1

1

1

1

1

1

11 1

1

1

1

1

1

1

1

1

1

1

1

11 1

1 ! 1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Page 32

j Part No. ! Description Parts Name

C381 ¡CU3503 Chip C. ÍGRM36CK020C50PT I 1i t C472 ¡CE0339 ¡Electrolytic C.

C382 ¡CU3505 ; Chip C. • ;GRM36CH040C50PT 1 1] . 1

C383 ÍCU3523 ¡Chip C. 'GRM36CH101J50PT ! 1 j 1 C474 ¡CU3535 Chip C. GRM36B102K50PT 1 1

C384 ¡CU3520 ! Chip C.

C386 ¡CU3526 ¡Chip C. GRM36CH181J25PT ¡ 11 1

C387 ÍCU3047

C389 ;CU3538

C390 j CU3523

C391 ICU3503 ¡Chip C. GRM36CK020C50PT i 1

C392 CU3512 ¡Chip C. GRM36CH120J50PT ! 1

C393 CU3506

C394 CU3507

C395 CU3535

C396 CU3547

C397 CU3535

C398 CU3504

CU3535

C399

C401 CU3505

C402 CU3511

CU3111

C403

C404 CU3547

CU3505

C405

C406 CU3511

C407 CS0424

CU3102

C408

C409

CU3549

C410 CU3111

CU3535

C411

C412 CU3111

C413 CU3549

CU3535

C414

C415 CU3523

C416 CU3523

C417 ¡CU0002 Chip C. 2012 CH 50V 1.0PFC

C418 ÍCU3503